(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4202658号

(P4202658)

(45) 発行日 平成20年12月24日(2008.12.24)

(24) 登録日 平成20年10月17日(2008.10.17)

(51) Int.Cl.

F 1

G 11 B 20/12 (2006.01)

G 11 B 20/10 (2006.01)G 11 B 20/12 103

G 11 B 20/10 311

請求項の数 8 (全 22 頁)

(21) 出願番号 特願2002-46591 (P2002-46591)

(22) 出願日 平成14年2月22日 (2002.2.22)

(65) 公開番号 特開2003-249029 (P2003-249029A)

(43) 公開日 平成15年9月5日 (2003.9.5)

審査請求日 平成17年1月4日 (2005.1.4)

前置審査

(73) 特許権者 308014341

富士通マイクロエレクトロニクス株式会社

東京都新宿区西新宿二丁目7番1号

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100105957

弁理士 恩田 誠

(72) 発明者 山脇 昌史

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

審査官 藤原 敏利

最終頁に続く

(54) 【発明の名称】データ書き込み装置及びDVDフォーマットデータ生成方法

(57) 【特許請求の範囲】

【請求項 1】

DVDメディアに対するDVDフォーマットデータの生成処理及び書き込み処理を制御する中央処理部と、前記DVDフォーマットデータの生成処理及び書き込み処理を、複数のセクタで構成されるブロック毎に行うコントローラ部とを備えたデータ書き込み装置であって、

前記コントローラ部は、

1ブロックずつのユーザーデータを取り込んで、バッファメモリに格納するホストインターフェースと、前記バッファメモリから前記ユーザーデータを読み出して、1ブロックずつDVDフォーマットデータに変換して、前記バッファメモリに格納する誤り訂正部と、

前記DVDフォーマットデータを前記バッファメモリから1ブロックずつ読み出して、DVDメディアに対し書き込み処理を行うフォーマッタとを含み、

前記誤り訂正部は、前記バッファメモリからの前記ユーザーデータの読み出しと並行して、最終ブロックのデータの足りないセクタに対するパディング処理データを生成して前記ユーザーデータに対してパディング処理を行うパディング処理回路を備え、

前記パディング処理回路は、

data type設定レジスタの格納内容に基づいて、前記最終ブロックのパディング処理対象セクタを検出する検出部と、

前記DVDフォーマットデータの生成時に、前記検出部の出力信号に基づいてパディン

10

20

グ処理データを生成して出力するパディング処理データ生成部とから構成したことを特徴とするデータ書き込み装置。

【請求項 2】

前記誤り訂正部には、最終ブロックの各セクタのID部にdata typeを設定するdata type設定部を備えたことを特徴とする請求項1記載のデータ書き込み装置。

【請求項 3】

前記誤り訂正部は、前記最終ブロックのDVDフォーマットデータの生成後に書き込み終了フラグを設定し、前記フォーマッタは前記最終ブロックのDVDフォーマットデータの書き込み終了後、前記書き込み終了フラグに基づいてリンクング部の書き込み処理を行うことを特徴とする請求項1または2記載のデータ書き込み装置。

10

【請求項 4】

前記data type設定レジスタには、前記最終ブロックの各セクタに対応するビットにそれぞれdata typeを格納し、前記検出部は前記data type設定レジスタの隣り合うビットの格納内容のAND論理を算出して出力することを特徴とする請求項1乃至3のいずれか一項に記載のデータ書き込み装置。

【請求項 5】

前記data type設定レジスタには、前記最終ブロックの各セクタに対応するビットにそれぞれdata typeを格納し、前記検出部は前記data type設定レジスタの格納内容に基づいてパディング処理対象セクタの先頭セクタを検出するデコード回路で構成したことを特徴とする請求項1乃至3のいずれか一項に記載のデータ書き込み装置。

20

【請求項 6】

前記data type設定レジスタには、前記最終ブロックの各セクタにおいてdata typeを設定する先頭セクタの値を格納し、前記検出部は前記先頭セクタの値に「1」を加算してパディング処理対象セクタの先頭セクタを検出する加算器で構成したことを特徴とする請求項1乃至3のいずれか一項に記載のデータ書き込み装置。

【請求項 7】

前記パディング処理データ生成部には、前記検出部の出力信号に基づいて、前記バッファメモリに格納されているデータに代えて、パディング処理データを選択する選択回路を設けたことを特徴とする請求項1乃至6のいずれかに記載のデータ書き込み装置。

【請求項 8】

30

1ブロックずつのユーザーデータをホストインターフェースを介して取り込んで、バッファメモリに格納するステップと、

前記バッファメモリから誤り訂正部への前記ユーザーデータの読み出しと並行して、前記ユーザーデータにおける最終ブロックのデータの足りない領域を示す情報に基づいて前記データの足りない領域をパディング処理するステップと、

1ブロックずつDVDフォーマットデータに変換して前記バッファメモリに格納し、前記DVDフォーマットデータを前記バッファメモリからフォーマッタに1ブロックずつ読み出して、DVDメディアに対し書き込み処理を行うステップと、

最終ブロックのDVDフォーマットデータ生成時に前記誤り訂正部でパディング処理対象セクタに対するパディング処理データの生成を行うステップと、

を含むことを特徴とするDVDフォーマットデータ生成方法。

40

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、DVD-R、DVD-RW等の各種DVDメディアへのデータ書き込み装置に関するものである。

【0002】

近年、高密度、大容量媒体としてDVD (Digital Versatile Disc) の各種メディアが注目されている。また、書き込み可能なDVD-R、DVD-RW等のメディアも広く利用されるようになっている。このようなDVD-R、DVD-RW、DVD+RWメディア

50

では、書き込み動作時に特有の書き込み処理が必要であり、これらのメディアの大容量媒体としての特性を最大限活用するために、その書き込み動作を迅速に行うことが必要となつている。

【0003】

【従来の技術】

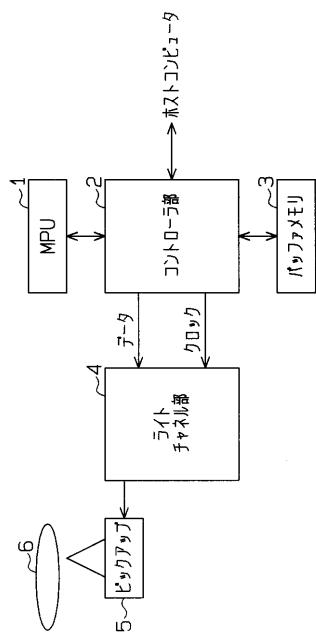

DVD-Rを例にとって、DVDメディアに対するデータ書き込み装置の概要を図13に示す。MPU1により制御されるコントローラ部2は、ホストコンピュータからインターフェースを介して入力されるデータの処理を行い、バッファメモリ3に格納する。

【0004】

また、コントローラ部2はバッファメモリ3に格納されているデータを読み出して、クロック信号とともにライトチャネル部4に出力する。ライトチャネル部4は入力されたデータを、ピックアップ5を介してDVD-Rメディア6に書き込む。

【0005】

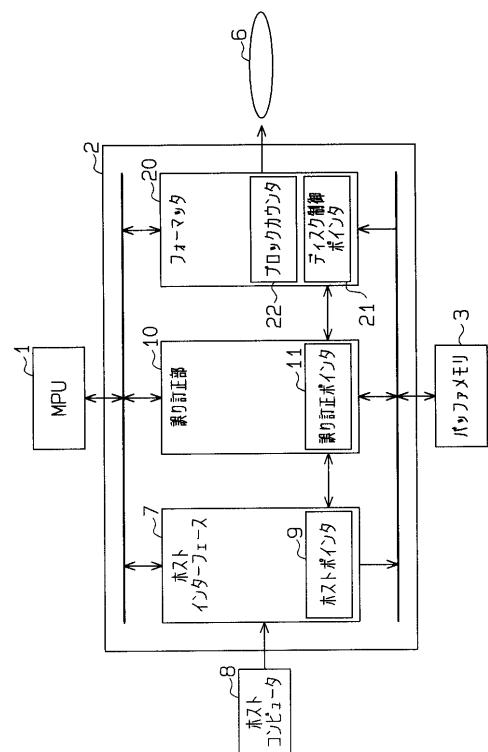

前記コントローラ部2の具体的構成を図14に従って説明する。ホストインターフェース7は、ホストコンピュータ8から転送されるデータをバッファメモリ3に格納し、1ブロック分に相当する32kバイトのデータをバッファメモリ3に格納した時点でホストポインタ9を更新し、その値を誤り訂正部(ECC)10に出力する。

【0006】

誤り訂正部10は、ホストポインタ9と自身の誤り訂正ポインタ11との値に差が生じた場合、バッファメモリ3内に32kバイトのデータが格納されたことを認識し、そのデータをバッファメモリ3から読み出して誤り検出符号の計算及びデータのスクランブル処理を行って、DVDフォーマットのデータを生成した後、そのデータをバッファメモリ3に書き戻す。

【0007】

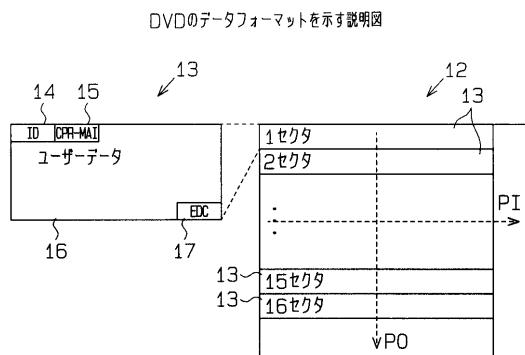

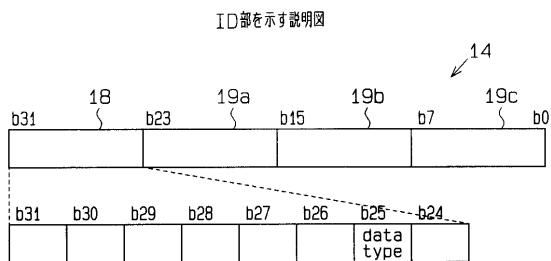

この誤り訂正部10の動作を図15及び図16に従って詳細に説明する。図15に示すように、1つのブロック12は16のセクタ13で構成される。各セクタ13は、6バイトのID部14と、同じく6バイトの CPR-MAI部15と、2kバイトのユーザーデータ16と、4バイトのEDC(Error Detection Code)部17で構成される。

【0008】

ID部14は、図17に示すように、1バイトのセクタ情報18と、3バイトのセクタアドレス19a, 19b, 19cとで構成され、さらに読み取ったID部14に誤りが含まれているか否かを判別するための2バイトの検出符号が付加される。

【0009】

CPR-MAI部15は、コピー制限等を設定するために使用される。EDC部17は、ID部14からユーザーデータ16の最終バイトまで演算することにより得られる誤り検出符号が格納される。

【0010】

ID部14及びCPR-MAI部15は、通常誤り訂正部10内のレジスタに設定されているか、あるいはバッファメモリ3内の所定の領域にあらかじめ書き込まれており、誤り検出符号あるいは誤り訂正符号の生成に際し、データの一部として使用される。

【0011】

上記のように構成されたセクタ13を16セクタ分集め、縦方向の16バイト長の誤り訂正符号POと、横方向の10バイト長の誤り訂正符号PIとを付加したフォーマットで1つのブロック12が構成される。

【0012】

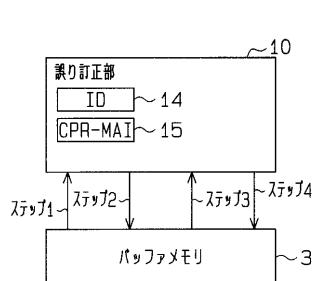

上記のような誤り検出符号及び誤り訂正符号PI, POの生成動作を説明すると、図16に示すように、誤り訂正部10はまずバッファメモリ3からユーザーデータを読み出し、誤り訂正部10に格納されているID部14やCPR-MAI部15をもとにEDC部17に格納する誤り検出符号を生成する(ステップ1)。

【0013】

10

20

30

40

50

次いで、誤り訂正部 10 はデータをバッファメモリ 3 に書き戻す（ステップ 2）。このとき、ユーザーデータ 16 についてはスクランブル処理を行ってバッファメモリ 3 に書き戻す。このスクランブル処理は、例えば所定の数式で求められた値とデータとの排他的論理和を算出する処理を行う。

【0014】

このような動作を 16 セクタ分行った後、誤り訂正部 10 は再びバッファメモリ 3 からデータを読み出し（ステップ 3）、誤り訂正符号 P I, P O の生成を行い、その誤り訂正符号 P I, P O を付加した 1 ブロック分のデータを再びバッファメモリ 3 に書き戻す（ステップ 4）。

【0015】

このとき、誤り訂正符号 P I, P O の生成はそれぞれ独立して行う必要があるため、ステップ 3 とステップ 4 が 2 回繰り返される。

誤り訂正符号 P I, P O の生成が終了すると、誤り訂正部 10 は誤り訂正ポインタ 11 を更新し、その更新値をフォーマッタ 20 に出力する。

【0016】

フォーマッタ 20 は、誤り訂正ポインタ 11 の値と、自身のディスク制御ポインタ 21 との値に差が生じると、バッファメモリ 3 に格納されている 1 ブロック分のデータを読み出して、DVD-R メディア 6 に書き込む。

【0017】

フォーマッタ 20 における誤り訂正ポインタ 11 の値とディスク制御ポインタ 21 の値との比較動作は、当該ブロックの書き込み動作の開始時に行われる。各ポインタ 11, 21 の値に差が生じていない場合、すなわち誤り訂正部 10 での誤り訂正符号 P I, P O の生成が間に合わなかった場合には、バッファメモリ 3 には書き込むべきデータが格納されていないので、フォーマッタ 20 はデータエンプティと判断して、書き込み処理を中止する。

【0018】

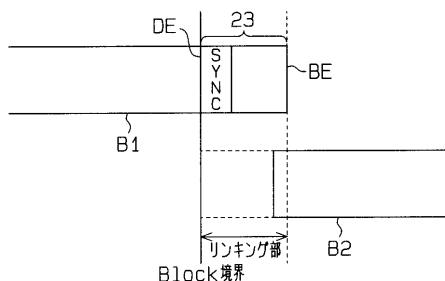

次に、DVD-R メディア 6 に対する書き込み処理に特有な処理動作を説明する。DVD-R メディア 6 に対する書き込み処理には、リンクングロスエリア（Linking Loss Area）のデータ処理、データ ID 部のビット付加及びリンクング部に対する書き込み処理が必要となる。

【0019】

リンクング部は、前回書き込んだデータの終端と、次に書き込むデータの始端とのつなぎの部分を指し、書き込み済データの再生時につなぎの部分が問題なく再生されるようにするためには存在する。

【0020】

図 18 に示すように、前回書き込まれたデータの最終ブロック B1 の終端部分は、次に書き込まれる別データの先頭ブロック B2 の先頭からある程度進んだ位置まで延長して書き込む必要がある。

【0021】

すなわち、最終ブロック B1 の終端部分は、データの終端 D E から、さらにシンクマーク SYNC と、ID 部及び 00h 等のデータをリンクング部 23 として終端 B E まで書き込んで終了する。

【0022】

また、次に書き込まれる別データの先頭ブロック B2 は、前回書き込まれたデータの終端 B E を基準として ± 数バイトの範囲から書き込みを開始する必要がある。

【0023】

次に、最終ブロック B1 及び先頭ブロック B2 には、リンクングロスエリアを設ける必要がある。すなわち、DVD のデータ構成は 1 ブロックが 32k バイト（16 セクタ）で構成されるが、書き込むべきデータの総量が 32k バイトで割り切れない場合、最終ブロック B1 と、先頭ブロック B2 とにリンクングロスエリアが設けられる。

10

20

30

40

50

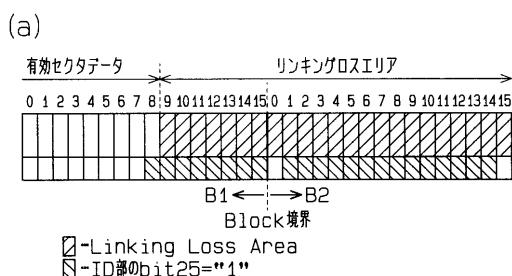

## 【0024】

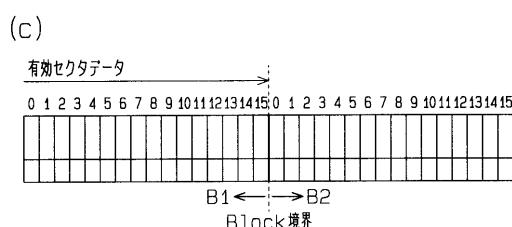

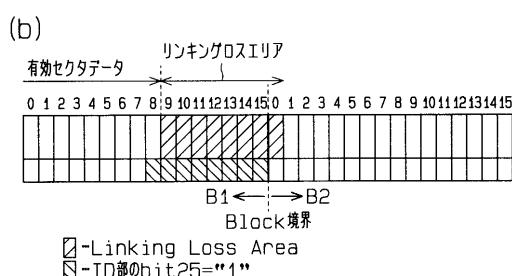

このリンクグロスエリアは、図19(a)に示す32kリンクと、図19(b)に示す2kリンクとがある。32kリンクは、最終ブロックB1の有効セクタデータが16セクタに満たない場合、そのデータ不足セクタと、次に書き込まれる別データの先頭ブロックB2の16セクタをリンクグロスエリアとするものである。

## 【0025】

2kリンクは、最終ブロックB1の有効セクタデータが16セクタに満たない場合、そのデータ不足セクタと、次に書き込まれる別データの先頭ブロックB2の2セクタをリンクグロスエリアとするものである。

## 【0026】

また、図19(c)に示すように、最終ブロックB1の有効セクタデータが丁度16セクタあり、かつ続く開始ブロック中にリンクグロスエリアを設けないケースも許されており、このようなケースをロスレスリンクという。

## 【0027】

このリンクグロスエリアを構成する各セクタのユーザーデータ部分には、00hのデータをパディングすることが規格で決められている。さらに、リンクグロスエリアが設定される場合には、図17に示すように、一部のセクタのID部のビット25(data type)の位置に「1」を設定する必要がある。

## 【0028】

ビット25の位置に「1」を設定する対象セクタOSは、図19(a)に示す32kリンクでは、最終ブロックB1において有効セクタデータが格納される最終セクタと、データ不足セクタと、先頭ブロックB2において、リンクグロスエリアの先頭セクタと最終セクタを除く各セクタである。

## 【0029】

図19(b)に示す2kリンクでは、最終ブロックB1において有効セクタデータが格納される最終セクタと、データ不足セクタの各セクタである。

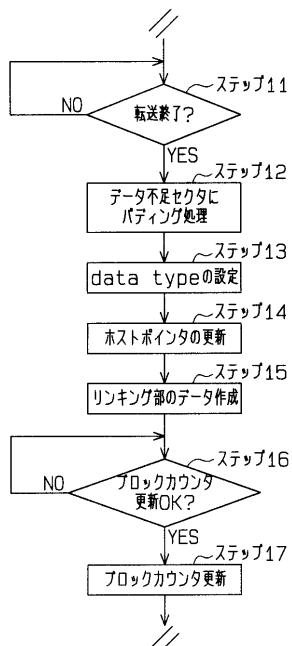

このようなDVD-Rメディア6に対する書き込み終了処理動作は、MPU1により制御され、その処理動作を図20に従って説明する。

## 【0030】

MPU1は、ホストコンピュータから転送されるデータの終了タイミングを検出すると(ステップ11)、最終ブロックB1のデータ不足セクタに00hのデータを書き込むパディング処理を行う(ステップ12)。

## 【0031】

このパディング処理は、データ不足セクタに00hを書き込むハードウェアを用意するか、あるいはMPU1がバッファメモリ3内のデータ不足セクタに00hを書き込む処理を行う。

## 【0032】

次いで、ID部14のビット25にdata typeの設定が必要であるので、誤り訂正部10に対し、data typeビットの設定を行う(ステップ13)。

次に、MPU1は誤り訂正部10に誤り訂正符号の生成を指示する。この誤り訂正符号の生成の指示は、ホストインターフェース7のホストポインタ9の更新をMPU1で行ってもよい(ステップ14)。そして、誤り訂正部10では最終ブロックB1の誤り訂正符号の生成が行われる。

## 【0033】

次いで、誤り訂正符号の生成終了後に、MPU1は図18に示すリンクグロス部23のデータを作成し(ステップ15)、フォーマッタ20のブロックカウンタ22の値を更新する(ステップ16, 17)。

## 【0034】

ステップ16では、MPU1によるブロックカウンタ22の更新のタイミングと、フォーマッタ20によるブロックカウンタ22の更新のタイミングとが一致しないようにして、

10

20

30

40

50

ブロックカウンタ 22 の更新処理の誤動作を防止している。

【0035】

フォーマッタ 20 は、ブロックカウンタ 22 の値から書き込み終了位置を認識し、書き込み終了位置を認識後は、リンク処理を行って書き込み処理を終了する。

【0036】

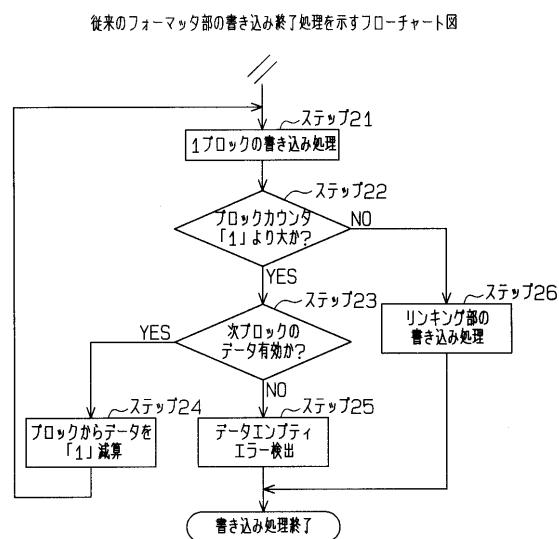

上記のような書き込み終了処理動作時のフォーマッタ 20 の動作を図 21 に従って説明する。

フォーマッタ 20 は、DVD-R メディア 6 に対し、データの書き込み処理を 1 ブロックずつ行うが、各ブロックの書き込み処理が終了する度に、次に書き込み処理を行うブロックのデータが有効か否かをチェックする。

10

【0037】

すなわち、1 ブロックの書き込み処理が終了すると（ステップ 21）、フォーマッタ 20 はブロックカウンタ 22 の値をチェックし（ステップ 22）、その値が「1」より大きい値であれば、次に書き込み処理を行うブロックのデータが有効か否かをチェックする（ステップ 23）。

【0038】

そのチェック動作を説明すると、フォーマッタ 20 は誤り訂正部 10 の誤り訂正ポインタ 11 と、自身のディスク制御ポインタ 21 の値を比較し、不一致であればバッファメモリ 3 に書き込み処理を行うべきデータが格納されていることを認識する。

20

【0039】

この場合には、ブロックカウンタ 22 の値を「1」減算して（ステップ 24）、ステップ 21 に復帰し、次のブロックの書き込み処理を行う。

ステップ 23 において、上記ポインタの値が一致している場合には、フォーマッタ 20 はバッファメモリ 3 内に書き込み処理を行うべきデータが未だ格納されていないと認識し、データエンプティエラーを検出して（ステップ 25）、書き込み処理動作を終了する。

【0040】

ステップ 22 において、ブロックカウンタの値が「1」以下であれば、フォーマッタ 20 は最終ブロック B1 の書き込み処理が終了したことを認識して、リンク部 23 の書き込み処理を行い（ステップ 26）、書き込み処理を終了する。

【0041】

30

【発明が解決しようとする課題】

上記のような DVD-R メディア 6 に対する書き込み終了処理動作では、MPU 1 は、リンクグロスエリアへの 00h のパディング処理と、リンクグロスエリア等の対象セクタの ID 部 14 に対する data type の設定と、誤り訂正符号の生成指示と、リンク部 23 への書き込みデータの生成と、フォーマッタ 20 への書き込み処理動作の終了指示等が必要となる。

【0042】

すなわち、DVD-R メディア 6 に対する書き込み処理動作では、あらかじめデータ転送量を知ることはできないため、ホストコンピュータ 8 から転送終了コマンドを受信した後に、上記のような書き込み終了動作を行わなければならない。

40

【0043】

上記のような書き込み終了動作に時間要すると、フォーマッタ 20 においてデータエンプティエラーが発生するおそれがある。DVD-R メディア 6 では、データの書き直しができないため、データエンプティエラーが発生すると、それまでに書き込まれたデータを破棄し、新たな領域に再度書き込み処理動作を最初からやり直す必要がある。

【0044】

従って、データエンプティエラーが発生すると、データの書き込み処理効率が低下するという問題点がある。

この発明の目的は、DVD フォーマットデータの書き込み終了処理動作において、データエンプティエラーの発生を防止して、書き込み処理効率を向上させ得るデータ書き込み装

50

置を提供することにある。

#### 【0045】

##### 【課題を解決するための手段】

中央処理部は、DVDメディアに対するDVDフォーマットデータの生成処理及び書き込み処理を制御し、コントローラ部は前記DVDフォーマットデータの生成処理及び書き込み処理を、複数のセクタで構成されるブロック毎に行う。前記コントローラ部には、最終ブロックのリンクグロスエリアに対するパディング処理データの生成を行うパディング処理回路を設けた。

#### 【0046】

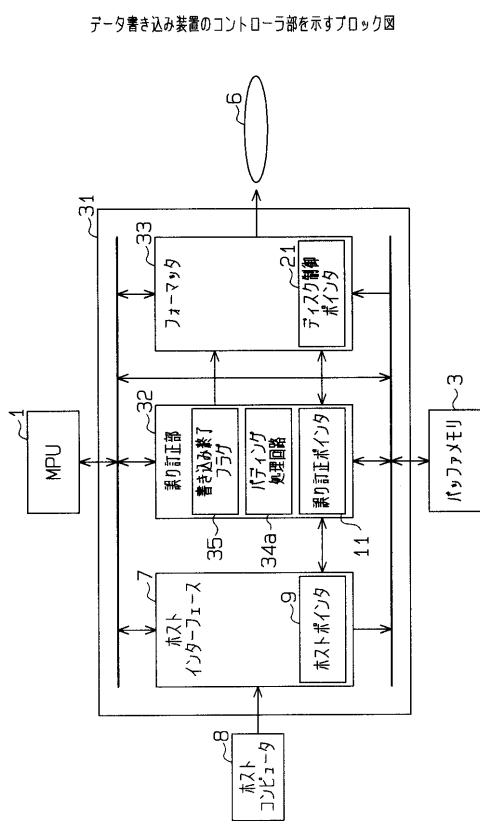

また、図1に示すように、コントローラ部31は、1ブロックずつのユーザーデータを取り込んで、バッファメモリ3に格納するホストインターフェース7と、前記バッファメモリ3から前記ユーザーデータを読み出して、1ブロックずつDVDフォーマットデータに変換して、前記バッファメモリ3に格納する誤り訂正部32と、前記DVDフォーマットデータを前記バッファメモリ3から1ブロックずつ読み出して、DVDメディアに対し書き込み処理を行うフォーマッタ33とから構成される。前記誤り訂正部32に、前記バッファメモリからの前記ユーザーデータの読み出しと並行して、最終ブロックのデータの足りないセクタに対するパディング処理データを生成して前記ユーザーデータに対してパディング処理を行うパディング処理回路34aを備えた。このパディング処理回路34aは、data type設定レジスタの格納内容に基づいて、前記最終ブロックのパディング処理対象セクタを検出する検出部と、前記DVDフォーマットデータの生成時に、前記検出部の出力信号に基づいてパディング処理データを生成して出力するパディング処理データ生成部とから構成される。

10

20

#### 【0047】

##### 【発明の実施の形態】

###### (第一の実施の形態)

以下、この発明を具体化したデータ書き込み装置の第一の実施の形態を説明する。なお、前記従来例と同一構成部分は、同一符号を付して説明する。

#### 【0048】

図1は、データ書き込み装置のコントローラ部31を示す。このコントローラ部31は、誤り訂正部32及びフォーマッタ33を除いて、前記従来例と同様に構成される。

30

#### 【0049】

前記誤り訂正部32には、前記従来例の誤り訂正部10に対しパディング処理回路34aと、書き込み終了フラグ35が付加される。

前記フォーマッタ33は、前記従来例のフォーマッタ20からブロックカウンタ22が省略されている。

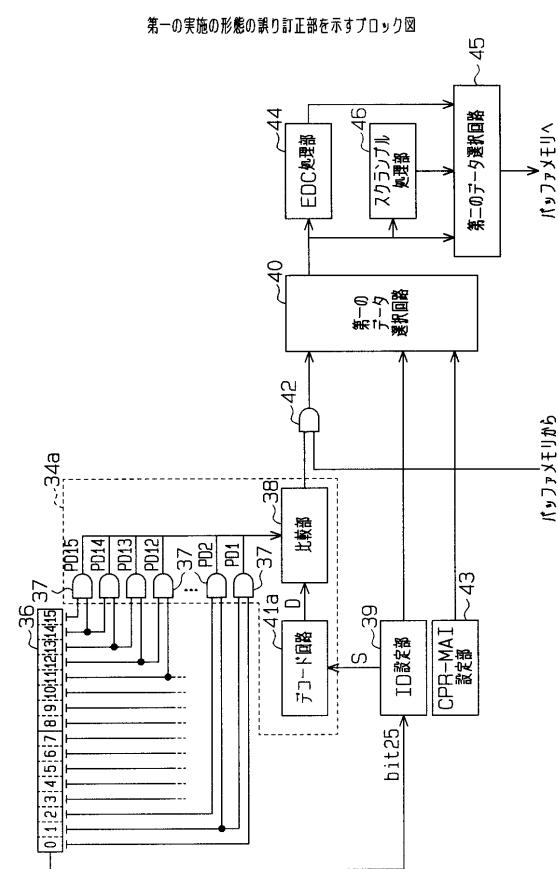

#### 【0050】

前記誤り訂正部32のパディング処理回路34aに関する構成を図2に従って説明する。data type設定レジスタ36は、16ビットのフリップフロップ回路で構成される。このレジスタ36は、前記従来例と同様に誤り訂正部32内に備えられ、書き込みデータの最終ブロックにおいて所定のセクタのビット25にdata typeを設定するためのレジスタであって、各ビットが最終ブロックの16のセクタにそれぞれ対応している。

40

#### 【0051】

そして、図19(a)に示すように、例えば最終ブロックの最初のセクタ0からセクタ8まで、有効セクタデータが入力されている場合、レジスタ36のビット0~7まで「0」が格納され、ビット8~15まで「1」が格納されることになる。

#### 【0052】

前記data type設定レジスタ36の隣り合う2ビットの格納データは、それぞれAND回路37に入力される。そして、15個のAND回路37の出力信号PD1~PD15はパディング処理対象セクタを示すものであり、上記のようにレジスタ36のビット0~7まで「0」が格納され、ビット8~15まで「1」が格納される場合、出力信号PD1~P

50

D 8までは「0」となり、同P D 9～P D 15が「1」となる。

【0053】

従って、この場合には最終ブロックの10番目のセクタ9から16番目のセクタ15がパディング処理対象セクタであることがわかる。そして、15個のAND回路37の出力信号P D 1～P D 15はそれぞれ比較部38に出力される。

【0054】

前記data type設定レジスタ36の各ビットの出力信号は、ID設定部(data type設定部)39に出力される。このID設定部39は、図17に示すデータID部14に格納するデータを生成するものであり、4バイトのID部14と、2バイトの誤り検出符号を生成して、第一のデータ選択回路40に出力する。

10

【0055】

そして、この生成動作時に、ID設定部39はdata type設定レジスタ36の出力信号に基づいて、各セクタのビット25に設定する値を決定する。

すなわち、上記のようにレジスタ36のビット0～7まで「0」が格納され、ビット8～15まで「1」が格納されている場合には、セクタ8～15のビット25に「1」を設定することになる。

【0056】

このID設定部39は、データ処理を1セクタずつ行い、1セクタのデータ処理を行う度にID値、すなわちセクタアドレスを1ずつインクリメントする。このID値のビット3～0をセクタ値Sとし、そのセクタ値Sとdata type設定レジスタ36の各ビットの値に基づいて、上記のようにビット25に「1」を設定するセクタが決定される。

20

【0057】

前記セクタ値Sは、デコード回路41aに入力される。デコード回路41aは、図3に示す変換テーブルに基づいてセクタ値Sをデコードして、そのデコード値Dを前記比較部38に出力する。

【0058】

前記デコード値Dは、セクタ値Sを16ビットの2値信号に変換して出力するものである。

前記比較部38は、前記AND回路37の出力信号P D 1～P D 15と、デコード値Dの最下位ビットを除く15ビットとを比較する。そして、例えばセクタ値Sが10であると、デコード値Dは「0000000000100000」となり、ここで前記出力信号P D 10が「1」であると、当該10番目のセクタは、パディング処理対象セクタとなり、比較部38は「0」をAND回路42に出力する。

30

【0059】

このようにして、各セクタの書き込み処理動作時に当該セクタがパディング処理対象セクタであるか否かが比較部38で判定され、前記AND回路37、デコード回路41a及びAND回路42で前記パディング処理回路34aが構成される。

【0060】

前記AND回路42には、前記バッファメモリ3から処理中の当該セクタのユーザーデータが入力される。従って、AND回路42の出力信号はパディング処理対象セクタであれば、すべて「0」となり、パディング処理対象セクタ以外であれば、ユーザーデータがそのまま出力される。

40

【0061】

前記第一のデータ選択回路40には、前記AND回路42の出力信号と、前記ID設定部39の出力信号と、C P R - M A I設定部43の出力信号が入力される。

【0062】

そして、第一のデータ選択回路40は、ID設定部39から出力される6バイトのID部データと、C P R - M A I設定部43から出力される6バイトのC P R - M A I部データと、2048バイトのユーザーデータとをこの順番で出力する。

【0063】

50

EDC処理部44は、第一のデータ選択回路40から出力されるすべてのデータを取り込んで、EDC検出符号を生成し、第二のデータ選択回路45に出力する。

【0064】

スクランブル処理部46は、第一のデータ選択回路40から出力されるユーザーデータを取り込んでスクランブル処理を行い、第二のデータ選択回路45に出力する。

【0065】

第二のデータ選択回路45は、前記第一のデータ選択回路40の出力信号と、EDC処理部44の出力信号と、スクランブル処理部46の出力信号とを取り込み、図15に示す順番で各セクタに書き込み処理を行うために、ID部、CPR-MAI部、スクランブル処理されたユーザーデータ及びEDC部の順番で選択し、バッファメモリ3に出力する。 10

【0066】

前記誤り訂正部32に設けられる書き込み終了フラグ35は、誤り訂正部32において、最終ブロックの誤り訂正符号の生成が終了した時点で設定され、かつそのフラグがフォーマッタ33に出力される。

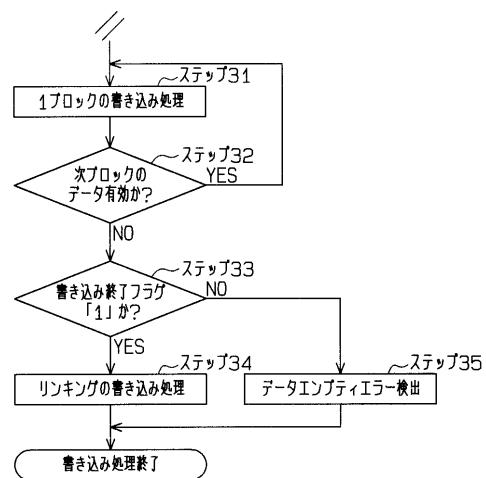

【0067】

図4は、フォーマッタ33の書き込み処理動作を示す。フォーマッタ33は、DVD-Rメディア6に対する書き込み処理を1ブロックずつ行う(ステップ31)。

【0068】

そして、1ブロックの書き込み処理が終了する毎に次ブロックの書き込みデータが有効であるか否か、すなわち誤り訂正部32の誤り訂正ポインタ11と、フォーマッタ33のディスク制御ポインタ21とが一致するか否かを検出する(ステップ32)。 20

【0069】

通常、最終ブロック以外の書き込み処理では、誤り訂正ポインタ11とディスク制御ポインタ21の値は一致しないので、フォーマッタ33は次ブロックの書き込みデータが有効であることを認識して、バッファメモリ3に格納されている次ブロックの書き込みデータを順次書き込み処理する(ステップ31, 32)。

【0070】

ステップ31において、最終ブロックの書き込みデータが終了すると、バッファメモリ3に次ブロックの書き込みデータは存在せず、誤り訂正ポインタ11とディスク制御ポインタ21の値は一致しているため、フォーマッタ33は次ブロックの書き込みデータは有効ではないと認識する(ステップ32)。 30

【0071】

次いで、フォーマッタ33は誤り訂正部の書き込み終了フラグ35の値を確認する(ステップ33)。書き込み終了フラグ35は、最終ブロックの誤り訂正符号の生成が終了した時点で「1」が設定されているので、フォーマッタ33は最終ブロックの書き込み処理に続いて、リンクング部の書き込み処理を行い(ステップ34)、書き込み処理を終了する。

【0072】

また、ステップ32において、最終ブロック以外の書き込み処理で、誤り訂正ポインタ11とディスク制御ポインタ21の値が一致すると、ステップ33において、書き込み終了フラグ35は「0」であるので、フォーマッタ33はデータエンプティエラーを検出して(ステップ35)、書き込み処理を終了する。 40

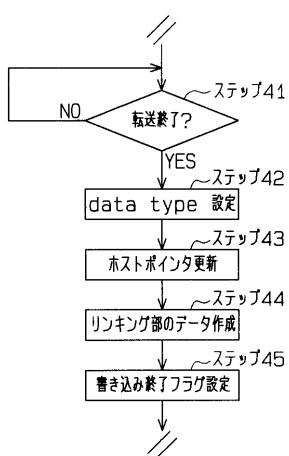

【0073】

図5は、MPU1(中央処理部)の書き込み終了処理動作を示す。MPU1は、ホストコンピュータ8からの書き込みデータの転送終了を検出すると(ステップ41)、data type設定レジスタ36にdata type設定レジスタ36の設定を行う(ステップ42)。

【0074】

次いで、MPU1はホストインターフェース7のホストポインタ9を更新する(ステップ43)。すると、誤り訂正部32ではdata type設定レジスタ36の格納内容に基づいて、最終ブロックを構成する各セクタのビット25にdata typeの設定を行い、さらにパディ 50

ング処理を行うセクタの検出を行い、当該セクタにパディング処理を行う。

【0075】

次いで、誤り訂正部32が最終ブロックの各セクタのID部、CPR-MAI部、スクランブル処理されたユーザーデータ及びEDC部を生成している間に、MPU1はリンク部に書き込むデータの生成を行う(ステップ44)。

【0076】

このリンク部23は、DVD-RのGeneral Version2.0の規格によれば、16バイトのデータを最終ブロックの書き込みデータに統一して書き込めばよい。その16バイトの内訳は、ID部及びCPR-MAI部で12バイトであり、残りの4バイトがユーザーデータである。

10

【0077】

従って、MPU1が生成するのは4バイトのユーザーデータのみであり、このようなリンク部23の書き込みデータがMPU1によりバッファメモリ3に書き込まれる。

【0078】

次いで、MPU1は誤り訂正部32の書き込み終了フラグ35に「1」を設定して(ステップ45)、ホストコンピュータ8の指示を待つ状態となる。

上記のように構成されたDVD-Rメディア6に対する書き込み処理装置では、次に示す作用効果を得ることができる。

(1) 最終ブロックの各セクタのID部14のビット25に対するdata typeの設定は、MPU1によりdata type設定レジスタ36に格納された内容に基づいて、誤り訂正部32のID設定部39で設定することができる。

20

(2) パディング処理回路34aでは、AND回路37でdata type設定レジスタ36の隣り合うビットのAND論理を演算することにより、MPU1による処理を介在させることなく、パディング処理を必要とするセクタを検出することができる。

(3) パディング処理を必要とするセクタには、MPU1による処理を介在させることなく、誤り訂正部32によりパディング処理を行うための00hの書き込みデータを生成して、バッファメモリ3に書き戻すことができる。

(4) パディング処理を行うための00hの書き込みデータは、セクタ値をデコード回路41aでデコードしたデコード信号Dと、AND回路37の出力信号PD1～PD15とを比較部38で比較する。そして、その比較結果とバッファメモリ3から読み出される書き込みデータとのAND論理を演算することにより生成することができる。

30

(5) 誤り訂正部32にパディング処理回路34aを付加するだけで、MPU1による処理を介在させることなく、パディング処理を行うための00hの書き込みデータを生成することができる。

(6) 誤り訂正部32での最終ブロックのデータ処理に並行して、MPU1でリンク部23への書き込みデータの生成を行うことができる。

(7) 誤り訂正部32に書き込み終了フラグ35を設定したことにより、フォーマッタ33による最終ブロックの書き込み処理が終了した後、直ちにリンク部23の書き込み処理を行うことができる。従って、リンク部23の書き込み処理に移行する際ににおけるデータエンプティエラーの発生を未然に防止することができる。

40

(8) 書き込み終了処理動作時に、MPU1の負荷を軽減して、データエンプティエラーの発生を未然に防止することができる。

【0079】

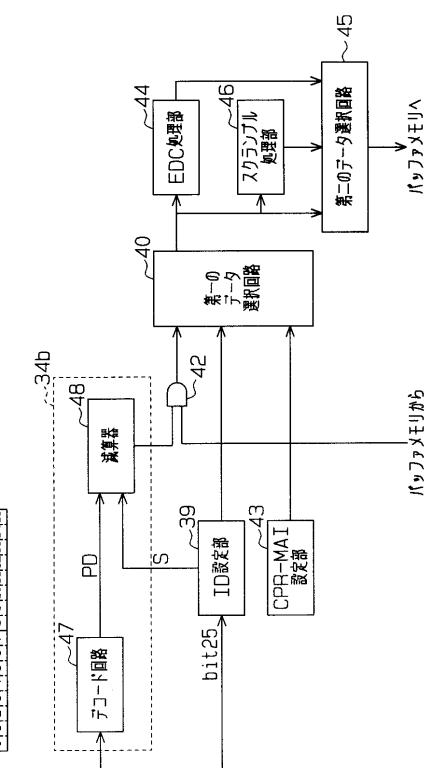

(第二の実施の形態)

図6は、第二の実施の形態を示す。この実施の形態は、前記第一の実施の形態のパディング処理回路34aの構成をパディング処理回路34bに変更したものであり、その他の構成は第一の実施の形態と同様である。前記実施の形態と同一構成部分は、同一符号を付して説明する。

【0080】

パディング処理回路34bは、デコード回路47と、減算器48とで構成される。

50

デコード回路47は、data type設定レジスタ36の各ビットの格納データを図7に示す変換テーブルに基づいてデコードして、PD値を生成し、前記減算器48に出力する。

【0081】

すなわち、最終ブロックを構成するセクタ0～16のうち、例えばセクタ8以降でdata typeが「1」である場合、すなわちID部のビット25に「1」を設定する場合には、デコード回路47はPD値「9」を出力する。これは、セクタ9以降がパディング処理対象セクタであることを示す。

【0082】

前記減算器48は、ID設定部39から出力されるセクタ値Sから前記PD値を減算して、その減算結果が0以上となったとき、Lレベルの信号をAND回路42に出力する。

10

【0083】

すなわち、PD値が「9」である場合には、セクタ9以降でパディング処理が行われる。このような動作により、このパディング処理回路34bを備えた書き込み処理回路では、前記第一の実施の形態と同様な作用効果を得ることができるとともに、パディング処理回路34bをさらに簡略化することができる。

【0084】

(第三の実施の形態)

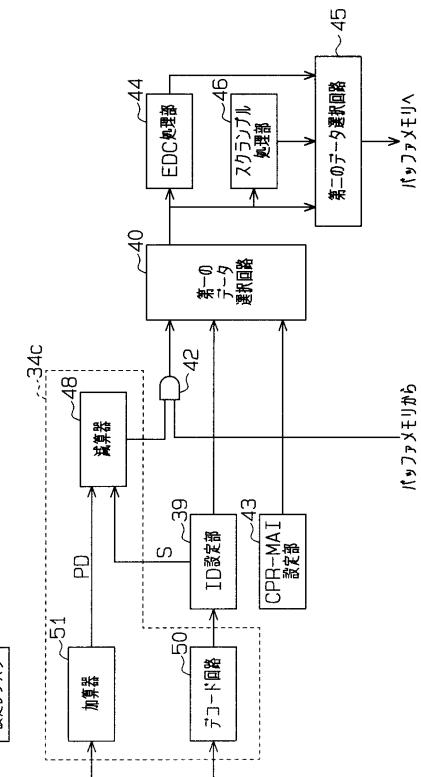

図8は、第三の実施の形態を示す。この実施の形態は、前記第二の実施の形態のdata type設定レジスタ36及びパディング処理回路34bの構成を変更したものであり、その他の構成は第二の実施の形態と同様である。前記実施の形態と同一構成部分は、同一符号を付して説明する。

20

【0085】

前記第一及び第二の実施の形態では、data type設定レジスタは、最終ブロックの各セクタに対応した15ビットのレジスタで構成されるが、この実施の形態のdata type設定レジスタ49には、最終ブロックにおいて、data typeに最初に「1」を設定するセクタ値がMPU1により設定される。

【0086】

data type設定レジスタ49の格納内容は、デコード回路50に入力される。デコード回路50は、図9に示す変換テーブルに基づいて、data type設定レジスタ49の格納内容を15ビットのdata type設定値に変換して出力する。

30

【0087】

このdata type設定値は、前記第一及び第二の実施の形態のdata type設定レジスタ36の格納内容に相当するものであり、最終ブロックの各セクタにおいて、data typeに「1」を設定するセクタを示すものである。前記デコード回路50の出力信号は、前記各実施の形態と同様なID設定部39に出力される。

【0088】

前記data type設定レジスタ49の格納内容は、加算器51に入力される。前記加算器51は、data type設定レジスタ49の格納内容に「1」を加算して、PD値として前記第二の実施の形態と同様な減算器48に出力する。

【0089】

40

すなわち、data type設定レジスタ49の格納内容に「1」を加算した値が、パディング処理を開始するセクタ値となる。そして、前記デコード回路50、加算器51及び減算器48とでパディング処理回路34cが構成される。

【0090】

このような構成により、前記第二の実施の形態と同様な作用効果を得ることができる。

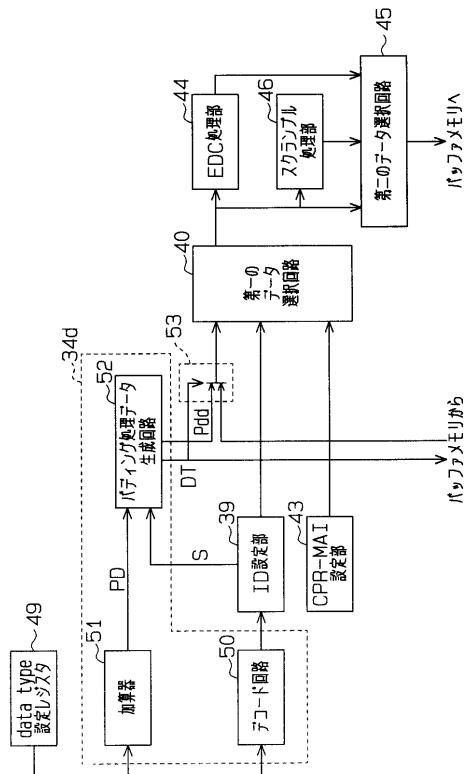

(第四の実施の形態)

図10は、第四の実施の形態を示す。この実施の形態は、前記第三の実施の形態の減算器48とAND回路42に代えて、パディング処理データ生成回路52とセレクタ回路53としたものであり、その他の構成は、第三の実施の形態と同様である。

【0091】

50

パディング処理データ生成回路 52 は、加算器 51 から出力される P D 値と、 I D 設定部 39 から出力されるセクタ値 S との比較に基づいて、パディング処理を行うセクタであることを判別すると、「00h」のパディング処理データ p d d を生成して前記セレクタ回路 53 に出力する。

【0092】

また、パディング処理データ生成回路 52 は、パディング処理を行うセクタであることを判別すると、パディング処理検出信号 D T を前記セレクタ回路 53 及びデータ読み取り回路（図示しない）に出力する。

【0093】

データ読み取り回路は、パディング処理検出信号 D T の入力に基づいて、バッファメモリ 3 からのセクタデータの読み出しを停止する。セレクタ回路 53 は、パディング処理検出信号 D T の入力に基づいて、パディング処理データ生成回路 52 から出力されるパディング処理データ p d d を第一のデータ選択回路 40 に出力する。 10

【0094】

そして、前記デコード回路 50 、加算器 51 及びパディング処理データ生成回路 52 とでパディング処理回路 34d が構成される。

このような構成により、パディング処理対象セクタ以外では、バッファメモリ 3 から読み出されたセクタデータが第一のデータ選択回路 40 に出力され、パディング処理対象セクタとなった場合には、パディング処理データ p d d が第一のデータ選択回路 40 に出力される。 20

【0095】

従って、前記第三の実施の形態と同様な作用効果を得ることができるとともに、パディング処理動作時にはバッファメモリ 3 からのデータ読み出し動作を停止することができるので、消費電力を低減することができる。

【0096】

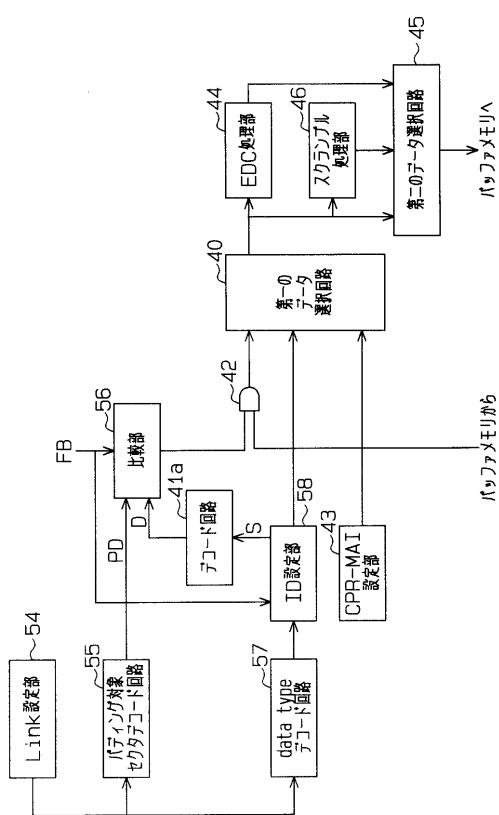

（第五の実施の形態）

図 11 及び図 12 は、第五の実施の形態を示す。この実施の形態は書き込み開始時の先頭ブロックを構成する各セクタへのビット 25 への data type 「 1 」 の設定及びパディング処理を行うための構成を備えた誤り訂正部を示す。

【0097】

Link 設定部 54 は、リンクグロスエリアが図 19 ( a ) に示す 32k - Link であるか、あるいは同図 ( b ) に示す 2k - Link であるかが MPU1 により設定される。 30

【0098】

Link 設定部 54 の格納内容は、パディング対象セクタデコード回路 55 に入力される。パディング対象セクタデコード回路 55 は、図 12 ( a ) に示す変換テーブルに基づいて、パディング対象セクタに対応するビットを「 1 」とした P D 値を出力する。

【0099】

すなわち、先頭ブロックのパディング処理対象セクタは、 32k - Link であるか、あるいは 2k - Link であるかにより決定されるので、パディング対象セクタが変換テーブルにより自動的に決定されて P D 値として比較部 56 に出力される。 40

【0100】

Link 設定部 54 の格納内容は、 data type デコード回路 57 に入力される。 data type デコード回路 57 は、図 12 ( b ) に示す変換テーブルに基づいて、 data type に「 1 」を設定するセクタに対応するビットを「 1 」として I D 設定部 58 に出力する。

【0101】

すなわち、 data type に「 1 」を設定するセクタは、 32k - Link であるか、あるいは 2k - Link であるかにより決定されるので、対象セクタが変換テーブルにより自動的に決定されて出力される。

【0102】

前記比較部 56 及び I D 設定部 58 には先頭ブロック検出信号 F B が入力される。そして 50

、先頭ブロック検出信号FBが入力されたときに限り、比較部56及びID設定部58が動作するように構成される。上記以外の構成は、前記第一の実施の形態と同様である。

【0103】

このような構成により、先頭ブロックの書き込み処理動作時には、data typeデコード回路57の出力信号に基づいて、対象セクタのビット25にdata typeの設定を行うことができる。

【0104】

また、パディング対象セクタデコード回路55から出力されるPD値に基づいて、対象セクタにパディング処理を行うことができる。

上記各実施の形態は、次に示すように変更することもできる。

10

- ・第一～第四の実施の形態において、フォーマッタ33には従来例のフォーマッタ20に設けたブロックカウンタ22と同様なブロックカウンタを設けてもよい。この場合には、ブロックカウンタのカウント値が「1」となり、かつ書き込み終了フラグ35が「1」であるとき、リンク処理に移行するように設定する。

- ・第三の実施の形態において、data type設定レジスタ49にパディング処理を開始するセクタ値を格納するようにしてもよい。この場合には、デコード回路50において、data type設定レジスタ49の格納内容の1つ前のセクタからdata typeに「1」の設定を開始するような変換テーブルを設定すればよい。

- ・第五の実施の形態において、先頭ブロック検出信号FBを比較部56及びID設定部58に入力することにより、先頭ブロックに限り、パディング処理とdata typeの設定を可能とした。これ以外に、先頭ブロック検出信号FBをパディング対象セクタデコード回路55及びdata typeデコード回路57に入力して、先頭ブロック以外では、パディング対象セクタデコード回路55及びdata typeデコード回路57の動作を無効とするようにしてもよい。

20

- ・第一～第四の実施の形態と第五の実施の形態とを組み合わせた構成としてもよい。

- ・前記各実施の形態は、DVD-RWメディアに対する書き込み装置に使用することもできる。

- ・前記各実施の形態は、DVD+RWメディアに対する書き込み装置に応用することもできる。

【0105】

30

DVD+RWの場合、data typeビットの用途が異なるため、data typeレジスタをそのままパディング処理に利用できないが、第一～第四の実施の形態に示すdata typeビットの設定レジスタをパディング処理設定レジスタとして用意すれば可能である。

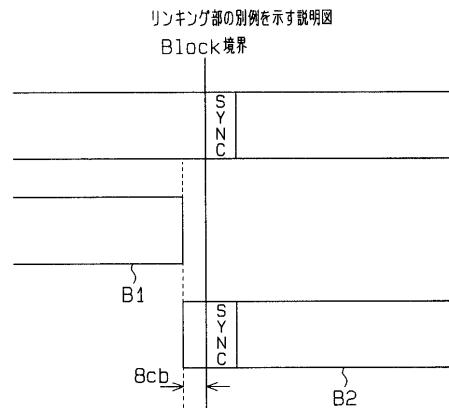

【0106】

また、図22に示すように、DVD+RWのリンク部は、先頭ブロックB2において、8cb(チャネルビット)早くを行い、最終ブロックB1の書き込みは、8cb早く終了するように規定されている。

【0107】

データの書き込み開始時には、8cb分のダミーデータを書き込む処理を行えばよく、バッファメモリにそのためのデータを格納する必要はなく、MPUによる制御も必要ない。

40

【0108】

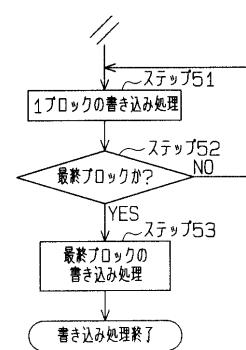

最終ブロックB1の書き込み処理は、フォーマッタで図23に示す処理を行えばよい。すなわち、1ブロック毎の書き込み処理を行うとき、各ブロックの書き込み開始に先立って、最終ブロックであるか否かをフラグにより検出し(ステップ51, 52)、最終ブロックであれば8cb早く書き込み処理を終了する(ステップ53)。

【0109】

また、フォーマッタにブロックカウンタを備えて、残りの処理ブロック数が0であるときに最終フラグが1になっていなければ、エラーを検出するようにしてもよい。

【0110】

また、各ブロックの書き込み処理に先立って、誤り訂正部の誤り訂正ポインタと、フォー

50

マッタのディスク制御ポインタとを比較して、データエンプティであるか否かを検出するようにしてよい。

## 【0111】

MPUの書き込み終了処理は、図5に示すフローチャートのステップ44の処理、すなわちリンク部のデータ作成処理を省略した動作となる。

将来において、DVDデータフォーマットを使用した他のメディアが現れた場合にも、DVD-Rと同様に最終ブロックのデータが足りないセクタについて「00h」のパディング処理を行う必要があり、それがEDCの演算を伴うようなケースであれば、本発明を応用することができる。

## 【0112】

10

(付記1) DVDメディアに対するDVDフォーマットデータの生成処理及び書き込み処理を制御する中央処理部と、

前記DVDフォーマットデータの生成処理及び書き込み処理を、複数のセクタで構成されるブロック毎に行うコントローラ部と

を備えたデータ書き込み装置であって、

前記コントローラ部には、最終ブロックのリンクグロスエリアに対するパディング処理データの生成を行うパディング処理回路を設けたことを特徴とするデータ書き込み装置。

(1)

(付記2) 前記コントローラ部は、

1ブロックずつのユーザーデータを取り込んで、バッファメモリに格納するホストインターフェースと、

前記バッファメモリから前記ユーザーデータを読み出して、1ブロックずつDVDフォーマットデータに変換して、前記バッファメモリに格納する誤り訂正部と、

前記DVDフォーマットデータを前記バッファメモリから1ブロックずつ読み出して、DVDメディアに対し書き込み処理を行うフォーマッタと

から構成し、

前記誤り訂正部に、前記パディング処理回路を備えたことを特徴とする付記1記載のデータ書き込み装置。(2)

(付記3) 前記誤り訂正部には、最終ブロックの各セクタのID部にdata typeを設定するdata type設定部を備えたことを特徴とする付記2記載のデータ書き込み装置。(3)

30

(付記4) 前記誤り訂正部は、前記最終ブロックのDVDフォーマットデータの生成後に書き込み終了フラグを設定し、前記フォーマッタは前記最終ブロックのDVDフォーマットデータの書き込み終了後、前記書き込み終了フラグに基づいてリンク部の書き込み処理を行うことを特徴とする請求項2または3記載のデータ書き込み装置。(4)

(付記5) 付記2～付記4の構成を備えたことを特徴とするデータ書き込み装置。

(付記6) 前記パディング処理回路は、

data type設定レジスタの格納内容に基づいて、前記最終ブロックのパディング処理対象セクタを検出する検出部と、

前記DVDフォーマットデータの生成時に、前記検出部の出力信号に基づいてパディング処理データを生成して出力するパディング処理データ生成部と

40

から構成したことを特徴とする付記2乃至5のいずれかに記載のデータ書き込み装置。(5)

(付記7) 前記data type設定レジスタには、前記最終ブロックの各セクタに対応するビットにそれぞれdata typeを格納し、前記検出部は前記data type設定レジスタの隣り合うビットの格納内容のAND論理を算出して出力することを特徴とする付記6記載のデータ書き込み装置。(6)

(付記8) 前記data type設定レジスタには、前記最終ブロックの各セクタに対応するビットにそれぞれdata typeを格納し、前記検出部は前記data type設定レジスタの格納内容に基づいてパディング処理対象セクタの先頭セクタを検出するデコード回路で構成したことを特徴とする付記6記載のデータ書き込み装置。(7)

50

(付記 9) 前記data type設定レジスタには、前記最終ブロックの各セクタにおいてdata typeを設定する先頭セクタの値を格納し、前記検出部は前記先頭セクタの値に「1」を加算してパディング処理対象セクタの先頭セクタを検出する加算器で構成したことを特徴とする付記6記載のデータ書き込み装置。(8)

(付記 10) 前記パディング処理データ生成部には、前記検出部の出力信号に基づいて、前記バッファメモリに格納されているデータに代えて、パディング処理データを選択する選択回路を設けたことを特徴とする付記6乃至9のいずれかに記載のデータ書き込み装置。(9)

(付記 11) 1ブロックずつのユーザーデータをホストインターフェースを介して取り込んで、バッファメモリに格納し、前記バッファメモリから前記ユーザーデータを誤り訂正部に読み出して、1ブロックずつDVDフォーマットデータに変換して前記バッファメモリに格納し、前記DVDフォーマットデータを前記バッファメモリからフォーマッタに1ブロックずつ読み出して、DVDメディアに対し書き込み処理を行い、最終ブロックのDVDフォーマットデータ生成時に前記誤り訂正部でパディング処理対象セクタに対するパディング処理データの生成を行うことを特徴とするDVDフォーマットデータ生成方法。10

(10)

(付記 12) 最終ブロックのDVDフォーマットデータ生成時に、前記誤り訂正部で、最終ブロックの各セクタのID部にdata typeを設定することを特徴とする付記11記載のDVDフォーマットデータ生成方法。

(付記 13) 前記最終ブロックのDVDフォーマットデータの書き込み終了後、書き込み終了フラグに基づいてリンクング部の書き込み処理を行うことを特徴とする付記11または12記載のDVDフォーマットデータ生成方法。20

(付記 14) 前記コントローラ部には、先頭ブロックのリンクングロスエリアに対するパディング処理データの生成を行うパディング処理回路を設けたことを特徴とする付記1記載のデータ書き込み装置。

【0113】

### 【発明の効果】

以上詳述したように、この発明は、DVDフォーマットデータの書き込み終了処理動作において、データエンプティエラーの発生を防止して、書き込み処理効率を向上させ得るデータ書き込み装置を提供することができる。30

### 【図面の簡単な説明】

【図1】 データ書き込み装置のコントローラ部を示すブロック図である。

【図2】 第一の実施の形態の誤り訂正部を示すブロック図である。

【図3】 デコード回路の変換テーブルを示す説明図である。

【図4】 フォーマッタ部の動作を示すフローチャート図である。

【図5】 MPUの書き込み終了処理を示すフローチャート図である。

【図6】 第二の実施の形態を示すブロック図である。

【図7】 デコード回路の変換テーブルを示す説明図である。

【図8】 第三の実施の形態を示すブロック図である。

【図9】 デコード回路の変換テーブルを示す説明図である。40

【図10】 第四の実施の形態を示すブロック図である。

【図11】 第五の実施の形態を示すブロック図である。

【図12】 デコード回路の変換テーブルを示す説明図である。

【図13】 データ書き込み装置を示すブロック図である。

【図14】 従来のコントローラ部を示すブロック図である。

【図15】 DVDのデータフォーマットを示す説明図である。

【図16】 DVDの誤り訂正処理手順を示す説明図である。

【図17】 ID部を示す説明図である。

【図18】 リンキング部を示す説明図である。

【図19】 リンキングロスエリアを示す説明図である。50

【図20】 従来のMPUの書き込み終了処理を示すフローチャート図である。

【図21】 従来のフォーマッタ部の書き込み終了処理を示すフローチャート図である。

【図22】 リンキング部の別例を示す説明図である。

【図23】 フォーマッタ部の動作の別例を示すフローチャート図である。

【符号の説明】

- 1 中央処理部 (MPU)

3 1 コントローラ部

3 4 a ~ 3 4 d パディング処理回路

B 1 最終ブロック

【図1】

【図2】

【図3】

デコード回路の変換テーブルを示す説明図

【 図 4 】

### フォーマッタ部の動作を示すフローチャート図

( 5 )

### MPI の書き込み終了処理を示すフローチャート

【 6 】

## 第二の実施の形態を示すブロック図

【図7】

デコード回路の変換テーブルを示す説明図

| data type | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | PD値 |

|-----------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|-----|

| 0         | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1   |

| 1         | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 2  | 1   |

| 2         | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 3  | 2   |

| 3         | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 4  | 3   |

| 4         | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 5  | 4   |

| 5         | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 6  | 5   |

| 6         | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 7  | 6   |

| 7         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 8  | 7   |

| 8         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 9  | 8   |

| 9         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1  | 1  | 1  | 1  | 1  | A  | 9   |

| A         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1  | 1  | 1  | 1  | 1  | B  | A   |

| B         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 1  | 1  | 1  | 1  | C  | B   |

| C         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 1  | 1  | 1  | D  | C   |

| D         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 1  | 1  | E  | D   |

| E         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 1  | F  | E   |

| F         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  | F   |

【図8】

第三の実施の形態を示すブロック図

【図9】

デコード回路の変換テーブルを示す説明図

| data type | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | PD値 |

|-----------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|-----|

| 0         | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1   |

| 1         | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 2  | 1   |

| 2         | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 3  | 2   |

| 3         | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 4  | 3   |

| 4         | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 5  | 4   |

| 5         | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 6  | 5   |

| 6         | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 7  | 6   |

| 7         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 8  | 7   |

| 8         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 9  | 8   |

| 9         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1  | 1  | 1  | 1  | 1  | A  | A   |

| A         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1  | 1  | 1  | 1  | 1  | B  | B   |

| B         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 1  | 1  | 1  | 1  | C  | C   |

| C         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 1  | 1  | 1  | D  | D   |

| D         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 1  | 1  | E  | E   |

| E         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 1  | F  | F   |

| F         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  | F   |

【図10】

第四の実施の形態を示すブロック図

【図 1 1】

第五の実施の形態を示すブロック図

【図 1 2】

デコード回路の変換テーブルを示す説明図

(a)

| PD類型     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|----------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Lossless | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

| 2K       | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

| 32K      | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

(b)

| data type | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Lossless  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2K        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 32K       | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

【図 1 3】

データ書き込み装置を示すブロック図

【図 1 4】

従来のコントローラ部を示すブロック図

【図15】

【図16】

DVDOの誤り訂正処理手順を示す説明図

【図17】

【図18】

リンク部を示す説明図

【図19】

リンクグロスエリアを示す説明図

【図20】

従来のMPUの書き込み終了処理を示すフローチャート図

【図21】

【図22】

【図23】

フォーマッタ部の動作の別例を示すフローチャート図

---

フロントページの続き

(56)参考文献 特開2000-215607(JP, A)

特開2000-260163(JP, A)

特開平06-162671(JP, A)

特開平09-282805(JP, A)

特開平09-270171(JP, A)

(58)調査した分野(Int.Cl. , DB名)

G11B 20/10-20/16

G11B 7/00- 7/013