(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5124344号

(P5124344)

(45) 発行日 平成25年1月23日(2013.1.23)

(24) 登録日 平成24年11月2日(2012.11.2)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO2M 7/48 (2007.01)   | HO2M 7/48 E   |

| HO2M 7/5387 (2007.01) | HO2M 7/5387 Z |

| C23C 14/34 (2006.01)  | C23C 14/34 Z  |

| HO5H 1/46 (2006.01)   | HO5H 1/46 R   |

請求項の数 7 (全 17 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2008-137077 (P2008-137077)  |

| (22) 出願日  | 平成20年5月26日 (2008.5.26)        |

| (65) 公開番号 | 特開2009-284732 (P2009-284732A) |

| (43) 公開日  | 平成21年12月3日 (2009.12.3)        |

| 審査請求日     | 平成23年3月11日 (2011.3.11)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000231464<br>株式会社アルパック<br>神奈川県茅ヶ崎市萩園2500番地 |

| (74) 代理人  | 110000305<br>特許業務法人青義                      |

| (72) 発明者  | 堀下 芳邦<br>神奈川県茅ヶ崎市萩園2500 株式会社<br>アルパック内     |

| (72) 発明者  | 松原 忍<br>神奈川県茅ヶ崎市萩園2500 株式会社<br>アルパック内      |

| (72) 発明者  | 小野 敦<br>神奈川県茅ヶ崎市萩園2500 株式会社<br>アルパック内      |

最終頁に続く

(54) 【発明の名称】バイポーラパルス電源及び複数のバイポーラパルス電源からなる電源装置並びに出力方法

## (57) 【特許請求の範囲】

## 【請求項 1】

直流電力供給源からの正負の直流出力間に接続されたスイッチング素子から構成されるプリッジ回路を備え、スイッチング素子の作動を制御してプラズマに接触する一対の電極に所定の周波数でバイポーラパルス状に出力するバイポーラパルス電源において、

前記電極に出力する際に、その当初は前記電極への出力が定電圧特性を有し、その後に前記電極への出力が定電流特性を有するように前記出力を切り換える出力特性切換回路を備えたことを特徴とするバイポーラパルス電源。

## 【請求項 2】

前記出力特性切換回路は、前記直流電力供給源からプリッジ回路への正負の直流出力のうち少なくとも一方に配置されたインダクタと、前記インダクタに並列接続された他のスイッチング素子とを備え、前記スイッチング素子の切換え当初に前記他のスイッチング素子を所定時間作動させてインダクタを短絡することを特徴とする請求項1記載のバイポーラパルス電源。 10

## 【請求項 3】

前記出力特性切換回路は、前記直流電力供給源からプリッジ回路への正負の直流出力のうち少なくとも一方に配置されたインダクタと、前記インダクタに並列接続され、過電圧発生時に前記インダクタを短絡するダイオードとを備えることを特徴とする請求項1記載のバイポーラパルス電源。

## 【請求項 4】

前記他のスイッチング素子またはダイオードに直列に抵抗を接続したことを特徴とする請求項2または請求項3記載のバイポーラパルス電源。

【請求項5】

前記電極は、スパッタリング法を実施する処理室内に配置した一対のターゲットであることを特徴とする請求項1乃至請求項4のいずれか1項に記載のバイポーラパルス電源。

【請求項6】

請求項1乃至請求項5のいずれか1項に記載のバイポーラパルス電源を複数台並列接続してなる電源装置であって、各バイポーラパルス電源を同期させて同一の処理室内に配置した少なくとも一対の電極に対しバイポーラパルス状に出力するように構成したことを特徴とする電源装置。

10

【請求項7】

直流電力供給源からの正負の直流出力間に接続された、プラズマに接触する一対の電極に対し、所定の周波数でバイポーラパルス状に出力する出力方法において、

前記電極に出力する際に、その当初は定電圧特性を有し、その後に定電流特性を有するように前記出力を切り換えることを特徴とする出力方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プラズマ及び表面処理装置にバイポーラパルス状に電力供給するバイポーラパルス電源及び複数のバイポーラパルス電源からなる電源装置、並びに直流電力供給源からの正負の直流出力間に接続された、プラズマに接触する一対の電極に対し、所定の周波数でバイポーラパルス状に出力する出力方法に関する。

20

【背景技術】

【0002】

この種のバイポーラパルス電源は、例えば処理基板表面に所定の薄膜を形成するスパッタリング装置に用いられ、直流電力を供給する整流回路と、この整流回路の正負の出力間に接続され、4個のスイッチング素子からなるMOSFETブリッジ回路とを有するものが知られている。そして、制御手段によって各スイッチング素子を適宜作動させて、出力端（電極）である一対のターゲットに所定の周波数で交互に極性を切換えて任意のパルス電圧を印加し、ターゲットをアノード電極、カソード電極に交互にそれぞれ切換えてアノード電極及びカソード電極間にグロー放電を生じさせてプラズマ雰囲気を形成し、各ターゲットをスパッタリングする。これにより、ターゲット表面に蓄積する電荷が反対の位相電圧を印加したとき打ち消され、安定的な放電が得られるという利点がある（例えば、特許文献1）。

30

【0003】

このようなグロー放電中では、何らかの原因によりアーク放電（異常放電）が発生することが知られている。アーク放電が発生すると、プラズマ（負荷）のインピーダンスが急激に小さくなるため、急激な電圧低下が起こり、それに伴って電流が増加する。ここで、ターゲットが、特にアルミニウム等の金属製である場合、高いアーク電流値のアーク放電がターゲット間で局所的に発生すると、ターゲットが溶かされて放出されたものが処理基板表面に付着するというパーティクルやスプラッシュ（数μm～数百μmの塊）が発生し、良好な成膜ができない。

40

【0004】

のことから、上記特許文献1記載のバイポーラパルス電源では、ブリッジ回路からの出力電流を検出する検出回路と、アーク放電発生時の電流上昇を抑制するインダクタとを設け、この検出回路で検出した出力電流が定常出力電流値を超えたときに、作動中のスイッチング素子を切換え、その電極への出力を一旦遮断する。そして、過電流が鎮静してその値が定常出力電流値近くになると、その電極への出力を再開するようにしている。この場合、出力電流が一定の範囲を超えて変化すると、異常放電の前段現象（マイクロアーク

50

)として捉え、その消弧処理を行うことで電流変化量の多いアーク放電の発生を抑制することもできる。

#### 【0005】

ここで、直流電力供給源からの出力が定電圧特性を有していれば、インダクタンス成分より容量成分(キャパシタンス)成分が支配的になる。このため、アーク放電発生時に、プラズマ負荷側のインピーダンスが小さくなる(場合によっては、数オーム以下まで小さくなる)ことで、出力とプラズマ(負荷)とが結合されて容量成分から急激に出力側に放出される。その結果、インダクタンス値の小さなインダクタを設けも、電流上昇を効率よく抑制できず、短時間(数μSの間)で過電流が流れる(つまり、アーク放電発生時の単位時間当たりの電流上昇率が高い)という問題がある。

10

#### 【0006】

単位時間当たりの電流上昇率が高い場合、電流変化量が比較的小さい状態を捕らえてマイクロアーク処理を行うときですら、電圧変化に遅れて発生する電流変化に基づくアーク放電検出からプラズマへの電力供給の遮断までの時間内で大きなアーク電流が流れる場合があり、放出されるアークエネルギーが大きくなっている(定常電流値の2倍程度の電流が流れ)、スプラッシュやパーティクルが発生し易くなり、特に、アーク放電が連続して発生しているときには、スプラッシュやパーティクルの発生を実質的に抑制できない。

#### 【0007】

他方で、プラズマのインダクタンス成分より一桁以上大きいインダクタンス値のインダクタを設けると、直流電源供給源からの出力は定電流特性となり、アーク放電の発生時の単位時間当たりの電流上昇率が制限される。然し、ブリッジ回路の各スイッチング素子を切換えるとき、通常の放電電圧より高い電圧が発生する場合がある。つまり、プラズマにインダクタンス成分が発生することで、各ターゲットでの極性反転時に過電圧が生じる。このように過電圧が生じると、アーク放電を誘発する虞がある。

20

#### 【特許文献1】特許第3639605号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

そこで、本発明、以上の点に鑑み、スプラッシュやパーティクルの発生に直結するアーク放電発生時の電流上昇を効果的に制限しつつ、極性反転時に過電圧が生じることを防止できるようにしたバイポーラパルス電源及び複数のバイポーラパルス電源からなる電源装置並びに出力方法を提供することをその課題とする。

30

#### 【課題を解決するための手段】

#### 【0009】

上記課題を解決するために、本発明のバイポーラパルス電源は、直流電力供給源からの正負の直流出力間に接続されたスイッチング素子から構成されるブリッジ回路を備え、スイッチング素子の作動を制御してプラズマに接触する一対の電極に所定の周波数でバイポーラパルス状に出力するバイポーラパルス電源において、前記電極に出力する際に、その当初は前記電極への出力が定電圧特性を有し、その後に前記電極への出力が定電流特性を有するように前記出力を切り換える出力特性切換回路を備えたことを特徴とする。

40

#### 【0010】

本発明によれば、出力特性切換回路を設けたことで、何らかの原因でアーク放電が発生した場合、プラズマのインピーダンスが急激に小さくなることに起因して急激な電圧低下が起こり、それに伴って電流が増加する。このとき、直流電源供給源から電極への出力が定電流特性であるため、アーク放電の発生時の単位時間当たりの電流上昇率が制限される。他方で、各電極での極性反転時にのみ定電圧特性となっていることで、その極性反転時に過電圧が生じることが防止され、過電流に起因したアーク放電の発生が抑制される。

#### 【0011】

本発明においては、前記出力特性切換回路が、前記直流電力供給源からブリッジ回路への正負の直流出力のうち少なくとも一方に配置されたインダクタと、前記インダクタに並列

50

に接続された他のスイッチング素子とを備え、前記スイッチング素子の切換え当初に前記他のスイッチング素子を所定時間作動させてインダクタを短絡する構成を採用すれば、定電圧特性から定電流特性に切り換わる構成を簡単に実現できる。この場合、上記スイッチング素子の切換のタイミングは、プラズマの発生空間の容積（即ち、プラズマのインピーダンス）に応じて適宜設定することができ、また、マイクロアーク処理時には、アーク放電の発生時の電流上昇率が制限されるように上記スイッチング素子がオフに制御される。

#### 【0012】

他方で、前記出力特性切換回路は、前記直流電力供給源からブリッジ回路への正負の直流出力のうち少なくとも一方に配置されたインダクタと、前記インダクタに並列接続され、過電圧発生時に前記インダクタを短絡するダイオードとを備える構成を採用すれば、極性反転時に過電圧が生じている間、ダイオードがオン状態となってインダクタが短絡されることで、その間だけ定電圧特性になる。これによれば、切換えを制御する必要があるスイッチング素子を用いないため、回路構成やその制御を簡素化できてよい。10

#### 【0013】

本発明においては、前記他のスイッチング素子またはダイオードに直列に抵抗を接続した構成を採用し、極性反転時に生じる過電圧からスイッチング素子やダイオードを保護するようにしてもよい。

#### 【0014】

なお、本発明においては、前記電極は、スパッタリング法を実施する処理室内に配置した一対のターゲットである場合に、特に有効である。20

#### 【0015】

また、上記課題を解決するために、本発明の電源装置は、請求項1乃至請求項5のいずれか1項に記載のバイポーラパルス電源を複数台並列接続してなる電源装置であって、各バイポーラパルス電源を同期させて同一の処理室内に配置した少なくとも一対の電極に対しバイポーラパルス状に出力するように構成したことを特徴とする。

#### 【0016】

更に、上記課題を解決するために、本発明は、直流電力供給源からの正負の直流出力間に接続された、プラズマに接触する一対の電極に対し、所定の周波数でバイポーラパルス状に出力する出力方法において、前記電極に出力する際に、その当初は定電圧特性を有し、その後に定電流特性を有するように前記出力を切り換えることを特徴とする。30

#### 【発明を実施するための最良の形態】

#### 【0017】

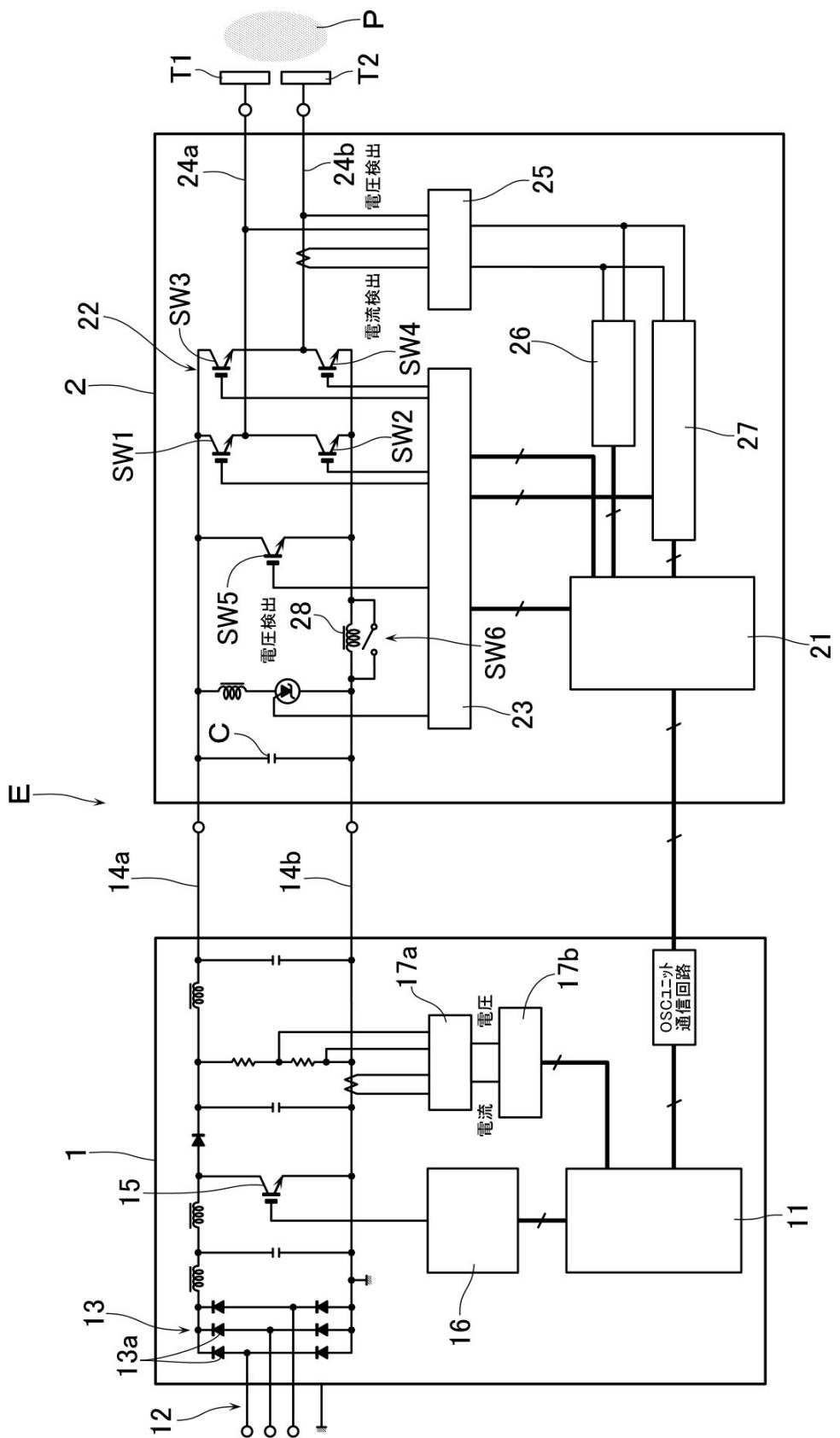

以下に図面を参照して本発明のバイポーラパルス電源Eを説明する。図1に示すように、バイポーラパルス電源Eは、例えばスパッタリング装置内の処理基板に対向させて配置され、プラズマPに接触する電極である一対のターゲットT1、T2に対し、所定の周波数でバイポーラパルス状に電力供給（出力）するために用いられる。バイポーラパルス電源Eは、直流電力の供給を可能とする直流電力供給部1と、各ターゲットT1、T2への出力を制御する発振部2とから構成される。出力電圧の波形は、略方形波や略正弦波であつてもよい。

#### 【0018】

直流電力供給部1は、その作動を制御する第1のCPU回路11と、商用の交流電力（3相AC200V又は400V）が入力される入力部12と、入力された交流電力を整流して直流電力に変換する6個のダイオード13aからなる整流回路13とを有し、正負の直流電力ライン14a、14bを介して直流電力を発振部2に出力する。また、直流電力供給部1には、直流電力ライン14a、14b間に設けたスイッチングトランジスタ15と、第1のCPU回路11に通信自在に接続され、スイッチングトランジスタ15のオン、オフを制御する出力発振用のドライバー回路16とが設けられている。直流電力ライン14a、14b間に、その電流、電圧を検出する検出回路17aが接続され、検出回路17aで検出された電流、電圧は、A/D変換回路17bを介して第1のCPU回路11に入力されるようになっている。4050

## 【0019】

発振部2には、第1のCPU回路11に通信自在に接続された第2のCPU回路21と、正負の直流電力ライン14a、14b間に接続された4個の第1乃至第4のスイッチングトランジスタSW1乃至SW4からなるブリッジ回路22と、第2のCPU回路21に通信自在に接続され、各スイッチングトランジスタSW1乃至SW4のオン、オフの切換を制御する出力発振用のドライバー回路23とが設けられている。

## 【0020】

そして、出力発振用のドライバー回路23によって、例えば第1及び第4のスイッチングトランジスタSW1、SW4と、第2及び第3のスイッチングトランジスタSW2、SW3とのオン、オフのタイミングが反転するように各スイッチングトランジスタSW1乃至SW4の切換えを制御すると、ブリッジ回路22からの出力ライン24a、24bを介して一対のターゲットT1、T2にバイポーラパルス状に出力される。出力ライン24a、24bには、一対のターゲットT1、T2への出力電流及び出力電圧を検出する検出回路25が接続され、この検出回路25で検出された出力電流及び出力電圧は、AD変換回路26を介して第2のCPU回路21に入力されるようになっている。

10

## 【0021】

ここで、上記構成のバイポーラパルス電源Eにおいて、直流電力供給部1から直流電力を出力した状態で各スイッチングトランジスタSW1乃至SW4を切換えたのでは、それらのスイッチング損失が多大となるため、各スイッチングトランジスタSW1乃至SW4の耐久性が向上するように構成する必要がある。そこで、直流電力供給部1からの正負の直流出力ライン14a、14b間に、出力発振用のドライバー回路23によってオン、オフの切換が制御される出力短絡用のスイッチングトランジスタSW5を設け、出力短絡用のスイッチトランジスタSW5の短絡状態（ターゲットT1、T2への出力が遮断される状態）で、ブリッジ回路22の各スイッチングトランジスタSW1乃至SW4の切換えを行うように構成している。

20

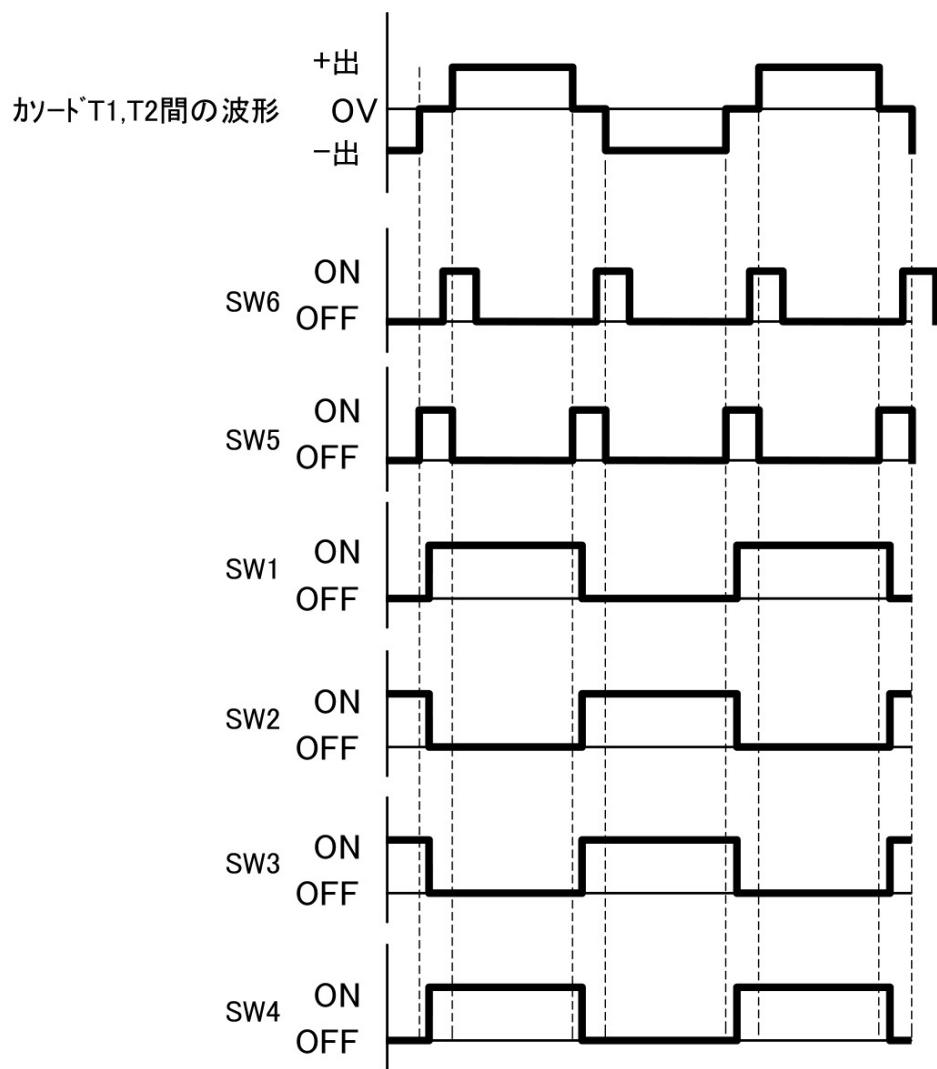

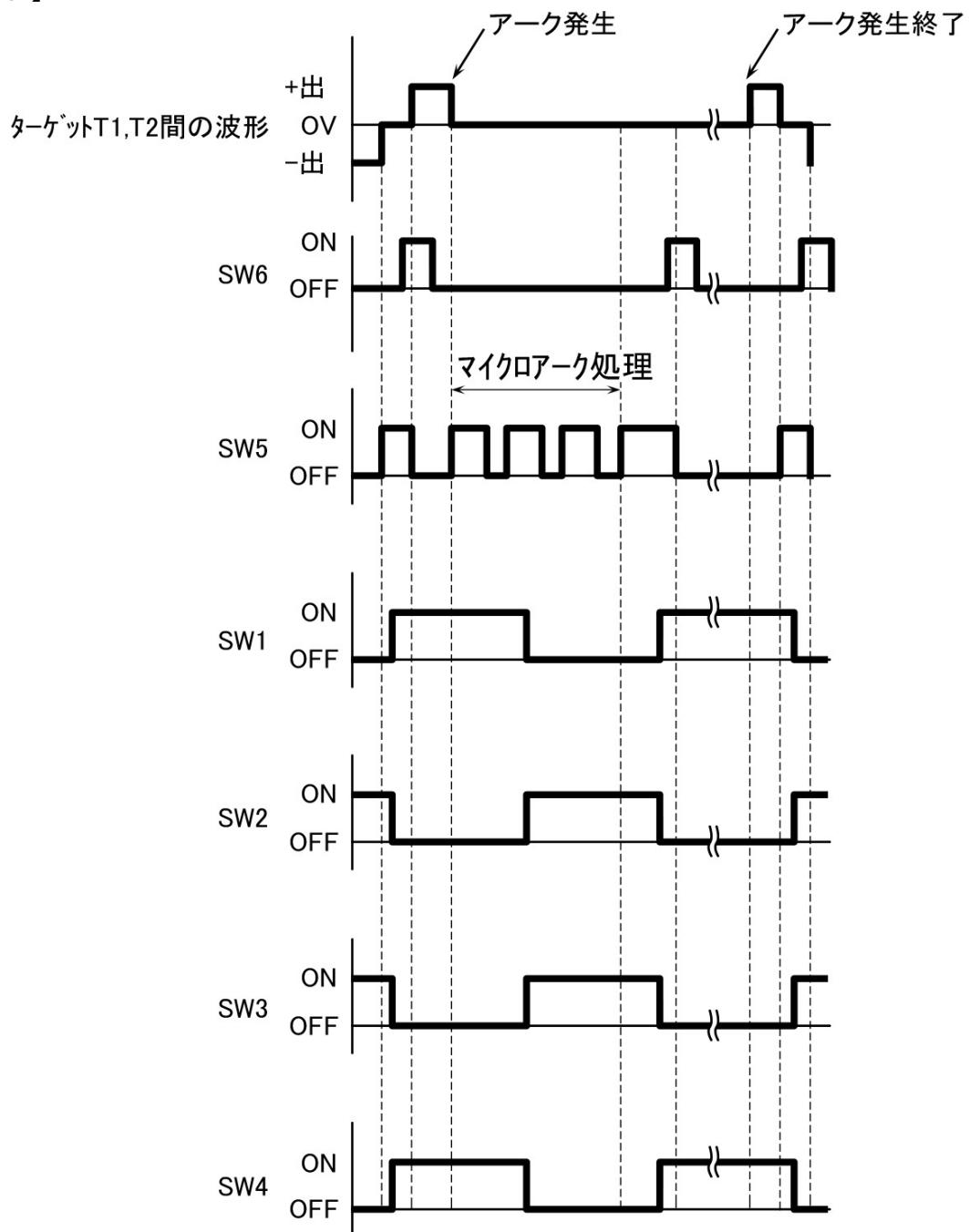

## 【0022】

つまり、図2に示すように、一対のターゲットT1、T2にバイポーラパルス状に出力する場合、スイッチングトランジスタSW5の短絡状態（オン）で、例えば第1及び第4のスイッチングトランジスタSW1、SW4をオンし、その後、スイッチングトランジスタSW5の短絡を解除（オフ）して一方のターゲットT1に出力する（ターゲットT1に負の電位が印加される）。次いで、スイッチングトランジスタSW5を再度短絡し、第1及び第4のスイッチングトランジスタSW1、SW4をオフすると共に、第2及び第3のスイッチングトランジスタSW2、SW3をオンし、その後、スイッチングトランジスタSW5をオフして他方のターゲットT2に出力する（ターゲットT2に負の電位が印加される）。

30

## 【0023】

そして、各スイッチングトランジスタSW1乃至SW4のオン、オフのタイミングが反転する上記制御を繰り返すことで、一対のターゲットT1、T2の間に所定の周波数でバイポーラパルス状に出力される。その際、所定圧力に保持された装置内にArなどのスペッタガスを導入した状態で、所定の周波数で交互に極性をかえて電力投入される一対のターゲットT1、T2がアノード電極、カソード電極に交互に切換わり、アノード電極及びカソード電極間にグロー放電を生じさせてプラズマ雰囲気が形成され、各ターゲットT1、T2がスパッタリングされる。

40

## 【0024】

これにより、ターゲットT1、T2への出力する際に発生するスイッチング損失は、スイッチングトランジスタSW5でのみ発生し、各スイッチングトランジスタSW1乃至SW4にはスイッチング損失が殆ど発生しない。その結果、高機能のスイッチング素子を用いることなく、高い耐久性を達成でき、しかも、4個のスイッチング素子でスイッチング損失が発生する場合のような十分な放熱機構が不要になり、低コスト化が図れる。

## 【0025】

50

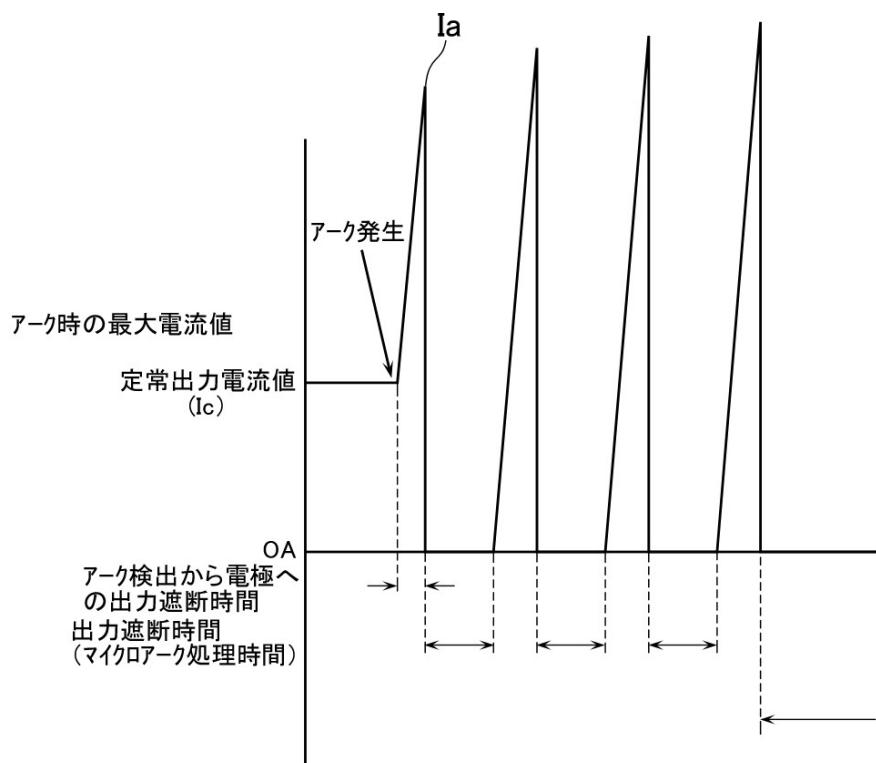

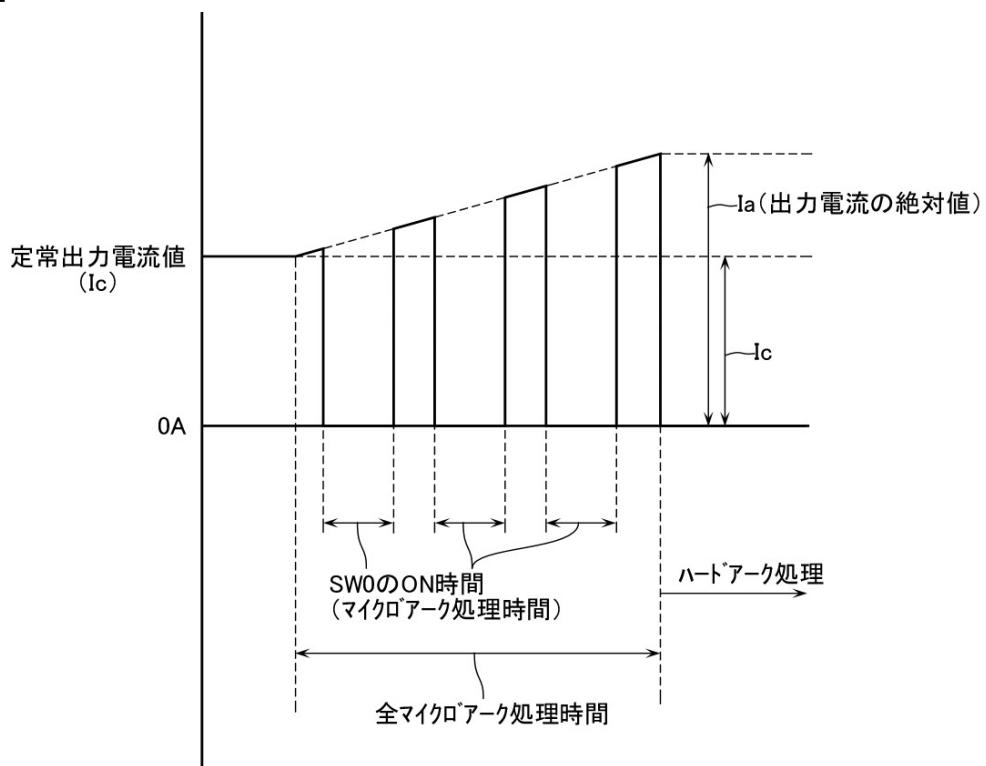

ここで、直流電力供給部1からの出力が定電圧特性であると、インダクタンス成分より容量成分(キャパシタンス)成分が支配的になる。このように容量成分(キャパシタンス)成分が支配的であると、アーク放電発生時にプラズマ負荷側のインピーダンスが小さくなることで、出力とプラズマ負荷とが結合されて容量成分から急激に出力側に放出される。このため、検出手段によるアーク放電の検出から電極への出力遮断までの時間内で大きなアーク電流が流れる。その結果、一度の処理でアーク放電を消弧できないと、マイクロアーク処理を行う毎にアーク電流値が高くなり(放出されるアークエネルギーが大きくなる)、スプラッシュやパーティクルが発生し易くなる(図3参照)。

#### 【0026】

そこで、負の直流出力ライン14bに、プラズマのインダクタンス成分より大きいインダクタンス値を有するインダクタ28を設けることとした(図1参照)。ここで、マイクロアーク処理時の電流上昇率が、定常電流値の200%より小さく、より好ましくは、150%以下に制限する場合、アーク放電発生時の出力電流上昇率( $i$ )が、インダクタ28のインダクタンス値をL、ターゲットT1、T2への出力電圧をV及び電流変化時間tとすると、 $i = t \cdot V / L$ で算出される。その際、一対のターゲットT1、T2への出力電圧を500V、出力電流を100Aとし、マイクロアーク処理(出力遮断)時間を200μSとし、過電流を検出して出力を遮断するまでの電流上昇率を150%にするには、 $i$ は50Aとなる。このような場合には2mHのインダクタンス値を持つインダクタ28を負の直流出力ライン14bに接続すればよい。尚、本実施の形態では、負の直流出力ライン14bに所定値のインダクタ28を設けることとしたが、インダクタ28の接続位置はこれに限定されるものではなく、正の直流出力ライン14aまたは正負の両直流出力ライン14a、14bにそれぞれ設けてもよい。

#### 【0027】

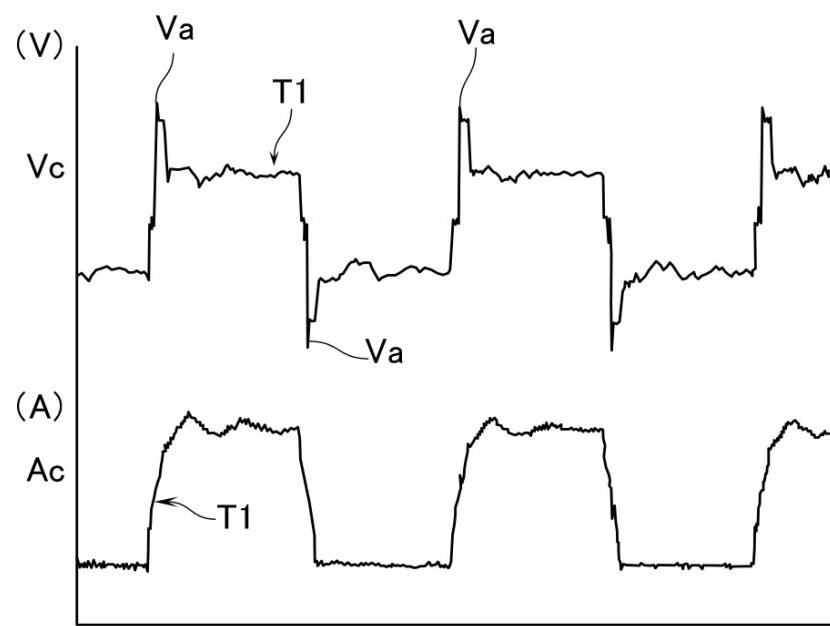

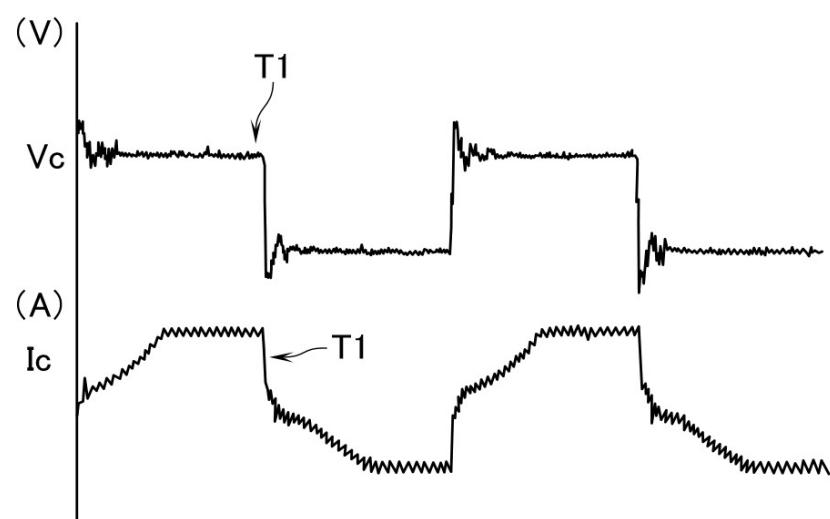

上記のように、例えば2mHの値を持つインダクタ28を設けた場合、ブリッジ回路22の各スイッチング素子SW1乃至SW4を所定の周波数(例えば、5kHz)で切換えるときに通常の放電電圧Vcより高い電圧Vaが発生する(図4(a)参照)。つまり、プラズマPにインダクタンス成分が発生し、一対のターゲットT1、T2への出力を交互に切り換える毎(極性反転時)に過電圧が生じる。このように過電圧が生じると、アーク放電を誘発する虞がある。なお、図4では、一方のターゲットT1での出力電圧及び出力電流の変化のみを示している。

#### 【0028】

そこで、直流電力供給部1からの正負の直流出力ライン14a、14bに、上記インダクタ28及び当該インダクタ28に並列接続された他のスイッチング素子SW6とを備える出力特性切換回路を設けることとした(図1参照)。スイッチング素子SW6は、FETなど公知の構造を有するものであり、ドライバー回路23によってオン、オフの切換が制御される。また、過電圧を防止する際に、スイッチング素子SW6を保護するため当該スイッチング素子SW6に直列に例えば数~数百の抵抗値を有する抵抗(図示せず)を接続した構成を採用してもよい。

#### 【0029】

そして、スイッチングトランジスタSW5の短絡状態(オン)で、例えば第1及び第4のスイッチングトランジスタSW1、SW4をオンし、その後、スイッチングトランジスタSW5の短絡を解除(オフ)して一方のターゲットT1に出力する場合に、スイッチング素子SW6を一定期間オンすることでインダクタ28を短絡する。次に、スイッチングトランジスタSW5を再度短絡し、第1及び第4のスイッチングトランジスタSW1、SW4をオフすると共に、第2及び第3のスイッチングトランジスタSW2、SW3をオンし、その後、スイッチングトランジスタSW5をオフした後にも、スイッチング素子SW6を一定期間オンすることでインダクタ28を短絡する(図2参照)。尚、スイッチング素子SW6の切換のタイミング(スイッチング素子SW6をオンさせる時間)、プラズマの発生空間の容積(即ち、プラズマのインピーダンス)に応じて適宜設定することができ、また、後述するマイクロアーク処理時には、アーク放電の発生時の電流上昇率が制限さ

10

20

30

40

50

れるようにスイッチング素子 SW 6 がオフに制御される。

**【 0 0 3 0 】**

このように極性反転時にスイッチング素子 SW 6 を作動させてインダクタ 2 8 を所定時間だけ短絡することで、インダクタ 2 8 が短絡されている間、ターゲット T 1、T 2 への出力が定電圧特性となり、出力電流 I c が徐々に増加する（つまり、出力電流は 0 A から始まるランプ出力となる）。そして、スイッチング素子 SW 6 をオフに戻すと、定電流特性となり、各ターゲット T 1、T 2 での極性反転時に過電圧が生じることが防止され、過電流に起因したアーク放電の発生を抑制がされる（図 4 ( b ) 参照）。

**【 0 0 3 1 】**

次に、本発明のバイポーラパルス電源におけるアーク処理について説明する。即ち、上記のようなグロー放電中では、何らかの原因によりアーク放電が発生する場合があり、アーク放電が発生すると、プラズマのインピーダンスが急激に小さくなるため、急激に電圧低下が起こり、それに伴って電流が増加する。このことから、検出回路 2 5 で検出された出力電流及び出力電圧が入力されるアーク検出制御回路 2 7 を第 2 の C P U 回路 2 1 に通信自在に設け（図 1 参照）、出力電流が一定の範囲を超えて変化すると、アーク放電の前段現象（マイクロアーク）として捉え、その消弧処理を行うことでアーク電流の大きなアーク放電の発生を抑制する。

**【 0 0 3 2 】**

図 5 及び図 6 を参照して説明すれば、検出回路 2 5 で検出した出力電流 I a が、定常出力電流値 I c を超えたとき、アーク検出制御回路 2 7 によってアーク放電発生の前段現状として捕え、第 2 の C P U 回路 2 1 及びアーク検出制御回路 2 7 を介して出力発振用のドライバー回路 2 3 によって出力短絡用のスイッチングトランジスタ SW 5 が短絡（オン）される。このとき、直流出力ライン 1 4 b にインダクタ 2 8 を設けていることで、直流電源供給部 1 からの出力が定電流特性となり、アーク放電の発生時の電流上昇率が制限される。出力短絡用のスイッチングトランジスタ SW 5 が短絡（オン）されたとき、ブリッジ回路 2 2 の各スイッチングトランジスタ SW 1 乃至 SW 4 は、いずれか一方のターゲット T 1、T 2 への出力状態に保持されているが、スイッチングトランジスタ SW 0 が短絡されることでターゲット T 1、T 2 への出力が遮断される（マイクロアーク処理）。

**【 0 0 3 3 】**

次いで、所定時間経過後（数 μ S ~ 数 m S）に、出力短絡用のスイッチングトランジスタ SW 5 の短絡を解除（オフ）し、各スイッチングトランジスタ SW 1 乃至 SW 4 の作動状態に応じていずれか一方のターゲット T 1、T 2 への出力を再開する。このとき、スイッチング素子 SW 6 を一定期間オンすることでインダクタ 2 8 が短絡され、上記同様に、インダクタ 2 8 が短絡されている間、ターゲット T 1、T 2 への出力が定電圧特性となり、一方のターゲット T 1、T 2 への出力再開時に、過電圧が生じることが防止される。そして、アーク検出制御回路 2 7 によって出力電流 V a が定常出力電流値 V c を超えているかを判断し、定常出力電流値 V c を未だ超えていれば、出力発振用ドライバー回路 2 3 によって出力短絡用のスイッチングトランジスタ SW 5 を再度短絡する。

**【 0 0 3 4 】**

この一連のマイクロアーク処理を複数回繰り返しても出力電流 I a が定常出力電流値 I c を超えた状態のままであるか、または、出力電流 I a が予め設定された所定値を超えると、スラッシュやパーティクルの発生を誘発するアーク放電が発生すると判断し、第 1 の C P U 回路 1 1 からの制御によってスイッチングトランジスタ 1 5 をオフし、直流電力供給部 1 からの出力を停止する（ハードアーク処理）。この処理の間でも、アーク電流値は、定常電流値の 200 % より小さく保持されること（図 6 参照）、出力中の 2 個のスイッチングトランジスタ SW 1 乃至 SW 4 を切換えてアーク放電の消弧処理を行う場合より、応答性よくその出力遮断の制御ができることが相俟って、放出されるアークエネルギーが小さくして、スラッシュやパーティクルの発生を効果的に抑制できる。この処理の間、ブリッジ回路 2 2 の各スイッチングトランジスタ SW 1 乃至 SW 4 にはスイッチング損失が殆ど発生しないため、その耐久性を一層向上できる。

10

20

30

40

50

## 【0035】

なお、本実施の形態では、バイポーラパルス電源Eにより電極たるターゲットT1、T2に出力（マイクロアーク処理の際に出力を再開する場合を含む）する際に、その当初は前記各電極への出力が定電圧特性を有し、その後に前記各電極への出力が定電流特性を有するように切り換える出力特性切換回路として、インダクタ28及びスイッチング素子SW6を設けたものを例に説明したがこれに限定されるものではない。

## 【0036】

例えば、FET等のスイッチング素子に代えて、過電圧発生時にインダクタ28を短絡するダイオード（図示せず）をインダクタ28に並列接続して出力特性切換回路とする構成を採用できる。これにより、簡単な構成で出力特性切換回路を実現でき、その上、スイッチング素子を用いた場合のような制御が不要になってよい。この場合、直流電力供給部1からの正負の直流出力ライン14a、14bに接続されたキャパシタCと、インダクタ28に並列であって相互に直列接続されたダイオードD及び抵抗Rとから構成される出力クランプ回路で出力特性切換回路としてもよい。キュパシタCとしては、5～20μFのものが用いられ、抵抗Rとしては、数～10の範囲のものを用いればよい。

10

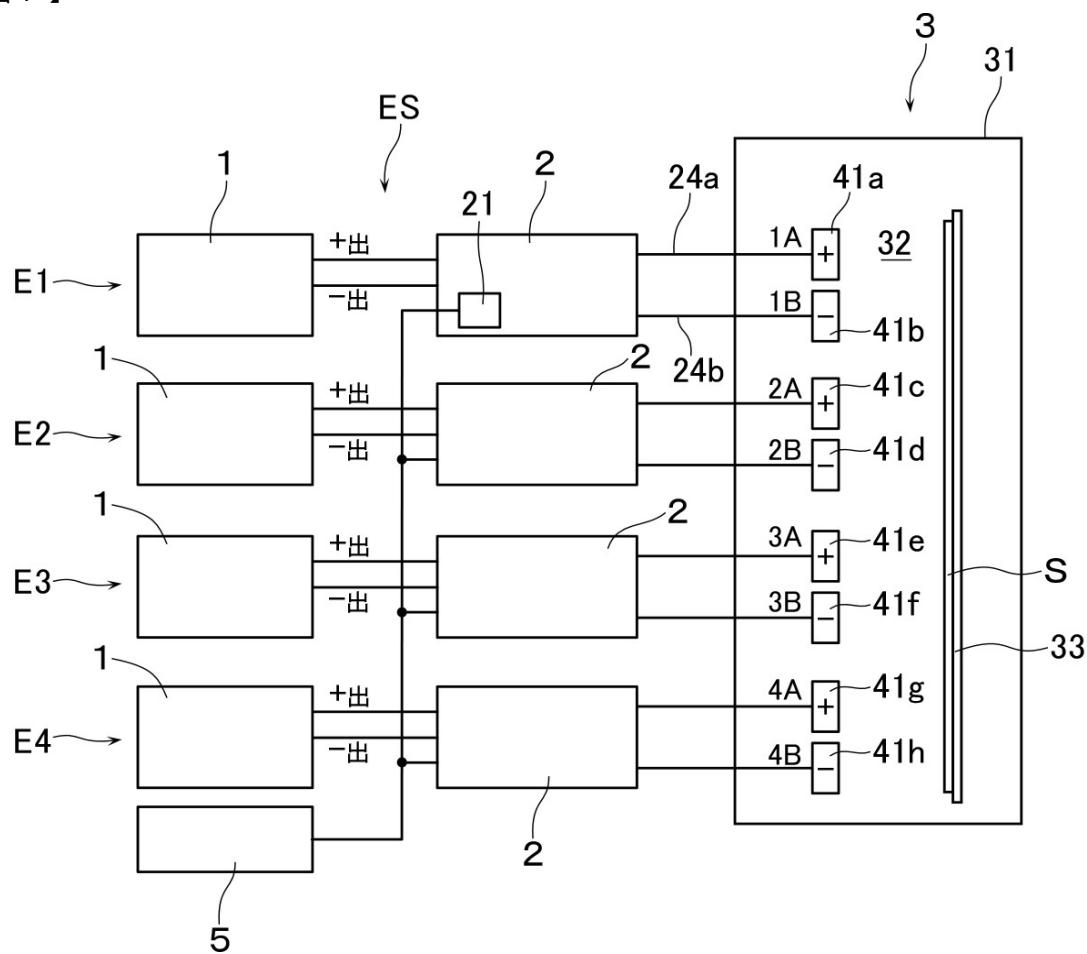

## 【0037】

次に、図7及び図8を参照して、本発明のバイポーラパルス電源Eを複数台並列接続してなる電源装置について説明する。ESは、本発明の電源装置であり、この電源装置ESは、例えば次の構成を有するマグネットロンスパッタリング装置（以下、「スパッタ装置」という）3に用いられている。

20

## 【0038】

スパッタ装置3は、ロータリーポンプ、ターボ分子ポンプなどの真空排気手段（図示せず）を介して所定の真空圧（例えば、10<sup>-5</sup>Pa）に保持できる真空チャンバ31を有し、スパッタ室（処理室）32を構成する。真空チャンバ31の上部には、例えばFPD製造の際に用いられる大面積の処理基板Sを電位的にフローティング状態で保持する基板ホルダー33が設けられている。真空チャンバ31にはまた、プロセスガスをスパッタ室32内に導入するガス導入管（図示せず）が設けられ、Ar等の希ガスからなるスパッタガスや反応性スパッタにより所定の薄膜を形成する場合に処理基板S表面に形成しようとする薄膜の組成に応じて適宜選択されるO<sub>2</sub>、N<sub>2</sub>やH<sub>2</sub>Oなどの反応性ガスとが処理室32に導入できる。

30

## 【0039】

スパッタ室32には、処理基板Sに対向させて、複数枚（本実施の形態では8枚）のターゲット41a乃至41hが等間隔で並設されている。各ターゲット41a乃至41hは、Al、Ti、Mo、インジウム及び錫の酸化物（ITO）やインジウム及び錫の合金など、処理基板S表面に形成しようとする薄膜の組成に応じて公知の方法で作製され、例えば略直方体（上面視において長方形）など同形状に形成されている。

## 【0040】

各ターゲット41a乃至41hは、スパッタ中、ターゲット41a乃至41hを冷却するバッキングプレートに、インジウムやスズなどのボンディング材を介して接合されている。各ターゲット41a乃至41hは、未使用時のスパッタ面が処理基板Sに平行な同一平面上に位置するように、絶縁部材を介して真空チャンバ31に設けられる。また、ターゲット41a乃至41hの後方（スパッタ面と背向する側）には、公知の構造を有する磁石組立体（図示せず）が配置され、各ターゲット41a乃至41hの前方（スパッタ面）側で電離した電子及びスパッタリングによって生じた二次電子を捕捉することで、各ターゲット41a乃至41h前方での電子密度を高くしてプラズマ密度が高まり、スパッタレートを高くできる。

40

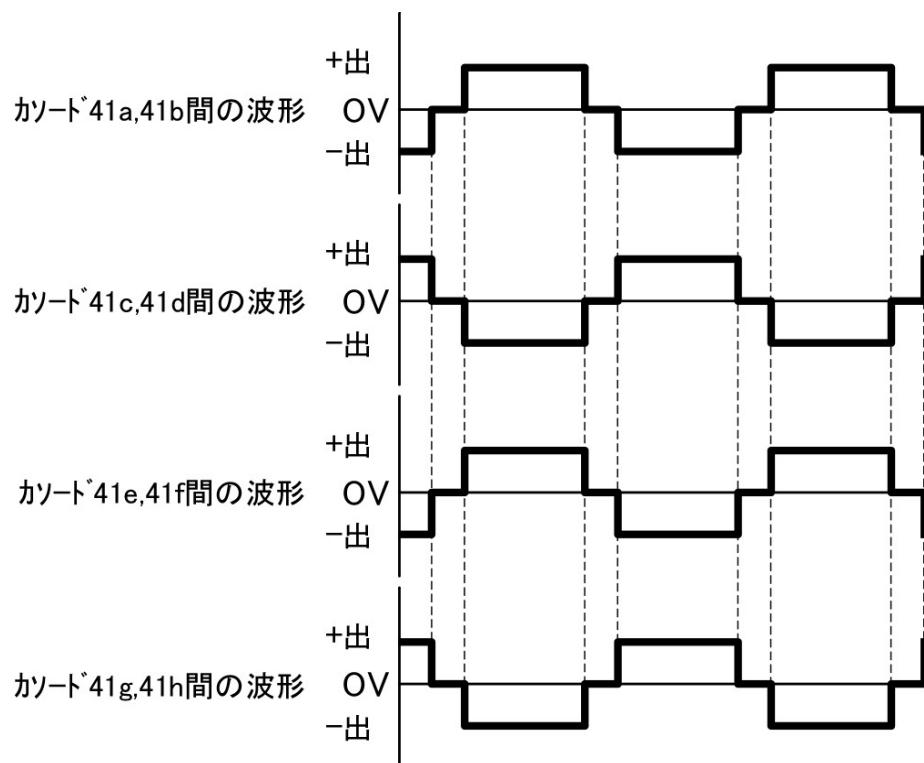

## 【0041】

各ターゲット41a乃至41hは、隣り合う2枚で一対のターゲット（41aと41b、41cと41d、41eと41f、41gと41h）を構成し、一対のターゲット41a乃至41h毎に割当てて上記実施の形態のバイポーラパルス電源E1乃至E4が設けら

50

れ、バイポーラパルス電源 E 1 乃至 E 4 からの出力ライン 2 4 a、2 4 b が各一対のターゲット 4 1 a、4 1 b (4 1 c 及び 4 1 d、4 1 e 及び 4 1 f、4 1 g 及び 4 1 h) に接続されている。これにより、バイポーラパルス電源 E 1 乃至 E 4 によって、各一対のターゲット 4 1 a 乃至 4 1 h に対し交互に極性をバイポーラパルス状の電力供給が可能になる。

#### 【0042】

本実施の形態では、安定してターゲット 4 1 a 乃至 4 1 h の前方にプラズマを生成するために、相互に隣接するターゲット 4 1 a 乃至 4 1 h の極性が相互に反転するように、各バイポーラパルス電源 E 1 乃至 E 4 を同期させて電力供給される（図 5 参照）。この同期運転のために、各バイポーラパルス電源 E 1 乃至 E 4 の第 2 の C P U 回路 2 1 に通信自在に接続された C P U からなる統括制御手段 5 が設けられている。10

#### 【0043】

そして、各バイポーラパルス電源 E 1 乃至 E 4 の出力短絡用のスイッチングトランジスタ S W 5 の短絡状態で、各バイポーラパルス電源 E 1 乃至 E 4 毎に、第 1 及び第 4 のスイッチングトランジスタ S W 1、S W 4 と、第 2 及び第 3 のスイッチングトランジスタ S W 2、S W 3 とのオン、オフのタイミングが反転すると共に、相互に隣合うターゲット 4 1 a 乃至 4 1 h への極性が反転するように各スイッチングトランジスタ S W 1 乃至 S W 4 を作動させた後、統括制御手段 5 からの出力でスイッチングトランジスタ S W 5 の短絡が解除され、一対のターゲットのうち各一方のもの 4 1 a、4 1 c、4 1 e、4 1 g に出力する。20

#### 【0044】

次いで、統括制御手段 5 からの出力で各バイポーラパルス電源 E 1 乃至 E 4 の出力短絡用のスイッチングトランジスタ S W 5 を短絡し、各スイッチングトランジスタ S W 1 乃至 S W 4 を切換えた後に、統括制御手段からの出力でスイッチングトランジスタ S W 5 の短絡が解除し、他方の各ターゲット 4 1 b、4 1 d、4 1 f、4 1 h に出力する。そして、上記制御を繰り返すことで、各ターゲット 4 1 a 乃至 4 1 h に所定の周波数でバイポーラパルス状に電力供給されて同期運転される。

#### 【0045】

この同期運転の際、統括制御手段 5 によって各バイポーラパルス電源 E 1 乃至 E 4 の出力短絡用のスイッチング素子 S W 5 のオン、オフの切換えのタイミングのみを同期させれば良いため、各バイポーラパルス電源 E 1 乃至 E 4 のスイッチング素子 S W 1 乃至 S W 4 を十分な余裕を持って作動させることができ、各バイポーラパルス電源のスイッチング素子や制御回路に個体差があっても、その同期運転は容易である。30

#### 【0046】

また、各バイポーラパルス電源 E 1 乃至 E 4 は、スペッタリング中に、いずれか 1 個のバイポーラパルス電源において検出回路 2 5 で検出した出力電流 I a が、定常出力電流値 I c を超えたとき、そのバイポーラパルス電源のアーク検出制御回路 2 3 による出力短絡用のスイッチングトランジスタ S W 5 の切換えで上述したマイクロアーク処理を行うよう構成されている。

#### 【0047】

いずれか 1 個のバイポーラパルス電源でマイクロアーク処理を行う際、このバイポーラパルス電源からの出力ケーブル 2 4 a、2 4 b が接続された一対のターゲットと、この一対のターゲットに隣合う他のバイポーラパルス電源からの出力ケーブル 2 4 a、2 4 b が接続された他のターゲットとの電位が相互に一致していると、アーク放電を消弧し易くできる。

#### 【0048】

本実施の形態では、いずれか 1 個のバイポーラパルス電源 E 1 乃至 E 4 においてマイクロアーク処理を開始したとき、それが統括制御手段 5 を介して、隣合うターゲットに出力しているバイポーラパルス電源の第 2 の C P U 回路 2 1 にそれが出力される。この場合、その第 2 の C P U 回路 2 1 を介して、出力発振用のドライバー回路 2 3 によって出力短絡50

用のスイッチングトランジスタ SW5 が一旦短絡され、各スイッチングトランジスタ SW1 乃至 SW4 の作動状態に応じて、電位が相互に一致するように各スイッチングトランジスタ SW1 乃至 SW4 の作動のタイミングが変更され、出力短絡用のスイッチングトランジスタ SW5 の短絡が解除され、ターゲットに出力されるようにしている。

#### 【0049】

尚、本実施の形態では、各バイポーラパルス電源 E1 乃至 E4 を同期運転するため統括制御手段を設けたものについて説明したが、いずれか1個の第2のCPU回路21を統括制御手段として構成し（マスター電源）、この統括制御手段の出力によって、他のバイポーラパルス電源 E2 乃至 E4（スレーブ電源）の作動が制御されるようにしてもよい。また、上記のものでは、一つのバイポーラパルス電源 E1 乃至 E4 で一対のターゲットに出力するものを例に説明したが、複数台のバイポーラパルス電源 E1 乃至 E4 で一対のターゲットに出力するような場合にも本発明を適用できる。10

#### 【図面の簡単な説明】

#### 【0050】

【図1】本発明のバイポーラパルス電源の構成を概略的に示す図。

【図2】本発明のバイポーラパルス電源の出力制御を説明する図。

【図3】従来のバイポーラパルス電源でのマイクロアーク処理時の電流変化を説明する図。20

【図4】(a) 及び (b) は、一対の電極への出力電圧及び出力電流の波形を説明する図。

【図5】本発明のバイポーラパルス電源でのマイクロアーク処理を説明する図。

【図6】本発明のバイポーラパルス電源でのマイクロアーク処理時の電流変化を説明する図。

【図7】本発明の電源装置を用いたスパッタリング装置を概略的に説明する図。

【図8】本発明の電源装置の出力制御を説明する図。

#### 【符号の説明】

#### 【0051】

1 直流電力供給部

2 発振部

22 ブリッジ回路

24a、24b 出力ケーブル

25 出力電流、電圧検出回路

27 アーク検知制御回路

28 インダクタ

E バイポーラパルス電源

SW1 乃至 SW6 スイッチング素子

T1、T2 電極（ターゲット）

10

20

30

【図1】

【図2】

【図3】

【図4】

(a)

(b)

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

審査官 槙木澤 昌司

(56)参考文献 特開平06-113561(JP,A)

特開2000-331798(JP,A)

特開2009-284733(JP,A)

特開2009-280890(JP,A)

特開2009-284734(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 7/48

H02M 7/5387

C23C 14/34

H05H 1/46