(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년02월05일

(11) 등록번호 10-1591855

(24) 등록일자 2016년01월29일

(51) 국제특허분류(Int. Cl.)

*H01L 21/336* (2006.01) *H01L 21/3063* (2006.01)

*H01L 21/31* (2006.01)

(21) 출원번호 10-2008-0079538

(22) 출원일자 2008년08월13일

심사청구일자 2013년08월13일

(65) 공개번호 10-2009-0031216

(43) 공개일자 2009년03월25일

(30) 우선권주장

11/858,535 2007년09월20일 미국(US)

(56) 선행기술조사문헌

JP2001176839 A\*

WO2007054403 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

삼성전자 주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

글로벌파운드리즈 싱가포르 퍼티이 엘티디

싱가포르 738406 스트리트 2 우드랜즈 인더스트리

얼 파크 디 60

(뒷면에 계속)

(72) 발명자

박상진

경기 용인시 기흥구 한보라1로64번길 22, 104동

1406호 (보라동, 삼성래미안아파트)

헨리, 리차드 오.

미국, 12533-6683 뉴욕, 호프웰 정션, 2070 루트

52

(뒷면에 계속)

(74) 대리인

특허법인가산

전체 청구항 수 : 총 5 항

심사관 : 박성호

(54) 발명의 명칭 반도체 집적 회로 장치의 제조 방법

**(57) 요 약**

반도체 집적 회로 장치의 제조 방법이 제공된다. 상기 반도체 집적 회로 장치의 제조 방법은 반도체 기판과, 상기 반도체 기판 상에 게이트와, 상기 게이트 측벽에 형성된 질화막과, 상기 반도체 기판과 상기 질화막 사이와 상기 게이트와 상기 질화막 사이에 형성된 산화막과, 상기 게이트에 인접하여 상기 반도체 기판 내에 형성된 불순물 영역을 포함하는 반도체 소자를 제공하고, 산화막에 대한 질화막의 선택비가 1 초과인 불산(hydrofluoric acid)을 이용하여 상기 질화막의 적어도 일부를 치각하고, 상기 반도체 기판과 상기 게이트 상에 스트레스막을 형성하는 것을 포함한다.

**대 표 도 - 도1f**

(73) 특허권자

인피니언 테크놀로지스 아게

독일연방공화국 85579 노이비베르크 암 캄페온

1-12

인터넷서널 비즈니스 머신즈 코오퍼레이션

미국 뉴욕주 10504 아몬크 뉴 오차드 로드

(72) 발명자

권오성

미국, 12590 뉴욕, 와핑거스 폴스, 올엔젤힐가 35

9번지

권오정

미국, 12533 뉴욕, 호프웰 정션, 판루 코트 5

탄, 용 시양

미국, 12533-6683 뉴욕, 호프웰 정션, 2070 루트

52

---

## 명세서

### 청구범위

#### 청구항 1

반도체 기판과, 상기 반도체 기판 상에 게이트와, 상기 게이트 측벽에 형성된 질화막과, 상기 반도체 기판과 상기 질화막 사이와 상기 게이트와 상기 질화막 사이에 형성된 산화막과, 상기 게이트에 인접하여 상기 반도체 기판 내에 형성된 불순물 영역을 포함하는 반도체 소자를 제공하고,

상기 질화막 상에 블록킹 산화막 및 블록킹 질화막을 순차적으로 형성하고,

산화막에 대한 질화막의 선택비가 1 초과인 불산(hydrofluoric acid)을 이용하여 상기 블록킹 질화막의 적어도 일부를 식각하고,

상기 선택비가 1 미만인 불산을 이용하여 상기 블록킹 산화막의 적어도 일부를 식각하고,

상기 선택비가 1 초과인 불산을 이용하여 상기 질화막의 적어도 일부를 식각하고,

상기 반도체 기판과 상기 게이트 상에 식각 정지막 및 스트레스막을 순차적으로 형성하고,

상기 선택비가 1 초과인 불산을 이용하여 상기 스트레스막을 제거하는 것을 포함하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

삭제

#### 청구항 6

제 1항에 있어서,

상기 스트레스막을 형성하기 전에, 상기 불순물 영역 내에 실리사이드막을 형성하는 것을 더 포함하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 7

삭제

#### 청구항 8

삭제

#### 청구항 9

삭제

#### 청구항 10

제 1항에 있어서,

상기 반도체 소자는 상기 반도체 기판 상에 형성된 잔류 산화막, 또는 상기 질화막 상에 형성된 잔류 산화막을

더 포함하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 11

제 1항에 있어서,

산화막에 대한 질화막의 선택비가 1 초과인 불산을 이용하여 상기 질화막의 일부를 식각하고,

상기 스트레스막을 형성하기 전에, 상기 식각 후 잔류하는 상기 질화막을 제거하는 것을 더 포함하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 12

삭제

#### 청구항 13

반도체 기판과, 상기 반도체 기판 상에 형성된 게이트와, 상기 게이트의 양측벽에 순차적으로 형성된 스페이서 산화막과 스페이서 질화막과, 상기 반도체 기판과 상기 스페이서 질화막 사이와 상기 스페이서 산화막과 상기 스페이서 질화막 사이에 형성된 접착 산화막과, 상기 스페이서 산화막에 정렬되어 형성된 제1 불순물 영역과, 상기 스페이서 질화막에 정렬되어 형성된 제2 불순물 영역을 포함하는 반도체 소자를 제공하고,

상기 스페이서 질화막 상에 블록킹 산화막 및 블록킹 질화막을 순차적으로 형성하고,

산화막에 대한 질화막의 선택비가 1 초과인 불산(hydrofluoric acid)를 이용하여 상기 블록킹 질화막의 적어도 일부를 습식 식각하고,

상기 선택비가 1 미만인 불산을 이용하여 상기 블록킹 산화막의 적어도 일부를 습식 식각하고,

상기 선택비가 1 초과인 불산을 이용하여 상기 스페이서 질화막의 적어도 일부를 습식 식각하고, 상기 제2 불순물 영역 내에 실리사이드막을 형성하고,

상기 반도체 기판과 상기 게이트 상에 식각 정지막과 스트레스막을 순차적으로 형성하는 것을 포함하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

#### 청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

청구항 35

삭제

### 발명의 설명

#### 발명의 상세한 설명

#### 기술 분야

[0001] 본 발명은 안정적인 식각이 가능한 반도체 집적 회로 장치의 제조 방법에 관한 것이다.

### 배경기술

[0002] 질화막은 물리적, 화학적으로 안정적이므로, 반도체 집적 회로 장치의 제조 과정 중에 많이 사용된다. 예를 들어, 질화막은 산화막에 비해 기계적 강도, 수증기 배리어(barrier) 특성, 나트륨 배리어 특성 등이 더 우수하다. 반면, 질화막은 식각에 의해 제거하는 것이 용이하지 않다.

[0003] 이러한 질화막은 산화막에 대해 선택적으로 제거되어야 하는 경우가 많다. 종래에는 인산(phosphoric acid,  $H_3PO_4$ )을 사용하여 산화막에 대해서 선택적으로 질화막을 식각하였다. 예를 들어, 인산이 담긴 배스(bath)에 질화막과 산화막이 형성된 반도체 기판을 투입하고, 배스를 약 160~170°C의 온도로 가열함으로써 식각 공정을 진행한다. 이 때, 질화막의 식각율은 약 40~45Å/min이고, 산화막의 식각율은 약 1.2~2.0Å/min 일 수 있다. 즉, 약 160~170°C의 온도에서 산화막에 대한 질화막의 선택비(selectivity for nitride to oxide)은 약 26~27이 된다.

[0004] 그런데, 인산은 점성(viscosity)이 높기 때문에, 약 2시간 정도 예열(pre-heating)을 해야 약 160~170°C에 이를 수 있다. 또한, 인산은 안정성이 떨어지기 때문에, 실제 인산을 이용한 식각 공정이 진행되기 전에 적어도 2번의 더미 사이클(dummy cycle)이 요구된다. 또한, 인산을 이용한 식각은 비용이 많이 듈다.

### 발명의 내용

#### 해결 하고자 하는 과제

[0005] 본 발명이 이루고자 하는 기술적 과제는, 안정적인 식각이 가능한 반도체 집적 회로 장치의 제조 방법을 제공하는 것이다.

[0006] 본 발명의 기술적 과제들은 이상에서 언급한 기술적 과제로 제한되지 않으며, 언급되지 않은 또 다른 기술적 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

#### 과제 해결手段

[0007] 상기 기술적 과제를 달성하기 위한 본 발명의 일 태양에 따른 반도체 집적 회로 장치의 제조 방법은 반도체 기판과, 상기 반도체 기판 상에 게이트와, 상기 게이트 측벽에 형성된 질화막과, 상기 반도체 기판과 상기 질화막 사이와 상기 게이트와 상기 질화막 사이에 형성된 산화막과, 상기 게이트에 인접하여 상기 반도체 기판 내에 형성된 불순물 영역을 포함하는 반도체 소자를 제공하고, 산화막에 대한 질화막의 선택비가 1 초과인 불산(hydrofluoric acid)을 이용하여 상기 질화막의 적어도 일부를 식각하고, 상기 반도체 기판과 상기 게이트 상에 스트레스막을 형성하는 것을 포함한다.

[0008] 상기 기술적 과제를 달성하기 위한 본 발명의 다른 태양에 따른 반도체 집적 회로 장치의 제조 방법은 반도체 기판과, 상기 반도체 기판 상에 형성된 게이트와, 상기 게이트의 양측벽에 순차적으로 형성된 스페이서 산화막과 스페이서 질화막과, 상기 반도체 기판과 상기 스페이서 질화막 사이와 상기 스페이서 산화막과 상기 스페이서 질화막 사이에 형성된 접착 산화막과, 상기 스페이서 산화막에 정렬되어 형성된 제1 불순물 영역과, 상기 스페이서 질화막에 정렬되어 형성된 제2 불순물 영역을 포함하는 반도체 소자를 제공하고, 산화막에 대한 질화막의 선택비가 1 초과인 불산(hydrofluoric acid)을 이용하여 상기 스페이서 질화막의 적어도 일부를 습식 식각하고, 상기 제2 불순물 영역 내에 실리사이드막을 형성하고, 상기 반도체 기판과 상기 게이트 상에 식각 정지막과 스트레스막을 순차적으로 형성하는 것을 포함한다.

[0009] 상기 기술적 과제를 달성하기 위한 본 발명의 또 다른 태양에 따른 집적 회로 장치의 제조 방법은 반도체 기판 상에 형성된 제1 및 제2 반도체 소자를 제공하되, 상기 각 반도체 소자는 상기 반도체 기판 상에 게이트와, 상기 게이트에 인접하여 상기 반도체 기판 내에 형성된 불순물 영역을 포함하고, 상기 제1 및 제2 반도체 소자 상에 블로킹(blocking) 산화막 및 블로킹 질화막을 순차적으로 형성하고, 산화막에 대한 질화막의 선택비가 1초과인 불산(hydrofluoric acid)을 이용하여 상기 제1 반도체 소자 상에 형성된 블로킹 질화막을 식각하는 것은 포함한다.

[0010] 상기 기술적 과제를 달성하기 위한 본 발명의 또 다른 태양에 따른 집적 회로 장치의 제조 방법은 반도체 기판 상에 형성된 제1 및 제2 반도체 소자를 제공하되, 상기 각 반도체 소자는 상기 반도체 기판 상에 게이트와, 상

기 게이트에 인접하여 상기 반도체 기판 내에 형성된 불순물 영역을 포함하고, 상기 제1 및 제2 반도체 소자 상에 식각 정지막 및 스트레스막을 순차적으로 형성하고, 산화막에 대한 질화막의 선택비가 1초과인 불산(hydrofluoric acid)를 이용하여 상기 제1 반도체 소자 상에 형성된 스트레스막을 제거하는 것을 포함한다.

[0011] 상기 기술적 과제를 달성하기 위한 본 발명의 또 다른 태양에 따른 집적 회로 장치의 제조 방법은 반도체 기판 상에 순차적으로 형성된 패드 산화막 및 패드 질화막을 형성하고, 상기 패드 질화막을 식각 마스크로 이용하여 상기 반도체 기판 내에 트렌치를 형성하고, 상기 트렌치를 따라 라이너 산화막을 컨포말하게(conformally) 형성하고, 상기 라이너 산화막 및 상기 패드 질화막을 따라 라이너 질화막을 컨포말하게 형성하고, 상기 라이너 질화막 상에 상기 트렌치가 매립되도록 매립 산화막을 형성하고, 산화막에 대한 질화막의 선택비는 약 0.7 ~ 약 1.4 인 제1 불산을 이용하여 상기 패드 질화막의 상면이 노출되도록 상기 매립 산화막의 일부와 상기 라이너 질화막의 일부를 식각하고, 상기 패드 질화막을 제거하는 것을 포함한다.

[0012] 상기 기술적 과제를 달성하기 위한 본 발명의 또 다른 태양에 따른 집적 회로 장치의 제조 방법은 반도체 기판 상에 순차적으로 형성된 패드 산화막 및 패드 질화막과, 상기 패드 산화막 및 패드 질화막을 식각 마스크로 이용하여 상기 반도체 기판 내에 형성된 트렌치와, 상기 트렌치를 따라 컨포말하게 형성된 라이너 산화막과, 상기 라이너 산화막 및 상기 패드 질화막을 따라 컨포말하게 형성된 라이너 질화막과, 상기 라이너 질화막 상에 상기 트렌치가 매립되도록 형성된 매립 산화막을 포함하는 반도체 기판을 배스(bath)에 위치시키고, 상기 배스 내에서 불산의 온도 및/또는 농도를 변화시켜면서, 상기 매립 산화막의 일부, 상기 라이너 질화막의 일부, 상기 패드 질화막을 식각하는 것을 포함한다.

[0013] 본 발명의 기타 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

### 발명의 실시를 위한 구체적인 내용

[0014] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

[0015] 하나의 소자(elements)가 다른 소자와 "접속된(connected to)" 또는 "커플링된(coupled to)" 이라고 지칭되는 것은, 다른 소자와 직접 연결 또는 커플링된 경우 또는 중간에 다른 소자를 개재한 경우를 모두 포함한다. 반면, 하나의 소자가 다른 소자와 "직접 접속된(directly connected to)" 또는 "직접 커플링된(directly coupled to)"으로 지칭되는 것은 중간에 다른 소자를 개재하지 않은 것을 나타낸다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. "및/또는"은 언급된 아이템들의 각각 및 하나 이상의 모든 조합을 포함한다.

[0016] 비록 제1, 제2 등이 다양한 소자, 구성요소 및/또는 섹션들을 서술하기 위해서 사용되나, 이들 소자, 구성요소 및/또는 섹션들은 이들 용어에 의해 제한되지 않음은 물론이다. 이들 용어들은 단지 하나의 소자, 구성요소 또는 섹션들을 다른 소자, 구성요소 또는 섹션들과 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 소자, 제1 구성요소 또는 제1 섹션은 본 발명의 기술적 사상 내에서 제2 소자, 제2 구성요소 또는 제2 섹션 일 수도 있음을 물론이다.

[0017] 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다(comprises)" 및/또는 "포함하는(comprising)"은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

[0018] 다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어(기술 및 과학적 용어를 포함)는 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않는 한 이상적으로 또는 과도하게 해석되지 않는다.

[0019] 공간적으로 상대적인 용어인 "아래(below)", "아래(beneath)", "하부(lower)", "위(above)", "상(upper)" 등은 도면에 도시되어 있는 바와 같이 하나의 소자 또는 구성 요소들과 다른 소자 또는 구성 요소들과의 상관관계를 용이하게 기술하기 위해 사용될 수 있다. 공간적으로 상대적인 용어는 도면에 도시되어 있는 방향에 더하여 사

용시 또는 동작시 소자의 서로 다른 방향을 포함하는 용어로 이해되어야 한다. 예를 들면, 도면에 도시되어 있는 소자를 뒤집을 경우, 다른 소자의 "아래(below)" 또는 "아래(beneath)"로 기술된 소자는 다른 소자의 "위(above)"에 놓여질 수 있다. 따라서, 예시적인 용어인 "아래"는 아래와 위의 방향을 모두 포함할 수 있다. 소자는 다른 방향으로도 배향될 수 있고, 이에 따라 공간적으로 상대적인 용어들은 배향에 따라 해석될 수 있다.

[0020] 표 1은 불산(hydrofluoric acid)의 상온(room temperature)에서의 선택비와, 고온(hot temperature)에서의 선택비를 정리한 표이다.

[0021] 표 1을 참조하면, LPNit는 저압(low pressure) CVD(Chemical Vapor Deposition) 공정을 통해서 형성된 질화막이고, RTNit는 상온(room temperature) CVD 공정을 통해서 형성된 질화막이고, TmOx는 열산화 방식으로 형성된 산화막이고, LTO는 저온(low temperature) CVD 공정을 통해서 형성된 산화막을 의미한다.

[0022] 불산은 온도가 높을수록 산화막에 대한 질화막의 선택비(selectivity for nitride to oxide)가 높아지고, 농도가 낮아질수록 산화막에 대한 질화막의 선택비가 높아진다. 예를 들어 구체적으로 설명하면, 300:1로 회석된 불산이 25°C의 경우 LPNit : TmOx는 0.32 : 1 이지만, 300:1로 회석된 불산이 65°C의 경우 LPNit : TmOx는 0.81 : 1로 높아짐을 알 수 있다. 또한, 65°C의 불산이 300:1로 회석된 경우 RTNit : TmOx는 2.14:1 이지만, 65°C의 불산이 1500:1로 회석된 경우에는 RTNit : TmOx는 41.8:1로 높아짐을 알 수 있다.

**표 1**

|                       | LPNit : TmOx | RTNit : TmOx | LPNit : LTO | RTNit : LTO |

|-----------------------|--------------|--------------|-------------|-------------|

| 300:1 dHF<br>at 25°C  | 0.32 : 1     | -            | -           | -           |

| 300:1 dHF<br>at 65°C  | 0.81 : 1     | 2.14 : 1     | 0.65 : 1    | 1.78 : 1    |

| 1500:1 dHF<br>at 80°C | 24.5 : 1     | 41.8 : 1     | 5.83 : 1    | 9.95 : 1    |

[0024] 불산에서 질화막을 식각하는 데 사용되는 반응종(reactive species)은 모노플로라이드종(monofluoride species)(즉, F-, HF)인 반면, 산화막을 식각하는 데 사용되는 반응종은 디플로라이드종(difluoride species)(HF<sub>2</sub>-, H<sub>2</sub>F<sub>2</sub>)이 사용된다. 따라서, 불산의 산화막에 대한 질화막의 선택비는, 불산 내에 모노플로라이드 종이 더 많은지, 디플로라이드 종이 더 많은지에 따라 결정된다. 즉, 불산의 온도가 높거나 농도가 낮아지면 디플로라이드 종보다 모노플로라이드 종이 더 많아지기 때문에, 불산의 산화막에 대한 질화막의 선택비는 높아지게 된다.

[0025] 불산의 온도가 높아질수록, 불산의 산화막에 대한 질화막의 선택비가 높아질 수 있으나, 공정 조건 등에 적절히 맞추어서 온도 범위를 조절해야 한다. 표 1에서는 불산의 온도에 대해서 65°C, 80°C에 대해서만 나타내었으나, 예를 들어, 약 65°C 이상 85°C 미만의 온도 범위내에서 불산의 온도를 조절할 수 있다. 85°C가 넘는 경우, 기술적으로 구현은 어렵지 않을 것으로 판단되나 배스(bath)를 이루는 물질이 히팅 시스템(heating system)에 따라 사용온도는 제한될 수 있다.

[0026] 또한, 불산의 농도는 낮을수록, 불산의 산화막에 대한 질화막의 선택비는 높아질 수 있으나, 공정 조건 등에 적절히 맞추어서 농도 범위를 조절해야 한다. 표 1에서는 불산의 농도에 대해서 300:1, 1500:1을 예로 들었으나, 산화막에 대한 질화막의 선택비를 충분히 올리기 위해서는 약 1000:1 ~ 약 2500:1로 회석할 수 있고, 더 자세하게는 약 1500 : 1 ~ 약 2000 : 1로 회석할 수 있다.

[0027] 표 1에서 나와있듯이, 불산의 산화막에 대한 질화막의 선택비는 인산(인산의 경우 약 26:1~27:1)과 유사한 정도 까지 조절할 수 있다. 뿐만 아니라, 불산은 인산보다 상당히 안정성이 높고, 비용이 적게 든다. 또한, 온도를 빠르게 올릴 수 있기 때문에, 부가적인 준비 시간이 불필요하다. 또한, 유사한 산화막에 대한 질화막의 선택비가 필요한 식각 공정에서, 불산(약 65°C 이상 85°C 미만)을 이용한 식각 공정은 인산(약 160~170°C)을 이용한 식각 공정에 비해서 상대적으로 낮은 온도에서 진행된다.

[0028] 이하에서는, 산화막에 대한 질화막의 선택비가 예를 들어, 24.5 : 1인 경우, "산화막에 대한 질화막의 선택비는 24.5이다."라고 기재한다.

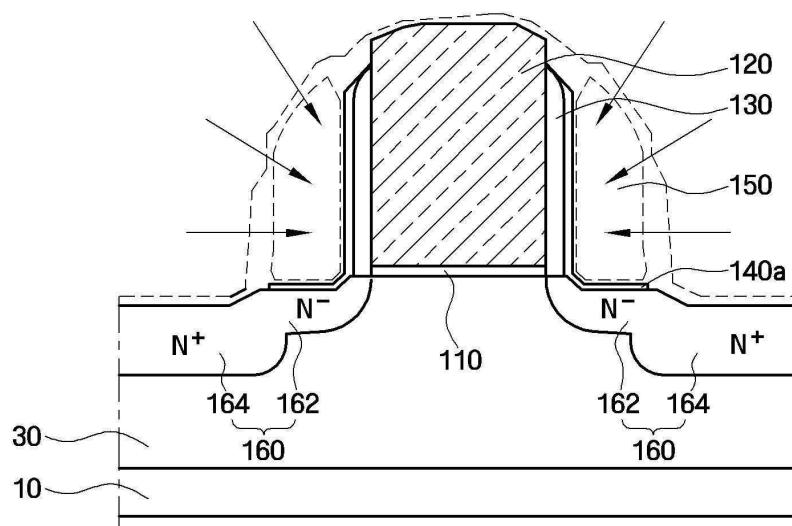

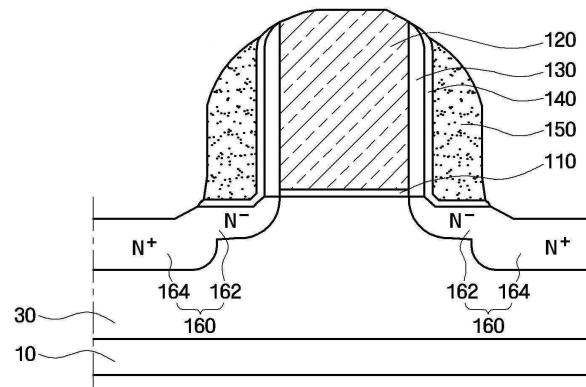

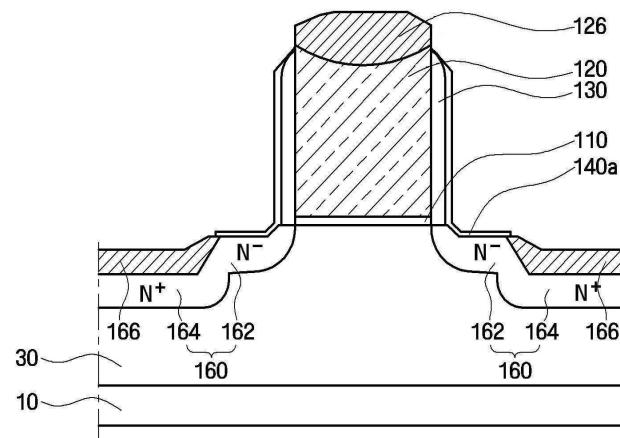

[0029] 도 1a 내지 도 1h는 본 발명의 제1 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도

들이다. 여기서는, NMOS 트랜지스터를 제조하는 것을 예로 들어 설명하였으나, 이에 한정되는 것은 아니다. 즉, PMOS 트랜지스터의 제조 과정에 적용하여도 무방하다.

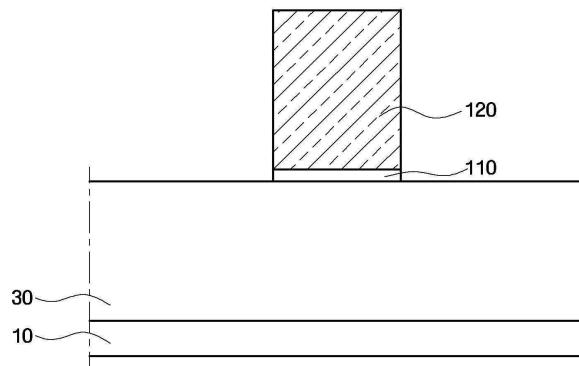

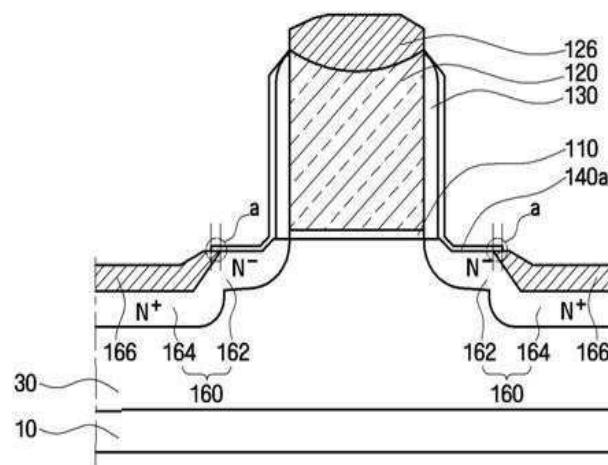

[0030] 도 1a를 참조하면, 반도체 기판(10) 상에 소자 분리 영역을 형성하여 액티브 영역을 정의하고, 액티브 영역 상에 게이트 절연막(110)과 게이트(120)를 순차적으로 형성한다. 이어서, 액티브 영역 상에 P형 불순물을 주입하여 P웰(30)을 형성한다.

[0031] 구체적으로, 반도체 기판(10)은 실리콘 기판, SOI(Silicon On Insulator) 기판, 갈륨 비소 기판, 실리콘 게르마늄 기판, 세라믹 기판, 석영 기판, 또는 디스플레이용 유리 기판 등이 될 수 있고, 소자 분리 영역(20)은 LOCOS(LOCal Oxidation of Silicon)방법을 이용한 FOX(Field OXide) 또는 STI(Shallow Trench Isolation)가 될 수 있다. 또한, 게이트 절연막(110)은 예를 들어,  $\text{SiO}_2$ ,  $\text{SiON}$ ,  $\text{Si}_3\text{N}_4$ ,  $\text{Ge}_x\text{O}_y\text{N}_z$ ,  $\text{Ge}_x\text{Si}_y\text{O}_z$ , 고유전율 물질 및 이들의 적층막이 사용될 수 있다. 여기서, 고유전율 물질은  $\text{HfO}_2$ ,  $\text{ZrO}_2$ ,  $\text{Al}_2\text{O}_3$ ,  $\text{Ta}_2\text{O}_5$ , 하프늄 실리케이트, 지르코늄 실리케이트 등이 될 수 있다. 또한, 게이트(120)는 예를 들어, 폴리 실리콘(poly Si), 불순물이 이온주입된 폴리 실리콘 등이 사용될 수 있다.

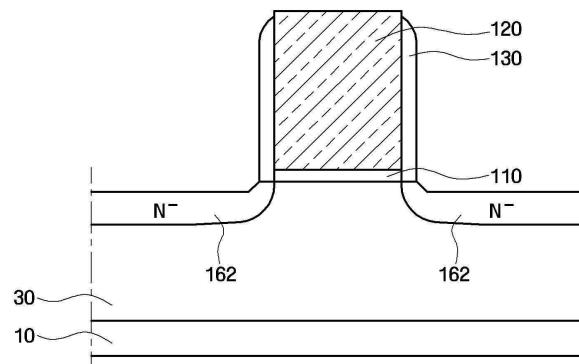

[0032] 도 1b를 참조하면, 게이트(120)의 측벽에 스페이서 산화막(130)을 형성한다. 구체적으로, 게이트(120)가 형성된 반도체 기판(10) 전면에 산화막을 형성한 후 에치백(etch back)과 같은 전면 식각 공정을 이용하여, 게이트(120)의 측벽에 스페이서 산화막(130)을 형성한다.

[0033] 이어서, 스페이서 산화막(130)에 정렬된 제1 불순물 영역(162)을 형성한다. 구체적으로, 스페이서 산화막(130)을 이온 주입 마스크로 하여 N형 불순물, 예를 들어, 비소(As)를 주입할 수 있다. 여기서, 선택적으로 액티브 영역 내에 각각 할로 이온(halo ion)을 주입할 수 있다. 할로 이온은 채널 영역의 길이가 짧아짐에 따른 편치스루우 현상을 방지하기 위하여 게이트(120) 형성 후 반도체 기판(10)의 액티브 영역의 농도를 높이기 위하여 주입되는 이온을 의미한다. 할로 이온은 소오스/드레인 영역을 형성하기 위해 주입하는 이온과 반대 타입의 이온이 주로 사용된다. 따라서, 액티브 영역 내에는 P형 불순물, 예를 들어 봉소(B)를 주입할 수 있다.

[0034] 이어서, 열공정을 실시한다. 열공정의 방식은 RTA(Rapid Thermal Annealing) 또는 LSA(LaSer Annealing) 등의 방식을 이용할 수 있다.

[0035] 도 1c를 참조하면, 스페이서 산화막(130) 상에 형성된 스페이서 질화막(150)과, 반도체 기판(10)과 스페이서 질화막(150) 사이와 스페이서 산화막(130)과 스페이서 질화막(150) 사이에 형성된 접착 산화막(140)을 형성한다. 구체적으로, 게이트(120), 스페이서 산화막(130)이 형성된 반도체 기판(10) 전면에 산화막, 질화막을 형성한 후 에치백과 같은 전면 식각 공정을 이용하여, 상기 스페이서 질화막(150)과 접착 산화막(140)을 형성한다. 스페이서 질화막(150)이 게이트(120) 및 반도체 기판(10)과 잘 접착하지 않지 않기 때문에, 접착 산화막(140)을 반도체 기판(10)과 스페이서 질화막(150) 사이, 스페이서 산화막(130)과 스페이서 질화막(150) 사이에 L자 형태로 형성한다. 이와 동시에, 접착 산화막(140)은 게이트(120) 및 반도체 기판(10)이 스페이서 질화막(150)에 의해 받는 스트레스를 최소화시켜줄 수 있다. 즉, 접착 산화막(140)은 버퍼 역할도 하게 된다. 이러한 접착 산화막(140)은 예를 들어, LTO 일 수 있으나, 이에 한정되는 것은 아니다.

[0036] 이어서, 스페이서 질화막(150)에 정렬된 제2 불순물 영역(164)을 형성한다. 구체적으로, 스페이서 질화막(150)을 이온 주입 마스크로 하여 N형 불순물, 예를 들어, 비소(As)를 주입할 수 있다. 제2 불순물 영역(164)은 제1 불순물 영역(162)보다 더 높은 도팽 농도를 갖고, 더 깊은 영역에 형성될 수 있다. 즉, 제1 및 제2 불순물 영역(162, 164)은 LDD(Lightly Diffused Drain) 구조의 소오스/드레인 영역(160)을 구성하게 된다. 도면으로 설명하지는 않았으나, NMOS 트랜지스터의 소오스/드레인 영역(160)은 다양한 구조로 변형 가능하며, 예를 들어, DDD(Double Diffused Drain), MIDDD(Mask Islanded Double Diffused Drain), MLDD(Mask LDD), LDMS(Lateral Double-diffused MOS) 구조 등이 될 수 있다.

[0037] 이어서, 열공정을 실시한다. 열공정의 방식은 RTA 또는 LSA 등의 방식을 이용할 수 있다.

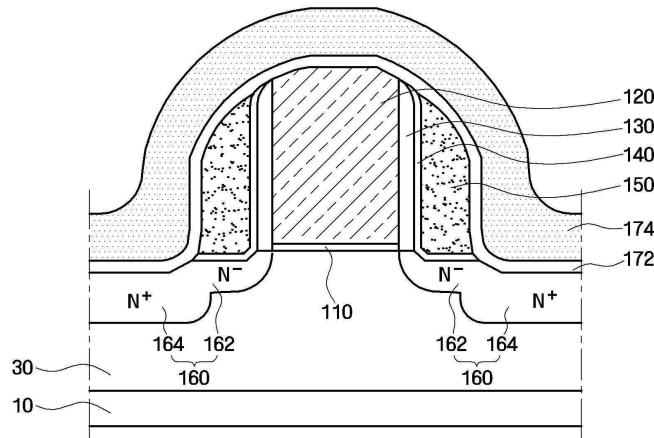

[0038] 도 1d를 참조하면, NMOS 트랜지스터 상에 블로킹 산화막(172)과 블로킹 질화막(174)을 순차적으로 형성한다.

[0039] 구체적으로, 후속 단계에서 실리사이드막을 형성하는 공정을 실시하는데, 블로킹 산화막(172)과 블로킹 질화막(174)은 반도체 기판(10) 상에 실리사이드막을 형성하지 않을 부분을 블로킹하기 위한 것이다. 실리사이드막을 형성하지 않을 부분은 예를 들어, 고속 동작이 불필요한 MOS 트랜지스터일 수 있다.

[0040] 도 1e를 참조하면, NMOS 트랜지스터 상에 블로킹 질화막(174)을 식각한다. 즉, 도시된 NMOS 트랜지스터에는 후속 단계에서 실리사이드막을 형성할 것이므로, NMOS 트랜지스터 상에 있는 블로킹 질화막(174)을 제거하는 것이

다.

[0041] 특히, 본 발명의 제1 실시예에서, 블로킹 질화막(174)은 산화막에 대한 질화막의 선택비가 1을 초과하는 불산을 이용하여 제거할 수 있다. 전술한 바와 같이, 불산은 온도가 높아지거나 농도가 낮아질수록 산화막에 대한 질화막의 선택비가 높아진다. 여기서 사용되는 불산은, 예를 들어 약 65°C 이상 약 85°C 미만일 수 있고, 약 1000 : 1 ~ 약 2500 : 1로 희석할 수 있고, 더 자세하게는 약 1500 : 1 ~ 약 2000 : 1로 희석할 수 있다. 여기서, 블로킹 산화막(172)은 식각 정지막 역할을 한다. 따라서, 블로킹 산화막(172)은 산화막에 대한 질화막의 선택비가 1을 초과하는 불산에 의해 전부 제거되지 않고, 반도체 기판(10), 스페이서 질화막(150) 및/또는 게이트(120) 상에 잔류 산화막(172a)으로 남아있게 된다.

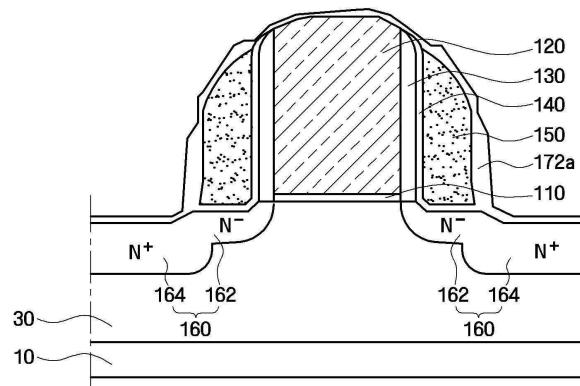

[0042] 도 1f를 참조하면, NMOS 트랜지스터의 스페이서 질화막(150)을 제거한다.

[0043] 특히, 스페이서 질화막(150)은 산화막에 대한 질화막의 선택비가 1을 초과하는 불산을 이용하여 제거할 수 있다.

[0044] 또는, 산화막에 대한 질화막의 선택비가 1 미만인 불산을 이용하여 잔류 산화막(172a)을 먼저 제거하여 스페이서 질화막(150)이 노출되도록 하고, 이어서 산화막에 대한 질화막의 선택비가 1 초과인 불산을 이용하여 스페이서 질화막을 제거할 수도 있다.

[0045] 또는, 산화막에 대한 질화막의 선택비가 1 미만인 불산을 이용하여 잔류 산화막(172a)을 먼저 제거하여 스페이서 질화막(150)이 노출되도록 하고, 이어서 산화막에 대한 질화막의 선택비가 1 초과인 불산을 이용하여 스페이서 질화막을 제거하고, 이어서 산화막에 대한 질화막의 선택비가 1 미만인 불산을 이용하여 접착 산화막(140a)의 일부를 더 제거할 수도 있다.

[0046] 전술한 바와 같이, 불산은 온도가 높아지거나 농도가 낮아질수록 산화막에 대한 질화막의 선택비가 높아진다. 예를 들어, 산화막에 대한 질화막의 선택비가 1 초과하는 불산의 온도는 약 65°C 이상 약 85°C 미만일 수 있고, 약 1000 : 1 ~ 약 2500 : 1로 희석할 수 있고, 더 자세하게는 약 1500 : 1 ~ 약 2000 : 1로 희석할 수 있다. 산화막에 대한 질화막의 선택비가 1 미만의 불산의 온도는 예를 들어, 상온일 수 있고, 산화막에 대한 질화막의 선택비가 1 초과인 불산보다 덜 희석될 수 있다.

[0047] 본 발명의 제1 실시예에서, NMOS 트랜지스터의 스페이서 질화막(150)을 제거하는 이유는 다음과 같다. 후속 단계에서 스트레스막(NMOS 트랜지스터 상에 인장 스트레스막, PMOS 트랜지스터 상에 압축 스트레스막)을 형성하는데(도 1h 참조), 스페이서 질화막(150)이 제거되면 스트레스막과 NMOS 트랜지스터의 채널 사이의 거리가 가까워지기 때문에, 스트레스 효과가 NMOS 트랜지스터의 채널에 잘 전달될 수 있다.

[0048] 그런데, 스페이서 질화막(150)을 제거할 때, 반도체 기판(10) 상에 형성되어 있는 접착 산화막(140a)이 전부 제거되어서는 안 된다. 왜냐하면, 후속 단계에서 실리사이드막을 형성하는데(도 1g), 반도체 기판(10) 상에 형성되어 있는 접착 산화막(140a)이 없다면, 실리사이드막이 게이트에 매우 인접하여 형성된다. 이러한 경우, 누설 전류가 발생될 가능성이 높아지기 때문이다. 따라서, 스페이서 질화막(150)을 제거하되, 반도체 기판(10) 상에는 접착 산화막(140a)이 남아 있어야 한다.

[0049] 도 1g를 참조하면, 제2 불순물 영역(164) 및/또는 게이트(120) 내에 실리사이드막(126, 166)을 형성한다.

[0050] 구체적으로, 스페이서 질화막(150)이 제거된 NMOS 트랜지스터 상에 NiPt 또는 NiPt/TiN과 같은 금속막을 형성한다. 이후, RTA 또는 LSA와 같은 열공정을 하여 실리사이드막(126, 166)을 형성한다. 이후, 금속막을 제거한다. 선택적으로 다시, 열공정을 진행할 수 있다.

[0051] 특히, 본 발명의 제1 실시예에서, 실리사이드막(166)은 접착 산화막(140)과 일부 오버랩될 수 있다.

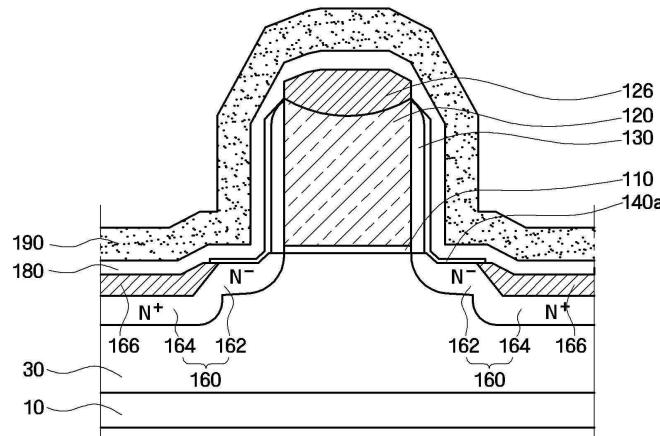

[0052] 도 1h를 참조하면, NMOS 트랜지스터 상에 식각 정지막(180)과 스트레스막(190)을 순차적으로 형성한다.

[0053] 구체적으로, 식각 정지막(180)은 LTO와 같은 산화막일 수 있고, 스트레스막(190)은 질화막일 수 있다. 스트레스막(190)으로 질화막을 쓰는 경우, N-H 본딩(bonding)과 Si-H 본딩의 비율에 따라 인장 스트레스(tensile stress)를 주게 되는지, 압축 스트레스(compressive stress)를 주게 되는지가 결정된다. 즉, N-H본딩/Si-H본딩의 비율이 약 1~5이면 인장 스트레스를 주게 되고, 약 5~20이면 압축 스트레스를 주게 된다. 인장 스트레스를 갖는 스트레스막(190)은 NMOS 트랜지스터의 동작 특성을 향상시켜 주고, 압축 스트레스를 갖는 스트레스막(190)은 PMOS 트랜지스터의 동작 특성을 향상시켜 준다. 따라서, 본 발명의 NMOS 트랜지스터 상에는 인장 스트레스를 갖는 스트레스막을 형성할 수 있다.

[0054] 한편, 본 발명의 제1 실시예에서는 반도체 기판 상에 게이트를 형성하고(도 1a 참조), 게이트 측벽에 스페이서 산화막을 형성하고, 스페이서 산화막에 정렬된 제1 불순물 영역을 형성하고(도 1b 참조), 스페이서 산화막 상에 형성된 스페이서 질화막과, 반도체 기판과 스페이서 질화막 사이와 상기 스페이서 산화막과 스페이서 질화막 사이에 형성된 접착 산화막을 형성하고, 스페이서 질화막에 정렬된 제2 불순물 영역을 형성하고(도 1c 참조), 산화막에 대한 질화막의 선택비가 1 초과인 불산(hydrofluoric acid)를 이용하여 스페이서 질화막의 적어도 일부를 습식 식각하고(도 1f 참조), 제2 불순물 영역 내에 실리사이드막을 형성하고(도 1g 참조), 반도체 기판과 게이트 상에 식각 정지막과 스트레스막을 순차적으로 형성하는 것(도 1h 참조)으로 설명하였으나, 이에 한정되는 것은 아니다.

[0055] 즉, 어떠한 방식으로 만들어졌는지에 상관없이, 게이트와, 게이트의 측벽에 형성된 질화막과, 반도체 기판과 질화막 사이와 게이트와 질화막 사이에 산화막이 있는 반도체 소자를 제공하고, 산화막에 대한 질화막의 선택비가 1 초과인 불산을 이용하여 상기 반도체 소자에 식각 공정을 진행할 수 있음은, 본 발명이 속하는 기술의 당업자에게 자명하다.

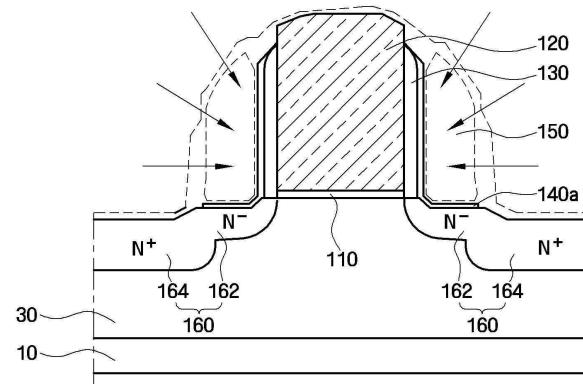

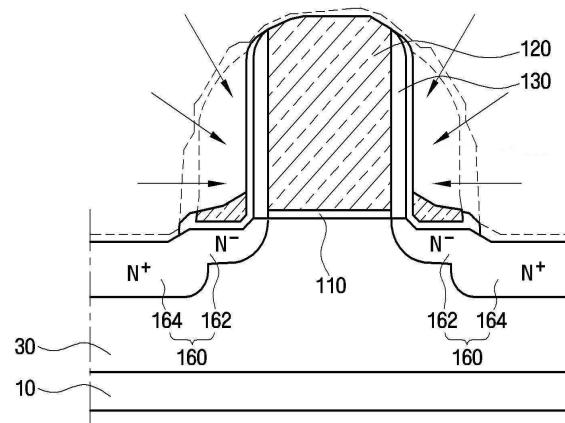

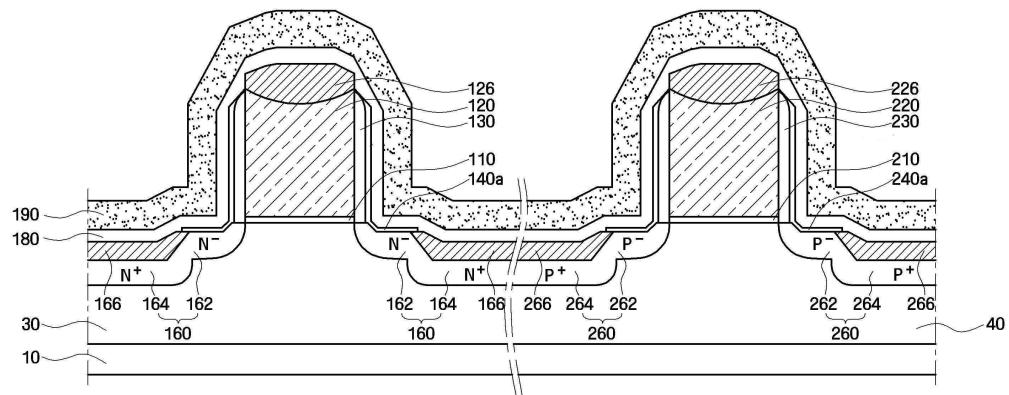

[0056] 도 2a 내지 도 2c는 본 발명의 제2 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다. 본 발명의 제2 실시예는 스페이서 질화막을 제거하는 과정이 제1 실시예와 차이가 있으므로, 이에 대해서 도 2a 내지 도 2c를 참조하여 자세히 설명하도록 한다.

[0057] 도 2a를 참조하면, NMOS 트랜지스터의 스페이서 질화막(150)의 일부를 제거한다.

[0058] 특히, 스페이서 질화막(150)은 산화막에 대한 질화막의 선택비가 1을 초과하는 불산을 이용하여 제거할 수 있다.

[0059] 또는, 산화막에 대한 질화막의 선택비가 1 미만인 불산을 이용하여 잔류 산화막(172a)을 먼저 제거하여 스페이서 질화막(150)이 노출되도록 하고, 이어서 산화막에 대한 질화막의 선택비가 1 초과인 불산을 이용하여 스페이서 질화막을 제거할 수도 있다.

[0060] 도 2b를 참조하면, 제2 불순물 영역(164) 및/또는 게이트(120) 내에 실리사이드막(126, 166)을 형성한다.

[0061] 도 2c를 참조하면, RIE(Reactive Ion Etching)를 이용하여 잔류하는 스페이서 질화막(150)을 식각한다.

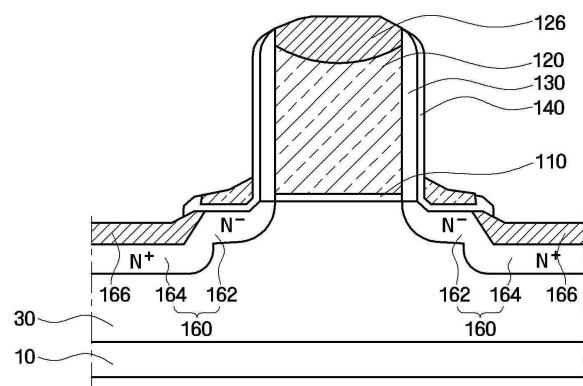

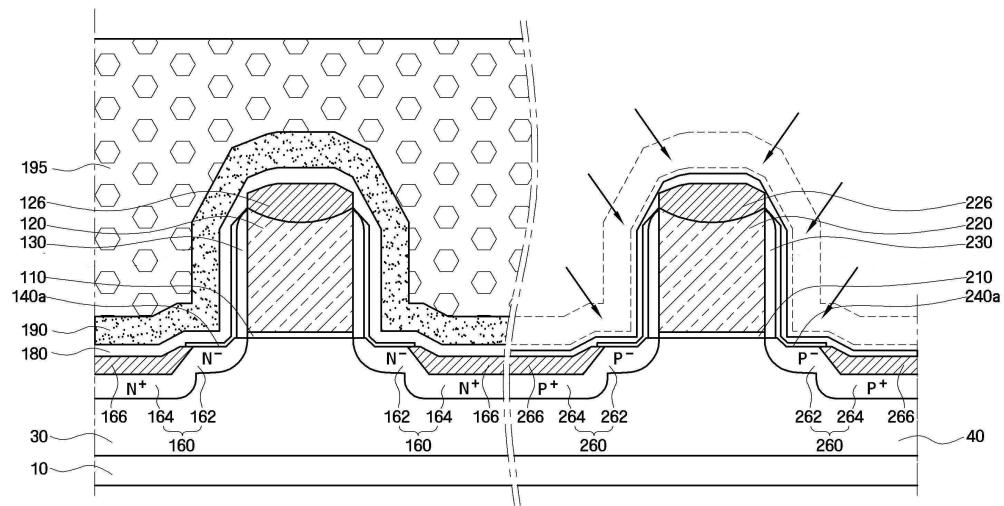

[0062] 도 3a 및 도 3b는 본 발명의 제3 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다.

[0063] 도 3a를 참조하면, 반도체 기판(10) 상에 NMOS 및 PMOS 트랜지스터를 형성한다. NMOS 트랜지스터는 도 1a 내지 도 1h를 통해서 설명한 방법을 통해서 형성하고, PMOS 트랜지스터도 상기 NMOS 트랜지스터의 제조 방법과 유사한 방법을 이용하여 형성한다. PMOS 트랜지스터에서 설명되지 않는 도면부호는 다음과 같다. 40은 N웰, 220은 게이트, 230은 스페이서 산화막, 240a는 접착 산화막, 260은 소오스/드레인 영역, 262는 제1 불순물 영역, 264는 제2 불순물 영역, 226, 266은 실리사이드막을 나타낸다.

[0064] 이어서, NMOS 및 PMOS 트랜지스터 상에는 도 1h과 같은 식각 정지막(180)과 스트레스막(190)을 형성한다. 스트레스막(190)으로 질화막을 쓰는 경우, N-H 본딩(bonding)과 Si-H 본딩의 비율에 따라 인장 스트레스를 주게 되는지, 압축 스트레스를 주게 되는지가 결정된다. 인장 스트레스를 갖는 스트레스막은 NMOS 트랜지스터의 동작 특성을 향상시켜 주고, 압축 스트레스를 갖는 스트레스막은 PMOS 트랜지스터의 동작 특성을 향상시켜 준다. 반면, PMOS 트랜지스터 상에 인장 스트레스를 주는 스트레스막이 형성되어 있으면, PMOS 트랜지스터의 동작 특성을 떨어뜨린다. 따라서, 스트레스막(174)이 인장 스트레스를 갖는 경우, PMOS 트랜지스터 상에 형성된 스트레스막(190)을 제거해야 한다.

[0065] 도 3b를 참조하면, PMOS 트랜지스터 상에 형성된 스트레스막(190)을 제거한다.

[0066] 구체적으로, 반도체 기판(10) 상에 NMOS 트랜지스터를 마스킹하는 포토레지스트 패턴(195)을 형성하고, 산화막에 대한 질화막의 선택비가 1초과인 불산을 이용하여, PMOS 트랜지스터 상에 형성된 스트레스막(190)을 제거한다. 전술한 바와 같이, 산화막에 대한 질화막의 선택비가 1 초과하는 불산의 온도는 약 65°C 이상 약 85°C 미만 일 수 있고, 약 1000 : 1 ~ 약 2500 : 1로 희석할 수 있고, 더 자세하게는 약 1500 : 1 ~ 약 2000 : 1로 희석 할 수 있다.

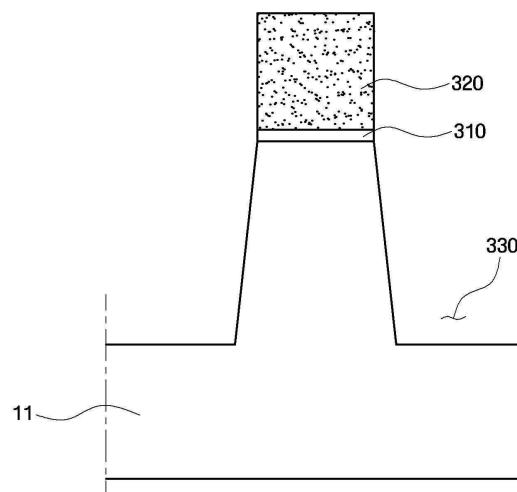

[0067] 도 4a 내지 도 4d는 본 발명의 제4 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다.

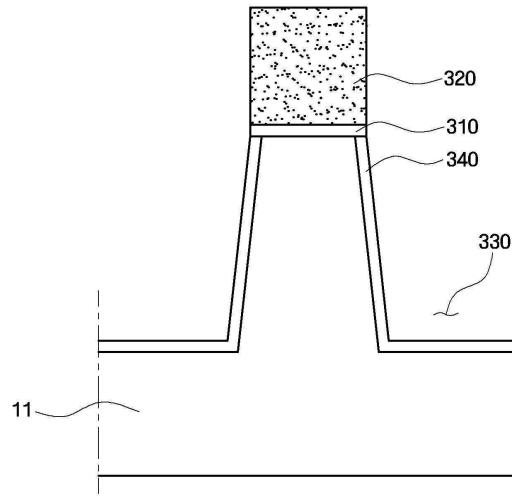

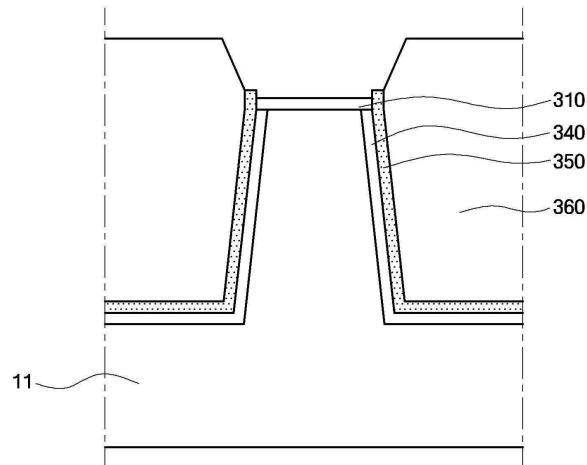

- [0068] 도 4a를 참조하면, 반도체 기판(11) 내에 트렌치(330)를 형성한다.

- [0069] 자세히 설명하면, 반도체 기판(11) 상에 트렌치를 정의하는 패드 산화막(310), 패드 질화막(320)을 순차적으로 형성한다. 패드 산화막(310)은 산화(oxidation) 방식을 이용하여 약 40~150Å의 두께로 성장시킬 수 있고, 패드 질화막(320)은 패드 산화막(310) 상에 LPCVD(Low Pressure Chemical Vapor Deposition) 방식을 이용하여 약 600~1500Å의 두께로 적층시킬 수 있다. 여기서, 패드 산화막(310)은 반도체 기판(11)과 패드 질화막(320) 사이의 스트레스를 완화시켜 준다. 패드 질화막(320)은 트렌치(330)의 형성시 식각 마스크로서 사용되며, 후속 단계의 CMP 공정에서 식각 정지막의 역할도 한다.

- [0070] 이어서, 패드 질화막(320)을 식각 마스크로 이용하여 3000Å 정도의 얇은 깊이로 트렌치(330)를 형성한다. 예를 들어, RIE(Reactive Ion Etching)을 이용하여 트렌치(330)를 형성할 수 있다.

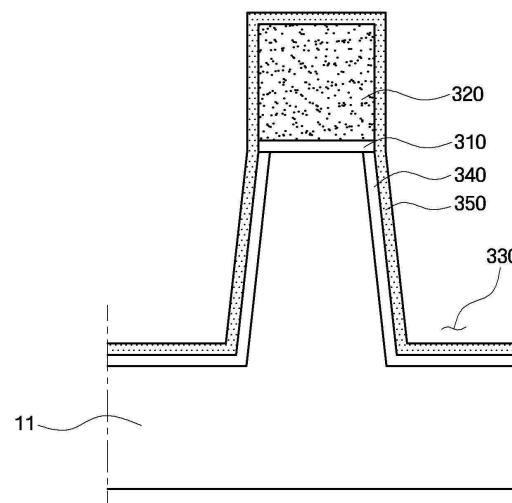

- [0071] 도 4b를 참조하면, 트렌치(330)를 따라 라이너 산화막(340)을 커포말하게(conformally) 형성한다.

- [0072] 자세히 설명하면, 트렌치(330)의 내벽에 라이너 산화막(340), 예를 들어 산화막을 약 800~900°C의 온도에서 산화 방식을 이용하여 약 100~400Å의 두께로 성장시킨다. 라이너 산화막(340)은 트렌치(330)의 내벽에, 식각에 의해 존재하는 손상된 실리콘 격자를 치유한다.

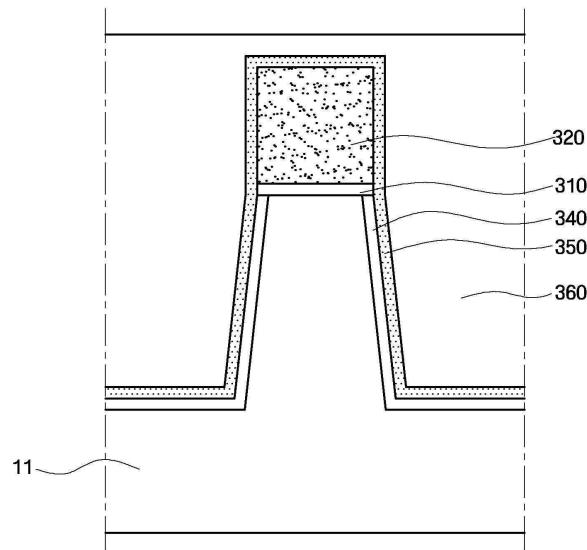

- [0073] 도 4c를 참조하면, 라이너 산화막(340) 및 패드 질화막(320)을 따라 트렌치(330)를 따라 라이너 질화막(350)을 커포말하게 형성한다.

- [0074] 자세히 설명하면, 라이너 질화막(350)은 LPCVD 방식을 이용하여 약 70~300Å의 두께로 적층시킨다.

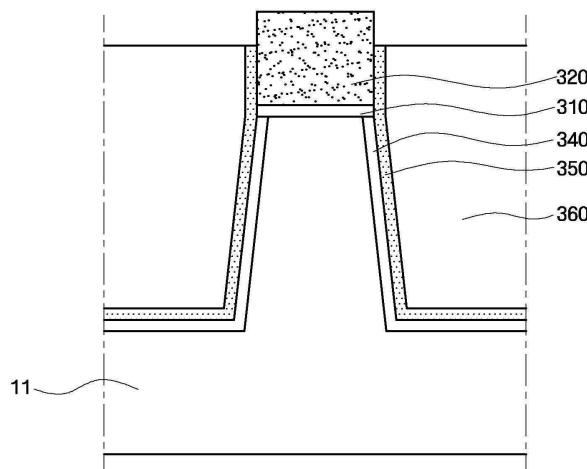

- [0075] 도 4d를 참조하면, 라이너 질화막(350) 상에 트렌치(330)가 매립되도록 매립 산화막(360)을 형성한다.

- [0076] 자세히 설명하면, 우선 트렌치를 매립하기 충분한 두께로 반도체 기판(11) 상에 산화막을 형성한다. 이 때, 트렌치(330) 내의 절연막에는 빈 공간, 즉 보이드(void)가 존재하지 않는 것이 바람직하다. 반도체 소자의 설계룰(design rule)에 따라 다소 차이가 있지만, O<sub>3</sub>-TEOS(Tetra Ortho Silicate Glass) APCVD(Atmospheric Pressure Chemical Vapor Deposition)이나 PECVD(Plasma Enhanced Chemical Vapor Deposition) 방식 또는 HDP CVD(High Density Plasma Chemical Vapor Deposition) 방식에 의해 형성할 수 있다.

- [0077] 이어서, CMP 방식을 이용하여 평탄화한다. 선택적으로, 열공정을 진행할 수 있다.

- [0078] 도 4e를 참조하면, 패드 질화막(320)의 상면이 노출되도록 매립 산화막(360)의 일부와 라이너 질화막(350)의 일부는 식각한다. 특히, 본 발명의 제4 실시예에서는 매립 산화막(360)의 일부를 제거하여 매립 산화막(360)의 높이를 낮추는 것과, 라이너 질화막(350)의 일부를 식각하는 것을 동시에 진행한다.

- [0079] 자세히 설명하면, 산화막에 대한 질화막의 선택비가 약 0.7 이상 약 1.4 미만인 불산을 이용하여 매립 산화막(360)의 일부와 라이너 질화막(350)의 일부를 식각한다. 산화막에 대한 질화막의 선택비는 약 1일 수도 있다. 예를 들어, 이러한 불산은 온도가 약 65°C 이상 85°C 미만이고, 농도는 약 300:1 정도일 수 있다.

- [0080] 도 4f를 참조하면, 패드 질화막(320)을 제거하여, 패드 산화막(310)이 드러나도록 할 수 있다.

- [0081] 인산을 이용하여 패드 질화막(320)을 제거할 수 있다.

- [0082] 또는, 산화막에 대한 질화막의 선택비가 약 10 ~ 약 50인 불산을 이용하여 패드 질화막(320)을 제거할 수 있다. 이러한 불산의 온도는 약 65°C 이상 85°C 미만일 수 있다. 또한, 산화막에 대한 질화막의 선택비를 충분히 올리기 위해서는 불산을 약 1000:1 ~ 약 2500:1로 희석할 수 있고, 더 자세하게는 약 1500 : 1 ~ 약 2000 : 1로 희석할 수 있다.

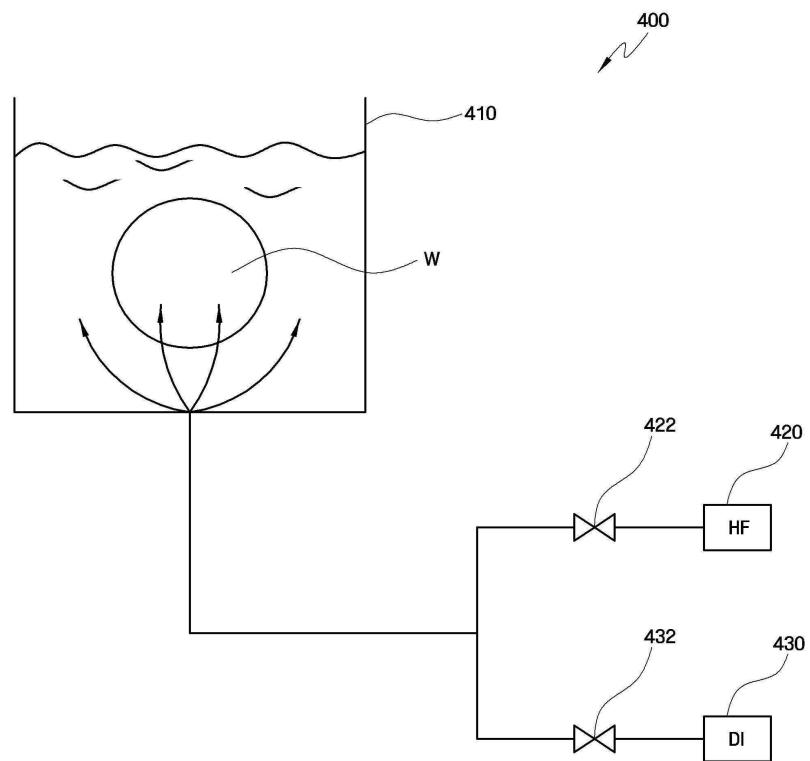

- [0083] 도 5는 본 발명의 제5 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 도면이다. 본 발명의 제 5실시예는 전술한 매립 산화막의 일부 및 라이너 질화막의 일부를 제거하는 단계(도 4e 참조), 패드 산화막을 제거하는 단계(도 4f 참조)를 하나의 배스 내에서 연속적으로 실시한다는 점이, 제4 실시예와 다르다.

- [0084] 도 5를 참조하면, 반도체 제조 설비(400)는 배스(bath)(410), 불소 저장부(420), 밸브(422), 초순수(DI) 저장부(430), 밸브(432)를 포함한다.

- [0085] 우선, 반도체 기판(W) 상에 순차적으로 형성된 패드 산화막 및 패드 질화막과, 패드 산화막 및 패드 질화막을 식각 마스크로 이용하여 반도체 기판(W) 내에 형성된 트렌치와, 트렌치를 따라 커포말하게 형성된 라이너 산화막과, 라이너 산화막 및 패드 질화막을 따라 커포말하게 형성된 라이너 질화막과, 라이너 질화막 상에 트렌치가

매립되도록 형성된 매립 산화막을 포함하는 반도체 기판(W)을 베스(410)에 위치시킨다.

[0086] 이어서, 베스(410) 내에서 불산의 온도 및/또는 농도를 변화시켜가면서, 매립 산화막의 일부, 라이너 질화막의 일부, 패드 질화막을 삭각하게 된다.

[0087] 즉, 패드 질화막의 상면이 노출되도록 매립 산화막의 일부, 라이너 질화막의 일부를 제거하는 단계에서 사용되는 불산은, 산화막에 대한 질화막의 선택비가 약 0.7 ~ 약 1.4가 되도록, 밸브(422, 432)를 조절함으로써 불산의 농도를 조절한다. 예를 들어, 불산의 농도는 약 300:1 정도일 수 있다.

[0088] 이어서, 패드 질화막을 제거하는 단계에서 사용되는 불산은, 산화막에 대한 질화막의 선택비가 약 10 ~ 약 50이 되도록, 밸브(422, 432)를 조절함으로써 불산의 농도를 조절한다. 예를 들어, 불산의 농도는 약 1000:1 ~ 약 2500:1 일 수 있고, 더 자세하게는 약 1500 : 1 ~ 약 2000 : 1일 수 있다.

[0089] 다만, 이러한 농도의 수치는 예시적인 것에 불과하나, 매립 산화막의 일부, 라이너 질화막의 일부를 제거하는 단계에서 사용되는 불산보다 농도가 낮도록 조절할 수 있다.

[0090] 또한, 본 발명의 제5 실시예에서는, 패드 질화막을 제거하는 단계의 불산과, 매립 산화막의 일부, 라이너 질화막의 일부를 제거하는 단계의 불산의 온도는 동일한 것을 예로 들었으나, 이에 한정되는 것은 아니다. 즉, 산화막에 대한 질화막의 선택비를 높이기 위해서, 매립 산화막의 일부, 라이너 질화막의 일부를 제거하는 단계에서 불산의 온도를 더 높여도 무방하다.

[0091] 본 발명의 제5 실시예에서는, 불산의 농도를 2번 조절하는 것(즉, 매립 산화막의 일부, 라이너 질화막의 일부를 제거하는 단계, 패드 질화막을 제거하는 단계에서 각각 농도를 조절함)로 나누어 설명하였으나, 본 발명의 권리범위는 이에 한정되는 것은 아니다. 즉, 하나의 베스 내에 반도체 기판(W)을 위치시키고, 불산의 온도 및/또는 농도를 3번 이상 조절하여 불산의 산화막에 대한 질화막의 선택비를 3번 이상 조절함으로써, 매립 산화막의 일부, 라이너 질화막의 일부, 패드 질화막을 제거하여도 무방하다.

[0092] 또한, 반도체 제조 설비(400)는 배치 타입(batch type)일 수도 있고, 싱글 타입(single type)일 수도 있다.

[0093] 이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

### 도면의 간단한 설명

[0094] 도 1a 내지 도 1h는 본 발명의 제1 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다.

[0095] 도 2a 내지 도 2c는 본 발명의 제2 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다.

[0096] 도 3a 및 도 3b는 본 발명의 제3 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다.

[0097] 도 4a 내지 도 4f는 본 발명의 제4 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 단면도들이다.

[0098] 도 5는 본 발명의 제5 실시예에 따른 반도체 집적 회로 장치의 제조 방법을 설명하기 위한 도면이다.

[0099] (도면의 주요부분에 대한 부호의 설명)

[0100] 110 : 게이트 절연막 120 : 게이트

[0101] 130 : 스페이서 산화막 140 : 접착 산화막

[0102] 150 : 스페이서 질화막 160 : 소오스/드레인 영역

[0103] 172 : 블로킹 산화막 174 : 블로킹 질화막

[0104] 180 : 삭각 정지막 190 : 스트레스막

|        |               |               |

|--------|---------------|---------------|

| [0105] | 310 : 패드 산화막  | 320 : 패드 질화막  |

| [0106] | 330 : 트렌치     | 340 : 라이너 산화막 |

| [0107] | 350 : 라이너 질화막 | 360 : 매립 산화막  |

| [0108] | 410 : 배스      | 420 : 불소 저장부  |

| [0109] | 430 : 초순수 저장부 |               |

### 도면

도면1a

도면1b

도면1c

도면1d

도면1e

도면1f

도면1g

도면1h

도면2a

도면2b

도면2c

도면3a

도면3b

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

도면5