(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4240985号

(P4240985)

(45) 発行日 平成21年3月18日(2009.3.18)

(24) 登録日 平成21年1月9日(2009.1.9)

(51) Int.Cl.

F 1

|             |           |

|-------------|-----------|

| HO1L 21/822 | (2006.01) |

| HO1L 27/04  | (2006.01) |

| GO6F 15/78  | (2006.01) |

| HO4N 5/60   | (2006.01) |

|      |       |      |

|------|-------|------|

| HO1L | 27/04 | E    |

| GO6F | 15/78 | 510E |

| HO4N | 5/60  | Z    |

請求項の数 1 (全 9 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2002-294860 (P2002-294860)  |

| (22) 出願日     | 平成14年10月8日 (2002.10.8)        |

| (65) 公開番号    | 特開2003-203986 (P2003-203986A) |

| (43) 公開日     | 平成15年7月18日 (2003.7.18)        |

| 審査請求日        | 平成17年9月20日 (2005.9.20)        |

| (31) 優先権主張番号 | 09/973,264                    |

| (32) 優先日     | 平成13年10月9日 (2001.10.9)        |

| (33) 優先権主張国  | 米国(US)                        |

|           |                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 501263810<br>トムソン ライセンシング<br>Thomson Licensing<br>フランス国, エフ-92100 プローニュ ビヤンクール, ケ アルフォンス<br>ル ガロ, 46番地<br>46 Quai A. Le Gallio<br>, F-92100 Boulogne-Billancourt, France |

| (74) 代理人  | 100115864<br>弁理士 木越 力                                                                                                                                                    |

| (72) 発明者  | ジーン カール センデルウエツク<br>アメリカ合衆国 インディアナ州 インディアナポリス イースト・セブンティーセカンド・ストリート 5415                                                                                                 |

最終頁に続く

(54) 【発明の名称】信号処理システム

## (57) 【特許請求の範囲】

## 【請求項 1】

信号処理システムであって、

集積回路のピンに結合され、前記集積回路内部の第1の信号に作用する第1の動作機能を与える手段と、

制御信号に応答して、外部からの第2の信号を、前記集積回路のピンに結合および非結合させる手段と、

から成り、

前記第2の信号が前記ピンに結合されると、前記集積回路内にある第2の動作機能を与える手段が、前記第2の信号に作用し、

前記第2の信号が前記ピンに結合されると、前記第1の信号が前記ピンにおいて自動的に動作不能にされる、前記信号処理システム。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、集積回路(Integrated Circuit: IC)の1つの端子に信号の機能を多重化する回路構成に関し、特に、外部信号を切り替えてICに結合させ、ICの動作機能を利用して外部信号を制御できるようにする信号処理システムに関するものである。

## 【0002】

**【従来の技術】**

信号処理回路が集積回路の形態で多量に製造されるに伴い、ICの製造者はICの接続点の数をできるだけ少なくすることが望ましい。

**【0003】**

何故なら、外部回路との接続はICパッケージ上のピン(pin)を介して行わねばならず、これはICのサイズとコストを決定する1つの要因となるからである。

**【0004】**

低コストの電子装置、例えば、テレビジョン受像機またはラジオ受信機の場合、オーディオ信号処理用に作られたICにおいて、外部オーディオ入力を備えず、内部に音量調節を有する装置の前面パネルにオーディオ/ビジュアル入力ジャックを備えることが望ましい。ICにこのような望ましい特徴を組み入れるには通常、このような補助(auxiliary)オーディオ信号の音量調節のためにオーディオ用のICを別個に使用する必要がある。これには相当に余分なコストが掛かる。従って、ICを最大限に利用するためには、ICの製造者が以前は他の目的に供していたICの端子において付加的機能を組み合わせるかまたは多重化することが望ましい。本文中で、ICの「ピン(pin)」と「端子(terminal)」は同義語である。

10

**【0005】**

集積回路のピンの多重使用については、例えば、特許文献1、特許文献2および特許文献3に開示されている。特許文献4に開示されているデジタルICでは、外部デジタル信号は、デジタル・デエンファシス(demphasiss)回路の切替えに使用されるICピンに接続される。特許文献5では、1つの入力端子を電圧レベルの異なる2つの信号に使用している。

20

**【0006】****【特許文献1】**

米国特許第4,434,474号明細書

**【特許文献2】**

米国特許第4,293,870号明細書

**【特許文献3】**

米国特許第4,173,769号明細書

**【特許文献4】**

30

米国特許第5,594,442号明細書

**【特許文献5】**

米国特許第4,675,550号明細書

**【0007】****【発明が解決しようとする課題】**

本発明の構成により、外部信号を切り替えてICに結合させることにより集積回路(IC)の貴重なピンを多重化することが可能となり、これによってICのコストおよびサイズを削減することが可能となる。

**【0008】****【課題を解決するための手段】**

40

ICを備える信号処理システムにおいて、固有の内部(inttrinsic)信号がICの1つのピンに供給され、この信号に対する第1の動作機能がそのピンに発生され、更に信号の経路に沿って発生される。この信号に対する第2の動作機能はICの内部に発生される。外来の外部信号は切り替えられてこのピンに結合され、第2の動作機能が外部信号に作用することができる。第2の信号は低いソース・インピーダンスでピンに結合され、第2の信号が切り替えられて動作すると、第1の動作機能は無効にされ(defeat)て、第1の信号は大幅に減衰される。回路が切り替えられて第2の信号をピンに結合させないようにすると、外部信号の信号路および低いソース・インピーダンスは何れも外されるので、第1の動作機能およびICのピンにおける第1の信号が回復される。

特許請求の範囲と実施例との対応関係を実施例で使われている参照番号を用いて示すと

50

以下の通りである。

(請求項 1) 信号処理システムであつて、

集積回路のピン(51)において、前記集積回路内部の第1の信号に第1の動作機能を与える手段(20)と、

外部からの第2の信号(70)を、前記集積回路のピンに結合させる手段(40~60)とから成り、

前記集積回路内にある第2の動作機能を与える手段(22)が、前記第2の信号に作用し、

前記第2の信号は、インまたはアウトに切り替えられ、前記第2の信号がインのとき、

前記第1の信号が前記ピンにおいて動作不能にされる、前記信号処理システム。

10

### 【0009】

#### 【発明の実施の形態】

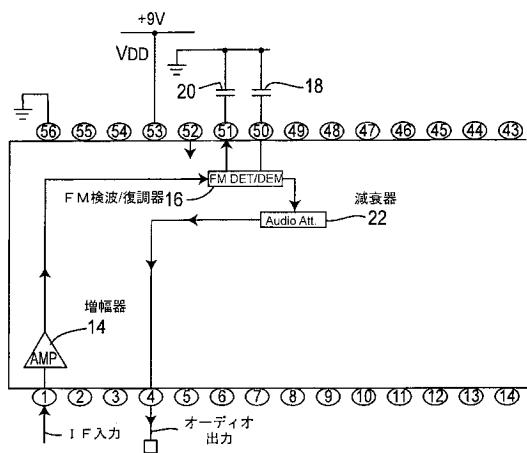

この集積回路は、東芝製のTB1253ANマイクロプロセッサである。図1は、関係するICピンの概略図を示す。4.5MHzの音声搬送波IF信号はピン1に結合される。IF信号は、増幅器14で増幅され、FM検波器/復調器(detector/demodulator)16で増幅され復調される。ピン50は直流(DC)フィルタ・ピンであり、コンデンサ18はグランド(ground:大地)に接続される。ピン51はデエンファシス・ピンであり、2200pFコンデンサ20はグランドに接続され、34Kohm内部抵抗34(図2参照)と組み合わせて、SN(信号対雑音)比改善のためにFM送信機でFM信号に与えられるプリエンファシスの等化に必要な75μsecのデエンファシス特性を与える。減衰器(attenuator)22はオーディオ信号路内で検波器/復調器16に続き、検波器16から得られる復調された内部(internal)オーディオ信号だけに作用し、外部ソースからの信号には作用しない。何故なら、このICチップにはそのような外部(extrinsic)信号を受け入れる手段が設けられていなかつたからである。減衰器22からの出力はピン4に結合され、広帯域(wideband)FMステレオ出力信号となる。しかしながら、以下に説明するように、本発明の態様によれば、デエンファシス・フィルタを含むピン51の二重(dual)使用が可能となり、このチップは減衰器22により制御できる外部信号の入力を受け入れることができる。

20

### 【0010】

30

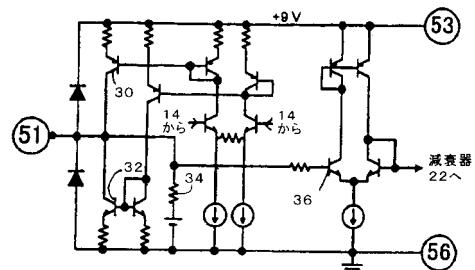

図2に、ピン51、53、56についてICの内部回路の概略図を示す。ピン56はピン51と53に対して基準電位にある。復調されたオーディオ信号はトランジスタ30、32によってピン51に結合される。デエンファシス・コンデンサ20は抵抗34と共に75μsecデエンファシス・フィルタ回路となる。次に、ピン51からの信号はトランジスタ36に、そしてオーディオ減衰器22に結合される。図2に示すチップの内部回路の残部は本発明を形成しない。従って、上述した特定の構成要素を除き、本発明を開示しクレームするのに必要な場合以外、図2のチップの内部回路についてこれ以上述べない。

### 【0011】

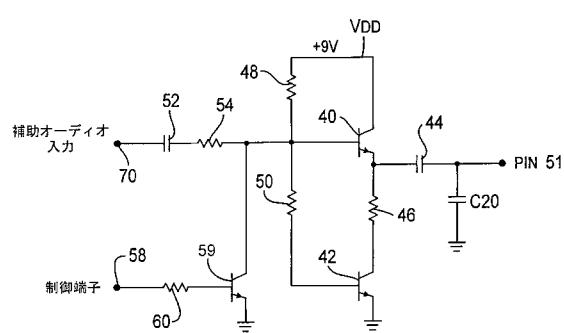

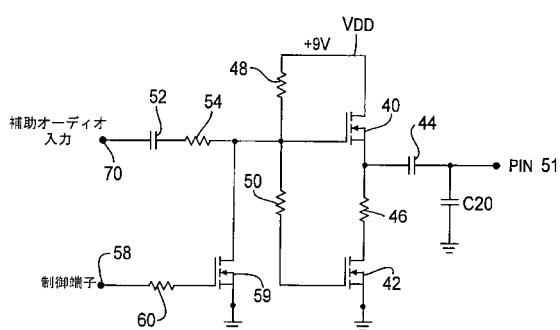

ピン51におけるデエンファシス・フィルタ・コンデンサは、オーディオ信号路内にあり、本発明の態様によれば、ピン51は外部オーディオ信号の入力点である。適正な切替え(switching)により、例えば、テレビジョン受像機の前面パネルのオーディオ・ジャックからの外部のオーディオ信号の音量を減衰する安価な方法が得られる。低インピーダンス・ソース(すなわち、コンデンサ20のインピーダンスより低い)からピン51に外部信号が入力され、この信号はトランジスタ36に、そして減衰器22に結合され、減衰器22の作用をうける。この動作を行う回路を図3に示す。図4に示す回路はNチャンネルMOSFETトランジスタを使用しており、対応する構成要素は図3と同じ番号で示す。図3で述べたことは図4にも適用され、簡略のために図4につき別個に同じ説明を繰り返し述べない。

40

### 【0012】

図3と図4について説明する。信号結合(signal coupling)モードにお

50

いて、トランジスタ40と42は同じ伝導型（例えば、NPN/NチャンネルMOSFET）であり、電源 $V_{DD}$ とグランド間に直列に接続され、外部信号はトランジスタ40のエミッタ/ソース電極から得られ、結合コンデンサ44を通り、デエンファシス・フィルタ・コンデンサ20およびピン51に至る。抵抗46はトランジスタ40のエミッタをトランジスタ42のコレクタに結合させる。バイアス分圧抵抗48、50（電源 $V_{DD}$ から結合される）はトランジスタ42を飽和状態にし、抵抗48と50間の接合点はトランジスタ40をその動作特性の線形部分にバイアスする。

#### 【0013】

端子70における補助オーディオ入力からの信号（外部信号）は、結合コンデンサ52と分離抵抗54を通ってトランジスタ40のベースに結合される。トランジスタ40は、コレクタ接地で、エミッタ/ソース・フォロワの構成なので、この増幅器の出力インピーダンスは低い値（ここでは、抵抗46の6800hm）であり、トランジスタ40のエミッタ/ソース電極の低出力インピーダンスと同様である。この構成の効果は二重である。第1に、低い出力インピーダンスにより、コンデンサ20が外部信号に及ぼす悪い分流（short）効果が消される。第2に、この低出力インピーダンスはピン51からグランドに結合され、内部信号は事実上ゼロに減衰されるので、内部信号と外部信号は同時にピン51に存在しない。すなわち、外部信号がスイッチ“オン”にされると、内部信号は“オフ”にされる。

#### 【0014】

図3および図4の回路を切り替えて制御するために、トランジスタ59のコレクタはトランジスタ40のベースに結合され、トランジスタ59のベースはバイアスなしに分離抵抗60を通って制御端子58に結合される。上述した信号結合モードにおいて、トランジスタ59（バイアスなし）は開路（open circuit）であって、この信号結合回路に影響を及ぼさない。しかしながら、外部信号を“オフ”にするために正（プラス）の制御信号を端子58に印加すると、トランジスタ59は飽和して、トランジスタ40のベースをほぼグランド電位に引き寄せる。トランジスタ40は逆バイアス（カットオフ）になり、トランジスタ42（既に飽和している）もカットオフになる。この信号非結合（non coupling）構成の効果は三重である。第1に、トランジスタ40がカットオフされると、もはや外部信号はピン51に結合されない。第2に、トランジスタ40がカットオフされると、そのエミッタが呈する低いソース・インピーダンスは変えられ開路になる。第3に、トランジスタ42（既に飽和している）はそのバイアスを失い、やはり切り替えられてカットオフ状態になるので、低いソース・インピーダンスの他方の抵抗46は開路になる。従って、この信号非結合モードでは、内部信号の減衰は除去され、コンデンサ20とピン51に負荷する2個のインピーダンスは除去され、ピン51への外部信号の結合は外され、内部信号とデエンファシス・フィルタ回路は通常の動作をする。

#### 【0015】

端子58における制御信号は、前面パネルまたはリモコン信号に応答して、または前面パネルの切替え入力ジャックから前面パネルのプラグの挿入/取外しに反応して、例えば、マイクロプロセッサ（図示せず）から発生される。

#### 【0016】

本文中で使用される、動作（作用）、例えば、I Cのピンにおける切替え（スイッチング）は、ピンから物理的に離れて実行される電子的/電気的動作を含み、その動作はピンに結合される。

#### 【0017】

本文中で、伝導型は、トランジスタの製法（例えば、合金、エピタキシャル）に関わりなく、NPNまたはPNP接合型バイポーラ・トランジスタ、NまたはPチャンネルのJFET（接合型電界効果トランジスタ）、CMOS（相補形MOS）、MOSFET（電界効果トランジスタ）デバイス、などを含む。

#### 【0018】

本文中で、JFET、CMOSおよびMOSFETデバイスのゲートまたは制御電極は

10

20

30

40

50

、接合型トランジスタのベース電極に相当し、ドレインとソースはそれぞれ、接合型トランジスタのコレクタとエミッタに相当するものと考えられている。最近の電界効果トランジスタは、個別素子またはICの一部であるとに関係なく、対称的であり、ドレインとソースは互いに交換可能である。

**【0019】**

本明細書中で使用される、内部(*intrinsic*)信号とは、その信号がICのピン51に到達する前に既にIC内に信号の流れを有する信号であり、外部(*extrinsic*)信号とはICの外部で発生した信号のことである。

**【0020】**

以下に他の実施例を例示する。

(1) 集積回路内部の第1の信号を供給する手段と、

集積回路のピンに発生される第1の動作機能を前記第1の信号に与える手段と、

集積回路によって前記第1の信号に第2の動作機能を与える手段と、

外部からの第2の信号を集積回路の前記ピンに結合させる手段と、から成り、前記第2の動作機能を与える手段が前記第2の信号に作用する、信号処理システム。

(2) 前記第1および前記第2の信号がアナログ・オーディオ信号である、(1)記載の信号処理システム。

(3) 前記第1の動作機能がデエンファシスであり、前記第2の動作機能が可変減衰器である、(1)記載の信号処理システム。

(4) 前記第2の信号が入力または出力に切り替えられ、入力に切り替えられると、前記第1の信号がオフに切り替えられる、(1)記載の信号処理システム。

(5) 前記ピンが双方向の信号路として働く、(1)記載の信号処理システム。

(6) 集積回路のピンにおいて、集積回路内部の第1の信号に第1の動作機能を与える手段と、

外部からの第2の信号を集積回路の前記ピンに結合させる手段と、から成り、集積回路内に在って第2の動作機能を与える手段が前記第2の信号に作用する、信号処理システム。

(7) 前記第1および前記第2の信号がアナログ・オーディオ信号である、(6)記載の信号処理システム。

(8) 前記第1の動作機能がデエンファシスであり、前記第2の動作機能が可変減衰器である、(6)記載の信号処理システム。

(9) 前記第2の信号が前記ピンにおいて入力または出力に切り替えられ、入力に切り替えられると、前記ピンにおいて前記第1の信号が動作不能にされる、(6)記載の信号処理システム。

(10) 前記ピンが双方向の信号路として働く、(6)記載の信号処理システム。

(11) 集積回路のピンにおいて、集積回路内部の第1の信号に動作機能を与える手段と、

外部からの第2の信号を集積回路の前記ピンに結合させる手段と、から成り、前記第2の信号が前記ピンに結合されると、前記ピンに存在する前記第1の信号がオフに切り替えられる、信号処理システム。

(12) 前記第1および前記第2の信号がアナログ・オーディオ信号である、(11)記載の信号処理システム。

(13) 前記第1の動作機能がデエンファシスである、(11)記載の信号処理システム。

(14) 前記ピンが双方向の信号路として働く、(11)記載の信号処理システム。

(15) 集積回路内部の第1の信号を供給する手段と、

集積回路のピンにおいて前記第1の信号に第1の動作機能を与える手段と、

集積回路によって前記第1の信号に第2の動作機能を与える手段と、

外部からの第2の信号を集積回路の前記ピンに結合させる手段と、から成り、前記第2の動作機能を与える手段が前記第2の信号に作用し、

前記第2の信号は入力または出力に切り替えられ、入力に切り替えられると、前記ピンに

10

20

30

40

50

おいて前記第1の信号はオフに切り替えられる、信号処理システム。

(16) 前記ピンが双方向の信号路として働く、(15)記載の信号処理システム。

(17) 集積回路内部の第1の信号を供給する手段と、

集積回路のピンにおいて前記第1の信号に第1の動作機能を与える手段と、

集積回路によって前記第1の信号に第2の動作機能を与える手段と、

外部からの第2の信号を集積回路の前記ピンに結合させる手段と、から成り、第2の動作機能を与える前記手段が前記第2の信号に作用し、

前記ピンが双方向の信号路として働き、

前記第2の信号は入力または出力に切り替えられ、入力に切り替えられると前記第1の信号が前記ピンにおいてオフに切り替えられる、信号処理システム。

10

(18) 信号を切替え可能に結合させる回路であって、

各々がそれぞれベース／ゲート電極とエミッタ／ソース電極とコレクタ／ドレイン電極を有する第1および第2のトランジスタを具え、該2個のトランジタは同じ伝導型であり且つ電源と基準点との間に直列に結合されており、

信号結合モードにおいて、出力信号は前記第1のエミッタ／ソース電極から結合され、前記第2のコレクタ／ドレイン電極は抵抗を通して前記第1のエミッタ／ソース電極に結合され、

前記第1のベース／ゲート電極はバイアス手段を有し且つ入力信号を受信し、前記バイアス手段は前記第1のトランジスタを線形の信号伝送状態にし、前記出力信号は前記第1のエミッタ／ソース電極によって結合され、前記バイアス手段はまた前記第2のベース／ゲート電極をバイアスし、その結果、前記第2のトランジスタは飽和状態になり、

20

前記バイアス手段は前記第1のトランジスタが信号非結合状態になるように、前記第1のトランジスタをカットオフ状態にすることによって、この回路は信号結合モードから信号非結合モードに切り替えられ、前記バイアス手段は前記第2のコレクタ／ドレイン電極の作用により、また前記第2のトランジスタをカットオフ状態にするので、前記第1のエミッタ／ソース電極は切り替えられて前記基準点に対して高いインピーダンスになり、このようにして、前記第1のエミッタ／ソース電極によりインピーダンス負荷を除去する、前記信号を切替え可能に結合させる回路。

#### 【図面の簡単な説明】

【図1】関係する集積回路のピンの略図と共に、前記ピンに関連する電子的機能のプロック図を示す。

30

【図2】図1の集積回路の関係する部分の概略図を示す。

【図3】本発明の態様による信号結合回路の1つの実施例の概略図を示す。

【図4】本発明の態様による信号結合回路の別の実施例の概略図を示す。

#### 【符号の説明】

14 増幅器

16 FM検波器／復調器

18 コンデンサ

20 デエンファシス・コンデンサ

22 減衰器

40

30 トランジスタ

32 トランジスタ

36 トランジスタ

40 トランジスタ

42 トランジスタ

44 コンデンサ

46 抵抗

48 抵抗

50 抵抗

52 結合コンデンサ

50

- 5 4 分離抵抗

5 6 トランジスタ

5 8 制御端子

6 0 分離抵抗

7 0 補助オーディオ入力(外部信号)端子

【図 1】

【図 2】

【図3】

【図4】

---

フロントページの続き

審査官 池淵 立

(56)参考文献 特開平06-112733(JP,A)

特開平04-006854(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04