(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW I494928 B

(45)公告日：中華民國 104 (2015) 年 08 月 01 日

(21)申請案號：101115558

(22)申請日：中華民國 101 (2012) 年 05 月 02 日

(51)Int. Cl. : G11C16/06 (2006.01)

H01L27/115 (2006.01)

(30)優先權：2011/05/02 美國

13/099,298

(71)申請人：旺宏電子股份有限公司 (中華民國) MACRONIX INTERNATIONAL CO., LTD.

(TW)

新竹市新竹科學工業園區力行路 16 號

(72)發明人：呂函庭 LUE, HANG TING (TW) ; 洪俊雄 HUNG, CHUN HSIUNG (TW) ; 郭明昌

KUO, MING CHANG (TW)

(74)代理人：祁明輝；林素華

(56)參考文獻：

|    |                |    |                |

|----|----------------|----|----------------|

| TW | 201030943A     | US | 2005/0224849A1 |

| US | 2006/0103007A1 | US | 2010/0025811A1 |

| US | 2010/0064096A1 | US | 2010/0230807A1 |

| US | 2011/0299317A1 |    |                |

審查人員：謝志偉

申請專利範圍項數：34 項 圖式數：59 共 148 頁

(54)名稱

具有二極體搭接之熱輔助快閃記憶體

THERMALLY ASSISTED FLASH MEMORY WITH DIODE STRAPPING

(57)摘要

一種記憶體包括一陣列之記憶體單元，其包括數行與數列。記憶體包括電路，其耦接至字線，施加一第一偏壓至於陣列中之一或多條字線上之一第一組隔開的位置，同時施加一不同於第一偏壓之第二偏壓至字線上之一第二組隔開的位置，在第一組隔開的位置中之位置係穿插在第二組隔開的位置中之位置之間，藉以使電流被引發在第一與第二組之位置之間，其導致字線之加熱。

A memory includes an array of memory cells including rows and columns. The memory includes circuitry coupled to the word lines applying a first bias voltage to a first set of spaced-apart locations on a word line or word lines in the array, while applying a second bias voltage different than the first bias voltage, to a second set of spaced-apart locations on the word line or word lines, locations in the first set of spaced-apart locations being interleaved among locations in the second set of spaced-apart locations, whereby current flow is induced between locations in the first and second sets of locations that cause heating of the word line or word lines.

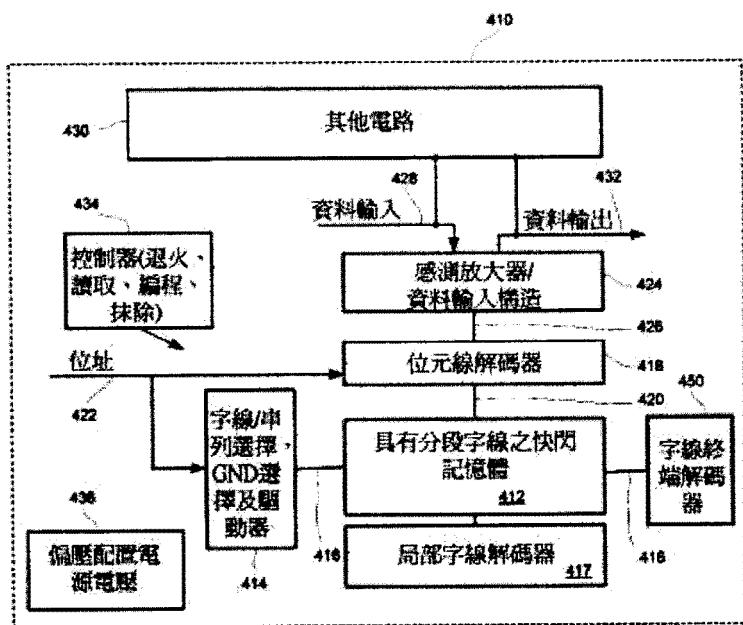

第 4 圖

- 410 . . . 積體電路

- 412 . . . 記憶體陣列

- 414 . . . 解碼器

- 416 . . . 字線

- 417 . . . 局部字線解碼器

- 418 . . . 位元線解碼器

- 420 . . . 位元線

- 422 . . . 匯流排

- 424 . . . 感測放大器與資料輸入構造

- 426 . . . 資料匯流排

- 428 . . . 資料輸入線

- 430 . . . 電路

- 432 . . . 資料輸出線

- 434 . . . 控制器

- 436 . . . 偏壓配置電源電壓與電流源

- 450 . . . 字線終端解碼器

## 六、發明說明：

### 【發明所屬之技術領域】

本發明是有關於快閃記憶體技術。

### 【先前技術】

快閃記憶體係為一種類型之非揮發性積體電路記憶體技術。典型的快閃記憶體單元由一場效電晶體 FET 構造及一阻擋介電層所構成，FET 構造具有由一通道隔開之源極及汲極，以及與通道隔開一電荷儲存構造之閘極，電荷儲存構造包括一隧道介電層、電荷儲存層(浮動閘或介電)及一阻擋介電層。依據早期習知之電荷補捉記憶體設計(被稱為 SONOS 裝置)，源極、汲極及通道係形成於一矽基板(S)中，隧道介電層係由氧化矽(O)所組成，電荷儲存層係由氮化矽(N)所組成，阻擋介電層係由氧化矽(O)所組成，而閘極包括多晶矽(S)。更多先進的快閃記憶體技術已被發展，使用帶隙工程穿隧介電材料於介電電荷補捉單元中。一種帶隙工程單元技術係被稱為 BE-SONOS，如 Hang-Ting Lue 等人說明於"Scaling Evaluation of BE-SONOS NAND Flash Beyond 20 nm"，2008 Symposium on VLSI technology, Digest of Papers, June 2008, and in H. T. Lue *et al.*, IEDM Tech. Dig., 2005, pp. 547-550。

理想上是可以提供改善快閃記憶體之操作速度及耐久性之技術。

### 【發明內容】

本發明說明一種記憶體裝置，其包括用於對裝置上之快閃記憶體單元進行熱退火之資源。可應用一種用於操作

快閃記憶體之方法，其包括執行讀取、編程及抹除操作；及不是穿插在讀取、編程及抹除操作之間，就是在讀取、編程及抹除操作期間，對陣列中之記憶體單元之電荷補捉構造進行熱退火。討論於下之實驗結果顯示出，藉由修理工在編程及抹除循環期間所累積之損壞，適當的退火操作可改善耐久性。舉例而言，藉由周期性地對陣列中之記憶體單元進行退火，可大幅地改善裝置之有效耐久性，包括達成一百萬循環及更多之耐久性循環性能。又，藉由在操作期間(例如在抹除操作期間)施加退火，可改善被影響的操作之性能。在譬如一抹除操作期間，熱退火可輔助電子釋放，並藉以改善抹除速度。

積體電路記憶體可利用字線驅動器及字線終端電路來實施，其因應於解碼器電路及可選的其他控制電路以驅動對應的字線上電流。此電流可導致選擇的字線之電阻式加熱，其被傳送至介電電荷補捉構造以供退火操作用。此種及其他技術可被應用以允許退火操作之彈性運送。

又，可使用一電路來實施一記憶體，此電路藉由施加一第一偏壓至陣列中之字線上之一第一組隔開的位置，同時施加一不同於第一偏壓之第二偏壓至字線上之一第二組隔開的位置來操作，第一組隔開的位置係穿插在第二組隔開的位置之位置之間，藉以在導致字線之加熱之第一與第二組之位置中之位置之間引發電流。

說明於此之技術係適合與 BE-SONOS 記憶體技術及其他快閃記憶體技術一起使用。

為了對本發明之上述及其他方面有更佳的瞭解，下文

特舉較佳實施例，並配合所附圖式，作詳細說明如下：

### 【實施方式】

以下將參考圖 1-58 而提供本技術之實施例之詳細說明。

圖 1A 為一記憶體單元之簡化立體圖，記憶體單元具有在一個半導體本體 13 中之一源極 11 與一汲極 12，而在源極與汲極之間有一通道區。字線 10 在本體 13 之通道區之上方提供一閘極。一多層介電堆疊 14 為介設於閘極與本體 13 之通道區之間，並作為一介電電荷補捉構造。在圖 1A 所顯示之例子中，閘極電流(或字線電流)係顯示為用以加熱電荷補捉構造之電源。第 1B 圖具有與圖 1A 之構造相同的參考數字，並顯示通道電流(或位元線電流)係為用以加熱電荷補捉構造之電源之一例子。第 1C 圖具有與圖 1A 與 1B 之構造相同的參考數字，並顯示閘極電流(或字線電流)以及通道電流(或位元線電流)之組合為用以加熱電荷補捉構造之電源之一例子。

關於多層介電堆疊 14 之實行之一項技術係已知為帶隙工程 SONOS (BE-SONOS) 電荷補捉技術。參見譬如 Lue 之美國專利第 7,315,474 號，其猶如完全提出於此地併入作參考。

一種 BE-SONOS 多層介電堆疊之一例子包括在通道上之一多層穿隧層。多層穿隧層係藉由使用下述三層而實現：一層氧化矽或氮氧化矽，其在通道之中央區域中小於 2 nm 厚；一第二層之氮化矽，其在中央區域中小於 3 nm

厚；以及包括氧化矽或氮氧化矽之一第三層，其在中央區域中小於 4 nm 厚。電荷捕捉層係形成於穿隧層上，穿隧層包括在中央區域中具有大於 5 nm 之厚度之氮化矽。阻擋層係形成於電荷捕捉層與包括一絕緣材料之閘極之間，並具有在中央區域中大於 5 nm 之一有效氧化層厚度。在其他實施例中，介電電荷捕捉構造可以與鄰近閘極之穿隧層和鄰近通道之阻擋層一起被配置。

替代記憶體單元可使用不同的電荷捕捉構造，包括譬如更傳統的氮化層構造；如下所說明之電荷捕捉構造：Shin 等人之"一種具有 Al<sub>2</sub>O<sub>3</sub> 或上氧化層之高可靠度的 SONOS 型 NAND 快閃記憶體單元(A Highly Reliable SONOS-type NAND Flash Memory cell with Al<sub>2</sub>O<sub>3</sub> or Top Oxide)"，IEDM，2003 年 (MANOS)；Shin 等人之"一種使用 63 nm 製程技術以供一種數十億位元快閃 EEPROM 用之嶄新的 NAND 型 MONOS 記憶體(A Novel NAND-type MONOS Memory using 63 nm Process Technology for a Multi-Gigabit Flash EEPROMs )"，IEEE 2005 年；以及共同擁有且共同審理中的美國專利申請暗號 11/845,276，其申請日為 2007 年 8 月 27 日，且猶如完全提出於此地併入作參考。又，參考第 38-45 圖，可應用於此所說明之技術之其他快閃記憶體技術係說明於下。

BE-SONOS 技術，以及其他介電電荷捕捉技術與浮動閘電荷捕捉技術可具有相當的溫度敏感度。溫度敏感度可包括從損壞恢復至藉由一熱退火在編程與抹除循環期間產生之構造之能力。因此，藉由施加一熱退火，可恢復或

改善介電電荷捕捉構造之電荷儲存特徵。又，溫度敏感度可包括改善的性能。舉例而言，在某些介電電荷捕捉記憶體構造的情況下，如果在一負閘極偏壓之下，在福勒諾爾德哈姆(FN)穿隧期間可施加熱，則熱輔助電子釋放(de-trapping)可被提高，並變成一項與電洞穿隧結合以改善抹除速度之顯著因素。

一項施加熱至一記憶體單元之技術包括藉由使用一字線中之電流而產生之電阻式加熱，如圖 1A 所示。字線一般為無終端的線(unterminated lines)，或利用很高的阻抗被終結，俾能使一字線驅動器在沒有產生相當的電流的情況下將一字線充電至一目標電壓。為了在一字線中引發電流流動，接收字線電壓之字線必須以允許電流流動的方式被終結。又，在一負閘極電壓 FN 穿隧操作中，電場係被引發而橫越過介電電荷捕捉層。因此，可藉由引發電流流動同時亦引發電場以支援一抹除操作，來執行一結合的抹除/退火操作。如果需要的話，電流流動亦可在讀取與編程操作期間被引發。電流流動亦可在記憶體處於閒置時，在穿插讀取、編程及抹除之任務功能的操作中被引發。因此，可配置一電路以達成穿插讀取操作、編程操作及抹除操作，或在讀取操作、編程操作及抹除操作期間之退火操作。

藉由適當地引發通過一字線之電流，關於一特定單元之閘極之局部溫度可被提高大於  $400^{\circ}\text{C}$ 。因為閘極係與介電電荷捕捉構造接觸，所以熱被傳輸並完成退火。一種自我修復快閃記憶體裝置可突破快閃記憶體耐久性之瓶

頸。記憶體裝置可使用一字線(閘極)以作為一內部焦耳加熱器，用以在很短的時間內產生局部高溫，從而提供非常快的脈衝退火及 P/E (編程/抹除)循環引起的損壞之修正。局部高溫度係比藉由外部加熱可能產生的溫度高得多。

一電流可沿著字線(閘極)而被傳導以產生焦耳熱。鄰近閘極處可輕易地加熱快閃記憶體裝置之隧道氧化層，藉以退火出由 P/E 循環所導致的損壞。由於高活化能 ( $E_a > 1.1 \text{ eV}$ )，且因而是大的溫度加速因子，字線加熱器可在很短的時間內有效地產生熱退火。

在某些實施例中，可能需要一種通過一字線之相當高的電流(例如大於 2 毫安培(mA))以產生足夠的焦耳熱。然而，一快閃記憶體裝置中之字線可具有大於 1 公厘之長度。因為長度，所以相對應的字線電阻非常高。舉例而言，一多晶矽字線( $R_s$ )之薄片電阻可以是 30 歐姆/平方，字線( $W$ )之通道寬度可以是 30 nm(奈米)，而字線長度( $L$ )可以是 1 mm(公厘)。於此例中，正方形係為( $30 \text{ nm} \times 30 \text{ nm}$ )，而字線之電阻( $R$ )係被計算成為 1 M-ohm(百萬歐姆)：

$$\begin{aligned} R &= L \times W \times R_s = 1 \text{ mm} \times 30 \text{ nm} \times 30 \text{ ohm} / (30 \text{ nm} \times 30 \text{ nm}) \\ &= 1 \times 10^6 \text{ ohm(歐姆)} \end{aligned}$$

具有 1 M-ohm 電阻之一字線將在 500 伏特之字線壓降之內產生大約 2 mA 之電流。這種高電壓並不實際。

理想上是儘可能可以減少字線電阻以減少所需要的電壓。一種減少字線電阻之方法係用以縮小字線長度。另一種方法係減少字線之薄片電阻。如果橫越過一字線之壓降( $V$ )被減少至 10V，且橫越過字線所產生之電流( $I$ )需要

2mA，則字線之電阻( $R$ )係被計算成為 5K-Ohm(千歐姆)：

$R = V/I = 10V / 2mA = 5 K\text{-ohm}$ 。

如果一字線( $R_s$ )之薄片電阻係譬如藉由使用一金屬字線而減少至 1 歐姆/平方，且通道寬度( $W$ )仍然是 30 nm，則字線長度( $L$ )被計算為：

$$L = R / (W \times R_s) = 5 K\text{-ohm} / (30nm \times 1 \text{ ohm} / (30nm \times 30nm)) = 150 \times 10^{-6} \text{ 公尺}。$$

因此，於此例子中，具有  $150 \mu m$ (微米)以下之長度之金屬字線可被設計成提供大於 2mA 之電流給於大約 10 V 之電壓下之足夠焦耳熱使用。對於一大陣列而言，字線可藉由實體上切割字線並藉由使用開關以施加電壓供退火用，或電性地在不需要實體上切割字線的情況下，並藉由使用二極體搭接或其他電路以施加退火偏壓而被分段，使得操作電壓與電流範圍落在積體電路環境之公差之內。對一實體上分段的實施例而言，局部字線係耦接至全域字線。

在本發明之一個實施例中，在 BE-SONOS(帶隙工程矽氧化氮氧化矽)電荷捕捉 NAND 快閃記憶體單元中之隧道氧化層 ONO(氧化層-氮化物-氧化層)，係利用大於 400 °C 之溫度(藉由一內部焦耳加熱器而在幾毫秒之內產生)而快速被退火。實施例證明大於 10 百萬(10M)編程/抹除循環之耐久性以及大於 10M 循環之資料保存。

第 2 圖係為一種簡化的單一裝置佈局圖。此裝置包括藉由一個半導體本體中之佈植而實施之一源極 22 與一汲極 23。此裝置包括一閘極 29。閘極 29 可具有局部狹小區

域，以便局部集中電流，其中較寬區域位於遠離單元之記憶體元件被隔開的相對的一端 20 與對向端 21。記憶體單元係形成於在閘極 29 與源極/汲極佈植之間的交點 24。

如所顯示的，可藉由使用耦接至閘極之一端 20 之一字線驅動器 25 來引發退火。一字線終端電路(其可能類似於一字線驅動器)係耦接至閘極之對向端 21。字線終端電路包括一個可以因應於位址解碼或其他控制電路之開關 26，用以選擇性地將字線耦接至一終端電路 27(其可包括偏壓電路)，用以適當的允許電流流動或避免電流流動。終端電路藉由施加相對於由字線驅動器所施加之電壓之電壓差異，來允許閘極上之電流流動橫越過字線。在一例子中，字線驅動器與終端電路可被配置以在字線之一側施加大約 1 伏特之電壓，且在另一側施加大約 0 伏特之電壓。在沒有建立一顯著電場的情況下，這導致一電流，並引發於記憶體單元之熱。在另一例子中，終端電路可被配置以在一側施加大約 20 伏特且在另一側施加大約 19 伏特，藉以導致一電流以引發熱，同時亦於記憶體單元引發電場以支援編程，包括福勒諾爾德哈姆編程。在另一例子中，終端電路可被配置以在一側施加負電壓(例如大約 -16 伏特)且在另一側施加大約 -15 伏特，藉以導致一電流以引發熱，同時亦於記憶體單元引發電場以支援抹除，包括負場福勒諾爾德哈姆抹除。

參考第 1 與 2 圖說明之用於熱退火記憶體單元之手段包括多條字線或其他閘極構造，閘極構造具有驅動器及終端電路，其選擇性地被控制以靠近記憶體單元之介電電荷

捕捉構造引發電阻式加熱。於其他實施例中，用於熱退火記憶體單元之手段可使用位元線中之電流來產生被施加至記憶體單元之介電電荷捕捉構造的熱。又，記憶體單元可能在具有在介電電荷捕捉層上方，或在介電電荷捕捉層下方之一額外一組之電阻式線之陣列中被實施。舉例而言，額外一組之熱退火線可能鄰接於一金屬層中之標準字線或在其上方而被實施，且用於加熱單元。亦，記憶體單元可能在一基板上方被實施，此基板包括在介電電荷捕捉構造下方之一組熱退火線。舉例而言，在一絕緣體上矽基板的情況下，一電阻可被埋入在記憶體單元下方，藉由使用譬如在絕緣體下方或埋入在絕緣體內之一摻雜多晶矽線而被實施。字線加熱因為字線接近電荷捕捉構造可能是最有效的。然而，可使用其他構造以提供用以熱退火之手段，如上述所略述的。

快閃記憶體裝置一般係藉由使用 NAND 或 NOR 架構(包括譬如虛接地架構以及 AND 架構，雖然其他是已知的)而實施。NAND 架構在被運用至資料儲存應用時，其高密度及高速是受歡迎的。NOR 架構係更佳適合於其他應用，例如碼儲存，於此，隨機位元組存取是重要的。於此所說明之熱輔助記憶體單元可被部署在 NAND、NOR、虛接地與 AND 架構中，以及在其他配置中。

第 3 圖係為顯示一種 NAND 架構之佈局之電路圖，NAND 架構包括分別藉由串列(string)選擇電晶體(例如 36)與接地選擇電晶體(例如 37)而耦接至各個位元線 BL-1 至 BL-2，且耦接至一共通源極 CS 線 35 之 NAND 串列 31、

32。為了說明的目的，為了讀取 NAND 串列 31 中之一條對應的字線 WL(i)上的一目標記憶體單元 30，一讀取偏壓位準係被施加至選擇的字線 WL(i)。未被選取的字線係利用足以導通最高門檻值狀態中之記憶體單元之一通過電壓而被驅動。一讀取偏壓係被施加在選擇的位元線上。在未被選取的位元線上，位元線電壓被設定至接地位準或接近 CS 線之位準之位準。

為了使用字線以施加熱以供一熱退火使用，此陣列係具體形成有複數個解碼的字線驅動器 38 連同在字線之相反側之複數個解碼的終端電路 39。在驅動器與解碼的終端電路 39 之間的字線之長度可藉由適當地分割此陣列而如期望的被具體形成。舉例而言，字線驅動器/終端開關對可在適合一特定實施例時為 100 條位元線之分段、1000 條位元線之分段，或其他長度之分段而實現。藉由使用解碼的終端電路 39(其選擇性地將字線耦接至一偏壓電路或使字線與一偏壓電路解耦)允許在裝置之操作期間以低電流模式，且以較高的電流模式使用字線以供熱退火使用。又，在裝置之某些操作模式(例如讀取操作、編程操作以及抹除操作)中，字線可能以一高電流模式被操作，而字線選擇性地耦接至終端電路，用於在操作期間執行熱退火。

第 4 圖係為如於此所說明的採用熱退火以供快閃記憶體使用之一積體電路之簡化方塊圖。積體電路 410 包括一個藉由使用一積體電路基板上之快閃記憶體單元而實現之記憶體陣列 412。一接地選擇與串列選擇解碼器 414(包括適當的驅動器)係耦接至沿著記憶體陣列 412 中

之列所排列之串列選擇線與接地選擇線，並與其電性連通。又，解碼器 414 包括數個全域字線驅動器，其係以與全域字線終端電路與解碼器 450 協調地被操作。一位元線(行)解碼器與驅動器 418 係耦接至沿著記憶體陣列 412 中之行被排列之複數個位元線 420 並與其電性連通，用於從記憶體陣列 412 中之記憶體單元讀取資料，並將資料寫入至記憶體單元。位址係在匯流排 422 上被供應至字線解碼器與串列選擇解碼器 414，並供應至位元線解碼器 418。可選擇地，一局部字線解碼器 417 可被包括且用來將局部字線連接至全域字線對，其係耦接至全域字線驅動器與全域字線終端電路。

在使用字線上之電流流動以引發熱以供介電電荷補捉構造之熱退火使用之實施例中，一字線終端解碼器 450 係耦接至此陣列之字線 416。字線終端解碼器 450 可因應於位址及控制信號，其表示或係在一操作模式期間為此裝置產生，用以選擇性地將字線連接至終端電路，或用以允許終端電路被耦接至選擇的字線，如上所述。

方塊 424 中之包括供讀取、編程及抹除模式用之電流源之感測放大器與資料輸入構造，係經由資料匯流排 426 而耦接至位元線解碼器 418。資料係經由資料輸入線 428 而從積體電路 410 上之輸入/輸出埠，或從積體電路 410 內部或外部之其他資料源被提供至方塊 424 中之資料輸入構造。資料係經由資料輸出線 432 而從方塊 424 中之感測放大器被提供至積體電路 410 上之輸入/輸出埠，或提供至積體電路 410 內部或外部之其他資料目標。

使用一偏壓配置狀態機器而於此例子中被實施之一控制器 434 控制偏壓配置電源電壓與電流源 436(例如供字線及位元線用之讀取、編程、抹除、抹除確認、編程確認電壓或電流)之施加，並藉由使用一存取控制過程過程來控制字線/源極線操作。控制器 434 包括用於致能熱退火(包括用以控制用以將偏壓條件運用至用於執行熱退火操作之局部字線之全域字線對之使用)之邏輯。

控制器 434 可藉由使用如習知技藝已知的特殊用途邏輯電路而被實施。在替代實施例中，控制器 434 包括一通用處理器，其可能在相同的積體電路上被實施，並執行一電腦編程以控制裝置之操作。在又其他實施例中，特殊用途邏輯電路與一通用處理器之組合可能被利用來實行控制器 434。

在所顯示的實施例中，其他電路 430 係被包括在積體電路 410 上，例如一通用處理器或特殊目的應用電路，或提供由記憶體單元陣列所支援之系統單晶片功能性之模組之組合。

又，在某些實施例中，控制器包括編程/抹除循環計數器，以及用以設置待應用在熱退火處理過程之配置中的參數之暫存器。控制器可參考第 9-11 圖及第 28-30 圖執行於此所說明之程序，連同其他處理過程以及讀取與寫入之任務功能操作。

供實行一 NAND 陣列用之一項共通技術包括在半導體基板的條帶之間的淺渠溝隔離 STI 構造之使用。一連串的記憶體單元係在每個條中被實施。記憶體單元包括具有

N 型摻雜(供 p 通道裝置用)或 P 型摻雜(供 n-通道裝置用)之其中一個之通道區，以及沿著具有相反導電型式之條帶而在通道區之間的源極/汲極區。電荷捕捉構造係形成在通道區上方，而字線與位元線係被圖案化以建立對於 NAND 單元之存取。

第 5 圖顯示一種 NAND 陣列佈局，包括在行之間之淺渠溝隔離，適合與說明於此之用於熱退火之手段一起使用。在佈局中，複數個充填絕緣體之渠溝 51-1 至 51-5 係形成於半導體基板中。半導體條帶 52-1 至 52-4 位於數對之充填絕緣體之渠溝 51-1 至 51-5(例如淺渠溝隔離 STI 構造)之間。電荷捕捉構造(未顯示)伏在半導體條帶上面。複數條字線 53-1 至 53-4 係形成於電荷捕捉構造上方，及相對於半導體條帶 52-1 至 52-4 正交地延伸。半導體條帶包括具有一第一導電性型式之複數個源極/汲極區(標示為 S/D)及具有一第二導電性型式之複數個通道區(位於字線下方)。

第 6 圖顯示沿著字線 53-2 之第 5 圖之陣列之剖面。ONONO 介電電荷捕捉構造(BE-SONOS 裝置之特徵)位在字線 53-2 與半導體本體中之 P 井之間。充填絕緣體之渠溝 51-1 至 51-5 分離垂直於紙張延伸之 NAND 串列。字線可包括多層構造之多晶矽與矽化物(如顯示的)或其他材料組合。這些材料可被配置以在電流期間提供電阻式加熱，且供電阻式加熱傳輸至介電電荷捕捉構造以供熱退火使用。

第 7 圖以剖面顯示複數個以串聯排列以形成一 NAND 串列之介電電荷捕捉快閃記憶體單元。第 7 圖之剖面係對

應至沿著條帶 52-1 中之一 NAND 串列之沿著第 5 圖之線 7-7 之一區段。然而，第 7 圖顯示一連串之六個記憶體單元與接地選擇開關和串列選擇開關，從而比出現在第 5 圖之佈局中更多的構造。

參見第 7 圖，記憶體單元係形成於一個半導體本體 70 中。對 n 通道記憶體單元而言，半導體本體 70 可以是在一個半導體晶片中之較深的 n 井之內的一隔離 p 井。或者，半導體本體 70 可被一絕緣層或其他隔離。某些實施例可採用 p 通道記憶體單元，於其中關於半導體本體之摻雜將是 N 型。

複數個記憶體單元係以朝垂直於字線之一位元線方向延伸的一串列被配置。字線 82-87 延伸橫越過一些平行 NAND 串列。端子 72-78 係藉由半導體本體 70 中之 N 型區域(關於 n 通道裝置)而形成，並作為記憶體單元之源極/汲極區。藉由具有在一接地選擇線 GSL 81 中之一閘極之一 MOS 電晶體而形成之一第一開關，係連接於符合第一字線 82 之記憶體單元與藉由半導體本體 70 中之一 N 型區域而形成之一接點 71 之間。接點 71 係連接至共通源極 CS 線 80。藉由具有在一串列選擇線 SSL 88 中之一閘極之一 MOS 電晶體而形成之一第二開關，係連接於對應至最終字線 87 之記憶體單元與藉由半導體本體 70 中之一 N 型區域而形成之一接點 79 之間。接點 79 係連接至一位元線 BL 90。在所顯示的實施例中之第一與第二開關係為 MOS 電晶體，其具有藉由譬如二氧化矽而形成之閘極介電層 97 與 98。

於此圖例中，為簡化之便，串列中有六個記憶體單元。在典型的實施例中，一 NAND 串列可包括串聯排列之 16、32 或更多記憶體單元。對應於字線 82-87 之記憶體單元具有在字線與半導體本體 70 中之通道區之間的介電電荷補捉構造 99。又，已發展出無接面之 NAND 快閃構造之實施例，於此從此構造可能省略源極/汲極端子 73-77，以及可選擇的端子 72 與 78。

在所顯示的實施例中之電荷補捉構造包括如上所述之一 ONONO 多層堆疊。如上所述，字線係用於在電荷補捉構造(例如 99)中以引發熱，並使熱退火從循環損壞恢復。退火亦可在- FN 抹除期間被施加以改善抹除速度。

關於一負閘極電壓 FN(- FN)操作，偏壓條件係顯示在第 7 圖中之 NAND 串列上。為了譬如藉由使用 -FN 穿隧引發一區塊抹除，字線係偏壓有一負抹除電壓 -VE，且位元線與共通源極線係偏壓有一正抹除電壓 + VE 或接地，而串列選擇開關係偏壓有一電壓，用於將 +VE 電壓耦接至半導體本體 70。這設置一個引發從通道至介電電荷補捉構造中之電荷補捉層之電洞穿隧之電場，用以抹除方塊中之記憶體單元。為了改善抹除性能，字線可被終結，俾能使電流在區塊抹除期間流動，如以閘極構造上之箭號表示的。在抹除操作期間，電流引發熱，熱被傳輸至介電電荷補捉構造。

包括如上所述之"無接面"構造之替代實施例包括在一第一 N 型源極/汲極端子與一第二 N 型源極/汲極端子之間的複數條字線(例如 8 條或 16 條)，以及 n 通道裝置之一

連續的 P 型通道構造，且對 p 通道裝置而言，反之亦然。因此，如於此所說明之 NAND 陣列之實施例可包括在摻入一導電性型式(與通道之導電性型式相反)之源極/汲極端子之間的一個以上的閘極。於此替代中，個別單元係以一種使通道構造反轉，藉以為個別閘極建立反轉源極/汲極區的方式，藉由使鄰近字線偏壓而被存取。參見 Hsu 等人之共同擁有的美國專利第 7,382,654 號，其係併入作參考，猶如完全提出於此。

NAND 串列可被實施在各種配置中，包括 finFET 技術、淺渠溝隔離技術、垂直 NAND 技術以及其他技術。關於一例子之垂直 NAND 構造，請參見 Kim 等人之歐洲專利申請第 EP 2 048 709 號，名稱為「非揮發性記憶體裝置、其操作方法及其製造方法(Non-volatile memory device, method of operating same and method of fabricating the same)」。

第 8 圖係為包括實施在絕緣基板上之薄膜電晶體記憶體單元之一記憶體構造之簡化透視圖。這係為一種代表構造，於其中在裝置設計上將熱隔離納入考量，用以提供更多有效的熱產生與較低的功率。在構造上，實施一種"絕緣層上有矽 SOI"設計方法。一絕緣體 102 係形成於積體電路的一基板上，藉以提供熱與電性絕緣兩者。一薄膜半導體本體 101 係形成在絕緣體 102 上面。源極/汲極區 110 以及通道區 109、111 係在半導體本體 101 中被實施。一介電電荷捕捉構造 104 係形成在薄膜半導體本體 101 上面。字線係藉由使用一多層構造(包括各個層之多晶矽

105、106 及複數層之矽化物 107、108)而實施。多晶矽/矽化物層之厚度可被減少以增加字線之電阻，且藉以增加熱產生。又，在一 SOI 型構造中被實施之薄膜半導體本體 101 可藉由記憶體單元減少熱吸收，藉以允許於較低功率下產生較高的溫度。又，可使用額外熱絕緣技術。舉例而言，可在區域 103 之字線之間實施空氣間隔(air spacer)，及其他熱絕緣構造。

第 9-11 圖顯示替代操作方法，於其中熱退火循環係被部署在一快閃記憶體裝置中。這些方法可譬如使用參考第 4 圖所說明之控制器 434 而被執行。

第 9 圖顯示一代表處理過程，於其中熱退火循環係穿插在關於記憶體裝置之任務功能操作(讀取、編程、抹除)之間。在裝置之操作期間，執行編程/抹除循環操作，如以方塊 200 表示。一種供第 9 圖之方法用之控制器計算編程/抹除循環(例如藉由計算編程操作，藉由計算抹除操作，或藉由計算編程與抹除操作對)(方塊 201)，並監視此計數(方塊 202)。如果計數尚未達到一門檻值，則演算法迴路繼續計數循環。如果計數達到一門檻值，則控制器施加一熱退火循環(方塊 203)。編程/抹除循環計數與熱退火循環可在適合一特定實施例時根據多組的單元，例如根據一逐列基礎、根據一逐行基礎、根據一逐方塊基礎或遍及一整個陣列而被施加。退火可在適合功率消耗需求與一既定實施例之其他需求時，同時被施加至單元之一列或行，或施加至較多組之單元。一編程抹除循環可被定義為寫入一記憶體單元以從編程狀態至抹除狀態且回到編程狀態之事

件之組合，且通常使用作為用以測量快閃記憶體之耐久性之單位。如上所述，為了在使用一積體電路記憶體期間計算編程抹除循環，可使用一晶片上的計數器以計算施加至個別記憶體單元之編程循環，至記憶體單元之區塊內的記憶體單元的編程循環，施加至個別記憶體單元之抹除循環，至記憶體單元之區塊內的記憶體單元之抹除循環，或用以計算寫入一記憶體單元以從編程狀態至抹除狀態且回到編程狀態之事件之組合。這些方法全部可提供持久的實際編程抹除循環之數目之一跡象，並在用以施加一熱退火循環時足夠決定之一精度。

第 10 圖顯示另一處理過程，於其中熱退火循環係穿插在任務功能操作之間。在第 10 圖之處理過程中，編程/抹除循環操作係在正常操作期間被執行，如以方塊 301 表示。控制器監測一區塊抹除功能之執行，並決定何時已完成一區塊抹除操作(方塊 302)。如果沒有區塊抹除操作被完成，則處理過程繼續監視且正常操作。如果成功地完成一次區塊抹除操作，則控制器施加一熱退火循環(方塊 303)。這種熱退火循環係以與區塊抹除協調的方式被執行，其乃因為其係開始因應於區塊抹除操作之偵測與完成。在區塊抹除與熱退火循環之間的其他邏輯連結，亦可導致區塊抹除與熱退火循環之協調性能。

第 11 圖顯示一代表處理過程，於其中熱退火係在關於記憶體裝置之一任務功能(於此例子之區塊抹除)期間被施加。在第 11 圖之處理過程中，關於記憶體裝置之正常編程/抹除循環正發生，如以方塊 400 表示。處理過程決定

一區塊抹除是否已被要求(方塊 401)。如果不是，處理過程繼續正常操作並監視。如果一區塊抹除操作被要求，則控制器在區塊抹除操作期間終結字線，俾能使熱產生電流被施加至被抹除之記憶體單元，或以其他方式被施加至熱退火(方塊 402)。如上所述，這不但改善抹除性能，而且允許介電電荷補捉構造從編程/抹除循環損壞恢復。當完成區塊抹除功能(方塊 403)時，處理過程回復至正常操作。

第 12 圖及 13 顯示沿著一實驗用裝置(包括 NAND 架構 BE-SONOS 記憶體單元，以 75 nm 之節點製造)之測量，其中引發熱退火之電流係藉由順向源極/汲極退火而產生，在源極/汲極端子與單元之半導體本體之間的接合係藉此而順向偏壓以引發電流。這模倣如上所述之其他加熱構造之作用情形。在第 12 圖中，顯示汲極電流對閘極電壓之曲線圖。蹤跡 1201 顯示在 10,000 次編程/抹除循環之後的一記憶體單元之性能，其顯示或許因循環損壞之結果出現的性能方面的一輕微退化。蹤跡 1202 與蹤跡 1203 分別顯示在一第一退火與一第二退火之後的性能。在退火步驟之後，大幅改善了此裝置之次臨界斜率(sub-threshold slope)，其表示界面態階損壞(Dit)係藉由使用熱退火而受到抑制。

第 13 圖顯示在退火之前的 10,000 次循環以及在退火之後的 10,000 次循環之門檻電壓對測試的記憶體單元之編程/抹除循環的循環次數。此圖顯示此裝置同樣執行在退火之前的 10,000 次循環與在退火之後的下一 10,000 次循環兩者。

第 14-16 圖分別顯示關於在測試的 NAND 架構 BE-SONOS 記憶體單元上之一第一組之 100,000 次編程/抹除循環，關於在一熱退火之後的一第二組之 100,000 次編程/抹除循環，以及關於在熱退火之後的一第十組之 100,000 次編程/抹除循環之門檻值分佈。在第 14 圖中，顯示無法輕易區別之七種曲線圖。這些曲線圖對應至於 10 次循環下之性能、於 100 次循環下之性能、於 1000 次循環下之性能、於 10,000 次循環下之性能、於 50,000 次循環下之性能，以及於 100,000 次循環下之性能。第 14 圖顯示當循環次數增加至大約 100 時，抹除狀態視窗之上部邊緣到達大約 2.3 V。編程狀態視窗維持相當的常數，其具有於大約 3.5 V 下之較低邊緣。

第 15 圖顯示關於在一熱退火之後的一第二組之 100,000 次循環，抹除狀態視窗之上部邊緣停留在大約 2.6 V 以下，而編程狀態視窗停留在大約 3.5 V 之上。第 16 圖顯示關於在熱退火之後的第十組之 100,000 次循環，抹除狀態視窗維持在大約 2.9 V 以下，而編程狀態視窗維持在大約 3.4 V 之上。

第 14-16 圖所顯示之結果顯示藉由每 100,000 次循環就使用熱退火處理，就可將裝置性能維持超過 1 百萬次循環。

第 17-19 圖顯示頁編程照射量(shot count)(亦即，用於在一編程、確認，再試循環演算法中成功地編程所需要的編程脈衝之數目)及超過 100,000 次編程/抹除循環之總抹除時間變化。此圖顯示關於頁編程照射量之最差狀況計算

之蹤跡、一平均數目之頁編程照射量及一總數抹除時間蹤跡。第 17 圖顯示關於第一組之 100,000 次循環之性能。第 18 圖顯示關於在熱退火之後的一第二組之 100,000 次循環之性能。第 19 圖顯示關於利用熱退火之一第十組之 100,000 次循環之性能。這些圖顯示在第十組之 100,000 次 P/E 循環之後伴隨著一熱退火，編程/抹除循環條件幾乎完全被恢復，並顯示超過一百萬次循環之耐久性。

第 20 圖顯示關於一 BE-SONOS 記憶體單元中，利用及不利用熱退火之抹除性能，BE-SONOS 記憶體單元具有一多層穿隧層、一電荷補捉層及一阻擋層，多層穿隧層包括 1.3 nm 的氧化矽、2 nm 的氮化矽及 3.5 nm 的氧化矽，電荷補捉層包括 7 奈米的氮化矽及一個包括 8.5 nm 的氧化矽的阻擋層。一個 -17 伏特之 -FN 抹除偏壓係被施加橫越過閘極及裝置之本體。關於在這些條件下之從約 5 V 至約 0 V 之一門檻值降低之在 25°C 之抹除時間係接近 1 秒。於 250°C 之提升之溫度，在這些條件下之抹除時間降至大約 11 ms。因此，第 20 圖顯示在一抹除操作期間施加熱退火可改善抹除性能。

第 21 圖係為退火時間之阿列尼厄圖表(秒對  $q/(kT)$ )，顯示關於在一 BE-SONOS 裝置中之熱輔助抹除操作之估計之退火時間。三個蹤跡係被顯示，其中最上蹤跡呈現 1.2 電子伏特之活化能，在中間之蹤跡呈現 1.5 電子伏特之活化能，而較低的蹤跡呈現 1.8 電子伏特之活化能。又，為了計算，基於實驗假設用於恢復所需要之退火時間於 250°C 下大約是兩個小時。基於顯示於曲線圖之計

算，在大約  $600^{\circ}\text{C}$  之溫度下，所需要之退火時間將只有一些毫秒(ms)，且係因此適合在目前快閃記憶體規格之抹除速度需求之內使用。使用說明於此之電阻式加熱可達成像  $600^{\circ}\text{C}$  那樣的溫度。

第 22 圖係為一積體電路上之一記憶體陣列之一區段之簡化視圖。記憶體包括一陣列之記憶體單元，其包括多行與多列。此陣列之記憶體單元可能被配置在一 NAND 構造中。此陣列中之記憶體單元可包括位於一絕緣基板上之半導體本體。

第 22 圖所顯示之區段包括排列成局部字線 2230a 至 2230f 之字線段。局部字線係與一種配置中之對應對之全域字線(以區段之反側的兩個結尾箭號表示)耦接，其可參考局部字線 2230a 被理解。一第一開關 2262L 係用於經由一接點 2281 而將一對中的一第一全域字線 2260L 連接至局部字線 2230a。一第二開關 2262R 係用於經由一接點 2283 將此對中之一第二全域字線 2260R 連接至局部字線 2230a。此種配置係以一種關於此陣列之記憶體單元之所顯示的方塊中的每條局部字線及其對應對之全域字線之圖案被重複。因此，第一(或左側)開關 2262L 與第二(或右側)開關 2262R 係耦接至局部字線 2230a 至 2230f 之對應的第一(左)與第二(右)端。記憶體亦包括沿著對應行之位元線 2210。位元線可包括近端位元線 2210，其係經由接點 2215 耦接至全域位元線(未顯示)。

將偏壓連接至局部字線之電路包括耦接至一對全域字線之開關 2262L、2262R。此對全域字線包括數條沿著

相對應的列耦接至局部字線 2230a 至 2230f 之第一開關 2262L 之第一全域字線 2260L，以及數條沿著相對應的列耦接至局部字線 2230a 至 2230f 之第二開關 2262R 之第二全域字線 2260R。

記憶體包括耦接至第 22 圖所顯示之陣列之一位址解碼器(未顯示)，其包括耦接至局部字線 2230a 至 2230f 之第一開關 2262L 與第二開關 2262R 之一局部字線解碼器，用以將選擇的局部字線耦接至相對應對之全域字線 2260L 與 2260R。此例子之局部字線解碼器係耦接至第一局部字線選擇線 2270L 與第二局部字線選擇線 2270R，其分別控制第一開關 2262L 與第二開關 2262R，以供第 22 圖所顯示之陣列中的單元之一方塊或一行之方塊使用。每個第一開關 2262L 可包括一 FET 電晶體，其具有一閘極、一輸入以及一輸出。第一局部字線選擇線 2270L 係耦接至第一開關 2262L 之閘極。第一開關 2262L 之輸入係耦接至第一全域字線 2260L。第一開關 2262L 之輸出係耦接至局部字線 2230a 至 2230f 之第一端。

同樣地，每個第二開關 2262R 可包括具有一閘極、一輸入以及一輸出之一 FET 電晶體，例如一種金屬-氧化物-半導體場效電晶體(MOSFET)。第二局部字線選擇線 2270R 係耦接至第二開關 2262R 之閘極。第二開關 2262R 之輸入係耦接至第二全域字線 2260R。第二開關 2262R 之輸出係耦接至局部字線 2230a 至 2230f 之第二端。

譬如結合第 3 與 4 圖，記憶體包括如上所述耦接至對應對之全域字線之複數個配對的字線驅動器與字線終端

電路。配對的字線驅動器與字線終端電路包括耦接至此相對應對中之一第一全域字線 2260L 之一字線驅動器，以及耦接至此相對應對中之第二全域字線 2260R 之一字線終端電路。字線驅動器電路與字線終端電路係適合於施加不同的偏壓條件至第一與第二全域字線，俾能在選擇的局部字線上引發一選擇的偏壓配置。字線驅動器與終端電路可藉由使用類似的電路而被實施，用以將選擇的偏壓條件施加至局部字線，包括電壓位準、電流源、偏壓電路等等。標語"驅動器"與"終端電路"係使用於此，用以暗示在任何既定操作中之電路之角色可以是不同的，於此譬如施加比另一個更高的電壓，且未必暗示它們係使用不同的電路設計而實施。

於此實施例中，為了說明之目的，記憶體單元之方塊包括六條近端位元線與六條局部字線。此技術之實施例可包括各種尺寸之方塊。舉例而言，在一 NAND 架構中，每個方塊可包括在串列選擇電晶體與接地選擇電晶體之間的 16、32 或 64 條局部字線。又，以近端位元線之數目的角度看，可依據待被實現之期望熱退火特徵以及局部字線之電阻選擇方塊之寬度。

局部字線之電阻係為所使用的材料、局部字線之剖面積以及局部字線之長度之函數。在一代表實施例中，局部字線之材料可包括金屬或其他材料，其具有大約 1 歐姆/平方與大約  $30\text{ nm} \times 30\text{ nm}$  之剖面積之一薄片電阻。局部字線之長度可以是大約  $150\mu$ ，其將譬如容納給定  $100\text{ nm}$  間隔之 1500 條近端位元線。當然這些數值取決於在積體

電路之設計上可被納入考量之各種因素。

顯示於此例中之記憶體單元之陣列係以一種 NAND 配置被排列，於此近端位元線 2210 包括一連串的單元中之記憶體單元之通道。每個 NAND 串列包括經由接點 2215 將串列(亦即，近端位元線 2210)耦接至一全域位元線之一串列選擇開關 2290，以及將串列(亦即，近端位元線 2210)耦接至一共通源極線 2250 或其他參照符號之一接地選擇開關 2280。串列選擇開關可以藉由具有一串列選擇線 SSL 2220 之一閘極之一 MOS 電晶體而形成。接地選擇開關可以藉由具有一接地選擇線 GSL 2240 之一閘極之一 MOS 電晶體而形成。

在操作上，第一全域字線 2260L 與第二全域字線 2260R 兩者被控制，以經由第一開關 2262L 與第二開關 2262R 將偏壓條件連接至局部字線 2230a 至 2230f，包括在組合偏壓配置中用以引發電流以供熱退火以及其他需要選擇的記憶體單元之操作使用。

第 23 圖係為施加偏壓給一陣列之記憶體單元之電路之立體圖。此電路包括複數條近端位元線 2310a、2310b，以及複數條局部字線 2330a、2330b、2330c。記憶體單元產生於近端位元線 2310a、2310b 與局部字線 2330a、2330b、2330c 之交點。第一與第二開關(例如局部字線 2330a 上之開關 2362L 與 2362R)係耦接至每一條局部字線 2330a、2330b、2330c 之第一與第二端。於此實施例，局部字線之左端上的開關 2362L 係耦接至接觸構造 2363L，它們係藉此連接至伏在局部字線上面之全域字線 2360L。

又，局部字線之右端上的開關 2362R 係耦接至接觸構造 2363R，它們係藉此連接至伏在局部字線下面之全域字線 2360R。於此例子中之一局部字線解碼器係耦接至第一局部字線選擇線 2370L 與第二局部字線選擇線 2370R，其分別控制開關 2362L 與開關 2362R。用於施加一偏壓配置至記憶體單元之方塊之電路之這種配置，可利用在一陣列之記憶體單元之下的一絕緣層而在裝置中被實施，例如在使用薄膜記憶體單元之實施例中被實施。

第 24 圖係為一陣列構造之剖面圖，於其中一第一全域字線 2460L 係被部署在一局部字線 2430 之上，而一第二全域字線 2460R 係被部署在局部字線 2430 之下。此陣列之剖面圖係沿著第一全域字線 2460L、第二全域字線 2460R 以及局部字線 2430。於此構造中，一絕緣層 2401 伏在一基板(未顯示)上面，此基板可包括多重層之記憶體陣列、邏輯電路以及其他積體電路特徵部。一第一圖案化導體層伏在絕緣層 2401 上面，於其中佈局包括全域字線 2460R 之"第二"全域字線。絕緣層 2402 伏在包括全域字線 2460R 之圖案化導體層上面。覆蓋於絕緣層 2402 上的是一陣列層，其包括複數條近端位元線 2410a、2410b、2410c、2410d 連同用於選擇局部字線 2430 之開關的電晶體本體 2462L 與 2462R。複數條近端位元線 2410a、2410b、2410c、2410d 係被排列於此視圖中，俾能使位元線延伸進入並離開紙張之平面。

一記憶體元件層 2480(例如多層介電電荷捕捉構造)伏在複數條近端位元線 2410a、2410b、2410c、2410d 上面。

局部字線 2430 伏在記憶體元件層 2480 上面。局部字線選擇線 2470L 與 2470R 分別伏在電晶體本體 2462L 與 2462R 上面。局部字線選擇線 2470L 與 2470R 係被排列於此視圖中，俾能使它們延伸進入並離開紙張之平面。

電晶體本體 2462L 與 2462R 包括源極、通道以及汲極區域(未顯示)。局部字線選擇線 2470L 與 2470R 係被配置成在電晶體本體 2462L 與 2462R 之通道上面的閘極。電晶體本體 2462L 之源極與汲極端子之其中一個係連接至在局部字線上面延伸之一導電插塞 2469L，而電晶體本體 2462L 之源極與汲極端子之另一個係經由一連接器 2468L 連接至局部字線 2430 之一第一端。同樣地，電晶體本體 2462R 之源極與汲極端子之其中一個係連接至在局部字線下面延伸之一導電插塞 2469R，而電晶體本體 2462R 之源極與汲極端子之另一個係經由一連接器 2468R 連接至局部字線 2430 之一第二端。在某些實施例中，局部字線 2430 可延伸在電晶體本體 2462L 與 2462R 以及且形成於其間之接點之上面，以作為更複雜的連接器 2468L 與 2468R 之替代方案。

包括局部字線 2430 以及局部字線選擇線 2470L 與 2470R 之構造係部署在一絕緣填充 2403 之內。一第二圖案化導體層伏在絕緣填充 2403 上面，於其中佈局包括全域字線 2460L 之"第一"全域字線。如顯示的，導電插塞 2469L 將電晶體本體 2462L 連接至上層的全域字線 2460L。同樣地，導電插塞 2469R 將電晶體本體 2462R 連接至下層的全域字線 2460R。絕緣層 2404 伏在包括全域字線 2460L 之

圖案化導體層上面。

第 25 圖係為施加偏壓給一陣列之記憶體單元之電路之立體圖。此電路包括複數條近端位元線 2510a、2510b 以及複數條局部字線 2530a、2530b、2530c。記憶體單元產生於近端位元線 2510a、2510b 與局部字線 2530a、2530b、2530c 之交點。第一與第二開關(例如局部字線 2530a 上之開關 2562L 與 2562R)係耦接至每一條局部字線 2530a、2530b、2530c 之第一與第二端。於此實施例，局部字線之左端上的開關 2562L 係耦接至接觸構造 2563L，它們係藉此連接至伏在局部字線上面之全域字線 2560L。又，局部字線之右端上的開關 2562R 係耦接至接觸構造 2563R，它們係藉此連接至全域字線 2560R，且亦伏在局部字線上面。於此例子中之一局部字線解碼器係耦接至第一局部字線選擇線 2570L 與第二局部字線選擇線 2570R，其分別控制開關 2562L 與開關 2562R。

第 26A 圖係為一陣列構造之剖面圖，於其中全域字線對之第一全域字線 2660L 與第二全域字線 2660R 兩者係部署在局部字線上面。此陣列之剖面圖係沿著局部字線 2630，其中第一與第二全域字線以相同位準與附圖中之一斷流器(cutout)特徵部對準以顯露兩者。於此構造中，一個半導體基板 2601 包括被渠溝隔離構造 2615a、2615b、2615c、2615d、2615e 隔開之複數條近端位元線 2610a、2610b、2610c、2610d。又，電晶體本體 2662L 與電晶體本體 2662R 係形成於此陣列中之每個列上之基板 2601 中。電晶體本體 2662L 與電晶體本體 2662R 包括源極、通

道以及汲極區域(未顯示)。一記憶體元件層 2680(例如多層介電電荷捕捉構造)伏在複數條近端位元線 2610a、2610b、2610c、2610d 上面。一局部字線 2630 伏在記憶體元件層 2680 上面。局部字線選擇線 2670L 與 2670R 分別伏在電晶體本體 2662L 與電晶體本體 2662R 中之電晶體通道上面。局部字線選擇線 2670L 與 2670R 係被排列於此視圖中，俾能使它們延伸進入並離開紙張之平面。

局部字線選擇線 2670L 與 2670R 係被配置成在電晶體本體 2662L 與電晶體本體 2662R 之通道上面的閘極。電晶體本體 2662L 之源極與汲極端子之其中一個係連接至延伸在局部字線上面之一導電插塞 2669L，而電晶體本體 2662L 之源極與汲極端子之另一個係經由一連接器 2668L 連接至局部字線 2630 之一第一端。同樣地，電晶體本體 2662R 之源極與汲極端子之其中一個係連接至延伸在局部字線上面之一導電插塞 2669R，其朝垂直於紙張之平面之方向潛在地偏移，而電晶體本體 2662R 之源極與汲極端子之另一個係經由一連接器 2668R 連接至局部字線 2630 之一第二端。在某些實施例中，局部字線 2630 可延伸在電晶體本體 2662L 與電晶體本體 2662R 以及形成於其間之接點上面，以作為更複雜的連接器 2668L 與 2668R 之替代方案。

包括局部字線 2630 以及局部字線選擇線 2670L 與 2670R 之構造係部署在一絕緣填充 2603 之內。一圖案化導體層伏在絕緣填充 2603 上面，於其中佈局包括全域字線 2660L 之"第一"全域字線與包括全域字線 2660R 之"第二"

全域字線。如顯示的，導電插塞 2669L 將電晶體本體 2662L 連接至上層的全域字線 2660L。同樣地，導電插塞 2669R 將電晶體本體 2662R 連接至上層的全域字線 2660R。絕緣層 2604 伏在包括全域字線 2660L 與全域字線 2660R 之圖案化導體層上面。

第 26B 圖顯示關於局部字線 2630a 與上層對之全域字線 2660L/2660R，以及局部字線 2630b 與上層對之全域字線 2661L/2661R 之佈局或俯視圖。在這些對之全域字線中之第一與第二全域字線兩者伏在局部字線上面之實施例中，可增加垂直於局部字線之間隔以為每條局部字線容納兩條全域字線。全域字線可具有一"扭轉(twisted)"佈局，其可改善接觸至下層的局部字線選擇電晶體之彈性，或它們可以是直線狀，如第 26B 圖所示。又，在某些實施例中，第一全域位元線可在覆蓋於局部字線上之一第一圖案化導體層中被實施，而每對中之第二全域位元線可在覆蓋於第一全域位元線上之一額外圖案化導體層中被實施。

包括配置在記憶體陣列之上方的第一全域字線 2660L 與第二全域字線 2660R 之構造，可藉由使用主體矽裝置上之快閃記憶體以及絕緣體上矽型裝置上之薄膜電晶體 TFT 快閃記憶體及其他記憶體構造而被實施。

第 27A 至 27D 圖顯示用來將偏壓條件施加至此陣列中之記憶體單元之全域字線/局部字線電路之各種配置。在第 27A 圖中，一 NAND 架構陣列係顯示有四個區段，其包括一般在符合圓形 2701、2702、2703、2704 之陣列之區域中的記憶體單元。在一 NAND 架構中，全域位元線

GBL(例如 2740)係沿著具有串列選擇電晶體與接地選擇電晶體之行而被配置，用於將個別串列耦接在一全域位元線 GBL 與一通源極 CS 線 2714 之間。於此圖中，全域位元線 GBL 伏在陣列上面，並只顯示於與串列選擇電晶體之接觸點，用以避免模糊化圖中之其他部分。串列係藉由使用上區段上的一串列選擇線 SLL 2709 以及下區段上的一串列選擇線 2710 而耦接至它們對應的全域位元線，串列選擇線 SLL 2709 與串列選擇線 2710 係與字線平行被配置並作為供如所顯示的串列選擇電晶體用之閘極。串列係藉由使用上區段之一接地選擇線 GSL 2712 以及下區段之一接地選擇線 GSL 2713 而耦接至共通源極 CS 線。如所顯示的，有沿著陣列中之記憶體單元之每個列而被配置之成對的全域字線 GWL1、GWL2。這種佈局可被視為沿著位元線之上至下反射鏡影像佈局，藉以允許區段共享至全域位元線之共通源極線與接點。在每個區段之內，局部字線(以粗虛線表示)係以每端上之 MOS 電晶體之型式連接至開關。這些開關係藉由使用一左局部字線選擇線 LWSL(例如 2721)與一右局部字線選擇線 LWSR(例如 2722)而受到控制。這些開關可被排列在各種配置中。於此例子中，第 27A 圖所顯示之開關配置之放大視圖係顯示於圓形 2750 中。圓形 2750 中之開關配置顯示沿著一列(其包括一左側局部字線 LWL-L 與一右側局部字線 LWL-R)延伸之一第一全域字線 GWL1 與一第二全域字線 GWL2。一 MOS 電晶體 2752 具有耦接至左側局部字線 LWL-L 之一第一源極/汲極端子以及耦接至一第一層間接點 2753(其連接至第一全域字線

GWL1)之第二源極/汲極端子。一 MOS 電晶體 2754 具有耦接至右側局部字線 LWL-R 之一第一源極/汲極端子以及耦接至一第二層間接點 2755(其連接至第二全域字線 GWL2)之第二源極/汲極端子。圓形 2750 所顯示之開關配置係經由此陣列而重複在局部字線之末端上，並允許每條局部字線之一端連接至其中一條全域字線，且允許每條局部字線之另一端連接至其他的全域字線。

第 27B 圖顯示一替代陣列佈局，於其中圓形 2750A 中之開關配置利用單一層間接點 2757 而非兩個層間接點，如第 27B 圖所示。於此圖中對於類似的元件重複使用於第 27A 圖中之參考數字，且不再說明這種元件。於此例子中，在圓形 2750A 與 2750B 中有兩個開關配置。圓形 2750A 中之開關配置顯示沿著一列(其包括一左側局部字線 LWL-L 與一右側局部字線 LWL-R)延伸之一第一全域字線 GWL1 與一第二全域字線 GWL2。一 MOS 電晶體 2752A 具有耦接至左側局部字線 LWL-L 之一第一源極/汲極端子以及耦接至層間接點 2757(其連接至第一全域字線 GWL1)之第二源極/汲極端子。一 MOS 電晶體 2754A 具有耦接至右側局部字線 LWL-R 之一第一源極/汲極端子以及耦接至相同的層間接點 2757(其連接至第一全域字線 GWL1)之第二源極/汲極端子。

圓形 2750A 中之開關配置顯示沿著一列(其包括一左側局部字線 LWL-L 與一右側局部字線 LWL-R)延伸之一第一全域字線 GWL1 與一第二全域字線 GWL2。一 MOS 電晶體 2752A 具有耦接至左側局部字線 LWL-L 之一第一源

極/汲極端子以及耦接至層間接點 2757(其連接至第一全域字線 GWL1)之第二源極/汲極端子。一 MOS 電晶體 2754A 具有耦接至右側局部字線 LWL-R 之一第一源極/汲極端子以及耦接至相同的層間接點 2757(其連接至第一全域字線 GWL1)之第二源極/汲極端子。

圓形 2750B 所顯示之開關配置係被排列以將局部字線連接至位在每段之相反側之第二全域字線 GWL2。因此，配置 2750B 包括沿著一列(其包括一左側局部字線 LWL-L 與一右側局部字線 LWL-R)延伸之一第一全域字線 GWL1 與一第二全域字線 GWL2。一 MOS 電晶體 2752B 具有耦接至左側局部字線 LWL-L 之一第一源極/汲極端子以及耦接至層間接點 2758(其連接至第二全域字線 GWL2)之第二源極/汲極端子。一 MOS 電晶體 2754B 具有耦接至右側局部字線 LWL-R 之一第一源極/汲極端子以及耦接至相同的層間接點 2758(其連接至第二全域字線 GWL2)之第二源極/汲極端子。開關配置 2750A 與 2750B 之圖案係經由此陣列而重複，並允許每條局部字線之一端連接至其中一條全域字線，且允許每條局部字線之另一端連接至其他的全域字線。

第 27C 與 27D 圖顯示沿著記憶體陣列中之一列而排列之全域字線對與局部字線，以及對應的全域字線驅動器之代表配置，於此一驅動器亦可作為一全域字線終端電路。

第 27C 圖顯示類似第 27B 圖之配置，其包括包含全域字線 2762 與 2765 之一第一全域字線對。全域字線 2762

係連接於一端上之一左/右全域字線驅動器 2760 與另一端上之一互補式左/右全域字線驅動器 2761 之間。同樣地，全域字線 2765 係連接於一端上之一左/右全域字線驅動器 2763 與另一端上之一互補式左/右全域字線驅動器 2764 之間。

於此說明中，有沿著列被排列之四個字線段 (2766-2769) 與相對應的全域字線對 2762/2765。全域字線 2762 上之一接點 2772 係經由一開關連接至局部字線 2766 之右端。局部字線 2766 之左端係經由一第一開關連接至全域字線 2765 上之接點 2770。又，全域字線 2765 上之接點 2770 係經由一第二開關連接至局部字線 2767 之左端。全域字線 2762 上之接點 2773 係經由一第一開關連接至局部字線 2767 之右端，並經由一第二開關連接至局部字線 2768 之左端。局部字線 2768 之右端係經由一第一開關連接至全域字線 2765 上之接點 2771。又，全域字線 2765 上之接點 2771 係經由一第二開關連接至局部字線 2769 之左端。全域字線 2762 上之接點 2774 係經由一開關連接至局部字線 2769 之右端。

於此配置中，驅動器 2760 與 2761 可基於局部字線選擇器解碼而被配置，俾能使在導電模式(例如熱退火)期間橫越過局部字線所施加之偏壓條件藉由依據選擇的局部字線交替較高電壓與較低電壓角色來維持相同的電流方向。或者，依據選擇的局部字線，可允許導電模式利用朝相對方向之電流操作。

第 27D 圖顯示類似第 27A 圖之配置，其包括一個包

含全域字線 2782 與 2785 之第一全域字線對。全域字線 2782 係連接於一端上之一左全域字線驅動器 2780 與另一端上之一互補式右全域字線驅動器 2781 之間。同樣地，全域字線 2785 係連接於一端上之一左全域字線驅動器 2783 與另一端上之一互補式右全域字線驅動器 2784 之間。

於此說明中，有沿著列被排列之四個字線段 (2786-2789) 與相對應的全域字線對 2782/2785。全域字線 2785 上之接點 2790、2791、2792 以及 2793 係經由各自的開關連接至各自的局部字線 2786 至 2789 之右端。全域字線 2782 上之接點 2794、2795、2796 以及 2797 係經由各自的開關連接至各自的局部字線 2786 至 2789 之左端。

於此配置中，在全域字線以及耦接至局部字線之開關之間有兩倍之多的層間接點，如第 27C 圖之配置。然而，全域字線驅動器可被配置，俾能使它們獨立於選擇的局部字線專門地操作作為一左側驅動器或作為一右側驅動器。

第 28 圖顯示一代表處理過程，於其中熱退火循環係藉由使用第一與第二全域字線而穿插在關於記憶體裝置之任務功能操作(讀取、編程、抹除)之間。在裝置之操作期間，執行編程/抹除循環操作，如以方塊 2801 表示。裝置上之控制電路包括用以維持編程與抹除循環、編程循環或抹除循環之次數計算或計數(例如藉由計算編程操作，藉由計算抹除操作，或藉由計算編程與抹除操作對)之邏輯(方塊 2803)，並監視此計算(方塊 2805)。控制電路亦包括用於執行於下所說明之後續步驟的邏輯。如果計數尚未達到一門檻值，則控制電路進行回圈以繼續計數循環。當計

數達到一門檻值時，則控制電路接著將第一與第二全域字線耦接至選擇的對應的局部字線(2810)，並控制複數個配對的字線驅動器與字線終端電路，用以施加偏壓至在選擇的局部字線中引發電流流之全域位元線對(2815)。

編程與抹除循環計數與熱退火循環可在適合一特定實施例時，根據多組之單元，例如根據逐列基礎、根據逐行基礎、根據逐方塊基礎，或遍及整個陣列而被施加。退火可在適合功率消耗需求與一既定實施例之其他需求時，同時被施加至單元之一列或行，或施加至較多組之單元。

第 29 圖顯示另一種處理過程，於其中熱退火循環係藉由使用第一與第二全域字線而穿插在關於記憶體裝置之任務功能操作(讀取、編程、抹除)之間。在第 29 圖之處理過程中，編程/抹除循環操作係在正常操作期間被執行，如以方塊 2901 表示。控制電路包括用以監測一區塊抹除功能之執行以及用於執行於下所說明之後續步驟之邏輯。控制電路決定何時已完成一區塊抹除操作(方塊 2905)。如果沒有區塊抹除操作被完成，則控制電路繼續監視且正常操作。如果成功地完成一次區塊抹除操作，則控制電路為對應的局部字線(2910)解碼第一與第二全域字線，並控制複數個配對的字線驅動器與字線終端電路，用以施加偏壓至在選擇的局部字線中引發電流流之全域位元線對(2915)。

第 30 圖顯示一代表處理過程，於其中熱退火係藉由使用第一與第二全域字線而在關於記憶體裝置之一任務

功能(於此例子中之一區塊抹除)期間被施加。在第 30 圖之處理過程中，關於記憶體裝置之正常編程/抹除循環正發生，如以方塊 3001 表示。控制電路包括用以決定一區塊抹除是否已被要求(方塊 3005)並用於執行於下所說明之後續步驟之邏輯。如果一區塊抹除尚未被要求，則控制電路繼續正常操作與監視。如果一區塊抹除操作被要求，則控制電路在區塊抹除操作期間終結字線，俾能使被抹除之記憶體單元可利用熱產生電流，或者以其他方式施加熱退火(方塊 3007)。如上所述，這不但可改善抹除性能，而且允許介電電荷補捉構造從編程/抹除循環損壞恢復。當完成區塊抹除功能(方塊 3020)時，處理過程回復至正常操作。

依據本技術之實驗已為後編程/抹除循環的裝置施加各種字線電流及退火脈衝，於此記憶體裝置是在一測試配置中之 BE-SONOS 介電電荷補捉記憶體。字線電流包括 1.2mA、1.6mA 以及 2mA。退火脈衝之範圍從 0.1 毫秒(ms)至 100 秒。記憶體裝置執行 10,000 次 PE 循環以看見損壞效果。就在熱退火期間之門檻電壓漂移、次門檻斜率恢復以及轉導而論之實驗結果係詳細說明於下。

第 31 圖係為門檻電壓對退火脈衝寬度之曲線圖，顯示在熱退火期間之門檻電壓漂移之實驗結果。在任何編程/抹除循環之前的門檻電壓大約為 6.2V。在沒有退火的情況下，且在 10,000 次 PE 循環之後，編程的門檻電壓漂移成大約 7.0V。利用 1.2mA、1.6mA 以及 2mA 之退火電流，而退火電流是一毫秒或更少，門檻電壓分別漂移成大約 6.7V、6.4V 以及 5.7V。因此，實驗證明當字線電流係為

1.6mA 或 2mA 時，由字線加熱器所提供之脈衝退火可提供在退火脈衝寬度之一毫秒之內的非常快速的門檻電壓恢復時間。

第 32 圖係為次門檻斜率對退火脈衝寬度之曲線圖，顯示在熱退火之後之次門檻恢復之實驗結果。對應於上述之門檻電壓漂移之實驗結果，後 PE 循環的裝置顯現快速的次門檻斜率(SS)恢復。在任何編程/抹除循環之前，在測試之下的記憶體裝置顯現大約在 220mV/10 年及 280mV/10 年之間的 SS。在 10,000 次編程/抹除循環之後，在沒有退火的情況下，在測試之下的記憶體單元顯現大約在 410mV/10 年與 490mV/10 年之間的 SS。利用 1.2mA、1.6mA 以及 2mA 之退火電流，在幾毫秒之內，在測試之下的記憶體單元分別顯現大約 430mV/10 年、360mV/10 年以及 250mV/10 年之 SS。因此，實驗證明由字線加熱器所提供之脈衝退火，可利用一毫秒退火脈衝寬度提供快速的次門檻斜率恢復時間，且字線電流大約是 2mA。

第 33 圖係為轉導對退火脈衝寬度之曲線圖，顯示在熱退火期間之轉導恢復之實驗結果。對應於上述之門檻電壓漂移與次門檻斜率恢復之實驗結果，後編程/抹除循環的裝置顯現快速轉導( $g_m$ )恢復。在任何編程/抹除循環之前，在測試之下的記憶體裝置顯現大約在  $0.11 \mu A/V$  以及  $0.14 \mu A/10$  年之間的  $g_m$ 。在 10,000 次編程/抹除循環之後，在沒有退火的情況下，在測試之下的記憶體裝置分別顯現大約在  $0.4 \mu A/V$  與  $0.9 \mu A/V$  之間的  $g_m$ 。利用 1.2mA、1.6mA 以及 2mA 之退火電流，在一毫秒左右之內，在測試之下

的記憶體單元分別顯現大約  $0.85 \mu A/V$ 、 $0.8 \mu A/V$  以及  $1.1 \mu A/V$  之  $g_m$ 。因此，實驗證明由字線加熱器所提供之脈衝退火可提供快速的轉導恢復時間。

一項 10 個百萬循環編程/抹除循環耐久性測試已被實現以測試由本技術所作出的耐久性改善。此測試在每 10,000 次編程/抹除循環直到 10,000,000 次編程/抹除循環之後施加一熱退火。編程/抹除循環係利用一種啞巴模式 (dumb-mode)(具有於 +19V 下持續  $10 \mu sec$  之一單發 (one-shot) 編程操作以及於 -13V 下持續  $10 msec$ (毫秒)之一單發抹除操作)而完成。藉由橫越過閘極之壓降所造成的具有  $2mA$  閘極電流之  $100msec$  之熱退火脈衝，係在每 10,000 次編程/抹除循環之後被施加。耐久性測試之結果係說明於下。

第 34 圖係為門檻電壓對編程/抹除循環次數之曲線圖，顯示熱退火之實驗結果。耐久性測試之結果顯示在每 10,000 次編程/抹除循環之後，處於編程狀態之門檻電壓由於裝置退化向上漂移了大約  $1V$ 。在施加熱退火脈衝之後，處於編程狀態之門檻電壓由於退火與電荷損失降低。

第 35 圖係為次門檻斜率對編程/抹除循環次數之曲線圖，顯示熱退火之實驗結果。耐久性測試之結果顯示次門檻斜率在熱退火之後完全被恢復至在  $200mV/10$  年之下。

第 36 圖係為汲極電流對控制閘電壓之曲線圖，顯示在編程/抹除循環期間同時施加熱退火之 IV 曲線之實驗結果。耐久性測試之結果顯示關於編程與抹除狀態之相對應的 IV 曲線(汲極電流對控制閘)顯現出，以每 10,000 次編

程/抹除循環施加熱退火的方式在 1 千萬次編程/抹除循環之後不會有退化。

第 37 圖係為門檻電壓對保持時間之曲線圖，顯示施加熱退火之實驗結果。此實驗係針對於室溫下且於 150°C 下之保持時間、針對沒有編程/抹除循環之快閃記憶體裝置以及針對具有 1 千萬次循環以上的記憶體裝置而實施。2mA/10 秒之熱退火脈衝已被施加至具有 1 千萬次編程/抹除循環以上的記憶體裝置。具有 1 千萬次循環以上的記憶體裝置顯現出可以與於室溫下以及於 150°C 下之快閃記憶體裝置比較的保持時間，而大約 0.2V 之門檻電壓漂移亦可與快閃記憶體裝置比較。

第 38-45 圖顯示各種型式之快閃記憶體單元，其中局部字線、全域字線配置以及允許如於此所說明的熱退火技術之其他構造可被應用至此快閃記憶體單元。

第 38 圖係為為了熱退火操作而配置的一浮動閘記憶體單元之剖面圖。記憶體單元包括一基板 3810。源極與汲極區域 3820 與 3830 係形成於基板 3810 中。一隧道氧化層 3860 係形成在基板 3810、源極區域 3820 與汲極區域 3830 上方。一浮動閘 3870 係在隧道氧化層 3860 上方。一多晶矽層間氧化層係在浮動閘 3870 上方。一控制閘 3890 係形成於多晶矽層間氧化層 3880 之頂端上。

為了熱退火操作，控制閘 3890 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線與一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏

壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 39 圖係為為了熱退火操作而配置的一奈米晶體記憶體單元之剖面圖。記憶體單元包括一基板 3910。源極與汲極區域 3920 與 3930 係形成於基板 3910 中。一閘極氧化層 3980 係形成在基板 3910、源極區域 3920 與汲極區域 3930 上方。奈米晶體微粒 3970 係埋入在閘極氧化層 3980 之內。一控制閘 3990 係形成於閘極氧化層 3980 之頂端上。

為了熱退火操作，控制閘 3990 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線與一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一開關與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 40 圖係為為了熱退火操作而配置的一 TANOS ( $Ta\text{N}/\text{Al}_2\text{O}_3/\text{SiN}/\text{SiO}_2/\text{Si}$ ) 記憶體單元之剖面圖。記憶體單元包括一基板 4010。源極與汲極區域 4020 與 4030 係形成於基板 4010 中。包括  $\text{SiO}_2$  之一穿隧介電層 4060 係形成在基板 4010、源極區域 4020 與汲極區域 4030 上方。包括  $\text{SiN}$  之一捕捉層 4070 係形成在穿隧介電層 4060 上方。包括  $\text{Al}_2\text{O}_3$  之一阻擋氧化層 4080 係形成在捕捉層 4070 上

方。一控制閘 4090 係形成於阻擋氧化層 4080 之頂端上。

為了熱退火操作，控制閘 4090 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線與一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 41 圖係為為了熱退火操作而配置的一 MA-BESONOS 記憶體單元之剖面圖。記憶體單元包括一基板 4110。源極與汲極區域 4120 與 4130 係形成於基板 4110 中。包括一 ONO(氧化物-氮化層-氧化物)穿隧構造之一帶隙工程穿隧屏障 4150 係形成在基板 4110、源極區域 4120 與汲極區域 4130 上方。包括 SiN(氮化矽)之一電荷捕捉介電層 4160 係形成在帶隙工程穿隧屏障 4150 上方。一上氧化層 4170 係形成在電荷捕捉介電層 4160 上方。一高介電常數覆蓋層 4180 係形成在上氧化層 4170 上方。一控制閘 4190 係形成於高介電常數覆蓋層 4180 之頂端上。控制閘 4190 可能是金屬閘極或多晶矽閘極。

為了熱退火操作，控制閘 4190 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線與一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施

例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 42 圖係為為了熱退火操作而配置的一種 FinFET 記憶體單元之剖面圖。記憶體單元包括形成於從一基板伸出之一基板鰭片(未顯示)上之源極與汲極區域 4220 與 4230。源極與汲極區域 4220 與 4230 具有一寬度 4225。一 ONO (氧化物-氮化物-氧化物)堆疊 4250 係形成於基板鰭片上。ONO 堆疊 4250 包括在基板鰭片上方之下氧化層、在下氧化層上方之一電荷補捉層(SiN)，以及在電荷補捉層上方之上氧化層。一控制閘 4290 係形成在 ONO 堆疊 4250 之頂端上。控制閘 4290 具有一長度 4295。

為了熱退火操作，控制閘 4290 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線及一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 43 圖係為為了熱退火操作而配置的一分離閘記憶體單元之剖面圖。記憶體單元包括一基板 4310。源極與汲極區域 4320 與 4330 係形成於基板 4310 中。一隧道氧化層 4395 係形成在基板 4310 上方。一閘極 4390 係形成在隧道氧化層 4395 上方。一浮動閘 4370 亦形成在隧道氧化

層 4395 上方。

為了熱退火操作，閘極 4390 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線與一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 44 圖係為為了熱退火操作而配置的另一個分離閘記憶體單元之剖面圖。記憶體單元包括一基板 4410。源極與汲極區域 4420 與 4430 係形成於基板 4410 中。一第一隧道氧化層 4495 係形成在基板 4410 上方。一存取閘極 4490 係形成在第一隧道氧化層 4495 上方。一第二隧道氧化層 4475 係形成在基板 4410 上方。一浮動閘 4470 係形成在第二隧道氧化層 4475 上方。一介電層 4485 係形成在浮動閘 4470 上方。一控制閘 4480 係形成在介電層 4485 上方。一隔離間隙 4460 係被建構以使存取閘極 4490 與控制閘 4480 和浮動閘 4470 分離。

存取閘極 4490 具有一寬度 4493。控制閘 4480 具有一寬度 4483。隔離間隙 4460 具有一寬度 4463。第一隧道氧化層 4495 具有厚度 4493。第二隧道氧化層 4475 具有一厚度 4473。源極與汲極區域 4420 與 4430 具有一厚度 4425。

為了熱退火操作，存取閘極 4490 及/或控制閘 4480 可能耦接至一局部字線，其係經由一第一開關與一第二開

關而耦接至一第一全域字線與一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 45 圖係為為了熱退火操作而配置的一種 SONOS (矽氧化氮氧化矽) 記憶體單元之剖面圖。記憶體單元包括一基板 4510。源極與汲極區域 4520 與 4530 係形成於基板 4510 中。一下氧化層 4560 係形成在基板 4510、源極區域 4520 與汲極區域 4530 上方。一電荷捕捉層 4570 係在下氧化層 4560 上方。電荷捕捉層 4570 可包括例如  $\text{Si}_3\text{N}_4$  之氮化矽材料。位元線 4550 係由電荷捕捉層 4570 所包圍。一上氧化層 4580 係在電荷捕捉層 4570 上方。一閘極 4590 係形成於上氧化層 4580 之頂端上。

為了熱退火操作，控制閘 4590 可能耦接至一局部字線，其係經由一第一開關與一第二開關而耦接至一第一全域字線及一第二全域字線。在操作上，第一全域字線與第二全域字線兩者可經由第一與第二開關被解碼以提供偏壓至局部字線，用以引發供熱退火用之電流。於其他實施例中，譬如利用以下相關於第 54-58 圖所討論之方法而實施之二極體搭接可能用來引發熱退火。又，在某些實施例中可能利用通道電流以引發熱退火。

第 46 圖係為一種分段字線 NOR 記憶體陣列之一區段之簡化視圖，分段字線 NOR 記憶體陣列包括第一全域字

線對 4660L、4660R，第二全域字線對 4661L、4661R，數條局部字線 4632，以及數條局部字線 4634。於此例子中，存在有一陣列之快閃記憶體單元，其包括以一 NOR 配置被排列之沿著局部字線 4632 之單元 4682、4684、4686，以及沿著局部字線 4634 之對應的單元。於此說明中，每條局部字線段上只有三個單元。然而，如上所述，遍及依據熱退火處理過程之需求所決定的分段之長度，每條字線段可被耦接至多數個單元。一共通源極線 4690 係耦接至單元之源極端子，並耦接至源極線終端電路(未顯示)，其執行如為陣列之特定實施例所指定的。位元線 BL<sub>n-1</sub>、BL<sub>n</sub> 與 BL<sub>n+1</sub> 係耦接至此陣列之行中的單元之汲極側，並耦接至供特定陣列用之存取電路設計。

局部字線 4632 在左側具有數個接觸點 4664L，且在右側具有接觸點 4664R。類似的終端點係形成於局部字線 4634 上。包括左側之電晶體 4662L 與右側之 4662R 之開關係耦接至左側之相對應的接觸點 4664L 與右側之 4664R，並耦接至相對應的全域字線 4660L 與 4660R。左側之控制線 4670L 與右側之 4670R 係耦接至此陣列之一區段中的電晶體 4662L 與 4662R 之閘極，用以如上所述控制電流施加至局部字線。在另一實施例中，接觸點 4664L 與 4664R 係譬如利用以下相關於第 54-58 圖所討論之方法，而經由二極體耦接至第一與第二導體，電流係藉此而在局部字線 4634 中被引發。

第 47 圖係為一種分段字線虛接地記憶體陣列之一區段之簡化視圖，分段字線虛接地記憶體陣列包括第一全域

字線對 4760L、4760R，第二全域字線對(未標示)，數條局部字線 4732 以及數條局部字線 4734。於此例子中，存在有一陣列之快閃記憶體單元，其包括以一虛接地配置被排列之沿著局部字線 4732 之單元 4782、4784、4786、4788，以及沿著局部字線 4734 之對應的單元。於此說明中，每條局部字線段上只有四個單元。然而，如上所述，遍及依據熱退火處理過程之需求所決定的分段之長度，每條字線段可被耦接至多數個單元。位元線 BLn-2、BLn-1、BLn、BLn+1 以及 BLn+2 係耦接至此陣列之行中的單元之對向側，並耦接至為特定陣列設計之存取電路。

局部字線段 4732 在左側具有接觸點 4764L，且在右側具有接觸點 4764R。類似的終端點係形成於局部字線 4734 上。包括左側之電晶體 4762L 與右側之電晶體 4762R 之開關係耦接至左側之相對應的接觸點 4764L 與右側之接觸點 4764R，並耦接至相對應的全域字線 4760L 與 4760R。左側之控制線 4770L 與右側之控制線 4770R 係耦接至此陣列之一區段中的電晶體 4762L 與 4762R 之閘極，用以如上所述控制電流施加至局部字線。在另一個實施例中，接觸點 4764L 與 4764R 係譬如利用以下相關於第 54-58 圖所討論之方法而經由二極體耦接至第一與第二導體，電流係藉此而在局部字線 4734 中被引發。

第 48 圖係為一種分段字線 AND 記憶體陣列之一區段之簡化視圖，分段字線 AND 記憶體陣列包括第一全域字線對 4860L、4860R，第二全域字線對(未標示)，以及局部字線 4832 與 4834。於此例子中，存在有一陣列之快閃記

憶體單元，其包括以一 AND 陣列配置被排列之沿著局部字線段 4832 之單元 4882、4884、4886，以及沿著局部字線段 4834 之對應的單元。於此說明中，每條局部字線段上只有三個單元。然而，如上所述，遍及依據熱退火處理過程之需求所決定的分段之長度，每條字線段可被耦接至多數個單元。位元線 BL0、BL1、…BLn 以及電源線 SL0、SL1、…SLn 係耦接至此陣列之行中的單元之對向側，並耦接至為特定陣列設計之存取電路。

字線段 4832 在左側具有接觸點 4864L，且在右側具有接觸點 4864R。類似的終端點係形成於字線段 4834 上。包括左側之電晶體 4862L 與右側之電晶體 4862R 之開關係耦接至左側之相對應的接觸點 4864L 與右側之接觸點 4864R，並耦接至相對應的全域字線對 4860L 與 4860R。左側之控制線 4870L 與右側之控制線 4870R 係耦接至此陣列之一區段中的電晶體 4862L 與 4862R 之閘極，用以如上所述控制電流施加至局部字線。在另一個實施例中，接觸點 4864L 與 4864R 係譬如利用以下相關於第 54-58 圖所討論之方法，而經由二極體耦接至第一與第二導體，電流係藉此而在字線段 4834 中被引發。

第 49 圖係為一種為了記憶體單元之熱退火而配置的使用垂直閘極之分段字線 3D 記憶體陣列之一區段之簡化視圖。第 49 圖所顯示之陣列之實施例可被完成，如說明在美國專利申請號 13/245,587，名稱為供一 3D 記憶體陣列用之架構(Architecture for a 3D Memory Array)，申請日為 2011 年 9 月 26 日，其係併入作參考猶如完全提出於此。

3D 陣列包括複數個層級之記憶體單元，包括包含記憶體單元 4981 之層級，以及包含記憶體單元 4982、4984、4986 之層級。每個層級包括複數個 NAND 串列，其係耦接至每個層級中之對應的位元線，例如在包含記憶體單元 4982、4994、4986 之層級中的位元線 4967。覆蓋於記憶體單元層級之堆疊上的是複數個字線段，包括字線段 4969。這些段包括垂直延伸(包括延伸 4965 與 4966)，其耦接至各種層級中的記憶體單元之間極。因此，字線段 4969 之延伸 4965 係耦接至分別在第一與第二層級中之記憶體單元 4981 與 4986 之控制閘。

字線段 4969 在左側具有接觸點 4964L，且在右側具有接觸點 4964R。類似的終端點係形成於其他字線段上。包括左側之電晶體 4962L 與右側之電晶體 4962R 之開關係耦接至左側之相對應的接觸點 4864L 與右側之接觸點 4864R，並耦接至相對應的全域字線 4960L 與 4960R。左側之控制線 4970L 與右側之控制線 4970R 係耦接至此陣列之一區段中的電晶體 4962L 與 4962R 之間極，用以如上所述控制電流施加至局部字線。在另一實施例中，接觸點 4964L 與 4964R 係譬如利用以下相關於第 54-58 圖所討論之方法而經由二極體耦接至第一與第二導體，電流係藉此而在字線段 4969 中被引發。吾人可能期望施加電流至位元線而與施加電流至於此實施例中的字線結合，並期望基於相對應的記憶體單元之位準調整施加至位元線之電流量。

第 50 圖顯示為熱退火而配置之一種垂直 NAND 串列

3D 陣列。在第 50 圖所顯示之實施例中，有複數個垂直 NAND 串列，其包括具有一串列選擇電晶體 5080 之串列，連同供耦接至一串列選擇線 SSL 之複數個其他 NAND 串列用之串列選擇電晶體。記憶體單元係串聯配置在串列選擇電晶體(例如 5080)與一共通源極選擇電晶體(例如耦接至與串列選擇電晶體 5080 相同的 NAND 串列之共通源極電晶體 5081)之間。一共通源極線 5050 終結複數個垂直 NAND 串列。二極體(例如一二極體 5090)可被使用以使共通源極線 5050 與基板隔離。包括一位元線 5010 之複數條位元線係具體形成在陣列之上端上方，並藉由使用串列選擇電晶體與共通源極選擇電晶體而耦接至相對應的垂直 NAND 串列。包括剛好在串列選擇電晶體層之下的一字線構造 5048 之複數個字線構造，係具體形成在此陣列之對應的層級中。

字線構造 5048 在左側具有接觸點 5064L(其將字線構造之三個尖部耦接在一起)，且在右側具有接觸點 5064R。類似的終端點係形成於其他位準中之其他字線構造上。在包括字線構造 5048 之位準中包括左側之電晶體 5062L 與右側之電晶體 5062R 之開關，係耦接至左側之相對應的接觸點 5064L 與右側之接觸點 5064R，並耦接至相對應的全域字線 5060L 與 50560R。左側之控制線 5070L 與右側之控制線 5070R 係耦接至此陣列之一區段中的電晶體 5062L 與 5062R 之閘極，用以如上所述控制電流施加至局部字線。在另一實施例中，接觸點 5064L 與 5064R 係譬如利用以下相關於第 54-58 圖所討論之方法而經由二極體耦接至

第一與第二導體，電流係藉此而在一字線中被引發。吾人可能期望施加電流至位元線而與施加電流至於此實施例中的字線結合，並期望基於相對應的記憶體單元之位準調整施加至位元線之電流量。

第 51 圖係為一分段字線 3D 垂直-堆疊-陣列-電晶體(VSAT)記憶體陣列(如說明於此之為了熱退火之施加所作的變化)之一區段之簡化視圖，基於 Kim 等人之"供超高密度及成本效益 NAND 快閃記憶體裝置及 SSD(固態硬碟)用之新穎的垂直-堆疊-陣列-電晶體(VSAT)"所說明的，其發表在 2009 年科技論文研討會 VLSI 技術文摘，第 186-187 頁，此文章係猶如完全提出於此地併入作參考。第 51 圖之構造可使用一種"閘極第一及通道最後處理過程"來實施，其中閘極係沈積於多層 Si 台地(mesas)上上，同時形成管道構造。Kim 等人陳述：

"在藉由一乾蝕刻製程建立一 Si 台地以後，多層之摻雜多晶矽及氮化膜係沈積於頂端。摻雜多晶矽及氮化膜係分別被使用作為閘極電極及在閘極之間之隔離材料。活性區域係在對多重層刻以圖案及一後續乾蝕刻製程之後被定義。所有閘極電極係在一 CMP 製程之後露出於相同平面上，允許對閘極電極之輕易存取。穿隧-氧化層、電荷捕捉-氮化層及控制氧化膜係依序沈積於活性區域中，伴隨著通道材料之一多晶矽沈積製程。最後，為了隔離垂直串列，實現一蝕刻製程"。

可添加熱退火偏壓，於此構造中製出到達通道層之接觸，舉例而言。或者，字線可被分段或被二極體搭接，以提供

退火電流。

第 52 圖係為一分段字線 3D 管形可調位元成本 (P-BiCS) 記憶體陣列(如說明於此之為了熱退火之施加所作的變化)之一區段之簡化視圖，基於 Katsumata 等人之「具有 16 堆疊層之管狀 BiCS 快閃記憶體及供超高密度儲存裝置用之多級單元操作」所說明的，其發表在 2009 年科技論文研討會 VLSI 技術文摘，第 136-137 頁，此文章係猶如完全提出於此地併入作參考。基本構造之 P-BiCS 快閃記憶體係顯示於第 52 圖。如 Katsumata 等人所陳述的：「兩個鄰近 NAND 串列係被以下電極控制閘門之所謂的管道-連接部(PC)連接於底部。供 U 形管道用之其中一個端子係連接至位元線(BL)，而另一端子係由電源線(SL)連綁。SL 由第三級金屬之網狀配線所構成且被第一及第二級金屬接達，類似習知之平坦化技術，因此 SL 之電阻足夠低。SG 電晶體兩者係被置於 SL 與 BL 之下方。控制-閘極(CG)係被縫隙隔離，並面向彼此以作為幾個梳子圖案。記憶體薄膜是由一阻擋薄膜、一電荷捕捉薄膜與基於氧化物的薄膜所構成，以作為一隧道薄膜。基於氧化物的隧道-薄膜之實施例係因為從隧道薄膜之沈積到本體矽之連續處理是可適用的。」熱退火偏壓可被添加，於此構造中製出到達通道層之接觸，舉例而言。或者，字線可被分段或被二極體搭接，以提供退火電流。

第 53 圖係為一替代分段字線 3D 記憶體陣列(如說明於此之為了熱退火之施加所作的變化)之一區段之簡化視圖，基於 Kim 等人之"克服關於兆位元密度儲存之堆疊限

制之多層垂直閘極 NAND 快閃記憶體"所說明的，其發表在 2009 年科技論文研討會 VLSI 技術文摘，第 188-189 頁，此文章係猶如完全提出於此地併入作參考。VG-NAND 快閃記憶體包括字線 WL、位元線 BL，共同電源線 CSL，而一水平的活性串列具有圖案。供 SSL、WL、GSL 使用之垂直閘極 VG 係被使用。電荷補捉層係配置於一活性本體與垂直閘極之間。垂直插塞施加 DC 至源極及活性本體(Vbb)。WL 及 BL 係在製得單元陣列之前之製造初期形成。源極及活性本體(Vbb)係電性地被綁至 CSL，用於致能本體抹除操作。在抹除期間，一正偏壓係被施加至 CSL。除了 SSL 改變以外，每層可相當於一平面式 NAND 快閃記憶體。熱退火偏壓可藉由使用位元線或字線而被施加至譬如 NAND 串列。

第 54 圖係為在作為兩個"熱板"導體之以二極體搭接之第一與第二導體 5430 及 5410 之間之一字線 5420 之簡化視圖。字線 5420 可藉由使用一金屬構造(於此及於說明於此之技術之其他實施例中)而被實施，基於耐火或"高溫"材料，像是鎢，其適合用來作說明於此之退火處理過程之溫度。二極體搭接係藉由使用一第一複數個二極體 5452、5454、5456 來實施，使它們的陽極耦接至字線 5420，使它們的陰極耦接至第一導體 5410；並藉由使用一第二複數個二極體 5442，5444 來實施，使它們的陰極耦接至字線 5420，使它們的陽極耦接至第二導體 5430。於某些實施例中可使用 P+/N- 及 N+/P- 二極體來實施二極體。或者，可使用具有金屬/半導體介面之肖基(Schottky)二極體來實施二

極體。在使二極體接觸字線之位置之間之距離可依據記憶體陣列之實施例被選擇，俾能建立適當的加熱效率。舉例而言，在 P+/N- 及 N+/P- 二極體之位置之間大約 150 微米之距離，可以適合於上述結合實體上分段字線實施例所計算之理由。實際間距可基於用於傳送偏壓之構造之電阻字線之電阻及關於應用此技術之特定記憶體構造之焦耳熱效率來設計。

於此配置中，二極體搭接支持電流從第二導體 5430 通過字線 5420 之段，到第一導體 5410，但阻擋電流逆流。第一複數個二極體係耦接至字線及沿著字線之一第一複數個隔開的位置，而第二複數個二極體係於一第二複數個隔開的位置沿著字線耦接至字線，第二複數個隔開的位置係與第一複數個位置中之數個位置穿插。因此，當第二導體 5430 被係被充分高於第一導體 5410 之電壓之一電壓偏壓時，電流沿著字線 5420 流動通過第二複數個二極體而到隔開的位置，從這些位置到供第一複數個二極體用之接觸位置之電流如圖中之箭號 5421、5422、5423 及 5424 顯示。此種實施例藉由電性地分割字線而不需要物理分段，而允許施加偏壓，其引發電流以供熱退火用。亦，二極體之佈局區域可以大幅地低於實施開關電晶體(說明於提出於此之其他實施例)所需要的。

第一導體 5410 及第二導體 5430 可藉由使用種種的配置而被實施，這些配置包括每一個第一與第二導體具有類似於每個字線之間距之配置，以及第一與第二導體係為具有實質上大於一個別的字線之寬度之板之配置，其中每一

個耦接一些字線。

第 55 圖係為在具有二極體搭接之兩個"熱板"導體之間之多重局部字線之簡化視圖。於此例子中，一第一導體 5510 及一第二導體 5530 係使用二極體搭接來偏壓一第一字線 5522 及一第二字線 5524。供特定字線 5524 用之二極體搭接電路包括：一第一複數個二極體 5556 及 5555，它們的陰極耦接至第一導體 5510，而它們的陽極耦接至字線 5524；及第二複數個二極體 5546 及 5548，它們的陽極耦接至字線 5524 而陰極耦接至第二導體 5530。供特定字線 5522 用之二極體搭接電路包括：一第一複數個二極體 5552 及 5554，它們的陽極耦接至字線 5522，而它們的陰極耦接至第一導體 5510；及一第二複數個二極體 5542 及 5544，它們的陽極耦接至第二導體 5530，而它們的陰極耦接至字線 5522。因此，第 55 圖顯示一實施例，其中一對的第一與第二導體係與供至少兩字線用之二極體搭接電路一起被利用。

第 56 圖係為利用兩個"熱板"導體來二極體搭接一字線之構造之一個例子之 3D 視圖。此構造包括一基板 5610，於其上形成一陣列之記憶體單元。基板可包括一個半導體或一絕緣體，適合一特定實施例之需要。記憶體單元可包括半導體本體 5620，其在基板 5610 上之一絕緣層 5630 之內延伸進出頁面，且記憶體單元通道係形成於其中。一個具有上述其中一種構造之多層電荷捕捉構造 5640 伏在半導體本體 5620 上面。最好是使用一金屬或其他導電材料(其可被使用以提供電流於易於管理的偏壓位準)來

實施之一字線 5650，係伏在電荷補捉構造 5640 上面。在一個伏在記憶體陣列上面之圖案化金屬層中，一第一導體 5670 及一第二導體 5690 係被實施，並作為"熱板"導體以使用二極體搭接來傳送電流至字線之段。

如所顯示，於字線上之一第一接觸位置中，形成一 P-N 二極體，其包括一 P 型半導體元件 5688，最好是具有相當高的(P+)摻雜濃度，並與字線接觸。元件 5688 作為二極體之陽極。最好是具有相當低的(N-)摻雜濃度之一 N 型半導體元件 5686 係形成於 P 型半導體元件 5688 上，以形成一個二極體。元件 5686 作為二極體之陰極。一縱橫導體 5684 接觸半導體元件 5686，其在一覆蓋層中促進二極體連接至導體 5690。於此實施例，延伸通過一絕緣層(未顯示)之一插塞 5682 製造在縱橫導體 5684 與"熱板"導體 5690 之間之接觸。

同樣地，在字線上之一第二接觸位置中，形成一 N-P 二極體，包括一 N 型半導體元件 5668，其最好是具有一相當高的(N+)摻雜濃度，並與字線接觸。元件 5668 作為二極體之陰極。最好是具有相當低的(P-)摻雜濃度之一 P 型半導體元件 5666，係形成於 N 型半導體元件 5668 上，以形成一個二極體。元件 5666 作為二極體之陽極。一縱橫導體 5664 接觸半導體元件 5666，其於一覆蓋層中促進二極體連接至導體 5670。於此實施例，延伸通過一絕緣層(未顯示)之一插塞 5662 可製造在插塞 5662 與"熱板"導體 5670 之間之接觸。

如可被看見的，在二極體搭接電路中之二極體可以種

種的電路配置被耦接至字線及第一與第二導體，這些配置可依據記憶體陣列之構造來作選擇。又，每一個"熱板"導體可被使用以偏壓複數條字線。

第 57 圖係為具有二極體搭接之複數條字線之佈局視圖，這些字線共用單一對的"熱板"導體，其包括第一導體 5770 及第二導體 5790。於此佈局圖例中，構造的說明係從下層至上層。於下顯示層中，於半導體本體(未顯示)中有複數個半導體條帶 5721，5722，5723，5724...，其於一基板(未顯示)上譬如可包括一 finFET 型式 NAND 串列構造之鰭片。於下一個層，複數條字線 5751，5752，5753，5754 延伸正交地橫越過條帶 5721，5722，5723，5724。於字線 5751，5752，5753，5754 上方之一層中，一第一複數個 P-N 二極體(例如二極體 5786)及一第二複數個 N-P 二極體(例如二極體 5766)係沿著字線以隔開的位置被耦接。於第一與第二複數個二極體上方之一層中，縱橫導體 5784 及 5764 係被實施(縱橫導體上之斷流器(cutout)顯示下層的二極體之位置)。最後，實施覆蓋縱橫導體 5784 及 5764、第一與第二"熱板"導體 5770 與 5790。"熱板"導體之寬度可以實質上大於所顯示的那些，只受限於它們被耦接之複數條字線之間距。

快閃記憶體陣列及其他型式之記憶體陣列可能需要相當高的正及負電壓被施加橫越過記憶體單元，以供編程及抹除操作。這建構一種使鄰近字線(包括可能經由二極體搭接耦接至相同對之"熱板"導體之字線)可能具有實質上不同的施加偏壓之狀態。因此，"熱板"導體之偏壓可被控

制以在正常操作期間促進電流之阻隔。於一實施例中，"熱板"導體係維持於一浮動或未連接條件，俾能不允許沿著導體之長度有電流流動。於另一實施例中，"熱板"導體可在操作期間被偏壓於逆向偏壓二極體搭接之二極體之電壓位準。

第 58 圖係為具有二極體搭接之兩個"熱板"導體\*之間之多重局部字線之簡化視圖，顯示在陣列之正常操作期間之潛行路徑之消去。於第 58 圖中，說明於第 55 圖之構造係被再造成具有相同的參考數字。此外，經由第一導體 5510 之在字線 5522 與字線 5524 之間之電流路徑 5800 及 5801 係被顯示以供參考。又，經由第二導體 5530 之在字線 5522 與字線 5524 之間電流路徑 5802 及 5803 係被顯示以供參考。於可能在一快閃記憶體裝置之編程期間產生之之例示偏壓配置中，字線 5524 可被施加大約 +20 伏特以供編程用，而未被選取的字線 5522 可被施加大約 +10 伏特以作為一通過電壓位準。這兩字線 5522 及 5524 係經由二極體搭接耦接至相同對之導體 5510 及 5530。然而，電流路徑 5800 及 5801 係分別地被對向二極體 5552 及 5556 及對向二極體 5554 及 5555 阻擋。為達成此種阻擋效應，第一導體 5510 可被施加大於 +20 伏特之電壓，或於一替代方案中是維持浮動。又，電流路徑 5802 及 5803 係被對向二極體 5542 及 5546 及對向二極體 5544 及 5548 阻擋。為達成此種阻擋效應，第二導體 5530 可被施加低於 +10 伏特之電壓，或於一替代方案中是維持浮動。

因此，在用於在快閃記憶體中讀取、編程或抹除之陣

列之正常操作期間，熱板導體可以是藉由取消選擇一熱板驅動器而浮動，或被偏壓以確保二極體之逆向偏壓。最好是，應利用浮動熱板。電容耦合導致浮動熱板導體被升壓至未阻礙一阻隔作用之電壓位準。在字線與熱板導體之間之電容耦合應該是小的，因為在隔開的位置之二極體電容應該是相當小。因此，使用二極體搭接技術不應大幅地影響字線 RC 延遲特徵。

第 59 圖係為採用說明於此之熱退火以供快閃記憶體用之積體電路之簡化方塊圖。積體電路 470 包括一記憶體陣列 472，其係使用於一積體電路基板上之快閃記憶體單元來實施，於其中字線係使用譬如類似參考第 54-58 圖所說明之技術而被二極體搭接。一接地選擇及串列選擇解碼器 474(包括適當的驅動器)係耦接至及電性連通至串列選擇線及接地選擇線，其沿著記憶體陣列 472 之列配置。又，解碼器 474 包括耦接至字線 476 之字線驅動器。一位元線(行)解碼器及驅動器 478 係耦接至及電性連通至複數條位元線 480，其沿著記憶體陣列 472 中之行配置，用於從記憶體陣列 472 中之記憶體單元讀取資料，及將資料寫入至記憶體單元中。位址係於匯流排 482 上被提供至字線解碼器及串列選擇解碼器 474 及至位元線解碼器 478。

於此例子中，字線上之電流係用於引發熱，用於熱退火介電荷捕捉構造，且加熱器板驅動器 499 係被包括在內。字線終端解碼器 450 可回應於表示操作模式或在操作模式期間產生之位址及控制信號，以供裝置選擇性地連接字線至終端電路，或致能耦接至選擇的字線之終端電路，

如上所述。

在方塊 484 中之感測放大器及資料輸入構造包括用於讀取、編程及抹除模式之電流源，並經由資料匯流排 486 耦接至位元線解碼器 478。資料係經由資料輸入線 488 而從積體電路 470 上之輸入/輸出埠或積體電路 470 之內部或外部之其他資料源被提供至方塊 484 中之資料輸入構造。資料係經由資料輸出線 492 而從方塊 484 中之感測放大器被提供至積體電路 470 上之輸入/輸出埠或積體電路 470 之內部或外部之其他資料目標。

使用一偏壓配置狀態機器而實施於此例子中之一種控制器 494 控制偏壓配置電源電壓之施加及電流源 496，例如讀取、編程、抹除、抹除確認、編程確認電壓或供字線及位元線用之電流，並使用一存取控制過程來控制字線/電源線操作。控制器 494 包括用於致能熱退火之邏輯，包括控制全域字線對之使用，用於施加偏壓條件至局部字線以執行熱退火操作。

控制器 494 可藉由使用在本技術領域熟知之特殊用途邏輯電路而被實施。於替代實施例中，控制器 494 包括一通用處理器，其可能被實施於同一個執行一電腦編程以控制裝置之操作之積體電路上。於又其他實施例中，可能利用特殊用途邏輯電路及一通用處理器之組合以實施控制器 494。

於所說明的實施例中，其他電路 490 係包括於積體電路 470 上，例如一通用處理器或特殊用途應用電路，或提供被記憶體單元陣列所支持之系統單晶片功能性之多個

模組之組合。

又，於某些實施例中，控制器包括編程/抹除循環計數器，及用於設置待被施加至熱退火處理之配置之參數的暫存器。控制器可與其他處理過程及讀取及寫入之任務功能操作一起執行說明於此之程序(參考第 9-11 及 28-30 圖)。於應用第 11 圖之處理過程至第 59 圖之電路時，字線終結步驟係被使用二極體搭接電路施加偏壓至字線之步驟置換。於應用第 28-30 圖之處理過程至第 59 圖之電路時，解碼左右全域字線之步驟係被為陣列之選擇之區段偏壓第一與第二加熱器板之步驟置換。於應用第 30 圖之處理過程至第 59 圖之電路時，在區塊抹除期間終結字線之步驟亦可於某些實施例中被省略。

一種熱輔助快閃記憶體已被說明。此技術係適合與具有 NAND 架構之快閃記憶體裝置以及使用其他架構之裝置一起使用。因為增加之耐久性是可能的，所以快閃記憶體可亦被使用於暫存器配置中。藉由使用由字線中之電流所導致的電阻式加熱(譬如以其容易地被實施於積體電路裝置中的方式)，可產生熱以供熱退火用。藉由施加熱退火操作，可達成改善之耐久性及/或增加之抹除速度。

綜上所述，雖然本發明已以較佳實施例揭露如上，然其並非用以限定本發明。本發明所屬技術領域中具有通常知識者，在不脫離本發明之精神和範圍內，當可作各種之更動與潤飾。因此，本發明之保護範圍當視後附之申請專利範圍所界定者為準。

【圖式簡單說明】

第 1A 至 1C 圖是為了熱退火操作而配置之介電電荷捕捉記憶體單元之簡化立體圖。

第 2 圖是為了熱退火操作而配置之介電電荷捕捉單元之簡化佈局圖。

第 3 圖是為了熱退火操作而配置之共通源極型 NAND 型記憶體陣列之示意圖。

第 4 圖是為了熱退火操作而配置之包括分段字線，快閃記憶體陣列之一積體電路記憶體之方塊圖。

第 5 圖係為包括在行之間的絕緣充填渠溝之 NAND 陣列之記憶體單元之佈局圖。

第 6 圖係為沿著一字線而藉由使用 n 通道裝置之類似第 5 圖之 NAND 陣列之剖面圖。

第 7 圖係為沿著垂直於一條通過包括上與下選擇電晶體之單元通道之字線之 NAND 串列之簡化剖面圖。

第 8 圖顯示為熱退火而配置之記憶體單元之替代構造，包括為熱隔離而配置在薄膜半導體本體上之介電電荷捕捉記憶體單元。

第 9 圖係為用於施加熱退火循環之一種控制順序之簡化流程圖。

第 10 圖係為用於施加熱退火循環之另一種控制順序之簡化流程圖。

第 11 圖係為用於施加熱退火循環之又另一種控制順序之簡化流程圖。

第 12 圖係為汲極電流對控制閘電壓之曲線圖，顯示

施加熱退火之實驗結果。

第 13 圖係為門檻電壓對編程/抹除循環次數之曲線圖，顯示施加熱退火之實驗結果。

第 14 圖係為在第一循環順序之後，關於編程與抹除單元之門檻電壓分佈之曲線圖。

第 15 圖係為在跟隨一熱退火之一第二循環順序之後，關於編程與抹除單元之門檻電壓分佈之曲線圖。

第 16 圖係為在十個循環與退火順序之後，關於編程與抹除單元之門檻電壓分佈之曲線圖。

第 17 圖係為顯示在第一循環順序之後的編程與抹除條件之曲線圖。

第 18 圖係為顯示在跟隨一熱退火之一第二循環順序之後的編程與抹除條件之曲線圖。

第 19 圖係為顯示在十個循環與退火順序之後的編程與抹除條件之曲線圖。

第 20 圖顯示電荷補捉記憶體單元於室溫下以及於升高的溫度下之抹除性能。

第 21 圖係為接受抹除操作之電荷補捉記憶體單元的估計退火時間之圖。

第 22 圖係為分段字線快閃記憶體陣列(包括第全域字線、第二全域字線以及局部字線)之簡化截面圖。

第 23 圖係為顯示在記憶體陣列上方之第一全域字線與在記憶體陣列下方之第二全域字線之記憶體陣列之立體圖。

第 24 圖係為顯示在記憶體陣列上方之第一全域字線

以及在記憶體陣列之下方之第二全域字線之記憶體陣列之剖面圖。

第 25 圖係為顯示位於記憶體陣列之同一側之第一全域字線與第二全域字線兩者之記憶體陣列之立體圖。

第 26A 圖係為顯示在記憶體陣列之上方之第一全域字線與第二全域字線兩者之記憶體陣列之剖面圖。

第 26B 圖係為顯示第一全域字線與第二全域字線兩者在記憶體陣列之上方呈緊密間距之記憶體陣列之俯視圖。

第 27A 圖及第 27B 圖係為顯示替代分段字線解碼電路配置之示意圖。

第 27C 圖及第 27D 圖顯示關於沿著一對應列之局部字線之全域字線對之解碼配置。

第 28 圖係為用於利用第一與第二全域字線施加熱退火循環之控制順序之簡化流程圖。

第 29 圖係為用於利用第一與第二全域字線施加熱退火循環之另一控制順序之簡化流程圖。

第 30 圖係為用於利用第一與第二全域字線施加熱退火循環之又另一種控制順序之簡化流程圖。

第 31 圖係為門檻電壓對退火脈衝寬度之曲線圖，顯示在熱退火期間之門檻電壓漂移之實驗結果。

第 32 圖係為次門檻斜率對退火脈衝寬度之曲線圖，顯示在熱退火之後之次門檻恢復之實驗結果。

第 33 圖係為轉導對退火脈衝寬度之曲線圖，顯示在熱退火期間之轉導恢復之實驗結果。

第 34 圖係為門檻電壓對編程/抹除循環次數之曲線圖，顯示熱退火之實驗結果。

第 35 圖係為次門檻斜率對編程/抹除循環次數之曲線圖，顯示熱退火之實驗結果。

第 36 圖係為汲極電流對控制閘電壓之曲線圖，顯示在編程/抹除循環期間同時施加熱退火之 IV 曲線之實驗結果。

第 37 圖係為門檻電壓對保持時間之曲線圖，顯示施加熱退火之實驗結果。

第 38 圖係為為了熱退火操作而配置的浮動閘記憶體單元之剖面圖。

第 39 圖係為為了熱退火操作而配置的奈米晶體記憶體單元之剖面圖。

第 40 圖係為為了熱退火操作而配置的 TANOS 記憶體單元之剖面圖。

第 41 圖係為為了熱退火操作而配置的 MA-BESONOS 記憶體單元之剖面圖。

第 42 圖係為為了熱退火操作而配置的 FinFET 記憶體單元之剖面圖。

第 43 圖係為為了熱退火操作而配置的分離閘記憶體單元之剖面圖。

第 44 圖係為為了熱退火操作而配置的另一個分離閘記憶體單元之剖面圖。

第 45 圖係為為了熱退火操作而配置的 SONOS 記憶體單元之剖面圖。

第 46 圖係為一種分段字線 NOR 記憶體陣列之一區段之簡化視圖，分段字線 NOR 記憶體陣列包括第一全域字線、第二全域字線及局部字線。

第 47 圖係為一種分段字線虛接地記憶體陣列之一區段之簡化視圖，分段字線虛接地記憶體陣列包括第一全域字線、第二全域字線及局部字線。

第 48 圖係為一種分段字線 AND 記憶體陣列之一區段之簡化視圖，分段字線 AND 記憶體陣列包括第一全域字線、第二全域字線及局部字線。

第 49 圖係為一種使用垂直閘極之分段字線 3D 記憶體陣列之一區段之簡化視圖，分段字線 3D 記憶體陣列包括第一全域字線、第二全域字線及局部字線。

第 50 圖係為一種使用垂直位元線之分段字線 3D 記憶體陣列之一區段之簡化視圖，分段字線 3D 記憶體陣列包括第一全域字線、第二全域字線及局部字線。

第 51 圖係為為了熱退火而配置之一種分段字線 3D 垂直堆疊陣列電晶體(VSAT)記憶體陣列之一區段之簡化視圖。

第 52 圖係為為了熱退火而配置之一種分段字線 3D 管形可調位元成本(P-BiCS)記憶體陣列之一區段之簡化視圖。

第 53 圖係為為了熱退火而配置之一種替代分段字線 3D 記憶體陣列之一區段之簡化視圖。

第 54 圖係為具有二極體搭接之在第一與第二導體之間的一局部字線之簡化視圖。

第 55 圖係為具有二極體搭接之在第一與第二導體之間之多重局部字線之簡化視圖。

第 56 圖係為具有二極體搭接之在第一與第二導體之間之一局部字線之 3D 視圖。

第 57 圖係為具有二極體搭接之多重局部字線之佈局概要圖。

第 58 圖係為具有二極體搭接之在第一與第二導體之間之多重局部字線之簡化視圖，顯示潛行路徑之排除。

第 59 圖係為一種積體電路記憶體之方塊圖，積體電路記憶體包括為了熱退火操作而配置的一條二極體搭接的字線，快閃記憶體陣列。

#### 【主要元件符號說明】

10：字線

11：源極

12：汲極

13：半導體本體

14：多層介電堆疊

20：一端

21：對向端

22：源極

23：汲極

24：交點

25：字線驅動器

26：開關

- 27：終端電路

- 29：閘極

- 30：目標記憶體單元

- 31、32：NAND 串列

- 35：共通源極 CS 線

- 36：串列選擇電晶體

- 37：接地選擇電晶體

- 38：解碼的字線驅動器

- 39：解碼的終端電路

- 51-1 至 51-5：渠溝

- 52-1 至 52-4：半導體條帶

- 53-1 至 53-4：字線

- 70：半導體本體

- 71、79：接點

- 72 至 78：端子

- 73 至 77：源極/汲極端子

- 80：共通源極 CS 線

- 82 至 87：字線

- 88：串列選擇線 SSL

- 90：位元線 BL

- 97、98：閘極介電層

- 99：電荷捕捉構造

- 101：半導體本體

- 102：絕緣體

- 103：區域

- 104：介電電荷捕捉構造

105、106：多晶矽

107、108：矽化物

109、111：通道區

110：源極/汲極區

410：積體電路

412、472：記憶體陣列

414：解碼器

416：字線

417：局部字線解碼器

418：位元線解碼器

420：位元線

422：匯流排

424：感測放大器與資料輸入構造

426：資料匯流排

428：資料輸入線

430：電路

432：資料輸出線

434、494：控制器

436：偏壓配置電源電壓與電流源

450：字線終端解碼器

470：積體電路

474：解碼器

476：字線

478：解碼器

- 480：位元線

482：匯流排

486：資料匯流排

488：資料輸入線

490：其他電路

492：資料輸出線

496：電流源

499：加熱器板驅動器

1201、1202、1203：蹤跡

2210：位元線

2215、2281、2283：接點

2220：串列選擇線 SSL

2230a 至 2230f：局部字線

2250：共通源極線

2260L、2260R：全域字線

2262L、2262R：開關

2270L：第一局部字線選擇線

2270R：第二局部字線選擇線

2280：接地選擇開關

2290：串列選擇開關

2310a、2310b：近端位元線

2240、2712、2713、GSL 81：接地選擇線 GSL

2330a、2330b、2330c：局部字線

2360L、2360R：全域字線

2362L、2362R：開關

- 2363L、2363R、2563L、2563R：接觸構造

2370L、2370R：局部字線選擇線

2401：絕緣層

2402：絕緣層

2403：絕緣填充

2404：絕緣層

2410a、2410b、2410c、2410d：近端位元線

2430：局部字線

2460L、2460R：全域字線

2462L、2462R：電晶體本體

2468L、2468R：連接器

2469L、2469R：導電插塞

2470L、2470R：局部字線選擇線

2480、2680：記憶體元件層

2510a、2510b：近端位元線

2530a、2530b、2530c：局部字線

2560L、2560R：全域字線

2562L、2562R：開關

2570L、2570R：局部字線選擇線

2601：基板

2603：絕緣填充

2604：絕緣層

2610a、2610b、2610c、2610d：近端位元線

2615a、2615b、2615c、2615d、2615e：渠溝隔離構

造

- 2630、2630a、2630b：局部字線

2660L、2660R：全域字線

2661L、2661R：全域字線

2662L、2662R：電晶體本體

2668L、2668R：連接器

2669L、2669R：導電插塞

2670L、2670R：局部字線選擇線

2701、2702、2703、2704：圓形

2709：串列選擇線 SLL

2710：串列選擇線

2714：源極 CS 線

2750：圓形

2750A、2750B：開關配置

2752、2752A、2752B：MOS 電晶體

2753、2755、2757、2758：第一層間接點

2754、2754A、2754B：MOS 電晶體

2760、2761、2763、2780：字線驅動器

2762、2765、2782、2785：全域字線

2764：字線驅動器

2766 至 2769：局部字線

2770 至 2774：接點

2781：字線驅動器

2783、2784：全域字線驅動器

2786 至 2789：局部字線

2790 至 2797：接點

- 3810、3910：基板

3820：源極區域

3830：汲極區域

3860：隧道氧化層

3870、4370、4470：浮動閘

3880：多晶矽層間氧化層

3890、3990：控制閘

3920：源極區域

3930：汲極區域

3970：奈米晶體微粒

3980：閘極氧化層

4020：源極區域

4030：汲極區域

4060：穿隧介電層

4070：捕捉層

4080：阻擋氧化層

4090、4190、4290、4480、4590：控制閘

4010、4110、4310、4410、4510、5610：基板

4120：源極區域

4130：汲極區域

4150：帶隙工程穿隧屏障

4160：電荷補捉介電層

4170：上氧化層

4180：覆蓋層

4220、4230：源極與汲極區域

- 4225：寬度

4250：ONO 堆疊

4295：長度

4320：源極極區域

4330：汲極區域

4390：閘極

4395：隧道氧化層

4425、4473、4493：厚度

4430：汲極區域

4460：隔離間隙

4463：寬度

4475：第二隧道氧化層

4483：寬度

4485：介電層

4490：存取閘極

4493：寬度

4495：第一隧道氧化層

4520：源極區域

4530：汲極區域

4550：位元線

4560：下氧化層

4570：電荷捕捉層

4580：上氧化層

4590：閘極

4632：局部字線

4634：局部字線

4660L、4660R：全域字線

4661L、4661R：全域字線

4662L、4662R：電晶體

4664L、4664R：接觸點

4670L、4770L、4770R、4870L、4870R、4970L、4970R、

5070L、5070R：控制線

4682、4684、4686：單元

4690：共通源極線

4732、4734：局部字線

4760L、4760R：全域字線對

4762L、4762R：電晶體

4764L、4764R：接觸點

4782、4784、4786、4788：單元

4832、4834：局部字線

4862L、4862R：電晶體

4864L、4864R：接觸點

4882、4884、4886：單元

4960L、4960R：全域字線

4962L、4962R：電晶體

4964L、4964R：接觸點

4965、4966：延伸

4967：位元線

4969：字線段

4981、4982、4984、4986、4994：記憶體單元

- 5010：位元線

5048：字線構造

5050：共通源極線

5060L、50560R：全域字線

5062L、5062R：電晶體

5064L、5064R：接觸點

5080：串列選擇電晶體

5081：共通源極電晶體

5090：二極體

5410：導體

5420：字線

5421、5422、5423、5424：箭號

5430：導體

5442、5452、5454、5456：二極體

5510、5530：導體

5522、5524：字線

5542、5544、5546、5548：二極體

5552、5554、5555、5556：二極體

5620：半導體本體

5630：絕緣層

5640：電荷捕捉構造

5650：字線

5662：插塞

5664：縱橫導體

5666、5668：半導體元件

- 5670、5690：導體

5682：插塞

5684：縱橫導體

5686、5688：半導體元件

5721：條帶

5751：字線

5764、5784：縱橫導體

5766、5786：二極體

5770、5790：導體

5800、5801、5802、5803：電流路徑

4420：源極區域

10年2月16日修正本

## 發明專利說明書

公告本

(本說明書格式、順序，請勿任意更動，※記號部分請勿填寫)

※申請案號：101115558

※申請日：101.5.2

※IPC分類：

G11C 16/06 (2006.01)

H01L 27/115 (2006.01)

## 一、發明名稱：(中文/英文)

具有二極體搭接之熱輔助快閃記憶體 / THERMALLY ASSISTED FLASH MEMORY WITH DIODE STRAPPING

## 二、中文發明摘要：

一種記憶體包括一陣列之記憶體單元，其包括數行與數列。記憶體包括電路，其耦接至字線，施加一第一偏壓至於陣列中之一或多條字線上之一第一組隔開的位置，同時施加一不同於第一偏壓之第二偏壓至字線上之一第二組隔開的位置，在第一組隔開的位置中之位置係穿插在第二組隔開的位置中之位置之間，藉以使電流被引發在第一與第二組之位置之間，其導致字線之加熱。

## 三、英文發明摘要：

A memory includes an array of memory cells including rows and columns. The memory includes circuitry coupled to the word lines applying a first bias voltage to a first set of spaced-apart locations on a word line or word lines in the array, while applying a second bias voltage different than the first bias voltage, to a second set of spaced-apart locations on the word line or word lines, locations in the first set of spaced-apart locations being interleaved among locations in the second set of spaced-apart locations, whereby current flow is induced between locations in the first and second sets of locations that cause heating of the word line or word lines.

## 七、申請專利範圍：

1. 一種於一積體電路上之記憶體，包括：

一陣列之記憶體單元，

複數條字線及複數條位元線，耦接至該陣列中之該等記憶體單元；

至少一對的導體，該至少一對包括一第一導體及一第二導體；

一個二極體搭接電路，耦接至該些字線中之一特定字線，該特定字線係透過該些字線，於一第一組隔開的位置耦接至該第一導體，並於一第二組隔開的位置耦接至該第二導體，且在該第二組隔開的位置中之多個位置係為在該第一組之間之穿插位置；及

電路，用於施加偏壓至該至少一對的導體，其在該第一與第二組隔開的位置中之該些位置之間，於該特定字線中引發電流。

2. 如申請專利範圍第1項所述之記憶體，其中該二極體搭接電路包括：

一第一複數個二極體，耦接至該特定字線，於該第一複數個二極體中之二極體具有於該第一組隔開的位置耦接至該特定字線之各自的陽極，及耦接至該第一導體之各自的陰極；及

一第二複數個二極體，耦接至該特定字線，於該第二複數個二極體中之二極體具有於該第二組隔開的位置耦接至該特定字線之各自的陰極，及耦接至該第二導體之各自的陽極。

3. 如申請專利範圍第 1 項所述之記憶體，其中該些字線包括金屬導體。

4. 如申請專利範圍第 1 項所述之記憶體，其中該些字線係配置於一第一層之該積體電路中，而該至少一對的導體係配置於一第二層中，第二層位在該第一層之上或之下，且該二極體搭接電路包括複數個垂直二極體，位在該第一與第二層之間。

5. 如申請專利範圍第 1 項所述之記憶體，其中該些字線係配置於一第一層之該積體電路中，而該至少一對的導體係配置於在該第一層上方之一第二層中，且該二極體搭接電路包括：

一圖案化連接器層，位在該第一與第二層之間，具有一第一連接器及一第二連接器，該第一連接器係於一第一位置配置橫越過複數條字線中之一組字線，而該第二連接器係於一第二位置配置橫越過該組之字線；

一第一組層間連接部，位在該組之字線與該第一連接器之間；以及至少一層間連接部，位在該第一連接器與該第一導體之間；及

一第二組層間連接部，位在該組之字線及該第二連接器之間之通道之內；以及至少一層間連接部，位在該第二連接器及該第二導體之間。

6. 如申請專利範圍第 1 項所述之記憶體，包括控制電路，用於控制該電路以在一區塊抹除之後及與該區塊抹除協調，將引發該電流之偏壓施加至該至少一對的導體。

7. 如申請專利範圍第 1 項所述之記憶體，包括控制

電路，用於控制該電路以施加偏壓至該至少一對的導體，以在讀取、編程及抹除操作之間於時間上穿插地施加引發該電流之偏壓。

8. 如申請專利範圍第 1 項所述之記憶體，包括電路，用於控制該電路以施加偏壓至該至少一對的導體，其中該些偏壓之其中一個係為一負電壓。

9. 如申請專利範圍第 1 項所述之記憶體，包括控制電路，用於維持編程及抹除循環、編程循環或抹除循環之計算，且當該計算達到一門檻值時，用於導致該電路施加偏壓至該至少一對的導體。

10. 如申請專利範圍第 1 項所述之記憶體，其中該陣列係配置成一 NAND 架構。

11. 如申請專利範圍第 1 項所述之記憶體，其中該陣列中之該等記憶體單元包括多個半導體本體，位於一絕緣基板上。

12. 如申請專利範圍第 1 項所述之記憶體，其中該陣列中之該等記憶體單元包括浮動閘快閃記憶體。

13. 如申請專利範圍第 1 項所述之記憶體，其中該陣列中之該等記憶體單元包括多個快閃記憶體單元，其具有多個介電電荷捕捉構造，該介電電荷捕捉構造包括一穿隧層、一電荷捕捉層及一阻擋層，且其中該穿隧層包括少於 2 nm 厚的第一層之氧化矽或氮氧化矽、少於 3 nm 厚的第二層之氮化矽及包括少於 4 nm 厚的氧化矽或氮氧化矽之第三層。

14. 如申請專利範圍第 1 項所述之記憶體，其中在該

些第一與第二複數個該二極體中之至少一個二極體係一為肖基(Schottky)二極體。

15. 一種用於操作一陣列之記憶體單元之方法，包括：施加一第一偏壓至位於該陣列中之一條或多條字線上之一第一組隔開的位置，同時施加不同於該第一偏壓之一第二偏壓至該字線或該些字線上之一第二組隔開的位置，在該第一組隔開的位置中之多個位置係穿插在該第二組隔開的位置中之多個位置之間，藉以使電流被引發在該第一與第二組之位置之多個位置之間，其導致該字線或該些字線之加熱。

16. 如申請專利範圍第 15 項所述之方法，其中第一與第二導體係與該陣列一起配置，並使用一個二極體搭接電路耦接至該字線或該些字線，並包括使用該些第一與第二導體施加該第一與第二偏壓。

17. 如申請專利範圍第 16 項所述之方法，其中該二極體搭接電路包括：

一第一複數個二極體，耦接至一特定字線，在該第一複數個二極體中之多個二極體具有於該第一組隔開的位置耦接至該特定字線之各自的陽極，及耦接至該第一導體之各自的陰極；及

一第二複數個二極體，耦接至該特定字線，在該第二複數個二極體中多個二極體具有於該第二組隔開的位置耦接至該特定字線之各自的陰極，及耦接至該第二導體之各自的陽極，且其中該第一偏壓係低於該第二偏壓。

18. 如申請專利範圍第 15 項所述之方法，其中該字

線或該些字線包括多個金屬導體。

19. 如申請專利範圍第 15 項所述之方法，包括：在一區塊抹除之後及與該區塊抹除協調，施加該些第一與第二偏壓。

20. 如申請專利範圍第 15 項所述之方法，包括：於時間上穿插地施加該些第一與第二偏壓在讀取、編程及抹除操作之間。

21. 如申請專利範圍第 15 項所述之方法，其中，該些第一與第二偏壓之其中一個係為一負電壓。

22. 如申請專利範圍第 15 項所述之方法，包括：維持編程及抹除循環、編程循環或抹除循環之計算，及當該計算達到一門檻值時，施加該些第一與第二偏壓。

23. 如申請專利範圍第 15 項所述之方法，其中該陣列係配置成一 NAND 架構。

24. 如申請專利範圍第 15 項所述之方法，其中該陣列中之該等記憶體單元包括多個半導體本體，位於一絕緣基板上。

25. 如申請專利範圍第 15 項所述之方法，其中該陣列中之該等記憶體單元包括浮動閘快閃記憶體。

26. 如申請專利範圍第 15 項所述之方法，其中該陣列中之該等記憶體單元包括多個快閃記憶體單元，其具有多個介電電荷捕捉構造，該介電電荷捕捉構造包括一穿隧層、一電荷捕捉層及一阻擋層，且其中該穿隧層包括少於 2 nm 厚的第一層之氧化矽或氮氧化矽、少於 3 nm 厚的第二層之氮化矽及包括少於 4 nm 厚的氧化矽或氮氧化矽之

第三層。

27. 如申請專利範圍第 15 項所述之方法，其中在該些第一與第二複數個該二極體中之至少一個二極體係一肖基(Schottky)二極體。

28. 一種用於製造一記憶體於一積體電路上之方法，包括：

形成一陣列之記憶體單元，其包括多行與多列，其包括沿著該些列之多條字線；及

形成一個二極體搭接電路，其耦接至複數條字線中之一特定字線，該特定字線係透過該些字線，於一第一組隔開的位置耦接至一第一導體，及在一第二組隔開的位置耦接至一第二導體，且在該第二組隔開的位置中之多個位置係為在該第一組之間之穿插位置；及

形成電路，其耦接至該二極體搭接電路，用於連接偏壓至該至少一對的導體，其在該第一與第二組隔開的位置中之該些位置之間之該特定字線中引發電流。

29. 如申請專利範圍第 28 項所述之方法，其中形成該二極體搭接電路包括：

形成一第一複數個二極體，其耦接至該特定字線，在該第一複數個二極體中之多個二極體具有於該第一組隔開的位置耦接至該特定字線之各自的陽極，以及耦接至該第一導體之各自的陰極；及

形成一第二複數個二極體，其耦接至該特定字線，在該第二複數個二極體中之多個二極體具有於該第二組隔開的位置耦接至該特定字線之各自的陰極，及耦接至該第

二導體之各自的陽極。

30. 如申請專利範圍第 28 項所述之方法，其中該些字線包括多個金屬導體。

31. 如申請專利範圍第 28 項所述之方法，包括：配置該些字線於一第一層之該積體電路中，及配置該至少一對的導體於一第二層中，該第二層位在該第一層之上或之下，且該二極體搭接電路包括複數個垂直二極體，位在該第一與第二層之間。

32. 如申請專利範圍第 28 項所述之方法，其中該些字線係配置於一第一層之該積體電路中，而該至少一對的導體係配置於在該第一層上方之一第二層中，且形成該二極體搭接電路之步驟包括：

形成一圖案化連接器層在該第一與第二層之間，其具有一第一連接器及一第二連接器，該第一連接器係於一第一位置配置橫越過複數條字線中之一組字線，而該第二連接器係於一第二位置配置橫越過該組之字線；

形成一第一組層間連接部在該組之字線與該第一連接器之間，以及至少一層間連接部在該第一連接器與該第一導體之間；及

形成一第二組層間連接部在該組之字線及該第二連接器之間之通道之內，及至少一層間連接部分在該第二連接器及該第二導體之間。

33. 如申請專利範圍第 28 項所述之方法，包括形成一絕緣基板，且其中形成該陣列之步驟包括形成多個半導體本體於該絕緣基板上。

34. 如申請專利範圍第 28 項所述之方法，其中在該些第一與第二複數個該二極體中之至少一個二極體係為一肖基(Schottky)二極體。

四、指定代表圖：

(一)本案指定代表圖為：第（4）圖。

(二)本代表圖之元件符號簡單說明：

410：積體電路

412：記憶體陣列

414：解碼器

416：字線

417：局部字線解碼器

418：位元線解碼器

420：位元線

422：匯流排

424：感測放大器與資料輸入構造

426：資料匯流排

428：資料輸入線

430：電路

432：資料輸出線

434：控制器

436：偏壓配置電源電壓與電流源

450：字線終端解碼器

五、本案若有化學式時，請揭示最能顯示發明特徵的化學式：

無