(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3744826号

(P3744826)

(45) 発行日 平成18年2月15日(2006.2.15)

(24) 登録日 平成17年12月2日(2005.12.2)

(51) Int.C1.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b>  |             |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>550</b>  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>611A</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>621E</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>622K</b> |

請求項の数 14 (全 56 頁) 最終頁に続く

(21) 出願番号

特願2001-278735 (P2001-278735)

(22) 出願日

平成13年9月13日 (2001.9.13)

(65) 公開番号

特開2003-58130 (P2003-58130A)

(43) 公開日

平成15年2月28日 (2003.2.28)

審査請求日 平成16年2月5日 (2004.2.5)

(31) 優先権主張番号

特願2001-168517 (P2001-168517)

(32) 優先日

平成13年6月4日 (2001.6.4)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100090387

弁理士 布施 行夫

(74) 代理人 100090398

弁理士 大渕 美千栄

(72) 発明者 森田 晶

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 濱本 穎広

最終頁に続く

(54) 【発明の名称】表示制御回路、電気光学装置、表示装置及び表示制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに交差する第1～第N (Nは、自然数)の走査ライン及び第1～第M (Mは、自然数)の信号ラインにより特定される画素を有する電気光学装置の表示制御を行う表示制御回路であって、

所与の複数の信号ライン及び所与の複数の走査ラインごとに分割されたエリアブロックを単位として、表示エリア若しくは非表示エリアを指定するためのエリアブロック表示制御データを記憶するエリアブロック表示制御データ記憶手段と、

第1～第Nの走査ラインのうち少なくとも表示エリアに対応する走査ラインを順次走査駆動する走査駆動回路に対して、前記エリアブロック表示制御データに基づいて、表示エリア若しくは非表示エリアを前記エリアブロック単位で設定する走査駆動回路設定手段と、

第1～第Mの信号ラインのうち表示エリアに対応する信号ラインを信号駆動する信号駆動回路に対して、前記エリアブロック表示制御データに基づいて、表示エリア若しくは非表示エリアを前記エリアブロック単位で設定する信号駆動回路設定手段と、

前記第1～第Nの走査ラインのうち、前記表示エリアに対応する走査ラインである表示走査ラインは、毎フレーム周期で走査駆動すると共に、前記第1～第Nの走査ラインのうち、前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に所与の3以上の奇数フレーム周期で走査駆動するように、前記走査駆動回路を制御する手段とを含み、

前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする表示制御回路。

**【請求項 2】**

請求項 1 において、

所与の複数の走査ラインごとに分割されたラインブロックを単位として、表示エリア若しくは非表示エリアを指定するための帯パーシャル表示制御データを保持する帯パーシャル表示制御データ保持手段と、

第 1 のモードと第 2 のモードとを切り替えるためのモード切替手段と、

を含み、

前記第 1 のモードでは、

前記エリアブロック表示制御データに基づいて、前記走査駆動回路及び前記信号駆動回路に対し表示エリア若しくは非表示エリアを前記エリアブロック単位で設定し、

前記第 2 のモードでは、

前記帯パーシャル表示制御データに基づいて、前記走査駆動回路に対し表示エリア若しくは非表示エリアを前記ラインブロック単位で設定することを特徴とする表示制御回路。

**【請求項 3】**

互いに交差する第 1 ~ 第 N の走査ライン及び第 1 ~ 第 M の信号ラインにより特定される画素を有する電気光学装置の表示制御を行う表示制御回路であって、

所与の複数の走査ラインごとに分割されたエリアブロックを単位として、表示エリア若しくは非表示エリアを指定するための帯パーシャル表示制御データを保持する帯パーシャル表示データ保持手段と、

第 1 ~ 第 N の走査ラインを走査駆動する走査駆動回路に対して、前記帯パーシャル表示制御データに基づいて、表示エリア若しくは非表示エリアを前記エリアブロック単位で設定する走査駆動回路設定手段と、

前記第 1 ~ 第 N の走査ラインのうち、前記表示エリアに対応する走査ラインである表示走査ラインは、毎フレーム周期で走査駆動すると共に、前記第 1 ~ 第 N の走査ラインのうち、前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に所与の 3 以上の奇数フレーム周期で走査駆動するように、前記走査駆動回路を制御する手段とを含み、

前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする表示制御回路。

**【請求項 4】**

互いに交差する第 1 ~ 第 N の走査ライン及び第 1 ~ 第 M の信号ラインにより特定される画素を有する電気光学装置の表示制御を行う表示制御回路であって、

前記第 1 ~ 第 N の走査ラインを走査駆動する走査駆動回路に対して表示エリア若しくは非表示エリアを設定する手段と、

前記第 1 ~ 第 N の走査ラインのうち少なくともその一部が前記表示エリアに含まれる走査ラインである表示走査ラインは、毎フレーム周期で走査駆動し、前記第 1 ~ 第 N の走査ラインのうち前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に 3 以上の奇数フレーム周期で走査駆動するように、前記走査駆動回路を制御する手段と、

を含み、

前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする表示制御回路。

**【請求項 5】**

請求項 1 乃至 4 のいずれかにおいて、

前記所与の表示制御イベントが発生したフレームにおける前記表示制御イベントの発生以降の少なくとも 1 走査期間において、前記非表示走査ラインを走査駆動するように制御することを特徴とする表示制御回路。

**【請求項 6】**

10

20

30

40

50

請求項 1 乃至 5 のいずれかにおいて、

前記所与の表示制御イベントは、表示エリア若しくは非表示エリアの生成、消滅、移動及びサイズ変更のうち少なくとも 1 つに基づいて発生するイベントであることを特徴とする表示制御回路。

【請求項 7】

互いに交差する第 1 ~ 第 N の走査ライン及び第 1 ~ 第 M の信号ラインにより特定される画素と、

第 1 ~ 第 N の走査ラインを走査駆動する走査駆動回路と、

画像データに基づいて第 1 ~ 第 M の信号ラインを駆動する信号駆動回路と、

請求項 1 乃至 6 のいずれか記載の表示制御回路と、

を含むことを特徴とする電気光学装置。

10

【請求項 8】

請求項 7 において、

前記信号駆動回路は、

前記所与の複数の信号ラインごとに分割されたラインブロックを単位として、信号駆動するか否かを指定するためのブロック出力選択データを保持するブロック出力選択データ保持手段と、

前記所与の複数の信号ラインごとに分割されたラインブロックを単位として、表示エリア若しくは非表示エリアを指定するためのパーシャル表示データを保持するパーシャル表示データ保持手段と、

20

前記ブロック出力選択データにより信号駆動しないように指定されたラインブロックの信号ラインへの出力をハイインピーダンス状態にし、前記ブロック出力選択データにより信号駆動するように指定されたラインブロックの信号ラインに対し、前記パーシャル表示データに基づき、画像データに応じた信号駆動若しくは所与の非表示レベル電圧の供給のいずれかを行う信号ライン駆動手段と、

を有し、

前記表示制御回路は、

前記ブロック出力選択データを、前記信号駆動回路のブロック出力選択データ保持手段に設定するブロック出力選択データ設定手段と、

30

前記ラインブロックを単位として表示エリア若しくは非表示エリアを指定する第 1 のパーシャル表示データにより、表示エリアに指定された第 P ( P は、自然数 ) のブロックが、前記ブロック出力選択データにより信号駆動しないブロックとして指定されたときに、前記第 1 のパーシャル表示データを、第 P のブロックのデータを第 ( P + 1 ) のブロックのデータとしてシフトした第 2 のパーシャル表示データに変換するパーシャル表示データ変換手段と、

第 2 のパーシャル表示データを、前記信号駆動回路のパーシャル表示データ保持手段に設定するパーシャル表示データ設定手段と、

を含むことを特徴とする電気光学装置。

【請求項 9】

請求項 8 において、

40

前記所与の複数の信号ラインごとに分割されたラインブロックを単位として、表示エリア若しくは非表示エリアを指定する第 1 のパーシャル表示データにより、表示エリアに指定された第 P のブロックが、前記ブロック出力選択データにより信号駆動しないブロックとして指定されたときに、前記信号駆動回路に供給される第 1 の画像データを、第 1 の画像データのうち第 P のブロックに対応する画像データを第 ( P + 1 ) のブロックの画像データとしてシフトした第 2 の画像データを生成する画像データ生成手段と、

前記第 2 の画像データを、前記信号駆動回路に対して供給する画像データ供給手段と、を含むことを特徴とする電気光学装置。

【請求項 10】

互いに交差する第 1 ~ 第 N の走査ライン及び第 1 ~ 第 M の信号ラインにより特定される

50

画素を有する電気光学装置と、

第1～第Nの走査ラインを走査駆動する走査駆動回路と、

画像データに基づいて第1～第Mの信号ラインを駆動する信号駆動回路と、

請求項1乃至6のいずれか記載の表示制御回路と、

を含むことを特徴とする表示装置。

【請求項11】

互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置を表示制御するための表示制御方法であって、

所与の複数の信号ラインごとに分割されたラインブロックを単位として指定された第1～第Mの信号ラインを信号駆動する信号駆動回路と、所与の複数の走査ラインごとに分割されたラインブロックを単位として指定された第1～第Nの走査ラインを順次走査駆動する走査駆動回路とに対し、それぞれのラインブロック単位で表示エリア若しくは非表示エリアを設定し、10

表示エリアに対応する画像データを、前記信号駆動回路に対して供給し、

前記画像データに基づいて表示駆動する場合に、

非表示エリアに設定されたラインブロックの信号ラインに対し、所与の非表示レベル電圧を供給し、表示エリアに設定されたラインブロックの信号ラインを、前記画像データに応じた駆動電圧で信号駆動し、

表示エリアに設定されたラインブロックの走査ラインを、毎フレーム周期で走査駆動し、非表示エリアに設定されたラインブロックの走査ラインを、所与の基準フレームを基準に所与の3以上の奇数フレーム周期で駆動し、20

前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする表示制御方法。

【請求項12】

互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置を表示制御するための表示制御方法であって、

前記画素の領域に、表示エリア若しくは非表示エリアを設定し、

前記第1～第Nの走査ラインのうち少なくともその一部が前記表示エリアに含まれる走査ラインである表示走査ラインは、毎フレーム周期で走査駆動し、前記第1～第Nの走査ラインのうち前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に所与の3以上の奇数フレーム周期で走査駆動し、30

前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする表示制御方法。

【請求項13】

請求項11又は12において、

前記所与の表示制御イベントが発生したフレームにおける前記表示制御イベントの発生以降の少なくとも1走査期間において、前記非表示エリアに設定されたラインブロックの走査ラインを走査駆動することを特徴とする表示制御方法。

【請求項14】

請求項11乃至13のいずれかにおいて、40

前記所与の表示制御イベントは、表示エリア若しくは非表示エリアの生成、消滅、移動及びサイズ変更のうち少なくとも1つに基づいて発生するイベントであることを特徴とする表示制御方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、表示制御回路、これを用いた電気光学装置、表示装置及び表示制御方法に関する。

【0002】

【背景技術及び発明が解決しようとする課題】50

例えば携帯電話機のような電子機器の表示部には、液晶パネルが用いられており、電子機器の低消費電力化や小型軽量化等が図られている。この液晶パネルについては、近年の携帯電話機の普及によって情報性の高い静止画や動画が配信されるようになると、その高画質化が要求されるようになっている。

#### 【0003】

このような電子機器の表示部の高画質化を実現する液晶パネルとして、薄膜トランジスタ(Thin Film Transistor: 以下、TFTと略す。)液晶を用いたアクティブマトリクス型液晶パネルが知られている。TFT液晶を用いたアクティブマトリクス型液晶パネルは、ダイナミック駆動によるSTN(SuperTwisted Nematic)液晶を用いた単純マトリクス型液晶パネルに比べて、高速応答、高コントラストを実現し、動画等の表示に適している。

10

#### 【0004】

しかしながら、TFT液晶を用いたアクティブマトリクス型液晶パネルは、消費電力が大きく、携帯電話機のようなバッテリ駆動が行われる携帯型の電子機器の表示部として採用することが困難とされている。したがって、アクティブマトリクス型液晶パネルの低消費電力化が実現できれば、非常に有用なものとなる。その際、アクティブマトリクス型液晶パネルの画質の品位をできるだけ低下させないことが望ましい。

#### 【0005】

本発明は以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、高画質化と低消費電力化とを両立させ、アクティブマトリクス型液晶パネルに好適な表示制御回路、これを用いた電気光学装置、表示装置及び表示制御方法を提供することにある。

20

#### 【0006】

##### 【課題を解決するための手段】

上記課題を解決するために本発明は、互いに交差する第1～第N(Nは、自然数)の走査ライン及び第1～第M(Mは、自然数)の信号ラインにより特定される画素を有する電気光学装置の表示制御を行う表示制御回路であって、所与の複数の信号ライン及び所与の複数の走査ラインごとに分割されたエリアブロックを単位として、表示エリア若しくは非表示エリアを指定するためのエリアブロック表示制御データを記憶するエリアブロック表示制御データ記憶手段と、第1～第Nの走査ラインのうち少なくとも表示エリアに対応する走査ラインを順次走査駆動する走査駆動回路に対して、前記エリアブロック表示制御データに基づいて、表示エリア若しくは非表示エリアを前記エリアブロック単位で設定する走査駆動回路設定手段と、第1～第Mの信号ラインのうち表示エリアに対応する信号ラインを信号駆動する信号駆動回路に対して、前記エリアブロック表示制御データに基づいて、表示エリア若しくは非表示エリアを前記エリアブロック単位で設定する信号駆動回路設定手段とを含むことを特徴とする。

30

#### 【0007】

ここで、電気光学装置としては、例えば互いに交差する複数の走査ライン及び複数の信号ラインと、前記走査ラインと前記信号ラインに接続されたスイッチング手段と、前記スイッチング手段に接続された画素電極とを有するように構成しても良い。

#### 【0008】

40

また、エリアブロックとは、所与の複数の走査ラインごとに分割されたラインブロックと、所与の複数の信号ラインごとに分割されたラインブロックとにより特定されるブロックをいう。ラインブロック単位に分割される走査ラインは、互いに隣接した複数の走査ラインであっても良いし、任意に選択された複数の走査ラインであっても良い。また、ラインブロック単位に分割される信号ラインは、互いに隣接した複数の信号ラインであっても良いし、任意に選択された複数の信号ラインであっても良い。

#### 【0009】

本発明においては、エリアブロック表示制御データ記憶手段を備え、エリアブロック単位で表示エリア若しくは非表示エリアを指定し、信号駆動回路設定手段又は走査駆動回路設定手段により、信号駆動回路又は走査駆動回路に対し、それぞれラインブロック単位で表

50

示エリア若しくは非表示エリアを設定できるようにした。したがって、表示エリアのみを駆動することで、非表示エリアの駆動に伴なう消費電力分の削減が可能となるパーシャル表示制御を行う場合に、ピクセル単位で表示エリアを設定する場合に比べて、メモリ容量を大幅に削減し、簡素な構成で、低消費化を図ることができる。

#### 【0010】

また本発明に係る表示制御回路は、所与の複数の走査ラインごとに分割されたラインブロックを単位として、表示エリア若しくは非表示エリアを指定するための帯パーシャル表示制御データを保持する帯パーシャル表示制御データ保持手段と、第1のモードと第2のモードとを切り替えるためのモード切替手段とを含み、前記第1のモードでは、前記エリアブロック表示制御データに基づいて、前記走査駆動回路及び前記信号駆動回路に対し表示エリア若しくは非表示エリアを前記エリアブロック単位で設定し、前記第2のモードでは、前記帯パーシャル表示制御データに基づいて、前記走査駆動回路に対し表示エリア若しくは非表示エリアを前記ラインブロック単位で設定することを特徴とする。10

#### 【0011】

本発明によれば、さらに帯パーシャル表示制御データ保持手段を備え、帯パーシャル表示制御データに基づいて、走査ラインをラインブロック単位で表示エリア若しくは非表示エリアを設定するようにしたので、走査ライン方向のパーシャル表示制御に必要なメモリ容量を削減したパーシャル表示制御を行うことができるようになる。

#### 【0012】

また本発明に係る表示制御回路は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置の表示制御を行う表示制御回路であって、所与の複数の走査ラインごとに分割されたエリアブロックを単位として、表示エリア若しくは非表示エリアを指定するための帯パーシャル表示制御データを保持する帯パーシャル表示データ保持手段と、第1～第Nの走査ラインを走査駆動する走査駆動回路に対して、前記帯パーシャル表示制御データに基づいて、表示エリア若しくは非表示エリアを前記エリアブロック単位で設定する走査駆動回路設定手段とを含むことを特徴とする。20

#### 【0013】

本発明によれば、帯パーシャル表示制御データ保持手段を備え、帯パーシャル表示制御データに基づいて、走査ラインをエリアブロック単位で表示エリア若しくは非表示エリアを設定するようにしたので、走査ライン方向のパーシャル表示制御に必要なメモリ容量を削減し、低消費化が可能な表示エリア及び非表示エリアの設定の簡素化を図ることができる。30

#### 【0014】

また本発明に係る表示制御回路は、前記第1～第Nの走査ラインのうち、前記表示エリアに対応する走査ラインである表示走査ラインは、毎フレーム周期で走査駆動し、前記第1～第Nの走査ラインのうち、前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に所与の3以上の奇数フレーム周期で走査駆動するよう、前記走査駆動回路を制御する手段を含むことを特徴とする。

#### 【0015】

ここで、所与の基準フレームを基準に所与の3以上の奇数フレーム周期とは、所与の基準フレームを0フレームとしたときに、3フレーム目、5フレーム目、・・・、(2k+1) (kは、自然数)フレーム目を最終フレームとする周期をいう。40

#### 【0016】

なお、低消費電力化の観点では、非表示走査ラインが走査駆動されるフレーム周期は長ければ長いほど望ましい。

#### 【0017】

本発明によれば、表示エリアについては毎フレーム周期で走査駆動するが、非表示エリアについては3以上の奇数フレーム周期で走査駆動するため、極性反転駆動方式に対応するとともに、例えばTFTのリーケによる弊害を防止し、不要な走査駆動の削減による消費50

電力の低減が可能となる。

【0018】

また本発明は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置の表示制御を行う表示制御回路であって、前記第1～第Nの走査ラインを走査駆動する走査駆動回路に対して表示エリア若しくは非表示エリアを設定する手段と、前記第1～第Nの走査ラインのうち少なくともその一部が前記表示エリアに含まれる走査ラインである表示走査ラインは、毎フレーム周期で走査駆動し、前記第1～第Nの走査ラインのうち前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に3以上の奇数フレーム周期で走査駆動するよう10に、前記走査駆動回路を制御する手段とを含むことを特徴とする。

【0019】

本発明によれば、パーシャル表示制御が行われる場合に、表示エリアについては毎フレーム周期で走査駆動するが、非表示エリアについては、3以上の奇数フレーム周期で走査駆動するため、極性反転駆動方式に対応しながら、例えばTFTのリークによる弊害を防止し、不要な走査駆動の削減による消費電力の低減が可能となる。

【0020】

また本発明に係る表示制御回路は、前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする。

【0021】

本発明によれば、所与の表示制御イベントの発生により、それまでの表示エリア若しくは非表示エリアが変更になって、例えば非表示エリアが一瞬暗くなったりする表示品位の低下を回避することができる。20

【0022】

また本発明に係る表示制御回路は、前記所与の表示制御イベントが発生したフレームにおける前記表示制御イベントの発生以降の少なくとも1走査期間において、前記非表示走査ラインを走査駆動するように制御することを特徴とする。

【0023】

本発明によれば、表示制御イベントが発生した当該フレームにおいて、その発生タイミング以降、少なくとも1走査期間は、非表示走査ラインを走査駆動するようにしたので、該イベントの発生に伴う表示品位の低下が目立たなくすることができる。30

【0024】

また本発明に係る表示制御回路は、前記所与の表示制御イベントは、表示エリア若しくは非表示エリアの生成、消滅、移動及びサイズ変更のうち少なくとも1つに基づいて発生するイベントであることを特徴とする。

【0025】

本発明によれば、ウィンドウの生成、消滅、移動及びサイズ変更のいずれかによる表示品位の低下を防止することができる。

【0026】

また本発明に係る電気光学装置は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素と、第1～第Nの走査ラインを走査駆動する走査駆動回路と、画像データに基づいて第1～第Mの信号ラインを駆動する信号駆動回路と、上記いずれか記載の表示制御回路とを含むことを特徴とする。40

【0027】

本発明によれば、低消費化を実現できるパーシャル表示制御に伴なうメモリ容量を削減し、表示エリア若しくは非表示エリアの指定の簡素化を図ることができる電気光学装置を提供することができる。したがって、低消費化を図る電気光学装置の低コスト化を実現することができる。

【0028】

また本発明に係る電気光学装置は、前記信号駆動回路は、前記所与の複数の信号ラインごとに分割されたラインブロックを単位として、信号駆動するか否かを指定するためのプロ50

ック出力選択データを保持するブロック出力選択データ保持手段と、前記所与の複数の信号ラインごとに分割されたラインプロックを単位として、表示エリア若しくは非表示エリアを指定するためのパーシャル表示データを保持するパーシャル表示データ保持手段と、前記ブロック出力選択データにより信号駆動しないように指定されたラインプロックの信号ラインへの出力をハイインピーダンス状態にし、前記ブロック出力選択データにより信号駆動するように指定されたラインプロックの信号ラインに対し、前記パーシャル表示データに基づき、画像データに応じた信号駆動若しくは所与の非表示レベル電圧の供給のいずれかを行う信号ライン駆動手段とを有し、前記表示制御回路は、前記ブロック出力選択データを、前記信号駆動回路のブロック出力選択データ保持手段に設定するブロック出力選択データ設定手段と、前記ラインプロックを単位として表示エリア若しくは非表示エリアを指定する第1のパーシャル表示データにより、表示エリアに指定された第P（Pは、自然数）のブロックが、前記ブロック出力選択データにより信号駆動しないブロックとして指定されたときに、前記第1のパーシャル表示データを、第Pのブロックのデータを第（P+1）のブロックのデータとしてシフトした第2のパーシャル表示データに変換するパーシャル表示データ変換手段と、第2のパーシャル表示データを、前記信号駆動回路のパーシャル表示データ保持手段に設定するパーシャル表示データ設定手段とを含むことを特徴とする。10

#### 【0029】

本発明においては、信号駆動回路において、ブロック出力選択データにより、ラインプロックを単位に信号駆動しないように指定されたラインプロックの信号ラインへの出力をハイインピーダンス状態にし、信号駆動するように指定されたラインプロックの信号ラインに対し、パーシャル表示データに基づき、画像データに応じた信号駆動若しくは所与の非表示レベル電圧の供給のいずれかを行う場合に、表示制御回路にパーシャル表示データ変換手段を設けるようにした。このパーシャル表示変換手段は、ラインプロック単位に表示エリア若しくは非表示エリアを指定する第1のパーシャル表示データにおいて、表示エリアに指定された第Pのブロックが、ブロック出力選択データにより信号駆動しないブロックとして指定されたときに、第1のパーシャル表示データを、第Pのブロックのデータを第（P+1）のブロックのデータとしてシフトした第2のパーシャル表示データに変換する。20

#### 【0030】

こうすることで、ブロック出力選択データにより、表示パネルのパネルサイズの変化に容易に対応できる信号駆動回路を提供することができるという効果に加え、第1のパーシャル表示データを画像データに合わせて指定する場合に、ブロック出力選択データの設定値を考慮する必要がなくなり、例えばユーザの使い勝手を向上させることができる。30

#### 【0031】

また本発明に係る電気光学装置は、前記所与の複数の信号ラインごとに分割されたラインプロックを単位として、表示エリア若しくは非表示エリアを指定する第1のパーシャル表示データにより、表示エリアに指定された第Pのブロックが、前記ブロック出力選択データにより信号駆動しないブロックとして指定されたときに、前記信号駆動回路に供給される第1の画像データを、第1の画像データのうち第Pのブロックに対応する画像データを第（P+1）のブロックの画像データとしてシフトした第2の画像データを生成する画像データ生成手段と、前記第2の画像データを、前記信号駆動回路に対して供給する画像データ供給手段とを含むことを特徴とする。40

#### 【0032】

本発明においては、画像データ生成手段を備え、ラインプロックを単位として、表示エリア若しくは非表示エリアを指定する第1のパーシャル表示データにより、表示エリアに指定された第Pのブロックが、ブロック出力選択データにより信号駆動しないブロックとして指定されたときに、第1の画像データを、第1の画像データのうち第Pのブロックに対応する画像データを第（P+1）のブロックの画像データとしてシフトした第2の画像データを生成し、この第2の画像データを信号駆動回路に対して供給するようにした。これ50

により、ブロック出力選択データにより、表示パネルのパネルサイズの変化に容易に対応できる信号駆動回路に対しても、信号駆動するラインブロックとして指定されたラインブロックの信号ラインに対してのみ第2の画像データを供給することができるので、画像を作成する側、例えばユーザにとって、ブロック出力選択データの設定値を考慮する必要がなくなる。

#### 【0033】

また本発明に係る表示装置は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置と、第1～第Nの走査ラインを走査駆動する走査駆動回路と、画像データに基づいて第1～第Mの信号ラインを駆動する信号駆動回路と、上記記載の表示制御回路とを含むことを特徴とする。

10

#### 【0034】

本発明によれば、低消費化を実現できるパーシャル表示制御に伴なうメモリ容量を削減し、表示エリア若しくは非表示エリアの指定の簡素化を図ることができる表示装置を提供することができる。したがって、低消費化を図る表示装置の低コスト化を実現することができる。

#### 【0035】

また本発明は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置を表示制御するための表示制御方法であって、所与の複数の信号ライン及び所与の複数の走査ラインごとに分割されたエリアブロックを単位として、表示エリア若しくは非表示エリアを指定するためのエリアブロック表示制御データを記憶し、第1～第Nの走査ラインを走査駆動する走査駆動回路と、第1～第Mの信号ラインを信号駆動する信号駆動回路とに対し、前記エリアブロック表示制御データに基づいて表示エリア若しくは非表示エリアを前記エリアブロック単位で設定することを特徴とする。

20

#### 【0036】

本発明によれば、エリアブロック単位で表示エリア若しくは非表示エリアを指定するエリアブロック表示制御データに基づいて、信号駆動回路又は走査駆動回路に対し、それぞれラインブロック単位で表示エリア若しくは非表示エリアを設定できるようにした。したがって、表示エリアのみを駆動することで、非表示エリアの駆動に伴なう消費電力分の削減が可能となるパーシャル表示制御を行う場合に、ピクセル単位で表示エリアを設定する場合に比べて、メモリ容量を大幅に削減し、簡素な構成で、低消費化を図ることができる。

30

#### 【0037】

また本発明に係る表示制御方法は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置を表示制御するための表示制御方法であって、所与の複数の走査ラインごとに分割されたラインブロックを単位として、表示エリア若しくは非表示エリアを指定するための帯パーシャル表示制御データを保持し、第1～第Nの走査ラインを走査駆動する走査駆動回路に対して、前記帯パーシャル表示制御データに基づいて、表示エリア若しくは非表示エリアを前記ラインブロック単位で設定することを特徴とする。

#### 【0038】

40

本発明によれば、帯パーシャル表示制御データに基づいて、走査ラインをエリアブロック単位で表示エリア若しくは非表示エリアを設定するようにしたので、走査ライン方向のパーシャル表示制御に必要なメモリ容量を削減し、低消費化が可能な表示エリア及び非表示エリアの設定の簡素化を図ることができる。

#### 【0039】

また本発明は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置を表示制御するための表示制御方法であって、所与の複数の信号ラインごとに分割されたラインブロックを単位として指定された第1～第Mの信号ラインを信号駆動する信号駆動回路と、所与の複数の走査ラインごとに分割されたラインブロックを単位として指定された第1～第Nの走査ラインを順次走査駆動する走

50

査駆動回路とに対し、それぞれのラインブロック単位で表示エリア若しくは非表示エリアを設定し、表示エリアに対応する画像データを、前記信号駆動回路に対して供給することを特徴とする。

【0040】

本発明によれば、信号駆動回路及び走査駆動回路に対して、それぞれ複数のラインごとに分割されたラインブロック単位で、表示エリア若しくは非表示エリアを設定した後、表示エリアに表示させるための画像データを供給して表示駆動制御を行うようにしたので、非表示エリアの信号駆動に伴なう電力消費を低減するパーシャル表示制御を行うことができる。

【0041】

また本発明に係る表示制御方法は、前記画像データに基づいて表示駆動する場合に、非表示エリアに設定されたラインブロックの信号ラインに対し、所与の非表示レベル電圧を供給し、表示エリアに設定されたラインブロックの信号ラインを、前記画像データに応じた駆動電圧で信号駆動し、表示エリアに設定されたラインブロックの走査ラインを、順次走査駆動し、非表示エリアに設定されたラインブロックの走査ラインを、所与の3以上の奇数フレーム周期で駆動することを特徴とする。

【0042】

本発明によれば、非表示エリアに設定されたラインブロックの走査ラインを、3以上の奇数フレーム周期で走査駆動するようにしたので、例えば電気光学装置として、例えばTFTを用いた液晶パネルを用いた場合に、これまで消費電力が大きく、TFTのリーケによってダイナミックなパーシャル表示ができなかった問題点を解消し、画質の高品位と、低消費化とを両立させる表示制御方法を提供することができる。

【0043】

また本発明は、互いに交差する第1～第Nの走査ライン及び第1～第Mの信号ラインにより特定される画素を有する電気光学装置を表示制御するための表示制御方法であって、前記画素の領域に、表示エリア若しくは非表示エリアを設定し、前記第1～第Nの走査ラインのうち少なくともその一部が前記表示エリアに含まれる走査ラインである表示走査ラインは、毎フレーム周期で走査駆動し、前記第1～第Nの走査ラインのうち前記表示走査ラインを除く走査ラインである非表示走査ラインは、所与の基準フレームを基準に所与の3以上の奇数フレーム周期で走査駆動することを特徴とする。

【0044】

本発明によれば、パーシャル表示制御が行われる場合に、表示エリアについては毎フレーム周期で走査駆動するが、非表示エリアについては、3以上の奇数フレーム周期で走査駆動するため、極性反転駆動方式に対応しながら、例えばTFTのリーケによる弊害を防止し、不要な走査駆動の削減による消費電力の低減が可能となる。

【0045】

また本発明に係る表示制御方法は、前記所与の基準フレームは、所与の表示制御イベントが発生したフレームの次のフレームであることを特徴とする。

【0046】

本発明によれば、所与の表示制御イベントの発生により、それまでの表示エリア若しくは非表示エリアが変更になって、例えば非表示エリアが一瞬暗くなったりする表示品位の低下を回避することができる。

【0047】

また本発明に係る表示制御方法は、前記所与の表示制御イベントが発生したフレームにおける前記表示制御イベントの発生以降の少なくとも1走査期間において、前記非表示走査ラインを走査駆動することを特徴とする。

【0048】

本発明によれば、表示制御イベントが発生した当該フレームにおいて、その発生タイミング以降、少なくとも1走査期間は、非表示走査ラインを走査駆動するようにしたので、該イベントの発生に伴う表示品位の低下が目立たなくすることができる。

10

20

20

30

40

50

## 【0049】

また本発明に係る表示制御方法は、前記所与の表示制御イベントは、表示エリア若しくは非表示エリアの生成、消滅、移動及びサイズ変更のうち少なくとも1つに基づいて発生するイベントであることを特徴とする。

## 【0050】

本発明によれば、ウィンドウの生成、消滅、移動及びサイズ変更のいずれかによる表示品位の低下を防止することができる。

## 【0051】

## 【発明の実施の形態】

以下、本発明の好適な実施の形態について図面を用いて詳細に説明する。

10

## 【0052】

## 1. 表示装置

## 1.1 表示装置の構成

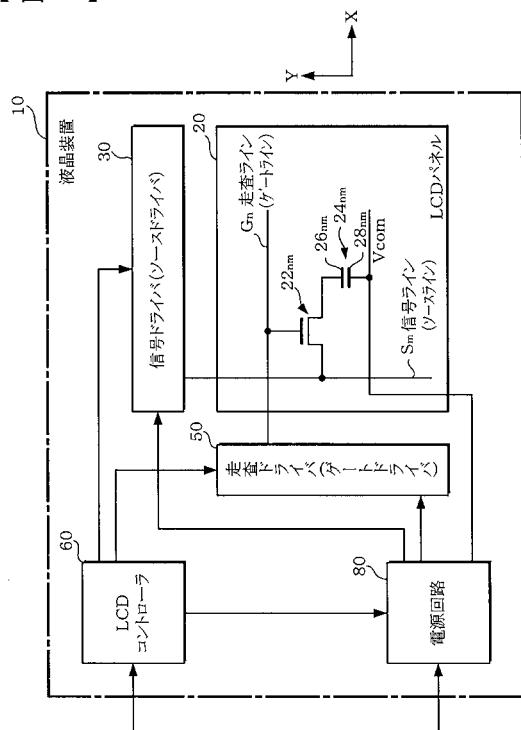

図1に、本実施形態における表示制御回路（LCDコントローラ、表示コントローラ）を適用した表示装置の構成の概要を示す。

## 【0053】

表示装置としての液晶装置10は、液晶ディスプレイ（Liquid Crystal Display：以下、LCDと略す。）パネル20、信号ドライバ（信号駆動回路）（狭義には、ソースドライバ）30、走査ドライバ（走査駆動回路）（狭義には、ゲートドライバ）50、LCDコントローラ60、電源回路80を含む。

20

## 【0054】

LCDパネル（広義には、電気光学装置）20は、例えばガラス基板上に形成される。このガラス基板上には、Y方向に複数配列されそれぞれX方向に伸びる走査ライン（狭義には、ゲートライン） $G_1 \sim G_N$ （Nは、2以上の自然数）と、X方向に複数配列されそれぞれY方向に伸びる信号ライン（狭義には、ソースライン） $S_1 \sim S_M$ （Mは、2以上の自然数）とが配置されている。また、走査ライン $G_n$ （1  $\leq n \leq N$ 、nは自然数）と信号ライン $S_m$ （1  $\leq m \leq M$ 、mは自然数）との交差点に対応して、TFT $22_{nm}$ （広義には、スイッチング手段）が設けられている。

## 【0055】

TFT $22_{nm}$ のゲート電極は、走査ライン $G_n$ に接続されている。TFT $22_{nm}$ のソース電極は、信号ライン $S_m$ に接続されている。TFT $22_{nm}$ のドレイン電極は、液晶容量（広義には液晶素子） $24_{nm}$ の画素電極 $26_{nm}$ に接続されている。

30

## 【0056】

液晶容量 $24_{nm}$ においては、画素電極 $26_{nm}$ に対向する対向電極 $28_{nm}$ との間に液晶が封入されて形成され、これら電極間の印加電圧に応じて画素の透過率が変化するようになっている。

## 【0057】

対向電極 $28_{nm}$ には、電源回路80により生成された対向電極電圧 $V_{com}$ が供給されている。

## 【0058】

40

信号ドライバ30は、一水平走査単位の画像データに基づいて、LCDパネル20の信号ライン $S_1 \sim S_M$ を駆動する。

## 【0059】

走査ドライバ50は、一垂直走査期間内に、水平同期信号に同期して、LCDパネル20の走査ライン $G_1 \sim G_N$ を順次走査駆動する。

## 【0060】

LCDコントローラ60は、図示しない中央処理装置（Central Processing Unit：以下、CPUと略す。）等のホストにより設定された内容にしたがって、信号ドライバ30、走査ドライバ50及び電源回路80を制御する。より具体的には、LCDコントローラ60は、信号ドライバ30及び走査ドライバ50に対して、例えば動作モードの設定や内部

50

で生成した垂直同期信号や水平同期信号の供給を行い、電源回路 80 に対しては対向電極電圧  $V_{com}$  の極性反転タイミングの供給を行う。

【0061】

電源回路 80 は、外部から供給される基準電圧に基づいて、LCD パネル 20 の液晶駆動に必要な電圧レベルや、対向電極電圧  $V_{com}$  を生成する。LCD パネル 20 の液晶駆動に必要な電圧レベルは、例えば信号ドライバ 30、走査ドライバ 50 及び LCD パネル 20 に供給される。また、対向電極電圧  $V_{com}$  は、LCD パネル 20 の TFT の画素電極に対向して設けられた対向電極に供給される。

【0062】

このような構成の液晶装置 10 は、LCD コントローラ 60 の制御の下、外部から供給される画像データに基づいて、信号ドライバ 30、走査ドライバ 50 及び電源回路 80 が協調して LCD パネル 20 を表示駆動する。 10

【0063】

なお、図 1 では、液晶装置 10 に LCD コントローラ 60 を含めて構成するようにしているが、LCD コントローラ 60 を液晶装置 10 の外部に設けて構成するようにしても良い。或いは、LCD コントローラ 60 と共にホストを、液晶装置 10 に含めるように構成することも可能である。

【0064】

また、図 1 では、LCD パネル 20 の外部に信号ドライバ 30 及び走査ドライバ 50 を設けるようにしているが、信号ドライバ 30 及び走査ドライバ 50 のうち少なくとも 1 つを LCD パネル 20 と同一ガラス基板上に、形成することができる。 20

【0065】

1.2 信号ドライバ

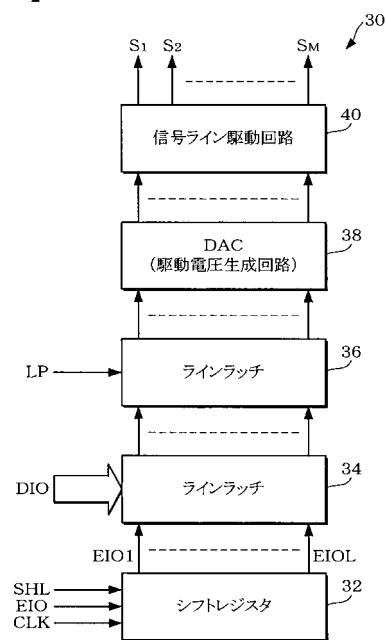

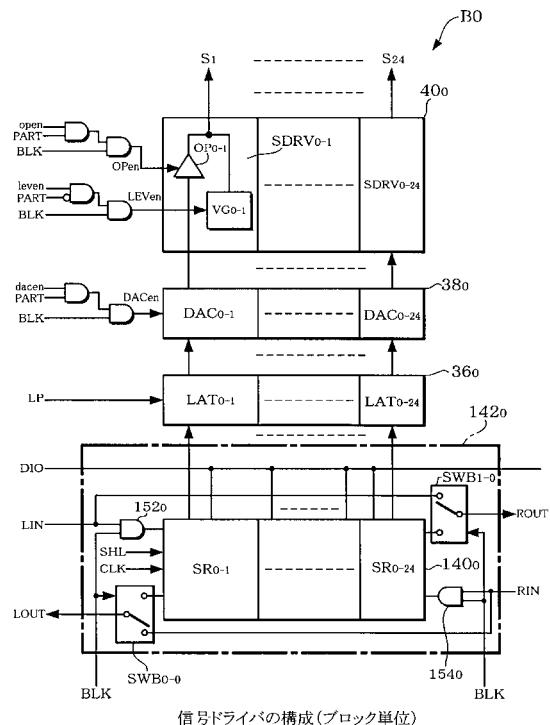

図 2 に、図 1 に示した信号ドライバの構成の概要を示す。

【0066】

信号ドライバ 30 は、シフトレジスタ 32、ラインラッチ 34、36、デジタル・アナログ変換回路（広義には、駆動電圧生成回路）38、信号ライン駆動回路 40 を含む。

【0067】

シフトレジスタ 32 は、複数のフリップフロップを有しており、これらフリップフロップが順次接続される。このシフトレジスタ 32 は、クロック信号 CLK に同期してイネーブル入出力信号 EIO を保持すると、順次クロック信号 CLK に同期して隣接するフリップフロップにイネーブル入出力信号 EIO をシフトする。 30

【0068】

また、このシフトレジスタ 32 には、シフト方向切り替え信号 SHL が供給される。シフトレジスタ 32 は、このシフト方向切り替え信号 SHL により、画像データ（DIO）のシフト方向と、イネーブル入出力信号 EIO の入出力方向が切り替えられる。したがって、信号ドライバ 30 の実装状態により信号ドライバ 30 に対して、画像データを供給する LCD コントローラ 60 の位置が異なった場合であっても、このシフト方向切り替え信号 SHL によりシフト方向を切り替えることによって、その配線の引き回しによって実装面積が拡大することなく、柔軟な実装を可能にすることができる。 40

【0069】

ラインラッチ 34 には、LCD コントローラ 60 から例えば 18 ビット（6 ビット（階調データ）×3（RGB 各色））単位で画像データ（DIO）が入力される。ラインラッチ 34 は、この画像データ（DIO）を、シフトレジスタ 32 の各フリップフロップで順次シフトされたイネーブル入出力信号 EIO に同期してラッチする。

【0070】

ラインラッチ 36 は、LCD コントローラ 60 から供給される水平同期信号 LP に同期して、ラインラッチ 34 でラッチされた一水平走査単位の画像データをラッチする。

【0071】

DAC 38 は、信号ラインごとに、画像データに基づいてアナログ化された駆動電圧を生 50

成する。

【0072】

信号ライン駆動回路40は、D A C 38によって生成された駆動電圧に基づいて、信号ラインを駆動する。

【0073】

このような信号ドライバ30は、LCDコントローラ60から順次入力される所与の単位（例えば18ビット単位）の画像データを順次取り込み、水平同期信号L Pに同期して一水平走査単位の画像データをラインラッチ36で一旦保持する。そして、この画像データに基づいて、各信号ラインを駆動する。この結果、LCDパネル20のTFTのソース電極には、画像データに基づく駆動電圧が供給される。

10

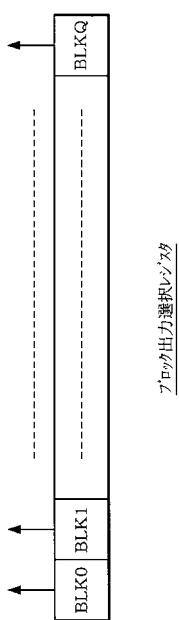

【0074】

この信号ドライバ30は、所与の複数の信号ラインごとに分割されたラインブロックを単位として、その出力をハイインピーダンス制御することができるようになっている。そのため、信号ドライバ30は、図3に示すように、ブロック出力選択レジスタ（ブロック出力選択データ保持手段）を有し、ラインブロック単位で各ブロックの信号ラインを駆動する信号ライン駆動回路の出力をハイインピーダンス制御するか否かを設定するためのブロック出力選択データ（広義には、制御指示データ）B L K 0～B L K Qを保持する。

【0075】

このブロック出力選択データにおいて、オン（「1」）に設定されたラインブロックの信号ラインは信号ライン駆動回路により信号駆動され、オフ（「0」）に設定されたブロックの信号ラインはハイインピーダンス状態となる。これにより、LCDパネル20の信号ラインに接続される信号ライン駆動回路をラインブロック単位で任意に選択できるようになり、LCDパネル20のサイズ変更に容易に対応することができる。また、駆動不要な信号ライン駆動回路で行われるインピーダンス変換に伴う消費電流を削減する。

20

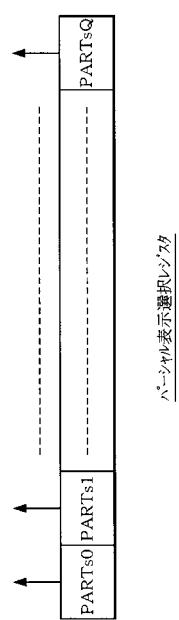

【0076】

また信号ドライバ30は、当該ラインブロック単位で表示エリア若しくは非表示エリアを設定することができるようになっている。そのため、信号ドライバ30は、図4に示すように、パーシャル表示選択レジスタ（パーシャル表示データ保持手段）を有し、ラインブロック単位で各ブロックの信号ラインを画像データに基づいて信号駆動するか否かを設定するためのパーシャル表示データ（広義には、制御指示データ）P A R T<sub>S</sub> 0～P A R T<sub>S</sub> Qを保持する。

30

【0077】

このパーシャル表示データにおいて、オン（「1」）が設定されたラインブロックの信号ラインに対しては、表示エリアとして画像データに基づいて信号駆動を行い、オフ（「0」）に設定されたブロックの信号ラインに対しては、非表示エリアとして所与の非表示レベル電圧が供給される。これにより、非表示エリアの信号ラインを駆動するインピーダンス変換手段としてのオペアンプ回路の電流消費を削減することができ、画質が高品位のTFTを用いたLCDパネルの低消費化を図ることができるようになる。同時に、非表示レベル電圧が供給される信号ラインにTFTを介して接続される液晶容量には、非表示として適切な電圧が印加されることになる。

40

【0078】

また、信号ドライバ30では、上述した制御単位であるブロックを8ピクセル単位としている。ここで、1ピクセルは、R G B信号の3ビットからなる。したがって、信号ドライバ30は、計24出力（例えば、S<sub>1</sub>～S<sub>24</sub>）を1ラインブロックとしている。これにより、LCDパネル20の表示エリアをキャラクタ文字（1バイト）単位で設定することができるので、携帯電話機のようなキャラクタ文字の表示を行う電子機器において、効率的な表示エリアの設定及びその画像表示が可能となる。

【0079】

図5に、信号ドライバ30の制御単位となるラインブロック単位の構成の概要を示す。

【0080】

50

この信号ドライバ30は、288本の信号ライン出力( $S_1 \sim S_{288}$ )を有しているものとする。

#### 【0081】

すなわち、信号ドライバ30は、24出力端子単位( $S_1 \sim S_{24}$ 、 $S_{25} \sim S_{48}$ 、 $\dots$ 、 $S_{265} \sim S_{288}$ )に、図5に示す構成を備えており、計12ラインブロック( $B_0 \sim B_{11}$ )を有している。以下では、図5は、ブロック $B_0$ を示すものとして説明するが、他のブロック $B_1 \sim B_{11}$ についても同様である。

#### 【0082】

信号ドライバ30のブロック $B_0$ は、信号ライン $S_1 \sim S_{24}$ の各信号ラインに対応して、シフトレジスタ $140_0$ を含むデータバイパス回路 $142_0$ 、ラインラッチ $36_0$ 、駆動電圧生成回路 $38_0$ 、信号ライン駆動回路 $40_0$ を含む。ここで、シフトレジスタ $140_0$ は、図2に示すシフトレジスタ $32$ 及びラインラッチ $34$ の機能を有する。

10

#### 【0083】

データバイパス回路 $142_0$ が有するシフトレジスタ $140_0$ は、各信号ラインに対応して $S_{R_{0-1}} \sim S_{R_{0-24}}$ を含む。ラインラッチ $36_0$ は、各信号ラインに対応して $LAT_{0-1} \sim LAT_{0-24}$ を含む。駆動電圧生成回路 $38_0$ は、各信号ラインに対応して $DAC_{0-1} \sim DAC_{0-24}$ を含む。信号ライン駆動回路 $40_0$ は、各信号ラインに対応して $SDRV_{0-1} \sim SDRV_{0-24}$ を含む。

#### 【0084】

上述したように信号ドライバ30は、ブロック出力選択レジスタ及びパーシャル表示選択レジスタを有しており、各ラインブロック単位でブロック出力選択データ及びパーシャル表示データが設定される。例えば、図5に示すブロック $B_0$ に対しては、図3に示すブロック出力選択データ $B_{LK0}$ が $B_{LK}$ として、図4に示すパーシャル表示データ $PART_{s0}$ が $PART$ として、それぞれ供給される。

20

#### 【0085】

データバイパス回路 $142_0$ は、 $LIN$ から $ROUT$ 方向若しくは $RIN$ から $LOUT$ 方向にシフトされるイネーブル入出力信号 $EIO$ に同期して、画像データ $DIO$ を取り込む。その際、データバイパス回路 $142_0$ は、ブロック出力選択データ $B_{LK}$ が「0」に設定されている場合、当該ラインブロックにシフトされたイネーブル入出力信号 $EIO$ をバイパスするための切り替え回路 $SWB_{1-0}$ 、 $SWB_{0-0}$ を含む。

30

#### 【0086】

切り替え回路 $SWB_{1-0}$ は、ブロック出力選択データ $B_{LK}$ が「1」(論理レベル「H」)のとき $S_{R_{0-24}}$ の出力データを右方向データ出力信号 $ROUT$ として出力する。一方、切り替え回路 $SWB_{0-0}$ は、ブロック出力選択データ $B_{LK}$ が「0」(論理レベル「L」)のとき左方向データ入力信号 $LIN$ として入力されたラインブロックからシフトされた画像データ(ブロック $B_0$ の場合は、 $DIO$ )を右方向データ出力信号 $ROUT$ として出力する。

#### 【0087】

切り替え回路 $SWB_{0-0}$ は、ブロック出力選択データ $B_{LK}$ が「1」(論理レベル「H」)のとき $S_{R_{0-1}}$ の出力データを左方向データ出力信号 $LOUT$ として出力する。一方、切り替え回路 $SWB_{0-0}$ は、ブロック出力選択データ $B_{LK}$ が「0」(論理レベル「L」)のとき右方向データ入力信号 $RIN$ として入力されたラインブロックからシフトされた画像データを左方向データ出力信号 $LOUT$ として出力する。

40

#### 【0088】

信号ライン $S_1 \sim S_{24}$ に対応した $S_{R_{0-1}} \sim S_{R_{0-24}}$ は、 $LIN$ 若しくは $RIN$ として供給されるイネーブル入出力信号 $EIO$ をシフトし、それぞれシフトされたイネーブル入出力信号 $EIO$ に同期して画像データ $DIO$ を取り込む。

#### 【0089】

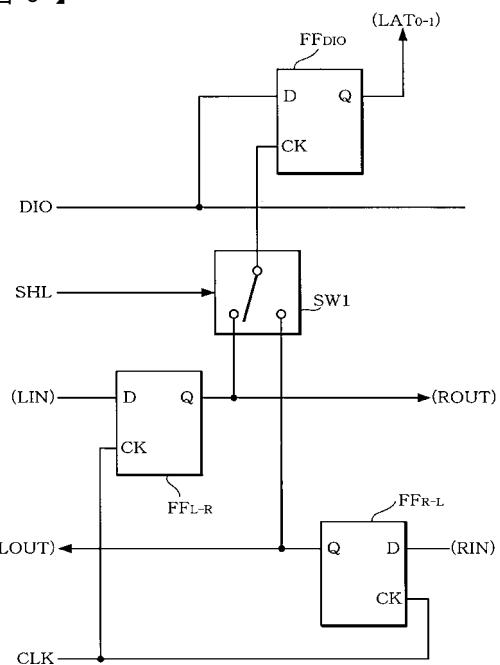

図6に、シフトレジスタ $140_0$ を構成する $S_{R_{0-1}}$ の構成を模式的に示す。

#### 【0090】

50

ここでは、 $SR_{0-1}$ の構成について示すが、他の $SR_{0-2} \sim SR_{0-24}$ についても同様に構成することができる。

【0091】

$SR_{0-1}$ は、 $FF_{L-R}$ 、 $FF_{R-L}$ 、 $FF_{D10}$ 、 $SW1$ を含む。

【0092】

$FF_{L-R}$ は、例えばイネーブル入出力信号 $EIO$ を、D端子に入力される左方向データ入力信号 $LIN$ として、CK端子に入力されるクロック信号の立ち上がりエッジに同期してラッチする。そして、Q端子から右方向データ出力信号 $ROUT$ として、 $SR_{0-2}$ のD端子に対して左方向データ入力信号 $LIN$ を供給する。

【0093】

10

$FF_{R-L}$ は、例えばイネーブル入出力信号 $EIO$ を、D端子に入力される右方向データ入力信号 $RIN$ として、CK端子に入力されるクロック信号の立ち上がりエッジに同期してラッチする。そして、Q端子から左方向データ出力信号 $ROUT$ を出力する。

【0094】

$FF_{L-R}$ のQ端子から出力される右方向データ出力信号 $ROUT$ は、 $SW1$ にも供給される。 $FF_{R-L}$ のQ端子から出力される左方向出力信号 $ROUT$ は、 $SW1$ にも供給される。

【0095】

$SW1$ は、シフト方向切り替え信号 $SHL$ に応じて、右方向データ出力信号 $ROUT$ 若しくは左方向データ出力信号 $ROUT$ のうち、いずれか一方を選択して、 $FF_{D10}$ のCK端子に供給する。

20

【0096】

$FF_{D10}$ は、このCK端子に供給される $SW1$ の選択出力信号に同期して、画像データ $DIO$ をラッチする。このラッチされた画像データは、Q端子からラインラッチ $36_0$ の $LAT_{0-1}$ に出力される。

【0097】

このようにして、シフトレジスタ $140_0$ の各 $SR_{0-1} \sim SR_{0-24}$ に保持された画像データは、水平同期信号 $LP$ に同期してそれぞれラインラッチ $36_0$ の各 $LAT_{0-1} \sim LAT_{0-24}$ にラッチされる。

【0098】

30

(ラインラッチ)

ラインラッチ $LAT_{0-1} \sim LAT_{0-24}$ にラッチされた信号ライン $S_1 \sim S_{24}$ に対応する画像データは、それぞれ駆動電圧生成回路の $DAC_{0-1} \sim DAC_{0-24}$ に供給される。

【0099】

(駆動電圧生成回路)

$DAC_{0-1} \sim DAC_{0-24}$ は、それぞれ $DAC$ イネーブル信号 $DAC_{en}$ が論理レベル「H」のときに、対応する $LAT_{0-1} \sim LAT_{0-24}$ から供給された例えは6ビットの階調データに基づいて、64レベルの階調電圧を発生する。

【0100】

$DAC$ イネーブル信号 $DAC_{en}$ は、イネーブル信号 $dacen0$ と、ブロック出力選択データ $BLK$ との論理積により生成される。このイネーブル信号 $dacen0$ は、信号ドライバ $30$ の図示しない制御回路で生成された $DAC$ 制御信号 $dacen$ と、パーシャル表示データ $PART$ との論理積により生成される。

40

【0101】

すなわち、 $DAC$ イネーブル信号 $DAC_{en}$ は、ブロック出力選択データ $BLK$ が「0」の場合には、パーシャル表示データ $PART$ の設定値にかかわらず、 $BK0$ の駆動電圧生成回路 $38_0$ は動作を停止する。また、ブロック出力選択データ $BLK$ が「1」の場合には、パーシャル表示エリアとして設定された場合にのみ $DAC$ 動作を行いう一方、パーシャル非表示エリアとして設定された場合、 $DAC$ 動作を停止してラダー抵抗に流れる電流消費を削減する。

50

## 【0102】

なお、このD A Cイネーブル信号D A C e nは、他の信号ラインS<sub>2</sub>～S<sub>24</sub>に対応するD A C<sub>0.2</sub>～D A C<sub>0.24</sub>にも同様に供給され、ラインプロック単位でD A Cの動作制御が行われる。

## 【0103】

(信号ライン駆動回路)

信号ライン駆動回路400のS D R V<sub>0.1</sub>～S D R V<sub>0.24</sub>は、それぞれインピーダンス変換手段としてのボルテージフォロワ接続されたオペアンプO P<sub>0.1</sub>～O P<sub>0.24</sub>と、パーシャル非表示レベル電圧供給回路V G<sub>0.1</sub>～V G<sub>0.24</sub>を含む。

## 【0104】

ボルテージフォロワ接続されたオペアンプO P<sub>0.1</sub>～O P<sub>0.24</sub>は、その出力端子が負帰還され、オペアンプの入力インピーダンスも極めて大きくなり、入力電流はほとんど流れなくなる。そして、オペアンプイネーブル信号O P e nが論理レベル「H」のときに、対応するD A C<sub>0.1</sub>～D A C<sub>0.24</sub>によって生成された駆動電圧をインピーダンス変換して、信号ラインS<sub>1</sub>～S<sub>24</sub>を駆動する。これにより、信号ラインS<sub>1</sub>～S<sub>24</sub>それぞれの出力負荷に依存することなく、信号駆動を行うことができる。

## 【0105】

オペアンプイネーブル信号O P e nは、イネーブル信号o p e n 0と、ブロック出力選択データB L Kとの論理積により生成される。このイネーブル信号o p e n 0は、信号ドライバ30の図示しない制御回路で生成されたオペアンプ制御信号o p e nと、パーシャル表示データP A R Tとの論理積により生成される。

## 【0106】

すなわち、オペアンプイネーブル信号O P e nは、ブロック出力選択データB L Kが「0」の場合には、パーシャル表示データP A R Tの設定値にかかわらず、B L K 0のオペアンプは動作を停止する（オペアンプの電流源を停止して、消費電流を削減する）。また、ブロック出力選択データB L Kが「1」の場合には、パーシャル表示エリアとして設定された場合にのみ駆動電圧生成回路で生成された駆動電圧を、インピーダンス変換して対応する信号ラインを駆動する一方、パーシャル非表示エリアとして設定された場合、オペアンプの動作を停止して、電流消費を削減する。

## 【0107】

(パーシャル非表示レベル電圧供給回路)

パーシャル非表示レベル電圧供給回路V G<sub>0.1</sub>～V G<sub>0.24</sub>は、非表示レベル電圧供給イネーブル信号L E V e nが論理レベル「H」の場合に、上述したパーシャル表示選択レジスタにおいて非表示エリア（出力がオフ）に設定されたとき、各信号ラインに供給する所との非表示レベル電圧V<sub>PART-LEVEL</sub>を生成する。

## 【0108】

ここで、非表示レベル電圧V<sub>PART-LEVEL</sub>は、画素の透過率が変化する所との閾値V<sub>CL</sub>と、この画素電極に対向する対向電極の対向電極電圧V<sub>com</sub>に対して、次の（1）式の関係を有する。

## 【0109】

$$|V_{PART-LEVEL} - V_{com}| < V_{CL} \quad \dots (1)$$

すなわち、非表示レベル電圧V<sub>PART-LEVEL</sub>は、駆動対象の信号ラインに接続されたT F Tのドレイン電極に接続される画素電極に印加された場合、液晶容量の印加電圧が、所との閾値V<sub>CL</sub>を越えないような電圧レベルとなっている。

## 【0110】

なお、この非表示レベル電圧V<sub>PART-LEVEL</sub>は、電圧レベルの生成及び制御の容易さから、対向電極電圧V<sub>com</sub>と同等の電圧レベルであることが望ましい。例えば、対向電極電圧V<sub>com</sub>と同等の電圧レベルが供給された場合、L C Dパネル20の非表示エリアには、液晶がオフのときの色が表示される。

## 【0111】

10

20

30

40

50

また、非表示レベル電圧供給回路  $V_{G_{0-1}} \sim V_{G_{0-24}}$  は、階調レベル電圧の両端の電圧レベル  $V_0$  若しくは  $V_8$  のいずれかを非表示レベル電圧  $V_{PART-LEVEL}$  として選択出力するができるようになっている。ここで、階調電圧レベルの両端の電圧レベル  $V_0$  若しくは  $V_8$  は、反転駆動方式によりフレームごとに交互に出力するための電圧レベルである。ここでは、ユーザによって指定された選択信号  $SEL$  により、非表示レベル電圧  $V_{PART-LEVEL}$  として、上述した対向電極電圧  $V_{com}$  か、階調レベル電圧の両端の電圧レベル  $V_0$  若しくは  $V_8$  かを選択できるようにする。これにより、ユーザは、非表示エリアの色の選択の自由度を高めることができる。

#### 【0112】

非表示レベル電圧供給イネーブル信号  $LEV_en$  は、信号ドライバ30の図示しない制御回路で生成された非表示レベル電圧供給回路制御信号  $lev_en$  と、パーシャル表示データ  $PART$  の反転との論理積により生成される。すなわち、非表示エリア（出力がオフ）として設定された場合にのみ所与の非表示レベル電圧を信号ラインに駆動し、表示エリア（出力がオン）として設定された場合、非表示レベル電圧供給回路  $V_{G_{0-1}} \sim V_{G_{0-24}}$  の出力はハイインピーダンス状態となって信号ラインの駆動を行わない。

#### 【0113】

なお、このオペアンプイネーブル信号  $OP_en$  及び非表示レベル電圧供給イネーブル信号  $LEV_en$  は、他の信号ライン  $S_2 \sim S_{24}$  に対応する  $SDRV_{0-2} \sim SDRV_{0-24}$  にも同様に供給され、ラインブロック単位で信号ラインの駆動制御が行われる。

#### 【0114】

##### 1.3 走査ドライバ

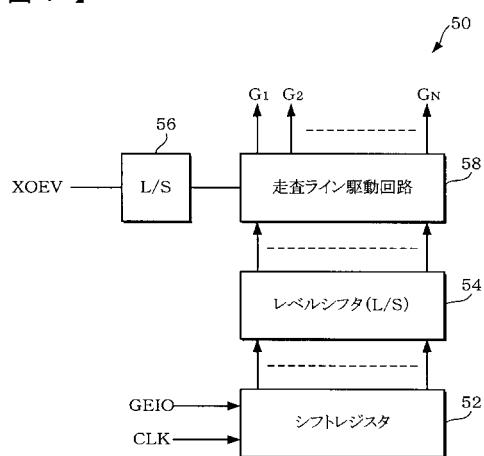

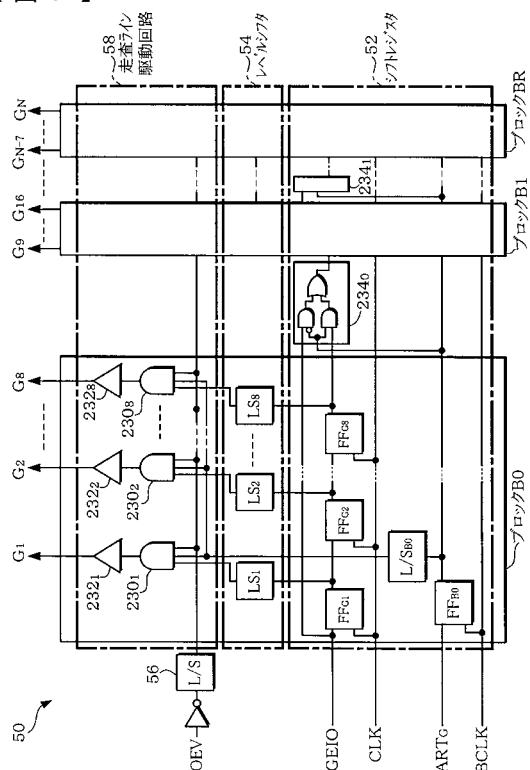

図7に、図1に示した走査ドライバの構成の概要を示す。

#### 【0115】

走査ドライバ50は、シフトレジスタ52、レベルシフタ（Level Shifter：以下、L/Sと略す。）54、56、走査ライン駆動回路58を含む。

#### 【0116】

シフトレジスタ52は、各走査ラインに対応して設けられたフリップフロップが順次接続される。このシフトレジスタ52は、クロック信号  $CLK$  に同期して走査イネーブル入出力信号  $GEIO$  をフリップフロップに保持すると、クロック信号  $CLK$  に同期して、順次隣接するフリップフロップに走査イネーブル入出力信号  $GEIO$  をシフトする。ここで入力される走査イネーブル入出力信号  $GEIO$  は、LCDコントローラ60から供給される垂直同期信号である。

#### 【0117】

$L/S_{54}$  は、LCDパネル20の液晶材に応じた電圧レベルにシフトする。この電圧レベルとしては、例えば  $20V \sim 50V$  の高い電圧レベルが必要とされるため、他のロジック回路部とは異なる高耐圧プロセスが用いられる。

#### 【0118】

走査ライン駆動回路58は、 $L/S_{54}$  によってシフトされた駆動電圧に基づいて、CMOS駆動を行う。また、この走査ドライバ50は、 $L/S_{56}$  を有しており、LCDコントローラ60から供給される出力イネーブル信号  $XOEV$  の電圧シフトが行われる。走査ライン駆動回路58は、 $L/S_{56}$  によってシフトされた出力イネーブル信号  $XOEV$  により、オンオフ制御が行われる。

#### 【0119】

このような走査ドライバ50は、垂直同期信号として入力されたイネーブル入出力信号  $GEIO$  が、クロック信号  $CLK$  に同期してシフトレジスタ52の各フリップフロップに順次シフトされる。シフトレジスタ52の各フリップフロップは、各走査ラインに対応して設けられているため、各フリップフロップに保持された垂直同期信号のパルスにより、走査ラインが逐一的に順次選択される。選択された走査ラインは、 $L/S_{54}$  によってシフトされた電圧レベルで、走査ライン駆動回路58により駆動される。これにより、LCDパネル20のTFTのゲート電極には、一垂直走査周期で所与の走査駆動電圧が供給され

10

20

30

40

50

ることになる。このとき、LCDパネル20の TFT のドレイン電極は、ソース電極に接続される信号ラインの電位に対応して、ほぼ同等の電位となる。

【0120】

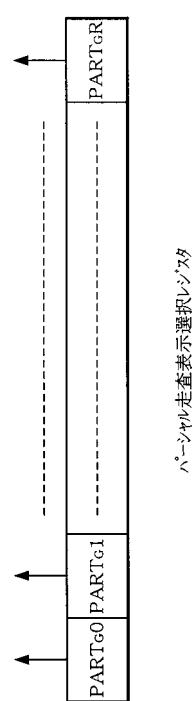

この走査ドライバ50は、所与の複数の走査ラインごとに分割されたラインブロックを単位として、表示エリア若しくは非表示エリアを設定することができるようになっている。そのため、走査ドライバ50は、図8に示すように、パーシャル走査表示選択レジスタを有し、当該ラインブロック単位で各ラインブロックの走査ラインを順次走査駆動するか否かを設定するためのパーシャル走査表示データ（広義には、制御指示データ）PART<sub>6</sub>0～PART<sub>6</sub>Rを保持する。

【0121】

このパーシャル走査表示データにおいて、オン（「1」）が設定されたラインブロックの走査ラインは、順次走査駆動され、オフ（「0」）に設定されたラインブロックの走査ラインに対しては、走査駆動されない。これにより、非表示エリアの走査ラインについて回路動作を停止させることができ、画質が高品位のTFTを用いたLCDパネルの低消費化を図ることができるようになる。

【0122】

また、走査ドライバ50は、上述した制御単位であるラインブロックを8走査ライン単位としている。これにより、LCDパネル20の表示エリアをキャラクタ文字（1バイト）単位で設定することができるので、携帯電話機のようなキャラクタ文字の表示を行う電子機器において、効率的な表示エリアの設定及びその画像表示が可能となる。

【0123】

図9に、このような走査ドライバ50の具体的な構成の一例を示す。

【0124】

シフトレジスタ52は、走査ラインG<sub>1</sub>～G<sub>N</sub>（第1～第Nの走査ライン）のそれぞれに対応して設けられたFF<sub>G1</sub>～FF<sub>GN</sub>（第1～第NのFF）が直列に接続される。FF<sub>G1</sub>（第1のFF）には、LCDコントローラ60から供給される走査イネーブル入出力信号GEIOが供給される。また、FF<sub>G1</sub>～FF<sub>GN</sub>は、同様にLCDコントローラ60から供給されるクロック信号CLKが供給される。FF<sub>G1</sub>～FF<sub>GN</sub>は、クロック信号CLKに同期して走査イネーブル入出力信号GEIO（所与のパルス信号）を順次シフトする。

【0125】

LCDコントローラ60から供給されるイネーブル入出力信号GEIOは、垂直同期信号である。また、LCDコントローラ60から供給されるクロック信号CLKは、水平同期信号である。

【0126】

L/S54は、走査ラインG<sub>1</sub>～G<sub>N</sub>のそれぞれに対応して設けられたレベルシフタ回路LS<sub>1</sub>～LS<sub>N</sub>（第1～第NのL/S回路）を有しており、対応するFF<sub>G1</sub>～FF<sub>GN</sub>の保持データの高電位側の電圧レベルを例えば20V～50Vの電圧レベルにシフトする。

【0127】

L/S56は、LCDコントローラ60から供給される出力イネーブル信号XOEVの反転信号（出力イネーブル信号）の高電位側の電圧レベルを例えば20V～50Vの電圧レベルにシフトする。

【0128】

走査ライン駆動回路58は、走査ラインG<sub>1</sub>～G<sub>N</sub>のそれぞれに対応して、マスク回路としてのAND回路230<sub>1</sub>～230<sub>N</sub>、CMOSバッファ回路232<sub>1</sub>～232<sub>N</sub>を含む。AND回路230<sub>1</sub>～230<sub>N</sub>及びCMOSバッファ回路232<sub>1</sub>～232<sub>N</sub>は、上述した例えば20V～50Vの電圧レベルで動作可能な高耐圧プロセスにより形成される。なお、この電圧レベルは、例えば駆動対象のLCDパネル20の液晶材等に応じて決められる。

【0129】

AND回路230<sub>1</sub>～230<sub>N</sub>は、LS<sub>1</sub>～LS<sub>N</sub>によってレベルシフトされたFF<sub>G1</sub>～FF<sub>GN</sub>の出力ノードの論理レベルを、L/S56によってレベルシフトされた出力イネーブル

10

20

30

40

50

信号 X O E V と、ラインブロック単位で指定されるブロック選択データとによりマスクする。より具体的には、パーシャル走査表示データが「0」に設定されている場合、出力イネーブル信号 X O E V の論理レベルにかかわらず、L S<sub>1</sub> ~ L S<sub>N</sub> の出力ノードの論理レベルを「L」にマスクする。また、パーシャル走査表示データが「1」に設定されている場合、出力イネーブル信号 X O E V により、L S<sub>1</sub> ~ L S<sub>N</sub> の出力ノードの論理レベルを「L」にマスクする。

#### 【0130】

パーシャル走査表示データは、ラインブロック単位に設けられる F F<sub>B0</sub> ~ F F<sub>BR</sub> に保持される。F F<sub>B0</sub> には、LCDコントローラ 60 からシリアル入力されるパーシャル走査表示データ P A R T<sub>G</sub> が供給される。F F<sub>B0</sub> ~ F F<sub>BR</sub> は、LCDコントローラ 60 から、シリアル入力されるパーシャル走査表示データ P A R T<sub>G</sub> を順次取り込むためのクロック信号 B C L K が共通に供給される。F F<sub>B0</sub> ~ F F<sub>BR</sub> は、F F<sub>B0</sub> に供給されたパーシャル走査表示データ P A R T<sub>G</sub> を、クロック信号 B C L K に同期して順次シフトする。

#### 【0131】

さらに、走査ドライバ 50 は、走査イネーブル入出力信号 G E I O をラインブロック単位にバイパスするためのデータ切り替え回路（バイパス手段）234<sub>0</sub> ~ 234<sub>R-1</sub> が設かれている。

#### 【0132】

例えば、ブロック選択データによりブロック B 1 の走査ライン駆動を行わないように指定した場合、ブロック B 0 の F F<sub>G1</sub> に供給される走査イネーブル入出力信号 G E I O は、F F<sub>G2</sub> ~ F F<sub>G8</sub> によりクロック信号 C L K に同期してシフトされるが、ブロック B 1 の F F<sub>G9</sub> に対応して設けられたデータ切り替え回路 234<sub>1</sub> により、ブロック B 2 の F F<sub>G17</sub> に F F<sub>G8</sub> のシフト出力が供給されることになる。

#### 【0133】

すなわち、ブロック B 0 に対応して設けられたデータ切り替え回路 234<sub>0</sub> は、前段のラインブロックから供給されるシフト出力（ブロック B 0 では F F<sub>G1</sub> に供給される走査イネーブル入出力信号 G E I O ）と、当該ラインブロックの最終段の F F のシフト出力（ブロック B 0 では F F<sub>G8</sub> から出力されるシフト出力）とを、当該ラインブロックのブロック選択データにより切り替える。データ切り替え回路 234<sub>0</sub> により切り替えられた出力信号は、ブロック B 1 に供給される。

#### 【0134】

なお、このようなデータ切り替え回路は、所与のシフト方向切り替え信号 S H L により、走査イネーブル入出力信号 G E I O のシフト方向を切替可能とするために、各ラインブロックについて逆側に設けるようにすることも可能である。この場合、ブロック B Q ~ B 1 に対応したデータ切り替え回路が設けられることになる。

#### 【0135】

このような構成の走査ドライバ 50 は、各ラインブロックに設けられた F F<sub>B0</sub> ~ F F<sub>BR</sub> に対し、表示エリアに設定されたラインブロックのブロック選択データが「1」、非表示エリアに設定されたラインブロックのブロック選択データが「0」となるように設定される。

#### 【0136】

そして、LCDコントローラ 60 により垂直同期信号及び水平同期信号が供給される。出力イネーブル信号 X O E V の論理レベル「L」の状態において、ラインブロック単位で設定されたブロック選択データが「0」の場合、CMOSバッファ回路 232<sub>1</sub> ~ 232<sub>N</sub> は、AND回路により L S の出力ノードの論理レベルがマスクされて論理レベル「L」となるため、当該走査ラインの駆動は行われない。

#### 【0137】

##### 1.4 LCDコントローラ

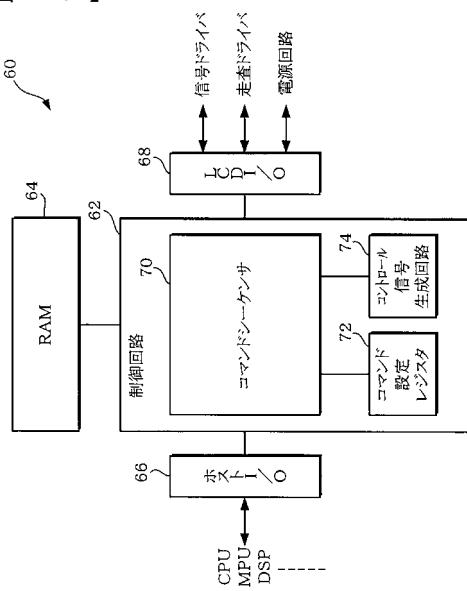

図 10 に、図 1 に示した LCDコントローラの構成の概要を示す。

#### 【0138】

10

20

30

40

50

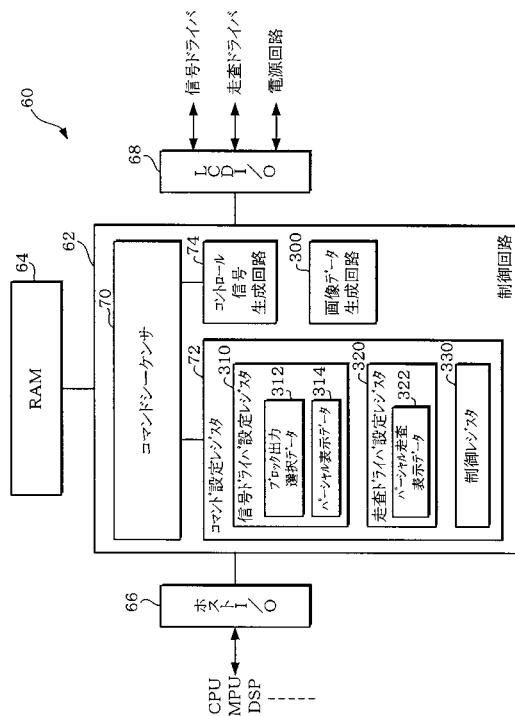

L C D コントローラ 6 0 は、制御回路 6 2、ランダムアクセスメモリ (Random Access Memory: 以下、RAMと略す。) (広義には、記憶手段) 6 4、ホスト入出力回路 (I / O) 6 6、L C D 入出力回路 6 8 を含む。さらに、制御回路 6 2 は、コマンドシーケンサ 7 0、コマンド設定レジスタ 7 2、コントロール信号生成回路 7 4 を含む。

【 0 1 3 9 】

制御回路 6 2 は、ホストによって設定された内容にしたがい、信号ドライバ 3 0、走査ドライバ 5 0 及び電源回路 8 0 の各種動作モード設定や同期制御等を行う。より具体的には、コマンドシーケンサ 7 0 が、ホストからの指示にしたがって、コマンド設定レジスタ 7 2 で設定された内容に基づいて、コントロール信号生成回路 7 4 で同期タイミングを生成したり、信号ドライバ等に対して所与の動作モードを設定したりする。

10

【 0 1 4 0 】

R A M 6 4 は、画像表示を行うためのフレームバッファとしての機能を有するとともに、制御回路 6 2 の作業領域にもなる。

【 0 1 4 1 】

このL C D コントローラ 6 0 には、ホストI / O 6 6 を介して、画像データや、信号ドライバ 3 0 及び走査ドライバ 5 0 を制御するためのコマンドデータが供給される。

【 0 1 4 2 】

より具体的には、ホストI / O 6 6 には、図示しないC P U や、デジタル信号処理装置 (Digital Signal Processor: D S P) 或いはマイクロプロセッサユニット (Micro Processor Unit: M P U) が接続される。L C D コントローラ 6 0 は、ホストI / O 6 6 を介し、画像データとして図示しないC P U より静止画データが供給されたり、D S P 或いはM P U より動画データが供給される。また、L C D コントローラ 6 0 は、ホストI / O 6 6 を介し、コマンドデータとして図示しないC P U より、信号ドライバ 3 0 又は走査ドライバ 5 0 を制御するためのレジスタの内容や、各種動作モードを設定するためのデータが供給される。

20

【 0 1 4 3 】

画像データとコマンドデータは、それぞれ別個のデータバスを介してデータを供給するようにも良いし、データバスを共用化しても良い。この場合、例えばコマンド (Command: C M D) 端子に入力された信号レベルによって、データバス上のデータが、画像データか、或いはコマンドデータかを識別できるようにすることで、画像データとコマンドデータとの共用化を容易に図ることができ、実装面積の縮小化が可能になる。

30

【 0 1 4 4 】

L C D コントローラ 6 0 は、画像データが供給された場合、この画像データをフレームバッファとしてのR A M 6 4 に保持する。一方、コマンドデータが供給された場合、L C D コントローラ 6 0 は、コマンド設定レジスタ 7 2 若しくはR A M 6 4 に保持する。

【 0 1 4 5 】

コマンドシーケンサ 7 0 は、コマンド設定レジスタ 7 2 に設定された内容にしたがって、コントロール信号生成回路 7 4 により各種タイミング信号を生成させる。また、コマンドシーケンサ 7 0 は、コマンド設定レジスタ 7 2 に設定された内容にしたがって、L C D 入出力回路 6 8 を介して、信号ドライバ 3 0、走査ドライバ 5 0 若しくは電源回路 8 0 のモード設定を行う。

40

【 0 1 4 6 】

また、コマンドシーケンサ 7 0 は、コントロール信号生成回路 7 4 で生成された表示タイミングにより、R A M 6 4 に記憶された画像データから所与の形式の画像データを生成し、L C D 入出力回路 (L C D I / O) 6 8 を介して、信号ドライバ 3 0 に供給するようになっている。

【 0 1 4 7 】

1 . 5 反転駆動方式

ところで、液晶を表示駆動する場合、液晶の耐久性や、コントラストの観点から、周期的に液晶容量に蓄積される電荷を放電する必要がある。そのため、上述した液晶装置 1 0 で

50

は、交流化駆動によって、所与の周期で液晶に印加される電圧の極性を反転させることが行われる。この交流化駆動方式としては、例えばフレーム反転駆動方式や、ライン反転駆動方式がある。

【0148】

フレーム反転駆動方式は、フレームごとに液晶容量に印加される電圧の極性を反転する方式である。一方、ライン反転駆動方式は、ラインごとに液晶容量に印加される電圧の極性を反転する方式である。なお、ライン反転駆動方式の場合も、各ラインに着目すれば、フレーム周期で液晶容量に印加される電圧の極性も反転される。

【0149】

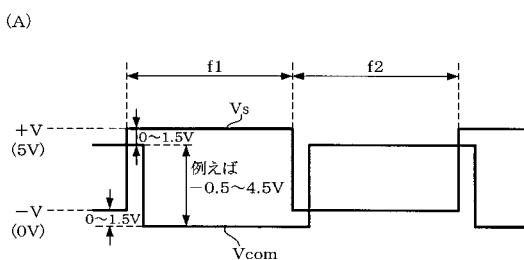

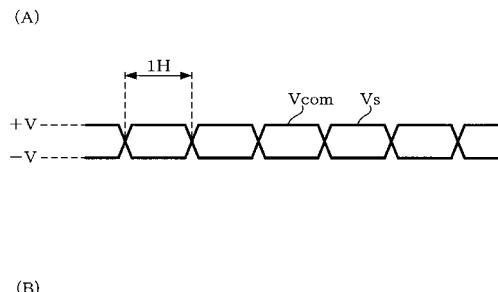

図11(A)、(B)に、フレーム反転駆動方式の動作を説明するための図を示す。図11(A)は、フレーム反転駆動方式による信号ラインの駆動電圧及び対向電極電圧 $V_{com}$ の波形を模式的に示したものである。図11(B)は、フレーム反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示したものである。

【0150】

フレーム反転駆動方式では、図11(A)に示すように信号ラインに印加される駆動電圧の極性が1フレーム周期ごとに反転されている。すなわち、信号ラインに接続されるTFTのソース電極に供給される電圧 $V_s$ は、フレーム $f_1$ では正極性「+V」、後続のフレーム $f_2$ では負極性の「-V」となる。一方、TFTのドレイン電極に接続される画素電極に対向する対向電極に供給される対向電極電圧 $V_{com}$ も、信号ラインの駆動電圧の極性反転周期に同期して反転される。

【0151】

液晶容量には、画素電極と対向電極との電圧の差が印加されるため、図11(B)に示すようにフレーム $f_1$ では正極性、フレーム2では負極性の電圧がそれぞれ印加されることになる。

【0152】

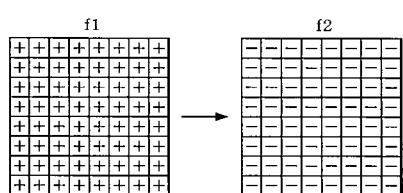

図12(A)、(B)に、ライン反転駆動方式の動作を説明するための図を示す。

【0153】

図12(A)は、ライン反転駆動方式による信号ラインの駆動電圧及び対向電極電圧 $V_{com}$ の波形を模式的に示したものである。図12(B)は、ライン反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示したものである。

【0154】

ライン反転駆動方式では、図12(A)に示すように信号ラインに印加される駆動電圧の極性が、各水平走査周期(1H)ごとに、かつ1フレーム周期ごとに反転されている。すなわち、信号ラインに接続されるTFTのソース電極に供給される電圧 $V_s$ は、フレーム $f_1$ の1Hでは正極性「+V」、2Hでは負極性の「-V」となる。なお、当該電圧 $V_s$ は、フレーム $f_2$ の1Hでは負極性「-V」、2Hでは正極性の「+V」となる。

【0155】

一方、TFTのドレイン電極に接続される画素電極に対向する対向電極に供給される対向電極電圧 $V_{com}$ も、信号ラインの駆動電圧の極性反転周期に同期して反転される。

【0156】

液晶容量には、画素電極と対向電極との電圧の差が印加されるため、走査ラインごとに極性を反転することで、図12(B)に示すようにフレーム周期で、各ラインごとに極性が反転する電圧がそれぞれ印加されることになる。

【0157】

一般的に、フレーム反転駆動方式に比べてライン反転駆動方式のほうが、変化の周期が1ライン周期となるため、画質の向上に貢献できるものの、消費電力が大きくなる。

【0158】

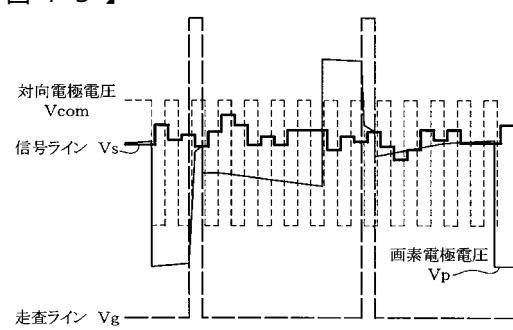

図13に、上述した構成の液晶装置10のLCDパネル20の駆動波形の一例を示す。ここでは、ライン反転駆動方式により駆動する場合を示している。

#### 【0159】

上述したように、液晶装置10では、LCDコントローラ60によって生成された表示タイミングにしたがって、信号ドライバ30、走査ドライバ50及び電源回路80が制御される。LCDコントローラ60は、信号ドライバ30に対しては一水平走査単位の画像データを順次転送するとともに、内部で生成した水平同期信号や反転駆動タイミングを示す極性反転信号POLを供給する。また、LCDコントローラ60は、走査ドライバ50に対しては、内部で生成した垂直同期信号を供給する。さらに、LCDコントローラ60は、電源回路80に対して対向電極電圧極性反転信号VCOMを供給する。

10

#### 【0160】

これにより、信号ドライバ30は、水平同期信号に同期して、一水平走査単位の画像データに基づいて信号ラインの駆動を行う。走査ドライバ50は、垂直同期信号をトリガとして、LCDパネル20にマトリックス状に配置された TFT のゲート電極に接続される走査ラインを、順次駆動電圧Vgで走査駆動する。電源回路80は、内部で生成した対向電極電圧Vcomを、対向電極電圧極性反転信号VCOMに同期して極性反転を行いながら、LCDパネル20の各対向電極に供給する。

#### 【0161】

液晶容量には、TFTのドレイン電極に接続される画素電極と対向電極の電圧Vcomとの電圧に応じた電荷が充電される。したがって、液晶容量に蓄積された電荷によって保持された画素電極電圧Vpが、所与の閾値VCLを越えると画像表示が可能となる。画素電極電圧Vpが所与の閾値VCLを越えると、その電圧レベルに応じて画素の透過率が変化し、階調表現が可能となる。

20

#### 【0162】

##### 1.7 パーシャル表示制御

上述した構成の液晶装置10を表示制御する本実施形態におけるLCDコントローラ60は、信号ドライバ30に対して、ブロック出力選択データ及びパーシャル表示データを設定することで、信号ラインの並び方向においてラインブロック単位で表示エリア及び非表示エリアが設定されるパーシャル表示制御が可能となる。また、同様に、LCDコントローラ60は、走査ドライバ50に対して、パーシャル走査表示データを設定することで、走査ラインの並び方向においてラインブロック単位で表示エリア及び非表示エリアが設定されるパーシャル表示制御が可能となる。

30

#### 【0163】

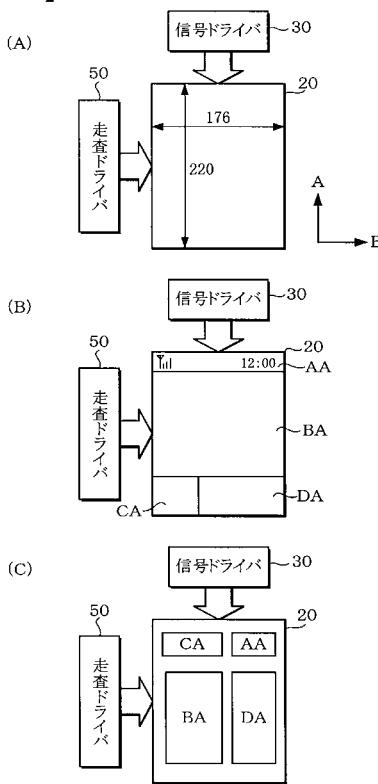

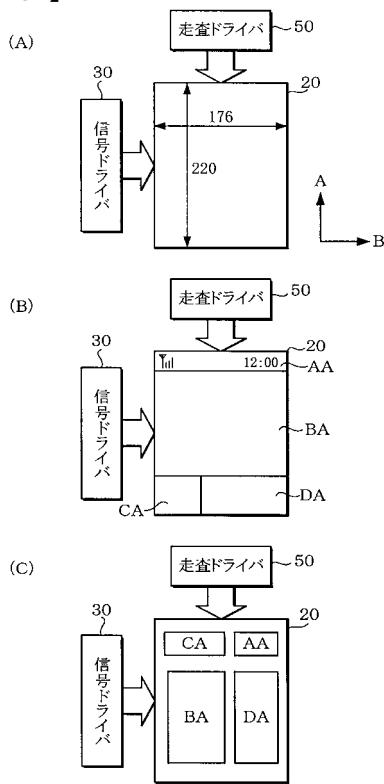

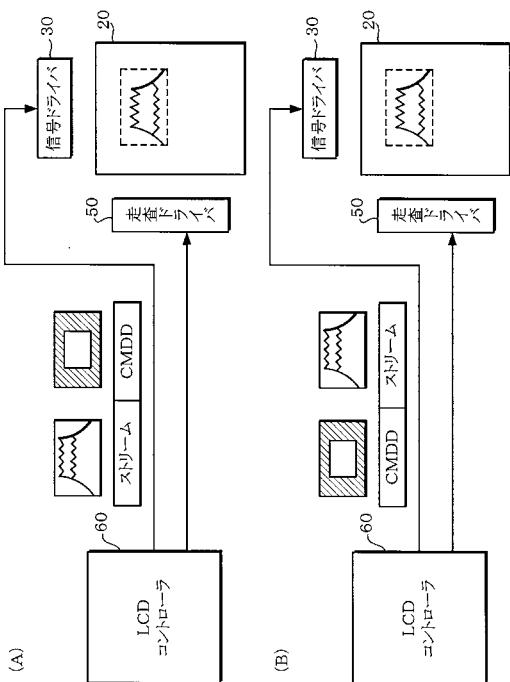

図14(A)、(B)、(C)に、本実施形態におけるLCDコントローラ60によるパーシャル表示制御の一例を模式的に示す。

#### 【0164】

A方向に走査ラインが配列され、B方向に信号ラインが配列されるLCDパネル20に対し、図14(A)に示すように信号ドライバ30及び走査ドライバ50を配置するものとする。例えば、このようなLCDパネル20により携帯電話機の表示部が構成される場合、図14(B)に示すように、表示領域AAに電波受信状態や時刻を表示させ、表示領域BAは待ち受け状態において非表示領域とすることができる。また、表示領域CA、DAには、動画情報やメールその他の情報を適宜表示させるようにしてよい。

40

#### 【0165】

また、図14(C)に示すように、各表示領域AA～DAの境界を設定し、任意の領域に配置するようにパーシャル表示制御を行うことで、ユーザにとって見やすい画面を提供することが可能となる。

#### 【0166】

このようにパーシャル表示制御によって、ウィンドウ表示を行うことができ、高品位の画質を提供できるTFTを用いたLCDパネルの低消費化を大幅に促進することができる。また、画面サイズの拡大に伴って操作性が低下するため、このようなパーシャル表示制御

50

を採用することにより、ユーザにとって操作性を向上させることができるようになる。

【0167】

図15(A)、(B)、(C)に、本実施形態におけるLCDコントローラ60によるパーシャル表示制御の他の例を模式的に示す。

【0168】

A方向に信号ラインが配列され、B方向に走査ラインが配列されるLCDパネル20に対し、図15(A)に示すように信号ドライバ30及び走査ドライバ50を配置するものとする。この場合も、図14(B)、(C)と同様に、図15(B)、(C)に示すように、パーシャル表示制御によって、ウィンドウ表示を行うことができ、高品位の画質を提供できる TFT を用いたLCDパネルの低消費化を大幅に促進することができる。また、画面サイズの拡大に伴って操作性が低下するため、このようなパーシャル表示制御を採用することにより、ユーザにとって操作性を向上させることができるようになる。

10

【0169】

特に、LCDコントローラ60により、信号ドライバ30及び走査ドライバ50に対してパーシャル表示制御を行うことで、LCDパネル20の表示領域内の任意の位置にウィンドウを表示させ、ウィンドウ内に適切な情報を表示させることができる。

【0170】

2. 本実施形態におけるLCDコントローラ

次に、このようなパーシャル表示制御を可能とするLCDコントローラ60について、より詳細に説明する。

20

【0171】

2.1 構成の具体例

図16に、本実施形態におけるLCDコントローラ60の機能ブロック構成の要部の一例を示す。

【0172】

ただし、図10に示したLCDコントローラ60と同一部分には同一符号を付している。

【0173】

制御回路62は、さらに画像データ生成回路（広義には、画像データ生成手段）300を含む。

【0174】

30

画像データ生成回路300は、例えばRAM64に一時的に蓄積される画像イメージのデータを、所与の形式の画像データに変換する。変換された画像データは、例えばコマンドシーケンサ（広義には、画像データ供給手段）70により、信号ドライバ30に対して供給される。

【0175】

また、制御回路62のコマンド設定レジスタ72は、より具体的には信号ドライバ設定レジスタ310、走査ドライバ設定レジスタ320、制御レジスタ330を含む。

【0176】

信号ドライバ設定レジスタ310は、パーシャル表示制御を行うために信号ドライバ30に設定すべきブロック出力選択データ312及びパーシャル表示データ314を保持する。ブロック出力選択データ312及びパーシャル表示データ314は、ホストI/O66を介して、図示しないホストによって設定される。

40

【0177】

走査ドライバ設定レジスタ320は、パーシャル表示制御を行うために走査ドライバ50に設定すべきパーシャル走査表示データ322を保持する。パーシャル走査表示データ322は、ホストI/O66を介して、図示しないホストによって設定される。

【0178】

制御レジスタ330は、LCDコントローラ60の動作制御を行うためのコントローラ制御データを保持する。コントローラ制御データは、ホストI/O66を介して、図示しないホストによって設定される。LCDコントローラ60のコマンドシーケンサ70は、こ

50

の制御レジスタ 330 に設定されたコントローラ制御データに基づいて動作制御を行い、信号ドライバ 30 及び走査ドライバ 50 に対するパーシャル表示制御を行うことができるようになっている。

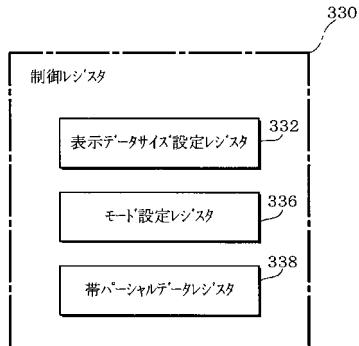

#### 【0179】

図 17 に、このような制御レジスタ 330 に保持されるコントローラ制御データの一例を示す。

#### 【0180】

制御レジスタ 330 は、表示データサイズ設定レジスタ 332、モード設定レジスタ 336、帯パーシャルデータレジスタ（帯パーシャル表示制御データ保持手段）338 を含む。

10

#### 【0181】

表示データサイズ設定レジスタ 332 には、LCD パネル 20 に表示される画像サイズを特定するための表示データサイズが設定される。表示データサイズは、ホスト I/O 66 を介し、図示しないホストによって設定される。

#### 【0182】

モード設定レジスタ 336 は、パーシャル表示制御を行うための各種モードを設定するためのモード設定データが設定される。モード設定データは、例えば図示しないホストにより、モード設定レジスタ 336 に各モードに対応したデータが設定されると、コマンドシーケンサ（広義には、モード切替手段）70 が当該モードで動作する。本実施形態における LCD コントローラ 60 は、モードによって異なるウィンドウ管理を行い、信号ドライバ 30 及び走査ドライバ 50 に対し、それぞれ最適なパーシャル表示制御を行う。

20

#### 【0183】

帯パーシャルデータレジスタ 338 は、走査ラインの並び方向のみでパーシャル表示制御を行うための表示制御データである帯パーシャルデータを保持する。帯パーシャルデータは、ホスト I/O 66 を介し、図示しないホストによって設定される。本実施形態では、上述したモード設定レジスタ 336 によって、所与の動作モードが指定されたときに帯パーシャルデータに基づくパーシャル表示制御が行われる。

#### 【0184】

このような LCD コントローラ 60 は、例えば図示しないホストによって、予めモード設定レジスタ 336 によって動作モードが指定される。帯パーシャルデータを用いる場合は、モード設定レジスタ 336 で所与の動作モードに設定した上で、帯パーシャルデータレジスタ 338 が設定される。その他の動作モードでは、RAM 64 にパーシャル表示制御される 1 又は複数のウィンドウを管理するためのメモリ領域が確保される。

30

#### 【0185】

その後、LCD コントローラ 60 は、図示しないホストによって、信号ドライバ設定レジスタ 310 及び走査ドライバ設定レジスタ 320 の各種データが設定されると、コマンドシーケンサ 70 により、LCD I/O 68 を介し、信号ドライバ 30 及び走査ドライバ 50 に対して、表示エリア及び非表示エリアを設定する。より具体的には、コマンドシーケンサ 70 は、信号ドライバ 30 に対しブロック出力選択データ及びパーシャル表示データを設定し、走査ドライバ 50 に対しパーシャル走査表示データを設定する。

40

#### 【0186】

その際、LCD コントローラ 60 は、モード設定レジスタ 336 で設定された動作モードに応じて、RAM 64 に確保されたメモリ上で管理される表示制御データ若しくは帯パーシャルデータを参照して、信号ドライバ 30 及び走査ドライバ 50 に対して、表示エリア（非表示エリア）を設定する。

#### 【0187】

その後、図示しないホストによって生成された画像データが一旦 RAM 64 に記憶され、画像データ生成回路 300 は、例えば表示データサイズ設定レジスタ 332 を参照しながら、所与の定型の画像データを生成する。LCD コントローラ 60 は、所与の表示タイミングを走査ドライバ 50 に対して供給するとともに、当該表示タイミングに同期して、生

50

成した画像データを信号ドライバ30に供給する。

【0188】

2.2 パーシャル表示制御

2.2.1 リフレッシュ

これまで、TFTを用いたアクティブマトリクス型液晶パネルでは、ダイナミックに切り替え可能なパーシャル表示制御が行われていなかった。上述したように、液晶の寿命の関係で、例えば60分の1秒ごとに交流化駆動を行っている。しかしながら、液晶容量に電荷が蓄積された状態でゲート電極をオンにしてしまうと液晶が劣化してしまうため、液晶容量に蓄積される電荷を放電する必要がある。そこで、TFTを用いたアクティブマトリクス型液晶パネルでは、非表示エリアについては、液晶容量の画素電極と対向電極との電位差を0にする、或いは多少のオフセットをもたせた電位差とすることが行われる。

10

【0189】

ところが、TFTのリークによって液晶容量には次第に電荷が蓄積されてしまうので、TFTのゲート電極をオフの状態を維持したとしても、最終的には閾値 $V_{CL}$ を越える電荷が蓄積されることになり、その結果画素の透過率が変化し、例えばグレイ表示となり、いわゆるパーシャル表示ができなくなる。

【0190】

すなわち、STN液晶を用いたパッシブマトリクス型液晶パネルの場合には走査駆動しない限り容易に実現できたパーシャル表示制御方法を、TFTを用いたアクティブマトリクス型液晶パネルにそのまま適用することはできない。したがって、これまでTFTを用いたアクティブマトリクス型液晶パネルにおいて非表示エリアを設定した場合、電源投入時から固定的に設定するしかなく、ダイナミックに切り替え可能なパーシャル表示制御を行うことができなかった。

20

【0191】

これに対して、本実施形態では、TFTのゲート電極の電圧を制御することにより、ダイナミックに切り替え可能なパーシャル表示制御を実現する。そして、このパーシャル表示制御により、非表示エリアの走査駆動に消費される電力を低減若しくは削減することが可能となる。

【0192】

より具体的には、走査ドライバ50は、ラインブロック単位で表示エリアに設定された走査ラインについて1フレーム周期で走査駆動を行い、ラインブロック単位で非表示エリアに設定された走査ラインを含む全走査ラインについて3フレーム以上の任意の奇数フレーム周期で走査駆動する。ここで、3以上の奇数フレーム周期とは、所与の基準フレームを0フレームとしたときに、3フレーム目、5フレーム目、・・・、(2k+1)(kは、自然数)フレーム目を最終フレームとする周期をいう。

30

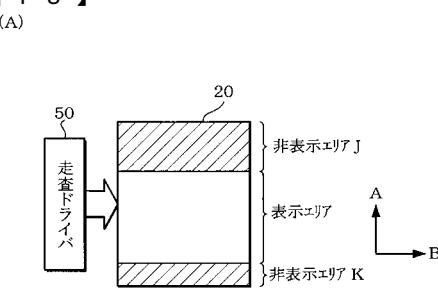

【0193】

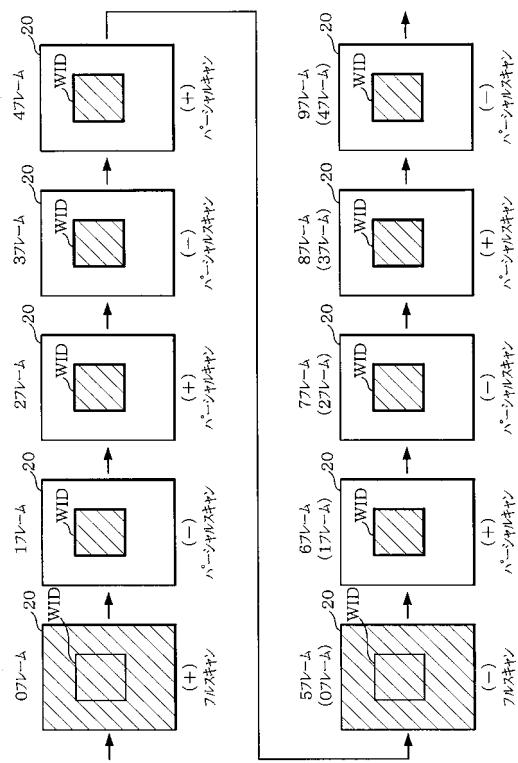

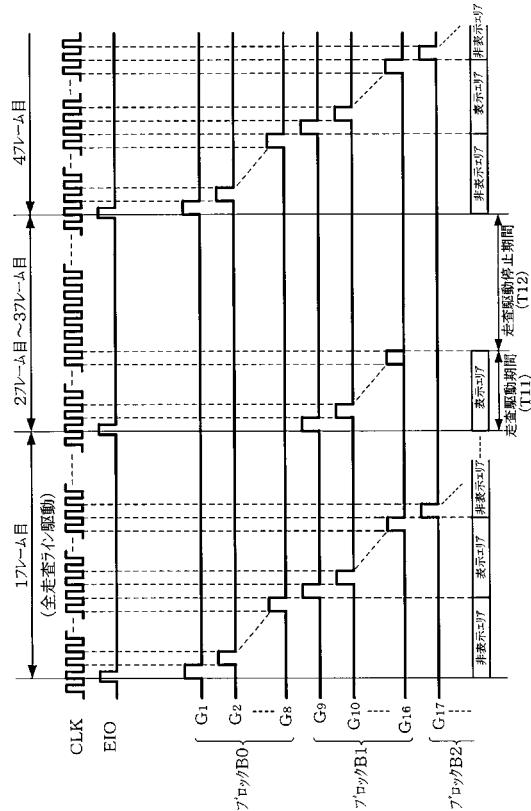

図18(A)、(B)に、本実施形態におけるLCDコントローラ60によって制御される走査ドライバ50の動作の一例を示す。

【0194】

例えば、LCDパネル20のA方向に、B方向に延びる複数の走査ラインが配列された場合に、図18(A)に示すようにラインブロック単位に表示エリア及び非表示エリアJ、Kが設定されているものとする。

40

【0195】

走査ドライバ50は、表示エリア及び非表示エリアJ、Kのラインブロックを含む全走査ラインを順次走査駆動するフレームを1フレーム目とした場合に、例えば図18(B)に示すように2フレームを空けた4フレーム目で、LCDパネル20の全走査ラインを順次走査駆動する。すなわち、図18(B)では、3フレーム周期でLCDパネル20の全走査ラインを走査駆動している。

【0196】

例えば1フレーム目の液晶容量の印加電圧の極性が正の場合、4フレーム目の当該液晶容

50

量の印加電圧の極性が負となり、7フレーム目の当該液晶容量の印加電圧の極性が正となって、交流化駆動を実現させることができる。しかも、全走査ラインを走査駆動するフレーム（1フレーム目と4フレーム目）の間の2フレーム目及び3フレーム目において、非表示エリアJ、Kに対応する走査ラインを走査駆動しないため、その分電力消費を低減させることが可能となる。

【0197】

このように、TFTを用いたアクティブマトリクス型液晶パネルにおいて、3以上の奇数（以下、特に言及しない場合も同様とする。）フレーム周期で非表示エリアの走査ラインをリフレッシュすることで、液晶容量の印加電圧の極性反転を行うとともに、TFTのリークによる弊害を防止し、不要な走査駆動の削減による消費電力の低減が可能となる。

10

【0198】

2.2.2 リフレッシュ制御

上述したリフレッシュにより、TFTを用いたアクティブマトリクス型液晶パネルにおいて、これまでに実現できなかった低消費化が可能となる。そして、さらに低消費化を追及しようとすると、フレーム周波数を低くしたり、上述のリフレッシュ周期を長くしたりすることになる。

【0199】

しかしながら、このようにすると、特にパーシャル表示制御によるウィンドウ表示を行った場合において、フレーム期間中にウィンドウの生成、消滅、移動又はサイズ変更等のウィンドウアクセス（表示エリアを設定するための上述の各種レジスタへのアクセス。表示制御イベント）などにより表示するウィンドウの状態が変化したとき、ちらつきなどにより表示品位の低下が見られる場合がある。これは、例えばTFTのリーク等の製品ばらつきに起因すると考えられ、この表示品位の低下を防止する適切なリフレッシュ制御を行うことが望ましい。

20

【0200】

そこで、本実施形態では、上述したウィンドウアクセスがあったフレームの次のフレームで、フルスキャン（全画面スキャン）を行うようにして、TFTのリークによる弊害を回避している。そして、このフルスキャンしたフレームを基準フレームとして、それ以降奇数フレーム周期でパーシャルスキャンを行う。

【0201】

30

ここで、フルスキャンとは、表示エリア及び非表示エリアに関わらず全走査ラインを走査することをいう。また、パーシャルスキャンとは、表示エリアに対応する走査ラインについて毎フレーム周期で走査し、非表示エリアに対応する走査ラインについて奇数フレーム周期で走査することをいう。

【0202】

こうすることで、製品ばらつき等の要因に伴う表示品位の低下を防止して、低消費化を実現できるパーシャル表示制御を行うことができる。

【0203】

40

このようなリフレッシュ制御を実現する具体的な方法としては、例えば次の3つの方法がある。以下、これらの方法について、詳細に説明する。

【0204】

2.2.3 第1の方法

上述したように非表示エリアに対応する走査ラインを所与の3以上の奇数フレーム周期で走査駆動するために、フレーム数をカウントするフレームカウンタを有している。例えば、このフレームカウンタは、フルスキャンを行うフレームを「0」とし、フレームごとにインクリメントを行う。そして、例えばフレームインターバルレジスタに保持された所与のフレーム数と、フレームカウンタのカウンタ値が一致したとき、フレームカウンタのカウンタ値が「0」にリセットされるように構成することができる。

【0205】

このように構成すると、フレームカウンタのカウンタ値が「0」となるフレームを検出す

50

るとフルスキャンを行い、その後は、フレームインターバルレジスタに保持されたフレーム数の周期でフルスキャンを行うことになる。

【0206】

そこで、第1の方法では、ウィンドウアクセスがあったフレームの次のフレームにおいて、フレームカウンタのカウンタ値を強制的に「0」にリセットする。

【0207】

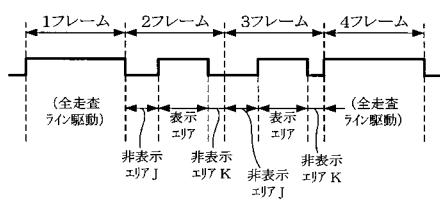

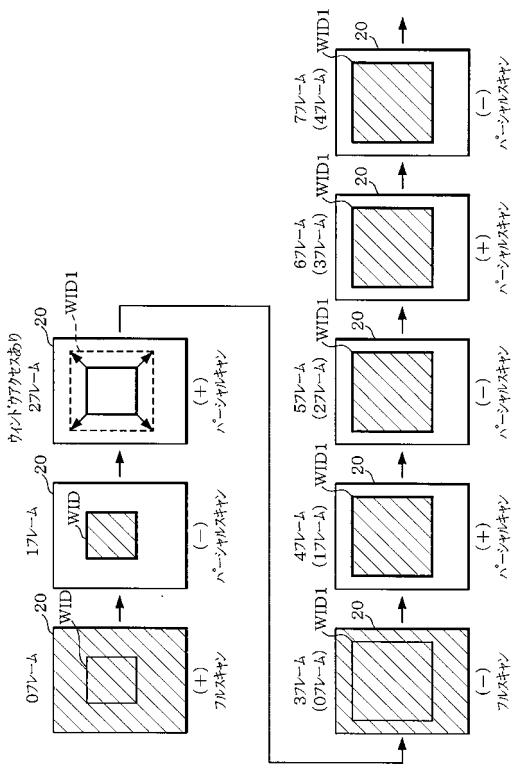

図19に、比較例として、ウィンドウアクセスがない場合のリフレッシュ動作を説明するための図を示す。

【0208】

ここで、LCDパネル20の表示領域に、信号ドライバ30及び走査ドライバ50により、ウィンドウWIDが設定されている場合を考える。このウィンドウWID内は、表示エリアとしてテキストや文字等の静止画像や動画像が表示される。

10

【0209】

なお、以下では、0フレーム目を基準フレームとして、奇数フレーム周期として例えば5フレーム周期でフルスキャンが行われるものとする。すなわち、表示エリアに対応する走査ラインは毎フレーム周期で走査されるが、非表示エリアに対応する走査ラインは5フレーム周期で走査されることになる。ここで、表示エリアに対応する走査ラインは、少なくともその一部が表示エリアに含まれる走査ライン（表示走査ライン）をいい、非表示エリアに対応する走査ラインは、それ以外の走査ライン（表示走査ラインを除く非表示走査ライン）をいう。

20

【0210】

また、フルスキャン及びパーシャルスキャンは、フレーム反転駆動方式若しくはライン反転駆動方式によりフレームごとにTFTの液晶容量の印加される極性の反転が行われるものとする。

【0211】

図19に示すように、0フレーム目では、正極性（+）で、表示エリア及び非表示エリアに関わらず、LCDパネル20の表示領域の全走査ラインに対して走査駆動が行われる（フルスキャン）。

【0212】

次の1～4フレーム目では、フレームごとに極性を反転させながら、表示エリアとしてウィンドウWID内に対応する走査ラインのみ走査駆動が行われる（パーシャルスキャン）。

30

【0213】

この0フレーム目から4フレーム目までは、フレームカウンタによりフレーム数のカウントが行われており、4フレーム目の次のフレーム目でカウンタ値が「0」にリセットされる。ただし、極性は、4フレーム目の正極性（+）が反転し、負極性（-）となる。

【0214】

そして、5フレーム目（0フレーム）では、負極性（-）でフルスキャンが行われ、これ以降の6～9フレーム目（1～4フレーム）では、フレームごとに極性を反転させながら、パーシャルスキャンが行われる。

40

【0215】

さらに、次の10フレーム目では、再びカウンタ値が「0」にリセットされ、9フレーム目の負極性（-）が反転した正極性（+）で、フルスキャンが行われ、以下これを繰り返す。

【0216】

図20に、第1の方法において、ウィンドウアクセスがあった場合のリフレッシュ動作を説明するための図を示す。

【0217】

ここでは、2フレーム目のフレーム期間中において、ウィンドウWIDからウィンドウWID1にサイズが変更された場合を示している。

50

## 【0218】

第1の方法では、上述したように、パーシャルスキャンを行っている2フレーム目(正極性(+) )でウィンドウアクセスがあったとき、次の3フレーム目(負極性(-) )でフルスキャンを行う。

## 【0219】

そして、次の4フレーム目(正極性(+) )で、サイズ変更後のウィンドウWID1について、パーシャルスキャンを行った後、5フレーム目(0フレーム)(負極性(-) )で再びフルスキャンを行う。

## 【0220】

これ以降の6~9フレーム目(1~4フレーム)では、フレームごとに極性を反転させながら、パーシャルスキャンが行われる。 10

## 【0221】

さらに、次の10フレーム目では、再びカウンタ値が「0」にリセットされ、9フレーム目の負極性(-)が反転した正極性(+)で、フルスキャンが行われ、以下これを繰り返す。

## 【0222】

こうすることで、サイズ変更等のウィンドウアクセスにより、ちらつきが見えてしまう場合であっても表示品位を低下させることなく、低消費化を図ることができる。

## 【0223】

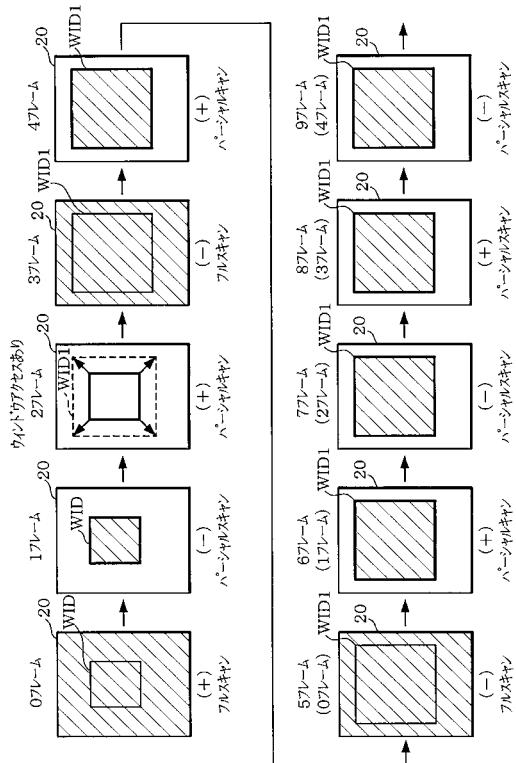

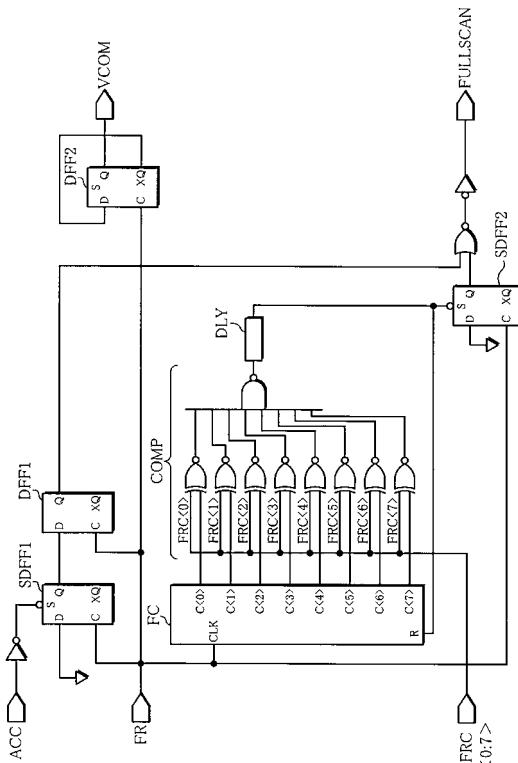

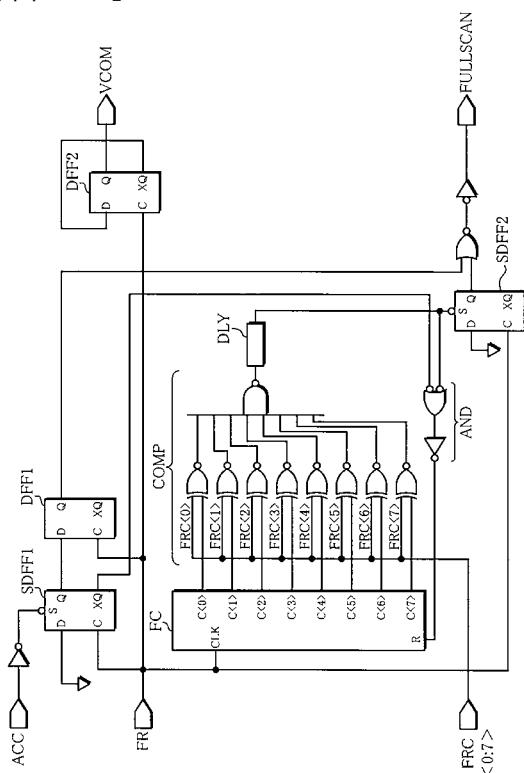

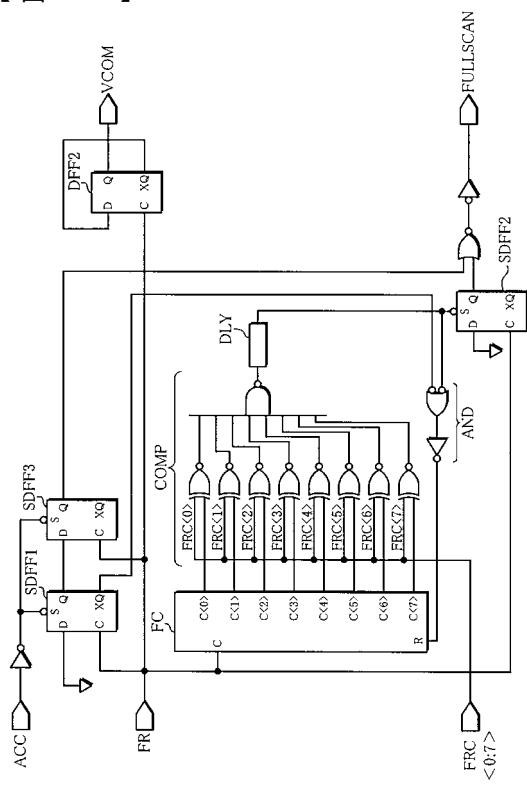

図21に、第1の方法を実現するための回路構成の一例を示す。 20

## 【0224】

ここで、ACCは、上述したウィンドウアクセスがあったときに論理レベル「H」になる信号である。FRは、極性反転化信号であり、フレームごとに供給されるパルス信号である。FRC<0:7>は、フレームインターバルレジスタに設定されたフレーム周期で、8ビットの信号である。VCOMは、対向電極の極性を反転するためのタイミング信号であり、図21に示すように、FR信号に同期して反転する信号である。FULLSCANは、上述したフルスキャンを行うための信号である。当該走査ラインの走査タイミングで、FULLSCANの論理レベルが「H」のとき、表示エリア及び非表示エリアに関わらず、走査駆動を行う。

## 【0225】

FRは、SDF1、SDF2、DF1、DF2、FCのクロック(C)端子に供給されている。SDF1、SDF2は、セット付きDフリップフロップで、DF1、DF2はDフリップフロップである。FCは、8ビットのフレームカウンタで、C端子に入力される信号のエッジに同期して1ずつインクリメントし、リセット(R)端子に入力される信号により内部のカウンタ値がリセットされる。 30

## 【0226】

DF2の反転出力データ(XQ)端子は、データ(D)端子とは互いに接続され、出力データ(Q)端子がVCOMとなる。

## 【0227】

ACCは、SDF1のセット(S)端子に供給されている。 40

## 【0228】

SDF1及びSDF2のD端子は、接地レベルに接続され、DF1のD端子は、SDF1のQ端子に接続される。

## 【0229】

FRC<0:7>は、COMPに供給される。COMPは、8ビットのコンパレータであり、FCの8ビット出力C<0:7>と、FRC<0:7>とをビットごとに一致するか否か判定することができる。

## 【0230】

COMPの出力は、DLYを介して、SDF2のS端子とFCのR端子に供給される。

DLYは、遅延素子である。FCの出力がFRC<0:7>と一致したときに、所与の遅 50

延時間経過後、F C のカウンタ値がリセットされる。

【0231】

D F F 1 の Q 端子の出力と S D F F 2 の Q 端子の出力との論理和が、F U L L S C A N となる。

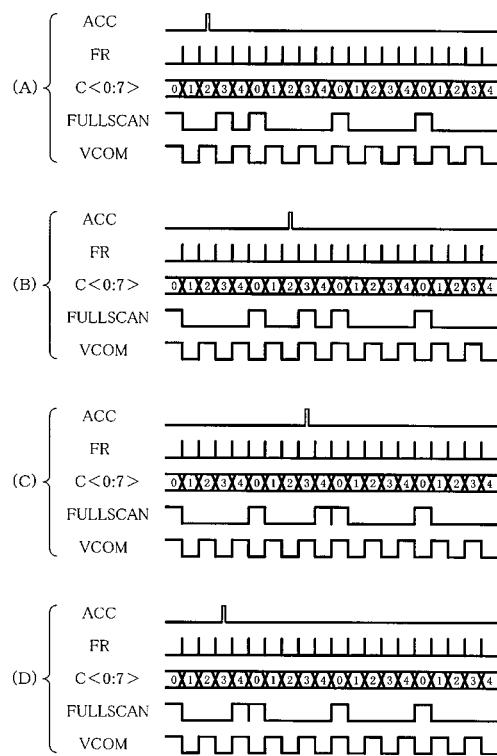

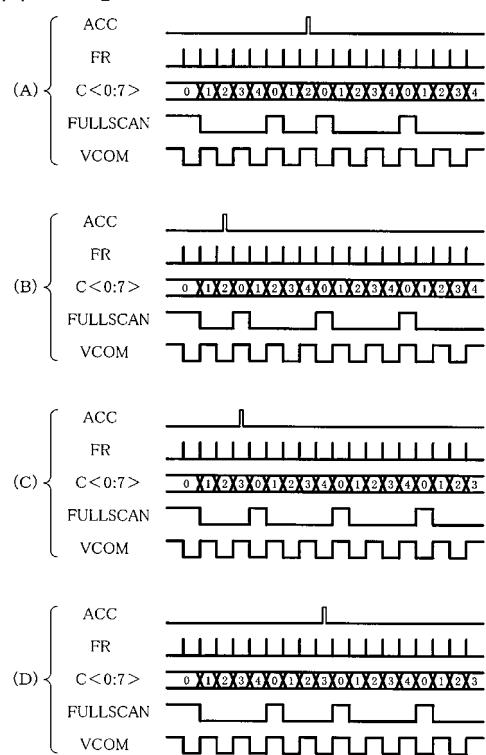

【0232】

図 22 ( A )、( B )、( C )、( D ) に、図 21 に示す回路におけるタイミングチャートを示す。

【0233】

ここで、図 22 ( A ) は、2 フレーム目で V C O M が正論理のときにウインドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図 22 ( B ) は、2 フレーム目で V C O M が負論理のときにウインドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図 22 ( C ) は、3 フレーム目で V C O M が正論理のときにウインドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図 22 ( D ) は、3 フレーム目で V C O M が負論理のときにウインドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。

【0234】

このように、ウインドウアクセスのあったフレームの次のフレームで、F U L L S C A N の論理レベルが「H」となっている。LCDコントローラ 60 は、例えば、F U L L S C A N が論理レベル「H」となると、ゲートドライバ 50 に対してコマンドを送出して、表示エリア及び非表示エリアに関わらず、当該走査ラインを走査駆動するように設定する。こうすることで、ゲートドライバ 50 により、フルスキャンが行われる。

【0235】

#### 2.2.4 第 2 の方法

第 1 の方法では、ウインドウアクセスがあった場合、フルスキャンを行うフレーム周期を固定しながら、次のフレームでフルスキャンを行っていた。したがって、例えば図 20 に示すように、3 フレーム目と 5 フレーム目でフルスキャンが行われるが、いずれも負極性 ( - ) で行われるため、画面を注視する観者にとって違和感が協調される場合がある。

【0236】

そこで、第 2 の方法では、ウインドウアクセスのあったフレームの次のフレームでフルスキャンを行うとともに、フレームカウンタのカウンタ値をリセットして、それ以降所与の 3 以上の奇数フレーム周期でフルスキャンを行うようにしている。

【0237】

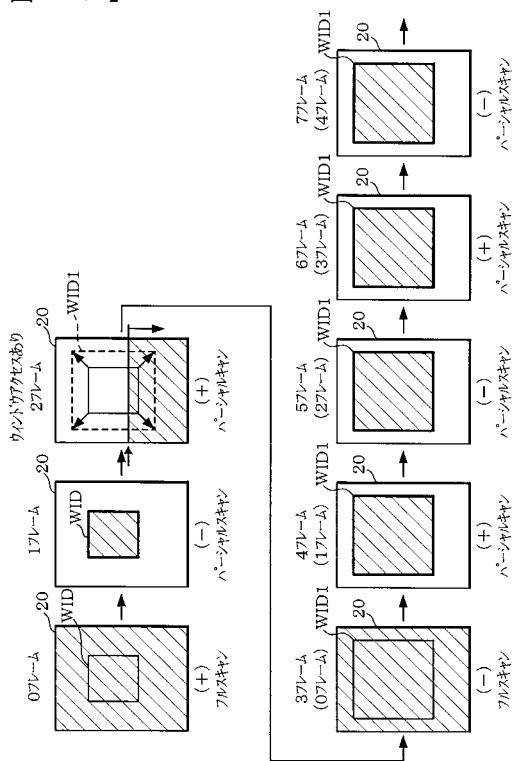

図 23 に、第 2 の方法において、ウインドウアクセスがあった場合のリフレッシュ動作を説明するための図を示す。

【0238】

ここでは、2 フレーム目のフレーム期間中において、ウインドウ W I D からウインドウ W I D 1 にサイズが変更された場合を示している。

【0239】

第 2 の方法では、上述したように、パーシャルスキャンを行っている 2 フレーム目 ( 正極性 ( + ) ) でウインドウアクセスがあったとき、次のフレーム ( 3 フレーム目 ) でフルスキャンを行う。このとき、フレームカウンタをリセットして、再び 2 フレーム目の極性を反転した負極性 ( - ) で、フルスキャンを行う。

【0240】

そして、続く 4 ~ 7 フレーム目 ( 1 ~ 4 フレーム ) では、フレームごとに極性を反転させながら、パーシャルスキャンが行われる。

【0241】

さらに、次の 8 フレーム目では、再びカウンタ値が「0」にリセットされ、7 フレーム目の負極性 ( - ) が反転した正極性 ( + ) で、フルスキャンが行われ、以下これを繰り返す。

**【0242】**

こうすることで、サイズ変更等のウィンドウアクセスにより、同極性のフルスキャンにより違和感が強調される場合がなくなり、表示品位をより一層向上させることができるようになる。

**【0243】**

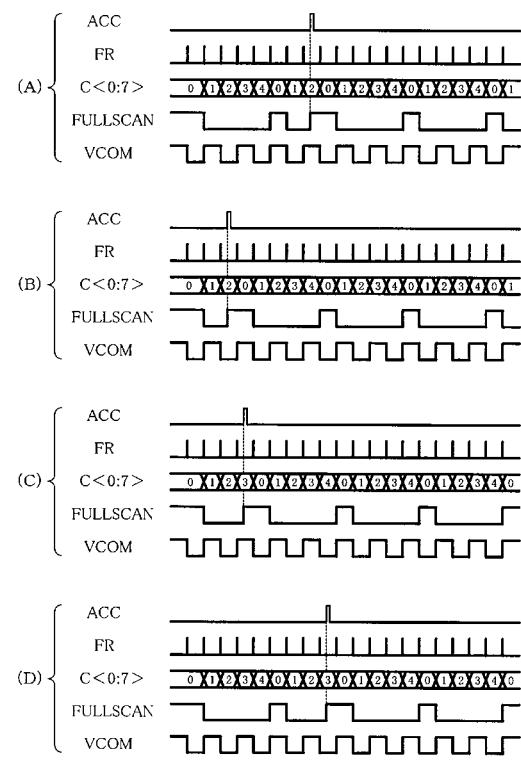

図24に、第2の方法を実現するための回路構成の一例を示す。

**【0244】**

ただし、図21に示す回路と同一部分には同一符号を付し、適宜説明を省略する。

**【0245】**

図24に示す回路が、図21に示す回路と異なる点は、SDF<sub>1</sub>からの反転出力とDL<sub>10</sub>Yの出力とのAND出力が、FCのR端子に供給されている点である。

**【0246】**

図25(A)、(B)、(C)、(D)に、図24に示す回路におけるタイミングチャートを示す。

**【0247】**

ここで、図25(A)は、2フレーム目でVCOMが正論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図25(B)は、2フレーム目でVCOMが負論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図25(C)は、3フレーム目でVCOMが正論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図25(D)は、3フレーム目でVCOMが負論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。

**【0248】**

このように、ウィンドウアクセスのあったフレームの次のフレームで、FULLSCANの論理レベルが「H」となるとともに、FCのカウンタ値も「0」にリセットされる。したがって、それ以降、ウィンドウアクセスのあったフレームの次のフレームを基準として、フレームインターバルレジスタに保持される所との3以上の奇数フレーム周期でフルスキャンが行われることになる。

**【0249】****2.2.5 第3の方法**

第2の方法では、ウィンドウアクセスがあった場合、次のフレームでフルスキャンを行い、この次のフレームを基準に、それ以降奇数フレーム周期でフルスキャンを行っていた。

**【0250】**

しかしながら、特にフレーム周波数が低い場合には、ウィンドウアクセスのあったフレームについて、表示品位が低下する場合がある。

**【0251】**

そこで、第3の方法では、第2の方法に加え、ウィンドウアクセスのあったフレームについても、ウィンドウアクセスの発生したタイミング以降、フルスキャンするようにしている。

**【0252】**

図26に、第3の方法において、ウィンドウアクセスがあった場合のリフレッシュ動作を説明するための図を示す。

**【0253】**

ここでは、2フレーム目のフレーム期間中において、ウィンドウWIDからウィンドウWID<sub>1</sub>にサイズが変更された場合を示している。

**【0254】**

第3の方法では、上述したように、パーシャルスキャンを行っている2フレーム目(正極性(+))でウィンドウアクセスがあったとき、次のフレーム(3フレーム目)でフルスキャンを行う。このとき、ウィンドウアクセスのあった2フレーム目において、例えばウ

10

20

30

40

50

インドウアクセスが発生したタイミングが、(N0-1) ライン目の走査ラインの走査タイミングとN0 ライン目の走査ラインの走査タイミングとの間である場合、N0 ライン目以降については、表示エリア及び非表示エリアに関わらず、走査ラインを走査駆動する。

【0255】

そして、フルスキャンを行った3フレーム目(0フレーム)に続く4~7フレーム目(1~4フレーム)では、フレームごとに極性を反転させながら、パーシャルスキャンが行われる。

【0256】

さらに、次の8フレーム目では、再びカウンタ値が「0」にリセットされ、7フレーム目の負極性(-)が反転した正極性(+)で、フルスキャンが行われ、以下これを繰り返す。

【0257】

こうすることで、フレーム周波数が低い場合でも、サイズ変更等のウィンドウアクセスのあったフレームで表示品位が低下することがなくなる。したがって、フレーム周波数の低下による低消費電力化と、表示品位の低下の防止とを両立させることができるようになる。

【0258】

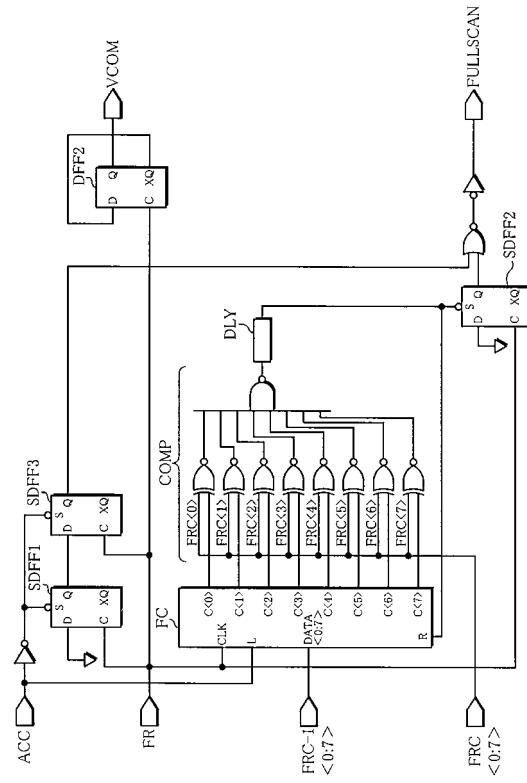

図27に、第3の方法を実現するための回路構成の一例を示す。

【0259】

ただし、図24に示す回路と同一部分には同一符号を付し、適宜説明を省略する。

20

【0260】

図27に示す回路が、図24に示す回路と異なる点は、DFF1の替わりにSDFF3が設けられている点である。SDFF3のS端子には、ACCが供給される。

【0261】

このように構成することで、ウィンドウアクセスの発生したタイミングにあわせて、FRとは非同期でSDFF3の保持データがセットされる。そして、セットされた保持データにより、ウィンドウアクセスの発生したフレーム途中にFULLSCANの論理レベルが「H」となる。

【0262】

図28(A)、(B)、(C)、(D)に、図27に示す回路におけるタイミングチャートを示す。

30

【0263】

ここで、図28(A)は、2フレーム目でVCOMが正論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図28(B)は、2フレーム目でVCOMが負論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図28(C)は、3フレーム目でVCOMが正論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。図28(D)は、3フレーム目でVCOMが負論理のときにウィンドウアクセスがあった場合の、当該回路によるリフレッシュ制御を示すタイミング図である。

40

【0264】

このように、ウィンドウアクセスのあったフレーム途中に、ACCに同期してFULLSCANの論理レベルが「H」となる。さらに、その次のフレームでもFULLSCANの論理レベルが「H」となるとともに、FCのカウンタ値も「0」にリセットされる。

【0265】

したがって、ウィンドウアクセスがあったフレームにおいて、ウィンドウアクセス発生タイミング以降の走査ラインは表示エリア及び非表示エリアに関わらず走査駆動される。そして、それ以降、ウィンドウアクセスのあったフレームの次のフレームを基準として、フレームインターバルレジスタに保持される所与の奇数フレーム周期でフルスキャンが行われることになる。

50

## 【0266】

なお、第3の方法を具体化する回路については、以下のようにすることも可能である。すなわち、例えばフルスキャンをN1(奇数)フレーム周期で行っている場合において、ウィンドウアクセスがあったときに、フレームカウンタのカウンタ値をリセットするのではなく、フレームカウンタに(N1-1)を強制的にロードする。したがって、次のフレームでは、フレームカウンタのカウンタ値はリセットされるので、上述の回路と同様の動作を行うことができる。

## 【0267】

図29に、第3の方法を実現するための回路構成の変形例を示す。

## 【0268】

ただし、図27に示す回路と同一部分には同一符号を付し、適宜説明を省略する。

10

## 【0269】

図29に示す回路が、図27に示す回路と異なる点は、FCにロード(L)端子と、DATA<0:7>端子とを設け、DLYの出力をSDFF2のS端子とFCのR端子とに供給している点である。

## 【0270】

FCのL端子には、ACCが供給される。FCのDATA<0:7>端子には、FRC-1<0:7>が供給される。FRC-1<0:7>は、FRC<0:7>で表される8ビットデータより1だけ減算した8ビットデータである。

## 【0271】

FCは、L端子に入力される信号の論理レベルが「H」となると、DATA<0:7>端子に入力される8ビットデータを内部のカウンタ値にロードする。

20

## 【0272】

このように構成することでも、ウィンドウアクセスの発生したタイミングにあわせて、FRとは非同期でSDFF3の保持データがセットされる。そして、セットされた保持データにより、ウィンドウアクセスの発生したフレーム中にFULLSCANの論理レベルが「H」となる。

## 【0273】

そして、ウィンドウアクセスのあった次のフレームではFCのカウンタ値が「0」となり、FULLSCANの論理レベルが「H」となる。

30

## 【0274】

## 2.3 ウィンドウ管理

上述したように、本実施形態におけるLCDコントローラ60は、信号ドライバ30及び走査ドライバ50に対し、それぞれ表示エリア及び非表示エリアを設定することで、ウィンドウ表示を行うことができる。

## 【0275】

本実施形態では、LCDパネル20の画面上で1又は複数のウィンドウを管理するため、RAM64上にウィンドウ管理データ(広義には、パーシャル表示制御データ)を記憶し、当該ウィンドウ管理データに基づいて各ウィンドウの表示制御を行う。より具体的には、ウィンドウ管理データを、LCDパネル20の表示領域に対応させ、表示エリアに対応したウィンドウ管理データに基づいて、LCDパネル20に表示される1又は複数のウィンドウを管理する。

40

## 【0276】

例えば、ウィンドウ管理データが「1」に設定されているアドレスに対応するLCDパネル20の表示位置を表示エリアとし、ウィンドウ管理データが「0」に設定されているアドレスに対応するLCDパネル20の表示位置を非表示エリアとすることができる。

## 【0277】

本実施形態では、このウィンドウ管理データを、各動作モードに応じて、エリアブロック単位、或いは帯パーシャルデータで指定される8走査ラインごとに分割されたラインブロック単位のいずれかを単位として、表示制御を行う。

50

## 【0278】

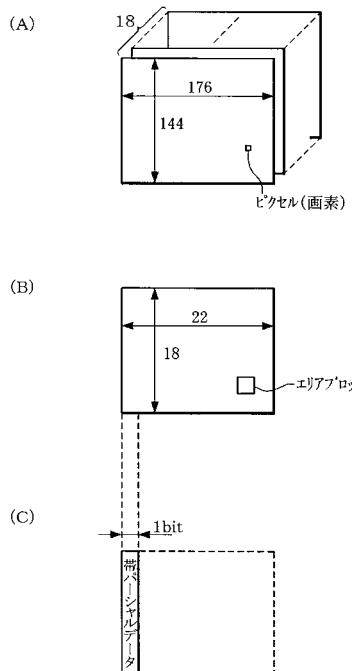

図30(A)、(B)、(C)に、各動作モードにおけるウィンドウ管理データを説明するための模式図を示す。

## 【0279】

ここで、LCDパネル20の画面サイズ(表示領域)を176×144画素とする。

## 【0280】

例えば、LCDパネル20の画面に対して設定される表示エリア若しくは非表示エリアが画素単位で設定される場合、LCDコントローラ60は、図30(A)に示すように、176×144画素分の画像データの18ビット(6ビット(階調データ)×3(RGB各色))分のメモリ領域を確保する必要がある。

10

## 【0281】

これに対して、本実施形態におけるモード設定レジスタ336によって設定される第1のモードでは、LCDパネル20の画面に対して設定される表示エリア若しくは非表示エリアは、エリアブロック単位で設定される。

## 【0282】

ここで、エリアブロックは、信号ラインを8ピクセル単位で分割し、走査ラインを8ライン単位で分割したエリアを単位とする。

## 【0283】

そのため、LCDコントローラ60は、図30(B)に示すように、22×18エリアブロック分の画像データのメモリ領域を確保する。これにより、RAM64に確保すべきメモリ領域を大幅に削減することができるようになる。

20

## 【0284】

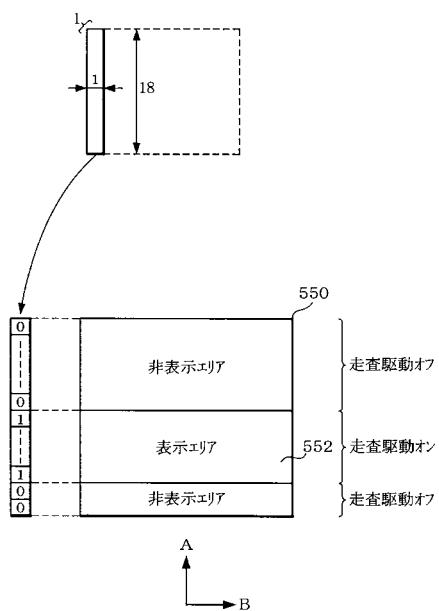

また、モード設定レジスタ336によって設定される第2のモードでは、LCDパネル20の画面に対して設定される表示エリア若しくは非表示エリアは、帯パーシャルデータにより、走査ラインの並び方向にのみ8走査ライン単位で設定される。

## 【0285】

そのため、LCDコントローラ60は、図30(C)に示すように、18ラインブロック分の帯パーシャルデータを、制御レジスタ330の帯パーシャルデータレジスタ338に保持する。これにより、RAM64にメモリ領域を確保する必要がなくなる。

## 【0286】

30

## 2.3.1 第1のモード

第1のモードでは、エリアブロック単位で管理されるウィンドウ管理データに基づいて、LCDパネル20の表示領域の該当位置にウィンドウが表示される。

## 【0287】

図31に、比較例として、画素単位で管理されるウィンドウ管理データに基づいて、ウィンドウ表示を行う場合の座標指定を模式的に示す。

## 【0288】

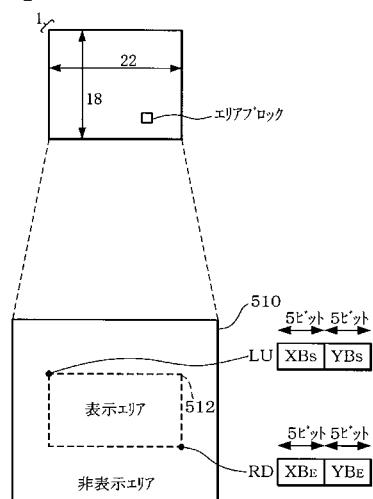

この場合、LCDコントローラ60は、LCDパネル20の表示領域500の表示エリア502に矩形のウィンドウ表示させるためには、表示エリア502の左上座標LU(X<sub>s</sub>, Y<sub>s</sub>)及び右下座標RD(X<sub>e</sub>, Y<sub>e</sub>)を指定する。

40

## 【0289】

したがって、ウィンドウ管理データが画素単位で管理された場合には、176×144画素を特定するために、各座標を指定するために必要なビット数は「8」となる。すなわち、表示エリア502を指定するためには、少なくとも32ビット((8ビット+8ビット)×2)が必要となる。ウィンドウ管理データにより、3つのウィンドウを同時に管理できるようにした場合には、表示エリアを指定するために96ビットが必要となる。

## 【0290】

図32に、第1のモードにおいて、エリアブロック単位で管理されるウィンドウ管理データに基づいて、ウィンドウ表示を行う場合の座標指定を模式的に示す。

## 【0291】

50

第1のモードでは、LCDコントローラ60は、LCDパネル20の表示領域510の表示エリア512に矩形のウィンドウ表示させるためには、表示エリア512の左上座標LU(XBs, YBs)及び右下座標RD(XBe, YBe)を指定する。

【0292】

エリアブロック単位で管理されるウィンドウ管理データ(エリアブロック表示制御データ)は、 $22 \times 18$ エリアブロックのうちいずれかのエリアブロックを特定するために、各座標位置に必要なビット数は「5」となる。すなわち、表示エリア512を指定するためには、少なくとも20ビット( $(5\text{ビット} + 5\text{ビット}) \times 2$ )が必要となる。ウィンドウ管理データにより、3つのウィンドウを同時に管理できるようにした場合には、表示エリアを指定するために60ビットだけでよく、画素単位でウィンドウを管理する場合に比べて、ウィンドウ指定を効率化できる。10

【0293】

ここで、LCDパネル20のB方向に走査ラインが延びる場合、当該走査ラインを走査駆動する走査ドライバ50が、LCDパネル20に対して図33に示す位置に配置されているものとする。

【0294】

まずLCDコントローラ60は、ホストによって、表示エリア若しくは非表示エリアに対応するウィンドウ管理データが設定される。

【0295】

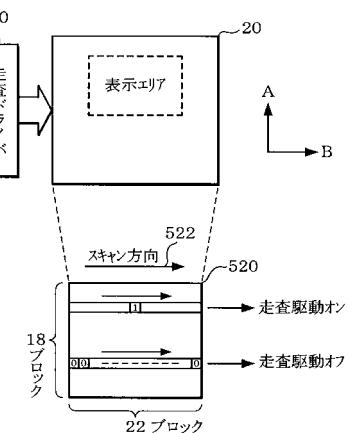

上述したパーソナル表示制御を行うLCDコントローラ60は、第1のモードにおいて、各エリアブロック単位に設定されたウィンドウ管理データ520を、スキャン方向522に沿ってスキャンする。20

【0296】

スキャン方向522に沿ってウィンドウ管理データ520を1ラインごとにスキャンしたときに、「1」が設定されたエリアブロックが少なくとも1つ存在する場合には、対応する走査ラインが走査駆動オンであると判断して、LCDコントローラ60のコマンドシーケンサ(広義には、走査駆動回路設定手段、信号駆動回路設定手段)70は、走査ドライバ50及び信号ドライバ30に対し、表示エリアを設定する。より具体的には、コマンドシーケンサ70は、走査ドライバ50のパーソナル走査表示選択レジスタを、パーソナル走査表示データ322に基づいて設定し、信号ドライバ30のブロック出力選択レジスタ及びパーソナル表示選択レジスタを、ブロック出力選択データ312及びパーソナル走査データ314に基づいて設定する。そして、コマンドシーケンサ70は、走査ドライバ50に対し、当該走査ラインの走査タイミングに合わせて、走査イネーブル入出力信号GEIOを供給し、信号ドライバ30に対し、所与の水平走査周期で、1走査ライン分ごとに画像データを、信号ドライバ30に対し逐次供給する。30

【0297】

これに対して、スキャン方向522に沿ってデータをスキャンしたときに、1ライン分のエリアブロック全てが「0」に設定されている場合には、当該走査ラインが走査駆動オフであると判断する。上述したように、LCDパネル20に対しては、周期的に走査駆動を行ってTFTのリーケによって液晶容量に蓄積される電荷を放電する必要がある。そのため、走査駆動オフであると判断された走査ラインに対しては、所与の基準フレームを基準とした任意の奇数フレーム周期で走査駆動され、それ以外の周期では走査駆動されない。したがって、LCDコントローラ60(コマンドシーケンサ70)は、走査駆動するフレームにおいてのみ、当該走査ラインの走査タイミングに合わせて、出力イネーブル信号XOEVを供給することになる。40

【0298】

ここで、所与の基準フレームとしては、例えばウィンドウの生成、消滅、変更などのイベントが発生して、上述した信号ドライバ設定レジスタ310、走査ドライバ設定レジスタ320若しくは制御レジスタ330のいずれかへのアクセスタイミングに対応したフレームをいう。すなわち、これら各種レジスタへのアクセスによって、表示されるウィンドウ50

が変更になったフレームを基準として、任意の奇数フレーム周期で非表示エリアの走査ラインが走査駆動されることになる。

【0299】

なお、上述したように、信号ドライバ30及び走査ドライバ50は、24出力単位及び8走査ライン単位で出力制御されるため、各ウィンドウを24出力単位及び8走査ライン単位で指定するようにしたが、これに限定されるものではなく、LCDコントローラ60は、ウィンドウ管理データを画素単位で管理することも可能である。

【0300】

なお、ここでは、信号ドライバ30及び走査ドライバ50の出力制御単位となる各ラインブロックを、24出力若しくは8走査ラインを単位として説明したが、これに限定されるものではなく、例えば各ラインブロックについて24出力以下若しくは8走査ライン以下を単位とすることも可能である。

10

【0301】

2.3.2 第2のモード

図34に、第2のモードにおいて、帯パーシャルデータに基づいて、ウィンドウ表示を行う場合の座標指定を模式的に示す。

【0302】

第2のモードでは、LCDコントローラ60は、LCDパネル20の表示領域550に表示エリア552を設定するために、帯パーシャルデータ（帯パーシャル表示制御データ）により、8走査ライン単位で表示エリア若しくは非表示エリアを指定する。

20

【0303】

したがって、表示エリア552を特定するために、必要なビット数は8走査ライン単位で1ビットのみである。これにより、表示エリアを指定するためのビット数を大幅に削減することができるようになる。

【0304】

ここで、図33に示したように、LCDパネル20のB方向に走査ラインが延びるものとすると、まずLCDコントローラ60は、表示エリア若しくは非表示エリアに対応した帯パーシャルデータが、図示しないホストによって設定される。

【0305】

上述したパーシャル表示制御を行うLCDコントローラ60は、第2のモードにおいて、帯パーシャルデータを参照し、「1」が設定されたラインブロックの走査ラインは走査駆動オンであると判断する。この場合、LCDコントローラ60のコマンドシーケンサ（広義には、走査駆動回路設定手段）70は、走査ドライバ50に対し、表示エリアを設定する。より具体的には、コマンドシーケンサ70は、走査ドライバ50のパーシャル走査表示選択レジスタを、パーシャル走査表示データ322に基づいて設定する。そして、コマンドシーケンサ70は、走査ドライバ50に対し、当該走査ラインの走査タイミングに合わせて、走査イネーブル入出力信号GEOを供給する。コマンドシーケンサ70は、信号ドライバ30に対し、所与の水平走査周期で、1走査ライン分ごとに画像データを逐次供給する。

30

【0306】

これに対して、帯パーシャルデータが「0」に設定されたラインブロックの走査ラインは、走査駆動オフであると判断する。上述したように、LCDパネル20に対しては、周期的に走査駆動を行ってTFTのリーキによって液晶容量に蓄積される電荷を放電する必要がある。そのため、走査駆動オフであると判断された走査ラインに対しては、所与の基準フレームを基準とした任意の奇数フレーム周期で走査駆動され、それ以外の周期では走査駆動されない。したがって、LCDコントローラ60（コマンドシーケンサ70）は、走査駆動するフレームにおいてのみ、当該走査ラインの走査タイミングに合わせて、出力イネーブル信号XOVEを供給することになる。

40

【0307】

本実施形態におけるLCDコントローラ60は、このようなモード設定レジスタ336に

50

によるモード切り替えを実現させることにより、メモリ容量の効率化と、表示ウィンドウ指定の簡略化とを図る。

【0308】

2.4 定型データの生成

LCDコントローラ60は、上述したように信号ドライバ30及び走査ドライバ50に対して、表示エリアを設定するとともに、当該表示エリアに対応する画像データを、信号ドライバ30に対して供給する。この画像データは、例えばユーザによって作成され、LCDコントローラ60に対して供給されるものである。

【0309】

ところで、上述した信号ドライバ30は、ブロック出力選択データにより、LCDパネル20のパネルサイズの変化に対応することができる。そのため、不要なラインブロックの信号ラインについて信号駆動を行わない。したがって、このままでは、ユーザは、作成した画像データをLCDコントローラ60に対して供給する場合、どのラインブロックの信号ラインについて信号駆動を行わないかを把握しておく必要がある。すなわち、ユーザは、当該ラインブロックを除外して信号駆動を行った場合に正常な画像が表示できるように、生成した画像データを加工してLCDコントローラ60に供給する必要がある。

【0310】

そこで、本実施形態におけるLCDコントローラ60は、ユーザの使い勝手を向上させるべく、ブロック出力選択データに応じて信号ドライバ30に対する画像データを生成することができるようになっている。これにより、ユーザは、信号ドライバ30において設定されたブロック出力選択データを認識することなく（どのラインブロックの信号ラインが信号駆動を行わないかを把握する必要がなく）、生成した画像データをそのままLCDコントローラ60に供給するだけで良い。

【0311】

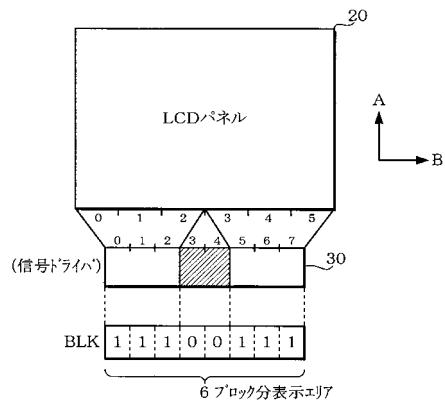

以下では、この点について具体的に説明する。

【0312】

ここで、LCDパネル20の表示領域がB方向に6ラインブロックに分割され、A方向については考慮しないものとする。また、信号ドライバ30は、例えば24出力単位に分割された8ラインブロックの信号ラインに対し、信号駆動できるものとする。

【0313】

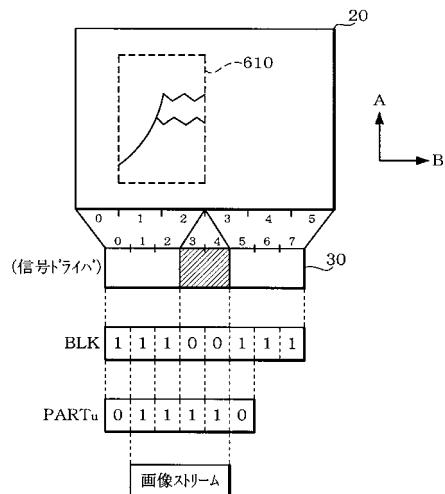

LCDパネル20に対して、信号ドライバ30により信号駆動を行う場合、6ラインブロック分の信号ラインを駆動するために、ブロック出力選択データにより、中心付近の2ラインブロックを除く。すなわち、図35に示すように、例えばシステム投入時に、ブロック出力選択データにより「11100111」を設定する。

【0314】

したがって、信号ドライバ30は、BLK0～BLK2及びBLK5～BLK7の信号ラインのみを信号駆動し、BLK3、BLK4の信号ライン駆動回路の出力をハイインピーダンス状態とする。信号ドライバ30のBLK0～BLK2及びBLK5～BLK7は、それぞれLCDパネル20のブロック番号0～5の信号ラインを信号駆動する。

【0315】

このようなLCDパネル20に対して、ユーザがB方向に4ラインブロック分の画像データを生成した場合を考える。

【0316】

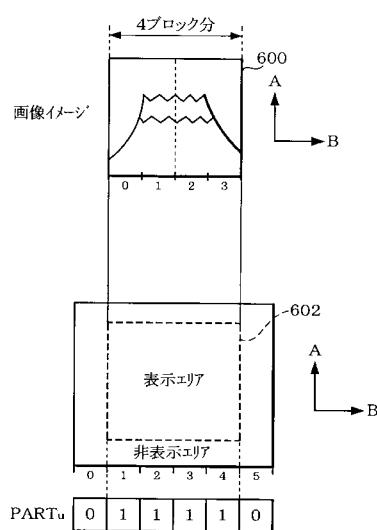

図36に、例えばユーザによって作成される画像イメージを模式的に示す。

【0317】

ユーザが、B方向に4ラインブロック分の1フレームの画像イメージを作成し、これをLCDパネル20の表示領域の表示エリア602に表示させる場合、ユーザは表示領域である6ラインブロック分のパーシャル表示データに対して、表示エリアに対応するラインブロックを「1」に設定する。

【0318】

10

20

30

40

50

一般的に、ユーザ（画像開発者）はLCDパネル20を信号駆動する信号ドライバ30について、どのラインブロックを用いるかについて把握していない。これは、LCDパネル20を信号駆動する信号ドライバ30のどの信号ラインを用いるかは、メーカー側の設計方針によって任意に決められることになるからである。そこで、ユーザは、ラインブロックのブロック番号0～5のうち、ブロック番号1～4の計4ラインブロックを表示エリアとして設定する。すなわち、ユーザは、パーシャル表示データPARTuとして「011110」を設定する。

#### 【0319】

この場合、図37に示したように、信号ドライバ30のBLK3及びBLK4に対して、パーシャル表示データPARTuによりユーザが設定した表示エリアが重複して設定されることになる。したがって、パーシャル表示データPARTuに対応して画像ストリーム（画像データ）が供給されたとしても、ブロック出力選択データとパーシャル表示データとがともに「1」に設定されたラインブロックのみが信号駆動されることになり、その結果として画像610が表示されることになる。

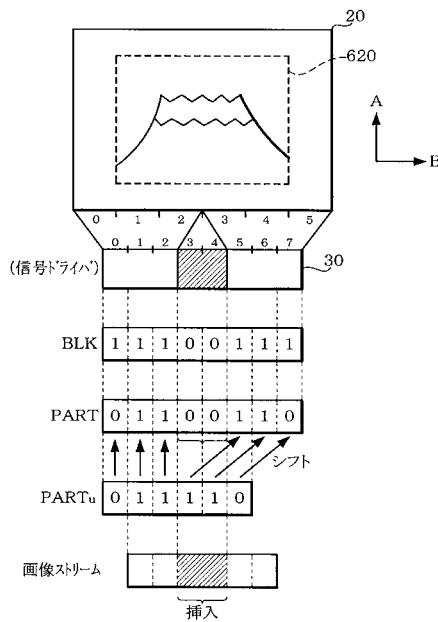

#### 【0320】

そこで、本実施形態では、ブロック出力選択データにおいて「0」が設定されているラインブロックに対応するパーシャル表示データPARTuをシフトすることによって、ユーザがブロック出力選択データの設定値を考慮することなく正しく表示エリアに対応した画像を表示させることができるようになっている。また、これに対応して画像ストリームをシフトして、定型フォーマットの画像ストリームを生成するようになっている。

#### 【0321】

より具体的には、図38に示すように、ブロック出力選択データで「0」に設定されるラインブロックに対応するパーシャル表示データPARTuを、ブロック出力選択データで「1」に設定されるラインブロックまでシフトしたパーシャル表示データPARTに変換する。そして、このパーシャル表示データPARTを、信号ドライバ30に供給する。そして、この変換の際にシフトした位置に対応する画像ストリームに、ダミーの画像データを挿入する。こうすることで、LCDパネル20のブロック番号3、4の信号ラインに対し、信号ドライバ30のBLK5及びBLK6に対応した画像ストリームに基づく信号駆動を行うことができ、正しい画像620を表示エリアに表示させることができるようになる。

#### 【0322】

そのため、本実施形態におけるLCDコントローラ60は、このようなパーシャル表示データPARTuからパーシャル表示データPARTを変換するパーシャル表示データ変換回路を含む。

#### 【0323】

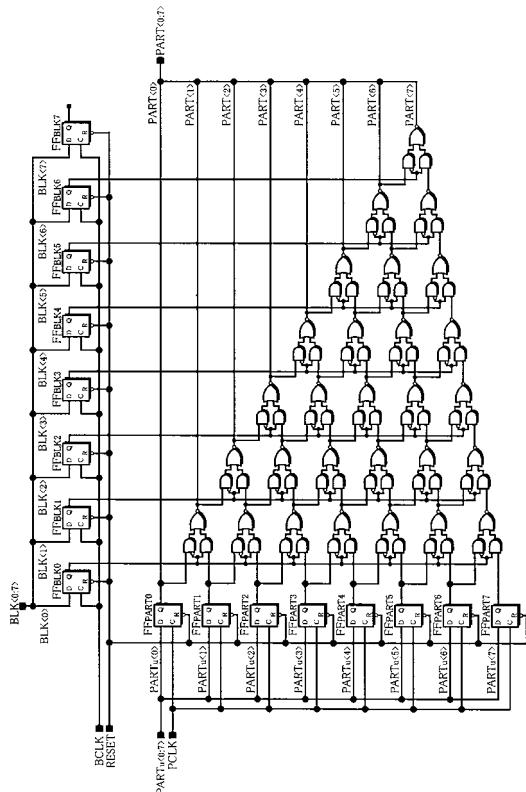

図39に、このパーシャル表示データ変換回路の一例を示す。

#### 【0324】

$F_F_{BLK0} \sim F_F_{BLK7}$ は、リセット信号RESETでリセットされ、それぞれクロック信号BCLKに同期してブロック出力選択データBLK<0:7>の計8ビットをラッチする。

#### 【0325】

$F_F_{PART0} \sim F_F_{PART7}$ は、リセット信号RESETでリセットされ、それぞれクロック信号PCLKに同期して、ユーザによって設定されるパーシャル表示データPARTu<0:7>の計8ビットをラッチする。

#### 【0326】

$F_F_{BLK0} \sim F_F_{BLK7}$ 、 $F_F_{PART0} \sim F_F_{PART7}$ の各Q端子は、セレクタ回路SELに接続される。

#### 【0327】

$F_F_{BLKa}$ 及び $F_F_{PARTb}$ の各Q端子が接続されるセレクタ回路SEL<sub>ab</sub>は、 $F_F_{BLKa}$ のQ端子から出力されるブロック出力選択データが「0」のとき、 $F_F_{PARTa-1}$ のQ端子から

10

20

30

40

50

出力されるパーシャル表示データを選択出力する。また、 $FF_{BLK_a}$ 及び $FF_{PART_b}$ の各Q端子が接続されるセレクタ回路 $SEL_{ab}$ は、 $FF_{BLK_a}$ のQ端子から出力されるブロック出力選択データが「1」のとき、 $FF_{PART_a}$ のQ端子から出力されるパーシャル表示データを選択出力する。

【0328】

したがって、ブロック出力選択データが「0」に設定されたラインブロックについては、パーシャル表示データ $PART_u$ （第1のパーシャル表示データ）が順次シフトされたパーシャル表示データ $PART$ （第2のパーシャル表示データ）が生成されることになる。

【0329】

LCDコントローラ60（コマンドシーケンサ（広義には、ブロック出力選択データ設定手段、パーシャル表示データ設定手段）70）は、ブロック出力選択データとともにこのパーシャル表示データ $PART$ を、信号ドライバ30の対応するレジスタに対して設定することになる。

【0330】

同様にして、画像データ生成回路300において、当該シフトされたラインブロックにダミーの画像データを挿入した画像データを生成し、定型の8ラインブロック分の画像ストリームを、信号ドライバ30に供給する。

【0331】

より具体的には、画像データ生成回路300は、表示エリア若しくは非表示エリアが指定されたユーザによるパーシャル表示データ $PART_u$ （第1のパーシャル表示データ）により表示エリアに指定された第Pのブロックが、前記ブロック出力選択データにより信号駆動しないラインブロックとして指定されたときに、信号ドライバ30に対して供給される画像データについて、第Pのブロックに対応する画像データを第 $(P + 1)$ のブロックの画像データとしてシフトした画像ストリームに変換する。そして、コマンドシーケンサ70によって、この変換した画像ストリームが、コマンドシーケンサ70によって供給される。

【0332】

こうすることで、上述したように、ユーザはブロック出力選択データの設定値を認識することなく、LCDパネル20のパネルサイズに柔軟に適応可能な信号ドライバ30を用いて設定された表示エリアに、正しい画像を表示させることができる。

【0333】

## 2.5 コマンド指定

LCDコントローラ60は、信号ドライバ30に対して、次のように画像ストリームを供給することができる。

【0334】

すなわち、図40（A）に示すように、表示エリアを指定するコマンド（CMD）を送信してから一連の画像ストリームを供給する場合と、図40（B）に示すように、一連の画像ストリームを送信してから表示エリアを指定するコマンド（CMD）を送信する場合とがある。ここで、コマンド（CMD）とは、例えば信号ドライバ30のブロック出力選択レジスタや、パーシャル表示選択レジスタの設定を含む。

【0335】

図40（A）に示すように、表示エリアを指定するコマンド（CMD）を送信してから一連の画像ストリームを供給する場合では、表示エリアに対応する画像データのみを供給すればよく、供給すべき画像データ量を減らすことができる。また、コマンドを受けてから、画像ストリームを取り込むため、コマンドで指定される非表示エリアの部分の画像データの取り込みを停止させることができ、その分低消費化を図ることができる。

【0336】

一方、図40（B）に示すように、一連の画像ストリームを送信してから表示エリアを指定するコマンド（CMD）を送信する場合では、表示領域全エリア分の画像データを供給する必要があるが、その分供給すべき画像データの生成処理を簡素化し、フレーム周波

10

20

30

40

50

数の増加や画像サイズの増大に伴って処理すべき時間が短くなった場合でも、安定した画像データの供給が可能となる。

【0337】

2.6 表示制御タイミングの一例

このような本実施形態におけるLCDコントローラ60によるパーシャル表示制御の一例を具体的に説明する。

【0338】

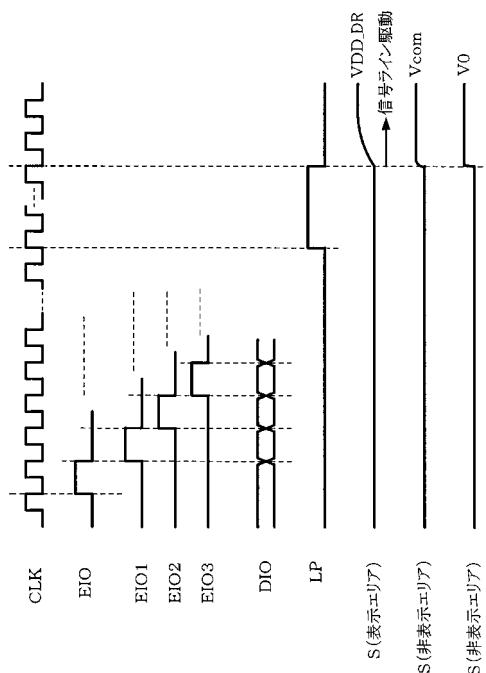

図41に、本実施形態におけるLCDコントローラ60によってパーシャル表示制御された信号ドライバ30の動作タイミングの一例を示す。

【0339】

上述したようにLCDコントローラ60によって、ラインブロック単位で表示エリア若しくは非表示エリアが設定された信号ドライバ30において、シフトレジスタは、クロック信号CLKに同期して、イネーブル入出力信号EIOがシフトされて、EIO1～EIO<sub>L</sub>（Lは、2以上の自然数）を生成する。そして、各EIO1～EIO<sub>L</sub>に同期してラインラッチに、画像データ（DIO）が順次ラッチされる。

【0340】

ラインラッチ36は、水平同期信号LPの立ち上がりに同期して、一水平走査単位の画像データをラッチし、その立ち下がりからDAC38及び信号ライン駆動回路40により信号ラインの駆動を行う。

【0341】

LCDコントローラ60によって、表示エリアに設定されたラインブロックの信号ラインについては、階調データに基づいて生成された駆動電圧に基づいて信号ラインが駆動される。一方、LCDコントローラ60によって、非表示エリアに設定されたラインブロックの信号ラインについては、対向電極電圧Vcom若しくは、階調電圧レベルの両端の電圧のうちの一方が選択出力される。

【0342】

また、ブロック出力非選択が選択されたラインブロックの信号ラインは、ハイインピーダンス状態に設定される（図示せず）。

【0343】

図42に、本実施形態におけるLCDコントローラ60によってパーシャル表示制御された走査ドライバ50の動作タイミングの一例を示す。

【0344】

ここでは、LCDコントローラ60によって、ブロックB1のみが表示エリアに設定され、ブロックB0、B2、…が非表示エリアに設定されているものとする。

【0345】

走査ドライバ50は、上述したように例えば1フレーム目及び4フレーム目において、ブロックB0～BQに対応する全走査ラインを順次走査駆動し、例えば2フレーム目及び3フレーム目において、表示エリアに設定されたブロックB1の走査ラインのみを走査駆動する。

【0346】

より具体的には、走査ドライバ50は、2フレーム目及び3フレーム目において、表示エリアに設定されたラインブロックの走査ラインにのみイネーブル入出力信号EIOが供給される。したがって、走査ドライバ50は、表示エリアに対応する期間T11のみを走査駆動する。このとき、LCDコントローラ60により制御される信号ドライバ30は、表示エリアに対応した画像データに基づいて信号ラインを駆動する。こうすることで、表示エリアに対応する走査タイミングだけ駆動を行えばよく、2フレーム目及び3フレーム目においては、走査駆動停止期間T12を設けることができる。

【0347】

このため、2フレーム目及び3フレームにおいて、走査駆動停止期間の分だけ走査駆動する必要がなくなるので、その分低消費化が可能となる。

10

20

30

40

50

## 【0348】

ここで、各フレームにおいては、非表示エリアの信号ラインに対し、信号ドライバ30により、液晶容量に印加される電圧が所与の閾値を越えないように所与の非表示レベル電圧が供給されるため、設定された表示エリアのみに所望の画像を表示するウィンドウを設定することができる。

## 【0349】

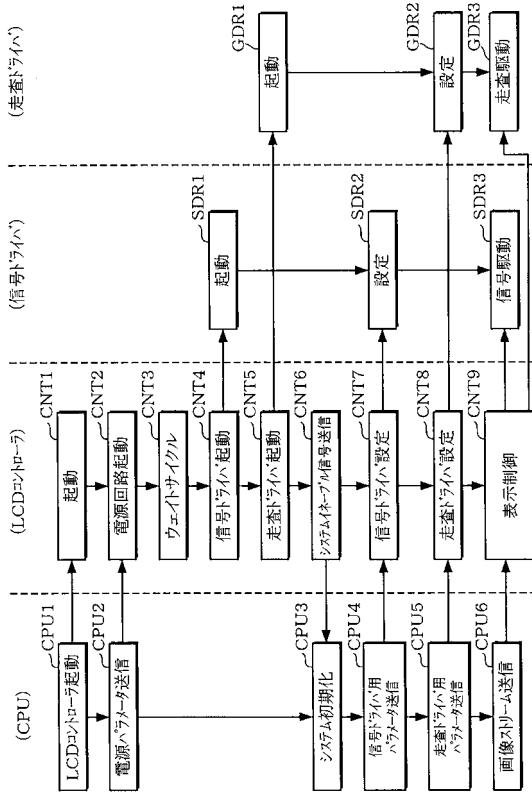

## 2.7 起動シーケンス

以上説明したようなLCDコントローラ60は、CPU等のホストにより設定された内容にしたがって、信号ドライバ30及び走査ドライバ50を制御することで、LCDパネルの表示制御を行う。

10

## 【0350】

したがって、本実施形態における表示装置の起動後のシーケンス（特にLCDコントローラの起動後のシーケンス）について、何ら考慮することなく個別に起動した場合、起動していない回路に対してパラメータが送信される等の不具合によって、正常に動作しない場合がある。

## 【0351】

本実施形態では、以下のような手順で信号ドライバ30及び走査ドライバ50を起動させた後に、所望の画像を表示させる。

## 【0352】

図43に、本実施形態における表示装置の起動シーケンスを模式的に示す。

20

## 【0353】

まず、システム電源投入時に、一斉にリセットを活性化した後、ホストからLCDコントローラ60を起動させる（CPU1）。これは、例えばLCDコントローラ60のリセットを解除することで実現することができる。

## 【0354】

LCDコントローラ60は、これを受けて起動する（CNT1）。

## 【0355】

また、ホストは、電源回路の昇圧効率や降圧効率を決定づける昇圧・降圧クロックの周波数などのパラメータをLCDコントローラ60に対して送信する（CNT2）。本実施形態は、LCDコントローラ60により電源回路が制御される。そこで、LCDコントローラ60は、電源回路を起動（リセットを解除）し（CNT2）、所与のウェイトサイクルが経過するのを待つ（CNT3）。LCDコントローラ60は、所与のウェイトサイクル経過後（CNT3）、信号ドライバ30を起動（リセットを解除）させ（CNT4）、走査ドライバ50を起動させる（CNT5）。

30

## 【0356】

これにより、LCDコントローラ60からの指示を受けた信号ドライバ30、走査ドライバ50が、起動する（SDR1、GDR1）。

## 【0357】

次に、LCDコントローラ60は、表示装置の起動の準備が整ったことをホストに通知するため、システムイネーブル信号を送信する（CNT6）。これを受けたホストは、システム初期化を行う（CPU3）。

40

## 【0358】

さらに、ホストは、信号ドライバ用パラメータ、走査ドライバ用パラメータを、LCDコントローラ60に送信する（CPU4、CPU5）。ここで、信号ドライバ用パラメータとは、例えばブロック出力選択レジスタの設定データや、パーシャル表示選択レジスタの設定データなどをいう。また、走査ドライバ用パラメータとは、例えばパーシャル走査表示選択レジスタの設定データなどをいう。

## 【0359】

LCDコントローラ60は、ホストから信号ドライバ用パラメータを受け取ると、その内容にしたがって信号ドライバ30に対して設定する処理を行う（CNT7、SDR2）。

50

また、LCDコントローラ60は、ホストから走査ドライバ用パラメータを受け取ると、その内容にしたがって走査ドライバ50に対して設定する処理を行う(CNT8、GDR2)。

【0360】

そして、ホストは、画像ストリームをLCDコントローラ60に対して送信し(CPU6)、LCDコントローラ60は、上述したように信号ドライバ30及び走査ドライバ50に対する表示制御を行う(CNT9)。信号ドライバ30及び走査ドライバ50は、信号駆動(SDR3)及び走査駆動(GDR3)を行って、表示装置の液晶パネルに画像表示を行わせる。

【0361】

3. その他

本実施形態では、TFT液晶を用いたLCDパネルを供える液晶装置を例に説明したが、これに限定されるものではない。例えば、信号ライン及び走査ラインにより特定される画素に対応して設けられた有機EL素子を含む有機ELパネルを表示駆動する信号ドライバ及び走査ドライバにも適用することができる。

【0362】

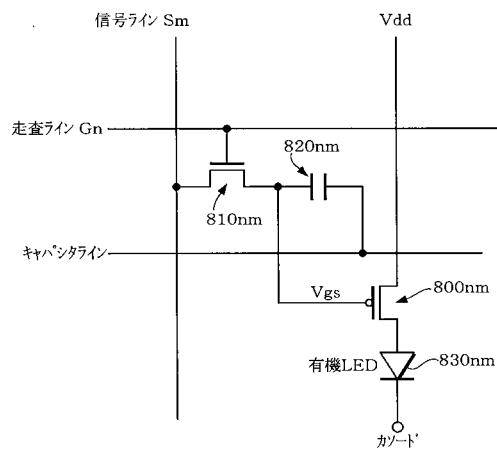

図44に、このような信号ドライバ及び走査ドライバにより表示制御される有機ELパネルにおける2トランジスタ方式の画素回路の一例を示す。

【0363】

有機ELパネルは、信号ライン $S_m$ と走査ライン $G_n$ との交差点に、駆動TFT $800_{nm}$ と、スイッチTFT $810_{nm}$ と、保持キャパシタ $820_{nm}$ と、有機LED $830_{nm}$ とを有する。駆動TFT $800_{nm}$ は、p型トランジスタにより構成される。

【0364】

駆動TFT $800_{nm}$ と有機LED $830_{nm}$ とは、電源ラインに直列に接続される。

【0365】

スイッチTFT $810_{nm}$ は、駆動TFT $800_{nm}$ のゲート電極と、信号ライン $S_m$ との間に挿入される。スイッチTFT $810_{nm}$ のゲート電極は、走査ライン $G_n$ に接続される。

【0366】

保持キャパシタ $820_{nm}$ は、駆動TFT $800_{nm}$ のゲート電極と、キャパシタラインとの間に挿入される。

【0367】

このような有機EL素子において、走査ライン $G_n$ が駆動されスイッチTFT $810_{nm}$ がオンになると、信号ライン $S_m$ の電圧が保持キャパシタ $820_{nm}$ に書き込まれるとともに、駆動TFT $800_{nm}$ のゲート電極に印加される。駆動TFT $800_{nm}$ のゲート電圧 $V_{gs}$ は、信号ライン $S_m$ の電圧によって決まり、駆動TFT $800_{nm}$ に流れる電流が定まる。駆動TFT $800_{nm}$ と有機LED $830_{nm}$ とは直列接続されているため、駆動TFT $800_{nm}$ に流れる電流がそのまま、有機LED $830_{nm}$ に流れる電流となる。

【0368】

したがって、保持キャパシタ $820_{nm}$ により信号ライン $S_m$ の電圧に応じたゲート電圧 $V_{gs}$ を保持することによって、例えば1フレーム期間中において、ゲート電圧 $V_{gs}$ に対応した電流を有機LED $830_{nm}$ に流すことで、当該フレームにおいて光り続ける画素を実現することができる。

【0369】

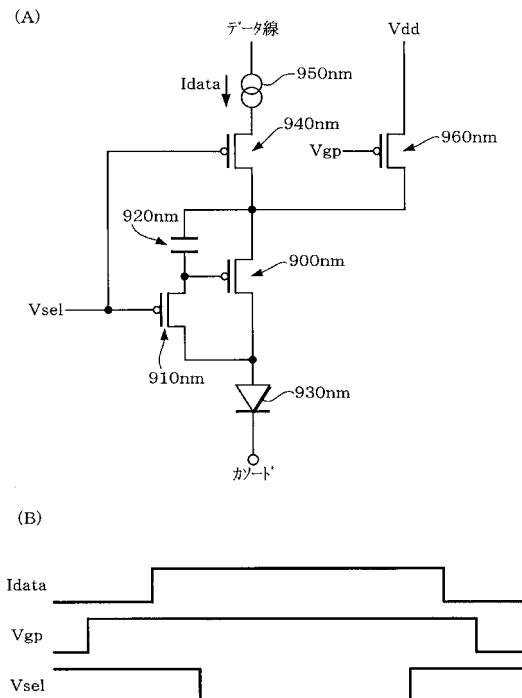

図45(A)に、上述した信号ドライバ及び走査ドライバにより表示制御される有機ELパネルにおける4トランジスタ方式の画素回路の一例を示す。図45(B)に、この画素回路の表示制御タイミングの一例を示す。

【0370】

この場合も、有機ELパネルは、駆動TFT $900_{nm}$ と、スイッチTFT $910_{nm}$ と、保持キャパシタ $920_{nm}$ と、有機LED $930_{nm}$ とを有する。

【0371】

10

20

30

40

50

図44に示した2トランジスタ方式の画素回路と異なる点は、定電圧の代わりにスイッチ素子としてのp型TFT940nmを介して定電流源950nmからの定電流Idataを画素に供給するようにした点と、電源ラインにスイッチ素子としてのp型TFT960nmを介して保持キャパシタ920nm及び駆動TFT900nmと接続するようにした点である。

【0372】

このような有機EL素子において、まずゲート電圧Vgpによりp型TFT960をオフにして電源ラインを遮断し、ゲート電圧Vselによりp型TFT940nmとスイッチTFT910nmをオンにして、定電流源950nmからの定電流Idataを駆動TFT900nmに流す。

【0373】

駆動TFT900nmに流れる電流が安定するまでの間に、保持キャパシタ920nmには定電流Idataに応じた電圧が保持される。

【0374】

続いて、ゲート電圧Vselによりp型TFT940nmとスイッチTFT910nmをオフにし、さらにゲート電圧Vgpによりp型TFT960nmをオンにし、電源ラインと駆動TFT900nm及び有機LED930nmを電気的に接続する。このとき、保持キャパシタ920nmに保持された電圧により、定電流Idataとほぼ同等か、又はこれに応じた大きさの電流が有機LED930nmに供給される。

【0375】

このような有機EL素子では、例えば、走査ラインをゲート電圧Vsel、信号ラインをデータ線として構成することができる。

【0376】

有機LEDは、透明アノード(ITO)の上部に発光層を設け、さらにその上部にメタルカソードを設けるようにしても良いし、メタルアノードの上部に、発光層、光透過性カソード、透明シールを設けるようにしても良く、その素子構造に限定されるものではない。

【0377】

なお、本発明は上述した実施の形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、プラズマディスプレイ装置にも適用可能である。

【図面の簡単な説明】

【図1】本実施形態における表示制御回路(LCDコントローラ)を適用した表示装置の構成の概要を示すブロック図である。

【図2】図1に示した信号ドライバの構成の概要を示すブロック図である。

【図3】ブロック出力選択レジスタの構成の概要を示す説明図である。

【図4】パーシャル表示選択レジスタの構成の概要を示す説明図である。

【図5】信号ドライバのラインプロック単位の構成の概要を示す構成図である。

【図6】信号ドライバのシフトレジスタを構成するSRの構成の一例を示す構成図である。

【図7】図1に示した走査ドライバの構成の概要を示すブロック図である。

【図8】パーシャル走査表示選択レジスタの構成の概要を示す説明図である。

【図9】走査ドライバの構成要部を示すブロック図である。

【図10】図1に示したLCDコントローラの構成の概要を示すブロック図である。

【図11】図11(A)は、フレーム反転駆動方式による信号ラインの駆動電圧及び対向電極電圧Vcomの波形を模式的に示す模式図である。図11(B)は、フレーム反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示す模式図である。

【図12】図12(A)は、ライン反転駆動方式による信号ラインの駆動電圧及び対向電極電圧Vcomの波形を模式的に示す模式図である。図12(B)は、ライン反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示す模式図である。

【図13】液晶装置のLCDパネルの駆動波形の一例を示す説明図である。

【図14】図14(A)、(B)、(C)は、本実施形態におけるLCDコントローラにより実現されるパーシャル表示制御の一例を模式的に示す説明図である。

【図15】図15(A)、(B)、(C)は、本実施形態におけるLCDコントローラにより実現されるパーシャル表示制御の他の例を模式的に示す説明図である。

【図16】本実施形態におけるLCDコントローラの構成要部を示すブロック図である。

【図17】本実施形態における制御レジスタの構成の概要を示す説明図である。

【図18】図18(A)、(B)は、走査ドライバの動作の一例を示す説明図である。

【図19】ウィンドウアクセスがない場合のリフレッシュ動作を説明するための説明図である。

【図20】本実施形態におけるリフレッシュ制御を実現する第1の方法において、ウィンドウアクセスがあった場合のリフレッシュ動作を説明するための説明図である。 10

【図21】本実施形態における第1の方法を実現するための回路構成図の一例である。

【図22】図22(A)、(B)、(C)、(D)は、本実施形態における第1の方法を実現するための回路構成図のタイミングの一例を示すタイミングチャートである。

【図23】本実施形態におけるリフレッシュ制御を実現する第2の方法において、ウィンドウアクセスがあった場合のリフレッシュ動作を説明するための説明図である。

【図24】本実施形態における第2の方法を実現するための回路構成図の一例である。

【図25】図25(A)、(B)、(C)、(D)は、本実施形態における第2の方法を実現するための回路構成図のタイミングの一例を示すタイミングチャートである。

【図26】本実施形態におけるリフレッシュ制御を実現する第3の方法において、ウィンドウアクセスがあった場合のリフレッシュ動作を説明するための説明図である。 20

【図27】本実施形態における第3の方法を実現するための回路構成図の一例である。

【図28】図28(A)、(B)、(C)、(D)は、本実施形態における第3の方法を実現するための回路構成図のタイミングの一例を示すタイミングチャートである。

【図29】本実施形態における第3の方法を実現するための回路構成図の変形例である。

【図30】図30(A)、(B)、(C)は、各動作モードにおけるウィンドウ管理データを説明するための説明図である。

【図31】画素単位でウィンドウを管理する場合について説明するための説明図である。

【図32】エリアブロック単位でウィンドウを管理する場合について説明するための説明図である。 30

【図33】エリアブロック単位でウィンドウを管理した場合の、走査駆動制御について説明するための説明図である。

【図34】帯パーシャルデータでウィンドウを管理する場合について説明するための説明図である。

【図35】信号ドライバの実装状態の一例を示す説明図である。

【図36】ユーザによって作成された画像に対応するパーシャル表示データを説明するための説明図である。

【図37】ユーザによって作成された画像に対応するパーシャル表示データと、ブロック出力選択データとの関係を説明するための説明図である。

【図38】ブロック出力選択データに基づいて、ユーザによって作成された画像に対応するパーシャル表示データの変換の必要性を説明するための説明図である。 40

【図39】パーシャル表示データ変換回路の構成の一例を示す構成図である。

【図40】図40(A)は、表示エリアを指定するコマンドを送信してから一連の画像ストリームを供給する場合を模式的に示す説明図である。図40(B)は、一連の画像ストリームを送信してから表示エリアを指定するコマンドを送信する場合を模式的に示す説明図である。

【図41】本実施形態におけるLCDコントローラによってパーシャル表示制御された信号ドライバの動作タイミングの一例を示すタイミング図である。

【図42】本実施形態におけるLCDコントローラによってパーシャル表示制御された走査ドライバの動作タイミングの一例を示すタイミング図である。 50

【図43】本実施形態における表示装置の初期化シーケンスを模式的に示す説明図である。

【図44】有機ELパネルにおける2トランジスタ方式の画素回路の一例を示す回路図である。

【図45】図45(A)は、有機ELパネルにおける4トランジスタ方式の画素回路の一例を示す回路図である。図45(B)は、4トランジスタ方式の画素回路の表示制御タイミングの一例を示すタイミング図である。

【符号の説明】

|                                                                        |                      |    |

|------------------------------------------------------------------------|----------------------|----|

| 10                                                                     | 液晶装置(表示装置)           | 10 |

| 20                                                                     | LCDパネル(表示パネル、電気光学装置) |    |

| 22 <sub>nm</sub>                                                       | TFT                  |    |

| 24 <sub>nm</sub>                                                       | 液晶容量                 |    |

| 26 <sub>nm</sub>                                                       | 画素電極                 |    |

| 28 <sub>nm</sub>                                                       | 対向電極                 |    |

| 30                                                                     | 信号ドライバ(信号駆動回路)       |    |

| 32、52、140 <sub>0</sub>                                                 | シフトレジスタ              |    |

| 34、36、36 <sub>0</sub>                                                  | ラインラッチ               |    |

| 38、38 <sub>0</sub>                                                     | DAC(駆動電圧生成回路)        |    |

| 40、40 <sub>0</sub>                                                     | 信号ライン駆動回路            |    |

| 50                                                                     | 走査ドライバ(走査駆動回路)       | 20 |

| 54、56                                                                  | L/S                  |    |

| 58                                                                     | 走査ライン駆動回路            |    |

| 60                                                                     | LCDコントローラ(表示制御回路)    |    |

| 62                                                                     | 制御回路 64 RAM          |    |

| 66                                                                     | ホストI/O               |    |

| 68                                                                     | LCD入出力(I/O)回路        |    |

| 70                                                                     | コマンドシーケンサ            |    |

| 72                                                                     | コマンド設定レジスタ           |    |

| 74                                                                     | コントロール信号生成回路         |    |

| 80                                                                     | 電源回路                 | 30 |

| 142 <sub>0</sub>                                                       | データバイパス回路            |    |

| 210 <sub>1</sub> ~210 <sub>N</sub> 、230 <sub>1</sub> ~230 <sub>N</sub> | AND回路                |    |

| 212 <sub>1</sub> ~212 <sub>N</sub> 、232 <sub>1</sub> ~232 <sub>N</sub> | CMOSバッファ回路           |    |

| 234 <sub>1</sub> ~234 <sub>Q-1</sub>                                   | データ切り替え回路            |    |

| 300                                                                    | 画像データ生成回路            |    |

| 310                                                                    | 信号ドライバ設定レジスタ         |    |

| 312                                                                    | ロック出力選択データ           |    |

| 314                                                                    | パーシャル表示データ           |    |

| 320                                                                    | 走査ドライバ設定レジスタ         |    |