(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0019408

(43) 공개일자 2017년02월21일

- (51) 국제특허분류(Int. Cl.)

*H05K 1/03* (2006.01)

(52) CPC특허분류

*H05K 1/036* (2013.01)

*B32B 15/08* (2013.01)

(21) 출원번호 10-2017-7000124

(22) 출원일자(국제) 2015년05월26일

심사청구일자 없음

(85) 번역문제출일자 2017년01월03일

(86) 국제출원번호 PCT/US2015/032363

(87) 국제공개번호 WO 2015/191273

국제공개일자 2015년12월17일

(30) 우선권주장

62/010,224 2014년06월10일 미국(US)

- (71) 출원인

쓰리엠 이노베이티브 프로퍼티즈 컴파니

미국 55133-3427 미네소타주 세인트 폴 퍼.오.박

스 33427 쓰리엠 센터

(72) 발명자

팔라니스와미 라비

싱가폴 768923 싱가폴 이순 애버뉴 7 1

나라그 알레잔드로 알드린 2세 아그카오일리

싱가폴 768923 싱가폴 이순 애버뉴 7 1

(뒷면에 계속)

(74) 대리인

양영준, 조윤성, 김영

전체 청구항 수 : 총 15 항

(54) 발명의 명칭 UV 차단성을 갖는 가요성 LED 조립체

### (57) 요 약

가요성 LED 조립체(300)가 기술된다. 보다 구체적으로, 기판 내 또는 위에 위치된 전도성 특징부(304, 306)를 갖는 기판(302), 및 UV 열화를 차단하기 위해 기판의 노출된 부분 위에 위치된 세라믹 층(310)을 갖는 가요성 LED(320) 조립체, 뿐만 아니라 그러한 조립체를 제조하는 방법이 기술된다.

**대 표 도** - 도3

(52) CPC특허분류

*B32B 27/281* (2013.01)

*B32B 7/12* (2013.01)

*H05K 1/0306* (2013.01)

*H05K 1/0346* (2013.01)

*H05K 1/189* (2013.01)

*H05K 3/28* (2013.01)

*H05K 2201/0154* (2013.01)

*H05K 2201/017* (2013.01)

*H05K 2201/10106* (2013.01)

(72) 발명자

푸 시양 신

싱가폴 768923 싱가폴 이순 애버뉴 7 1

---

고스기 히로미츠

일본 141-8684 도쿄 시나가와구 기타시나가와

6-7-29

## 명세서

### 청구범위

#### 청구항 1

가요성 LED 조립체로서,

가요성 중합체 기판;

가요성 기판의 표면 위 및 내부에 위치된 제1 전도성 특징부;

제1 전도성 특징부와 제2 전도성 특징부 사이의 가요성 중합체 기판의 일부분이 노출되도록, 제1 전도성 특징부로부터 이격되어 가요성 기판의 표면 위 및 내부에 위치된 제2 전도성 특징부; 및

제1 전도성 특징부와 제2 전도성 특징부 사이의 노출된 가요성 중합체 표면 위에 위치된 세라믹 층을 포함하는 가요성 LED 조립체.

#### 청구항 2

제1항에 있어서, 제1 및 제2 전도성 특징부 둘 모두 위에 장착된 LED를 추가로 포함하며, 가요성 중합체 기판이, 세라믹 층에 의해, LED로부터 방출되는 UV 광으로부터 차폐되는 가요성 LED 조립체.

#### 청구항 3

제1항에 있어서, 가요성 중합체 기판이 폴리이미드를 포함하는 가요성 LED 조립체.

#### 청구항 4

제1항에 있어서, 세라믹이 Al<sub>2</sub>O<sub>3</sub>, AlN, 또는 BN을 포함하는 가요성 LED 조립체.

#### 청구항 5

제2항에 있어서, LED가 제1 및 제2 전도성 특징부에 솔더 본딩(solder bonding)된 플립 칩을 포함하는 가요성 LED 조립체.

#### 청구항 6

제2항에 있어서, LED가 제1 및 제2 전도성 특징부에 용융 본딩(eutectic bonding)된 가요성 LED 조립체.

#### 청구항 7

제1항에 있어서, 제1 전도성 특징부 위에 장착되나 제2 전도성 특징부 위에 장착되지 않는 LED를 추가로 포함하며, 가요성 중합체 기판은, 세라믹 층에 의해, LED로부터 방출되는 UV 광으로부터 차폐되는 가요성 LED 조립체.

#### 청구항 8

제7항에 있어서, LED가 에폭시 바인딩 접착제, 전도성 페이스트, 이방성 전도성 페이스트(ACP), 이방성 전도성 필름(ACF) 또는 용융 본딩을 사용하여 제1 전도성 특징부에 부착되는 가요성 LED 조립체.

#### 청구항 9

가요성 LED 조립체로서,

그를 통해 연장되는 비아를 포함하는 가요성 중합체 기판;

가요성 기판의 하부 표면 위에 위치된 제1 전도성 특징부 - 제1 전도성 특징부의 일부분은 비아 바로 아래에 위치됨 -;

및

가요성 중합체 기판의 상부 표면 위에 위치된 세라믹 층을 포함하는 가요성 LED 조립체.

#### 청구항 10

제9항에 있어서, 가요성 중합체 기판 내의 제2 비아 및 가요성 기판의 하부 표면 위에 위치된 제2 전도성 특징부를 추가로 포함하며, 제2 전도성 특징부의 일부분이 제2 비아 바로 아래에 위치된 가요성 LED 조립체.

#### 청구항 11

LED 조립체의 제조 방법으로서,

기판의 표면에 세라믹 층을 도포하는 단계 - 기판은, 세라믹의 도포 전에, 그 위의 노출된 상부 표면이 중합체인 제1 부분 및 그 위의 노출된 상부 표면이 전도성 금속인 제2 부분을 포함함 -;

기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계; 및

기판의 표면의 제2 부분 내의 전도성 금속을 표면 처리(surface finishing)하는 단계를 포함하는, LED 조립체 제조 방법.

#### 청구항 12

제11항에 있어서, 기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계가, 제2 부분에 대응하는 세라믹 영역 위로 점착성(tacky) 라이너를 라미미네이팅하는 단계, 및 점착성 라이너를 제거함으로써 제2 부분으로부터 세라믹을 박리시키는 단계를 포함하는, LED 조립체 제조 방법.

#### 청구항 13

제11항에 있어서, 전도성 금속을 표면 처리하는 단계는 먼저 니켈 층을 도금하는 단계 및 이후 금 또는 은 층을 도금하는 단계를 포함하는 LED 조립체 제조 방법.

#### 청구항 14

제11항에 있어서, 세라믹 층이 스퍼터링 프로세스를 사용하여 도포되는 LED 조립체 제조 방법.

#### 청구항 15

제11항에 있어서, 세라믹이 질화 알루미늄을 포함하는 LED 조립체 제조 방법.

### 발명의 설명

#### 기술 분야

[0001]

본 발명은 가요성 LED 조립체에 관한 것이다.

#### 배경 기술

[0002]

가요성 회로 및 조립체는 종종 프린터, 컴퓨터, 모니터 등과 같은 다양한 전자 장비 응용물에서 커넥터로서 사용된다. 그러한 회로는 가요성과 공간 절약 둘 모두에서 이전에 사용된 경성 회로 보드에 비해 이점을 제공한다.

[0003]

회로를 위한 보다 고 가요성 재료들로의 움직임은, 그러한 회로에 장착된 LED로부터의 UV 광에 노출될 때 종래의 세라믹 기판에 비해, 예컨대, 가요성 폴리이미드 기판의 더 큰 열화(degradation)와 같은 도전 과제들을 생성하였다. 본 발명은 회로 기판의 열화를 방지하면서 LED의 가요성을 유지하는 해법을 제공하기 위한 것이다.

#### 발명의 내용

[0004]

일 태양에서, 본 발명은 가요성 LED 조립체에 관한 것이다. 가요성 LED 조립체는 가요성 중합체 기판, 제1 및 제2 전도성 특징부 및 세라믹 층을 포함한다. 제1 전도성 특징부는 가요성 기판의 표면 위 및 내부에 위치된다. 제2 전도성 특징부는, 제1 전도성 특징부와 제2 전도성 특징부 사이의 가요성 중합체 기판의 일부분이 노출되도록, 제1 전도성 특징부로부터 이격되어 가요성 기판의 표면 위 및 내부에 위치된다. 세라믹 층은 제1 전도성 특징부와 제2 전도성 특징부 사이의 노출된 가요성 중합체 표면 위에 위치된다.

[0005] 다른 태양에서, 본 발명은 가요성 LED 조립체에 관한 것이다. 가요성 LED 조립체는 가요성 중합체 기판, 제1 전도성 특징부 및 세라믹 층을 포함한다. 가요성 중합체 기판은 그것을 통해 연장되는 비아를 가진다. 제1 전도성 특징부는 가요성 기판의 하부 표면 위에 위치되고 제1 전도성 특징부의 일부분이 비아 바로 아래에 위치된다. 세라믹 층은 가요성 중합체 기판의 상부 표면 위에 위치된다. 선택적으로, 조립체는 가요성 중합체 기판 내의 제2 비아 및 가요성 기판의 하부 표면 위에 위치된 제2 전도성 특징부를 포함할 수 있으며, 제2 전도성 특징부의 일부분이 제2 비아 바로 아래에 위치된다.

[0006] 또 다른 태양에서, 본 발명은 LED 조립체의 제조 방법에 관한 것이다. 본 방법은 기판의 표면에 세라믹 층을 도포하는 단계 - 세라믹의 도포 전에, 기판은 그 위의 노출된 상부 표면이 중합체인 제1 부분 및 그 위의 노출된 상부 표면이 전도성 금속인 제2 부분을 포함함 -, 기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계, 및 기판의 표면의 제2 부분 내의 전도성 금속을 표면 처리(surface finishing)하는 단계를 포함한다.

### 도면의 간단한 설명

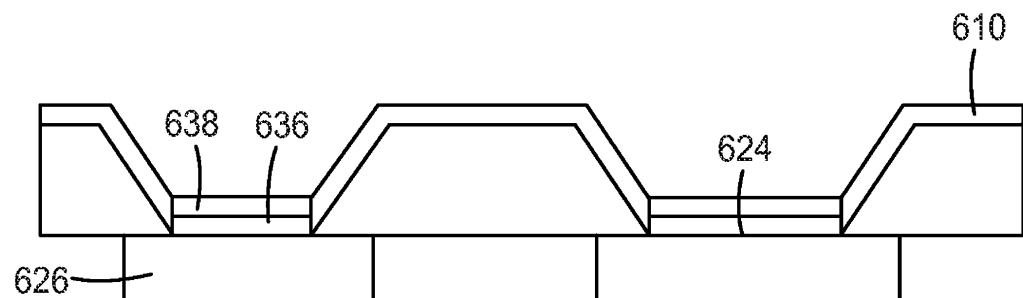

[0007] 도 1은 본 발명에 따른 가요성 LED 조립체의 단면도이다.

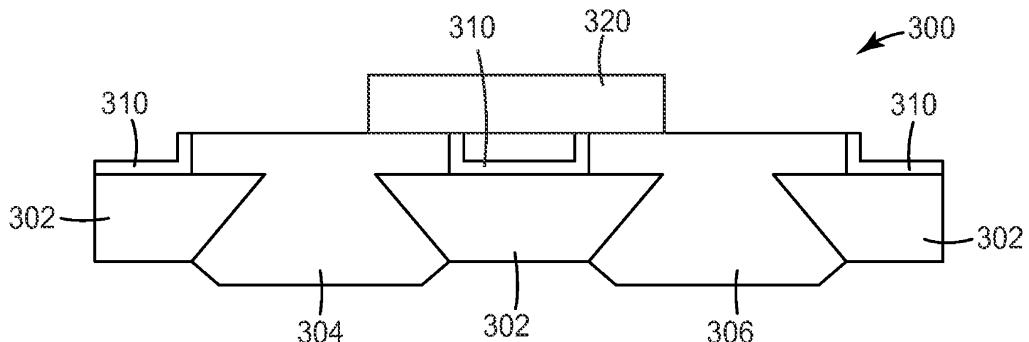

도 2는 본 발명에 따른 가요성 LED 조립체의 단면도이다.

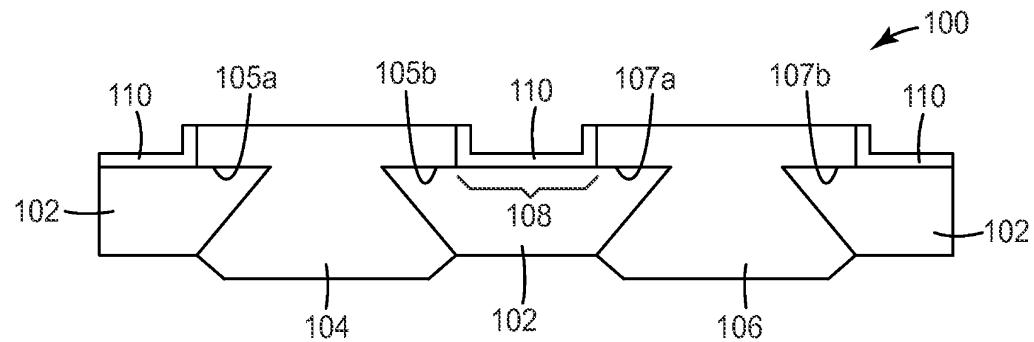

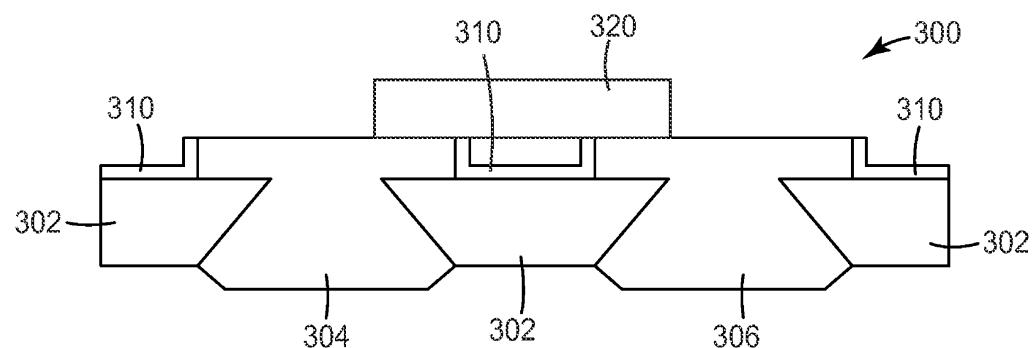

도 3은 본 발명에 따른 가요성 LED 조립체의 단면도이다.

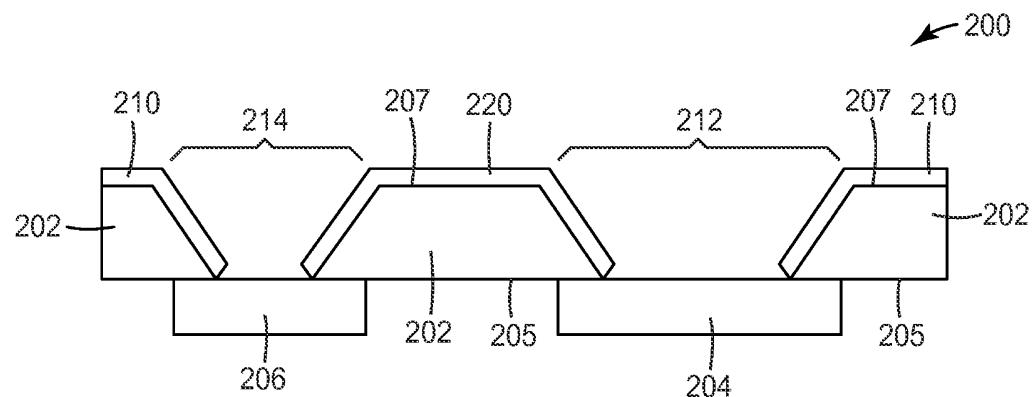

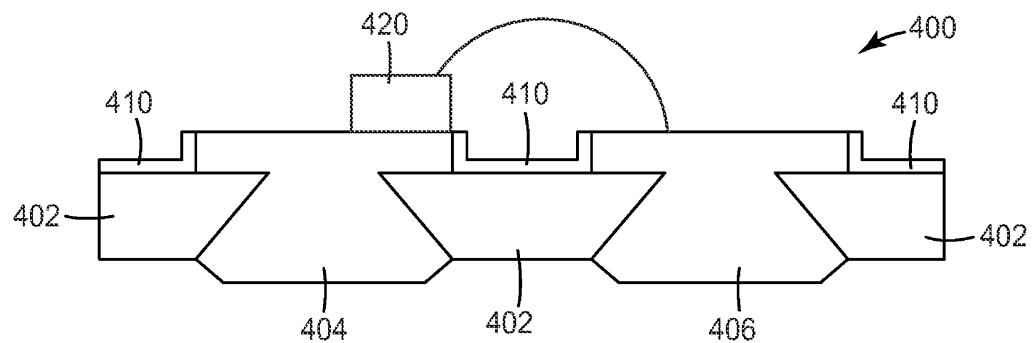

도 4는 본 발명에 따른 가요성 LED 조립체의 단면도이다.

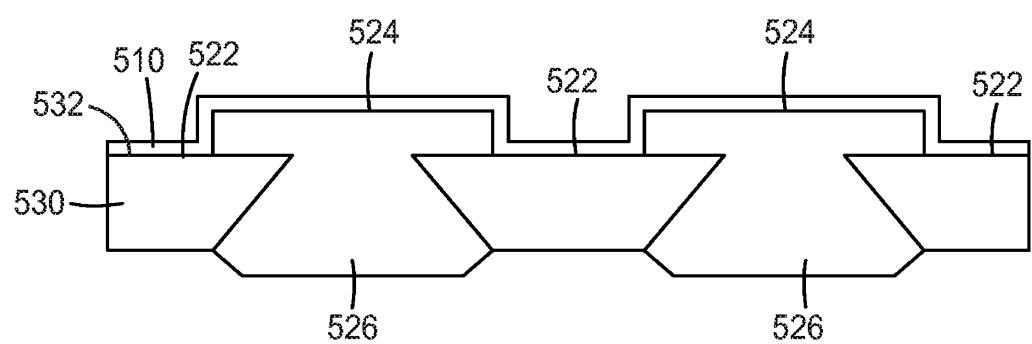

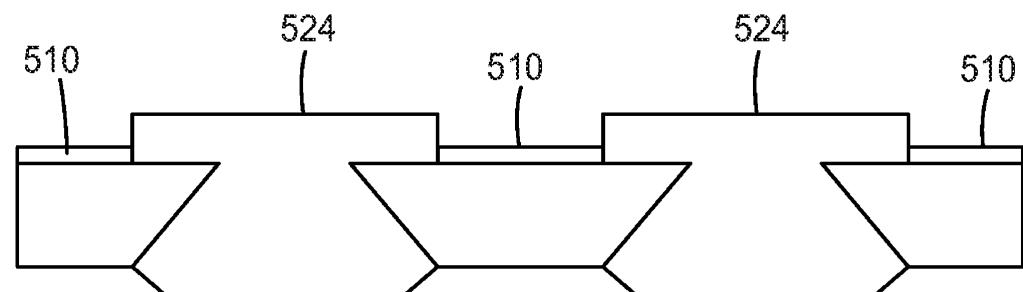

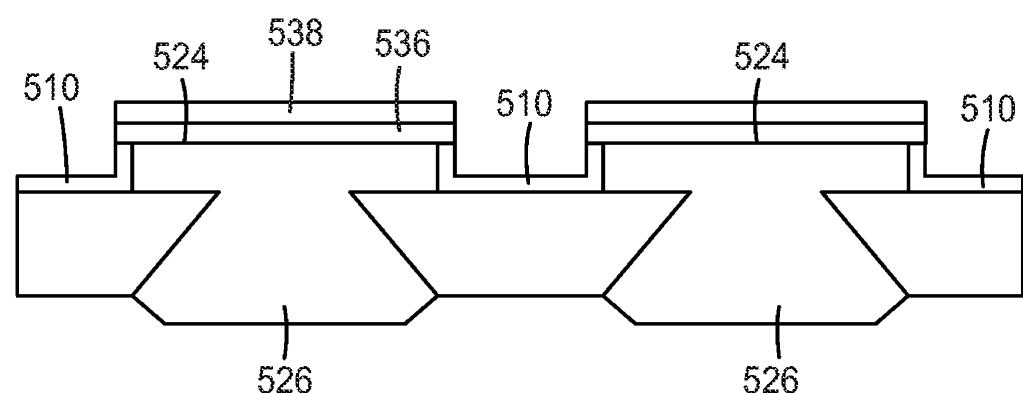

도 5a 내지 도 5c는 본 발명에 따른 가요성 LED 조립체를 제조하는 방법을 도시하는 흐름도를 제공한다.

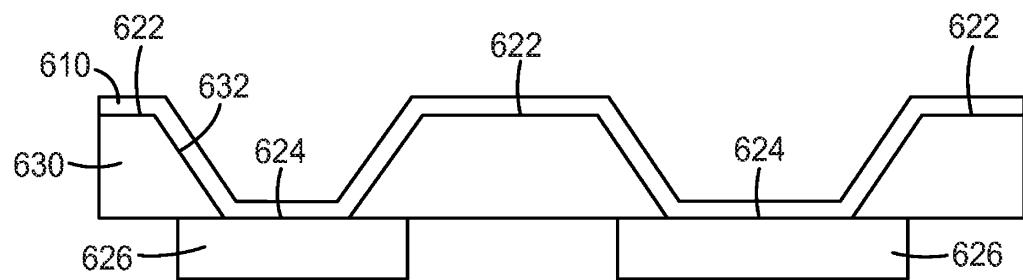

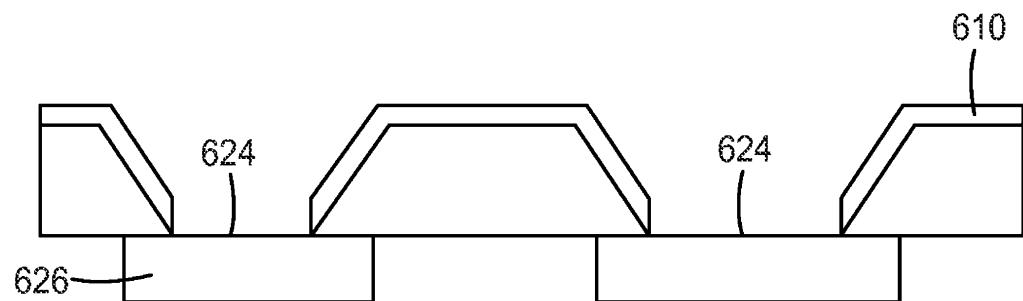

도 6a 내지 도 6c는 본 발명에 따른 가요성 LED 조립체를 제조하는 방법을 도시하는 흐름도를 제공한다.

도면들이 반드시 축척대로 된 것은 아니다. 도면들에 사용된 유사한 도면 부호들은 유사한 구성요소들을 지칭 한다. 그러나, 주어진 도면에서 구성요소를 지시하기 위한 도면 부호의 사용은 동일한 도면 부호로 표기된 다른 도면 내의 그 구성요소를 제한하도록 의도되지 않음이 이해될 것이다.

### 발명을 실시하기 위한 구체적인 내용

[0008] 이제 본 발명의 다양한 예시적인 실시예가 특히 도면을 참조하여 기술될 것이다. 본 발명의 예시적인 실시예는 본 발명의 사상 및 범주로부터 벗어남이 없이 다양한 변형 및 변경을 취할 수 있다. 따라서, 본 발명의 실시예는 하기의 기술된 예시적인 실시예로 제한되는 것이 아니라, 청구범위에 기재된 제한 및 그것의 임의의 등가물에 의해 좌우되어야 한다는 것이 이해되어야 한다.

[0009] 하기 설명에서, 본 명세서의 일부를 이루며 예시로서 도시된 첨부 도면을 참조한다. 다른 실시예들이 고려되며 본 발명의 범주 또는 사상으로부터 벗어남이 없이 이루어질 수 있다는 것이 이해되어야 한다. 따라서, 하기의 상세한 설명은 제한적 의미로 해석되지 않아야 한다.

[0010] 달리 지시되지 않는 한, 본 명세서 및 청구범위에 사용되는 특징부 크기, 양, 및 물리적 특성을 표현하는 모든 수치는 모든 경우에 용어 "약"에 의해 수식되는 것으로 이해되어야 한다. 따라서, 반대로 지시되지 않는 한, 이어지는 명세서 및 첨부된 청구범위에 기술된 수치적 파라미터는 본 명세서에 개시된 교시를 이용하는 당업자가 얻고자 하는 원하는 특성에 따라 변할 수 있는 근사치이다.

[0011] 본 명세서 및 첨부된 청구범위에 사용되는 바와 같이, 단수 형태 ("a", "an" 및 "the")는, 그 내용이 명백하게 달리 지시하지 않는 한, 복수의 지시 대상을 갖는 실시예를 포함한다. 본 명세서 및 첨부된 청구범위에 사용되는 바와 같이, 용어 "또는"은 일반적으로, 그 내용이 명백히 달리 지시하지 않는 한, 그의 의미에 있어서 "및/ 또는"을 포함하는 것으로 사용된다.

[0012] "하부", "상부", "바로 아래에", "아래에", "위에", 및 "상부에"를 포함하나 이에 한정되지 않는 공간적으로 관련된 용어는 본 명세서에 사용되는 경우, 구성요소(들)의 서로에 대한 공간적 관계를 기술하기 위한 용이한 설명을 위해 사용된다. 그러한 공간적으로 관련된 용어는 도면에 도시되고, 본 명세서에 기술된 특정 배향 이외에 사용 또는 작동 시 장치의 상이한 배향을 포함한다. 예를 들어, 도면에 도시된 물체가 반전되거나 뒤집히면, 다른 요소 아래에 또는 바로 아래에 있는 것으로 이전에 기술된 부분이 이를 다른 요소 위에 있을 것이다.

[0013] 본 명세서에 사용되는 바와 같이, 예를 들어 요소, 구성요소, 또는 층이 다른 요소, 구성요소, 또는 층과 "일치

하는 계면"을 형성하는 것으로, 또는 그 "위에" 있거나 그"에 연결"되거나 그"와 결합"되거나 또는 그"와 접촉"하는 것으로 기술되는 경우, 그것은 그 바로 위에 있거나 그에 직접적으로 연결되거나 그와 직접적으로 결합되거나 그와 직접 접촉할 수 있거나, 또는 개재하는 요소, 구성요소, 또는 층이, 예를 들어 특정 요소, 구성요소, 또는 층 위에 있거나 그와 연결되거나 그와 결합 또는 접촉할 수 있다. 예를 들어, 요소, 구성요소 또는 층이 다른 요소 "바로 위에"있거나, "그에 직접 연결"되거나, "그와 직접 결합"되거나, "그와 직접 접촉"하는 것으로 지칭될 때, 예를 들어 개재하는 요소, 구성요소 또는 층은 존재하지 않는다.

[0014] 도 1은 본 발명에 따른 가요성 LED 조립체(100)의 단면도를 제공한다. 가요성 LED 조립체(100)는 가요성 중합체 기판(102)을 포함한다. 가요성 중합체 기판(102)은, 바람직한 실시예에서, 폴리이미드로 제조될 수 있다. 대안적으로, 기판(102)은 PET, 액정 중합체, 폴리카보네이트, 폴리에테르 에테르 케톤, 열가소성 중합체, 또는 다른 적합한 가요성 재료일 수 있다. 가요성 중합체 기판(102)은 일반적으로 유전체 재료일 것이다. 조립체(100)는 가요성 기판(102)의 표면 위 및 내부에 위치된 제1 전도성 특징부(104)를 포함한다. 예를 들어, 제1 전도성 특징부는 분명히 기판의 평면 내에 위치되지만 또한 기판(102)의 표면 부분(105a, 105b) 위에 위치된다. 조립체(100)는 또한 가요성 기판의 표면(예컨대, 표면 부분(107a, 107b) 참조) 위 및 내부에 위치된 제2 전도성 특징부(106)를 추가로 포함한다.

[0015] 제1 전도성 특징부와 제2 전도성 특징부 사이의 가요성 중합체 기판의 일부분(108)이 노출되도록, 제2 전도성 특징부는 제1 전도성 특징부(104)로부터 이격되어 위치된다. 적어도 하나의 실시예에서, 제1 및 제2 전도성 특징부는 구리로 이루어질 수 있으나, 다른 전도성 재료가 사용될 수 있다. 마지막으로, 세라믹 층(110)이 제1 전도성 특징부와 제2 전도성 특징부 사이의 노출된 가요성 중합체 표면(108) 위에 위치된다. 세라믹(110)은 또한 가요성 기판(102)의 임의의 노출된 부분이 세라믹으로 덮이도록, 제1 및 제2 전도성 특징부의 대향 면들 및 기판의 표면 위에 위치될 수 있다. 특정 실시예들에서, 세라믹(110)은  $\text{Al}_2\text{O}_3$ , AlN, 또는 BN일 수 있고, 이를 각각은 적합한 UV 차폐 기능을 제공하지만, UV-차폐 특성을 갖는 다른 세라믹들이 이용될 수 있다.

[0016] 도 2는 본 발명에 따른 가요성 LED 조립체(200)의 다른 실시예를 도시한다. 이 실시예에서, 가요성 LED 조립체는 그를 통해 연장되는 비아(212)를 갖는 가요성 중합체 기판(202)을 포함한다. 제1 전도성 특징부(204)는 가요성 기판의 하부 표면(205) 위에 위치되고, 전도성 특징부(204)의 일부분이 비아(212) 바로 아래에 위치된다. 세라믹 층(210)은 가요성 중합체 기판의 상부 표면(207) 위에 위치된다. 추가적으로, 가요성 LED 조립체(200)는 가요성 중합체 기판 내의 제2 비아(214), 및 가요성 기판의 하부 표면(205) 상에 위치된 제2 전도성 특징부(206)를 포함할 수 있다. 제2 전도성 특징부(206)의 적어도 일부분은 제2 비아(214) 바로 아래에 위치된다. 제1 및 제2 전도성 특징부는 조립체(100)에서 전도성 특징부에 관해 기술된 특성들을 가질 수 있고, 세라믹 층 및 가요성 중합체 기판도 (동일한 명칭을 갖는 대응 특징부에 대해) 마찬가지일 수 있다.

[0017] 물론, 도 1 및 도 2의 구조체가 가요성 LED 조립체를 도시하므로, 궁극적으로 LED가 상기 구조체에 장착될 것이다. 다수의 적합한 LED 구조체가 사용될 수 있다. 도 3은 하나의 그러한 구조체를 도시한다. 가요성 LED 조립체(300)는 제1 전도성 특징부(304) 및 제2 전도성 특징부(306) 둘 모두 위에 장착된 LED(320)를 포함한다. 가요성 중합체 기판(302)은, 세라믹 층(310)에 의해, LED(320)로부터 방출되는 UV 광으로부터 차폐된다. 이 특정 구조체는 LED(320)가 플립 칩 또는 측방 다이(lateral die)인 구조체일 수 있다. LED(320)가 플립 칩인 경우, 그것은 솔더링 기법을 사용하여 제1 전도성 특징부(304) 및 제2 전도성 특징부(306)에 본딩될 수 있다. 대안적으로, LED는 제1 및 제2 전도성 특징부에 용융 본딩(eutectic bonding)될 수 있다.

[0018] 다른 실시예에서, LED는 제1 및 제2 전도성 특징부 중 하나 또는 이 둘 모두에 와이어 본딩될 수 있다. 도 4는 하나의 예시적인 구조체를 도시한다. 이 경우에, 가요성 LED 조립체(400)는 제1 전도성 특징부(404) 위에는 장착되지만 제2 전도성 특징부(406) 위에는 장착되지 않는 LED(420)를 포함한다. 다른 구조체에서와 같이, 가요성 중합체 기판(402)은 세라믹 층에 의해 LED로부터 방출되는 UV 광으로부터 차폐된다. 그러나, 여기서 LED는 제2 전도성 특징부(406)에 와이어 본딩된다. 이것은 또한 제1 전도성 특징부(404)에 와이어 본딩되거나, 애플리시 바인딩 접착제, 전도성 페이스트, 이방성 전도성 페이스트(ACP), 이방성 전도성 필름(ACF) 또는 용융 본딩을 사용하여 제1 전도성 특징부에 부착될 수 있다.

[0019] 또 다른 태양에서, 본 발명은 LED 조립체의 제조 방법에 관한 것이다. 그러한 방법이 도 5a 내지 도 5c에 도시되어 있다. 도 5a에 도시된 바와 같이, 본 방법의 제1 단계는 기판(530)의 표면(532)에 세라믹 층(510)을 도포하는 단계 - 기판은, 세라믹(510)의 도포 전에, 그 위의 노출된 상부 표면이 중합체인 제1 부분(즉, 제1 부분(522)), 및 그 위의 노출된 상부 표면이 전도성 금속(526)인 제2 부분(즉, 제2 부분(524))을 포함함 - 이다. 일 실시예에서, 세라믹 층(510)은 스퍼터링 프로세스를 사용하여 도포될 수 있다. 도포된 세라믹 층(510)은 세

라믹 층(110)에 관해 기술된 임의의 적합한 재료, 예를 들어, 질화 알루미늄일 수 있다. 일 예시적인 실시예에서, 전도성 금속(526)은 구리일 수 있다.

[0020] 도 5b에 도시된 다음 단계는, 기판의 표면의 제2 부분(524)으로부터 세라믹(510)을 제거하는 것이다. 제거 단계는 다수의 적합한 수단을 통해 달성될 수 있다. 예를 들어, 하나의 경우에, 점착성(tacky) 라이너가 제2 부분에 대응하는 세라믹(510)의 영역 위로 라미네이팅될 수 있다. 점착성 라이너가 제거될 때, 그것은 제2 부분(524)을 덮고 있는 세라믹을 박리시킨다. 대안적으로, 세라믹(510)은 강모 브러시(bristle brush) 기법, 즉, 연마 기판을 사용하여 기계적으로 세라믹을 털어내는(brush off) 기법을 사용하여 제2 부분 위로부터 제거될 수 있다. 또 다른 경우에, 세라믹 층은 마이크로-에칭 프로세스를 사용하여 제2 부분(524) 위로부터 제거될 수 있다.

[0021] 다음으로, 본 방법은 기판의 표면의 제2 부분(524) 내의 전도성 금속(526)을 표면 처리하는 단계를 포함한다. 도시된 바와 같이, 표면 처리 단계는 표면의 제2 부분(524) 상에 어떤 종류의 도금을 행하는 단계를 수반할 수 있다. 예를 들어, 표면 처리 단계는 무전해 도금, 전해 도금 또는 침지 도금의 수단에 의해 도금하는 단계를 포함할 수 있다. (도 5c의 예로 도시된) 일 실시예에서, 표면 처리 단계는 먼저 니켈 층(536)을 도금하는 단계, 및 이후 금 또는 은 층(538)을 도금하는 단계를 포함할 수 있다.

[0022] 동일한 종류의 프로세스가 도 2에 도시된 것과 유사한 가요성 LED 조립체에 또한 사용될 수 있다. 그러한 프로세스가 도 6a 내지 도 6c에 도시되어 있다. 여기서, 다시 (도 6a에 도시된) 제1 단계는, 기판(630)의 표면(632)에 세라믹 층(610)을 도포하는 단계 - 기판은, 세라믹(610)의 도포 전에, 그 위의 노출된 상부 표면이 중합체인 제1 부분(즉, 제1 부분(622)), 및 그 위의 노출된 상부 표면이 전도성 금속(626)인 제2 부분(즉, 제2 부분(624))을 포함함 - 이다.

[0023] 도 6b에 도시된 다음 단계는, 기판의 표면의 제2 부분(624)으로부터 세라믹(610)을 제거하는 것이다. 제거 단계는 도 5b에 관해 위에서 기술된 것과 같은 다수의 적합한 수단을 통해 달성될 수 있다.

[0024] 마지막으로, 본 방법은 기판의 표면의 제2 부분(624) 내의 전도성 금속(626)을 표면 처리하는 단계를 포함한다. 도시된 바와 같이, 표면 처리 단계는 표면의 제2 부분(624) 상에 어떤 종류의 도금을 행하는 단계를 수반할 수 있다. 예를 들어, 표면 처리 단계는 무전해 도금, 전해 도금 또는 침지 도금의 수단에 의해 도금하는 단계를 포함할 수 있다. (도 6c의 예로 도시된) 일 실시예에서, 표면 처리 단계는 먼저 니켈 층(636)을 도금하는 단계, 및 이후 금 또는 은 층(638)을 도금하는 단계를 포함할 수 있다.

[0025] 하기는 예시적인 실시예들의 목록이다.

[0026] 실시예 1은 가요성 LED 조립체로서,

[0027] 가요성 중합체 기판;

[0028] 가요성 기판의 표면 위 및 내부에 위치된 제1 전도성 특징부;

[0029] 제1 전도성 특징부와 제2 전도성 특징부 사이의 가요성 중합체 기판의 일부분이 노출되도록, 제1 전도성 특징부로부터 이격되어 가요성 기판의 표면 위 및 내부에 위치된 제2 전도성 특징부; 및

[0030] 제1 전도성 특징부와 제2 전도성 특징부 사이의 노출된 가요성 중합체 표면 위에 위치된 세라믹 층을 포함하는 가요성 LED 조립체이다.

[0031] 실시예 2는, 실시예 1에 있어서, 제1 및 제2 전도성 특징부 둘 모두 위에 장착된 LED를 추가로 포함하며, 가요성 중합체 기판이, 세라믹 층에 의해, LED로부터 방출되는 UV 광으로부터 차폐되는 가요성 LED 조립체이다.

[0032] 실시예 3은, 실시예 1에 있어서, 가요성 중합체 기판이 폴리이미드를 포함하는 가요성 LED 조립체이다.

[0033] 실시예 4는, 실시예 1에 있어서, 가요성 중합체 기판이 PET, 액정 중합체, 폴리카보네이트, 폴리에테르 에테르 케톤, 또는 열가소성 중합체를 포함하는 가요성 LED 조립체이다.

[0034] 실시예 5는, 실시예 1에 있어서, 제1 및 제2 전도성 특징부가 구리를 포함하는 가요성 LED 조립체이다.

[0035] 실시예 6은, 실시예 1에 있어서, 세라믹이  $\text{Al}_2\text{O}_3$ , AlN, 또는 BN을 포함하는 가요성 LED 조립체이다.

[0036] 실시예 7은, 실시예 2에 있어서, LED가 플립 칩을 포함하는 가요성 LED 조립체이다.

[0037] 실시예 8은, 실시예 7에 있어서, 플립 칩이 솔더링 기법을 사용하여 본딩되는 가요성 LED 조립체이다.

- [0038] 실시예 9는, 실시예 2에 있어서, LED가 와이어 본딩된 LED를 포함하는 가요성 LED 조립체이다.

- [0039] 실시예 10은, 실시예 2에 있어서, LED가 측방 다이를 포함하는 가요성 LED 조립체이다.

- [0040] 실시예 11은, 실시예 2에 있어서, LED가 제1 및 제2 전도성 특징부에 용융 본딩된 가요성 LED 조립체이다.

- [0041] 실시예 12는, 실시예 1에 있어서, 제1 전도성 특징부 위에 장착되나 제2 전도성 특징부 위에 장착되지 않는 LED를 추가로 포함하며, 가요성 중합체 기판은, 세라믹 층에 의해, LED로부터 방출되는 UV 광으로부터 차폐되는 가요성 LED 조립체이다.

- [0042] 실시예 13은, 실시예 12에 있어서, LED가 에폭시 바인딩 접착제, 전도성 페이스트, 이방성 전도성 페이스트(ACP), 이방성 전도성 필름(ACF) 또는 용융 본딩을 사용하여 제1 전도성 특징부에 부착되는 가요성 LED 조립체이다.

- [0043] 실시예 14는, 실시예 1에 있어서, 가요성 중합체 기판이 유전체를 포함하는 가요성 LED 어셈블리이다.

- [0044] 실시예 15는 가요성 LED 조립체로서,

- [0045] 그를 통해 연장되는 비아를 포함하는 가요성 중합체 기판;

- [0046] 가요성 기판의 하부 표면 위에 위치된 제1 전도성 특징부 - 제1 전도성 특징부의 일부분은 비아 바로 아래에 위치됨 -;

- [0047] 및

- [0048] 가요성 중합체 기판의 상부 표면 위에 위치된 세라믹 층을 포함하는 가요성 LED 조립체이다.

- [0049] 실시예 16은, 실시예 15에 있어서, 가요성 중합체 기판 내의 제2 비아 및 가요성 기판의 하부 표면 위에 위치된 제2 전도성 특징부를 추가로 포함하며, 제2 전도성 특징부의 일부분이 제2 비아 바로 아래에 위치된 가요성 LED 조립체이다.

- [0050] 실시예 17은 LED 조립체의 제조 방법으로서,

- [0051] 기판의 표면에 세라믹 층을 도포하는 단계 - 기판은, 세라믹의 도포 전에, 그 위의 노출된 상부 표면이 중합체인 제1 부분 및 그 위의 노출된 상부 표면이 전도성 금속인 제2 부분을 포함함 -;

- [0052] 기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계; 및

- [0053] 기판의 표면의 제2 부분 내의 전도성 금속을 표면 처리하는 단계를 포함하는, LED 조립체의 제조 방법이다.

- [0054] 실시예 18은, 실시예 17에 있어서, 기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계가, 제2 부분에 대응하는 세라믹 영역 위로 접착성 라이너를 라미네이팅하는 단계, 및 접착성 라이너를 제거함으로써 제2 부분으로부터 세라믹을 박리시키는 단계를 포함하는 방법이다.

- [0055] 실시예 19는, 실시예 17에 있어서, 기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계가, 강모 브러쉬 기법을 사용하는 단계를 포함하는 방법이다.

- [0056] 실시예 20은, 실시예 17에 있어서, 기판의 표면의 제2 부분으로부터 세라믹을 제거하는 단계가, 세라믹을 마이크로-에칭하는 단계를 포함하는 방법이다.

- [0057] 실시예 21은, 실시예 17에 있어서, 전도성 금속이 구리를 포함하는 방법이다.

- [0058] 실시예 22는, 실시예 17에 있어서, 전도성 금속을 표면 처리하는 단계가 무전해 도금, 전해 도금, 또는 침지 도금을 포함하는 방법이다.

- [0059] 실시예 23은, 실시예 17에 있어서, 전도성 금속을 표면 처리하는 단계가 먼저 니켈 층을 도금하는 단계 및 이후 금 또는 은 층을 도금하는 단계를 포함하는 방법이다.

- [0060] 실시예 24는, 실시예 17에 있어서, 세라믹 층이 스퍼터링 프로세스를 사용하여 도포되는 방법이다.

- [0061] 실시예 25는, 실시예 17에 있어서, 세라믹이 질화 알루미늄을 포함하는 방법이다.

## 도면

## 도면1

## 도면2

## 도면3

도면4

도면5a

도면5b

도면5c

도면6a

도면6b

도면6c