### (19) **日本国特許庁(JP)**

HO3K 17/06

(51) Int.C1.<sup>7</sup>

# (12) 特 許 公 報(B2)

HO3K 17/06

FI

(11)特許番号

特許第3604148号 (P3604148)

(45) 発行日 平成16年12月22日(2004.12.22)

(24) 登録日 平成16年10月8日 (2004.10.8)

C

|               |                       | ,         |                     |

|---------------|-----------------------|-----------|---------------------|

| HO2M 1/08     | HO2M                  | 1/08      | A                   |

| HO2M 7/537    | HO2M                  | 7/537     | E                   |

| HO2M 7/5387   | HO2M                  | 7/5387    | Z                   |

| HO3K 17/687   | нозк                  | 17/687    | F                   |

|               |                       |           | 請求項の数 10 (全 8 頁)    |

| (21) 出願番号     | 特願平8-504854           | (73) 特許権者 | <u> </u>            |

| (86) (22) 出願日 | 平成7年7月12日 (1995.7.12) |           | コーニンクレッカ フィリップス エレク |

| (65) 公表番号     | 特表平9-503116           |           | トロニクス エヌ ヴィ         |

| (43) 公表日      | 平成9年3月25日 (1997.3.25) |           | オランダ国 5621 ベーアー アイン |

| (86) 国際出願番号   | PCT/1B1995/000553     |           | ドーフェン フルーネヴァウツウェッハ  |

| (87) 国際公開番号   | W01996/002976         |           | 1                   |

| (87) 国際公開日    | 平成8年2月1日 (1996.2.1)   | (74) 代理人  |                     |

| 審査請求日         | 平成14年7月9日 (2002.7.9)  |           | 弁理士 杉村 興作           |

| (31) 優先権主張番号  | 08/275, 569           | (72) 発明者  | ワルネルダム レオ           |

| (32) 優先日      | 平成6年7月15日 (1994.7.15) |           | オランダ国 6537 エルデー ネイメ |

| (33) 優先権主張国   | 米国 (US)               |           | ヘン メイホルスト 63-78     |

|               |                       | (72) 発明者  | ジャナスワミー アナンド        |

|               |                       |           | アメリカ合衆国 カリフォルニア州 94 |

|               |                       |           | 086 サニーヴェイル サン ガブリエ |

|               |                       |           | ル ドライブ 120          |

|               |                       |           | 最終頁に続く              |

(54) 【発明の名称】ブートストラップダイオードエミュレータを用いるブリッジ回路用ドライバ回路

### (57)【特許請求の範囲】

#### 【請求項1】

れた下側パワートランジスタ及び上側パワートランジスタを有するブリッジ回路を駆動するとともに、第1端が前記出力端子に結合されている当該第1端と第2端とを有するブートストラップキャパシタを充電するドライバ回路であって、このドライバ回路が電源出力端に前記下側電圧ラインに対する制御電圧を発生する電源手段と、前記電源出力端に結合され、前記制御電圧により附勢される下側駆動モジュールであって、下側駆動制御信号を下側パワートランジスタの制御電極に供給して下側パワートランジスタを交互に導通及び非導通とする手段を有する当該下側駆動モジュールと、前記ブートストラップキャパシタの両端間のブートストラップ電圧によって附勢するためにこのブートストラップキャパシタに結合されるようになっている上側駆動モジュールであって、上側駆動制御信号を上側パワートランジスタの制御電極に供給して上側パワートランジスタを交互に導通及び非導通とする手段を有する当該上側駆動モジュールと、LDMOSトランジスタを有し、前記ブートストラップキャパシタを前記ブートストラップ電圧まで充電させるブートストラップダイオードエミュレータ手段であって、前記LDMOSト

ランジスタは、前記電源出力端に結合されたソース電極と、前記ブートストラップキャパシタの前記第2端に結合されるようになっているドレイン電極と、下側パワートランジスタが導通状態に駆動された際に前記LDMOSトランジスタを導通状態に駆動するための負荷制御回路を経て前記下側駆動モジュールに結合されたゲート電極と、バックゲート電極と

出力端子と高電圧直流電源の下側電圧ライン及び上側電圧ラインとの間にそれぞれ接続さ

10

を有し、このバックゲート及び前記ドレイン電極に寄生トランジスタが接続されている当該ブートストラップダイオードエミュレータ手段と

を具えている当該ドライバ回路において、

前記バックゲート電極をバイアスするとともに前記寄生トランジスタが前記ブートストラップキャパシタから分路除去するおそれのある電流を制限するバイアス兼制限手段が前記 バックゲート及び前記ドレイン電極に結合されていることを特徴とするドライバ回路。

#### 【請求項2】

請求の範囲 1 に記載のドライバ回路において、前記バイアス兼制限手段が、前記バックゲートに接続されたクランピングトランジスタ及び電流源を有していることを特徴とするドライバ回路。

#### 【請求項3】

請求の範囲 2 に記載のドライバ回路において、前記電流源が電流ミラー回路を有している ことを特徴とするドライバ回路。

#### 【請求項4】

請求の範囲1~3のいずれか一項に記載のドライバ回路において、前記負荷制御回路は、前記下側電圧ラインと前記制御電圧との間の電圧範囲を有するバッファ出力信号を生じるバッファ増幅器と、このバッファ増幅器の電圧範囲を前記のゲート電極に結合された点と前記のソース電極との間の電圧差の範囲に変換する変換手段とを有していることを特徴とするドライバ回路。

### 【請求項5】

請求の範囲 4 に記載のドライバ回路において、前記変換手段が容量性手段を有していることを特徴とするドライバ回路。

### 【請求項6】

請求の範囲 1 ~ 5 のいずれか一項に記載のドライバ回路において、前記負荷制御回路が更に、ドレイン及びゲート電極間に結合された前記LDMOSトランジスタのミラーキャパシタンスに流れる変位電流に応答して前記LDMOSトランジスタの前記ソース電極に前記ゲート電極をクランプする手段を有していることを特徴とするドライバ回路。

### 【請求項7】

請求の範囲6に記載のドライバ回路において、前記ソース電極に前記ゲート電極をクラン プする前記手段がPNPトランジスタを有していることを特徴とするドライバ回路。

#### 【請求項8】

請求の範囲1~7のいずれか一項に記載にドライバ回路において、前記LDMOSトランジスタのバックゲート及びソース電極間に容量性手段が結合されていることを特徴とするドライバ回路。

### 【請求項9】

請求の範囲 1~8のいずれか一項に記載のドライバ回路において、このドライバ回路が単 ーチップに集積化されていることを特徴とするドライバ回路。

#### 【請求項10】

ブリッジ回路と請求の範囲 1 ~ 9 のいずれか一項に記載のドライバ回路とを具えるランプ 点灯用安定器回路。」

### 【発明の詳細な説明】

本発明は出力端子と高電圧直流電源の下側電圧ライン及び上側電圧ラインとの間にそれぞれ接続された下側パワートランジスタ及び上側パワートランジスタを有するブリッジ回路を駆動するとともに、第1端が前記出力端子に結合されている当該第1端と第2端とを有するブートストラップキャパシタを充電するドライバ回路であって、このドライバ回路が電源出力端に前記下側電圧ラインに対する制御電圧を発生する電源手段と、

前記電源出力端に結合され、前記制御電圧により附勢される下側駆動モジュールであって、下側駆動制御信号を下側パワートランジスタの制御電極に供給して下側パワートランジスタを交互に導通及び非導通とする手段を有する当該下側駆動モジュールと、

前記ブートストラップキャパシタの両端間のブートストラップ電圧によって附勢するため

10

20

40

50

30

にこのブートストラップキャパシタに結合されるようになっている上側駆動モジュールであって、上側駆動制御信号を上側パワートランジスタの制御電極に供給して上側パワートランジスタを交互に導通及び非導通とする手段を有する当該上側駆動モジュールと、LDMOSトランジスタを有し、前記プートストラップキャパシタを前記プートストラップ電圧まで充電させるブートストラップダイオードエミュレータ手段であって、前記LDMOSトランジスタは、前記電源出力端に結合されたソース電極と、前記ブートストラップキャパシタの前記第2端に結合されるようになっているドレイン電極と、下側パワートランジスタが導通状態に駆動された際に前記LDMOSトランジスタを導通状態に駆動するための負荷制御回路を経て前記下側駆動モジュールに結合されたゲート電極と、バックゲート電極とを有するドライバ回路に関するものである。

このようなドライバ回路は本出願の優先日後に発行された米国特許第5,373,435号明細書から既知である。ブリッジ回路は、放電ランプ用の電子安定器、切換モード電源、モータ駆動及びDC - AC変換器に用いうる。上側駆動モジュールはモノリシック集積回路中に形成された絶縁されているウェル内に設けられており、LDMOSトランジスタはこのウェルの周縁の一部に沿って形成されている。LDMOSトランジスタを通る電流はウェルの周縁に対し垂直に流れ、所要の電流を流す容量はウェルの周縁に沿うLDMOSトランジスタを充分な長さに選択することにより得られるようにしている。LDMOSトランジスタの降伏電圧はウェルの周縁の絶縁特性によって決まる。その理由は、LDMOSトランジスタを形成するのに用いられる構造に等価の構造がウェルの周縁に浮動ウェルを形成する為である。

ブートストラップダイオードエミュレータを用いることにより、単一チップ上のドライバ 回路以外の素子と一緒にこのエミュレータを実現しうるという重要な利点が得られる。こ の場合、個々の素子を用いる場合よりも廉価で信頼的な方法でダイオード機能を実現しう る。

上述したダイオードエミュレータ手段と関連する欠点は、LDMOS装置に固有の寄生トランジスタがあるということであり、これら寄生トランジスタの1つは寄生PNPトランジスタであり、そのエミッタ及びベースはそれぞれLDMOSトランジスタのバックゲート及びドレインであり、そのコレクタはICの基板である。充電サイクル中のLDMOSトランジスタの起動に当って、寄生PNPトランジスタがある程度の電流をバックゲートから基板に分路し、ブートストラップキャパシタを充電するために得られる電流を減少させるということを確かめた。

本発明の目的は、ブートストラップダイオードエミュレータがより一層有効にブートストラップキャパシタを充電するドライバ回路を提供せんとするにある。

本発明は、出力端子と高電圧直流電源の下側電圧ライン及び上側電圧ラインとの間にそれぞれ接続された下側パワートランジスタ及び上側パワートランジスタを有するブリッジ回路を駆動するとともに、第1端が前記出力端子に結合されている当該第1端と第2端とを有するブートストラップキャパシタを充電するドライバ回路であって、このドライバ回路が

電源出力端に前記下側電圧ラインに対する制御電圧を発生する電源手段と、

前記電源出力端に結合され、前記制御電圧により附勢される下側駆動モジュールであって、下側駆動制御信号を下側パワートランジスタの制御電極に供給して下側パワートランジスタを交互に導通及び非導通とする手段を有する当該下側駆動モジュールと、

前記ブートストラップキャパシタの両端間のブートストラップ電圧によって附勢するためにこのブートストラップキャパシタに結合されるようになっている上側駆動モジュールであって、上側駆動制御信号を上側パワートランジスタの制御電極に供給して上側パワートランジスタを交互に導通及び非導通とする手段を有する当該上側駆動モジュールと、

LDMOSトランジスタを有し、前記ブートストラップキャパシタを前記ブートストラップ電圧まで充電させるブートストラップダイオードエミュレータ手段であって、前記LDMOSトランジスタは、前記電源出力端に結合されたソース電極と、前記ブートストラップキャパシタの前記第2端に結合されるようになっているドレイン電極と、下側パワートランジスタが導通状態に駆動された際に前記LDMOSトランジスタを導通状態に駆動するための負荷

10

20

30

40

50

20

30

40

50

制御回路を経て前記下側駆動モジュールに結合されたゲート電極と、バックゲート電極と を有し、このバックゲート及び前記ドレイン電極に寄生トランジスタが接続されている当 該ブートストラップダイオードエミュレータ手段と

を具えている当該ドライバ回路において、

前記バックゲート電極をバイアスするとともに前記寄生トランジスタが前記ブートストラップキャパシタから分路除去するおそれのある電流を制限するバイアス兼制限手段が前記バックゲート及び前記ドレイン電極に結合されていることを特徴とする。

これらのバイアス兼制限手段を用いることにより、バックゲート電極からLDMOSトランジスタに流れる電流を可成り抑圧しうるということを確かめた。

前記バイアス兼制限手段が前記バックゲート電極に接続されたクランピングトランジスタ及び電流源を有する場合には、LDMOSトランジスタのバックゲート電極から寄生トランジスタを経て流れる電流の量の極めて有効な抑圧を達成しうる。前記電流源は電流ミラー回路を有するようにするのが好ましい。

前記負荷制御回路は、前記下側電圧ラインと前記制御電圧との間の電圧範囲を有するバッファ出力信号を生じるバッファ増幅器と、このバッファ増幅器の電圧範囲を前記のゲート電極に結合された点と前記のソース電極との間の電圧差の範囲に変換する変換手段とにより、比較的簡単且つ信頼的に実現しうる。前記変換手段は容量性手段を有するのが好ましい。

ドレイン及びゲート電極間に結合された前記LDMOSトランジスタのミラーキャパシタンスを流れる変位電流に応答してこのLDMOSトランジスタのゲート電極をそのソース電極にクランプする手段を前記負荷制御回路に設けることにより、下側パワートランジスタがターン・オフする際に生じるスパイク電圧に応答してLDMOSトランジスタが導通状態に擬似駆動されるのを阻止することができる。クランプするためのこれらの手段はPNPトランジスタを用いて実現するのが好ましい。

ドレインにおける電圧過渡状態中にバックゲートが注入する電荷を収集するために、前記LDMOSトランジスタのバックゲート及びソース電極間に容量性手段を設けることができる

以下、図面を用いて本発明の実施例を説明する。図中、

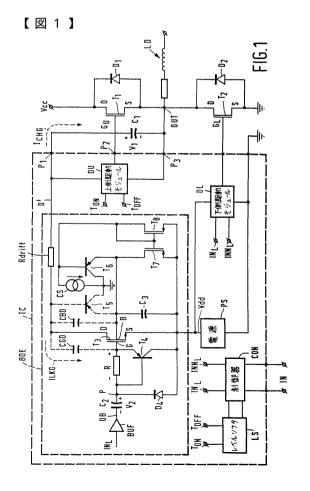

図1は、集積回路チップ中に設けられている素子をICで示す破線ブロックで囲んでいる本発明のドライバ回路を示す回路図であり、

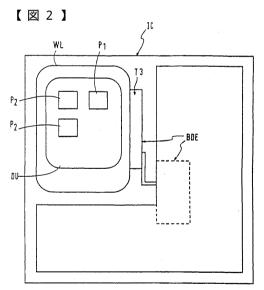

図 2 は、高電圧LDMOSトランジスタ $T_3$ を形成する細長領域を有する図 1 の破線ブロックIC に相当する集積回路チップを示す平面図である。

図 1 を参照するに、この図 1 には、高電圧モノリシック集積回路 ICに含まれる本発明によるドライバ回路が示されており、高電圧(約500ボルトまで)直流電源の両端間に直列に接続されたパワーMOSFET  $T_1$ 及び $T_2$ より成る外部の半ブリッジ回路を駆動するように接続されている。この半ブリッジ回路とドライバ回路との一般的な回路構成は前記の米国特許第4,989,127号明細書に開示されているのと同じであり、本発明によれば、チップ上(オンチップ)のブートストラップダイオードエミュレータBDEを設けるという点でこの米国特許の構成と相違する。

半ブリッジ回路では、パワートランジスタ $T_1$ を上側トランジスタと称する。その理由は、そのドレイン電極が図 1 に電位 $V_{cc}$ で示す直流電源の高電位側すなわち上側電圧ラインに接続されている為である。又、パワートランジスタ $T_2$ は下側トランジスタと称する。その理由は、そのソース電極が図 1 に接地電位として示す直流電源の低電位側すなわち下側電圧ラインに接続されている為である。上側トランジスタ $T_1$ のソース電極と下側トランジスタ $T_2$ のドレイン電極とは半ブリッジ回路の出力端子0UTに結合され、この出力端子は負荷 $T_2$ の一端にも接続されている。ガス入放電ランプに電力を与える場合のような電力供給分野では、負荷の他端を、直流電源の両端間の容量性分圧器(図示せず)の中間点に接続することにより電源電圧の半分の電位に維持することができる。周知のように、トランジスタ $T_1$ 及び $T_2$ は(20KHzより高い)高周波の繰返しサイクルに対し、例えば100KHz程度で切換えモードで動作し、約50ナノ秒程度の比較的短かい不感帯間隔だけ互いに分離されてい

10

20

30

40

50

る、1 サイクル中の2 つの期間すなわち位相のうちの異なる1 つの間に各トランジスタがターン・オン(すなわち導通状態に駆動)される。多くの分野では負荷LDが幾分誘導性のインピーダンスを有している為に電流の遮断時に生じるスイッチング過渡電圧がトランジスタ $T_1$  及び $T_2$  のそれぞれの固有の基板ダイオード $D_1$  及び $D_2$  により制限される。ダイオード $D_1$  は、下側のパワートランジスタ $T_2$  がターン・オフした際に出力端子OUTに生じる正の過渡電圧を制限するためのものであり、ダイオード $D_2$  は上側のパワートランジスタ $T_1$  がターン・オフした際に出力端子に生じる負の過渡電圧を制限するためのものである。

これらのサイクルは制御器CONにより確立され、この制御器CONは外部入力信号INに応答し て、下側トランジスタT₂の導通状態を制御する本来2進の命令信号IN₁及びその反転信号I NN,を生じるとともに、レベルシフタLSを介して上側トランジスタT,の導通状態を制御す るパルス命令信号Ton及びToffを生じる。命令信号INは、下側トランジスタToを導通状態 に駆動する必要がある場合の時間間隔すなわち位相中のみ1つの2進状態を有する。命令 信号ToN及びToffは雑音及び過渡状態を無くす目的でパルスの形態で生ぜしめられる。こ れら命令信号Ton及びToffは上側トランジスタTaをターン・オン及びターン・オフすべき 瞬時をそれぞれ表わす。下側トランジスタ命令信号IN,及びINN,は下側駆動モジュールDL に供給され、このモジュールDLはこれら信号に応答して、これら信号により規定される位 相中のみ下側トランジスタT2をターン・オンさせるようにこの下側トランジスタのゲート G」を駆動する。同様に、上側トランジスタ命令信号ToN及びTorrが上側駆動モジュールDU に供給され、このモジュールはこれら信号に応答して、これら信号により規定される位相 中上側トランジスタT<sub>1</sub>をターン・オンさせるようにこの上側トランジスタのゲートGUを駆 動する。上側駆動モジュールDU内のR/Sフリップフロップ(図示せず)が命令信号T。ハ及び T<sub>0 F F</sub> を I N L 及 び I N N L に 類似 する 2 進 形 態 に 変 換 し 、 上 側 駆 動 モ ジュ ー ル の バ ラ ン ス が 下 側 駆動モジュールDLと同じ設計となるようにしうる。

下側駆動モジュールDLは比較的低い電源電圧 $V_{\rm dd}$ 、例えば12ボルトで附勢され、上側駆動モジュールは、可成りの面積を犠牲にして集積回路 IC中に製造するにはあまりにも大きすぎる70nFの程度のキャパシタンスを有する外部のブートストラップキャパシタ $C_1$ の両端間の電圧 $V_1$ により附勢される。ブートストラップキャパシタ $C_1$ の一端はチップ上のブートストラップダイオードエミュレータBDEを経て電源電圧 $V_{\rm dd}$ に結合され、下側トランジスタ $V_{\rm dd}$ が導通状態にある際に出力端子OUTがほぼ接地電位に維持された場合に充電電流をキャパシタ $V_{\rm dd}$ に流し、電圧 $V_{\rm dd}$ よりもBDE及び $V_{\rm dd}$ の両端間のほんのわずかの電圧降下だけ小さい電圧にする。

次に図 2 をも参照するに、既知のように、上側駆動モジュールDUは、集積回路チップIC内の絶縁ウェルWL内に、例えば P 側分離領域により囲まれた N 側ウェル内に形成された C MOS 回路を有する。従って、ウェルWL は L D MOS トランジスタを得るのに用いるのと同様な構造により集積回路のバランスから絶縁される。高電圧ダイオードは、基板電流を大きくする為に接合分離技術で集積化することができない。これにより他の回路の動作を不能にするおそれがある。本発明の原理によれば、チップ上に設けたブートストラップダイオードエミュレータがウェルWLの周縁に沿って形成された L D MOS トランジスタ  $T_3$  を有する。 L D MOS トランジスタ  $T_3$  は(500ボルトを越える)ウェルの分離電圧と同程度の降伏電圧を固有的に有しており、電流はウェルの周縁に対し直角に流れる為に、ウェルの周縁の大きさを選択してこの周縁に沿って L D MOS トランジスタ  $T_3$  を形成することにより、流れる電流容量を適切に得ることができる。更に、L D MOS トランジスタ  $T_3$  の形成には追加面積の犠牲を必要としない。しかし、このトランジスタ  $T_3$  を駆動する回路に対し、集積回路上にわずかな追加の面積を必要とする為、下側トランジスタ  $T_2$  が導通状態に駆動された場合のみこの L D MOS トランジスタ  $T_3$  を導通状態にする。

図 1 に示すように、LDMOSトランジスタ $T_3$  は種々の固有の又は寄生の素子を有する理想的な装置として示してある。寄生のPNPトランジスタ $T_5$  があり、そのエミッタ及びベース電極はLDMOSトランジスタ $T_3$  のバックゲート電極 B 及びドレイン電極 D であり、トランジスタ $T_5$  のコレクタ電極は接地されている。このコレクタ電極が接地されている理由は、集積回路 ICの基板が接地されている為である。LDMOSトランジスタ $T_3$  は、バックゲート及びド

20

30

40

50

レイン間の寄生キャパシタCBDと、ゲート及びドレイン間のCGDと、理想的なLDMOSトランジスタのドレイン電極及びその実際のドレイン電極 D 間の固有の抵抗R<sub>drift</sub>とをも有する。この抵抗はLDMOSトランジスタの幅及び動作温度により決定される。

LDMOSトランジスタの幅は適用分野に基づいて選択される。LDMOSトランジスタ(75 $\mu$ mのリフト領域)の室温での代表的な $R_{on}$ はこの幅の1mm当り300 である。

LDMOSトランジスタT3は、そのソース電極 SがVddに接続され、その実際のドレイン電極 D がブートストラップキャパシタC<sub>1</sub>の高電圧側に接続されてソースホロワ構造で動作する 。トランジスタT<sub>3</sub>がターン・オンするのに応答して、ブートストラップキャパシタC<sub>1</sub>が充 電されてドレイン電極 DがVadに上昇する。トランジスタT3のターン・オン開始に当って は、寄生トランジスタT。によりそのエミッタからそのコレクタに流される電流を制限する 必要がある。その理由は、この寄生トランジスタの導通によりブートストラップキャパシ タC<sub>1</sub>を充電するために得られる電流を分路する為である。又、充電サイクル中の常規動作 中トランジスタT<sub>3</sub>のバックゲートを適切にバイアスする必要もある。このバイアスは常規 動作中バックゲートをバイアス電圧にクランプするためのPNPトランジスタT。を設けるこ とにより行ない、電流源によりバックゲートに給電して寄生トランジスタに流れる電流を 制限する。クランピングトランジスタT。のエミッタはバックゲートB(従って寄生トラン ジスタT<sub>5</sub>のエミッタ)と、FETトランジスタT<sub>8</sub>の電流を反射することにより電流源として 作用するFETトランジスタT7のドレインとに接続されている。トランジスタT6のコレクタ は接地され、そのベースはトランジスタT<sub>7</sub>,T<sub>8</sub>のゲートとトランジスタT<sub>8</sub>のドレインと、 電流源CSの一端とに接続されている。トランジスタT。のベースにおける電圧は低オーム抵 抗性として一定のクランプレベルを得るようにする必要がある。電流源CSの他端は接地す る。トランジスタT7,T8のソースはLDMOSトランジスタT3のソースに接続されている。 更に、LDMOSトランジスタT3のバックゲート及びソース間にキャパシタC3が接続されてい

電流源CSの電流はトランジスタ $T_8$ を流れ、電流ミラー作用の反射により同じ電流がトランジスタ $T_7$ を流れることに注意すべきである。

キャパシタC3は、トランジスタT3のドレインにおける電圧の過渡状態中にバックゲートが 注入する電荷を収集するものである。バックゲートBはトランジスタT3のソースSに対し て負にバイアスされた状態に維持することが重要である。キャパシタC<sub>3</sub>の値はLDMOSトラ ンジスタT3の幅に比例する。前述したように、この幅は実際の適用分野によって決まる。 バックゲートのバイアスの結果、LDMOSトランジスタT3をターン・オンさせるのに4Vのゲ ート・ソース電圧を必要とする。下側のパワートランジスタT₂を導通状態に駆動する際に LDMOSトランジスタT3をターン・オンさせるために、下側駆動命令信号 IN をバッファ増幅 器BUFに供給し、このバッファ増幅器が、下側のパワートランジスタT₂を導通状態に駆動 する際に電圧V<sub>dd</sub>にありそれ以外で零ボルトにある信号をバッファ増幅器の出力端OBに生 じるようにする。この電圧は比較的小さな第2のブートストラップキャパシタC2の一端に 供給される。このキャパシタ $C_2$ の他端 P はダイオード $D_4$ を経て電源電圧 $V_{dd}$ の点に結合さ れている。ブートストラップキャパシタ $C_2$ はトランジスタ $T_3$ のゲートキャパシタンスの少 なくとも 5 倍のキャパシタンスを有する。バッファ増幅器BUFは、第 2 のブートストラッ プキャパシタC₂がダイオードD₄を経てVααよりも1ダイオード降下分だけ低い電圧V₂に充 電される程度に充分低い出力インピーダンスを有する。このようにすることにより、バッ ファ増幅器の出力端OBにおける電圧の範囲(1ダイオード降下分よりも大きい)を点Pと LDMOSトランジスタT3のソース電極 S との間の電圧差の範囲に変える効果を生じる。点 P は約5Kの抵抗Rを経てトランジスタT3のゲート電極Gに接続されている。この抵抗は、 エミッタ、ベース及びコレクタがそれぞれトランジスタT₃のゲート電極、点P及びVddの 点に接続されているPNPトランジスタT4をターン・オンさせる電圧を発生させるのに用い られる。出力端OUTにおけるスイッチング過渡電圧によるLDMOSトランジスタT<sub>3</sub>の擬似ター ン・オンを阻止するために、トランジスタT₄がCց を経るミラー電流による抵抗Rの両端 間の電圧に応答してトランジスタT<sub>3</sub>のゲートをV<sub>dd</sub>に積極的に降下させる。さもないと、 出力端OUTにおける出力電圧が零から $V_{cc}$ へ変化し、LDMOSトランジスタ $T_3$ のドレイン電極

が対応する電圧範囲に亘って変化する場合の大きな正の電圧変化により生じるこの電流により、ゲート容量をターン・オンレベルに充電せしめてしまう。その結果、ブートストラップダイオードエミュレータBDEはブートストラップダイオードが導通する時にのみ導通し、ブートストラップキャパシタC<sub>1</sub>を正しく充電させる。

本発明によればその目的があらゆる点で満足されること明らかである。更に、本発明を詳細に説明したが、その原理の適用分野は更に広いものである。従って、本発明の範囲を逸脱することなく種々の変更を加えうること勿論である。

FIG.2

## フロントページの続き

審査官 柳下 勝幸

(56)参考文献 欧州特許出願公開第367006(EP,A2) 米国特許第5373435(US,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名) HO3K 17/00 HO2M 1/00,7/00