(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7401050号**

**(P7401050)**

(45)発行日 令和5年12月19日(2023.12.19)

(24)登録日 令和5年12月11日(2023.12.11)

(51)国際特許分類

|         |                  |     |         |        |         |

|---------|------------------|-----|---------|--------|---------|

| G 0 6 F | 13/362 (2006.01) | F I | G 0 6 F | 13/362 | 5 1 0 B |

| G 0 6 F | 13/14 (2006.01)  |     | G 0 6 F | 13/14  | 3 1 0 D |

| G 0 6 F | 13/36 (2006.01)  |     | G 0 6 F | 13/36  | 5 3 0 B |

請求項の数 5 (全14頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2018-174191(P2018-174191) |

| (22)出願日  | 平成30年9月18日(2018.9.18)       |

| (65)公開番号 | 特開2020-46876(P2020-46876A)  |

| (43)公開日  | 令和2年3月26日(2020.3.26)        |

| 審査請求日    | 令和3年9月6日(2021.9.6)          |

| 審判番号     | 不服2023-3707(P2023-3707/J1)  |

| 審判請求日    | 令和5年3月3日(2023.3.3)          |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (72)発明者  | 村山 公平<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| 合議体      |                                            |

| 審判長      | 須田 勝巳                                      |

| 審判官      | 山崎 慎一                                      |

| 審判官      | 吉田 美彦                                      |

最終頁に続く

(54)【発明の名称】 バス制御回路

**(57)【特許請求の範囲】****【請求項1】**

複数のバスマスターとスレーブモジュールとのバスの接続を制御するバス制御回路であつて、

前記複数のバスマスターに接続され、前記複数のバスマスターそれぞれからのバス転送要求信号を受信し、予め設定された優先順位に従ってバス転送要求信号を発行した前記複数のバスマスターの内の1つに対するバス権を付与することを示す調停結果信号を出力する单一の調停回路と、

複数のバススイッチとを有し、

前記複数のバススイッチそれぞれは、

複数のバス転送信号を受信するための複数の入力端子、および、前記複数の入力端子のうちの1つバス転送信号を下流に伝達するための出力端子とを有する選択回路と、

前記調停回路が output する前記調停結果信号を受信し、当該調停結果信号に基づいて前記選択回路に対して前記複数の入力端子のいずれか1つを選択するよう制御する制御回路とを有し、

前記複数のバススイッチの少なくともいずれか1つが有する前記複数の入力端子に、上流のバススイッチの出力端子および前記複数のバスマスターの少なくともいずれか1つが接続され、

最下流に位置するバススイッチが有する前記選択回路の出力端子に前記スレーブモジュールが接続される

ことを特徴とするバス制御回路。

**【請求項 2】**

前記制御回路は、前記調停結果信号をバススイッチの経路情報に変換し、切替選択信号として保持するメモリを有することを特徴とする請求項 1 に記載のバス制御回路。

**【請求項 3】**

前記制御回路が有する前記メモリは、前記单一の調停回路が前記調停結果信号を出力したサイクルにおいて前記切替選択信号を FIFO 形式で保持し、前記制御回路は、前記切替選択信号を保持された順に用いて、前記選択回路に対して前記複数の入力端子のいずれか 1 つを選択し、前記調停結果信号に対応するバス転送要求信号の最終転送がなされたサイクルで、前記調停結果信号に対応する前記切替選択信号を削除するよう制御することを特徴とする請求項 2 に記載のバス制御回路。

10

**【請求項 4】**

前記バススイッチは、アドレス情報バスを伝達するスイッチと、データ情報バスを伝達するスイッチを有することを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のバス制御回路。

**【請求項 5】**

前記調停回路は、前記複数のバスマスターから、前記バス転送要求信号とともにバス転送方向を示す情報を更に受信し、バス権を与えるとして決定したバスマスターからのバス転送方向を示す情報を前記調停結果信号とともにに出力し、

前記制御回路は、前記バス転送方向を示す情報を参照し、前記調停結果信号を、バススイッチの経路情報に変換し、切替選択信号として保持するメモリを有することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のバス制御回路。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は複数のバスマスターからスレーブへのアクセス時のバスマスター間のアクセス調停であるバス制御技術に関するものである。

**【背景技術】**

**【0002】**

CPU やシステムの機能を司り動作するモジュールを含むハードウェアシステムでは、共有バスを介して主記憶メモリなどのスレーブモジュールに接続されている。システムの動作に当たっては、バスマスターモジュールがバスを介してメモリへのアクセスを発行しシステムの動作を実現する。このようなハードウェアシステムは一般的には、半導体集積回路上に実装される。半導体技術の進展に伴い半導体集積回路に搭載可能な論理は飛躍的に向上し、それに伴いシステムの規模が拡大の一途をたどっている。

30

**【0003】**

このようにシステム規模が拡大すると、搭載可能な機能が増加し、それに伴い主記憶にアクセスするバスマスターモジュールの数も増加することになる。

**【0004】**

複数のバスマスターモジュールがメモリなどにアクセスを同時に発行する場合、共有バス上でアクセスが競合するため、システムが定める所定の動作仕様に従い優先度をつけて調停されることが一般的である。調停回路は一般にバスマスターからのアクセス要求を受け付け、動作仕様で定められる所定の条件に基づいてアクセス許可するバスマスターを選択する。バススイッチは調停回路で選択されたバスマスターの情報に基づき、複数のバスマスターモジュールのアクセスから 1 つのアクセスを選択する。一般にバススイッチでは、アドレスなどのアクセス属性を示す多ビットの信号やアクセステータなどの多ビットの信号を選択する論理として構成される。

40

**【0005】**

複数のバスマスターモジュールとスレーブ間の接続を構成するバスシステムとして単一の調停回路とバススイッチでバスシステム構成する SHARED BUS 方式と呼ばれるバ

50

スシステムが存在する。

**【 0 0 0 6 】**

SHARED BUS 方式では単一の調停回路でバスアクセスを選択するため、所定の優先度でスレーブモジュールにバス転送を伝達可能である。

**【 0 0 0 7 】**

しかしながら本方式ではバスマスタ数が増えるに従い、複数のバスマスタモジュールのアクセスから一つを選択するバススイッチにて、多ビットの信号が集中することにより半導体集積回路上で配線混雑が発生し、回路規模が大きくなってしまう課題がある。また、複数のバスマスタモジュールの多ビットのバス信号から1つを選択する論理構造となるため、論理段数が深くなることに起因して、動作周波数に制限が生じる課題が発生する。

10

**【 0 0 0 8 】**

例えば200を超えるバスマスタモジュールを単一のバススイッチで実装した場合、バスシステム回路全体で配線集中が発生する。配線集中を回避するために配置面積を拡大することによって回路規模が肥大化する。一方で論理段数が深いことでタイミング収束性が困難な論理に対して配置面積を拡大することで配線遅延がさらに大きくなり、動作周波数に制限が発生する。その結果、近年の多機能化によるバスマスタモジュール数が多いシステムでは、単一のバススイッチでバスシステムを構築することは実現することは困難である。

10

**【 0 0 0 9 】**

このような課題に対応し多くのバスマスタモジュールを取り扱う大規模システムでは、バススイッチを階層的に配置し多段で構成し、各バススイッチに接続されるバスアクセス間でアクセス調停を行う階層バス方式が一般的になりつつある（特許文献1）。

20

**【先行技術文献】**

**【特許文献】**

**【 0 0 1 0 】**

**【文献】特開2010-282405公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【 0 0 1 1 】**

しかしながら、階層バス方式では、バススイッチを多段で構成し、個々のバススイッチにてアクセス間の調停が行うものであった。このため、全てのマスタ間で設定される優先順位と多段で段階的に調停された結果の優先順位が異なる場合が生じる。

30

**【 0 0 1 2 】**

その結果、優先度が低いアクセスが優先度の高いアクセスに先立ってバス転送がスレーブモジュールに伝達されるケースが生じうる。一方で、大規模システムでは複数のプロセスやタスクが競合し動作するため、システム全体性能を満足するためにはバス転送の優先順位に従って実現することが求められるケースがある。このような場合、階層バス方式ではスレーブモジュールとの間に、バス転送のアクセス順を優先度に従ってアクセス順を並び替える論理が必要となる。アクセス順を並び替える論理は、複数のアドレスコマンドとそれに紐づく書き込みデータを保持が必要である。一般的にアドレスコマンドは、アドレス信号やマスタ識別信号、転送方向信号、転送タイプ信号等を有し40ビット程度の信号で表される。また、書き込みデータは、バス幅やバスプロトコルにも依存するが64ビットバスの場合はデータとバイトイネーブル情報の72ビットの信号で表される。さらに一つのアドレスコマンドに対して、バス転送のバースト長に応じて複数の72ビット信号で表される。例えば、バス転送のバースト長が16ビートである場合、1152ビットの信号が必要となる。ここで、アクセス順を並び替える論理が4転送保持して並び替える場合、4768ビットの信号を保持し、並び替える必要があり、相当数の回路規模を消費することとなる。さらに並び替え論理は条件を比較し出力する幅の広いデータを選択する論理となるため、配線混雑や動作周波数確保のためのステージ分割が必要となり、コストアップの要因となる。

40

50

**【0013】**

本発明は、上記の課題を鑑みたものであり、階層バス方式において所定の優先度に従いバス転送をスレーブモジュールに伝達可能なバス制御回路を提供しようとするものである。

**【課題を解決するための手段】****【0014】**

この課題を解決するため、例えば本発明のバス制御回路は以下の構成を備える。すなわち、

複数のバスマスターとスレーブモジュールとのバスの接続を制御するバス制御回路であつて、

前記複数のバスマスターに接続され、前記複数のバスマスターそれぞれからのバス転送要求信号を受信し、予め設定された優先順位に従ってバス転送要求信号を発行した前記複数のバスマスターの内の1つに対するバス権を付与することを示す調停結果信号を出力する单一の調停回路と、

10

複数のバススイッチとを有し、

前記複数のバススイッチそれぞれは、

複数のバス転送信号を受信するための複数の入力端子、および、前記複数の入力端子のうちの1つバス転送信号を下流に伝達するための出力端子とを有する選択回路と、

前記調停回路が output する前記調停結果信号を受信し、当該調停結果信号に基づいて前記選択回路に対して前記複数の入力端子のいずれか1つを選択するよう制御する制御回路とを有し、

20

前記複数のバススイッチの少なくともいずれか1つが有する前記複数の入力端子に、上流のバススイッチの出力端子および前記複数のバスマスターの少なくともいずれか1つが接続され、

最下流に位置するバススイッチが有する前記選択回路の出力端子に前記スレーブモジュールが接続されることを特徴とする。

**【発明の効果】****【0015】**

本発明により、階層バス方式において所定の優先度に従いバス転送をスレーブモジュールに伝達可能なバス制御回路を提供できるようになる。

**【図面の簡単な説明】**

30

**【0016】**

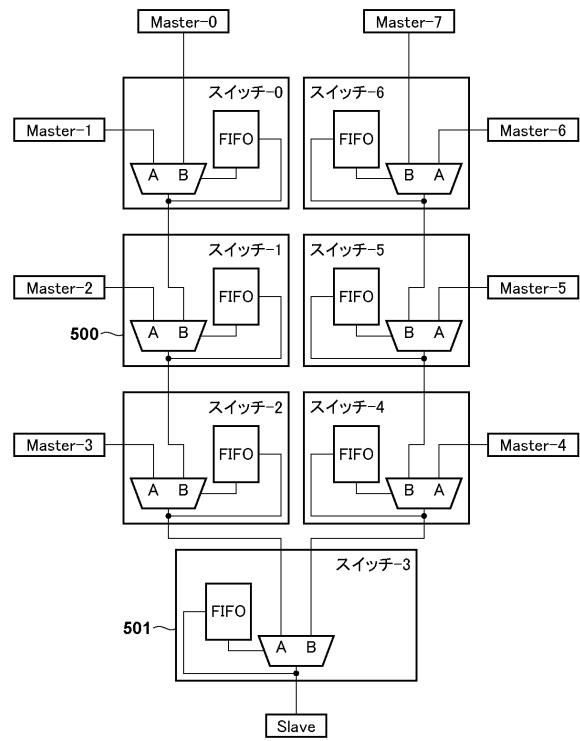

【図1】第1の実施形態におけるバスシステム構成図。

【図2】第1の実施形態におけるバススイッチ回路の構成図。

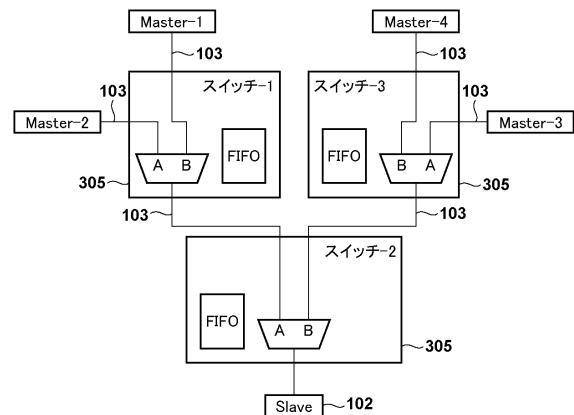

【図3】第2の実施形態におけるバスシステム構成図。

【図4】第2の実施形態におけるバススイッチ回路の構成図。

【図5】第2の実施形態におけるバスシステム構成概略図。

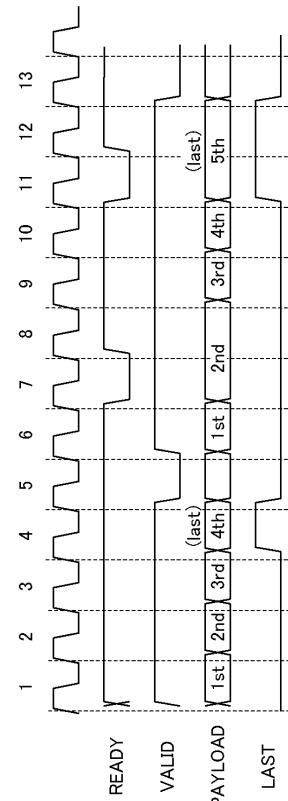

【図6】実施形態におけるス転送の信号波形例を示す図。

【図7】第2の実施形態の作用を説明するためのバスシステム構成図。

【図8】図7の作用説明におけるサイクル毎のバススイッチの状態説明図。

**【発明を実施するための形態】**

40

**【0017】**

以下、添付図面に従って本発明に係る実施形態を詳細に説明する。なお、以下に示す実施形態における構成は一例に過ぎず、本発明は図示された構成に限定されるものではない。

**【0018】****[第1の実施形態]**

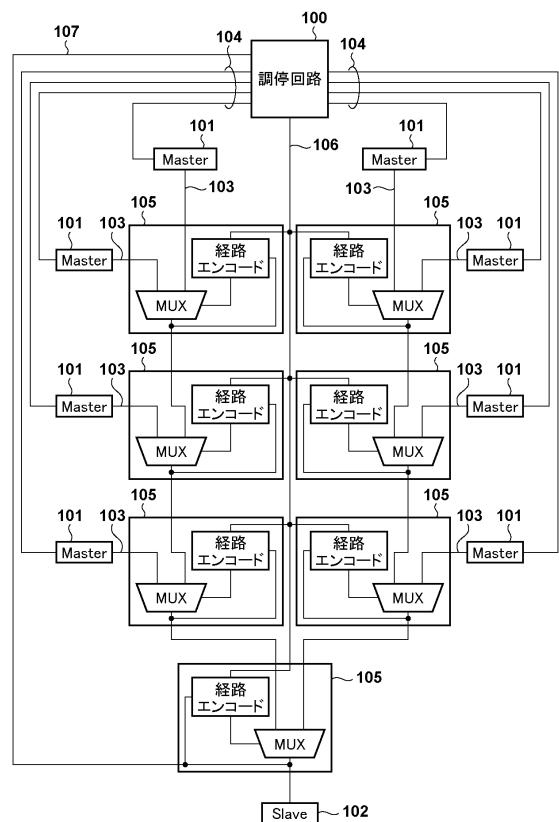

図1は、第1の実施形態におけるバス制御回路を搭載するバスシステムの構成図である。図1に例示するバスシステムは8つのバスマスター モジュール101と、1つのスレーブモジュール102で構成されるバスシステムである。なお、バスマスター モジュール、スレーブモジュールの数に特に制限はなく、あくまで例示であると理解されたい。

**【0019】**

50

バスマスタモジュール 101 はバス転送要求信号 104 とバス転送信号 103 を出力する。調停回路 100 は各バスマスタモジュール 101 のバス転送要求信号 104 を集約する。また、調停回路 100 は、バス転送要求を出力したバスマスタモジュール 101 の中から、予め設定された条件に従って、それらバス転送要求を調停し、バスアクセス権を与える対象の 1 つのバスマスタモジュール 101 を決定する。

#### 【0020】

バス転送要求信号 104 は、バスマスタモジュール 101 がバスアクセスの要求の有無を示す信号であり、バスアクセス要求の有無に加えて転送方向や当該バスアクセスの優先度情報を含んでいても構わない。

#### 【0021】

調停回路 100 は、各バスマスタモジュール 101 からのバス転送要求信号 104 を受け、バス転送許可を与えるバスマスタモジュールを決定する。そして、調停回路 100 は、決定したバスマスタモジュールにバス転送許可を与えるべく、該当するバスマスタモジュールからスレーブモジュール 102 に経路を表すバスマスタ情報を、調停結果信号 106 として出力する。この調停結果信号 106 はバスを構成する全てのバススイッチ回路 105 に伝達される。

#### 【0022】

なお、実施形態では、バスマスタの個数を 8 個の例を示している。そのうちの 1 つがスレーブモジュールと接続されることになるので、バスマスタを特定するためには 3 ビットあればよい。したがって、調停回路 100 が出力する調停結果信号 106 は、3 ビットと少ない信号線で表すことができる。

10

20

#### 【0023】

バスマスタモジュール 101 からスレーブモジュール 102 までの経路はバススイッチ回路 105 を介して接続され、各バスマスタモジュール 101 のバス転送信号 103 はバススイッチ回路 105 に入力される。

#### 【0024】

バス転送信号 103 は当該バスアクセスのアドレス情報やバス転送方向、バス転送識別情報などのコマンド情報を含む。また、スレーブモジュール 102 への書き込みの場合、バス転送信号 103 は、コマンド情報に加え、書き込むべきデータを含むことになる。

30

#### 【0025】

バススイッチ回路 105 は複数のバス転送信号 103 を入力し、一方を選択して出力バスに伝達するするスイッチ回路である。本実施形態では 2 つのバス転送信号 103 の入力バスの構成を例示している。以下、バススイッチ回路 105 の構成を説明する。

40

#### 【0026】

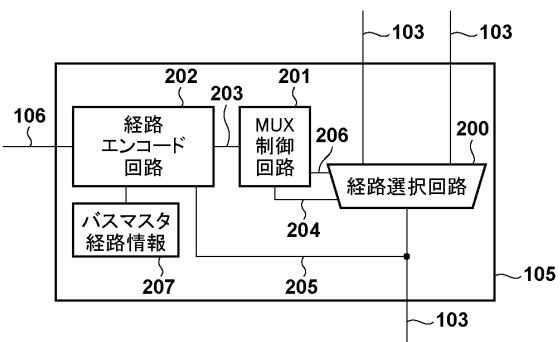

図 2 はバススイッチ回路 105 の構成図である。調停回路 100 から転送許可されるバスマスタモジュールの情報として通知され調停結果信号 106 は経路エンコード回路 202 に入力される。経路エンコード回路 202 は、受信した調停結果信号 106 に基づき、当該バスマスタモジュールのバス転送が当該バススイッチ回路 105 を介して転送されるか否かを判定する。経路エンコード回路 202 は、バス構成情報として当該バススイッチ回路 105 に入力される 2 つのバス転送信号 103 のそれぞれに対し、いずれのバスマスタモジュール 101 の転送が行われるかのバスマスタ経路情報 207 を保持している。このバスマスタ経路情報 207 は、例えば ROM やレジスタファイルなどのメモリに格納される。

#### 【0027】

当該バススイッチ回路 105 を介して転送される場合、経路エンコード回路 202 は、経路選択回路 200 のいずれの入力端子を選択するのかを示す情報をエンコードし、経路 MUX 制御回路 201 に経路選択情報 203 として通知する。当該バススイッチ回路 105 を介さないバス転送である場合は、経路エンコード回路 202 は、調停結果信号 106 9 に応答した処理は行わず、経路 MUX 制御回路 201 への通知は行わない。

#### 【0028】

50

経路MUX制御201は、経路選択回路200からの経路選択情報203の通知に従い、バスマスタ経路情報207を生成する。本例では、経路選択回路200は、2入力端子、1出力端子の選択回路となっているため、経路選択情報203は1ビットの情報である。

#### 【0029】

経路MUX制御回路201は経路エンコード回路202より経路選択情報203が通知されると、入力される2つのバス転送信号103のいずれか一方を選択するための切替選択信号204をスイッチの切替情報として生成し出力する。また、経路MUX制御回路201は、有効な切替選択信号204の有無を示すバスマスタ経路ステータス情報206を出力する。

#### 【0030】

経路エンコード回路202は、さらに、下流に出力されるバス転送信号103でバス転送の最終を示すフラグ信号205入力に有し、最終転送フラグ信号205の発行により当該転送の切替選択信号204と当該バスマスタ経路ステータス情報206の出力を停止する。最終転送フラグ信号205は、バスマスタモジュール101が発行したバス転送要求に関連付けられるバス転送の最終転送を示すフラグ信号である。フラグ信号の生成は任意であるが、例えば図6の波形に示すようにバス転送信号103がV A L I D、R E A D Yの2線ハンドシェイクによる転送においてバス転送のペイロードの最終サイクルを示すフラグ信号として実現しても構わない。図6の例では、2つのバス転送を示している。1番目の1連のバス転送は4サイクルのバス転送、2番目のバス転送は5サイクルのバス転送である。それぞれの最終のペイロード転送である4サイクル目の転送と5サイクル目の転送でL A S T信号を発行することで、1連のバス転送の最終サイクルを示している。ここでは、バス転送で明示的に最終転送を示すフラグを付与する形式を例示しているが、例えばペイロードに転送長データ情報を有し、その情報を参照することでフラグ信号を生成することも可能である。また、転送長が固定のバス転送である場合には、固定サイクル間隔でフラグ信号を生成しても構わない。

10

#### 【0031】

スレーブモジュール102にダイレクトに接続される、最下流の位置するバススイッチ回路105は、最終転送を示すフラグ信号205を、転送終了フラグ信号107として調停回路100に通知する。調停回路100は調停結果信号104を出力後、転送終了フラグ信号107の受信を待って次のバスアクセスの調停結果を出力する。経路選択回路200は切替選択信号204が示す値に基づき2つのバス転送信号103のいずれか一方を出力（もしくは通過）するよう制御する。また、経路選択回路200は、経路選択情報の状態である経路ステータス情報206の入力を有する。経路選択回路200は経路ステータス情報206で、有効な経路選択情報が無い場合、2入力のバス転送信号103のいずれも出力しないように制御する。すなわち、経路選択回路200は、有効なバス経路選択情報が入力されていない状態下では、上流からのバス転送信号103の情報を下流に伝達しないよう制御される。

20

#### 【0032】

このようにバススイッチ回路105を構成することにより、調停回路100により決定したバス権を取得するバスマスタモジュール101順にスレーブモジュール102へのバス転送の経路を構成し、バス転送を実現することが可能となる。

30

#### 【0033】

##### [第2の実施形態]

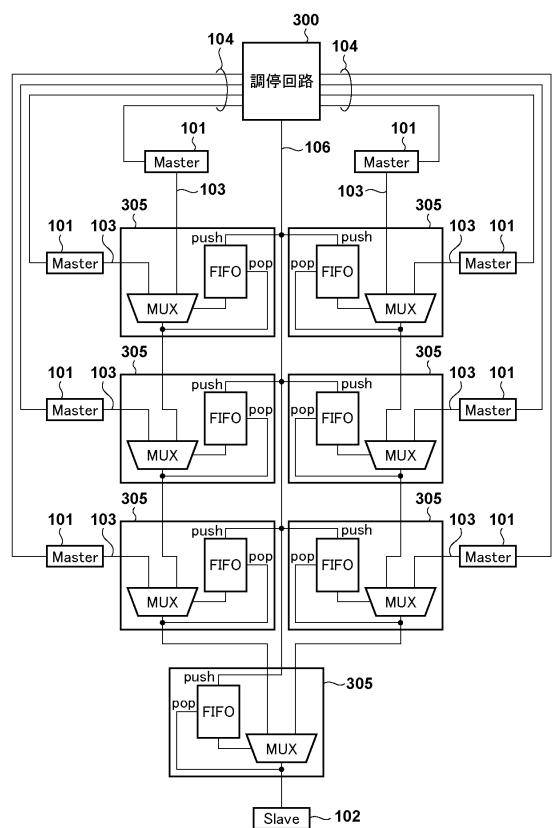

図3は第2の実施形態を示すバスシステムの構成図である。図3に例示するバスシステムは8つのバスマスタモジュール101と1つのスレーブモジュール102で構成されるバスシステムである。バスマスタモジュール101はバス転送要求信号104とバス転送信号103を出力する。

#### 【0034】

調停回路300は各バスマスタモジュール101からのバス転送要求に応答し、予め設定された条件に従って、複数のバス転送要求を調停し、バスアクセス権を与える1つのバ

40

50

スマスタモジュールを決定する。また、調停回路 300 は各バススマスタモジュール 101 のバス転送要求信号 104 を集約する。

#### 【0035】

バス転送要求信号 104 は、バススマスタモジュール 101 が発行するバスアクセスの要求の有無を示す信号であり、バスアクセス要求の有無に加えて転送方向や当該バスアクセスの優先度情報を含んでいても構わない。

#### 【0036】

調停回路 300 は、各バススマスタモジュール 101 からのバス転送要求を受け、バス転送許可を与える 1 つのバススマスタモジュールを決定し、バス転送許可を与えるバススマスタ情報を調停結果信号 106 として出力する。調停結果信号 106 はバスを構成する全てのバススイッチ回路 305 に伝達される。10

#### 【0037】

バススマスタモジュール 101 からスレーブモジュール 102 までの経路はバススイッチ回路 305 を介して接続され、各バススマスタモジュール 101 のバス転送信号 103 はバススイッチ回路 305 に入力される。

#### 【0038】

バス転送信号 103 は当該バスアクセスのアドレス情報やバス転送方向、バス転送識別情報などのコマンド情報を含む。また、スレーブモジュール 102 への書き込みの場合には、バス転送信号 103 は、その書き込みのデータを含むことになる。本実施形態では、コマンド情報と書き込みデータを含んだ構成を例示しているが、コマンド情報と書き込みデータがバス転送信号として分離した構成であっても構わない。20

#### 【0039】

バススイッチ回路 305 は複数のバス転送信号 103 を入力し、一方を選択して出力バスに伝達するスイッチ回路である。本実施形態では 2 つのバス転送信号 103 の入力バスの構成を例示している。以下、バススイッチ回路 305 の構成を説明する。

#### 【0040】

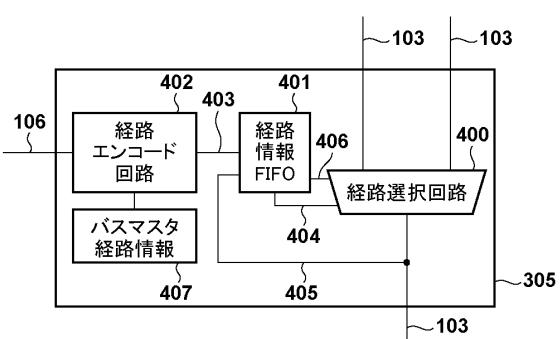

図 4 は第 2 の実施形態における、バススイッチ回路 305 の構成図である。調停回路 300 から転送許可されるバススマスタモジュールの情報として通知され調停結果信号 106 は経路エンコード回路 402 に入力される。経路エンコード回路 402 は、当該バススマスタモジュールのバス転送が当該バススイッチ回路 305 を介して転送されるか否かを判定する。このため、経路エンコード回路 402 は、バス構成情報として当該バススイッチ回路 305 に入力される 2 つのバス転送信号 103 のそれぞれに対し、いずれのバススマスタモジュール 101 の転送が行われるかの判定するためのバススマスタ経路情報 407 を保持している。30

#### 【0041】

当該バススイッチ回路 305 を介して転送される場合、経路エンコード回路 402 は、いずれのバス転送信号 103 より入力されるかの情報にエンコードし、経路情報 FIFO 401 に経路選択情報 403 として通知する。当該バススイッチ回路 305 を介さないバス転送である場合は、経路エンコード回路 402 は、調停結果信号 106 に応答した処理は行わず、経路情報 FIFO 401 への通知は行わない。40

#### 【0042】

図 5 は、図 3 に対して個々のバススマスタモジュール 101 とバススイッチ回路 305 それぞれを識別可能にし、個々のスイッチ回路 305 の経路選択論理の経路を識別可能に示したものである。以下、図 5 を参照して、スイッチ回路 305 の動作を説明する。

#### 【0043】

バススマスタモジュールの 1 つである「Master - 2」に繋がるスイッチ回路である“スイッチ - 1 (500)”に関して例示する。したがって、以下に説明する、経路選択回路 400 等は、スイッチ - 1 (500) 内のものとなることに注意されたい。転送許可されるバススマスタモジュールの情報が、Master - 0 あるいは Master - 1 である場合、経路エンコード回路 402 はスイッチ - 1 (500) を介する転送として判定する。50

経路エンコード回路 402 は経路 B より転送されるバス転送と判定し、本情報を経路選択情報 403 として経路情報 FIFO401 に通知する。転送許可されるバスマスタモジュールの情報が、Master - 2 である場合も同様に、経路エンコード回路 402 はスイッチ - 1 (500) を介する転送として判定する。経路エンコード回路 402 は経路 A より転送されるバス転送と判定し、本情報を経路選択情報 403 として経路情報 FIFO401 に通知する。対して、転送許可されるバスマスタモジュールの情報が Master - 3 から 7 のいずれかであった場合は、経路エンコード回路 402 はスイッチ - 1 (500) を介さない転送として判定し、経路選択情報 203 の通知を行わないよう動作する。

#### 【0044】

次にスレーブモジュール 102 にダイレクトに接続されるスイッチ回路であるスイッチ - 3 (501) に関して例示する。当該スイッチ - 3 は、転送許可されるバスマスタモジュールの情報が Master - 0 から 7 のいずれであっても、経路エンコード回路 402 はスイッチ - 3 (501) を介する転送として判定する。すなわち、スイッチ - 3 (501) を介さない転送と判定する条件は存在しない。転送許可されるバスマスタモジュールの情報が Master - 0 から 3 のいずれかであった場合、経路エンコード回路 402 は経路 A より転送されるバス転送と判定し、本情報を経路選択情報 403 として経路情報 FIFO401 に通知する。一方、転送許可されるバスマスタモジュールの情報が Master - 4 から 7 のいずれかであった場合、経路エンコード回路 402 は経路 B より転送されるバス転送と判定し、本情報を経路選択情報 403 として経路情報 FIFO401 に通知する。

10

#### 【0045】

経路選択情報 FIFO401 は経路選択回路 400 の選択情報を FIFO 形式で保持するよう構成される。経路エンコード回路 402 により通知される経路選択情報 403 を FIFO に登録する。本例では、経路選択回路 400 は 2 入力の選択回路となっているため、経路選択情報 403 は 1 ビットの情報であり、経路選択情報 FIFO401 は 1 ビットの FIFO として構成される。

20

#### 【0046】

経路選択情報 FIFO401 は経路エンコード回路 402 より経路選択情報 403 が通知されると、当該経路選択情報 403 を FIFO に登録する。さらに、下流に出力されるバス転送信号 403 でバス転送の最終を示すフラグ信号 405 入力を有し、最終転送フラグ信号 405 の発行により FIFO より一番古く登録されたエントリを削除するよう動作する。最終転送フラグ信号 405 は、バスマスタモジュール 101 が発行したバス転送要求に関連付けられるバス転送の最終転送を示すフラグ信号である。フラグ信号の生成は任意であるが、第 1 の実施形態と同様、例えば図 6 の波形に示すようにバス転送信号 103 が VALID・READY の 2 線ハンドシェイクによる転送においてバス転送のペイロードの最終サイクルを示すフラグ信号として実現しても構わない。

30

#### 【0047】

経路選択情報 FIFO401 は、FIFO の先頭に保持されている経路選択情報を経路選択回路 400 の切替選択信号 404 として出力する。経路選択回路 400 は切替選択信号 404 が示す値に基づき 2 入力のバス転送信号 103 のいずれかを出力するように制御する。以上より経路選択情報 FIFO401 はスイッチの切替順情報を保持するよう動作する。

40

#### 【0048】

また、経路選択回路 400 は経路情報 FIFO401 に保持される経路選択情報の状態である FIFO ステータス情報 406 の入力を有する。経路選択回路 400 は FIFO ステータス情報 406 で、FIFO に保持されている有効な経路選択情報のエントリが無い場合、2 入力のバス転送信号 103 のいずれも出力しないように制御する。すなわち、経路情報 FIFO401 のエントリが空の場合は上流からのバス転送信号 103 の情報を下流に伝達しないよう制御される。

#### 【0049】

50

このようにバススイッチ回路 305 を構成することにより、調停回路 300 により決定したバス権を取得するバスマスタモジュール 101 順にスレーブモジュール 102 へのバス転送の経路を構成し、バス転送を実現することが可能となる。

#### 【0050】

次に、図 7 に示した 4 つのバスマスタモジュール 101 のバス構成を用いて、バス全体の挙動を説明する。図 8 はサイクル毎のバスを構成する 3 つのバススイッチ回路 305 におけるバス転送信号 103 の状態と経路選択 FIFO401 の状態を示している。また、本例では説明を簡易にするために各バス転送は 2 サイクルの転送であるものとして例示する。Cycle - 0 では 4 つのバスマスタモジュールがバス転送要求を発行している状態で、調停回路 300 はまだ調停結果信号 106 が発行されていない状態である。各バスマスタモジュールはバス転送信号 103 を下流に向けて発行している状態である。本状態を図 8 では “valid” と示しており、スイッチ - 1 とスイッチ - 3 の経路 A、経路 B はそれぞれ “valid” となっている。各バススイッチの経路選択 FIFO401 は空の状態であり、そのため各バススイッチは下流にバス転送信号 103 を発行しない状態である。したがって、スイッチ - 2 の経路 A、経路 B はバス転送が発行されていない状態 “-” となっている。

10

#### 【0051】

本例では、調停回路 300 はバスマスタモジュール 101 からのバス転送要求に応答して、Master - 1、Master - 2、Master - 3 の順にバス権を与えるものとする。そして、Master - 1 は自身のバス転送が終了時あるいは終了前に次バス転送要求を発行し、Master - 4 に先立って Master - 1 に対してバス権を与えている。さらに、Master - 3 は Cycle - 8 でバス転送要求を発行し、Cycle - 9 で調停回路 (100) は Master - 3 に対してバス権を与えるよう動作しているものとする。

20

#### 【0052】

Cycle - 1 で調停回路 300 より Master - 1 に対してバス権が付与されると、スイッチ - 1 の経路情報 FIFO401 には経路 B の情報、スイッチ - 2 の経路情報 FIFO401 には経路 A の情報が登録される。スイッチ - 3 については、バス権が与えられた Master - 1 は当該スイッチとは関連しないため、経路情報 FIFO401 には経路情報が登録されず、FIFO は空の状態が継続する。スイッチ - 1 では、経路情報 FIFO401 に情報が登録されたため、経路選択回路 400 は経路 B を選択するよう動作し、スイッチ - 1 に入力される経路 B の Master - 1 の第一転送がスイッチ 2 に対して出力される。スイッチ - 2 の経路情報 FIFO401 にも情報が登録されたため、経路選択回路 400 は経路 A を選択するよう動作するが、スイッチ - 1 からのバス転送が入力前であるため、下流に有効なバス転送は発行されない。

30

#### 【0053】

Cycle - 2 で調停回路 300 より Master - 2 に対してバス権が付与されると、スイッチ - 1 の経路情報 FIFO401 には経路 A の情報、スイッチ - 2 の経路情報 FIFO401 には経路 A の情報が登録される。スイッチ - 1 では経路 B より Master - 1 の最終転送が伝送される状態であり、経路選択回路 400 の経路は切り換わっていない状態である。一方、スイッチ - 2 は、経路 A よりスイッチ - 1 より転送された Master - 1 の第一転送を下流のスレーブモジュール 102 に転送する。

40

#### 【0054】

Cycle - 3 で調停回路 300 より Master - 3 に対してバス権が付与されると、スイッチ - 3 の経路情報 FIFO401 には経路 A の情報、スイッチ - 2 の経路情報 FIFO401 には経路 B の情報が登録される。スイッチ - 1 はバス権が与えられた Master - 3 は当該スイッチとは関連しないため、経路情報 FIFO401 には登録されない。しかし、Cycle - 2 で経路 B を介した Master - 1 の最終転送が転送されたため、FIFO の一番古い経路 B のエントリが削除され、切替選択信号 404 は経路 A を示し経路選択回路 400 の経路が変更される。スイッチ - 3 では、経路情報 FIFO401

50

1に情報が登録されたため、経路選択回路400は経路Aを選択するように動作し、スイッチ-3に入力される経路AのMaster-3の第一転送がスイッチ2に対して出力される。スイッチ-2では経路AからのMaster-1の最終転送をスレーブに転送中となる。

#### 【0055】

Cycle-4にて、調停回路300よりMaster-1に対してバス権が付与されると、スイッチ-1の経路情報 FIFO401には経路Bの情報、スイッチ-2の経路情報 FIFO401には経路Aの情報が登録される。スイッチ-2では経路Aを介したMaster-1の最終転送がCycle-3で転送されたため、FIFOの一番古い経路Aのエントリが削除される。経路情報 FIFO401のエントリが削除されるが、切替選択信号404は次のエントリも経路Aであるため経路選択回路400のスイッチは経路Aの選択を継続し、Master-2の第一転送をスレーブモジュール102に転送する。10

#### 【0056】

Cycle-5にて、調停回路300よりMaster-4に対してバス権が付与されると、スイッチ-3の経路情報 FIFO401には経路Bの情報、スイッチ-2の経路情報 FIFO401には経路Bの情報が登録される。スイッチ-1はバス権が与えられたMaster-4は当該スイッチとは関連しないため、経路情報 FIFO401には登録されない。しかし、Cycle-4で経路Aを介したMaster-2の最終転送が転送されたため、FIFOの一番古い経路Aのエントリが削除され、切替選択信号404は経路Bを示し、経路選択回路400の経路が変更される。Cycle-5でスイッチ-2において、経路Aを介したMaster-2の最終転送がスレーブモジュール102に対して転送される。20

#### 【0057】

Cycle-6では、経路情報 FIFO401の一番古いエントリが削除され、経路選択回路400の経路が経路Bに変更され、スイッチ-3を介した転送に切り替わることとなる。以下、同様にMaster-3の転送が完了すると、スイッチ-2はCycle-8で経路Aに切り替わりMaster-1の転送がスレーブモジュールに転送される。Cycle-9で新たに調停回路300よりMaster-3に対してバス権が付与されると、スイッチ-3の経路情報 FIFO401には経路Aの情報、スイッチ-2の経路情報 FIFO401には経路Bの情報が登録される。Cycle-9でMaster-1の最終転送が完了するとCycle-10よりMaster-4のバス転送、Cycle-12よりMaster-3のバス転送がスレーブモジュール102に転送されるよう動作する。30

#### 【0058】

以上の実施形態で示されるように、複数のバススイッチ回路305を介してバスマスタモジュールからスレーブモジュールのバスを構成するバスシステムにて、簡易な選択論理で調停回路のバス権付与順にバス転送を発行可能である。特にスイッチの経路選択回路400の入力数を絞ることにより、少ないビット数のFIFOでバス全体の経路選択を構成することが可能となり、小コストで所望のバス転送優先順位が制御可能なバスシステムの構築が可能となる。40

#### 【0059】

また、本実施形態では明示していないが、調停回路300は各バススイッチ回路305の経路情報 FIFO401の状態を参照し、バス権付与を与えるタイミングを制御することも可能である。具体的には、経路情報 FIFO401のFIFOエントリの空き具合を参照し、空きがない場合にはFIFOエントリの空きが生じるまでバス権付与を待たせることも可能である。

#### 【0060】

また、先に示した例は調停回路300からの調停結果であるバス権付与情報をバススイッチ回路305に伝達する構成を示している。本実施形態ではバススイッチ回路305は経路情報 FIFO401のエントリが無い場合は経路選択回路400を介して下流にバス

転送を発行しないよう制御する。したがって、バスマスタモジュール 101 はバス転送要求を発行後にバス転送信号 103 を介してバス転送を発行しても構わない構成となっている。対して、調停回路 300 は調停結果であるバス権付与情報をバスマスタモジュール 101 に伝達しても構わない。バス権付与情報をバスマスタモジュールに伝達する構成を採用することにより、バスマスタモジュール 101 からのバス転送信号 103 の発行をバス権付与情報受領後に制御することが可能となる。これにより、経路選択回路 400 は経路情報 FIFO 401 のエントリが無い場合の制御が不要となる。

#### 【0061】

##### [実施形態の変形例]

第 1、第 2 の実施形態は、バスマスタモジュールからバススレーブモジュールへの経路でアドレス情報とデータ情報を同一経路で伝達する構成を示しているが、アドレス情報とデータ情報を独立に転送する構成にも適用可能である。すなわち、アドレス情報バスとデータ情報バスが独立に構成される形式に適用可能である。本構成では、バスマスタモジュール 101 はバス転送要求信号 104 とともにバス転送方向情報を調停回路 100 (又は 300 ) に通知する。調停回路 100 (又は 300 ) は調停結果信号 106 とともに、当該転送のバス転送方向情報をバススイッチ回路 105 (又は 305 ) に伝達される。バススイッチ回路はアドレス情報を伝達するバススイッチとデータ情報を伝達するバススイッチが独立して構成される。データ情報を伝達するバススイッチは、調停結果信号 106 とともに伝達されるバス転送方向情報を参照し、書き込み転送である場合のみバススイッチの経路情報に変換することにより実現される。

10

#### 【0062】

第 1、第 2 の実施形態では調停回路 100 (又は 300 ) が発行する調停結果信号 106 を、バスシステムを構成するすべてのバススイッチ回路 105 (又は 305 ) に一斉に通知される構成例を示している。一方で、調停結果信号 106 は一部のバススイッチ回路 105 (又は 305 ) にのみ通知される構成であっても構わない。例えば図 5 の構成を例にとると、Master - 0 から 3 に対するバスアクセス権の調停結果信号 106 の通知はスイッチ - 0 から 3 に対してのみ通知しても構わない。

20

#### 【0063】

第 1、第 2 の実施形態では、バススイッチ回路 105 (又は、305) は入力バスが 2 つとする、スイッチ回路構成を例示しているが、入力バスは 3 つ以上の構成であっても構わない。その場合、バススイッチに対する切替選択信号 204 (又は、404) は 2 ビット以上の信号で表されることになる。

30

#### 【符号の説明】

#### 【0064】

100、300...調停回路、101...バスマスタモジュール、102...スレーブモジュール、103...バス転送信号、104...バス転送要求信号、105、305...バススイッチ回路、106...調停結果信号、200、400...経路選択回路、201...経路MUX制御部、202、402...経路エンコード回路、203、403...経路選択情報、204、404...切替選択信号、205、405...バス転送最終フラグ信号、206...バスマスタ経路ステータス情報、207、407...バスマスタ経路情報、401...経路情報 FIFO

40

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図5】

【図6】

10

20

30

40

【図7】

【図8】

|          | 調停結果     | 経路A   | スイッチ-1 | FIFO  | 経路B   | スイッチ-2 | FIFO    | 経路A   | スイッチ-3 | FIFO  |

|----------|----------|-------|--------|-------|-------|--------|---------|-------|--------|-------|

| Cycle-0  | -        | valid | empty  | -     | -     | empty  | valid   | empty | empty  | empty |

| Cycle-1  | Master-1 | valid | 1st    | B     | -     | -      | A       | valid | valid  | empty |

| Cycle-2  | Master-2 | valid | last   | B-A   | 1st   | -      | A-A     | valid | valid  | empty |

| Cycle-3  | Master-3 | 1st   | valid  | A     | last  | -      | A-A-B   | 1st   | valid  | A     |

| Cycle-4  | Master-1 | last  | valid  | A-B   | 1st   | valid  | A-B-A   | 1st   | valid  | A     |

| Cycle-5  | Master-4 | -     | 1st    | B     | last  | valid  | A-B-A-B | 1st   | valid  | A-B   |

| Cycle-6  | -        | -     | 1st    | B     | valid | 1st    | B-A-B   | last  | valid  | A-B   |

| Cycle-7  | -        | -     | 1st    | B     | valid | last   | B-A-B   | -     | 1st    | B     |

| Cycle-8  | -        | -     | last   | B     | 1st   | valid  | A-B     | valid | 1st    | B     |

| Cycle-9  | Master-3 | -     | -      | empty | last  | valid  | A-B-B   | valid | 1st    | B-A   |

| Cycle-10 | -        | -     | -      | empty | -     | 1st    | B-B     | valid | last   | B-A   |

| Cycle-11 | -        | -     | -      | empty | -     | last   | B-B     | 1st   | -      | A     |

| Cycle-12 | -        | -     | -      | empty | -     | 1st    | B       | last  | -      | A     |

| Cycle-13 | -        | -     | -      | empty | -     | last   | B       | -     | -      | empty |

| Cycle-14 | -        | -     | -      | empty | -     | -      | empty   | -     | -      | empty |

50

---

フロントページの続き

(56)参考文献      米国特許第09117022(US, B2)

特開2008-117068(JP, A)

(58)調査した分野 (Int.Cl., DB名)

G06F13/362

G06F13/14

G06F13/36