(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

17 January 2008 (17.01.2008)

PCT

(10) International Publication Number

WO 2008/008759 A2(51) International Patent Classification:

H03D 7/16 (2006.01)(74) Agent: BACHAND, Richard A.; 5775 Morehouse Drive,

San Diego, California 92121 (US).(21) International Application Number:

PCT/US2007/073129(81) Designated States (unless otherwise indicated, for every

kind of national protection available): AE, AG, AL, AM,

AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH,

CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG,

ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL,

IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK,

LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW,

MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL,

PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY,

TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA,

ZM, ZW.

(22) International Filing Date: 10 July 2007 (10.07.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/830,198 11 July 2006 (11.07.2006) US

11/531,314 13 September 2006 (13.09.2006) US(71) Applicant (for all designated States except US): QUAL-

COMM INCORPORATED [US/US]; Attn: International

IP Administration, 5775 Morehouse Drive, San Diego, California

92121 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): ZHUO, Wei

[CN/US]; 13122 Sunstone Pointe, San Diego, California

92121 (US). HADJICHRISTOS, Aristotele [IT/US];

104 Northcode Drive, Cary, North Carolina 27519 (US).

SAHOTA, Gurkanwal Kamal [US/US]; 3560 Curlew

Street, San Diego, California 92103 (US). PENG, Solti

[CN/US]; 8875 Costa Verde Boulevard, #416, San Diego,

California 92122 (US).(84) Designated States (unless otherwise indicated, for every

kind of regional protection available): ARIPO (BW, GH,

GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM,

ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI,

FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL,

PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM,

GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Declarations under Rule 4.17:

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

[Continued on next page]

(54) Title: SYSTEMS, METHODS, AND APPARATUS FOR FREQUENCY CONVERSION

(57) Abstract: A method according to one embodiment includes using a quadrature set of local oscillator signals having duty cycles of substantially less than fifty percent to perform a mixing operation on a radio-frequency current signal. Other embodiments include using a quadrature set of local oscillator signals having duty cycles of less than twenty-five percent.

WO 2008/008759 A2

**Published:**

- without international search report and to be republished upon receipt of that report

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

## SYSTEMS, METHODS, AND APPARATUS FOR FREQUENCY CONVERSION

### Claim of Priority under 35 U.S.C. §119

[0000] The present Application for Patent claims priority to Provisional Application No. 60/830,198 entitled “Using non-overlap clock in quadrature mixer to improve noise and gain” filed July 11, 2006, and assigned to the assignee hereof and hereby expressly incorporated by reference herein.

### FIELD OF THE INVENTION

[0001] This invention relates to wireless communications.

### BACKGROUND

[0002] Many techniques for transferring information from one location to another include one or more frequency conversion operations. In a transmitting application, for example, a signal carrying information may be upconverted into a radio-frequency (RF) signal for transmission over a medium such as a wireless channel or a conductive or optical cable. In a receiving application, an RF signal carrying information may be received from such a medium and downconverted to an intermediate frequency or to baseband for processing and/or demodulation.

[0003] Mixers are commonly used to perform frequency conversion operations. In a typical application, a mixer is arranged to multiply a signal at an initial frequency F0 by a local oscillator (LO) signal to obtain components at the sum and difference frequencies. For example, a quadrature mixing operation may be used to obtain two channels that are 90 degrees out of phase according to an expression such as the following:

$$\cos(\omega_{F0}t)\cos(\omega_{LO}t) = \frac{1}{2}(\cos[(\omega_{F0} + \omega_{LO})t] + \cos[(\omega_{F0} - \omega_{LO})t]),$$

$$\cos(\omega_{F0}t)\sin(\omega_{LO}t) = \frac{1}{2}(\sin[(\omega_{F0} + \omega_{LO})t] - \sin[(\omega_{F0} - \omega_{LO})t]).$$

The desired one of the two resulting frequency components in each channel may be selected by bandpass filtering the mixer output if necessary.

**[0004]** In a heterodyne circuit, the intermediate frequency (IF) is significantly different from both baseband and RF, such that the conversion between baseband and RF is typically performed in two or more stages. In a homodyne or “zero-IF” circuit, the frequency of the LO signal is substantially equal to the RF, such that the signal is converted between baseband and RF in one stage. In other techniques that are termed “low-IF” or “near-zero-IF”, the IF is close to baseband (e.g., a few hundred kHz or less).

## SUMMARY

**[0005]** An apparatus according to one embodiment includes a frequency converter that has a signal generator configured to generate a first complementary pair of local oscillator (LO) signals and a second complementary pair of LO signals such that a phase difference between a signal of the first complementary pair and a signal of the second complementary pair is substantially equal to ninety degrees. The frequency converter also has a first mixer configured and arranged to mix a radio-frequency (RF) current signal with the first complementary pair of LO signals, and a second mixer configured and arranged to mix the RF current signal with the second complementary pair of LO signals. In this apparatus, the signal generator is configured to generate each signal of the first and second complementary pairs to have a duty cycle of substantially less than fifty percent.

**[0006]** A method of frequency conversion according to an embodiment includes generating a first complementary pair of local oscillator (LO) signals and a second complementary pair of LO signals such that a phase difference between a signal of the first complementary pair and a signal of the second complementary pair is substantially equal to ninety degrees. The method also includes mixing, in a first channel, a radio-frequency (RF) current signal with the first complementary pair of LO signals, and mixing, in a second channel, the RF current signal with the second complementary pair

of LO signals. In this method, each signal of the first and second complementary pairs has a duty cycle of substantially less than fifty percent.

**[0007]** An apparatus according to another embodiment includes a frequency converter having means for generating a first complementary pair of local oscillator (LO) signals and a second complementary pair of LO signals such that a phase difference between a signal of the first complementary pair and a signal of the second complementary pair is substantially equal to ninety degrees. The frequency converter also includes means for mixing, in a first channel, a radio-frequency (RF) current signal with the first complementary pair of LO signals, and means for mixing, in a second channel, the RF current signal with the second complementary pair of LO signals. In this apparatus, the means for generating is configured to generate each signal of the first and second complementary pairs to have a duty cycle of substantially less than fifty percent.

## BRIEF DESCRIPTION OF THE DRAWINGS

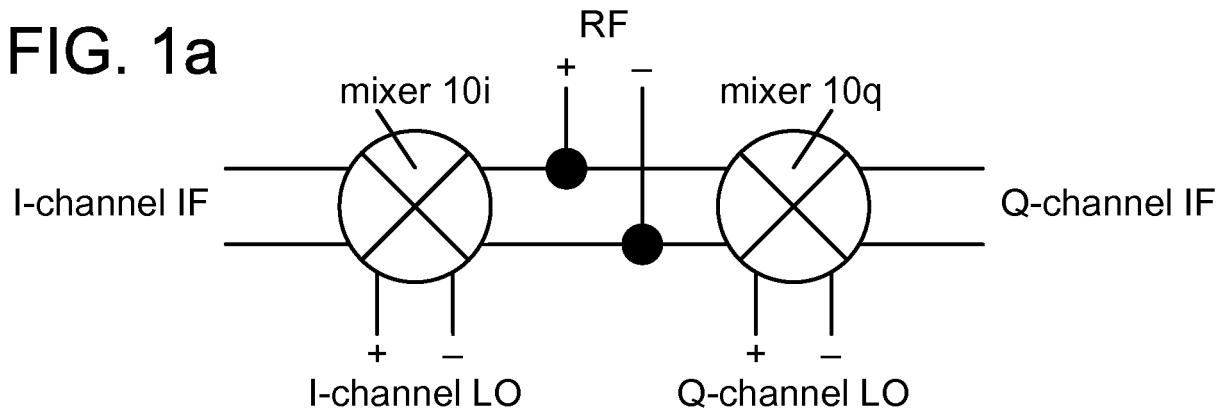

**[0008]** FIGURE 1a shows a block diagram of a frequency converter including two mixers.

**[0009]** FIGURE 1b shows a block diagram of a frequency converter driving transimpedance amplifiers.

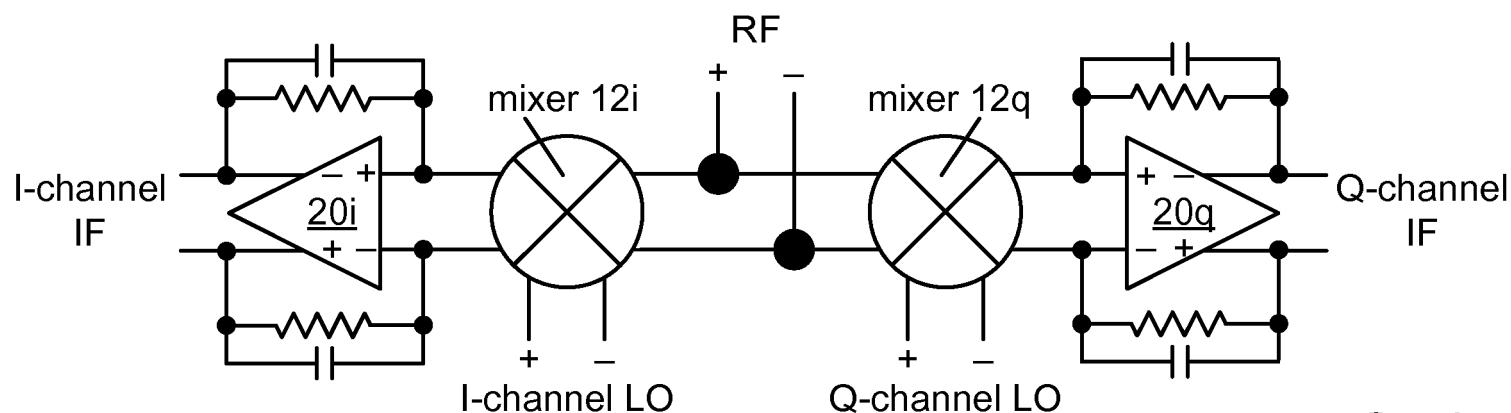

**[00010]** FIGURE 2a shows a schematic diagram of an implementation of an active mixer.

**[00011]** FIGURE 2b shows a schematic diagram of another implementation of an active mixer.

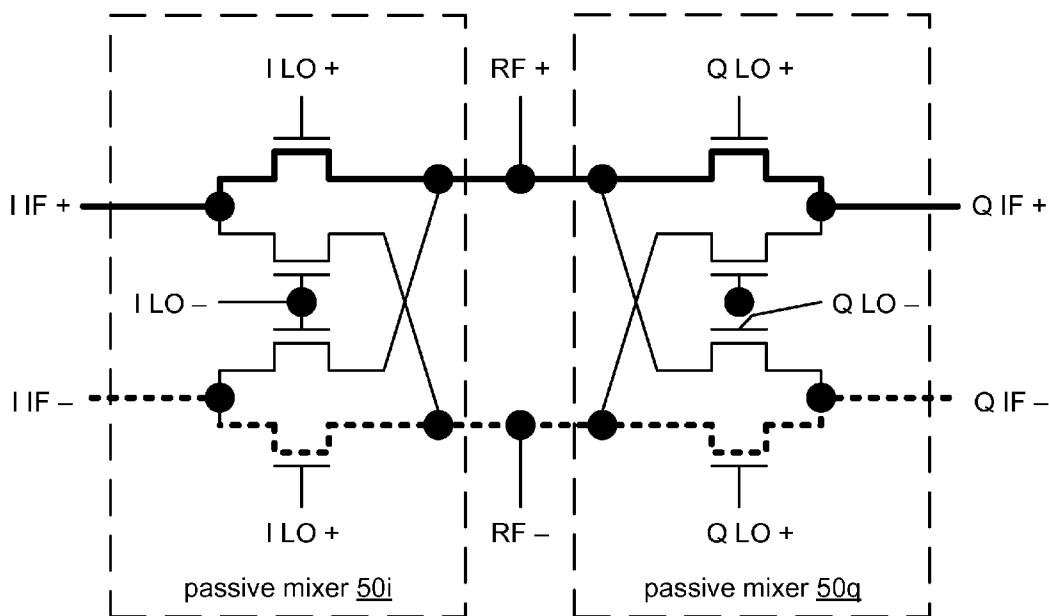

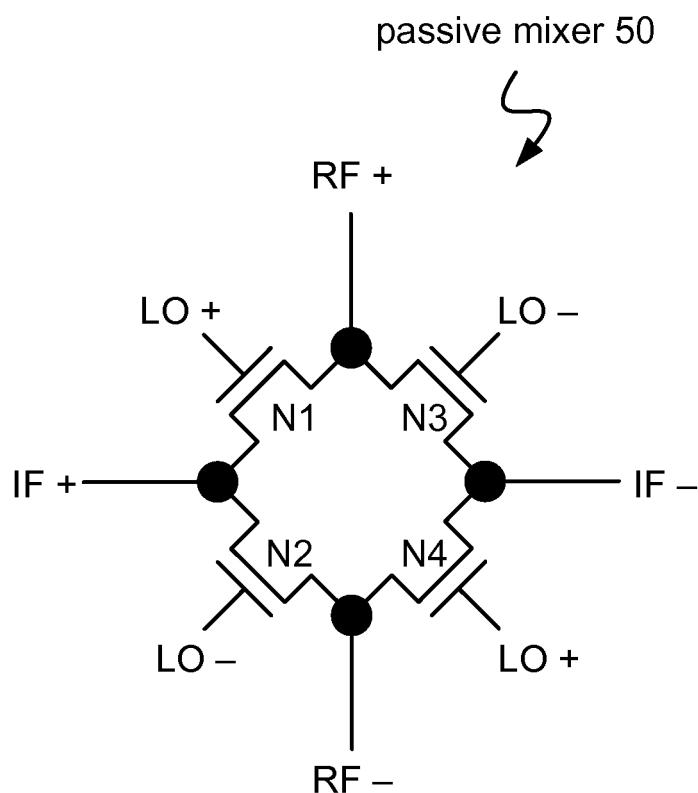

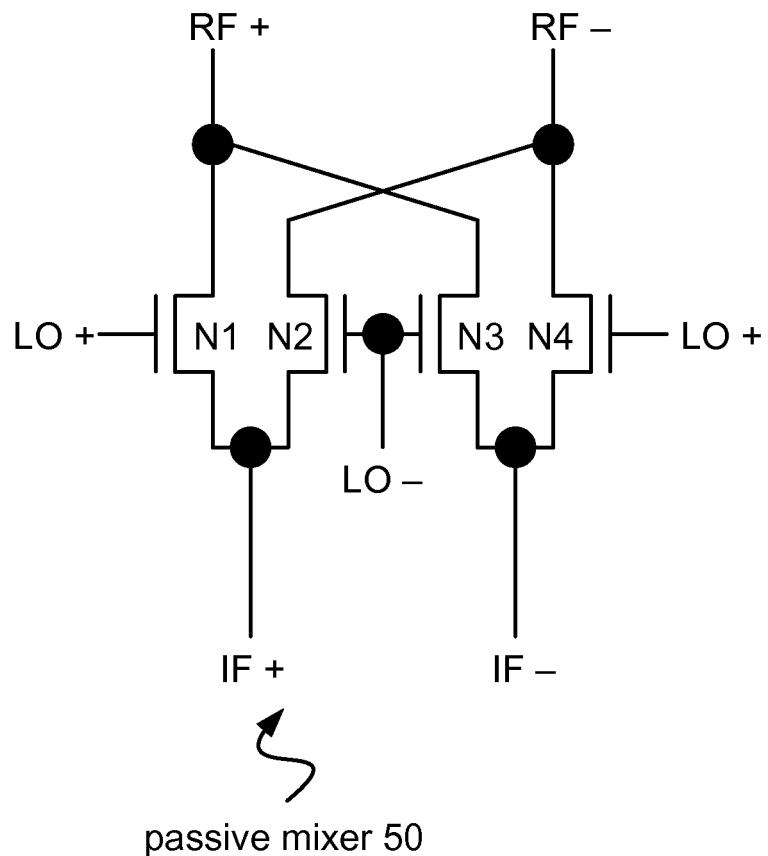

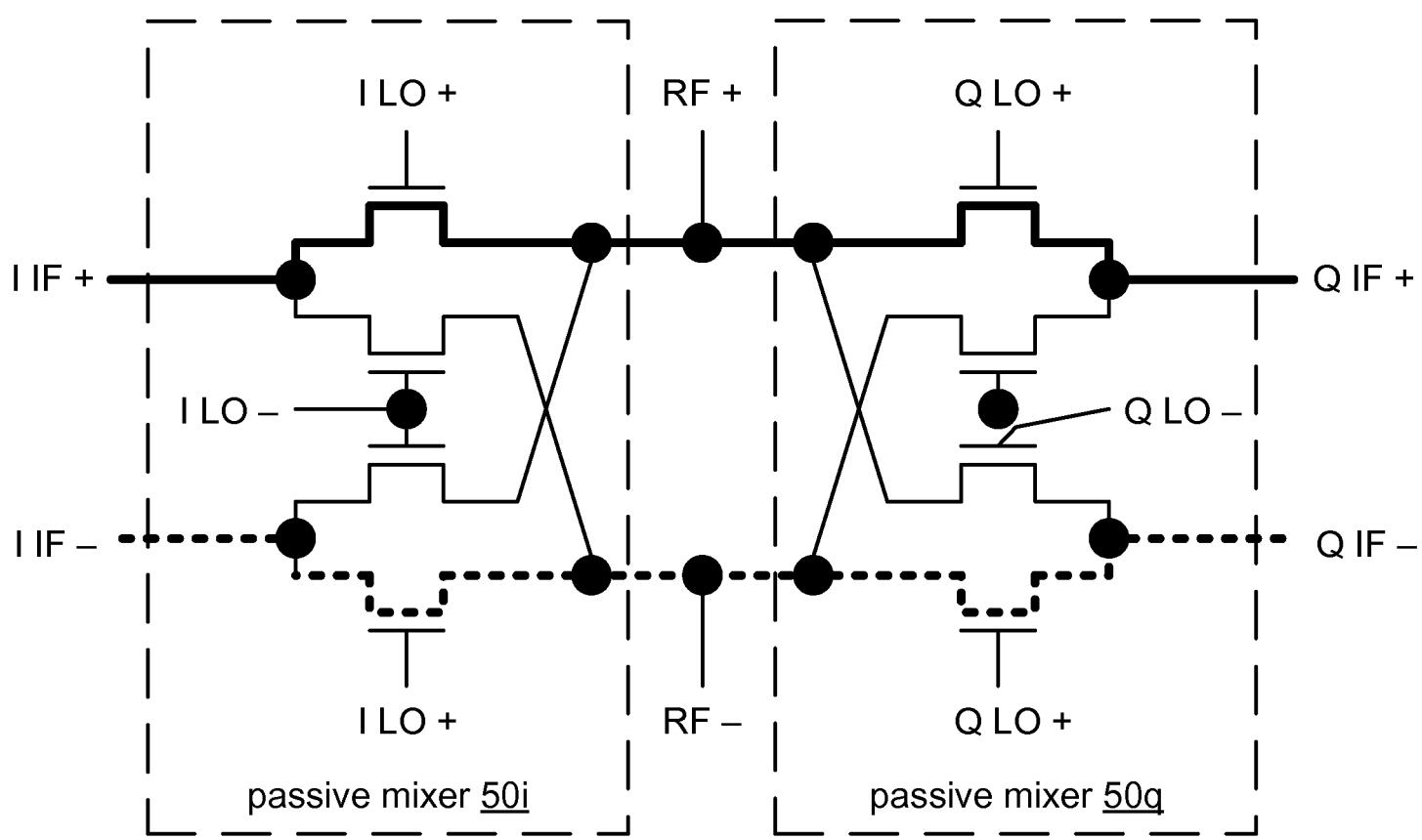

**[00012]** FIGURE 3a shows a schematic diagram of a passive mixer.

**[00013]** FIGURE 3b shows another schematic diagram of the passive mixer illustrated in FIGURE 3a.

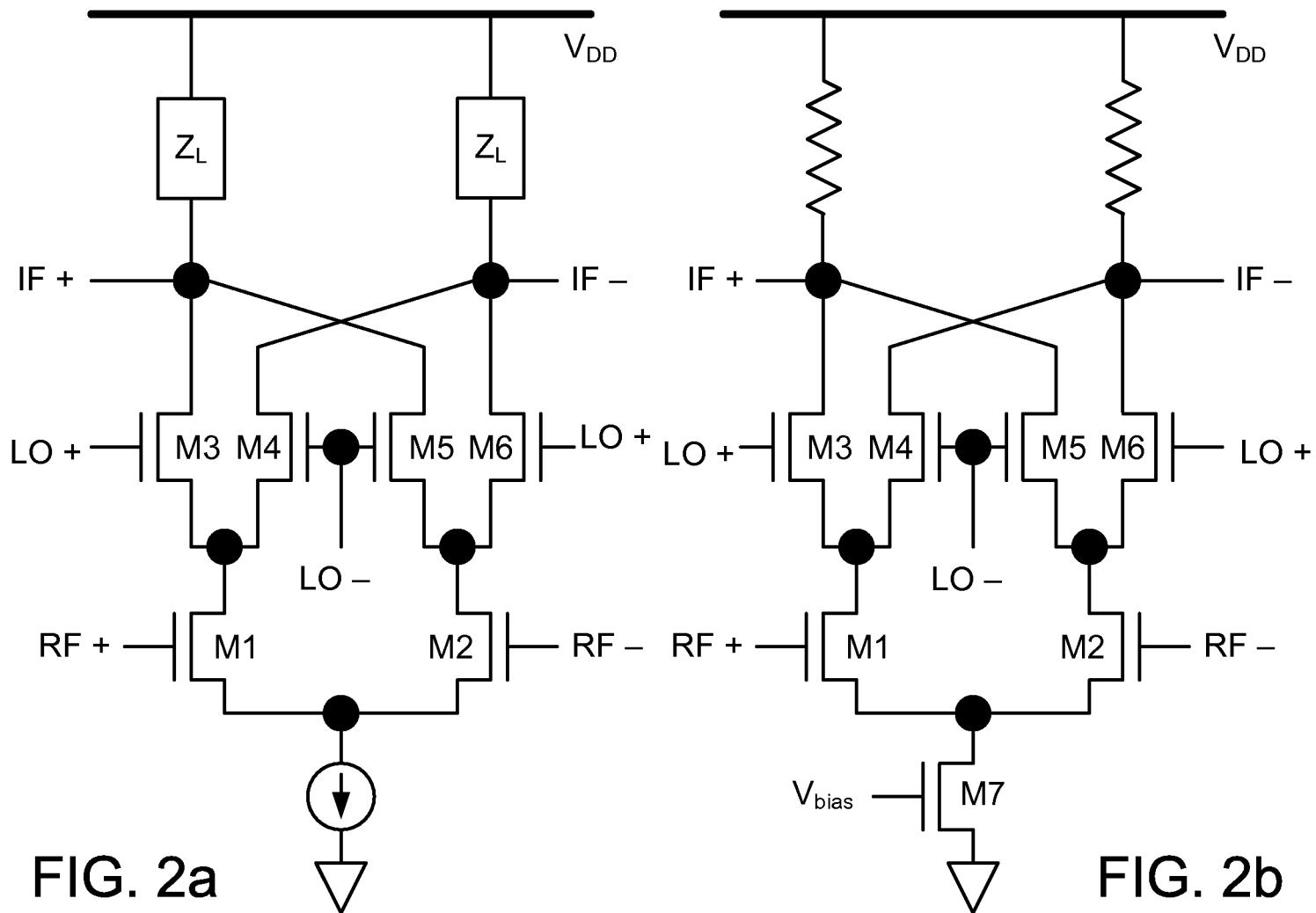

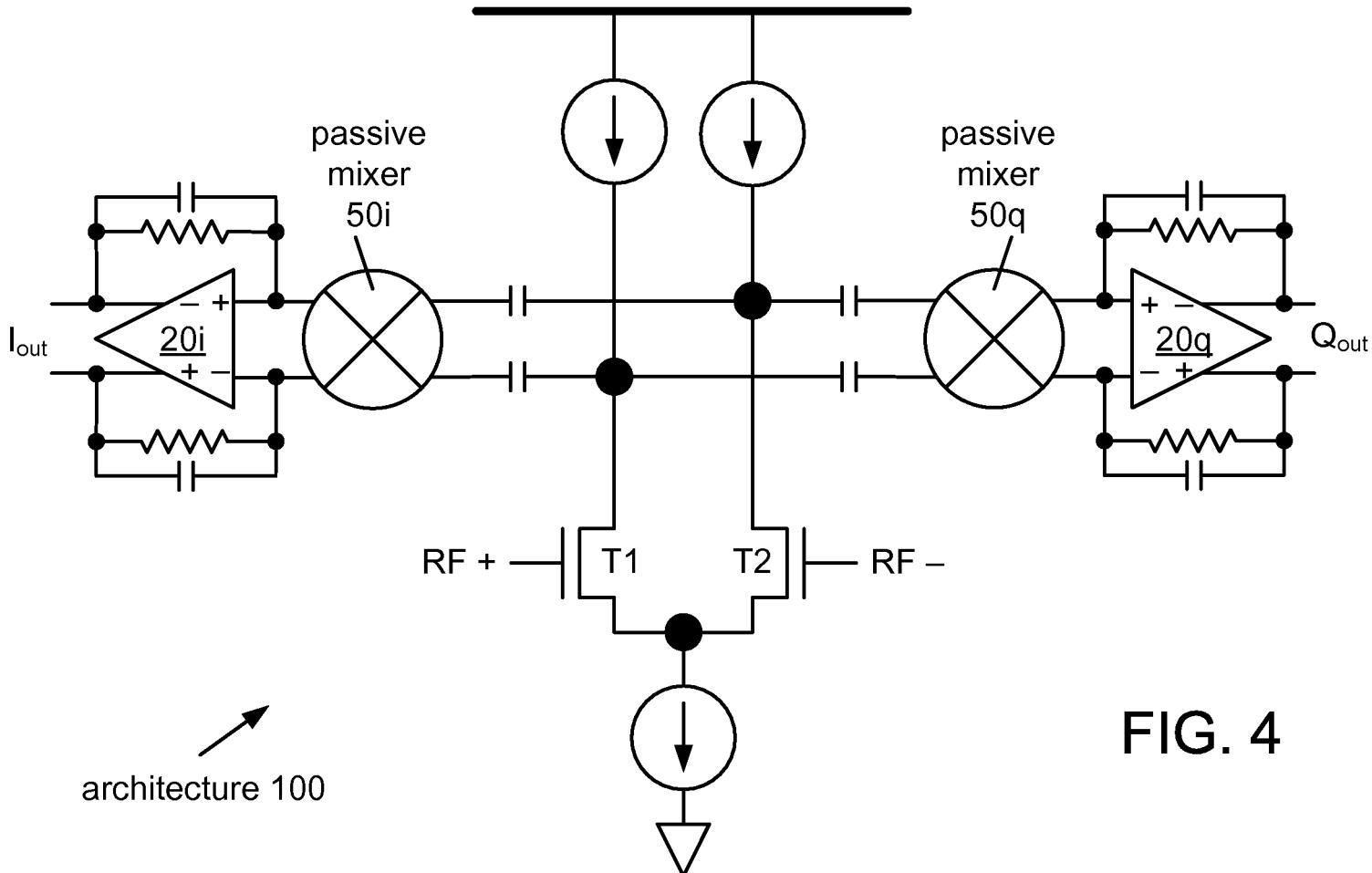

**[00014]** FIGURE 4 shows a block diagram of a frequency converter 100 based on a passive current-commutating mixer architecture.

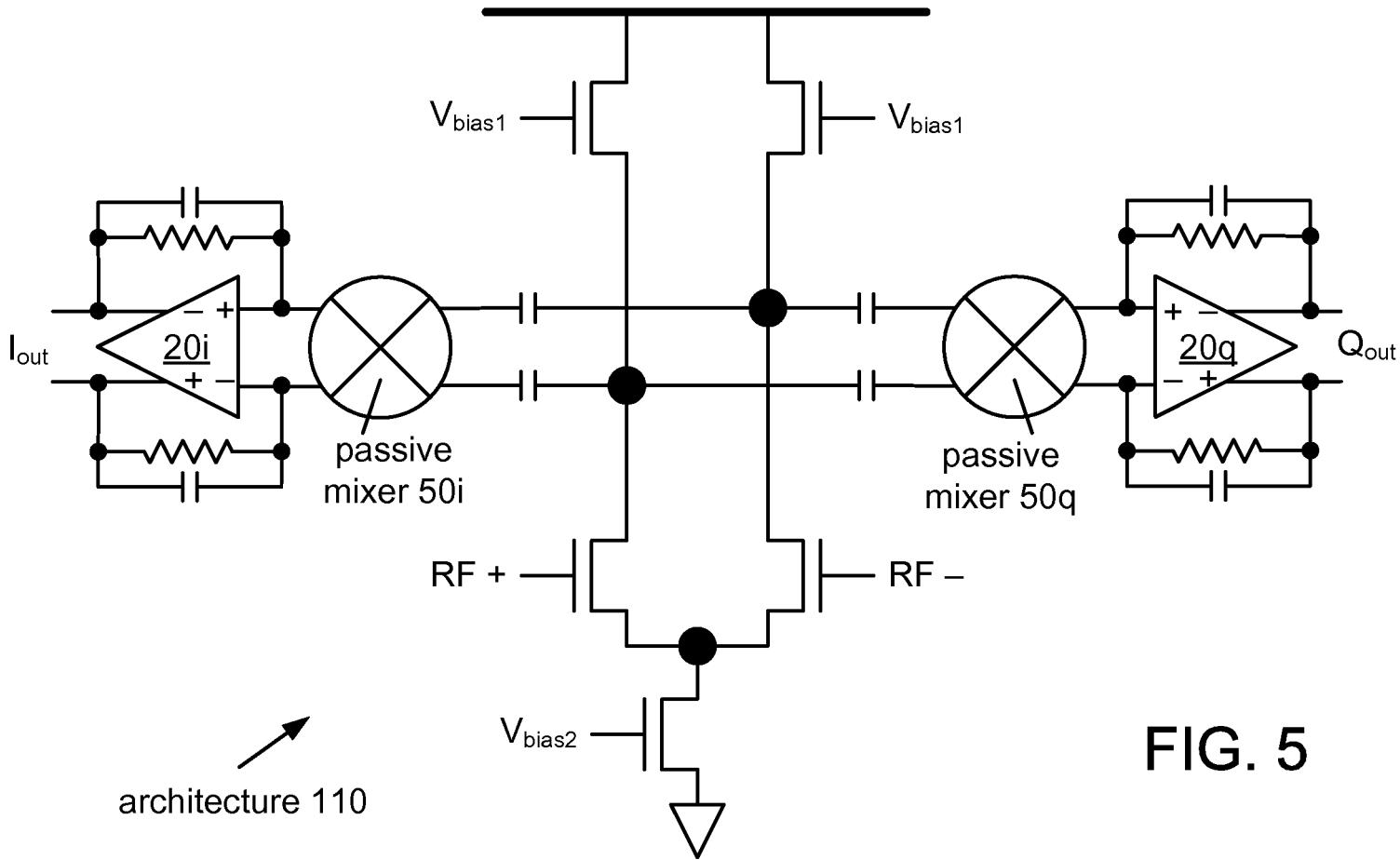

[00015] FIGURE 5 shows a block diagram of an example 110 of frequency converter 100.

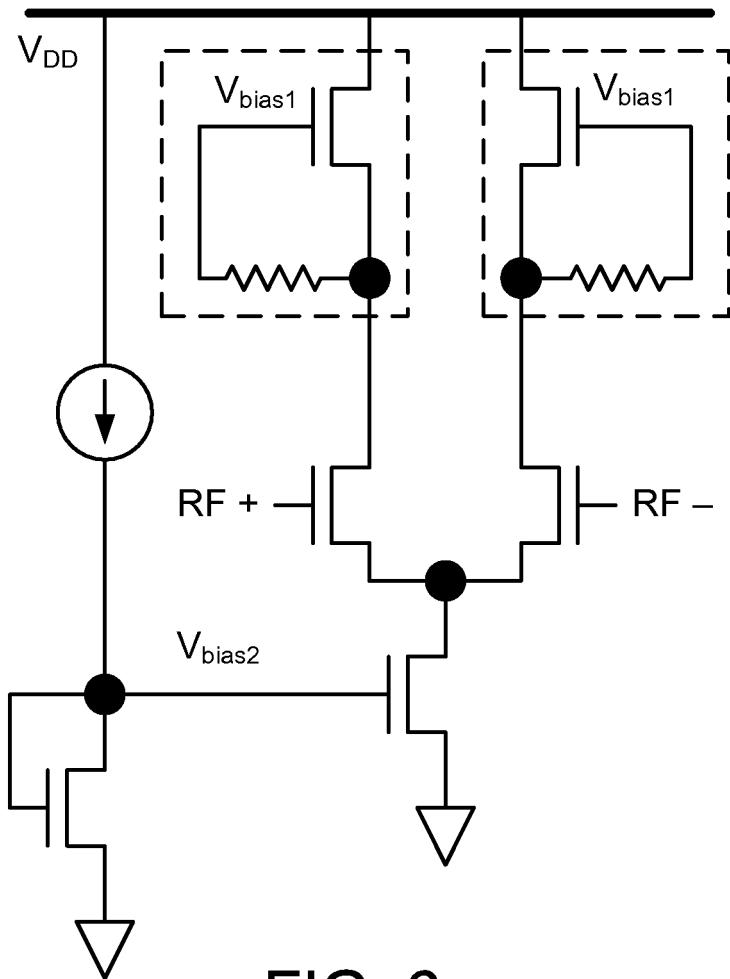

[00016] FIGURE 6a shows a schematic diagram of an example of a a biasing arrangement.

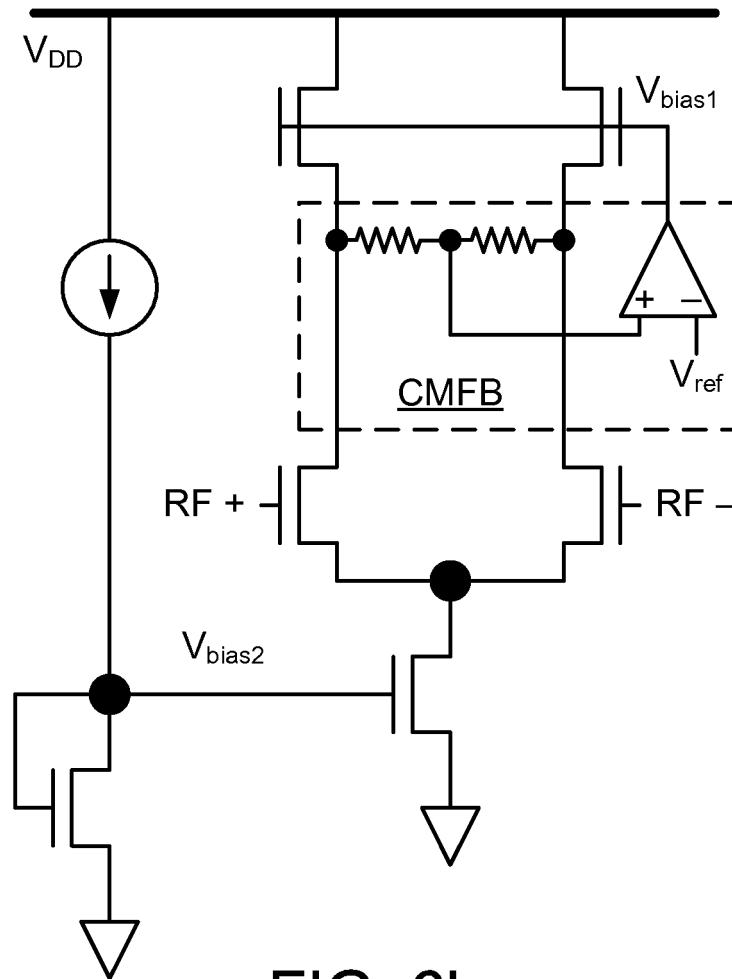

[00017] FIGURE 6b shows a schematic diagram of another example of a biasing arrangement.

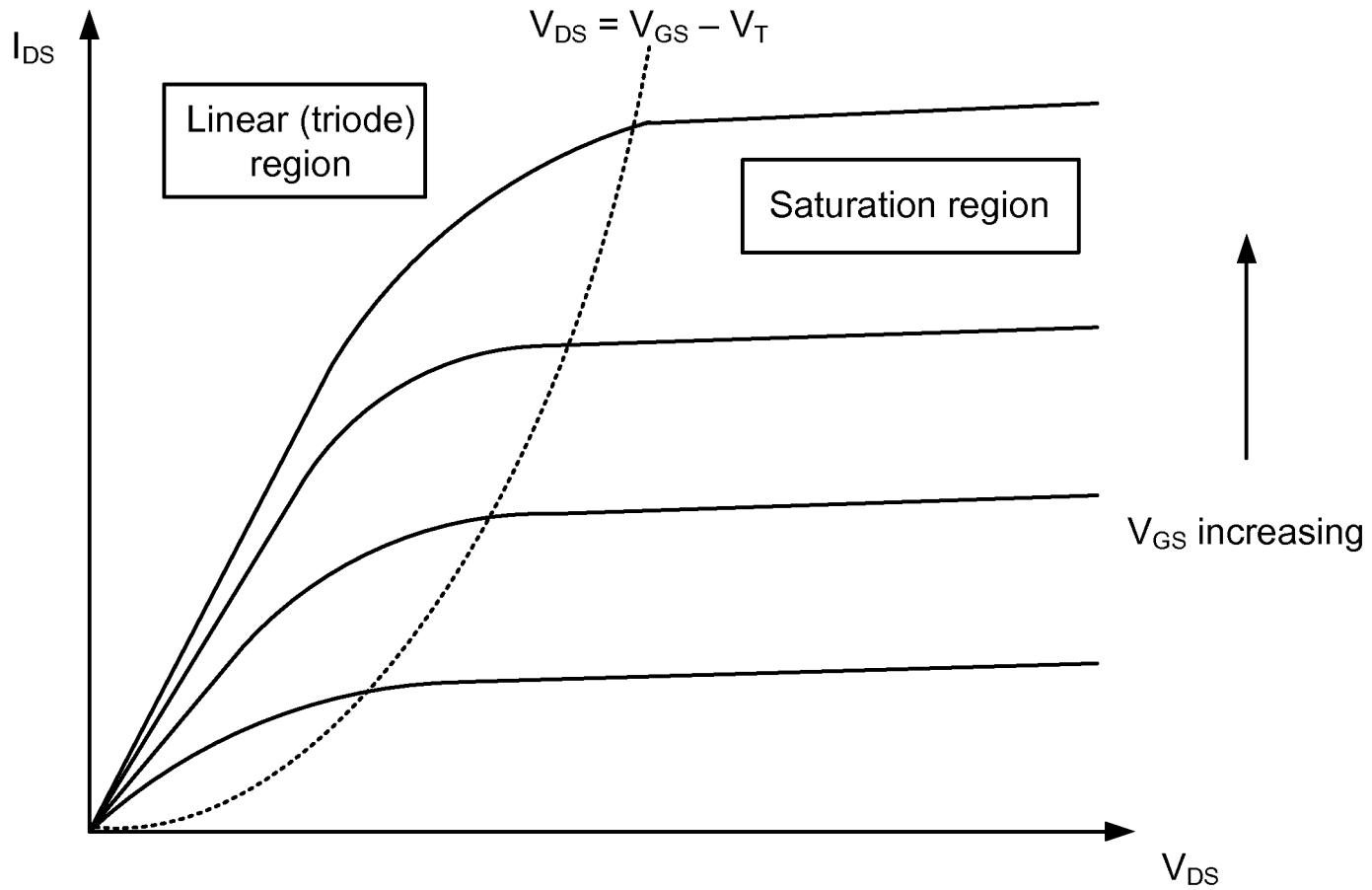

[00018] FIGURE 7 shows an example of a MOSFET characteristic curve.

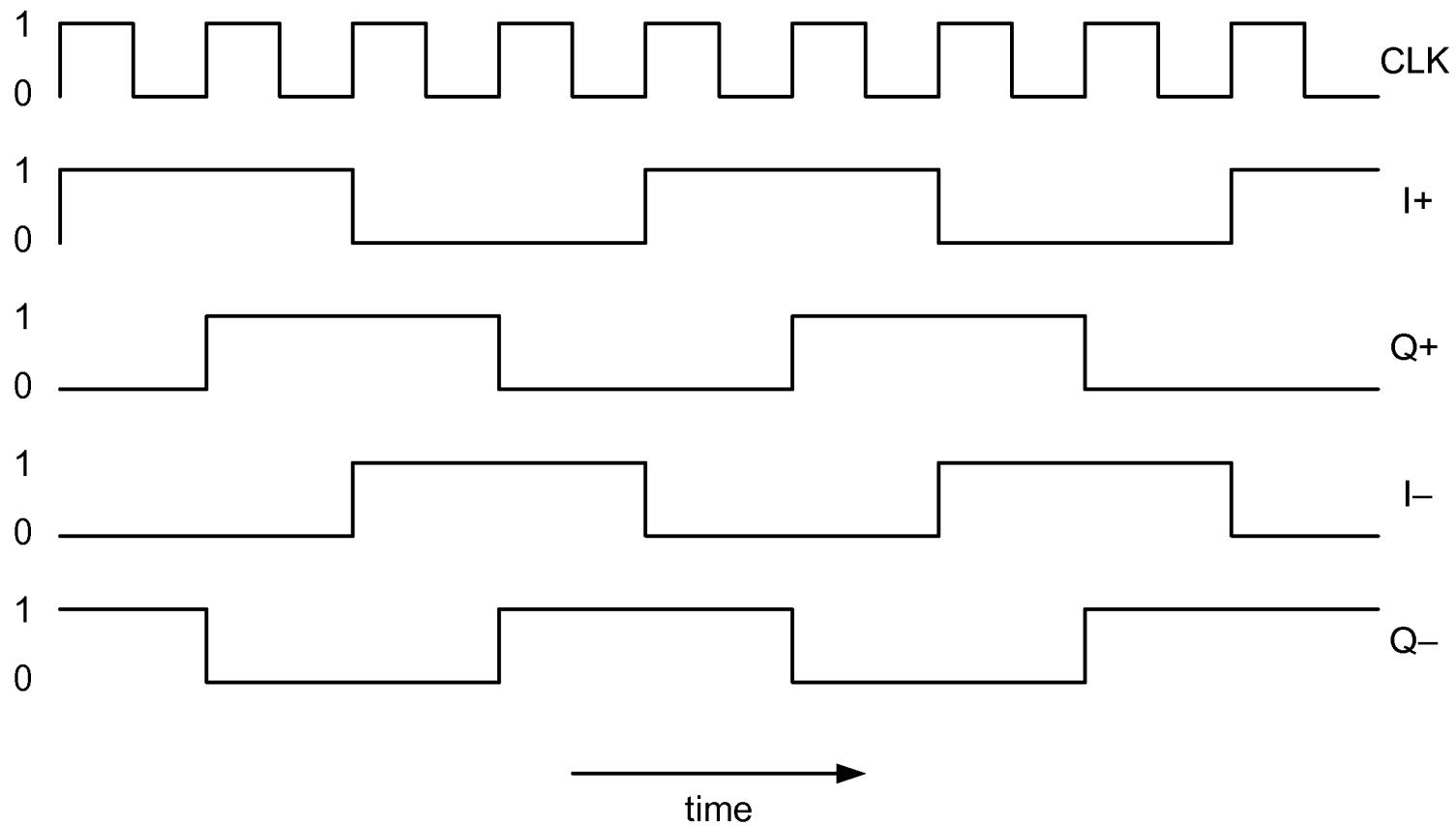

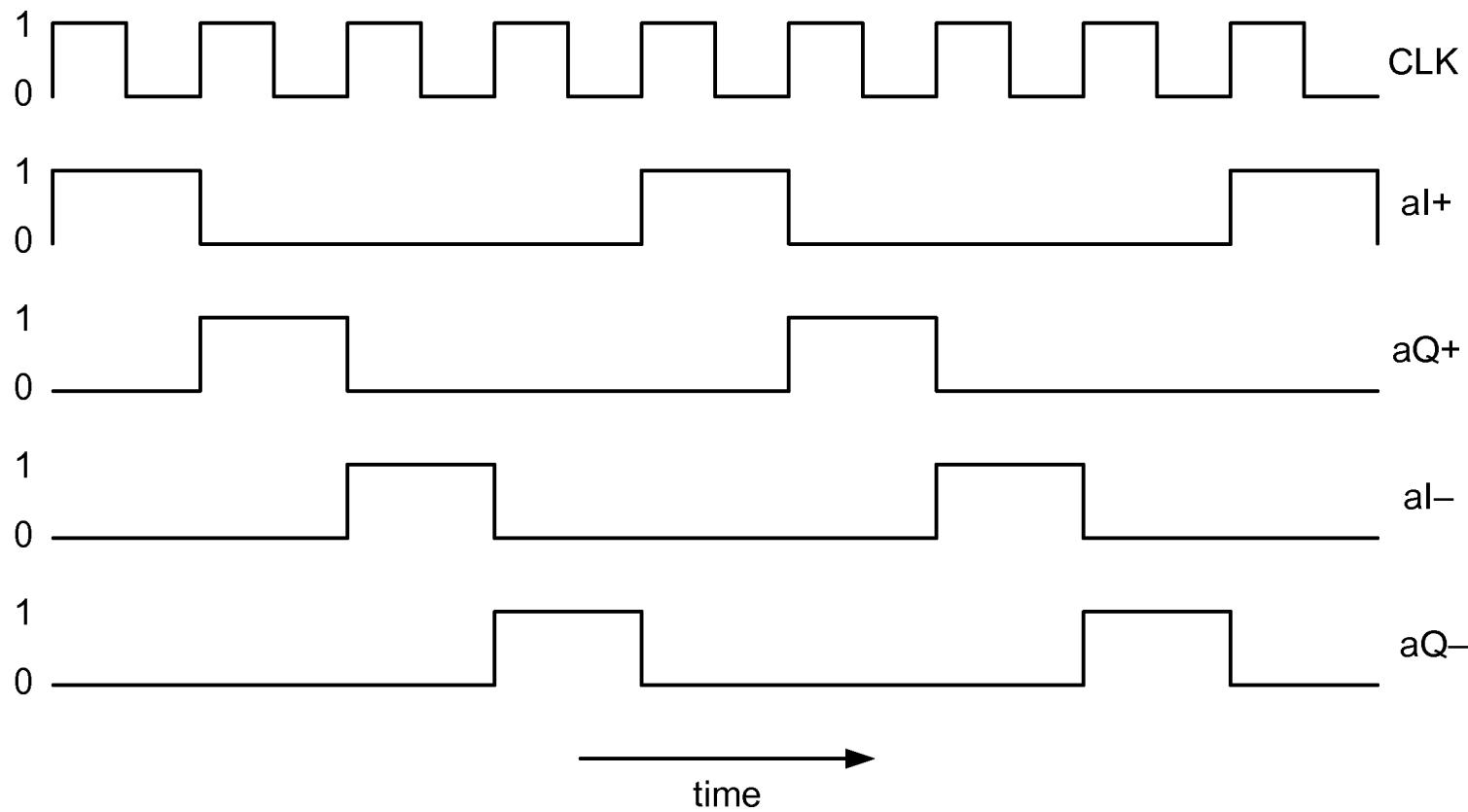

[00019] FIGURE 8 shows a diagram of a quadrature set of local oscillator signals having duty cycles of 50%.

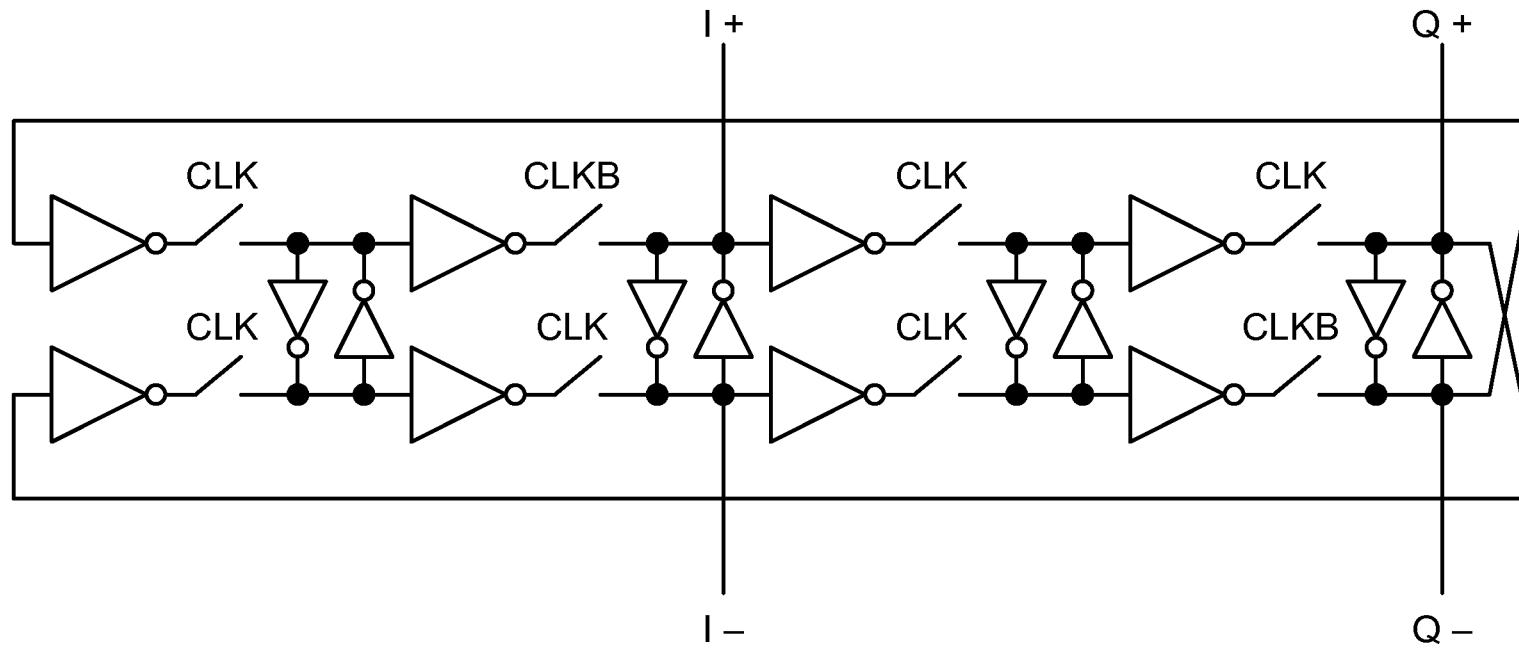

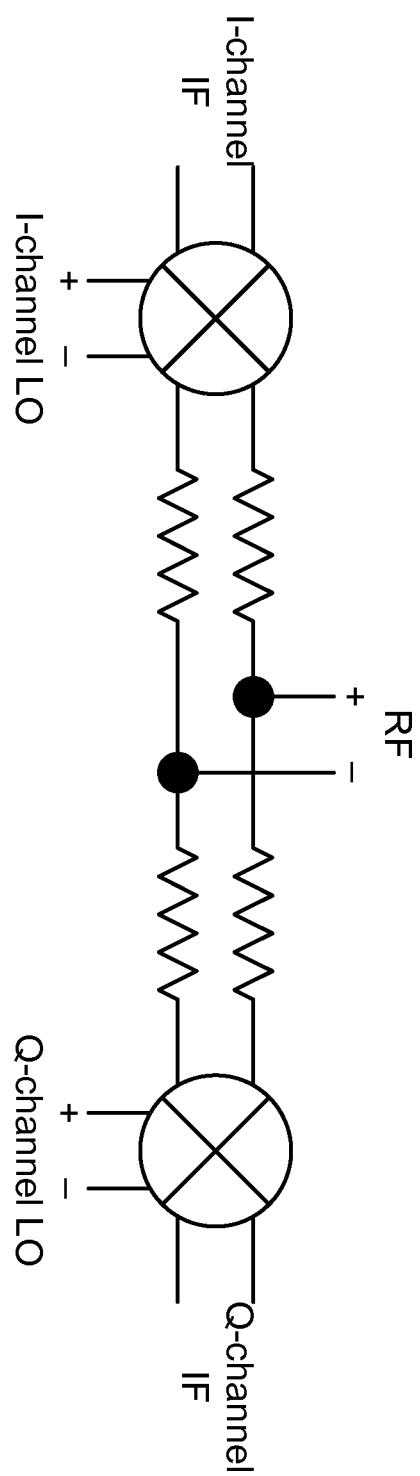

[00020] FIGURE 9 shows a block diagram of a divide-by-4 counter.

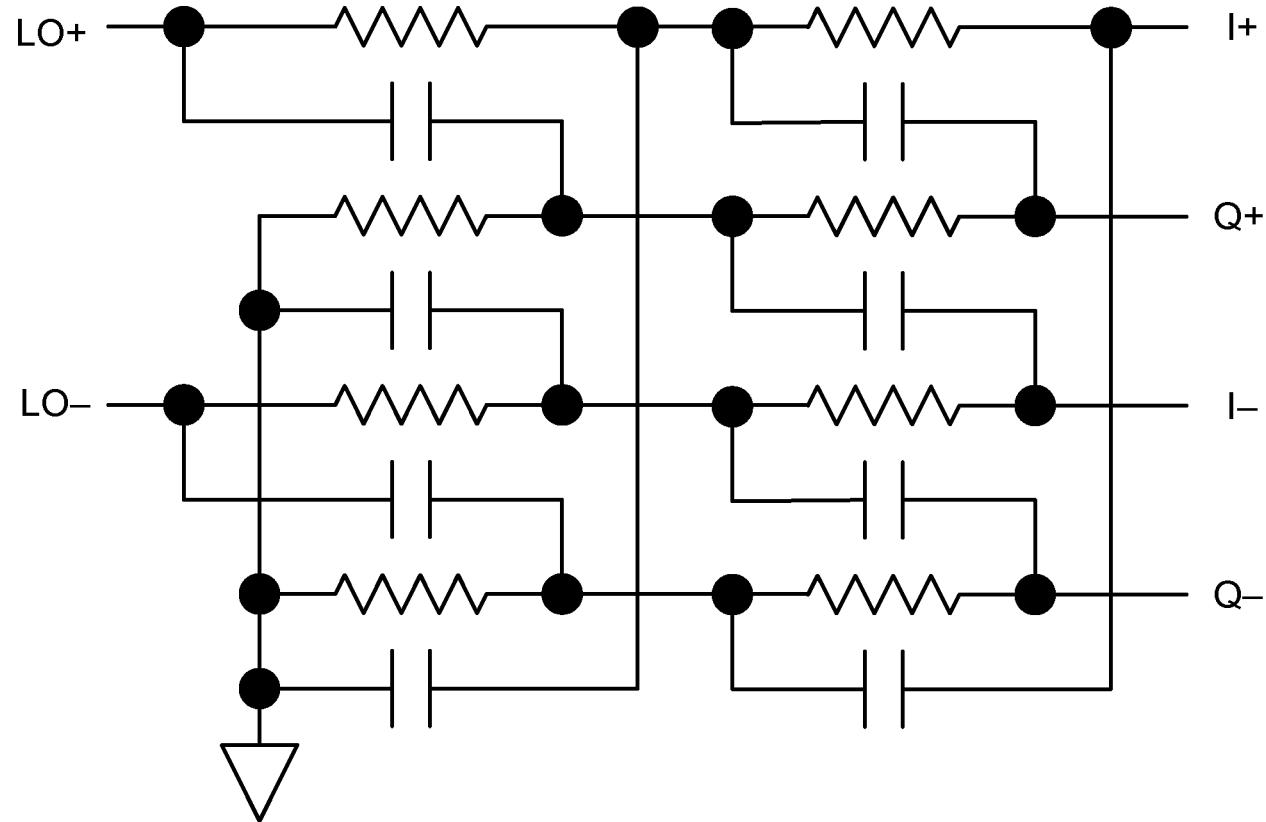

[00021] FIGURE 10 shows a schematic diagram of a polyphase filter.

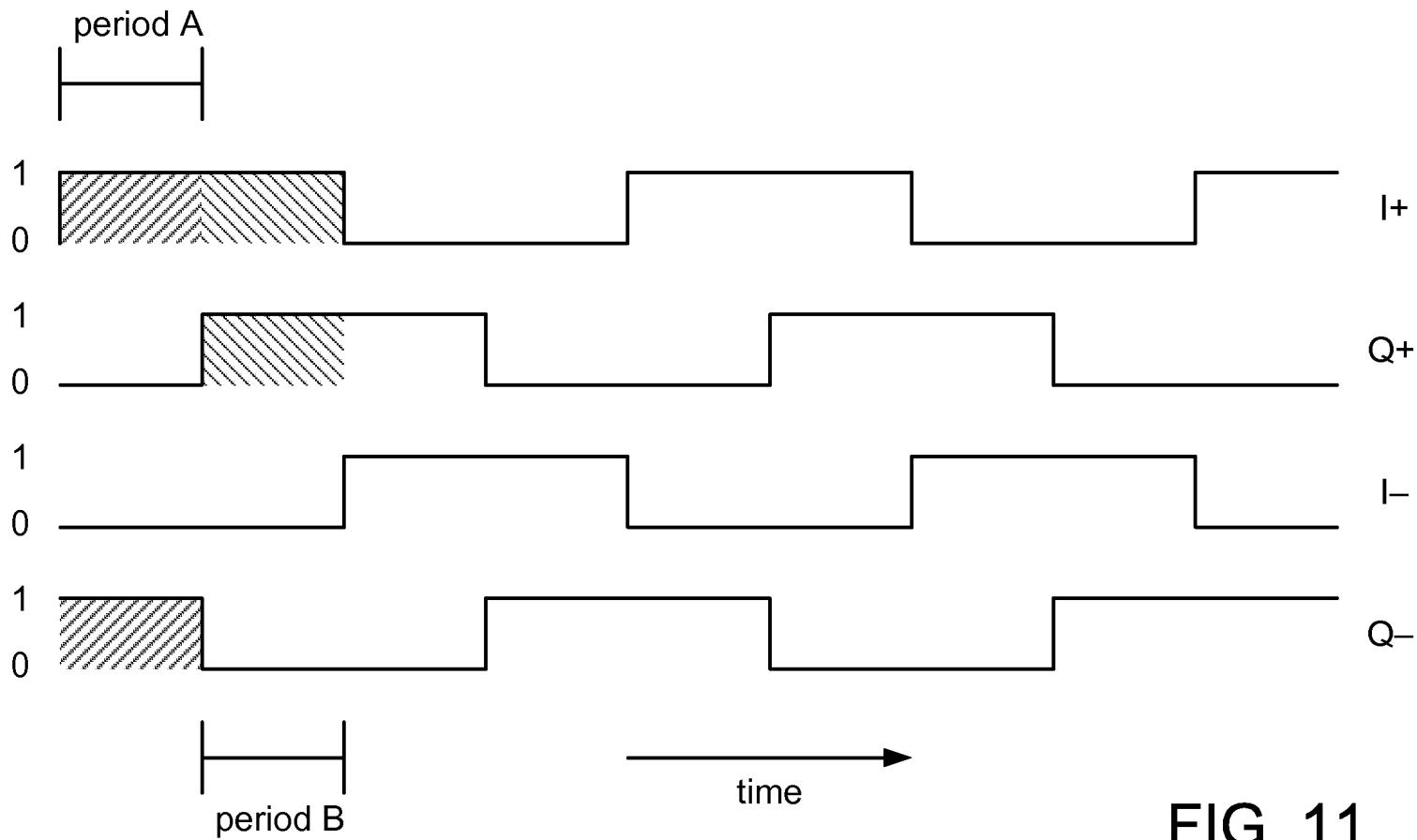

[00022] FIGURE 11 shows an example of overlap between on-cycles in the set of local oscillator signals of FIGURE 8.

[00023] FIGURE 12 shows an example of a cross-channel circuit path resulting from the overlap shown in period A of FIGURE 11.

[00024] FIGURE 13 shows an example of a cross-channel circuit path resulting from the overlap shown in period B of FIGURE 11.

[00025] FIGURE 14 shows an example of resistive isolation between I and Q mixers.

[00026] FIGURE 15 shows an example of a set of local oscillator signals according to an embodiment.

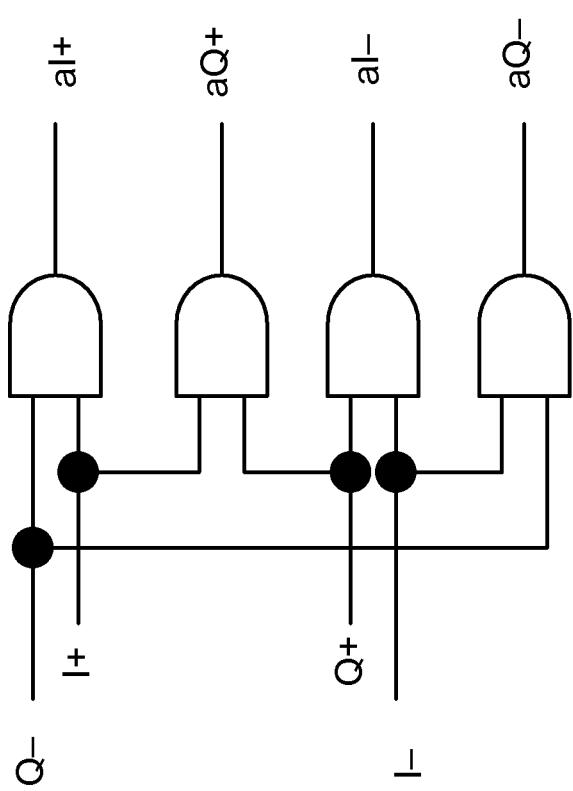

[00027] FIGURE 16 shows a block diagram of a logic circuit that may be used to convert the set of LO signals shown in FIGURE 8 into the set of LO signals shown in FIGURE 15.

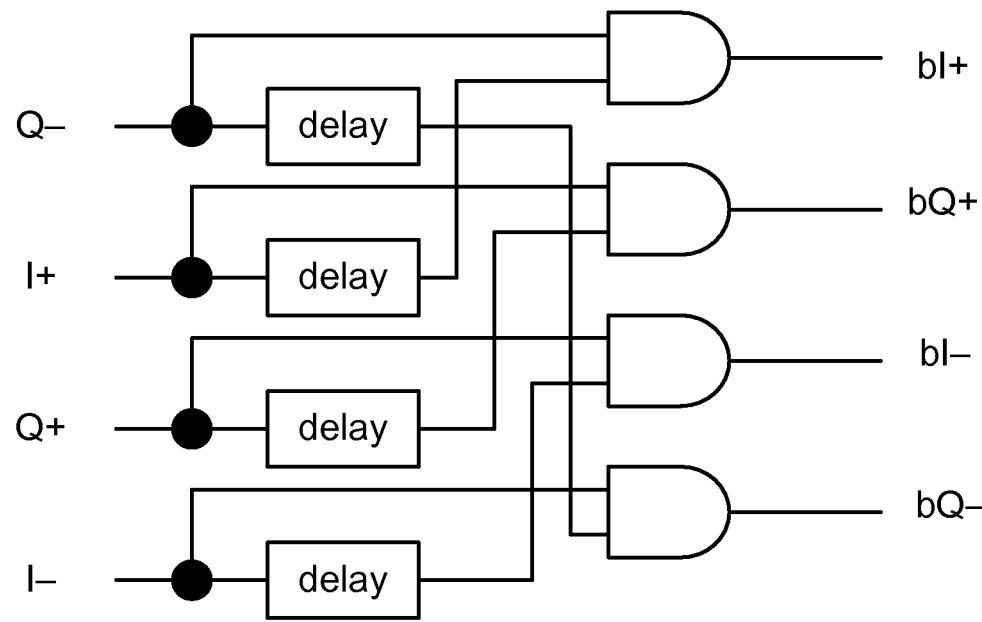

[00028] FIGURE 17 shows a block diagram of a logic circuit that may be used to convert the set of LO signals shown in FIGURE 8 into a set of LO signals having duty cycles of less than 25%.

## DETAILED DESCRIPTION

[00029] It is generally desirable to perform frequency conversion such that the conversion gain is maximized and/or the level of noise in the converted signal is minimized.

[00030] The term “node” is used herein to include its ordinary meaning of “a region of a circuit where there is no change in potential.” The term “terminal” is used herein to include its ordinary meaning of a “terminal node” of a circuit, device, or element.

[00031] Although for convenience the following description refers principally to applications and devices configured for signal reception, the structures and methods disclosed may also be applied to applications and devices configured for signal transmission, and such application is expressly contemplated and hereby disclosed.

[00032] Although the convention of labeling the opposite ends of a mixer as “RF” and “IF” is followed herein, use of the frequency converters and other structures disclosed herein for direct conversion or “zero-IF” applications (i.e., direct conversion between RF and baseband) is expressly contemplated and hereby disclosed. Therefore, it should be understood that the label “IF” as used herein simply indicates a signal at a frequency that is a difference between the RF and LO frequencies, which may be substantially equal to zero (i.e., a baseband signal).

[00033] FIGURE 1a shows a block diagram of a frequency converter based on a quadrature mixer architecture that includes two mixers 10i,q, each coupled to a differential RF input and outputting a respective one of a quadrature pair of IF signals. Mixers may be implemented in various ways. For example, some implementations use transmission line structures, passive components (resistors, capacitors, and/or inductors), and/or diodes. Most mixers, however, are implemented with active devices such as bipolar junction transistors (BJTs) or metal-oxide-semiconductor field-effect transistors

(MOSFETs), which may be fabricated to have desirable qualities such as low cost, small feature size, and good reproducibility. A MOSFET includes a gate configured to control current flow across a channel region, which is proximate to and insulated from the gate and has two ends (called “drain” and “source”), one at either side of the gate.

**[00034]** At the present time, mixers are typically implemented as switching mixers. A switching mixer is configured to multiply the RF signal by a sequence that alternates, according to a local oscillator frequency and phase, between two values having substantially equal amplitude and opposite magnitude (e.g., +1 and -1). Such mixers are implemented using devices such as BJTs or MOSFETs that are arranged to switch the two sides of the RF signal between the mixer output terminals.

**[00035]** A switching mixer architecture may be configured to switch an RF voltage (a “voltage-commutating” architecture) or an RF current (a “current-commutating” architecture). FIGURE 1b shows a block diagram of a frequency converter based on a current-commutating quadrature mixer architecture. In this example, the outputs of the switching mixers 12i,q drive respective transimpedance amplifiers 20i,q, implemented here as differential operational amplifiers with feedback, which convert the current signals into voltage signals.

**[00036]** A switching mixer may be implemented according to an active configuration or a passive configuration. FIGURE 2a shows a schematic diagram of one example of a double-balanced active current-commutating mixer circuit, also known as a Gilbert cell. This circuit includes a differential transconductance stage (M1, M2) and a quadrature mixer core (M3–M6). The mixer core includes two differential pairs (M3, M4 and M5, M6) and operates as a fully balanced, phase-reversing current switch. The gates of the mixer core switches are arranged to be driven by a pair of local oscillator (LO) signals LO+, LO– that are complementary (that is to say, 180 degrees out of phase). It is typically desirable for each LO signal to have a duty cycle that is substantially close to 50% (for example, to avoid even-order harmonics).

**[00037]** As shown in FIGURE 2b, the current source that provides the bias current to be switched (or “steered”) may be implemented as an active device M7. Alternatively, the current source may be implemented as an inductor or LC circuit (e.g., a parallel LC tank resonating at the RF frequency). In another example, the sources of devices M1,

M2 are connected directly to the V<sub>SS</sub> rail rather than through a current source. It is also possible for two mixer cores (e.g., one in the I channel and one in the Q channel) to share a common transconductance stage. The matched loads Z<sub>L</sub> may be implemented as resistors as shown in FIGURE 2b. Alternatively, the matched loads may be implemented as or including other passive components, such as inductors, or as active loads.

**[00038]** One potential disadvantage of active mixers is 1/f noise, commonly called “flicker noise.” The action of switching the RF signal from one switch of a differential pair of a switching mixer to the other does not occur instantaneously, and active mixers generate flicker noise when both switches in a differential pair are on (i.e., the channels of both devices are conducting). This period is called the “crossover point,” and it may occur especially at high frequencies when the waveform of the local oscillator becomes rounded rather than square. This flicker noise is visible at the mixer output and is generally proportional to the level of the DC bias current in the switching devices.

**[00039]** Flicker noise has a power spectral density that is inversely proportional to frequency. In a heterodyne architecture, the mixer output frequency is typically far above the range of frequencies in which flicker noise is significant. Because flicker noise dominates at low frequencies, however, it may become a significant problem with homodyne (“zero-IF” or “direct conversion”) and low-IF architectures. Flicker noise of the mixer switches is generally the dominant contributor to front-end flicker noise.

**[00040]** Flicker noise generation in the mixer may be greatly reduced by using a passive mixer rather than an active one. FIGURE 3a shows a schematic diagram of a passive mixer that includes four MOSFET switches N1–N4. FIGURE 3b shows another diagram of the same circuit that shows its ring structure. Because the channels of the switches of a passive mixer carry substantially no DC current, flicker noise generation by the switches may be largely eliminated, and this feature is a principal advantage of passive mixers in applications that are sensitive to 1/f noise.

**[00041]** The size of the switches in a switching mixer may be optimized according to a desired tradeoff between linearity and matching on one hand, and noise and driving requirements on the other hand. A larger switch will tend to have a lower on-resistance, which improves linearity and matching, but a bigger parasitic capacitance, which

increases noise and driving requirements. In one example, the switches N1–N4 of an implementation of a passive mixer are configured to have a W/L ratio in the range of about 300–400 (three hundred to four hundred).

**[00042]** As noted above, passive mixers operate with substantially no bias current and thus typically consume less power and generate much less flicker noise than active mixers. However, passive mixers also have a conversion gain of less than unity (i.e., a conversion loss) such that the output of a passive mixer usually must be amplified. Typically a passive mixer is followed by an amplification stage that may include an operational amplifier (or “opamp”). Unfortunately, opamps contribute both flicker and white noise, with flicker noise dominating at low frequencies (e.g., less than a few MHz for CMOS designs). It is desirable to minimize the level of the noise contribution by the amplification stage.

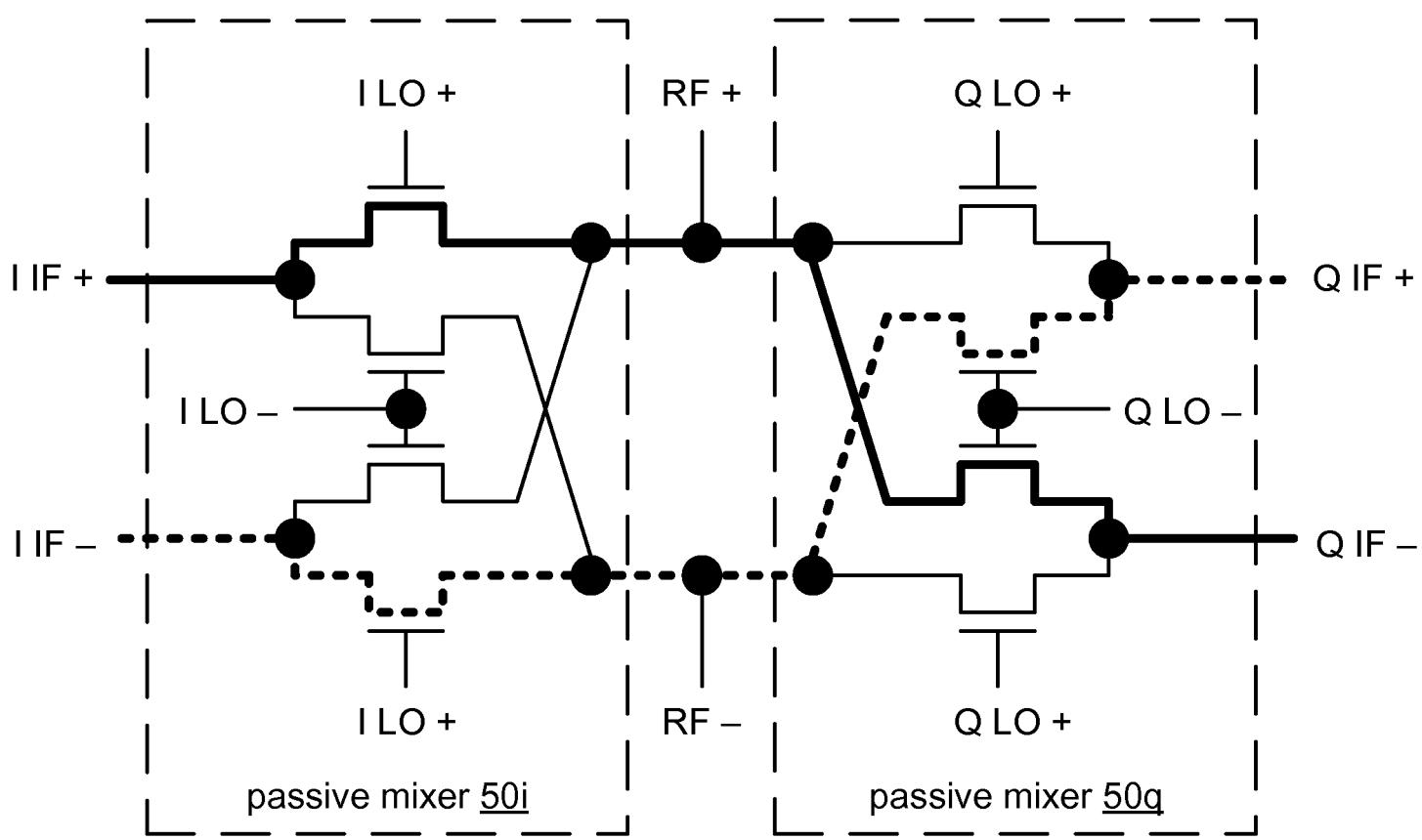

**[00043]** A passive mixer 50 as shown in FIGURE 3a,b may be used as a voltage-commutating mixer or as a current-commutating mixer. FIGURE 4 shows an example of a frequency converter 100 based on a current-commutating quadrature mixer architecture that includes two instances 50i,q of passive mixer 50. Frequency converter 100 has a transconductance stage (including devices T1, T2) that converts the RF voltage signal into a current signal and is AC coupled to the mixers. In another example, the sources of devices T1, T2 are connected directly to the V<sub>SS</sub> rail rather than through a current source. The local oscillator signals (not shown) may also be AC coupled (capacitively coupled) to the respective mixer switch gates. Each mixer drives a low-impedance load, which in this example is the virtual ground of a respective closed-loop opamp 20i,q. In some cases, each passive mixer 50i,q also has a small capacitor connected across its output terminals (e.g., to remove high-frequency components).

**[00044]** FIGURE 5 shows an example 110 of frequency converter 100 in which MOSFETs are used to implement the current sources. The gate bias voltages for these devices may be generated by various techniques. FIGURE 6a shows one example in which the devices that serve as active loads for devices T1, T2 are self-biased. In this particular example, each of the active load devices is diode-connected via a resistive path between its gate and source. FIGURE 6b shows another biasing example in which a common-mode feedback (CMFB) circuit is used to bias the active load devices. Other

forms of CMFB circuits may also be used in such an arrangement. Whether the active load devices are self-biased or biased using a CMFB circuit, a current mirror may be used to set the DC operation point of an active device that provides the DC current to the transconductance devices T1, T2, as shown in FIGURES 6a and 6b. Alternatively, another form of bias voltage generating circuit may be used to generate one or more of the gate bias voltages, such as a bandgap reference voltage generator or a PTAT (proportional to absolute temperature) biasing circuit.

**[00045]** FIGURE 7 shows an example of a MOSFET characteristic curve, where  $I_{DS}$  denotes current between drain and source (i.e., the most positive end and the most negative end, respectively, of the channel regions of an n-channel MOSFET),  $V_{DS}$  denotes voltage between drain and source,  $V_{GS}$  denotes voltage between gate and source, and  $V_T$  denotes the threshold voltage of the device. As may be appreciated from this figure, the impedance of a MOSFET ( $dV_{DS}/dI_{DS}$ ) depends upon the region in which the device is operated. The switches of an active mixer are typically biased to operate in the saturation region, resulting in a high impedance. The switches N1–N4 of a passive mixer are biased near the threshold to operate in the linear (or “triode”) region and thus have a low impedance.

**[00046]** As noted above, the gates of a switching mixer are typically driven by a pair of complementary LO signals. FIGURE 8 shows a diagram of a typical set of quadrature local oscillator signals for driving the mixers of a quadrature mixer architecture. The  $I^+$  and  $Q^+$  signals are 90 degrees out of phase, and each one has a complement ( $I^-$ ,  $Q^-$ ) that is 180 degrees out of phase. In this example, each of the four LO signals has an amplitude that alternates between 0 and 1 at the local oscillator frequency and according to the phase of the particular signal. The local oscillator signals are typically generated to have a duty cycle substantially close to 50%, which reduces even-order harmonics.

**[00047]** FIGURE 9 shows one example of a divide-by-four circuit that may be used to generate a set of quadrature local oscillator signals as shown in FIGURE 8. This divider takes a differential clock input (a clock signal CLK as shown in FIGURE 8 and its complement CLKB) and generates a rail-to-rail differential output for both I and Q channels. As shown in FIGURE 4, the divider includes latches that are smaller than the inverters (e.g., four times smaller) and are arranged between the differential paths,

which may help to maintain fast signal switching and good differential balance. Divide-by-four circuits including D flip-flops or differential inverters are also known.

**[00048]** In some cases, implementing an oscillator to generate a clock signal running at four times the LO frequency may not be feasible (e.g., in very high frequency or very low power applications) or may otherwise be undesirable. In such cases, another structure such as a polyphase filter or other phase-shift network may be used to generate the set of quadrature LO signals. FIGURE 10 shows one example of a second-order polyphase filter configured to generate a set of quadrature local oscillator signals as shown in FIGURE 8. Examples of other structures that may be used to generate the quadrature LO signals include transmission line structures and opamp-based all-pass networks.

**[00049]** The low impedance of the switches in a passive mixer may lead to several problems in practice. For example, poor isolation between the I and Q channels is one significant problem that may arise with the use of passive mixers in a quadrature frequency converter. As shown in FIGURE 8, for example, LO signals having duty cycles of about 50% are commonly used to drive a quadrature pair of switching mixers. One may appreciate from this figure that at any moment, one of the signals  $I^+$  and  $I^-$  is high, and one of the signals  $Q^+$  and  $Q^-$  is high. FIGURE 11 illustrates an example of two periods of overlap during an active half-cycle of the signal  $I^+$ . While the particular pair of active signals changes every quarter-cycle, as a consequence of this overlap, at any moment a switch is on in both of the I and Q mixers.

**[00050]** Because of the low impedance of the switches in the passive mixers, having switches on both sides open at the same time creates paths between the output terminals of the I mixer and the output terminals of the Q mixer. The bold lines in FIGURE 12 show an example of the paths between the I and Q mixer outputs that correspond to overlap period A shown in FIGURE 11, and the bold lines in FIGURE 13 show an example of the paths between the I and Q mixer outputs that correspond to overlap period B shown in FIGURE 11. When the mixers are arranged to drive a low-impedance input (such as the virtual ground of an opamp), one effect of these paths is that each mixer presents a low-impedance output.

**[00051]** The noise current generated by an opamp is inversely proportional to the output impedance of the preceding stage as presented at the opamp input. Consequently, the low output impedance of the passive mixer switch channels in the architecture of FIGURE 8 may lead to a higher noise contribution from the opamp stage. A low impedance between the I and Q channels may also lead to upper sideband and lower sideband transfer functions that are asymmetrical near the band edge. In a quadrature mixer architecture that includes passive mixers, it may be desirable to isolate the I and Q mixer inputs from each other. Such isolation may help to reduce noise at the outputs of amplifier stages following the mixers and/or to maintain flatness of gain across the bandwidth.

**[00052]** One approach to avoiding the effects of cross-coupling between I and Q passive mixers is to use a splitter to split each side of the differential RF input into two separate paths. While this approach may effectively isolate the mixers from each other, it is likely that a suitable splitter will be an off-chip component, thus increasing manufacturing cost and circuit footprint, while the splitter's insertion loss will further increase the overall conversion loss. As shown in FIGURE 13, another approach is to resistively isolate the input terminals of each mixer from the RF input. While such isolation may reduce leakage and cross-coupling of the I and Q mixers, this approach is also less than optimal. Besides the large voltage drop, which reduces voltage headroom and may increase conversion loss, the resistors will also contribute thermal noise.

**[00053]** In a current-commutating quadrature mixer architecture, adding a splitter or other isolation stage between the mixers may reduce the RF current available to each mixer and thus reduce conversion gain. Another factor that may reduce conversion gain in a current-commutating quadrature mixer architecture, even in the absence of an isolation stage, is overlapping on-periods of the I and Q mixers (as illustrated in FIGURE 11, for example). Regardless of whether the architecture includes active mixers or passive mixers, such a switch overlap allows the RF current to be split between the two mixers. As shown in FIGURE 11, switch overlap of the I and Q channels may occur constantly in a quadrature switching mixer architecture that uses local oscillator signals having duty cycles of 50%.

**[00054]** In a method according to an embodiment, mixing is performed using LO signals having a duty cycle of less than 50%. Although the switches in each mixer have a shorter on-period when such LO signals are used, more of the RF current is switched to the mixer during that time, yielding an overall theoretical increase in conversion gain. With respect to noise arising downstream of the mixer (which generally dominates at frequencies near baseband), this increase may result in a higher signal-to-noise ratio (SNR). By reducing or eliminating overlapping on-periods of passive mixers in the I and Q channels, such operation may also reduce opamp noise and may reduce or eliminate a need for an isolation stage between the channels. When LO signals having a duty cycle of 25% or less are used, for example, only one mixer is on at a time.

**[00055]** FIGURE 15 shows one example of a quadrature set of local oscillator signals that have duty cycles of 25%. As in the set of LO signals shown in FIGURE 8, the I+ and Q+ signals are 90 degrees out of phase, and each one has a complement (I-, Q-) that is 180 degrees out of phase. In this example, each of the four LO signals has an amplitude that alternates between 0 and 1 at the local oscillator frequency and according to the phase of the particular signal.

**[00056]** FIGURE 16 shows one example of a logic circuit including four AND gates that may be used to generate a set of LO signals having a 25% duty cycle from a set of LO signals having a 50% duty cycle. An LO signal generator as shown in FIGURE 8 or 9 may be modified to include such a circuit or its equivalent. In another implementation, an LO signal generator as shown in FIGURE 8 or 9 is modified to produce directly a set of LO signals having a 25% duty cycle.

**[00057]** A comparison of the theoretical conversion gains that may be expected from (A) a mixer architecture using a complementary pair of square-wave LO signals having a duty cycle of 50% and (B) the theoretical conversion gain that may be expected from a mixer architecture using a complementary pair of square-wave LO signals having a duty cycle of 25% may be calculated according to the following expression of a mixing operation:

$$\cos(\omega_{F0}t) \cos(\omega_{LO}t) = \frac{1}{2} (\cos[(\omega_{F0} + \omega_{LO})t] + \cos[(\omega_{F0} - \omega_{LO})t]),$$

where  $\omega_{F0}$  is the frequency of the input signal and  $\omega_{LO}$  is the frequency of the fundamental component of each LO signal. Using the symbols  $\alpha$  and  $\beta$  to denote respective weights for the input and LO frequencies, and the subscripts 1 and 2 to denote mixing operations using LO signals having duty cycles of 50% and 25%, respectively, we can express the ratio between these theoretical conversion gains as:

$$\frac{\alpha_2 \cos(\omega_{F0}t) \beta_2 (\cos \omega_{LO}t)}{\alpha_1 \cos(\omega_{F0}t) \beta_1 (\cos \omega_{LO}t)} = \frac{\alpha_2}{\alpha_1} \times \frac{\beta_2}{\beta_1}.$$

**[00058]** First, we consider the ratio of the weights  $\alpha$  for the input signals. When LO signals having a duty cycle of 50% are used to drive a quadrature pair of switching mixers, at any moment a switch is on in both of the I and Q mixers. When LO signals having a duty cycle of 50% are used to drive a quadrature pair of differential mixers as shown in FIGURES 2 or 3, for example, at any moment a pair of switches is on in each of the I and Q mixers. FIGURE 11 illustrates an example of such overlapping switch activations. This overlap causes the RF current to be split between the mixers, such that at any moment when a mixer switch or switch pair is on, that mixer receives only half of the RF input current. When LO signals having a duty cycle of 25% are used, however, at any moment when a mixer switch or switch pair is on, the mixer receives all of the RF input current. Thus the ratio  $\alpha_2/\alpha_1$  is equal to two.

**[00059]** A relation between the weights  $\beta$  for the LO signals may be determined by considering the LO signals in the frequency domain. The Fourier transform of a periodic train of rectangular pulses may be expressed using the following series:

$$f(t) = AD + \sum_{i=1}^{\infty} \frac{2A}{i\pi} \sin(i\pi D) \cos\left(2i\pi \frac{t}{T}\right),$$

where  $A$  is a gain constant and  $D$  is the duty cycle of each pulse. In this expression, the first term represents a DC offset and the terms of the summation represent the fundamental (for  $i = 1$ ) and harmonics (for  $i > 1$ ). For a duty cycle  $D$  equal to 0.5, the terms of the summation for all even  $i$  are equal to zero, so that the LO signal contains no even-order harmonics. For values of  $D$  that are not equal to 0.5, at least some of the summation terms that correspond to even-order harmonics are nonzero.

**[00060]** From the series above, we can express the fundamental frequency component as:

$$f_1(t) = \frac{2A}{\pi} \sin(\pi D) \cos\left(2\pi \frac{t}{T}\right) = \frac{2A}{\pi} \sin(\pi D) \cos(\omega_{LO} t).$$

For a duty cycle  $D$  of 50%, the factor  $\sin(\pi D)$  is equal to one. For a duty cycle  $D$  of 25%, the factor  $\sin(\pi D)$  is equal to  $\sqrt{2}/2$ . As the other factors of  $f_1(t)$  are independent of the duty cycle, the ratio  $\beta_2/\beta_1$  between the weights of the fundamental frequency component of the LO signals is equal to  $\sqrt{2}/2$ .

**[00061]** We can evaluate the ratio between the theoretical conversion gains by substituting the values for these two weight ratios into the expression above:

$$\frac{\alpha_2}{\alpha_1} \times \frac{\beta_2}{\beta_1} = 2 \times \frac{\sqrt{2}}{2} = \sqrt{2}.$$

This ratio applies individually to each of the I and Q channels. Because each of the I and Q channels thus achieves a theoretical gain of  $\sqrt{2}$  when a set of LO signals having a duty cycle of 25% is used (as compared to when a set of LO signals having a duty cycle of 50% is used), the overall theoretical signal gain is 3dB.

**[00062]** When an LO duty cycle of 25% is used instead of 50%, a gain of 3dB in SNR may be expected with respect to noise that arises downstream of the mixers (e.g., in the opamps). For example, a gain of 3dB in SNR may be expected at the output of an amplification stage following a mixer (e.g., an amplifier 20). Although this gain may not apply to noise which appears in the signal as received by the mixers (e.g., noise from a LNA), in some applications the dominant noise source occurs after the mixing stage. For a frequency converter based on passive mixers, for example, flicker noise comes mostly from opamps that follow the mixers.

**[00063]** When a set of quadrature LO signals is generated to have duty cycles of 25%, it is likely that the signals as applied at the mixers will have duty cycles greater than 25% due to distortions such as waveform rounding, which may be caused by effects such as parasitic capacitance. It may be appreciated from FIGURE 15 that if the duty

cycle exceeds 25%, switch on-time overlap between the I and Q channels may occur. Such overlap may result in RF current splitting and/or higher opamp noise as discussed above. In a further embodiment, the LO signals are generated to have duty cycles of less than 25%. In one such example, the LO signals are generated to have duty cycles that are substantially less than 25% (in the context of the duty cycles of the LO signals, “substantially less than” means “less than by 10% or more”). For example, the LO signal generator may be configured to generate a set of LO signals having duty cycles of 20% or even 15%. FIGURE 17 shows one example of a logic circuit having four AND gates and four delay elements that may be used to convert the set of LO signals shown in FIGURE 8 into a set of LO signals having duty cycles of less than 25%. In this case, a desired duty cycle for each output signal  $bI^{+/-}$ ,  $bQ^{+/-}$  may be configured by selecting an appropriate delay value for each delay element. An LO signal generator as shown in FIGURE 8 or 9 may be modified to include such a circuit or its equivalent. In another implementation, an LO signal generator as shown in FIGURE 8 or 9 is modified to produce directly a set of LO signals having a 25% duty cycle. As the magnitude of the fundamental frequency component decreases as the duty cycle becomes smaller, it may be desirable to determine a duty cycle value for the particular application that may be expected to avoid switch overlap while retaining a duty cycle value close to 25%.

**[00064]** Harmonics in the LO signals may give rise to unwanted components in the mixer output signal. An LO signal having a duty cycle close to 25%, for example, has a strong second-order harmonic that may give rise to components at frequencies  $\omega_{F0} \pm 2\omega_{LO}$ . In some cases, it may be desired to filter the mixer output or otherwise to select one from among two or more principal frequency components of the mixed signal. As noted above, for example, a small capacitor may be included across the output terminals of each mixer to suppress high frequencies.

**[00065]** The foregoing presentation of the described embodiments is provided to enable any person skilled in the art to make or use the present invention. Various modifications to these embodiments are possible, and the generic principles presented herein may be applied to other embodiments as well. For example, an embodiment may be implemented in part or in whole as a hard-wired circuit, as a circuit configuration fabricated into an application-specific integrated circuit, or as a firmware program loaded into non-volatile storage or a software program loaded from or into a data

storage medium (such as semiconductor or other volatile or nonvolatile memory, or magnetic and/or optical media such as a disk) as machine-readable code, such code being instructions executable by an array of logic elements such as a microprocessor or other digital signal processing unit or finite state machine.

**[00066]** Embodiments also include methods of frequency conversion as set forth in the appended claims and as expressly disclosed herein by descriptions of the operations of structural embodiments. Each of these methods may be tangibly embodied in one or more data storage media as machine-readable code.

**[00067]** Examples of wireless communications applications that use frequency conversion include portable devices for wireless communications, such as cellular telephones, personal digital assistants (PDAs), pagers, portable e-mail devices (such as the Blackberry<sup>TM</sup>), and satellite devices for consumer and other uses (e.g., GPS receivers, subscription music receivers, television receivers). Other examples of devices for wireless communications include devices configured to communicate over wireless local-area and/or personal-area networks, such as a device compliant with a version of one or more specifications such as IEEE standard 802.11a, 802.11b, and/or 802.11n; IEEE standard 802.15.4 (also called ZigBee<sup>TM</sup>); and IEEE standard 802.15.1 (Bluetooth<sup>TM</sup>); and/or an ultra-wideband (UWB) device. Embodiments include methods and structures as disclosed herein that are configured for use with any such examples.

**[00068]** An implementation of a frequency converter as described herein may be embodied in a chip, possibly as part of a larger circuit that may include an input stage (e.g., a transconductance stage including transistors T1, T2), an output stage (e.g., transimpedance amplifiers such as opamps 20i,q), and/or a quadrature local oscillator signal generator. Such a chip may also include other circuitry for signal reception and/or transmission, such as a low-noise amplifier, a power amplifier, a modulator, a demodulator, and/or a digital signal processor. Embodiments also include specifications in a hardware description language (such as a variety of Verilog or VHDL) of structures disclosed herein, and consumer electronic devices (e.g. cellular telephones) including one or more such structures. Thus, the present invention is not intended to be limited to the embodiments shown above but rather is to be accorded the widest scope consistent with the principles and novel features disclosed in any fashion herein.

**WHAT IS CLAIMED IS:****CLAIMS**

1. An apparatus including a frequency converter, said frequency converter comprising:

a signal generator configured to generate a first complementary pair of local oscillator (LO) signals and a second complementary pair of LO signals such that a phase difference between a signal of the first complementary pair and a signal of the second complementary pair is substantially equal to ninety degrees;

a first mixer configured and arranged to mix a radio-frequency (RF) current signal with the first complementary pair of LO signals; and

a second mixer configured and arranged to mix the RF current signal with the second complementary pair of LO signals,

wherein said signal generator is configured to generate each signal of the first and second complementary pairs to have a duty cycle of substantially less than fifty percent.

2. The apparatus according to claim 1, wherein said signal generator is configured to generate each signal of the first and second complementary pairs to have a duty cycle substantially equal to twenty-five percent.

3. The apparatus according to claim 1, wherein said signal generator is configured to generate each signal of the first and second complementary pairs to have a duty cycle of substantially less than twenty-five percent.

4. The apparatus according to claim 1, wherein said first mixer is configured and arranged to mix a differential RF current signal with the first complementary pair of LO signals, and

wherein said second mixer is configured and arranged to mix the differential RF current signal with the second complementary pair of LO signals.

5. The apparatus according to claim 1, said frequency converter comprising a transconductance stage configured and arranged to output the RF current signal based on an RF voltage signal.

6. The apparatus according to claim 1, wherein each of said first and second mixers includes a passive mixer.

7. The apparatus according to claim 1, wherein said first mixer is configured to commutate the RF current signal according to the first complementary pair of LO signals, and wherein said second mixer is configured to commutate the RF current signal according to the second complementary pair of LO signals.

8. The apparatus according to claim 1, wherein said first mixer is configured to periodically reverse the phase of the RF current signal according to the amplitudes of the first complementary pair of LO signals over time, and

wherein said second mixer is configured to periodically reverse the phase of the RF current signal according to the amplitudes of the second complementary pair of LO signals over time.

9. The apparatus according to claim 1, wherein each of said first and second mixers includes a Gilbert cell.

10. The apparatus according to claim 1, wherein said first mixer is configured to mix the RF current signal with the first complementary pair of LO signals to produce a baseband signal based on an in-phase component of the RF current signal, and

wherein said second mixer is configured to mix the RF current signal with the second complementary pair of LO signals to produce a baseband signal based on a quadrature component of the RF current signal.

11. The apparatus according to claim 1, wherein said frequency converter includes:

- a first transimpedance amplifier arranged to receive, from said first mixer, a frequency-converted signal based on the RF current signal and the first complementary pair;

- and

- a second transimpedance amplifier arranged to receive, from said second mixer, a frequency-converted signal based on the RF current signal and the second complementary pair.

12. The apparatus according to claim 11, wherein at least one among said first and second transimpedance amplifiers includes an operational amplifier.

13. The apparatus according to claim 3, wherein said apparatus is an integrated circuit.

14. The apparatus according to claim 3, wherein said apparatus is a device for wireless communications including said frequency converter.

15. The apparatus according to claim 3, wherein said apparatus comprises a cellular telephone including said frequency converter.

16. A data storage medium having a machine-executable specification, in a hardware description language, of the apparatus according to claim 3.

17. A method of frequency conversion, said method comprising:

- generating a first complementary pair of local oscillator (LO) signals and a second complementary pair of LO signals such that a phase difference between a signal of the first complementary pair and a signal of the second complementary pair is substantially equal to ninety degrees;

- in a first channel, mixing a radio-frequency (RF) current signal with the first complementary pair of LO signals; and

- in a second channel, mixing the RF current signal with the second complementary pair of LO signals,wherein each signal of the first and second complementary pairs has a duty cycle of substantially less than fifty percent.

18. The method of frequency conversion according to claim 17, said method comprising generating each of the signals of the first and second complementary pairs of LO signals to have a duty cycle substantially equal to twenty-five percent.

19. The method of frequency conversion according to claim 17, said method comprising generating each of the signals of the first and second complementary pairs of LO signals to have a duty cycle of less than twenty-five percent.

20. The method of frequency conversion according to claim 17, said method comprising generating each of the signals of the first and second complementary pairs of LO signals to have a duty cycle of substantially less than twenty-five percent.

21. The method of frequency conversion according to claim 17, wherein said mixing in a first channel comprises mixing a differential RF current signal with the first complementary pair of LO signals, and

wherein said mixing in a second channel comprises mixing the differential RF current signal with the second complementary pair of LO signals.

22. The method of frequency conversion according to claim 17, said method comprising converting an RF voltage signal to the RF current signal.

23. The method of frequency conversion according to claim 17, wherein said mixing in a first channel comprises commutating the RF current signal according to the first complementary pair of LO signals, and

wherein said mixing in a first channel comprises commutating the RF current signal according to the second complementary pair of LO signals.

24. The method of frequency conversion according to claim 17, wherein said mixing in a first channel comprises periodically reversing the phase of the RF current signal according to the amplitudes of the first complementary pair of LO signals over time, and

wherein said mixing in a second channel comprises periodically reversing the phase of the RF current signal according to the amplitudes of the second complementary pair of LO signals over time.

25. The method of frequency conversion according to claim 17, said method comprising, in the first channel, converting a frequency-converted signal based on the RF current signal and the first complementary pair to a voltage signal, and in the second channel, converting a frequency-converted signal based on the RF current signal and the second complementary pair to a voltage signal.

26. The method of frequency conversion according to claim 17, wherein said mixing in a first channel comprises mixing the RF current signal with the first complementary pair to produce a first baseband signal based on an in-phase component of the RF signal, and

wherein said mixing in a second channel comprises mixing the RF current signal with the second complementary pair to produce a second baseband signal based on a quadrature component of the RF signal.

27. An apparatus including a frequency converter, said frequency converter comprising:

means for generating a first complementary pair of local oscillator (LO) signals and a second complementary pair of LO signals such that a phase difference between a signal of the first complementary pair and a signal of the second complementary pair is substantially equal to ninety degrees;

in a first channel, means for mixing a radio-frequency (RF) current signal with the first complementary pair of LO signals; and

in a second channel, means for mixing the RF current signal with the second complementary pair of LO signals,

wherein said means for generating is configured to generate each signal of the first and second complementary pairs to have a duty cycle of substantially less than fifty percent.

28. The apparatus according to claim 27, wherein said means for generating is configured to generate each signal of the first and second complementary pairs to have a duty cycle substantially equal to twenty-five percent.

29. The apparatus according to claim 27, wherein said means for generating is configured to generate each signal of the first and second complementary pairs to have a duty cycle of substantially less than twenty-five percent.

30. The apparatus according to claim 27, said frequency converter comprising a means for converting an RF voltage signal to the RF current signal.

31. The apparatus according to claim 27, wherein said means for mixing in a first channel is configured to commutate the RF current signal according to the first complementary pair of LO signals, and

wherein said means for mixing in a second channel is configured to commutate the RF current signal according to the second complementary pair of LO signals.

32. The apparatus according to claim 27, wherein said means for mixing in a first channel is configured to periodically reverse the phase of the RF current signal according to the amplitudes of the first complementary pair of LO signals over time, and

wherein said means for mixing in a second channel is configured to periodically reverse the phase of the RF current signal according to the amplitudes of the second complementary pair of LO signals over time.

33. The apparatus according to claim 27, wherein said means for mixing in a first channel is configured to mix the RF current signal with the first complementary pair of LO signals to produce a baseband signal based on an in-phase component of the RF current signal, and

wherein said means for mixing in a second channel is configured to mix the RF current signal with the second complementary pair of LO signals to produce a baseband signal based on a quadrature component of the RF current signal.

34. The apparatus according to claim 27, wherein said frequency converter includes:

means for converting a frequency-converted signal, received from said means for mixing in a first channel and based on the RF current signal and the first complementary pair, to a voltage signal; and

means for converting a frequency-converted signal, received from said means for mixing in a second channel and based on the RF current signal and the second complementary pair, to a voltage signal.

35. The apparatus according to claim 29, wherein said apparatus is an integrated circuit.

36. The apparatus according to claim 29, wherein said apparatus comprises a device for wireless communications including said frequency converter.

37. The apparatus according to claim 29, wherein said apparatus comprises a cellular telephone including said frequency converter.

FIG. 1a

FIG. 1b

3/17

FIG. 3a

FIG. 3b

FIG. 4

FIG. 5

6/17

FIG. 6a

FIG. 6b

7/17

FIG. 7

8/17

FIG. 8

FIG. 9

FIG. 10

11/17

FIG. 11

12/17

FIG. 12

FIG. 13

FIG. 14

15/17

FIG. 15

FIG. 16

17/17

FIG. 17