US 20060271896A1

## (19) United States (12) Patent Application Publication (10) Pub. No.: US 2006/0271896 A1 Miyanishi et al.

### Nov. 30, 2006 (43) **Pub. Date:**

### (54) SEMICONDUCTOR DEVICE

(75) Inventors: Atsushi Miyanishi, Tokyo (JP); Hisashi Matsumoto, Tokyo (JP)

> Correspondence Address: **BUCHANAN, INGERSOLL & ROONEY PC POST OFFICE BOX 1404** ALEXANDRIA, VA 22313-1404 (US)

- (73) Assignee: Renesas Technology Corp.

- Appl. No.: 11/493,533 (21)

- (22) Filed: Jul. 27, 2006

#### **Related U.S. Application Data**

(62) Division of application No. 09/114,203, filed on Jul. 13, 1998, now Pat. No. 7,105,901.

#### Foreign Application Priority Data (30)

Jan. 29, 1998 (JP)..... P10-017011

#### **Publication Classification**

- (51) Int. Cl.

- G06F 17/50 (2006.01)

#### (57)ABSTRACT

An active area (1) is provided with a concave part in its corner portion in a shape along a plan view. An insulating film (7) encloses this active area. A gate electrode (30) is arranged on a depressed region (DR) having an edge portion which is located on a low position due to the concave part, while a gate electrode (20) is arranged on an ordinary region (OR) having an edge portion projecting beyond the depressed region. A gate end cap (margin part) of the gate electrode (20) has a length x, while that of the gate electrode (30) has a length  $x+\alpha$ . Thus provided is a semiconductor device causing no current defect between source/drain regions even if the active area and an insulating film defining this active area fail to satisfy the layout design following refinement of the semiconductor device.

.

FIG. 2

F I G. 3

FIG. 6

FIG. 9

FIG. 11

FIG. 15

# FIG. 16 (BACKGROUND ART)

FIG. 18

FIG. 19 (BACKGROUND ART)

FIG. 20

FIG. 21

FIG. 22 (BACKGROUND ART)

FIG. 25

FIG. 29 (BACKGROUND ART)

FIG. 30 (BACKGROUND ART)

FIG. 31 (BACKGROUND ART)

FIG. 32 (BACKGROUND ART)

FIG. 33 (BACKGROUND ART)

FIG. 34 (BACKGROUND ART)

FIG. 35 (BACKGROUND ART)

FIG. 36 (BACKGROUND ART)

## FIG. 37 (BACKGROUND ART)

### SEMICONDUCTOR DEVICE

#### CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a divisional application of application Ser. No. 09/114,203, filed Jul. 13, 1998.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

**[0003]** The present invention relates to a semiconductor device, and more particularly, it relates to the shape of a margin part of a gate electrode forming a MOS transistor which is provided on an active area having a concave part.

#### [0004] 2. Description of the Background Art

**[0005]** A semiconductor device formed by MOS transistors is generally provided with an insulating film which is formed to enclose an active area (element forming region) for electrically isolating this active area from other ones. The gate electrode of each MOS transistor provided on the active area is formed over the active area and the insulating film to divide the active area, thereby electrically isolating source/ drain regions formed on both sides of the gate electrode from each other.

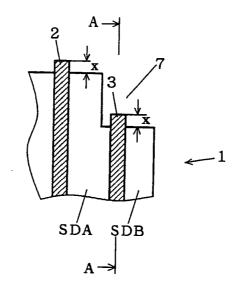

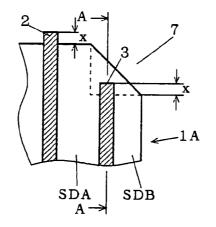

[0006] FIG. 29 shows a part of an active area and gate electrodes which are formed on this active area. Referring to FIG. 29, the active area 1 has a concave part on its corner portion in a shape along a plan view. In other words, the concave part partially reduces the width of the active area 1. An insulating film 7 encloses the active area 1. The gate electrode 3 is so formed that its end portion reaches an upper portion of the insulating film 7 on the concave part, while the gate electrode 2 is so formed that its end portion reaches an upper portion of the insulating film 7 in a portion other than the concave part.

[0007] The parts of the gate electrodes 2 and 3 reaching the upper portion of the insulating film 7 are referred to as gate end caps, and x represents the length thereof. The gate end caps are set as margin parts (gate parts extending beyond the active area 1) in the layout design phase so that the length of the gate electrodes 2 and 3 are not smaller than the span of the active area 1, and the length x thereof is uniformly set for all gate electrodes as that from an edge portion of the active area 1 on design. This length x is so set that the forward end portions of the gate electrodes 2 and 3 are not located on the active area 1 even if the same are rounded due to corrosion by etching or the like to partially reduce the gate length. Source/drain regions SDA and SDB are formed on both sides of the gate electrode 3. While still another source/drain region is formed on a side of the gate electrode 2, symbol therefor is omitted in FIG. 29.

**[0008]** Such a gate end cap is defined as a part between an endmost portion of each gate electrode and an edge portion of the active area. When two active areas are formed separately from each other and a single gate electrode is formed to extend over these two active areas, therefore, the gate electrode is provided on an insulating film between the two active areas. However, no gate end cap is present on this portion, due to absence of an end portion of the gate electrode.

**[0009]** While such a gate electrode has an end portion on its pad part provided with a contact hole or a via hole or directly connected to a wiring layer, no gate end cap is present on (required for) this part.

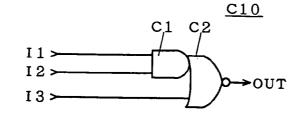

[0010] The active area 1 has a concave part when provided with an AND-NOR gate C10 shown in FIG. 30, for example. Referring to FIG. 30, an AND part C1 is supplied with input signals 11 and 12, while a second input of a NOR part C2 is supplied with an input signal I3.

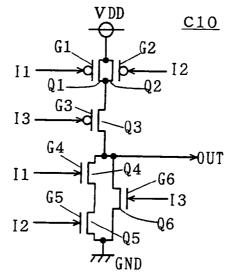

[0011] FIG. 31 shows the transistor level structure of the AND-NOR gate C10. The AND-NOR gate C10 comprises P-channel transistors Q1 and Q2 having source electrodes which are connected to a power source VDD in common, a PMOS transistor Q3 having a source electrode which is connected to drain electrodes of the P-channel transistors Q1 and Q2, NMOS transistors Q4 and Q6 having drain electrodes which are connected to that of the PMOS transistor Q3 in common, and an NMOS transistor Q5 having a drain electrode which is connected to a source electrode of the NMOS transistor Q4 and a source electrode which is grounded in common with that of the NMOS transistor Q6. The input signals I1 and I2 are supplied to gate electrodes G1, G2, G4 and G5 of the PMOS transistors Q1 and Q2 and the NMOS transistors Q4 and Q5, while the input signal I3 is supplied to gate electrodes G3 and G6 of the PMOS transistor Q3 and the NMOS transistor Q6. A common node between the PMOS transistor Q3 and the NMOS transistors Q4 and Q6 defines an output end.

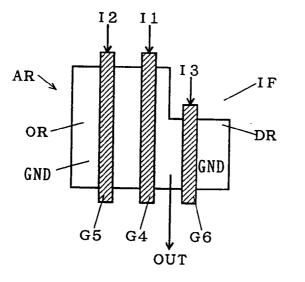

[0012] FIG. 32 illustrates the layout of the NMOS transistors Q4 to Q6 of the AND-NOR gate C10 having such a structure.

[0013] Referring to FIG. 32, an active area AR is provided with a concave part on its corner portion in a shape along a plan view, and an insulating film IF encloses this active area AR. The gate electrode G6 is formed on a depressed region DR having a span which is reduced due to the concave part, while the gate electrodes G4 and G5 are formed on an ordinary region OR other than the concave part.

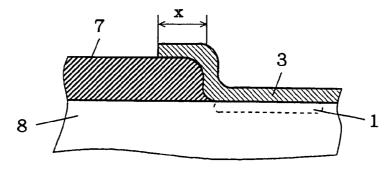

[0014] FIG. 33 is a sectional view taken along the line A-A in FIG. 29. As shown in FIG. 33, the gate electrode 3 formed on the active area 1 extends on the upper portion of the insulating film 7 over the length x of the gate end cap. Therefore, the source/drain regions SDA and SDB are electrically isolated from each other. While the active area 1 is invisible in the sectional direction since a channel region is formed on a portion of a silicon substrate 8 located under the gate electrode 3, FIG. 33 shows the position corresponding to the active area 1 with a broken line for convenience of illustration.

**[0015]** While the source/drain regions SDA and SDB are generally electrically isolated from each other regardless of the concave part of the active area **1**, such source/drain regions SDA and SDB may not be completely isolated from each other, depending on the shape of the concave part.

[0016] This case is now described with reference to FIGS. 34 and 35. FIG. 34 shows an active area 1A having a corner portion which is provided with no concave part but obliquely notched. FIG. 36 is a sectional view taken along the line A-A in FIG. 34. As shown in FIG. 36, a gate electrode 3 does not reach an upper portion of an insulating film 7, and the active area 1A is longer than the gate electrode 3.

[0017] When gate electrodes 2 and 3 similar to those shown in FIG. 29 are formed on this active area 1A having such a shape, an end portion of the gate electrode 3 does not reach the upper portion of the insulating film 7. Source/drain regions are generally formed by injecting an impurity through a gate electrode serving as an injection mask. If an impurity is injected through the gate electrode 3 serving as an injection mask, therefore, source/drain regions SDA and SDB are formed not only on both sides of the gate electrode 3 but also around a forward end portion thereof. Consequently, the source/drain regions SDA and SDB formed on both sides of the gate electrode 3 are electrically shorted to hinder the function of the MOS transistor.

**[0018] FIG. 35** shows an active area 1B provided on its corner portion with a concave part, which is not rectangularly shaped.

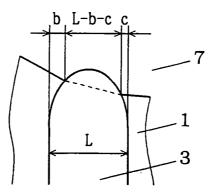

[0019] When gate electrodes 2 and 3 similar to those shown in FIG. 29 are formed on this active area 1B having such a shape, an end portion of the gate electrode 3 only partially reaches an upper portion of an insulating film 7. In this case, source/drain regions SDA and SDB formed on both sides of the gate electrode 3 are not electrically shorted but the gate length of the gate electrode 3 is partially reduced. Assuming that L represents the gate length of the gate electrode 3 and b represents the length of a part of the end portion of the gate electrode 3 not reaching the upper portion of the insulating film 7 as shown in FIG. 35, the substantial gate length is about L-b. When the gate length is thus partially reduced, a leakage current flows between the source/drain regions SDA and SDB in a transistor operation to deteriorate the function of the MOS transistor. FIG. 37 shows a gate electrode 3 having a forward end portion which is rounded due to corrosion by etching or the like. As shown in FIG. 37, both side surfaces of the gate electrode 3 only partially reach an upper portion of an insulating film 7 due to the rounded forward end portion. Assuming that b and c represent the lengths of such parts respectively, the substantial gate length is about L-b-c. Thus, the substantial gate length is further reduced as compared with a gate electrode having a forward end portion which is not rounded.

[0020] Formation of the active area 1A or 1B shown in FIG. 34 or 35 conceivably results from divergence of the insulating film from the layout design, an proximity effect in photolithography, displacement of the position for introducing the impurity from the planned one in formation of the source/drain regions SDA and SDB. It can be said that such a problem, which has become obvious following refinement of the semiconductor device, has heretofore been neglected.

#### SUMMARY OF THE INVENTION

**[0021]** According to a first aspect of the present invention, a semiconductor device comprises an active area which is provided with at least one MOS transistor and an insulating film defining the active area. The active area is set in a shape having a concave part in a shape along a plan view, the active area is provided with an ordinary region and a depressed region having an edge portion which is depressed beyond the ordinary region due to presence of the concave part, the MOS transistor includes a first MOS transistor which is formed on the depressed region and a second MOS transistor which is formed on the ordinary region, and the length of a margin part of a first gate electrode constructing

the first MOS transistor is set to be larger than that of a margin part of a second gate electrode constructing the second MOS transistor.

[0022] In the semiconductor device according to the first aspect of the present invention, the length of the margin part of the first gate electrode forming the first MOS transistor is set to be larger than that of the margin part of the second gate electrode forming the second MOS transistor, whereby an end portion of the first gate electrode completely reaches an upper portion of the insulating film even if an unnecessary active area exists in the concave part of the active area after various fabrication steps. Thus, the first gate electrode is prevented from partial reduction of its gate length, thereby preventing occurrence of current leakage between source/ drain regions which are formed on the exterior of both side surfaces of the first gate electrode. Even if the concave part is filled up with an unnecessary active area, further, the source/drain regions formed on the exterior of both side surfaces of the first gate electrode are electrically isolated from each other and prevented from shorting, whereby a normally operating MOS transistor can be obtained.

**[0023]** According to a second aspect of the present invention, the concave part is formed on a corner portion of the active area, and the length of the margin part of the first gate electrode is set at the total of the length of the margin part of the second gate electrode and a length which is equal to a depression length in the concave part.

**[0024]** In the semiconductor device according to the second aspect of the present invention, the margin part of the first gate electrode has a sufficient length, whereby the end portion of the first gate electrode completely reaches the upper portion of the insulating film even if the corner portion of the active area is provided with no concave part but obliquely notched after various fabrication steps, whereby the source/drain regions formed on the exterior of both side surfaces of the first gate electrode are electrically isolated from each other and prevented from shorting, whereby a normally operating MOS transistor can be obtained.

**[0025]** According to a third aspect of the present invention, the concave part is formed on a corner portion of the active area, and the length of the margin part of the first gate electrode is set at the total of the length of the margin part of the second gate electrode and the length of a portion between the edge portion of the depressed region and an intersection between a virtual line which is set to connect first and second convex corner portions of the active area in the concave part and the first gate electrode.

**[0026]** In the semiconductor device according to the third aspect of the present invention, the length of the margin part of the first gate electrode is set on the assumption that the corner portion of the active area is provided with no concave part but obliquely notched. Even if the corner portion of the active area is provided with no concave part but obliquely notched after various fabrication steps, therefore, the end portion of the first gate electrode completely reaches the upper portion of the insulating film, whereby the source/ drain regions formed on the exterior of both side surfaces of the first gate electrode are electrically isolated from each other and prevented from shorting, whereby a normally operating MOS transistor can be obtained. Further, the length of the margin part of the first gate electrode is prevented from being increased beyond necessity.

**[0027]** According to a fourth aspect of the present invention, the concave part is a dent part which is formed on a portion of the active area other than the corner portion, the ordinary region is divided into first and second ordinary regions due to presence of the dent part, an edge portion of the second ordinary region, and the length of the margin part of the first gate electrode is set at the total of the length of the margin part of the second gate electrode and a length which is equal to a depression length of the edge portions of the depressed region and the second ordinary region.

**[0028]** In the semiconductor device according to the fourth aspect of the present invention, the margin part of the first gate electrode has a sufficient length, whereby the end portion of the first gate electrode completely reaches the upper portion of the insulating film even if an unnecessary active area exists in the concave part of the active area after various fabrication steps, whereby the first gate electrode is prevented from partial reduction of its gate length. Therefore, occurrence of current leakage between the source/drain regions formed on the exterior of both side surfaces of the first gate electrode is prevented, whereby a normally operating MOS transistor can be obtained.

**[0029]** According to a fifth aspect of the present invention, the concave part is a dent part which is formed on a portion of the active area other than the corner portion, the ordinary region is divided into first and second ordinary regions due to presence of the dent part, an edge portion of the second ordinary region, and the length of the margin part of the first ordinary region, and the length of the length of the margin part of the second gate electrode and the length of a portion between the edge portion of the depressed region and an intersection between a virtual line which is set to connect first and second convex corner portions of the active area in the concave part and the first gate electrode.

**[0030]** In the semiconductor device according to the fifth aspect of the present invention, the length of the margin part of the first gate electrode is set on the assumption that the concave part is filled up with an unnecessary active area, whereby the length of the margin part of the first gate electrode is prevented from being increased beyond necessity.

[0031] According to a sixth aspect of the present invention, a semiconductor device comprises an active area which is provided with at least one MOS transistor, and an insulating film defining the active area. The active area is set in a shape having a concave part in a shape along a plan view, the active area is provided with an ordinary region and a depressed region having an edge portion which is depressed beyond the ordinary region due to presence of the concave part, the MOS transistor includes a first MOS transistor which is formed on the depressed region and a second MOS transistor which is formed on the ordinary region, and a margin part of a first gate electrode constructing the first MOS transistor is set in a shape having a bent portion which is bent at a prescribed angle to extend in a direction separating from the ordinary region.

**[0032]** In the semiconductor device according to the sixth aspect of the present invention, the margin part of the first gate electrode forming the first MOS transistor is set in the shape having the bent portion which is bent at the prescribed

angle to extend in the direction separating from the ordinary region, whereby the end portion of the first gate electrode completely reaches the upper portion of the insulating film even if an unnecessary active area exists in the concave part of the active area after various fabrication steps. Thus, the first gate electrode is prevented from partial reduction of its gate length, and occurrence of current leakage between the source/drain regions formed on the exterior of both side surfaces of the first gate electrode is prevented. Even if the concave part is filled up with an unnecessary active area, the source/drain regions formed on the exterior of both side surfaces of the first gate electrode are electrically isolated from each other and prevented from shorting, whereby a normally operating MOS transistor can be obtained.

**[0033]** According to a seventh aspect of the present invention, the concave part is formed on a corner portion of the active area, the prescribed angle is 90°, the depressed region includes a first edge portion which is perpendicular to the first gate electrode and a second edge portion which is parallel to the first gate electrode, the bent portion extends to be substantially in contact with or not in contact with the first edge portion of the depressed region, and the length of the bent portion is so set that its forward end portion projects beyond the second edge portion of the depressed region by a distance which is equal to the length of a margin part of a second gate electrode constructing the second MOS transistor.

[0034] In the semiconductor device according to the seventh aspect of the present invention, the forward end portion of the bent portion is set to project beyond the second edge portion of the depressed region, whereby the end portion of the first gate electrode completely reaches the upper portion of the insulating film even if an unnecessary active area exists in the concave part of the active area after various fabrication steps, whereby the first gate electrode is prevented from partial reduction of its gate length, occurrence of current leakage between the source/drain regions formed on the exterior of both side surfaces of the first gate electrode is prevented, and a normally operating MOS transistor can be obtained.

**[0035]** According to an eighth aspect of the present invention, the concave part is formed on a corner portion of the active area, the prescribed angle is 90°, the depressed region includes a first edge portion which is perpendicular to the first gate electrode and a second edge portion which is parallel to the first gate electrode, the bent portion extends to be not in contact with the first edge portion of the depressed region, and the length of the bent portion is so set that its forward end portion projects beyond an intersect position between a virtual line which is set to connect first and second convex corner portions of the active area in the concave part and the first gate electrode by a distance which is equal to the length of a margin part of a second gate electrode constructing the second MOS transistor.

**[0036]** In the semiconductor device according to the eighth aspect of the present invention, the length of the margin part of the first gate electrode is set on the assumption that the corner portion of the active area is provided with no concave part but obliquely notched. Even if the corner portion is provided with no concave part but obliquely notched after various fabrication steps, therefore, the end portion of the first gate electrode completely reaches

the upper portion of the insulating film. Thus, the source/ drain regions formed on the exterior of both side surfaces of the first gate electrode are electrically isolated from each other and prevented from shorting, whereby a normally operating MOS transistor can be obtained. Further, the length of the margin part of the first gate electrode is prevented from being increased beyond necessity.

[0037] According to a ninth aspect of the present invention, the concave part is formed on a corner portion of the active area, the bent portion is bent about an intersect position between a virtual line which is set to connect first and second convex corner portions of the active area in the concave part and the first gate electrode, the prescribed angle is smaller than 90°, and the length of the bent portion is so set that its forward end portion projects beyond the intersect position by a distance which is equal to the length of a margin part of a second gate electrode constructing the second MOS transistor.

**[0038]** In the semiconductor device according to the ninth aspect of the present invention, the forward end portion of the bent portion is set to project beyond the intersect position between the first gate electrode and the virtual line, whereby the end portion of the first gate electrode completely reaches the upper portion of the insulating film even if the corner portion of the active area is provided with no concave part but obliquely notched after various fabrication steps. Thus, the source/drain regions formed on the exterior or both side surfaces of the first gate electrode are electrically isolated from each other and prevented from shorting, whereby a normally operating MOS transistor can be obtained.

[0039] According to a tenth aspect of the present invention, a semiconductor device comprises an active area which is provided with at least one MOS transistor and an insulating film defining the active area. The active area is set in a shape having a concave part in a shape along a plan view, the active area is provided with an ordinary region and a depressed region having an edge portion which is depressed beyond the ordinary region due to presence of the concave part, the MOS transistor includes a plurality of MOS transistors which are arranged on the depressed region and electrically connected in parallel with each other, and respective gate electrodes of the plurality of MOS transistors are arranged in parallel with each other and electrically connected in common so that margin parts of at least a gate electrode which is located most approximately to the ordinary region and that adjacent to this gate electrode are connected with each other among the respective gate electrodes of the plurality of MOS transistors.

**[0040]** In the semiconductor device according to the tenth aspect of the present invention, the margin parts of at least the gate electrode located most approximately to the ordinary region and the gate electrode adjacent thereto are connected with each other among the respective gate electrodes of the plurality of MOS transistors when the two gate electrodes and a connected body of the respective margin parts enclose the source/drain regions between the two gate electrodes. Even if an unnecessary active area exists in the concave part of the active area after various fabrication steps, therefore, the source/drain regions between the two gate electrodes are electrically

isolated from the remaining source/drain regions and prevented from shorting, whereby normally operating MOS transistors can be obtained.

**[0041]** According to an eleventh aspect of the present invention, all margin parts of the respective gate electrodes of the plurality of MOS transistors are connected with each other.

**[0042]** In the semiconductor device according to the eleventh aspect of the present invention, all margin parts of the respective gate electrodes of the plurality of MOS transistors are connected when the plurality of MOS transistors which are electrically connected in parallel with each other are arranged on the depressed region. Even if an unnecessary active area exists in the concave part of the active area over a wide range, therefore, the source/drain regions between the gate electrodes are electrically isolated from each other and prevented from shorting, whereby normally operating MOS transistors can be obtained.

**[0043]** An object of the present invention is to provide a semiconductor device which causes no current defect between source/drain regions even if an active area and an insulating film defining this active area fail to satisfy the layout design following refinement of the semiconductor device.

**[0044]** The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

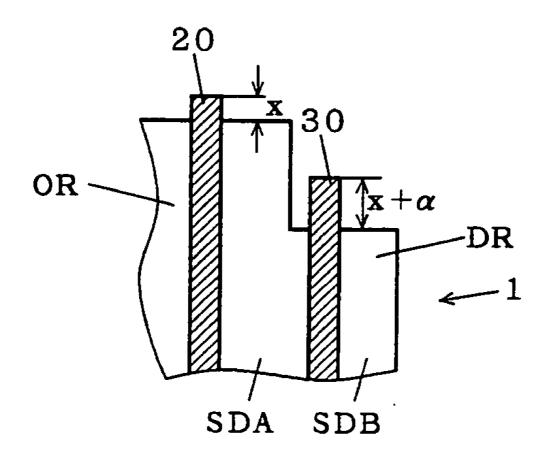

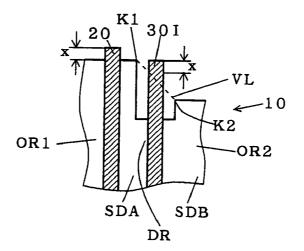

**[0045] FIG. 1** illustrates a semiconductor device according to an embodiment 1 of the present invention;

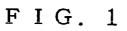

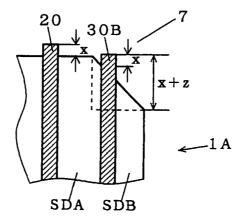

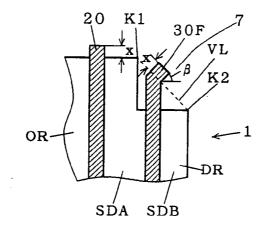

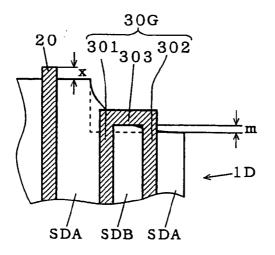

**[0046] FIG. 2** illustrates the semiconductor device according to the embodiment 1 of the present invention;

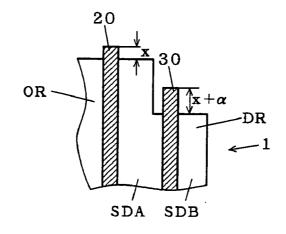

**[0047] FIG. 3** illustrates a modification 1 of the semiconductor device according to the embodiment 1 of the present invention;

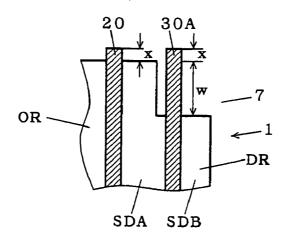

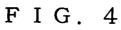

**[0048] FIG. 4** illustrates the modification 1 of the semiconductor device according to the embodiment 1 of the present invention;

**[0049] FIG. 5** illustrates a modification 2 of the semiconductor device according to the embodiment 1 of the present invention;

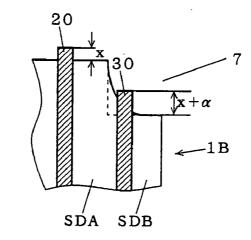

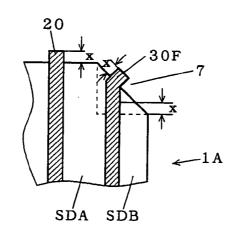

**[0050] FIG. 6** illustrates the modification 2 of the semiconductor device according to the embodiment 1 of the present invention;

**[0051] FIG. 7** illustrates still another modification of the semiconductor device according to the embodiment 1 of the present invention;

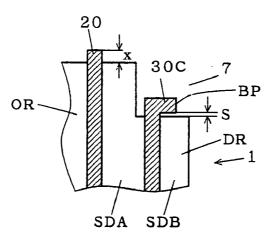

**[0052] FIG. 8** illustrates a semiconductor device according to an embodiment 2 of the present invention;

**[0053] FIG. 9** illustrates the semiconductor device according to the embodiment 2 of the present invention;

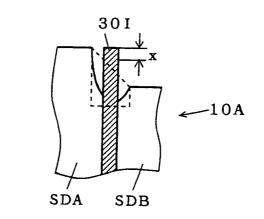

**[0054] FIG. 10** illustrates a modification 1 the semiconductor device according to the embodiment 2 of the present invention;

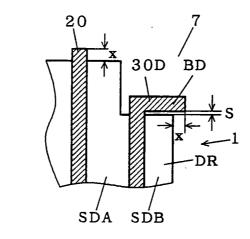

**[0055] FIG. 11** illustrates the modification 1 of the semiconductor device according to the embodiment 2 of the present invention;

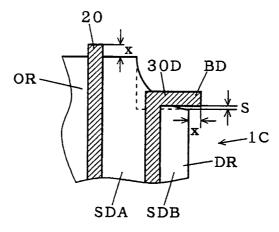

**[0056] FIG. 12** illustrates a modification 2 of the semiconductor device according to the embodiment 2 of the present invention;

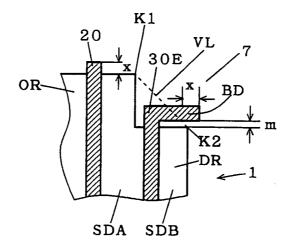

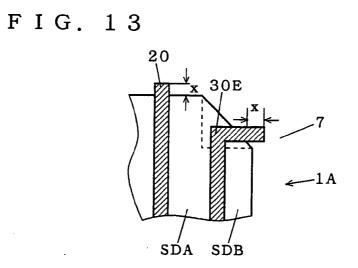

**[0057] FIG. 13** illustrates the modification 2 of the semiconductor device according to the embodiment 2 of the present invention:

**[0058] FIG. 14** illustrates a modification 3 of the semiconductor device according to the embodiment 2 of the present invention;

**[0059] FIG. 15** illustrates the modification 3 of the semiconductor device according to the embodiment 2 of the present invention;

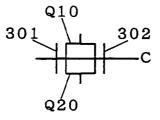

**[0060] FIG. 16** illustrates a semiconductor device according to an embodiment 3 of the present invention;

**[0061] FIG. 17** illustrates the semiconductor device according to the embodiment 3 of the present invention;

**[0062] FIG. 18** illustrates the semiconductor device according to the embodiment 3 of the present invention;

**[0063] FIG. 19** illustrates a modification of the semiconductor device according to the embodiment 3 of the present invention;

**[0064] FIG. 20** illustrates the modification of the semiconductor device according to the embodiment 3 of the present invention;

**[0065] FIG. 21** illustrates the modification of the semiconductor device according to the embodiment 3 of the present invention;

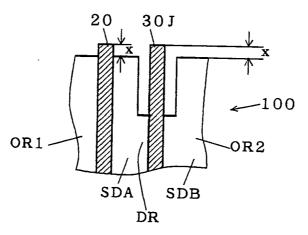

**[0066] FIG. 22** illustrates a semiconductor device according to an embodiment 4 of the present invention;

**[0067] FIG. 23** illustrates the semiconductor device according to the embodiment 4 of the present invention;

**[0068] FIG. 24** illustrates the semiconductor device according to the embodiment 4 of the present invention;

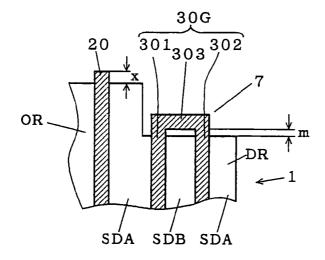

**[0069] FIG. 25** illustrates the semiconductor device according to the embodiment 4 of the present invention;

**[0070] FIG. 26** illustrates a modification 1 of the semiconductor device according to the embodiment 4 of the present invention;

**[0071] FIG. 27** illustrates the modification 1 of the semiconductor device according to the embodiment 4 of the present invention;

**[0072] FIG. 28** illustrates a modification 2 of the semiconductor device according to the embodiment 4 of the present invention;

[0073] FIG. 29 illustrates a problem in a conventional semiconductor device;

**[0074] FIG. 30** illustrates an exemplary circuit having a concave part in an active area;

[0075] FIG. 31 illustrates the exemplary circuit having the concave part in the active area;

[0076] FIG. 32 illustrates the layout of the exemplary circuit having the concave part in the active area;

[0077] FIG. 33 illustrates a sectional structure of a general active area;

**[0078] FIG. 34** illustrates the structure of a conventional semiconductor device;

**[0079] FIG. 35** illustrates the structure of another conventional semiconductor device;

**[0080] FIG. 36** illustrates a sectional structure of a depressed region of an active area; and

[0081] FIG. 37 illustrates the structure of still another conventional semiconductor device.

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

#### A. Embodiment 1

[0082] <A-1. Device Structure>

[0083] FIG. 1 shows a part of an active area 1 in the layout design phase of a semiconductor device according to an embodiment 1 of the present invention and gate electrodes 20 and 30 arranged on this active area 1. Referring to FIG. 1, the active area 1 is provided with a concave part on its corner portion in a shape along a plan view. An insulating film 7 encloses the active area 1. The gate electrode 30 is arranged on a depressed region DR having an edge portion which is located on a low position due to the concave part, and the gate electrode 20 is arranged on an ordinary region (a region other than the depressed region DR) OR having an edge portion projecting beyond the depressed region DR.

**[0084]** A gate end cap (margin part) of the gate electrode has a length x. This gate end cap is set as the margin part (gate portion extending beyond the active area) in order to prevent the length of the gate electrode from being reduced below the span of the active area The length x is so set that a forward portion of the gate electrode is not located on the active area even if this forward end portion is rounded due to corrosion by etching or the like to partially reduce the gate length. The length x of the gate end cap of the gate electrode **20** is set as that from an edge portion of the active area on layout design.

**[0085]** On the other hand, a gate end cap of the gate electrode **30** has a length  $x+\alpha$ . The additional length  $\alpha$  is set to be not more than the length x of the gate end cap of the gate electrode arranged on the ordinary region  $(0<\alpha \le x)$ , for example.

[0086] <A-2. Characteristic Function/Effect>

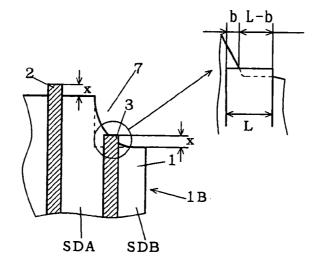

**[0087] FIG. 2** shows a part of an active area 1B of a semiconductor device actually fabricated on the basis of such design values and gate electrodes **20** and **30** arranged on this active area 1B. Referring to **FIG. 2**, the active area 1B is provided on its corner portion with a concave part, which is not rectangularly shaped. Such an active area 1B results from accumulation of subtle divergence of actual values from design values in various fabrication steps for forming an insulating film 7, source/drain regions SDA and SDB and the like, and it is not easy to thoroughly this problem. However, a gate end cap of the gate electrode **30** is set at the length  $x+\alpha$  as hereinabove described, whereby

an end portion of the gate electrode **30** completely reaches an upper portion of the insulating film **7** for preventing partial reduction of the gate length even if an unnecessary active area exists in the concave part of the active area **1B**. Thus, the source/drain regions SDA and SDB are prevented from occurrence of current leakage therebetween, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in **FIG. 1** is obtained, as a matter of course.

#### [0088] <A-3. Modification 1>

**[0089]** In the active area 1B shown in **FIG. 2**, an unnecessary active area merely partially exists in the concave part. If the corner portion is provided with no concave part but obliquely notched, however, no effect may be attained even if the length of the gate end cap is increased as described above. In this case, the length of the gate end cap is further increased as described below.

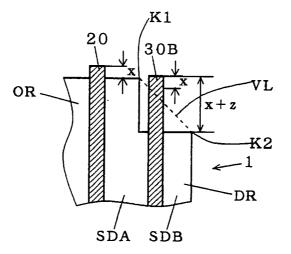

**[0090] FIG. 3** shows a part of an active area **1** in the layout design phase of a modification 1 of the semiconductor device according to the embodiment 1 of the present invention and gate electrodes **20** and **30**A arranged on this active area **1**. Referring to **FIG. 3**, the gate electrode **30**A is arranged on a depressed region DR having an edge portion which is located on a low position due to a concave part, and the gate electrode **20** is arranged on an ordinary region (region other than the depressed region) OR having an end portion projecting beyond the depressed region DR.

[0091] While a gate end cap of the gate electrode 20 has a length x, that of the gate electrode 30A has a length x+w. The additional length w is set to be equal to the depression length of the concave part, and endmost portions of the gate electrodes 20 and 30A are flush with each other as a result.

[0092] FIG. 4 shows a part of an active area 1A of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30A arranged on this active area 1A. Referring to FIG. 4, the active area 1A has a corner portion which is provided with no concave part but obliquely notched. A gate end cap of the gate electrode 30A is set at the length x+w as described above on the active area 1A having such a shape, whereby an end portion of the gate electrode 30A completely reaches an upper portion of an insulating film 7. Thus, source/drain regions SDA and SDB provided on both sides of the gate electrode 30A are electrically isolated from each other and prevented from shorting, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in FIG. 3 is obtained, as a matter of course.

[0093] <A-4. Modification 2>

**[0094]** While the length of the gate end cap of the gate electrode of the concave part is increased by the value equal to the depression length of the concave part in the aforementioned modification 1, the length of such a gate end cap may alternatively be decided as described below, in order to minimize the length.

**[0095] FIG. 5** shows a part of an active area 1 in the layout design phase of a modification 2 of the semiconductor device according to the embodiment 1 of the present inven-

tion and gate electrodes 20 and 30B arranged on this active area 1. Referring to FIG. 5, the gate electrode 30B is arranged on a depressed region DR having an edge portion which is located on a low position due to a concave part, while the gate electrode 20 is arranged on an ordinary region (region other than the depressed region) OR having an end portion projecting beyond the depressed region DR.

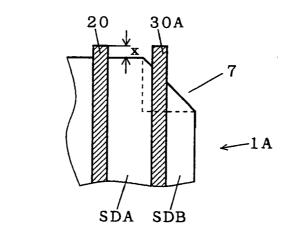

[0096] While a gate end cap of the gate electrode 20 has a length x, that of the gate electrode 30B has a length x+z. On the assumption that the corner portion of the active area 1 is provided with no concave part but obliquely notched, the additional length z is equalized with the length of a portion between an edge portion of the depressed region DR and a position where a virtual line VL connecting two convex corner portions K1 and K2 of the concave part of the active area 1 intersects with the gate electrode 30B, i.e., a position where the virtual line VL intersects with a longer side closer to the ordinary region OR in two longer sides of the gate end cap. The position where the virtual line VL intersects with the gate electrode 30B may be defined as that where the virtual line VL intersects with the center line of the gate electrode 30B or with a longer side closer to the ordinary region OR in two longer sides of the gate electrode 30B.

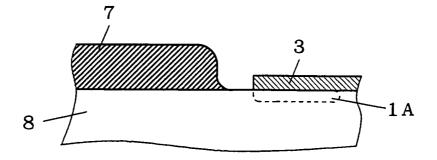

[0097] FIG. 6 shows a part of an active area 1A of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30B arranged on this active area 1A. Referring to FIG. 6, the active area 1A has a corner portion which is provided with no concave part but obliquely notched. A gate end cap of the gate electrode 30B is set at the length x+z as described above on the active area 1A having such a shape, whereby an end portion of the gate electrode 30B completely reaches an upper portion of an insulating film 7. Thus, source/drain regions SDA and SDB provided on both sides of the gate electrode 30B are electrically isolated from each other and prevented from shorting, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in FIG. 5 is obtained, as a matter of course.

**[0098]** In each of the semiconductor devices according to the embodiment 1 of the present invention and the modifications 1 and 2, only a single gate electrode is arranged on the depressed region and the length of its gate end cap is increased. If a plurality of gate electrodes are arranged on such a depressed region, the gate end cap of only the innermost gate electrode must be increased in length.

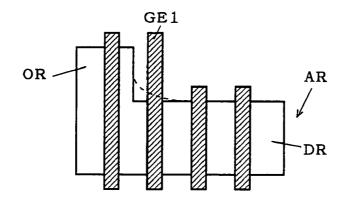

**[0099] FIG. 7** shows such a structure. Referring to **FIG.** 7, an active area AR has such a wide depressed region DR that a plurality of gate electrodes are arranged thereon. In this case, the length of a gate end cap is increased only in a gate electrode GE1 which is most approximate to an ordinary region OR. Since an unnecessary active area is generally formed in the vicinity of a side wall of a concave part as shown by a broken line, and hence the present invention is sufficiently applied to a gate electrode which is in the vicinity of the side wall.

#### B. Embodiment 2

#### [0100] <B-1. Device Structure>

[0101] FIG. 8 illustrates a part of an active area 1 in the layout design phase of a semiconductor device according to an embodiment 2 of the present invention and gate electrodes 20 and 30C arranged on this active area 1. Referring to FIG. 8, the active area 1 is provided with a concave part on its corner portion in a shape along a plan view. The gate electrode 30C is arranged on a depressed region DR having an edge portion which is located on a low position due to the concave part, and the gate electrode 20 is arranged on an ordinary region (region other than the depressed region) OR having an edge portion projecting beyond the depressed region DR. An insulating film 7 encloses the active area 1.

[0102] A gate end cap of the gate electrode 30C has a bent portion BP which is bent at an angle of about 90°, to extend oppositely to the ordinary region OR. This gate electrode 30C is so arranged as to maintain the distance between the bent portion BP and a horizontal edge portion (first edge portion) of the depressed region DR at a prescribed length s. The prescribed length s may be so set that the gate end cap is slightly in contact with or not in contact with the depressed region DR in plan view. The length of the bent portion BP may be substantially equal to the length x of a gate end cap of the gate electrode 20 arranged on the ordinary region OR.

[0103] <B-2. Characteristic Function/Effect>

[0104] FIG. 9 shows a part of an active area 1B of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30C arranged on this active area 1B. Referring to FIG. 9, the active area 1B is provided on its corner portion with a concave part, which is not rectangularly shaped. A gate end cap of the gate electrode 30C is bent at an angle of about 90° oppositely to an ordinary region OR as described above on the active area 1B having such a shape, whereby an end portion of the gate electrode 30C completely reaches an upper portion of an insulating film 7 even if an unnecessary active area exists in the concave part of the active area 1B, thereby preventing partial reduction of the gate length. Thus, source/drain regions SDA and SDB provided on both sides of the gate electrode 30B are electrically isolated from each other and prevented from shorting, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in FIG. 8 is obtained, as a matter of course.

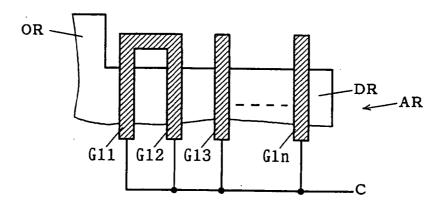

[0105] <B-3. Modification 1>

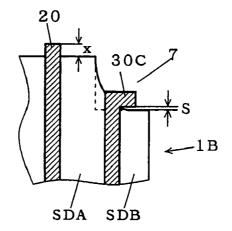

**[0106]** In the active area 1B shown in **FIG. 9**, an unnecessary active area merely partially exists in the concave part. If the unnecessary active area has a large area or the corner portion is provided with no concave part but obliquely notched, however, no effect may be attained by bending the gate end cap at an angle of about  $90^{\circ}$  oppositely to the ordinary region so that the bent portion BP has a length substantially equal to the length x of the gate end cap of the gate electrode arranged on the ordinary region. In this case, the length of such a bent portion is further increased as described below.

**[0107] FIG. 10** illustrates a part of an active area 1 in the layout design phase of a modification 1 of the semiconductor

device according to the embodiment 2 of the present invention and gate electrodes 20 and 30D arranged on this active area 1. Referring to FIG. 10, the gate electrode 30D having a bent portion BD which is bent at an angle of about 90° oppositely to an ordinary region is so arranged on a depressed region DR that a forward end portion of the bent portion BD projects beyond a vertical edge portion (second edge portion) of the depressed region DR. The forward end portion of the bent portion BD of the gate electrode 30D projects beyond the vertical edge portion of the depressed region DR by a length substantially equal to the length x of a gate end cap of the gate electrode 20 arranged on the ordinary region.

[0108] FIG. 11 shows a part of an active area 1C of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30D arranged on this active area 1C. Referring to FIG. 11, the active area 1C is provided on its corner portion with a concave part, which is not rectangularly shaped. While an unnecessary portion of the active area 1C has a larger area as compared with that of the active area 1B shown in FIG. 9, the gate electrode 30D is so formed that a forward end portion of its gate end cap projects beyond a vertical end portion of a depressed region DR by a length substantially equal to the length x, thereby preventing partial reduction of the gate length. Thus, source/drain regions SDA and SDB are prevented from occurrence of current leakage therebetween, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in FIG. 10 is obtained, as a matter of course.

**[0109]** <B-4. Modification 2>

**[0110]** While the forward end portion having the bent portion which is bent oppositely to the ordinary region projects beyond the vertical edge portion of the depressed region by a length substantially equal to the length x of a gate end cap of the gate electrode arranged on the ordinary region in the aforementioned modification 1, the length of such a gate end cap may be decided in the following manner, in order to minimize the same.

**[0111] FIG. 12** illustrates a part of an active area 1 in the layout design phase of a modification 2 of the semiconductor device according to the embodiment 2 of the present invention and gate electrodes 20 and 30E arranged on this active area 1. Referring to **FIG. 12**, the gate electrode **30**E having a bent portion BD which is bent at an angle of about 90° oppositely to an ordinary region OR is formed on a depressed region DR.

[0112] The gate electrode 30E is so arranged as to maintain the distance between the bent portion BD and a horizontal edge portion (first edge portion) of the depressed region DR at a prescribed length m. On the assumption that a corner portion of the active area 1 is provided with no concave part but obliquely notched, the gate electrode 30E is so formed as to project beyond a position where a virtual line VL connecting two convex corner portions K1 and K2 of the concave part of the active area 1 intersects with the bent portion BD, i.e., a position where the virtual line VL intersects with a longer side closer to the ordinary region OR in two longer sides of the bent portion BD, by a length substantially equal to the length x. Therefore, the length of

the gate end cap can be reduced as compared with that of the gate electrode **30**D described with reference to **FIG. 10**.

[0113] The position where the virtual line VL intersects with the gate electrode 30E may be defined as that where the virtual line VL intersects with the center line of the gate electrode 30E or with a longer side farther from the depressed region DR in two longer sides of the gate electrode 30E. A length m may be set in response to the virtual line VL. Namely, the length m may be reduced in case of setting the virtual line VL as connecting two points inside the two convex corner portions K1 and K2 of the concave part.

[0114] FIG. 13 shows a part of an active area 1A of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30E arranged on this active area 1A. Referring to FIG. 13, the active area 1A has a corner portion which is provided with no concave part but obliquely notched. A gate end cap of the gate electrode 30E is so formed as to project beyond the notched part of the active area 1A by a length substantially equal to the length x on the active area 1A having such a shape, whereby an end portion of the gate electrode 30A completely reaches an upper portion of an insulating film 7. Thus, source/drain regions SDA and SDB provided on both sides of the gate electrode 30E are electrically isolated from each other and prevented from shorting, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in FIG. 12 is obtained, as a matter of course.

[0115] <B-5. Modification 3>

**[0116]** While the gate electrode has the bent portion which is bent oppositely to the ordinary region in each of the aforementioned semiconductor devices according to the embodiment 2 and the modifications 1 and 2, the angle for bending the gate end cap is not restricted to  $90^{\circ}$ .

**[0117]** FIG. 14 illustrates a part of an active area 1 in the layout design phase of a modification 3 of the semiconductor device according to the embodiment 2 of the present invention and gate electrodes 20 and 30F arranged on this active area 1. Referring to FIG. 14, the gate electrode 30F has a bent portion which is bent at an angle  $\beta$  (0°< $\beta$ <90°) smaller than 90° in a direction separating from an ordinary region OR.

**[0118]** On the assumption that a corner portion of the active area 1 is provided with no concave part but obliquely notched, the gate electrode **30**F is bent at the angle  $\beta$  about a position where a virtual line VL connecting two convex corner portions K1 and K2 of the concave part of the active area 1 intersects with the bent portion, i.e., a position where the virtual line VL intersects with a longer side closer to a depressed region DR in two longer sides of the bent portion. The bent portion is so formed as to project beyond the bend center (the intersection between the virtual line VL and the bent portion) by a length substantially equal to the length x.

**[0119]** The position where the virtual line VL intersects with the gate electrode **30**F may be defined as that where the virtual line VL intersects with the center line of the gate electrode **30**F or with a longer side farther from the depressed region DR in two longer sides of the gate electrode **30**F.

[0120] FIG. 15 shows a part of an active area 1A of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30F arranged on this active area 1A. Referring to FIG. 15, the active area 1A has a corner portion which is provided with no concave part but obliquely notched. A gate end cap of the gate electrode 30F is so formed as to project beyond the notched part of the active area 1A by a length substantially equal to the length x on the active area 1A having such a shape, whereby an end portion of the gate electrode 30F completely reaches an upper portion of an insulating film 7. Thus, source/drain regions SDA and SDB provided on both sides of the gate electrode 30F are electrically isolated from each other and prevented from shorting, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in FIG. 14 is obtained, as a matter of course.

#### C. Embodiment 3

[0121] <C-1. Device Structure>

**[0122]** While only a single gate electrode is positioned on the concave part of the active area in each of the aforementioned semiconductor devices according to the embodiments 1 and 2 of the present invention, a plurality of gate electrodes may be formed on a concave part of an active area.

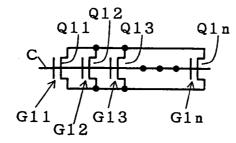

**[0123] FIG. 16** illustrates NMOS transistors Q10 and Q20 which are connected in parallel with each other. Referring to **FIG. 16**, drain electrodes as well as source electrodes of the NMOS transistors Q10 and Q20 are connected in common, while gate electrodes **301** and **302** thereof are connected to a common input part C.

**[0124] FIG. 17** shows a part of an active area **1** in the layout design phase of a semiconductor device according to an embodiment 3 of the present invention and gate electrodes **20** and **30**G arranged on this active area **1**. Referring to **FIG. 17**, the active area **1** has a concave part on its corner portion in a shape along a plan view. An insulating film **7** encloses the active area **1**. The gate electrode **30**G is arranged on a depressed region DR having an edge portion which is located on a low position due to the concave part, and the gate electrode **20** is arranged on an ordinary region (region other than the depressed region) OR having an end portion projecting beyond the depressed region DR.

**[0125]** The gate electrode **30**G is formed by gate electrodes **301** and **302** arranged on this depressed region DR successively from a side closer to the ordinary region OR and a connecting member **303** connecting gate end caps thereof with each other, to be U-shaped along a plan view. The gate electrode **30**G is so arranged as to maintain the distance between the connecting member **303** and a horizontal edge portion of the depressed region DR at a prescribed length m (m: at least zero).

[0126] <C-2. Characteristic Function/Effect>

[0127] FIG. 18 shows a part of an active area 1D of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30G arranged on this active area 1D. Referring to FIG. 18, the active area 1D is provided on its corner portion with a concave part, which is not rectangularly shaped. A gate end cap of the gate electrode 30G connects those of gate electrodes 301 and 302

with each other as described above on the active area 1D having such a shape. Even if an unnecessary active area exists in the concave part of the active area 1D, therefore, the gate electrodes **301** and **302** and a connecting member **303** enclose a source/drain region SDB for isolating the same from a source/drain region SDA located in the exterior of the gate electrodes **301** and **302** and preventing the same from shorting, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but the concave part is rectangularly shaped, a semiconductor device similar to that shown in **FIG. 17** is obtained, as a matter of course.

#### [0128] <C-3. Modification>

**[0129]** While two gate electrodes, i.e., two transistors are formed on the concave part of the active area in the aforementioned semiconductor device according to the embodiment 3 of the present invention, two or more gate electrodes may be formed on a concave part of such an active area.

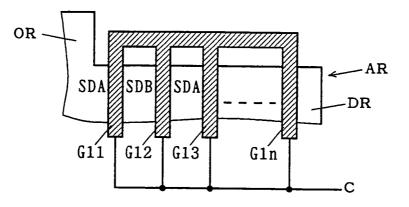

**[0130]** FIG. 19 shows NMOS transistors Q11 to Q1*n* which are connected in parallel with each other in a modification of the semiconductor device according to the embodiment 3 of the present invention. Referring to FIG. 19, drain electrodes as well as source electrodes of the NMOS transistors Q11 to Q1*n* are connected in common, while gate electrodes G11 to G1*n* of the NMOS transistors Q11 to Q1*n* are connected to a common input part C.

**[0131]** FIG. 20 shows such a parallel connected body of the NMOS transistors Q11 to Q1*n*, which is formed on a depressed region DR. Referring to FIG. 20, the gate electrodes G11 to G1*n* are arranged on a concave part of an active area AR successively from a side closer to an ordinary region OR. All gate end caps of the gate electrodes G11 to G1*n* are connected in common.

**[0132]** When a plurality of gate electrodes arranged on a depressed region are electrically connected in common and gate end caps thereof are also connected in common, the gate electrodes enclose source/drain regions for electrically isolating the same from each other and preventing adjacent ones of the source/drain regions from shorting even if an unnecessary region is present in a concave part of an active area over a wide range, whereby functions of MOS transistors can be maintained.

**[0133]** When two or more gate electrodes are formed on a depressed region, not all gate end caps of the gate electrodes may be connected in common, dissimilarly to the above.

**[0134]** As shown in **FIG. 21**, only gate end caps of a gate electrode G11 which is most approximate to an ordinary region OR and a gate electrode G12 adjacent thereto may be connected in common. The present invention is sufficiently applied to gate electrodes which are approximate to an ordinary region, since an unnecessary active area is generally formed in the vicinity of the ordinary region.

#### D. Embodiment 4

#### [0135] <D-1. Device Structure>

**[0136]** While the corner portion of the active area is provided with the concave part in each of the aforementioned semiconductor devices according to the embodiments

1 to 3 of the present invention, such a concave part may be formed on a portion other than the corner portion.

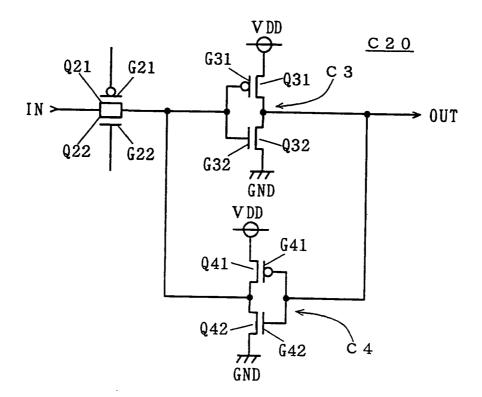

[0137] In relation to a concave part formed on a portion other than the corner portion of an active area, FIG. 22 shows a ratio latch circuit C20, for example. Referring to FIG. 22, an input end of an inverter circuit C3 which is formed by a PMOS transistor Q31 and an NMOS transistor Q32 is connected to an output end of a transmission gate which is formed by a PMOS transistor Q21 and an NMOS transistor Q22, and an output end of the inverter circuit C3 defines that of the ratio latch circuit C20. An input end of an invertor circuit C4 which is formed by a PMOS transistor Q41 and an NMOS transistor Q42 is connected to the output end of the inverter circuit C3, and an output end of the inverter circuit C4 is connected to the input end of the inverter circuit C3. The PMOS and NOS transistors Q21, Q22, Q31, Q32, Q41 and Q42 have gate electrodes G21, G22, G31, G32, G41 and G42 respectively.

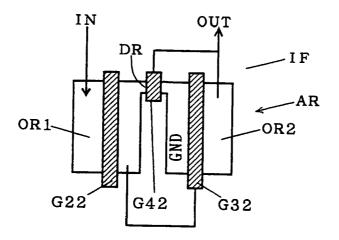

[0138] FIG. 23 is a layout diagram of the NMOS transistors Q22, Q32 and Q42 of the ratio latch circuit C20 having the aforementioned structure.

**[0139]** Referring to **FIG. 23**, an active area AR has a concave part on its center in a shape along a plan view. The gate electrode G42 is arranged on a depressed region DR having a span which is reduced due to the concave part, and the gate electrodes G22 and G23 are arranged on ordinary regions (regions other than the depressed region DR) OR1 and OR2, which are larger in span than the depressed region DR. An insulating film IF encloses the active area AR.

**[0140]** While an unnecessary active area may be formed on a concave part provided on a portion other than the corner portion of an active area, functional loss of a MOS transistor resulting from the presence of the unnecessary active area can be prevented by the following structure:

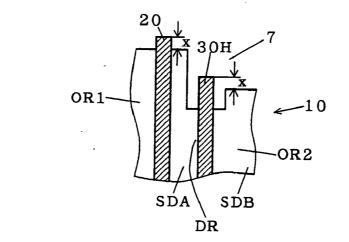

[0141] FIG. 24 shows a part of an active area 10 in the layout design phase of a modification of the semiconductor device according to the embodiment 4 of the present invention and gate electrodes 20 and 30H arranged on this active area 10. Referring to FIG. 24, the active area 10 has a concave part in a portion other than the corner portion in a shape along a plan view. An insulating film 7 encloses the active area 10. In this case, the concave part may alternatively be referred to as a dent part.

**[0142]** The gate electrode **30**H is arranged on a depressed region DR having an edge portion which is located on a low position due to the concave part. Ordinary regions (regions other than the depressed region) OR1 and OR2 (first and second ordinary regions) having edge portions projecting beyond the depressed region DR are provided on both sides of the depressed region DR. The gate electrode **20** is arranged on the ordinary region OR1. A gate end cap of the gate electrode **20** has a length x.

[0143] An end portion of the ordinary region OR2 is located on a position depressed from that of an end portion of the ordinary region OR1, to result in difference between the depression lengths of the ordinary regions OR1 and OR2. A gate end cap of the gate electrode 30H is formed to project beyond an edge portion of the ordinary region OR2 by a length substantially equal to the length x of the gate end cap of the gate electrode 20 arranged on the ordinary region OR1.

#### [0144] <D-2. Characteristic Function/Effect>

[0145] FIG. 25 shows a part of an active area 10A of a semiconductor device actually fabricated on the basis of such design values and gate electrodes 20 and 30H arranged on this active area 10A. Referring to FIG. 25, the active area 10A has a concave part which is not rectangularly shaped. A gate end cap of the gate electrode 30H is formed to project beyond an edge portion of an ordinary region OR2 by a length substantially equal to the length x of a gate end cap of the gate electrode 20 arranged on an ordinary region OR1 in the active area 10A having such a shape, whereby an end portion of the gate electrode 30H completely reaches an upper portion of an insulating film 7 even if an unnecessary active area exists in the concave part of the active area 10A, thereby preventing the gate electrode 30H from partial reduction of its gate length. Thus, occurrence of current leakage between source/drain regions SDA and SDB can be prevented, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process but no unnecessary region exists in the concave part, a semiconductor device similar to that shown in FIG. 24 is obtained, as a matter of course.

[0146] <D-3. Modification 1>

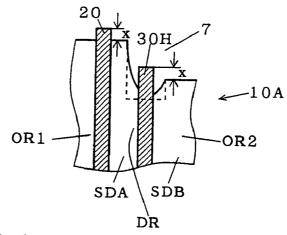

**[0147]** While the gate end cap of the gate electrode **30**H is formed to project beyond the edge portion of the ordinary region OR**2** by the length substantially equal to the length x of the gate end cap of the gate electrode **20** arranged on the ordinary region OR**1** as hereinabove described in the aforementioned semiconductor device according to the embodiment 4, the length of such a gate end cap may alternatively set in the following manner:

[0148] FIG. 26 shows a part of an active area 10 in the layout design phase of a modification 1 of the semiconductor device according to the embodiment 4 of the present invention and gate electrodes 20 and 30I arranged on this active area 10. Referring to FIG. 26, the gate electrode 30I is arranged on a depressed region DR, and the gate electrode 20 is arranged on an ordinary region OR1.

[0149] A gate end cap of the gate electrode 20 has a length x, while a gate end cap of the gate electrode 30I is so formed as to project beyond a position where a virtual line VL connecting two convex corner portions K1 and K2 of the concave part of the active area 10 intersects with the gate electrode 30I, i.e., a position where the virtual line VL intersects with a longer side closer to the ordinary region OR1 in two longer sides of the gate end cap by a length substantially equal to the length x.

**[0150]** The position where the virtual line VL intersects with the gate electrode **30**I may be defined as that where the virtual line VL intersects with the center line of the gate electrode **30**I or with a longer side closer to the ordinary region OR**2** in two longer sides of the gate electrode **30**I.

**[0151] FIG. 27** shows a part of an active area **10**A of a semiconductor device actually fabricated on the basis of such design values and a gate electrode **30**I arranged on this active area **10**A. Referring to **FIG. 27**, the active area **10**A has a concave part which is not rectangularly shaped. A gate end cap of the gate electrode **30**I is formed to project beyond an intersection between a virtual line VL and the gate electrode **30**I by a length substantially equal to a length x, whereby an end portion of the gate electrode **30**I completely

reaches an upper portion of an insulating film 7 even if an unnecessary active area exists in the concave part of the active area 10A, thereby preventing the gate electrode 30I from partial reduction of its gate length. Thus, occurrence of current leakage between source/drain regions SDA and SDB can be prevented, whereby the function of the MOS transistor can be maintained. If no problem arises in the fabrication process and no unnecessary region exists in the concave part, a semiconductor device similar to that shown in **FIG. 26** is obtained, as a matter of course.

[0152] <D-4. Modification 2>

**[0153]** While the ordinary regions OR1 and OR2 are different in depression length from each other in the aforementioned semiconductor device according to the embodiment 4 of the present invention, the length of a gate end cap may be set in the following manner if depression lengths on right and left sides of a concave part are identical to each other.

[0154] FIG. 28 shows a part of an active area 100 in the layout design phase of a modification 2 of the semiconductor device according to the embodiment 4 of the present invention and gate electrodes 20 and 30J arranged on this active area 100. The active area 100 shown in FIG. 28 is provided with depressed portions having the same length on right and left sides of a concave part. The gate electrode 30J is arranged on a depressed region DR having an edge portion which is located on a low position due to the concave part, and the gate electrode 20 is arranged on an ordinary region OR1.

**[0155]** A gate end cap of the gate electrode **30**J is so formed as to project beyond an edge portion of the depressed region DR by a length substantially equal to the length x of a gate end cap of the gate electrode **20** arranged on the ordinary region OR1. Even if the concave part is filled up with an unnecessary active area to disappear, source/drain regions SDA and SDB provided on both sides of the gate electrode **30**J are electrically isolated from each other and prevented from shorting due to the aforementioned structure, whereby the function of the MOS transistor can be maintained.

**[0156]** While the invention has been shown and described in detail, the following description is in all aspects illustrative and restrictive. It is therefore understood that numerous modifications and variations can be devised without departing from the scope of the invention.

#### We claim:

1. A semiconductor device comprising:

- an active area being provided with at least one MOS transistor; and

- an insulating film defining said active area, wherein

- said active area is set in a shape having a concave part in a shape along a plan view,

said active area is provided with:

- an ordinary region, and

- a depressed region having an edge portion being depressed beyond said ordinary region due to presence of said concave part,

said at least one MOS transistor includes:

- a plurality of MOS transistors being arranged on said depressed region and electrically connected in parallel with each other, and

- respective gate electrodes of said plurality of MOS transistors are arranged in parallel with each other and electrically connected in common,

- so that margin parts of at least a gate electrode being located most approximately to said ordinary region and

that adjacent to said gate electrode are connected with each other among said respective gate electrodes of said plurality of MOS transistors.

**2**. The semiconductor device in accordance with claim 1, wherein all margin parts of said respective gate electrodes of said plurality of MOS transistors are connected with each other.

\* \* \* \* \*