(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-363595

(P2004-363595A)

(43) 公開日 平成16年12月24日(2004.12.24)

(51) Int.Cl.<sup>7</sup>H01L 21/76

H01L 21/8242

H01L 27/108

F 1

H01L 21/76

H01L 27/10L

681D

テーマコード(参考)

5FO32

5FO83

審査請求 有 請求項の数 32 O L (全 15 頁)

(21) 出願番号 特願2004-159279 (P2004-159279)

(22) 出願日 平成16年5月28日 (2004.5.28)

(31) 優先権主張番号 10/250092

(32) 優先日 平成15年6月3日 (2003.6.3)

(33) 優先権主張国 米国(US)

(71) 出願人 3900009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESSES MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100086243

弁理士 坂口 博

(74) 代理人 100091568

弁理士 市位 嘉宏

(74) 代理人 100108501

弁理士 上野 剛史

最終頁に続く

(54) 【発明の名称】ポリシラザンをベースとする材料による高アスペクト比の分離構造体の充填

## (57) 【要約】

【課題】 分離構造体を形成する前に、少なくとも1つのp-n接合または異なる材料の界面を有するシリコン集積回路内の分離トレンチを充填するための方法を提供する。

【解決手段】 シラザンをベースとし、低い分子量を有するスピノン・オン材料を塗布するステップと、約450℃を超えない温度において酸素雰囲気内で、上記塗布した材料を予備ベーキングするステップと、H<sub>2</sub>O雰囲気内で450℃～800℃の範囲内の中間温度で加熱することにより上記材料の応力を変換するステップと、O<sub>2</sub>雰囲気内で高温で再び加熱し、その結果、プロセス・パラメータを変えることにより、調整することができる圧縮応力を有し、HDP技術により形成した酸化物誘電体に匹敵するエッティング速度を有するCMP研磨に十分耐える耐久性を有する最高1000℃まで安定な材料が得られるステップを含むプロセスによる、最高60までのアスペクト比を有する垂直FET(または、任意の前のレベルのp-n接合または異なる材料界面)を含む分離トレンチおよびキャバシタ・トレンチの充填。

**【特許請求の範囲】****【請求項 1】**

それに関連する温度許容度を有する一組の熱感知回路素子と一組の分離トレンチとを含む集積回路を形成するための方法であって、

シリコン基板を供給するステップと、

前記分離構造を形成する前に、ある温度許容度を有する少なくとも1つの回路素子を形成するステップと、

前記シリコン基板内に前記一組のトレンチをエッティングするステップと、

前記一組のトレンチを、シラザンを含むスピンドル・オン・トレンチ誘電体で充填するステップと、

約450°Cを超えない温度で前記基板を加熱するステップと、

約450°Cから約900°Cの範囲内の温度で、H<sub>2</sub>Oを含む雰囲気内で加熱することにより、前記トレンチ誘電体の応力を引張り応力から圧縮応力に変換するステップと、

800°Cを超える温度でO<sub>2</sub>を含む雰囲気内で加熱することにより前記基板をアニーリングするステップと、

前記集積回路を完成するステップとを含む方法。

**【請求項 2】**

前記応力変換ステップの時間および前記アニーリング・ステップの時間が、前記熱感知構成要素の温度許容度を超えないように関連づけられる、請求項1に記載の方法。

**【請求項 3】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、0.1~2G dyne/cm<sup>2</sup>の範囲内の圧縮応力を有し、約2未満のWERRを有するように関連づけられる、請求項1に記載の方法。

**【請求項 4】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、0.1~2G dyne/cm<sup>2</sup>の範囲内の圧縮応力を有し、約2未満のWERRを有するように関連づけられる、請求項2に記載の方法。

**【請求項 5】**

O<sub>2</sub>を含む雰囲気での前記基板の加熱ステップが、前記最終材料のWERRが、設計値にはほぼ等しくなるように調整された時間の間行われる、請求項2に記載の方法。

**【請求項 6】**

O<sub>2</sub>を含む雰囲気での前記基板の加熱ステップが、前記最終材料のWERRが、設計値にはほぼ等しくなるように調整された時間の間行われる、請求項3に記載の方法。

**【請求項 7】**

O<sub>2</sub>を含む雰囲気での前記基板の加熱ステップが、前記最終材料のWERRが設計値にはほぼ等しくなるように調整された時間の間行われる、請求項4に記載の方法。

**【請求項 8】**

前記トレンチが6より大きいアスペクト比を有し、

前記トレンチ誘電体が、O<sub>2</sub>雰囲気でのアニーリング・ステップの後でCMPにより平面化され、

水蒸気を含む雰囲気でのアニーリングが、平面化ステップの後で、前記トレンチの底部のところのトレンチ誘電体で、Si-N結合をSi-O結合に変換するのに十分な時間の間行われる、請求項1に記載の方法。

**【請求項 9】**

前記応力変換ステップの時間および前記アニーリング・ステップの時間が、熱感知構成要素の温度許容度を超えないように関連づけられる、請求項8に記載の方法。

**【請求項 10】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、0.1~2G dyne/cm<sup>2</sup>の範囲内の圧縮応力を有し、約2未満のWERRを有するように関連づけられる、請求項8に記載の方法。

10

20

30

40

50

**【請求項 1 1】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、 $0.1 \sim 2 \text{ G dyne/cm}^2$  の範囲内の圧縮応力を有し、約 2 未満の W E R R を有するように関連づけられる、請求項 9 に記載の方法。

**【請求項 1 2】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料の W E R R が設計値にほぼ等しくなるように調整された時間の間行われる、請求項 9 に記載の方法。

**【請求項 1 3】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料の W E R R が設計値にほぼ等しくなるように調整された時間の間行われる、請求項 10 に記載の方法。 10

**【請求項 1 4】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料の W E R R が設計値にほぼ等しくなるように調整された時間の間行われる、請求項 11 に記載の方法。

**【請求項 1 5】**

一組の回路素子と一組の分離トレンチとを含む集積回路を形成するための方法であって、シリコン基板を供給するステップと、

前記シリコン基板内に前記一組のトレンチをエッチングするステップと、

前記一組のトレンチを、シラザンを含むスピンドル・オン・トレンチ誘電体で充填するステップと、

約 450 を超えない温度で前記基板を加熱するステップと、 20

約 450 から約 900 の範囲内の温度で  $H_2O$  を含む雰囲気内で加熱することにより、前記トレンチ誘電体の応力を引張り応力から圧縮応力に変換するステップと、

800 を超える温度で  $O_2$  を含む雰囲気内で加熱することにより前記基板をアニーリングするステップと、

前記集積回路を完成するステップとを含む方法。

**【請求項 1 6】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、 $0.1 \sim 2 \text{ G dyne/cm}^2$  の範囲内の圧縮応力を有し、約 2 未満の W E R R を有するように関連づけられる、請求項 15 に記載の方法。

**【請求項 1 7】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料の W E R R が設計値より大きくならないように調整された時間の間行われる、請求項 16 に記載の方法。 30

**【請求項 1 8】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料の W E R R が設計値にほぼ等しくなるように調整された時間の間行われる、請求項 17 に記載の方法。

**【請求項 1 9】**

それに関連する温度許容度を有する一組の熱感知垂直トランジスタ D R A M セルと一組の分離トレンチとを含む集積回路を形成するための方法であって、

シリコン基板を供給するステップと、

前記分離構造体を形成する前に、ある温度許容度を有する少なくとも 1 つの垂直トランジスタ D R A M セルを形成するステップと、 40

前記シリコン基板内に前記一組のトレンチをエッチングするステップと、

前記一組のトレンチを、シラザンを含むスピンドル・オン・トレンチ誘電体で充填するステップと、

約 450 を超えない温度で前記基板を加熱するステップと、

約 450 から約 900 の範囲内の温度で、 $H_2O$  を含む雰囲気内で加熱することにより、前記トレンチ誘電体の前記応力を引張り応力から圧縮応力に変換するステップと、

800 を超える温度で  $O_2$  を含む雰囲気内で加熱することにより前記基板をアニーリングするステップと、

前記集積回路を完成するステップとを含む方法。

**【請求項 20】**

前記応力変換ステップの時間および前記アニーリング・ステップの時間が、前記垂直トランジスタDRAMセルの温度許容度を超えないように関連づけられる、請求項19に記載の方法。

**【請求項 21】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、 $0.1 \sim 2 \text{ G dyne/cm}^2$  の範囲内の圧縮応力を有し、約2未満のWERRを有するように関連づけられる、請求項19に記載の方法。

**【請求項 22】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、 $0.1 \sim 2 \text{ G dyne/cm}^2$  の範囲内の圧縮応力を有し、約2未満のWERRを有するように関連づけられる、請求項20に記載の方法。 10

**【請求項 23】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料のWERRが設計値にほぼ等しくなるように調整された時間の間行われる、請求項20に記載の方法。

**【請求項 24】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料のWERRが設計値にほぼ等しくなるように調整された時間の間行われる、請求項21に記載の方法。

**【請求項 25】**

$O_2$  を含む雰囲気内での前記基板の加熱ステップが、前記最終材料のWERRが設計値にほぼ等しくなるように調整された時間の間行われる、請求項22に記載の方法。 20

**【請求項 26】**

それに関連するある温度許容度を有する一組の熱感知回路素子と一組のシリコン基板内の分離トレンチとを有する集積回路であって、

前記一組のトレンチが、シラザンを含むスピンドル・オン・トレンチ誘電体で充填されていて、

前記基板が約450 を超えない温度で加熱されていて、

前記トレンチ誘電体の前記応力が、約450 ~ 900 の範囲内の温度で  $H_2O$  を含む雰囲気内で加熱することにより、引張り応力から圧縮応力に変換された圧縮応力であり、 30

前記基板が、800 を超えた温度で  $O_2$  を含む雰囲気内で加熱することによりアニーリングされている集積回路。

**【請求項 27】**

前記応力変換ステップの時間および前記アニーリング・ステップの時間が、前記熱感知構成要素の温度許容度を超えないように関連づけられた、請求項26に記載の回路。

**【請求項 28】**

応力変換の前記ステップおよびアニーリングの前記ステップが、結果として得られる材料が、 $0.1 \sim 2 \text{ G dyne/cm}^2$  の範囲内の圧縮応力を有し、約2未満のWERRを有するように関連づけられた、請求項26に記載の回路。

**【請求項 29】**

分離トレンチのサブセットがトランジスタを含むトランジスタ・エリアを囲み、

前記応力変換ステップの時間および温度が、誘電体トレンチ材料の前記応力が設計制限値より大きくならないようになっている、請求項26に記載の回路。 40

**【請求項 30】**

前記応力変換ステップの時間および温度が、前記誘電体トレンチ材料の前記応力が、設計値とほぼ等しくなるようになっている、請求項29に記載の回路。

**【請求項 31】**

前記応力変換ステップおよび前記アニーリング・ステップの時間および温度が、前記誘電体トレンチ材料の前記応力がHDP技術で堆積された酸化物の応力とほぼ等しくなるようになっている、請求項26に記載の回路。 50

**【請求項 3 2】**

前記応力変換ステップおよび前記アニーリング・ステップの時間および温度が、前記誘電体トレンチ材料の応力が、HDP技術で堆積された酸化物の応力とほぼ等しくなるようになっている、請求項29に記載の回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、集積回路の処理の際の高アスペクト比トレンチの充填に関する。

**【背景技術】****【0002】**

集積回路でグラウンド・ルール寸法が収縮するので、高アスペクト比トレンチの充填の問題が、通常、高度の処理の際に使用される浅溝分離プロセス(STI)で使用する分離トレンチの場合に特に問題になっている。

**【0003】**

従来、工業規格の充填材料およびプロセスは、高密度プラズマ(HDP)技術で堆積された酸化シリコン(SiO<sub>2</sub>)を使用してきた。優れた充填特性を有する高品質の材料を生成するので、この方法は広く採用されてきた。集積回路の設計者は、その構造規格および材料規格をこのプロセスおよび材料に適合させてきた。

**【0004】**

シリコンは圧電材料であるので、電界効果トランジスタ(FET)の特性は、トランジスタ本体上にかかる応力により影響を受ける。

**【0005】**

STIプロセスの際には、分離トレンチ材料は、トランジスタ本体の縁部と接触し、そのためその材料の応力が変化すると、トランジスタ本体の特性が、特にしきい値電圧およびトランジスタ・ドライブが影響を受ける。

**【0006】**

他の考慮事項として、集積回路を製造するために必要な長い時間がかかるプロセスは、現在高度に統合されている。すなわち、1つのプロセス・ステップの変更が、このステップの前後に行われるステップの結果に影響を与える恐れがあり、場合によっては、直前または直後ではなく、他のいくつかのステップ分だけ時間的に離れているステップに影響を与える恐れがある。

**【0007】**

それ故、あるプロセス・ステップを変更するのは、複数の次元または複数の要因を含む決定になる。新しいステップが、もっと丈夫で、もっと薄く、またはもっと密度の低い膜を製造したり、または時間を短縮するだけでは十分ではない。新しいステップは、プロセスの他の側面で利点を打ち消す欠点がないものでなければならない。

**【0008】**

分離トレンチ充填の特殊な場合には、本発明が解決する問題は、隙間を形成しないで高アスペクト比の分離トレンチを充填するという問題である。

**【0009】**

HDPプロセスを使用すると、通常、非整合堆積プロファイルができるが、大部分の整合堆積プロセスの場合のように、高アスペクト比のトレンチを充填すると、隙間(void)および/または継目(seam)ができることが分かっている。その理由は、材料が深いトレンチまたはアパートチャの上面に堆積し、最終的にピンチオフ(pinchoff)、頂部の開口部を塞ぎ、その後で材料がトレンチの底部に入り込むのを妨害するからである。このHDP技術は、4より大きいアスペクト比を有する構造体を充填する際に大きな問題を抱えている。

**【0010】**

分離構造体の頂部から塞いでいる材料を除去するために、主要な集積回路製造業者が使用する分離トレンチの充填の複雑なシーケンスは、下記の堆積およびエッチング・サイク

10

20

30

40

50

ルを含む。

【0011】

第1の堆積

第1の湿式エッティング（頂部上の塞いでいる材料を除去するため）

第2の堆積

第2の湿式エッティング

第3の堆積

エッティング（アパー・チャの過度の充填）

さらに、この処理は、乾式エッティングの厚さの低減およびその後で行われる化学的機械的研磨（CMP）を含むことができる。

10

【0012】

これは明らかにコストの高いプロセスであり、等価の充填材料を製造するもっとステップの数が少なく、コストの安いプロセスを開発することは非常に望ましいことである。

【0013】

すでに説明したように、新しいプロセスを導入するための決定の際の本質的な考慮事項は、例えば、より安いコストのようなその利点がその欠点を十分補えるかどうかということである。より詳細に説明すると、プロセスを大きく変えなくても、そのプロセスの密度、エッティング抵抗および応力が、HDP酸化物の特性に十分近いことである。

【0014】

少なくとも1つのp-n接合、またはそれに関連する温度許容度（thermal budget）（素子が受ける時間および温度に対する制限を意味する）を有する他の構造が、分離構造体が形成される前にチップ上にすでに形成されている場合には、もう1つの重要な問題は分離構造体の温度許容度である。任意の異なる材料（例えば、曲げシリコンを生成するためのSi/SiGe界面など）に対しても同じことが言える。このような接合または異なる材料の界面（まとめて、温度許容度を有する回路素子と呼ぶ）が分離構造体の前に形成された場合には、分離温度許容度が変化（増大）すると、ドーピング剤の内部拡散（または材料の内部拡散）が起こり、デバイスが劣化する。一般的に、材料拡散中の何らかの変化、およびドーピング剤の濃度のプロファイルの変化が、デバイスの性能を劣化させることが十分考えられる。

【0015】

適例としては、Asの外部への拡散が2つの埋め込みストラップ接点の間を移動するのに十分長い時間継続した場合には、2つの隣接するキャパシタが相互にクロストークを起こす垂直トランジスタDRAM/eDRAMである。深溝キャパシタは、分離構造体の前に形成されるので、過度のAsの外部への拡散を防止するために、分離処理の温度許容度は深溝キャパシタの温度許容度を超えてはならない。

30

【0016】

スピニ・オン・ガラス（SOG）またはスピニ・オン誘電体（SOD）と呼ばれる材料上のスピニは、優れた充填特性を有することが分かっている。

【0017】

また、これらの材料の他の特性は、HDP酸化物（HDPとも呼ばれる）の特性よりも遙かに劣っていることも分かっている。

【0018】

例えば、スピニ・オン・ガラスは、引張り応力、高い湿式エッティング速度を有し、熱的に不安定である。

【0019】

優れた充填特性を有するポリシラザンと呼ばれる材料についてある程度の研究が行われている。この材料は、[SiNR1R2NR3]<sub>n</sub>という構造式を有する。ここで、R1、R2およびR3は、無機ポリシラザンの場合には、すべて水素であり、有機ポリシラザンの場合には、アルキル、アリールまたはアルコキシル有機基である。便宜上、ポリシラザンを短縮してシラザンと呼ぶことにする。

40

50

**【 0 0 2 0 】**

この材料は、1,000～10,000の分子量を有する。この材料は、スピニ・オン・ステップ用の溶媒に溶かした溶液として塗布される。この溶媒は、予備ベーキング・ステップで比較的低い温度（約350未満）で蒸発させられ、この材料は種々の雰囲気内で加熱により硬化される。

**【 0 0 2 1 】**

Samsungは、金属の第1のレベルの下の中間誘電体膜を含むシラザンの種々の用途について研究を行った（英国特許G B 2 3 6 1 9 3 7号）。この研究において、推薦された膜は、900～1000の範囲の温度で水蒸気中でアニールされる。この参照文献は、結果として得られる応力またはCMPを考慮しないで、予備ベーキングおよび高温スチーム（水蒸気を含む）ベーキングという2つのステップからなるプロセスを使用する。平面化はスピニ・オン・プロセスだけで行った。

10

**【 0 0 2 2 】**

Samsungグループによるもう1つの参考文献である、I E E E 2 0 0 2 のV L S I技術に関するI E E Eシンポジウムの技術論文のダイジェスト132、133ページ（0-7803-7312-X/02）掲載の「0.1ミクロン以下のデバイス用のP-SOGを使用する隙間のない低応力の浅溝分離技術」（Void-Free and Low Stress Shallow Trench Isolation Technology using P-SOG for sub-0.1um Device）は、（先に湿式エッティングにより凹部を形成し）その後でHDP酸化物キャップを形成し、HDP酸化物のCMPを行う、700で酸化雰囲気内でアニーリングを行うシラザン・プロセスを開示している。

20

**【 0 0 2 3 】**

Samsungグループによるもう1つの参考文献である、2002年6月13日付けの米国特許出願番号U S 2 0 0 2 / 0 0 7 2 2 4 6 A 1号、および「60nmを超えるDRAMおよび他のデバイス用の新しいSOGを使用する非常に製造し易い低温度許容度の隙間と水蒸気を含まない前金属誘電体プロセス」（A Highly Manufacturable, Low Thermal Budget, Void and Seam free Pre-Metals Dielectric Process Using New SOG for beyond 60nm DRAM and Other Devices）（0-7803-7052-X/01）2001 I E E Eは、金属の第1のレベルの下に中間誘電体を形成するための3つのステップからなるプロセスを開示している。このプロセスの場合には、第1のベーキングは、350～500の範囲内の温度で行われる。アニーリング・プロセスは、600～1200の広い温度範囲で、好適には、酸化雰囲気内で行われる。

30

**【 0 0 2 4 】**

これらの参考文献は、ベーキング・ステップ（500未満）とアニーリング・ステップとの間に行われるCMPプロセスの使用を教示している。

40

**【 0 0 2 5 】**

上記参考文献は、半導体プロセスの統合は、用途に大きく依存することを示している。このプロセスは、応力がそのためにトランジスタが設計される応力でない場合には、または構造体の他の部分を除去するために主として設計されたエッティング・ステップで除去される膜のエッティングがあまりに高速であまりに大量である場合には、または、非常に重要であり変更することができない以降の高温ステップ中に膜が破損した場合には、絶縁を行う膜を形成するだけでは十分でない。分離誘電体のアニーリングが、すべての前に存在するp-n構造およびチップ上の界面をシフトしないことも重要である。

**【 0 0 2 6 】**

十分に分離するための基本的なジョブを実行し、工業規格HDP酸化物の応力およびエッティング抵抗に近い応力およびエッティング抵抗を有する分離トレンチ充填プロセスを発見するための努力が引き続き行われてきた。

【特許文献1】英国特許G B 2 3 6 1 9 3 7号

【特許文献2】米国特許出願番号U S 2 0 0 2 / 0 0 7 2 2 4 6 A 1号

【非特許文献1】I E E E 2 0 0 2 のV L S I技術に関するI E E Eシンポジウムの技術

50

論文のダイジェスト 132、133ページ(0-7803-7312-X/02)掲載の「0.1ミクロン以下のデバイス用のP-SOGを使用する隙間のない低応力の浅いトレンチ隔離技術」(Void-Free and Low Stress Shallow Trench Isolation Technology using P-SOG for sub-0.1um Device)

【非特許文献2】「60nmを超えるDRAMおよび他のデバイス用の新しいSOGを使用する非常に製造し易い低熱予算の隙間と水蒸気を含まない前金属誘電体プロセス」(A Highly Manufacturable, Low Thermal Budget, Void and Seam free Pre-Metals Dielectric Process Using New SOG for beyond 60nm DRAM and Other Devices)(0-7803-7052-X/01)2001 IEEE

10

【発明の開示】

【発明が解決しようとする課題】

【0027】

本発明は、分離構造体を形成する前に、少なくとも1つのp-n接合または異なる材料の界面を有するシリコン集積回路内の分離トレンチを充填するための方法に関する。

【課題を解決するための手段】

【0028】

本発明のある態様は、前のレベル接合の温度許容度制限内の圧縮応力を有する隙間のない熱的に安定した材料の製造である。

【0029】

本発明のある態様は、材料の応力を引張り応力から圧縮応力に変換する変換ステップである。

【0030】

本発明の別の態様は、後でアニーリングが乾燥した雰囲気内で行われる応力変換ステップである。

【0031】

本発明の別の態様は、後でアニーリングが乾燥した雰囲気内で行われる水蒸気雰囲気内での第1の加熱ステップである。

【0032】

本発明の別の態様は、最終材料の応力および湿式エッティング速度を適合するための、許可されたすべてのデバイス温度許容度およびアニーリング・ステップを関連づけるための機能である。

【発明を実施するための最良の形態】

【0033】

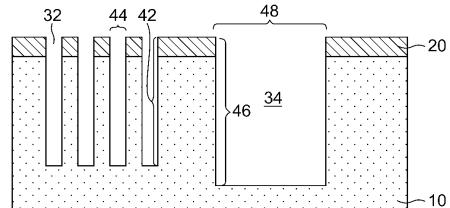

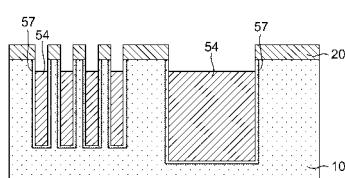

図1～図3は、SOD用途での基本シーケンスである。これらの図においては、パッド窒化物/酸化物20を有するシリコン基板10は、例えば、反応性イオン・エッティングのような任意の便利なプロセスによりその中にエッティングされた一組のアパートチャを有する。2つのサイズのアパートチャが示してあるが、それは実際のウェーハが、アパートチャ間に種々の間隔、種々のアパートチャの幅、および種々の深さを有することができるることを示すためである。このような違いは、例えば、パターン密度に依存する場合がある1回のエッティング・プロセスの変動によるものであり、または2つの異なるプロセス中に形成されたアパートチャを同時に充填したことによる場合がある。

【0034】

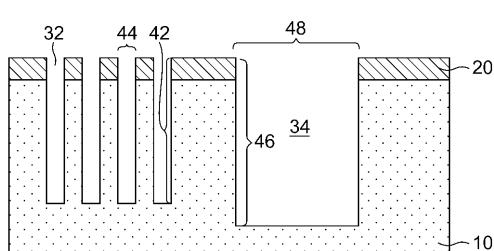

図1の右側では、アパートチャ34は、幅48および深さ46を有し、そのためアスペクト比は46/48である。アパートチャ32は、幅44および深さ42を有するので、アスペクト比は42/44である。アパートチャ32のアスペクト比は、アパートチャ34のアスペクト比よりも大きいので、当該プロセスは、ある範囲のアスペクト比に適応しなければならないことは明らかである。

【0035】

プロセス中、スピノン・オン誘電体(SOD)またはスピノン・オン・ガラス(SOG)と呼ばれるトレンチ誘電体充填物質が、上記材料を表面上に非常に均一に広げるために回転

50

しているウェーハに塗布される。適当な低い粘度を有する材料は、種々のアーチャ内に浸透し、あふれ出で、頂面 52 はパッド 20 の頂面よりも高くなる。図 2 はその結果を示す。

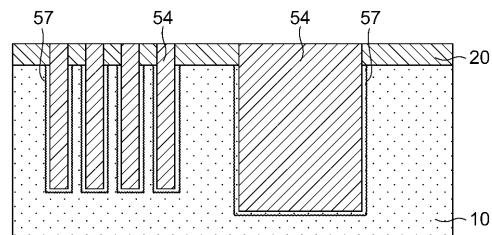

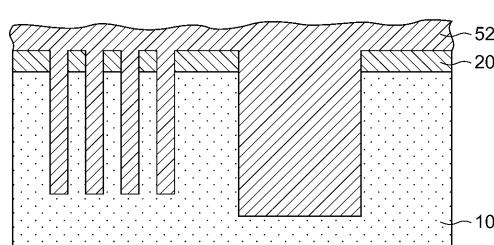

#### 【0036】

次に、図 3 に示すように、過度にあふれ出た材料を除去するために、ウェーハが CMP またはエッティングバック・ステップにより平面化される。図 3 は、また、酸化雰囲気内で材料をアニールすることによる、アーチャの側面に沿って形成された酸化物 57 の余分な厚さも示す。水蒸気を含む雰囲気内のアニーリングの従来のステップは、シラザン内の窒素および水素をアンモニアおよび分子状水素に変換し、この分子状水素は材料から抜け出し、後に大部分は酸化シリコンである残滓を残す。雰囲気が酸素を含んでいると、Si - N 結合から Si - O 結合への変換が促進される。最終材料の特性は、この変換が行われた程度により異なる。

#### 【0037】

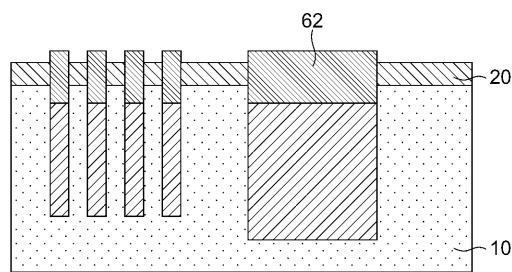

図 4 および図 5 は、シラザン充填 54 が任意の従来のエッティングにより凹み、HDP のキャップ層 62 が、標準技術により堆積され、CMP により平面化される本発明のオプションとしての態様を示す。

#### 【0038】

当業者であれば、シラザン層 54 の応力を HDP 層 62 の応力に近づけると、プロセスがさらにしっかりとし、結果がよくなることを理解することができるだろう。

#### 【0039】

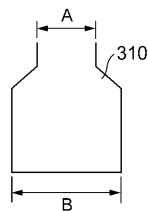

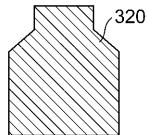

スピノン・オン材料は、化学蒸着法のようなプロセスでは充填できない種々のアーチャ・プロファイルを充填するという周知の特性を有する。図 6 を参照すると、この図は、内側に曲がったプロファイルを有するアーチャ 310 を示す。このことは、横方向の寸法 B が、アーチャの頂部のまたは頂部近くの対応する横方向の寸法 A より短い、少なくとも 1 つのレベルが存在することを意味する。このようなことは、トレンチ・キャバシタの場合には、設計により、平滑にするために壁部上に四角にディボット (divot) が形成された場合には、偶然発生する。

#### 【0040】

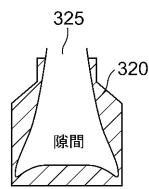

図 8 は、材料 320' の本体内にすでに形成された隙間 325 を含む CVD プロセスによる結果を示す。対照的に、図 7 は、アーチャを均一に充填するスピノン・オン・プロセスの結果を示す。

#### 【0041】

アスペクト比が約 4 を超える（垂直なトレンチ側壁プロファイルを形成する）場合には、浅溝分離、または STI と呼ばれる分離トレンチ用の工業規格材料は、アーチャを均一に充填しない高密度プラズマ援用酸化物（HDP 酸化物）であることは周知である。

#### 【0042】

現代の処理の場合には、チップ上のフィーチャの密度を増大するために非常に高い圧力がかけられるので、アスペクト比は常に増大する。プロセス・エンジニアは、現在約 10 の範囲内のアスペクト比を有する充填トレンチを取り扱っており、遙かに大きいアスペクト比を有する充填トレンチを計画している。全体の材料の一部を堆積するステップ、新しい材料が塞がらないようにアーチャの上部をクリーニングするステップ、次に、第 2 の部分を充填するステップを含む大きなアスペクト比のトレンチを充填するために、種々の複雑で高価なスキームが使用されている。

#### 【0043】

プロセス・エンジニアは、スピノン・オン材料の充填特性のほうが遥かにすぐれているにもかかわらず、前述のスキームを使用する。何故なら、現在、スピノン・オン材料は受け入れられないからである。分離トレンチの場合には、充填したトレンチを絶縁するだけでは、すなわち、電流を流さないというだけでは十分でない。プロセス統合は、プロセス内のステップおよび結果として得られる材料の特性が、プロセスおよび構造の残りと整合することを要求する。

## 【0044】

現在使用しているプロセスは、HDP酸化物の特性と整合させるために開発したものなので、これらの現在のプロセスを変更するのは大仕事である。HDP材料の材料特性をエミュレートするスピン・オン・プロセスを開発することができれば非常に有利である。

## 【0045】

本発明者は、スピン・オン材料の応力、組成および湿式エッティング抵抗をHDP酸化物のこれらのものと同様となるように調整することができることを発見した。

## 【0046】

製造業者の勧める方法で処理したポリシラザンは、低いエッティング抵抗、引張り応力および低い密度を有するHDPのこれらとは非常に異なる特性を有する最終材料を生成する。

10

## 【0047】

本発明によれば、処理ステップのシーケンスは下記のとおりである。

2000～4000の範囲の分子量を有するスピン・オン・シラザンをジブチル・エーテルのような溶媒内に溶解する。

20～120分間、100～450 の範囲内の温度でO<sub>2</sub> 霧囲気内(400～700トル)で予備ベーキングする。

20～120分間、450～800 の範囲内の温度で、水蒸気中で第1のアニーリングを行う。

前のレベルの温度許容度が許す場合には、20～120分間、800～1200 の範囲内の温度で水蒸気を含まない酸素霧囲気内(400～700トル)で、第2のアニーリングを行う。

20

## 【0048】

結果として得られる膜をCMPで平面化する。

## 【0049】

深いSTIトレーニング(アスペクト比が6より大きい)の場合には、追加ステップは、トレーニングの底部の材料が確実に酸化し、Si-N結合からSi-O結合に変換するように、CMPの後で20～120分間、450～800 の範囲内の温度で、水蒸気内で追加アニーリングを行う。

30

## 【0050】

本発明の有利な機能は、最終製品のパラメータを、処理パラメータを変化させることにより変えることができる。図に示すように、最終材料は、不純物による汚染が少ない高品質の酸化物であり、900 で1.5未満の湿式エッティング除去比(WERR)を有し、0.1～2 G dyne/cm<sup>2</sup> の範囲内の圧縮膜応力を有し、標準スラリによるCMPで平面化することができ、1000 を超える温度で熱的に安定していて、HDP酸化物より優れた厚さの均一性(1% 未満)を有する。

30

## 【0051】

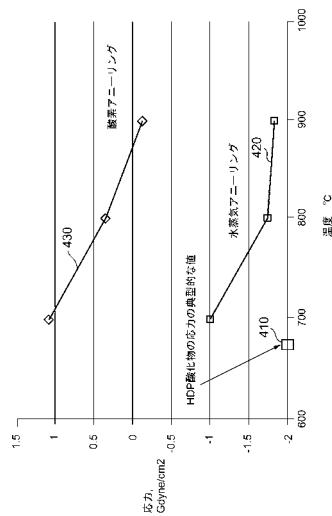

図9を参照すると、図のグラフは、水蒸気および酸素霧囲気内でアニールしたシラザン膜内の材料応力を示す。点410は、HDP酸化物の典型的な値を示す。曲線420は、700～900 の範囲内の水蒸気によるアニーリングの結果を示す。図を見れば分かるように、800 および900 のところの点はHDPに非常に近く、一方、酸素霧囲気内でアニールした膜の結果(曲線430)は、ある引張り応力を有する。

40

## 【0052】

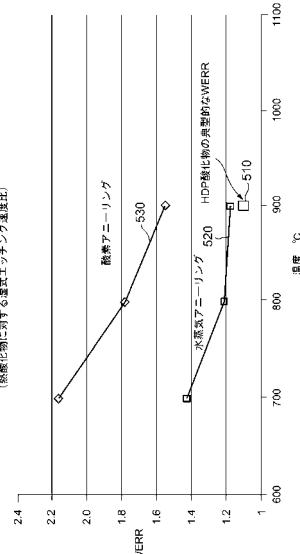

図10は、湿式エッティング速度、すなわち、熱酸化物の速度に対する当該膜のエッティング速度の比の対応する曲線を示す。エッティング材料は、緩衝剤で処理したフッ化水素酸(BHF)である。曲線520上の800および900 での水蒸気によるアニーリングの結果は、点510のHDP酸化物の結果に非常に似ていて、一方、酸素によるアニーリングの結果、曲線530は、遙かに高い(もっと低いエッティング抵抗を有する)。

## 【0053】

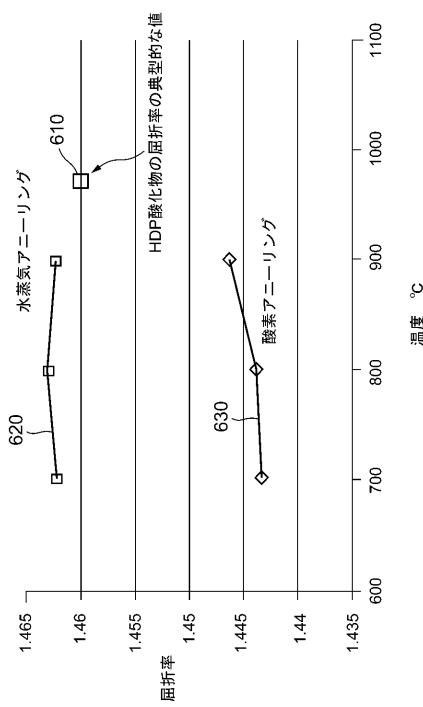

図11は、結果として得られる酸化物の屈折率の対応する結果を示す。屈折率は、材料

50

密度の測定値であり、またシリコン対酸素の化学量論的比率である。

#### 【0054】

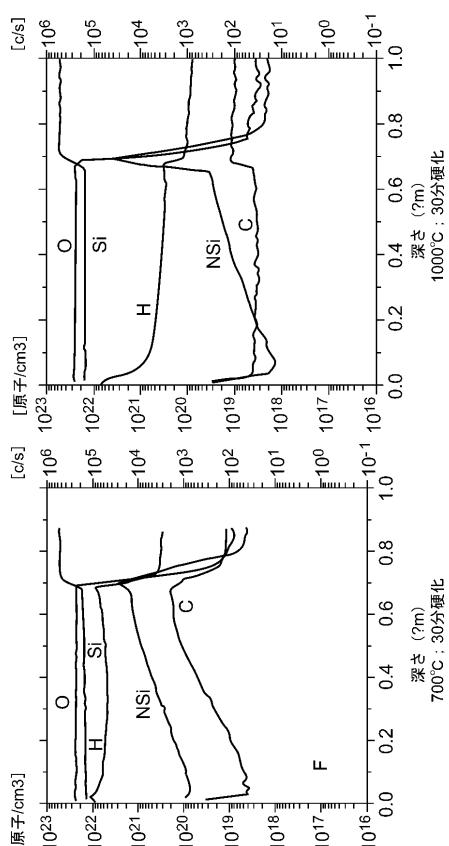

この場合も、曲線620（水蒸気によるアニーリング）は、HDP酸化物の通常の点610にもっと近い。一方、曲線630酸素によるアニーリング上の点は、かなり異なっている。図12は、2つの異なる温度（水蒸気中）でのアニーリング後の膜の組成を示す。Cの残留濃度（曲線C）、Nの残留濃度（曲線NSi）および水素の残留濃度（曲線H）は、1000の場合よりも700の場合の方が遙かに高い。

#### 【0055】

非常に高温（1000）で水蒸気によるアニーリングを行うと、不純物レベルの低い膜ができるが、従来レベル接合がもっと低い温度許容度制限を有する場合には、明らかにこの膜は使用することができない。垂直トランジスタの場合には、多くの場合、トランジスタを形成した後でSTIが行われ、例えば、100nm垂直DRAMグラウンド・ルールを仮定して、900を超える温度での任意の長い（10分を超える）アニーリングを行ってはならない。

#### 【0056】

シリコンの高温水蒸気による酸化についてのもう1つの周知の問題は、ドーピング剤の拡散（B、P、As等）のための活動エネルギーを低減し、その後でその拡散係数（いわゆる酸素促進拡散（OED））を増大する欠陥が形成されることである。この欠陥は、前のp-n接合プロファイル内の望ましくない変化をさらに大きくする。

#### 【0057】

800を超える温度で水蒸気による酸化を行うと、ウェーハ（バルク、エピタキシャルまたはSOI）内のシリコンの過度の酸化が起こり、このような過度の酸化により、能動エリア内で形成されるトランジスタのパラメータが劣化する恐れがあることが分かっている。厚い（300を超える）酸化膜がSTI側壁（特に、頂部の隅の部分）上に成長し、隣接する能動エリア内に応力が発生し、欠陥の数が増大する。パッドSiNストリップおよび以降のエッチングおよびアニーリング処理ステップの後で、頂部のSTIの隅に欠陥が容易に形成される。能動エリア内の応力は回路設計により変化する場合がある。本発明の利点は、新しいトレーニング材料が、それに対してトランジスタが設計された応力を変化させないことである。

#### 【0058】

シラザン膜に対して第1の800での水蒸気によるアニーリングを行ったら、800を超える温度で酸素内で第2のアニーリングに進むことが有利である。このようなアニーリングを行うと、湿式エッチング速度比がさらに低減し（熱酸化物の速度比の約1.1に）、膜応力圧縮が0.5~2Gdyn/cm<sup>2</sup>の範囲内に維持される。

#### 【0059】

最終膜の特性は、水蒸気によるアニーリングおよび酸素によるアニーリングの時間を変化させることにより、調整または適合することができる。

#### 【0060】

1つの好適な実施形態を参考しながら本発明を説明してきたが、当業者であれば特許請求の範囲の精神および範囲から逸脱することなしに、本発明を種々の別の方法で実行することができることを理解することができるだろう。

#### 【図面の簡単な説明】

#### 【0061】

【図1】本発明の実施における基板の一部である。

【図2】本発明の実施における基板の一部である。

【図3】本発明の実施における基板の一部である。

【図4】HDPキャップ層を塗布するためのオプションとしてのステップである。

【図5】HDPキャップ層を塗布するためのオプションとしてのステップである。

【図6】内側に曲がったプロファイルを有するアパー・チャの充填である。

【図7】内側に曲がったプロファイルを有するアパー・チャの充填である。

10

20

30

40

50

【図8】内側に曲がったプロファイルを有するアパー チャの充填である。

【図9】異なる処理による材料の応力のグラフである。

【図10】異なる処理による相対エッティング速度のグラフである。

【図11】異なる処理による相対エッティング速度のグラフである。

【図12】異なる処理による材料の組成のグラフである。

【符号の説明】

【0062】

10 シリコン基板

20 パッド窒化物 / 酸化物

34 アパー チャ

10

46 深さ

48 幅

52 頂面

54 シラザン層

57 酸化物

62 HDP層

310 アパー チャ

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

---

フロントページの続き

(72)発明者 マイケル・ピー・ベリヤンスキー

アメリカ合衆国 0 6 8 0 1 コネチカット州ベセル キングスウッド・ドライブ 4 4

(72)発明者 ラーマ・ディバカルニー

アメリカ合衆国 1 0 5 6 2 ニューヨーク州オッショニング シャーウッド・アヴェニュー 6 0

(72)発明者 ラーエルティス・エコノミコス

アメリカ合衆国 1 2 5 9 0 ニューヨーク州ワピンジャーズ・フォールズ レーク・オニアド・ドライブ 6 0

(72)発明者 ラジャラオ・ジャミー<sup>1</sup>

アメリカ合衆国 1 2 5 3 3 ニューヨーク州ホープウェル・ジャンクション トラシー・レーン 1 4

(72)発明者 ケネス・ティー・セトルマイヤー・ジュニア

アメリカ合衆国 1 2 5 7 0 ニューヨーク州ポクアグ スティル・ロード 5 8

(72)発明者 パドライク・シー・シェーファー

アメリカ合衆国 1 2 5 2 4 ニューヨーク州フィッシュキル ローカスト・コート 4 ピー

F ターム(参考) 5F032 AA35 AA36 AA49 AA77 BA02 BA03 CA14 CA17 DA33 DA74

5F083 AD03 NA01 PR33 PR39 PR40

【要約の続き】

【選択図】 図 1