# (19) World Intellectual Property Organization International Bureau

Ciliational Bulcau

(43) International Publication Date 8 May 2008 (08.05.2008) (10) International Publication Number WO 2008/052607 A2

(51) International Patent Classification: Not classified

(21) International Application Number:

PCT/EP2007/006423

(22) International Filing Date: 19 July 2007 (19.07.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/856,032 2 November 2006 (02.11.2006) US 60/858,353 13 November 2006 (13.11.2006) US

(71) Applicant: REDMERE TECHNOLOGY LTD. [IE/IE]; 2B Fingal Bay Business Park, Balbriggan, Co. Dublin (IE).

(72) Inventors: KEADY, Aidan, Gerard; 16, The Meadows, Oldtown Mill, Celbridge, Co. Kildare (IE). KEANE, John, Anthony; 11 Ardfield Green, Grange, Douglas, Co. Cork (IE). REA, Judy, Ann; 5, Ard Keale, Mount, Oval Village, Rochestown, Co. Cork (IE). GRIFFIN, Benjamin; Knockgorm, Midleton, Co. Cork (IE). HORAN, John, Martin; 44 Lindville, Blackrock, Co. Cork (IE).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declaration under Rule 4.17:**

— as to the identity of the inventor (Rule 4.17(i))

#### **Published:**

without international search report and to be republished upon receipt of that report

(54) Title: A PROGRAMMABLE HIGH-SPEED CABLE WITH EMBEDDED POWER CONTROL

(57) Abstract: An HDMI cable carries high speed encoded data which are transmitted differentially over data channels, along with a clock. High-frequency loss and differential skew within a differential signal may be compensated by analog circuits embedded in the cable. These embedded circuits are tuned at production for best performance by observing the quality of the recovered analog signal. The embedded circuits are powered by a combination of power sources, both carried within the cable, and harvested from the high-speed signals themselves.

#### A PROGRAMMABLE HIGH-SPEED CABLE WITH EMBEDDED POWER CONTROL

#### FIELD OF THE INVENTION

The present invention relates to high speed cables that carry serially encoded differential signals between electronic equipments, and in particular, multi-conductor cables interconnecting audio-visual equipment.

#### **BACKGROUND OF THE INVENTION**

The distribution of television signals has increasingly become based on digital methods and digitally encoded forms of video and audio signals. At the same time, higher resolution (high definition TV) has become available in the market place, commensurate with larger and higher definition displays. To meet the requirement of interconnecting such high definition displays with digital signal sources such as Digital Versatile Disc (DVD) players and receivers/decoders for digital satellite and digital cable distribution of video material, a digital interface standard has evolved, known as the High-Definition Multimedia Interface (HDMI). A detailed specification for HDMI can be obtained from the "hdmi.org" website. The HDMI specification currently available and used in this application is HDMI specification version 1.3 dated June 22, 2006, which is incorporated herein by reference. This HDMI standard can be employed for connecting digital video sources to digital video sinks over a cable that carries a number of digital signals and a clock signal.

The inherent characteristics and manufacturing imperfections of high-speed differential signaling cables such as may be used to carry HDMI signals have an adverse effect on the high-speed signals carried by the cable.

For example, any cable has a limited bandwidth and therefore acts as a low pass filter. The bandwidth of the cable is related to its length, the longer the cable the greater the filtering effect and the lower its bandwidth. As a result, high-frequency signals passing through the cable are attenuated, and their edges become less sharp. This leads to an increased risk of misinterpreting the received data at the receiver end of the cable, especially for long cables and high-speed data.

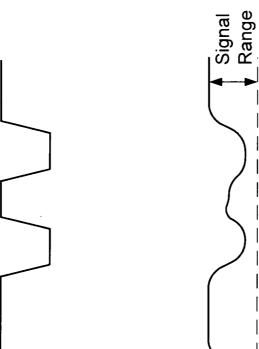

Figure 1A-1C illustrate the effect of the limited bandwidth of a cable on the transmitted signals. Figure 1A illustrates a high-speed signal to be transmitted through a high-speed cable, Figure 1B shows a distorted bandwidth-limited signal received at the receiver end of the cable (before equalization), and Figure 1C shows the received signal at the receiver end after equalization. As seen from Figure 1B, the signal edges are slowed and short pulses are narrowed,

not reaching the full transmitted amplitude.

Differential signaling cables are commonly used to carry high-speed digital signals in differential form, that is pulses of opposing polarities are transmitted on the two strands of the cable. The differential signal carried over such cables may be warped, that is the two signal components (positive and negative polarities V+ and V-) are skewed in time with respect to each other (differential skew), further distorting the received signal.

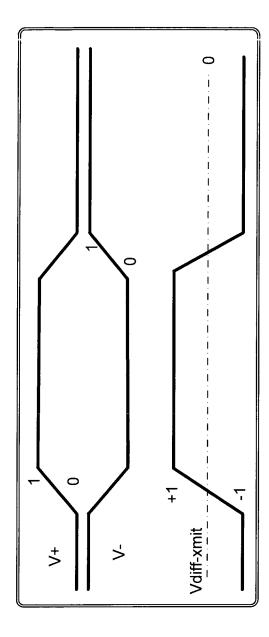

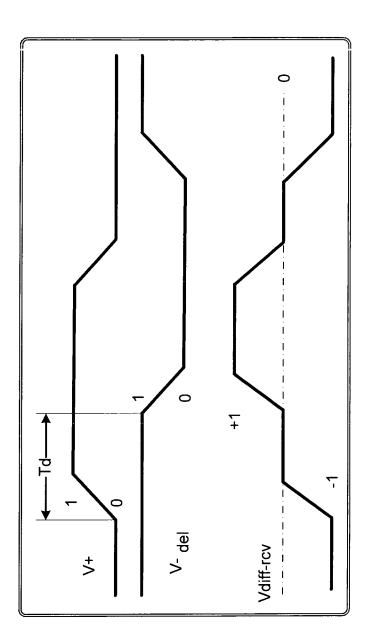

The impact of differential skew is depicted in timing diagrams in Figures 2A and 2B.

Figure 2A shows an example timing diagram of the two single ended signal components (V+, V-) of the differential data on an HDMI channel, as it may be transmitted by an HDMI source into a cable. A timing diagram of the corresponding differential signal (Vdiff-xmit) in Fig. 2A illustrates the corresponding differential signal that is clean and easily interpreted.

Figure 2B shows an example timing diagram of the two single ended signal components (V+ and V-del) of the differential data on an HDMI channel, as it might be received at the end of a cable. For the sake of clarity, only the effect of the differential skew is shown in Fig. 2B. The signals V+ and V- are skewed in time with respect to each other. The negative signal component V- is delayed with respect to the signal component V+ by a differential skew delay of Td. A timing diagram of the corresponding distorted differential signal (Vdiff-rcv) in Fig. 2B illustrates that, as a consequence of the differential skew, the differential signal Vdiff-rcv is significantly distorted with clearly visible plateaus in the signal where the differential signal is zero (0). These plateau regions can only be interpreted as noise by the receiver, the result of which is to reduce the width of the window of valid data. This reduction is seen as a closure of the receive data eye and directly compromises the channel quality. The amount of differential skew delay (Td) depends on the characteristics of each individual cable, and is basically constant.

Earlier approaches to improving cable quality so far have been limited to embedded passive equalizer circuits within the cable, which boost high frequencies of the signals attenuated in the cable. Such equalizers are fixed to compensate for a fixed cable length.

While the equalization required for a given cable depends largely on the length of the cable, other characteristics of high-speed signaling cables such as the differential skew, being more random, may vary substantially between the cables.

Accordingly, there is a need in the industry for the development of an improved high-speed signaling cable, which would provide improved signal characteristics.

Earlier High-Definition Multimedia Interface (HDMI) signal boosters that can be used to boost HDMI signals use external power inputs, see e.g. Long Reach<sup>TM</sup> product of Gennum corporation, which can be found at www.gennum.com/ip/pdffiles/gs8101.pdf. As a result, they

cannot be embedded in a standard HDMI cable. A more recent development is a stand-alone "super booster" that can be inserted inline with a cable, and is also available integrated in an HDMI cable, see references: Gefen Inc., http://www.gefen.com/kvm/product.jsp?prod\_id=2939, including an advertisement of a standalone HDMI "super booster; A manual for the standalone HDMI "super booster, which can be found at http://www.gefen.com/pdf/EXT-HDMI-141SB.pdf; and an advertisement for a cable with an integrated HDMI "super booster" http://www.gefen.com/kvm/cables/hdmicables.jsp#hdmisb

The possibility of embedding an active device within the cable is associated with a problem. Firstly, no power input may be available for such a device except through the cable, i.e. there is no provision for external power supplies. Secondly, in the case of the HDMI cable, there is not enough power available to power a simple signal regenerator, primarily because of the specification requirement to provide a termination voltage for the inputs. As a result, the embedded active device apparently cannot be powered as required.

In more detail, the main power requirement for an HDMI signal booster is the requirement to provide a termination voltage (3.3V) with the capability to source 12mA for each of three HDMI inputs. The power that is available from the cable comes from a 5V line, from which a maximum current of 5mA can be drawn (as per HDMI specification V1.3) when the sink device is active, i.e. the total available power is limited to 50mW. The combined power requirement of the input terminations on the other hand is approximately 12mA\*3.3V\*3 = 120mW. Unfortunately, these requirements cannot be met in a standard HDMI cable in a simple way.

Accordingly, there is a need in the industry for the development of an improved signal booster with an improved power control circuit for embedded cable applications based on or more active devices, which would avoid or mitigate the above noted problem.

#### **SUMMARY OF THE INVENTION**

There is an object of the invention to provide an improved programmable cable with embedded power control and boost device as well as methods and systems for calibrating the cable.

According to one aspect of the invention there is provided a cable for connecting a transmitting data source device to a receiving data sink device and carrying differential data signals including: a boost device for boosting at least one of the differential data signals, the boost device comprising: an electronic circuit for obtaining at least some of the electrical power required to operate the boost device from the at least one of the differential data signals.

The differential data signals are differential High Definition Multi-Media Interface (HDMI) signals and include a plurality of Transition Minimized Differential Signaling (TMDS) encoded data channels and a clock channel.

The boost device includes: a differential input circuit for receiving one of the differential data signals from the data source device; and a differential output circuit for transmitting a boosted one of the differential data signals to the data sink device, wherein said at least some of the electrical power is obtained from the data source and sink devices.

The differential output circuit and the differential input circuit are connected in series so as to conduct a current from the data sink device to the data source device.

The differential output circuit and the differential input circuit are joined at an intermediate voltage node such that load current from the data sink device flows through the differential output circuit to the intermediate voltage node, and the intermediate voltage node is connected as the supply voltage for the differential input circuit.

The cable further includes a voltage boost circuit between the intermediate voltage node and a second intermediate voltage node supplying voltage for the differential input circuit.

The voltage boost circuit includes a switched capacitor and a 2-phase clock, the capacitors used for periodically transferring energy from the intermediate voltage node to the second intermediate voltage node.

The boost device further includes a processing block having a transfer function for processing the differential signal received by the differential input circuit and conveying the processed signal to the differential output circuit.

The cable further includes a power converter for converting the power for operating the processing block from an available higher voltage, the power converter comprising switched capacitors and a 2-phase clock, the switched capacitors used for transferring energy from the available higher voltage to the processing block.

According to another aspect of the invention, there is provided a method for providing power to a boost device in a cable connected between a transmitting data source device and a receiving data sink device, comprising the steps of: receiving differential data signals from the data source device in a differential input circuit of the boost device; boosting at least one of the received differential data signals into a boosted differential data signal; transmitting the boosted differential data signal to the receiving data sink device with a differential output circuit of the boost device; and obtaining power to operate at least some of the circuitry of the boost device from the data source and sink devices through their connections with the differential input and output circuits respectively.

The method further comprises the step of connecting the differential output circuit and the differential input circuit in series so as to conduct a current from the data sink device to the data source device.

The method as described above further comprises the steps of: joining the differential output circuit and the differential input circuit at an intermediate voltage node such that load current from the data sink device flows through the differential output circuit to the intermediate voltage node; and connecting the intermediate voltage node as the supply voltage for the differential input circuit.

According to yet another aspect of the invention there is provided a boost device for connecting a transmitting data source device to a receiving data sink device, the transmitting data source device sending differential data signals into the boost device, the boost device for boosting at least one of the differential data signals, the boost device comprising an electronic circuit which obtains at least some of the electrical power required to operate the boost device from the at least one of the differential data signals.

In the boost device as described above, the differential data signals are differential High Definition Multi-Media Interface (HDMI) signals and include a plurality of Transition Minimized Differential Signaling (TMDS) encoded data channels and a clock channel.

The boost device further comprises: a differential input circuit for receiving one of the differential data signals from the data source device; and a differential output circuit for transmitting a boosted one of the differential data signals to the data sink device; wherein said at least some of the electrical power to operate the boost device is obtained from the data source and sink devices.

In the boost device described above, the differential output circuit and the differential input circuit are connected in series so as to conduct a current from the data sink device to the data source device.

The differential output circuit and the differential input circuit are joined at an intermediate voltage node such that load current from the data sink device flows through the differential output circuit to the intermediate voltage node, and the intermediate voltage node is connected as the supply voltage for the differential input circuit.

The boost device described above further includes a voltage boost circuit between the intermediate voltage node and a second intermediate voltage node supplying voltage for the differential input circuit.

The voltage boost circuit includes a switched capacitor and a 2-phase clock, the capacitor used for periodically transferring energy from the intermediate voltage node to the second

intermediate voltage node.

The boost device further comprises a processing block having a transfer function for processing the differential signal received by the differential input circuit and conveying the processed signal to the differential output circuit.

The boost device further comprises a power converter for converting the power for operating the processing block from an available higher voltage, the power converter comprising switched capacitors and a 2-phase clock, the switched capacitors used for transferring energy from the available higher voltage to the processing block.

According to one more aspects of the invention there is provided a cable for connecting a transmitting data source device to a receiving data sink device carrying differential signals including: a boost device for boosting at least one of the differential signals, the boost device comprising: an input circuit for receiving a raw differential signal from the data source device and outputting a recovered signal; a deskew circuit with first adjustable parameters for processing the recovered signal into a deskewed signal; an equalizer circuit with second adjustable parameters for processing the deskewed signal into an equalized signal; and an output circuit for amplifying the equalized signal into a boosted signal and sending the boosted signal to the data sink device.

In the cable described above, the boost device further includes a parameter memory for retaining the first and second adjustable parameters after they have been adjusted.

The cable further includes a control bus, and the parameter memory is accessible from said control bus.

The equalizer circuit comprises a circuit for adjusting a frequency response of the deskewed signal by changing the second adjustable parameters to produce the equalized signal. Preferably, the equalizer circuit has at least two settings of the second adjustable parameters for adjusting the frequency response.

In the cable of the embodiments of the invention, the deskew circuit is an analog differential deskew circuit for adjusting an existing time skew of two polarities of the differential signal by changing the first adjustable parameters.

The analog differential deskew circuit comprises: a number of delay units arranged sequentially; an analog selector, selecting a composite delay resulting from the delay units that are selected by the analog selector; and analog switches inserting the composite delay into the polarities of the differential signal.

The analog switches are inserting the composite delay into one or the other polarity of

the differential signal. Preferably, each of the analog delay units has a gain, which is substantially equal to 1.0, and each of the analog delay units comprises one or more amplifiers. In more detail, each analog delay unit comprises: first and second amplifiers having a common input, which is the input of the analog delay unit, and their outputs being summed to generate the output of the analog delay unit; the first amplifier having a gain of  $(1.0 - \Delta)$ , and a delay equal to a predetermined delay value; and the second amplifier having a gain of  $\Delta$ , and substantially the same delay as the first amplifier. Conveniently, the first amplifier is a follower stage, and e second amplifier has a shunt capacitor for setting the gain of  $\Delta$ .

According to one more aspect of the invention there is provided a boost device for connecting a transmitting data source device to a receiving data sink device, the transmitting data source device sending differential data signals into the boost device, the boost device for boosting at least one of the differential data signals, the boost device comprising: an input circuit for receiving a raw differential signal from the data source device and outputting a recovered signal; a deskew circuit with first adjustable parameters for processing the recovered signal into a deskewed signal; an equalizer circuit with second adjustable parameters for processing the deskewed signal into an equalized signal; and an output circuit for amplifying the equalized signal into a boosted signal and sending the boosted signal to the data sink device.

The boost device further includes a parameter memory for retaining the first and second adjustable parameters. The boost device also includes a control input for accessing the parameter memory.

The equalizer circuit comprises a circuit for adjusting a frequency response of the deskewed signal by changing the second adjustable parameters to produce the equalized signal. The equalizer circuit has at least two settings of the second adjustable parameters for adjusting the frequency response.

The deskew circuit is an analog differential deskew circuit for adjusting an existing time skew of two polarities of the differential signal by changing the first adjustable parameters.

Preferably, the analog differential deskew circuit comprises: a number of delay units arranged sequentially; an analog selector, selecting a composite delay resulting from the delay units that are selected by the analog selector; and analog switches inserting the composite delay into the polarities of the differential signal. Advantageously, the analog switches are inserting the composite delay into one or the other polarity of the differential signal.

Preferably, each of the analog delay units has a gain, which is substantially equal to 1.0 and comprises one or more amplifiers. In the embodiments of the invention, each analog delay

unit comprises: first and second amplifiers having a common input, which is the input of the analog delay unit, and their outputs being summed to generate the output of the analog delay unit; the first amplifier having a gain of  $(1.0 - \Delta)$ , and a delay equal to a predetermined delay value; and the second amplifier having a gain of  $\Delta$ , and substantially the same delay as the first amplifier.

Conveniently, the first amplifier is a follower stage, and the second amplifier has a shunt capacitor for setting the gain of  $\Delta$ .

According to yet one more aspect of the invention, there is provided a method for a sending differential signals from a transmitting data source device to a receiving data sink device through a cable that includes a boost device for boosting at least one of the differential signals, comprising the steps of: receiving a raw differential signal from the data source device in an input circuit of the boost device and outputting a recovered signal; processing the recovered signal in a deskew circuit with first adjustable parameters into a deskewed signal; processing the deskewed signal in an equalizer circuit with second adjustable parameters into an equalized signal; amplifying the equalized signal in an output circuit into a boosted signal; and sending the boosted signal to the data sink device.

The method further includes the steps of adjusting the first and second adjustable parameters; storing the first and second adjustable parameters in parameter memory; and accessing the parameter memory from a control input. Conveniently, the step of processing the recovered signal includes the step of adjusting an existing time skew of two polarities of the differential signal by changing the first adjustable parameters; and adjusting a frequency response of the deskewed signal by changing the second adjustable parameters.

In more detail, the step of changing the first adjustable parameters comprises the steps of arranging a number of delay units sequentially; selecting a composite delay resulting from number of delay units; and inserting the composite delay into the polarities of the differential signal. Beneficially, the step of inserting the composite delay includes inserting the composite delay into one or the other polarity of the differential signal. Conveniently, the step of arranging a number of delay units includes a step of selecting analog delay units each having a gain that is substantially equal to 1.0.

According to one more aspect of the invention, there is provided a cable for connecting a transmitting data source device to a receiving data sink device carrying differential signals including: a printed circuit board (PCB) and a boost device, the PCB including tracks for providing delays in coupling a raw differential signal from the data source device to two or more

inputs of the boost device; the boost device for boosting at least one of the differential signals, the boost device comprising: an input circuit for terminating the delayed raw differential signal; an input selector circuit with first adjustable parameters for selecting a delayed raw differential signal and outputting a recovered signal that is deskewed; an equalizer circuit with second adjustable parameters for processing the recovered signal into an equalized signal; and an output circuit for amplifying the equalized signal into a boosted signal and sending the boosted signal to the data sink device.

The boost device further includes a parameter memory for retaining the first and second adjustable parameters. The cable also includes a control bus, and the parameter memory is accessible from said control bus.

In the boost device, the input selector circuit for selecting the delayed raw differential signal for adjusting an existing time skew of two polarities of the differential signal is controlled by changing the first adjustable parameters. The equalizer circuit comprises a circuit for adjusting a frequency response of the deskewed signal by changing the second adjustable parameters to produce the equalized signal. Conveniently, the equalizer circuit has at least two settings of the second adjustable parameters for adjusting the frequency response.

The PCB comprises a number of tracks providing delays arranged sequentially, and the input selector circuit selecting a composite delay resulting from the tracks that are selected by the input selector circuit.

According to one more aspect of the invention, there is provided a cable for connecting a transmitting data source device to a receiving data sink device carrying differential signals including: a printed circuit board (PCB) and a boost device, the PCB including tracks for providing delays in coupling a raw differential signal from the data source device to two or more inputs of the boost device; the boost device for boosting at least one of the differential signals, the boost device comprising: an input circuit for terminating the delayed raw differential signal; an input selector circuit with first adjustable parameters for selecting a delayed raw differential signal and outputting a recovered signal that is coarsely deskewed; a deskew circuit with second adjustable parameters for processing the recovered and coarsely deskewed signal into a finely deskewed signal; an equalizer circuit with third adjustable parameters for processing the finely deskewed signal into an equalized signal; and an output circuit for amplifying the equalized signal into a boosted signal and sending the boosted signal to the data sink device.

Similar to previous embodiments of the invention, the boost device includes a parameter memory for retaining the first, second, and third adjustable parameters. The cable further includes a control bus, and the parameter memory is accessible from said control bus.

The input selector circuit for selecting the delayed raw differential signal for coarsely adjusting an existing time skew of two polarities of the differential signal is controlled by changing the first adjustable parameters, and in which the deskew circuit is an analog differential deskew circuit for finely adjusting a remaining time skew of two polarities of the differential signal by changing the second adjustable parameters.

The equalizer circuit comprises a circuit for adjusting a frequency response of the deskewed signal by changing the third adjustable parameters to produce the equalized signal. The equalizer circuit has at least two settings of the third adjustable parameters for adjusting the frequency response.

The cable as described above, wherein the PCB comprises a number of tracks providing delays arranged sequentially, and the input selector circuit selecting a composite delay resulting from the tracks that are selected by the input selector circuit, and wherein further the analog differential deskew circuit comprises: a number of delay units arranged sequentially; an analog selector, selecting a composite delay resulting from the delay units that are selected by the analog selector; and analog switches inserting the composite delay into the polarities of the differential signal. Beneficially, the analog switches are inserting the composite delay into one or the other polarity of the differential signal. Similar to other embodiments described above, each of the analog delay units has a gain, which is substantially equal to 1.0 and comprises one or more amplifiers.

Each analog delay unit comprises: first and second amplifiers having a common input, which is the input of the analog delay unit, and their outputs being summed to generate the output of the analog delay unit; the first amplifier having a gain of  $(1.0 - \Delta)$ , and a delay equal to a predetermined delay value; and the second amplifier having a gain of  $\Delta$ , and substantially the same delay as the first amplifier. Conveniently, the first amplifier is a follower stage, and the second amplifier has a shunt capacitor for setting the gain of  $\Delta$ .

According to yet one more aspect of the invention, there is provided a cable for connecting a transmitting data source device to a receiving data sink device carrying differential signals including: a boost device for boosting at least one of the differential signals, the boost device comprising: an input circuit for receiving a raw differential signal from the data source device and outputting a recovered signal; a deskew circuit with adjustable parameters for processing the recovered signal into a deskewed signal; and an output circuit for amplifying the deskewed signal into a boosted signal and sending the boosted signal to the data sink device.

The boost circuit further includes an equalizer circuit for adjusting the frequency

response of the deskewed signal.

The boost device also includes a parameter memory for retaining the adjustable parameters. The cable further includes a control bus, and the parameter memory is accessible from said control bus.

In this embodiment of the invention, the boost device further includes performance analysis circuitry for determining the performance of the cable.

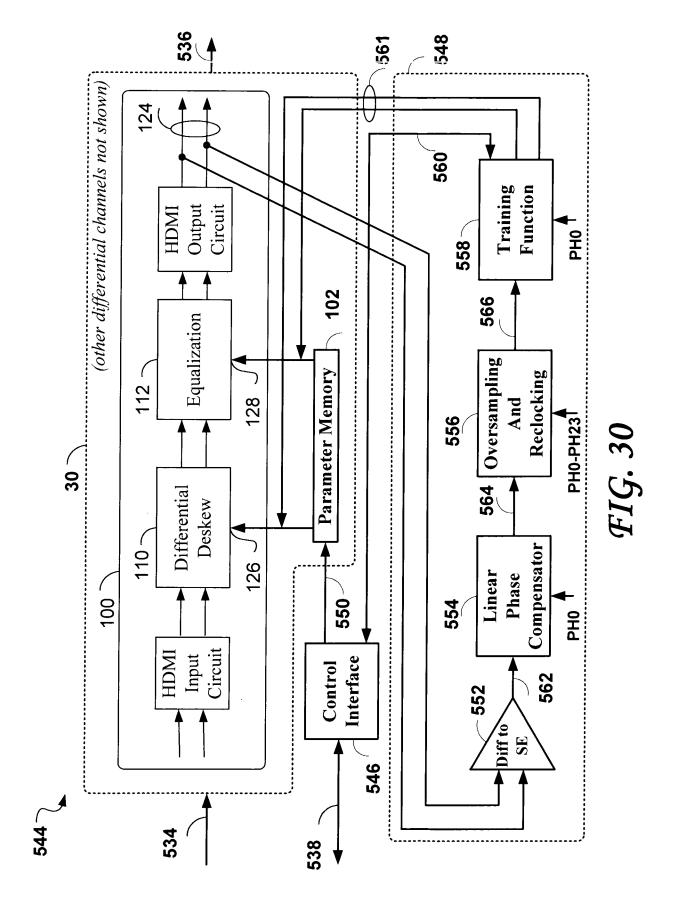

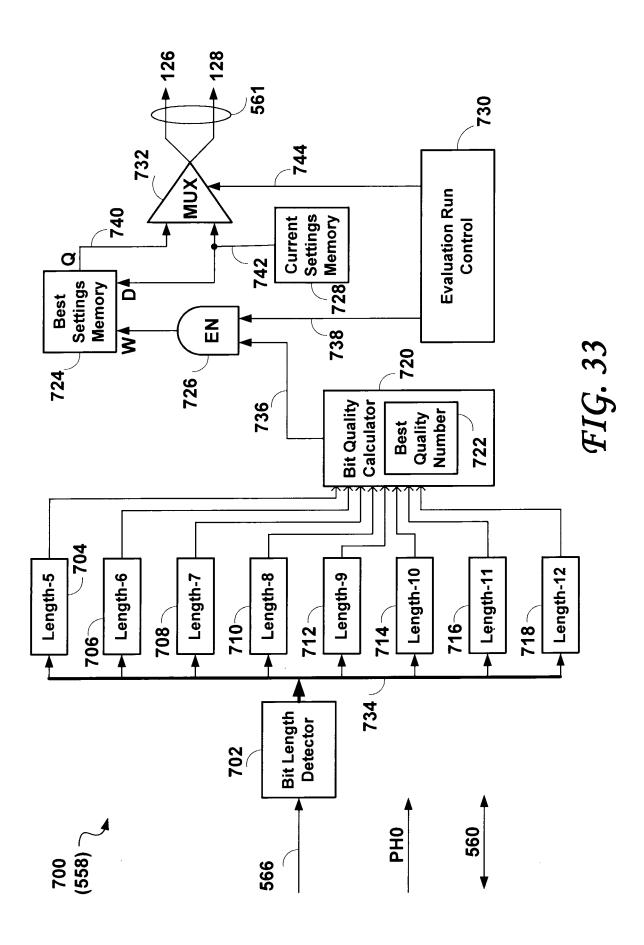

The performance analysis circuitry includes: a differential to single-ended block for converting the boosted signal to a single-ended signal; a linear phase compensator to phase-align the single-ended signal with a common clock signal; an oversampling circuit providing a digital representation of the phase-aligned single ended signal (a preprocessed data signal); and a training function circuit for estimating a quality of the preprocessed data signal, and adjusting the parameters of the deskew and equalizer circuitry (by changing the adjustable parameters) to improve the quality of the preprocessed data signal.

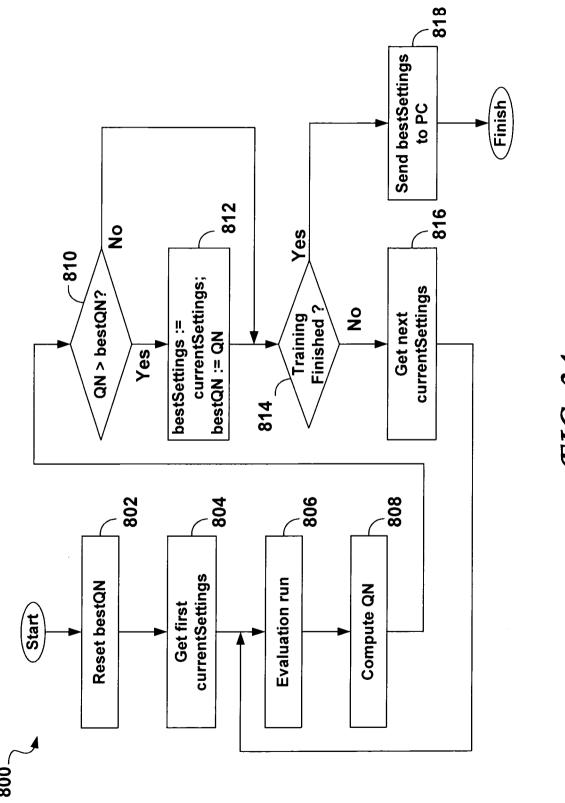

The training function circuit further comprises: a digital circuit for estimating the quality of the preprocessed data signal and generating a Quality Number indicating said quality; an evaluation run control circuit for adjusting the parameters of the deskew and equalizer circuitry to a number of predetermined settings, and for monitoring a predetermined number of the oversampled bits for each setting; a memory for retaining the best setting corresponding to the highest Quality Number; and a means for updating the said parameters to the best setting.

The performance analysis circuitry includes means for receiving a start trigger to the evaluation run control circuit, and for reporting the best setting over the control bus.

According to one additional aspect of the invention, there is provided a method for determining the performance of a cable comprising a boost device which receives a differential data signal, deskews and equalizes the differential data signal according to adjustable parameters, and outputs a boosted signal, the boost device further comprising a performance analysis circuitry, including steps of: converting the boosted signal to a single-ended signal; phase-aligning the single-ended signal with a common clock signal; oversampling the phase-aligned single ended signal and generating a preprocessed data signal; estimating a quality of the preprocessed data signal; and adjusting the adjustable parameters to improve the quality of the preprocessed data signal.

The method as described in claim 29, further comprising an evaluation step including the steps of: estimating the quality of the preprocessed data signal and generating a Quality Number indicating said quality; adjusting the adjustable parameters to a number of predetermined settings;

monitoring the preprocessed data signal for each setting; retaining the best setting corresponding to the highest Quality Number; and updating the adjustable parameters to the best setting.

The method described above further comprises the steps of: starting the evaluation method by receiving a start trigger, and reporting the best setting over a control bus.

According to one more aspect of the invention, there is provided a cable for connecting a transmitting data source device to a receiving data sink device carrying differential signals including: a boost device for boosting at least one of the differential signals, the boost device comprising: an input circuit for receiving a raw differential signal from the data source device and outputting a recovered signal; a deskew and equalizer circuits with adjustable parameters for processing the recovered signal into a deskewed signal and equalized signal; an output circuit for amplifying the deskewed and equalized signal into a boosted signal and sending the boosted signal to the data sink device; a parameter memory for storing the adjustable parameters; and performance analysis circuitry for determining the performance of the cable.

The cable further comprises a control bus, wherein the parameter memory is accessible from the control bus.

In the embodiments of the invention, the performance analysis circuitry includes: a differential to single-ended block for converting the boosted signal to a single-ended signal; a linear phase compensator to phase-align the single-ended signal with a common clock signal; an oversampling circuit providing a digital representation of the phase-aligned single ended signal to produce a preprocessed data signal; and a training function circuit for estimating a quality of the preprocessed data signal, and adjusting the parameters of the deskew and equalizer circuits by changing the adjustable parameters to improve the quality of the preprocessed data signal.

The training function circuit further comprises: a digital circuit for estimating the quality of the preprocessed data signal and generating a Quality Number indicating said quality; an evaluation run control circuit for adjusting the parameters of the deskew and equalizer circuitry to a number of predetermined settings, and for monitoring a predetermined number of the oversampled bits for each setting; a memory for retaining the best setting corresponding to the highest Quality Number; and a means for updating the said parameters to the best setting.

The performance analysis circuitry includes means for receiving a start trigger to the evaluation run control circuit, and for reporting the best setting over the control bus.

A system for calibrating the cable described above is also provided, including: a control computer attached to the control bus of the cable, and a data pattern generator attached to the cable and programmed to send differential signals into the cable; the control computer is configured to send a trigger over the control bus to the performance analysis circuitry to start the

evaluation run control circuit; to receive the best settings from the performance analysis circuitry; and to load parameters corresponding to the best settings into the parameter memory over the control bus.

Alternatively, the system for calibrating the cable described above comprises: a control computer attached to the control bus of the cable, and a data pattern generator attached to the cable and programmed to send differential signals into the cable; the control computer is configured to send a trigger over the control bus to the performance analysis circuitry to start the evaluation run control circuit; and the performance analysis circuitry is configured to load parameters corresponding to the best settings into the parameter memory over the control bus.

A corresponding method for calibrating a cable for transmitting differential signals is provided, the cable including a boost device for deskewing and equalizing the differential signals, the boost device having adjustable parameters and a parameter memory, the method comprising the steps of: sending a differential data signal into the cable; sending a trigger to the boost device;

performing a training run in the boost device, wherein the training run includes the steps of performing at least two evaluation runs with different settings of the adjustable parameters and evaluating the results with each of the at least two settings, retaining the best settings; and storing the best settings in the parameter memory.

The step of performing the evaluation run includes the steps of: processing the differential data signal into a deskewed signal; processing the deskewed signal into an equalized signal; and generating a preprocessed signal, which is a digital representation of the equalized signal.

The step of evaluating includes the steps of: determining the run length of contiguous "1" or "0" samples in the digital representation of the equalized signal within a window of at least one bit period; counting the number of occurrences of selected run lengths during an observation period of "N" bits; storing the counted numbers of occurrences in counters according to the selected run lengths; and processing the outputs of the counters into a Quality Number indicating the quality of the equalized signal.

According to yet one more aspect of the invention, there is provided a system for calibrating a cable for transmitting differential signals, the cable including a boost device for deskewing and equalizing the differential signals, the boost device having adjustable parameters and a parameter memory, the system comprising: means for sending a differential data signal into the cable; means for sending a trigger to the boost device; means for performing a training run in the boost device, including evaluation means for performing at least two evaluation runs

with different settings of the adjustable parameters, evaluating the results with each of the at least two settings and retaining the best settings; and means for storing the best settings in the parameter memory.

In the system for calibrating the cable described above, the evaluation means comprises: means for processing the differential data signal into a deskewed signal; means for processing the deskewed signal into an equalized signal; and means for generating a preprocessed signal, which is a digital representation of the equalized signal.

The evaluation means comprises: means for determining the run length of contiguous "1" or "0" samples in the digital representation of the equalized signal within a window of at least one bit period; means for counting the number of occurrences of selected run lengths during an observation period of "N" bits; means for storing the counted numbers of occurrences in counters according to the selected run lengths; and means for processing the outputs of the counters into a Quality Number indicating the quality of the equalized signal.

According to yet one more aspect of the invention, there is provided a system for calibrating a cable for transmitting differential signals, including a boost device having adjustable parameters and a parameter memory, the system comprising: a network analyzer capable of sending at least two signals into a cable input and measuring the response at a cable output; a computer connected to the network analyzer and to the parameter memory of the cable, the computer having a computer memory; and a computer program code stored in the computer memory for causing the computer to perform a calibration of the cable by changing the adjustable parameters and storing the results in the parameter memory of the cable.

The computer program code causes the computer to perform the calibration of the cable by performing a training run in the boost device, including performing at least two evaluation runs with different settings of the adjustable parameters and evaluating performance of the cable for each of the settings, and retaining the best settings. The computer program code also causes the computer to perform said at least two evaluation runs, each evaluation run including: processing the differential data signal into a deskewed signal; processing the deskewed signal into an equalized signal; and generating a preprocessed signal, which is a digital representation of the equalized signal. The computer program code further causes the computer to evaluate the performance of the cable for each of the settings by: determining the run length of contiguous "1" or "0" samples in the digital representation of the equalized signal within a window of at least one bit period; counting the number of occurrences of selected run lengths during an observation period of "N" bits; storing the counted numbers of occurrences in counters according to the selected run lengths; and processing the outputs of the counters into a Quality

Number indicating the quality of the equalized signal. Optionally, the system for calibrating the cable further comprises the cable to be calibrated.

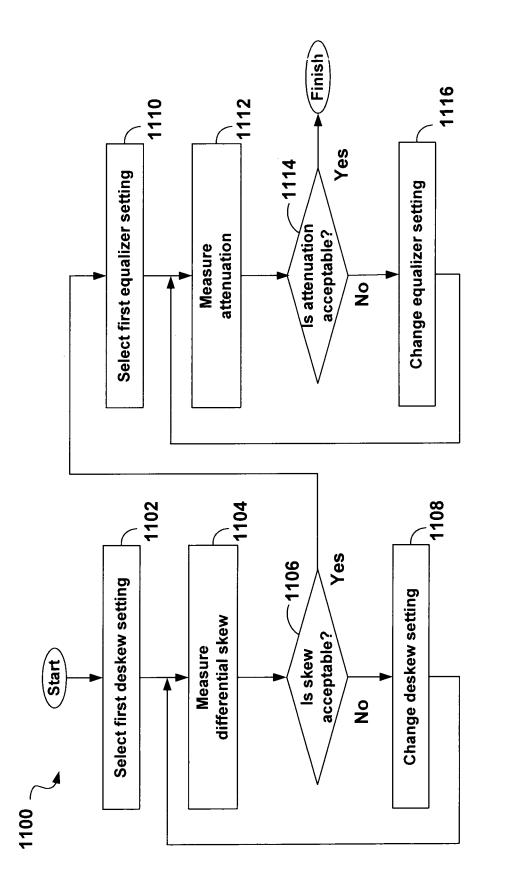

A method for operating the system for calibrating the cable described above comprises the steps of: (a) measuring differential skew of the differential signals at the cable output; (b) changing the adjustable parameters and repeating step (a) when the differential skew is higher than a predetermined skew threshold; (c) measuring attenuation at each of a predetermined number of frequencies; (d) changing the adjustable parameters and repeating step (c) when the attenuation is outside a predetermined range at any measured frequency; and (e) storing the parameters in the parameter memory.

The method further comprises the steps of: setting the predetermined skew threshold to the minimal value observed within a predetermined number of repeats of the step (a); setting the predetermined range to a value close to 0 db, and less than a predetermined limit at each of the measured frequencies; and setting the predetermined frequency to approximately a frequency of the differential signals for which the cable is intended.

Thus, an improved programmable cable with embedded power control and boost device is provided along with methods and systems for calibrating the cable.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

Embodiments of the invention will now be described, by way of example, with reference to the accompanying drawings in which:

**Figures 1A-1C** illustrate a high-speed signal to be transmitted through the high-speed cable, a distorted bandwidth-limited signal received at the end of the cable (before equalization), and the received signal after equalization respectively;

**Figures 2A** shows timing diagrams of the single ended signal components and the corresponding differential signal of the differential data on a differential signaling channel respectively as they might be transmitted by a transmitter into a cable;

Figures 2B shows example timing diagrams of the single ended signal components and the corresponding differential signal of the differential data as they might be received from the end of the cable;

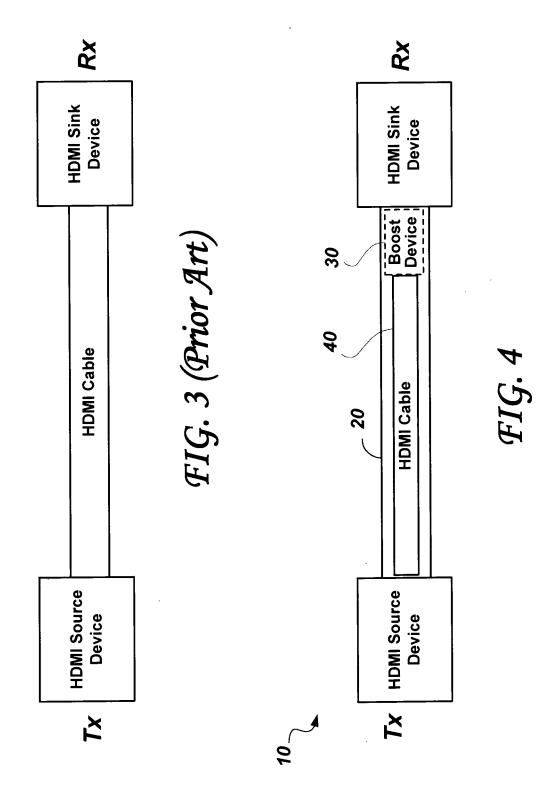

Figure 3 shows a prior art HDMI (High-Definition Multi-Media Interface) system;

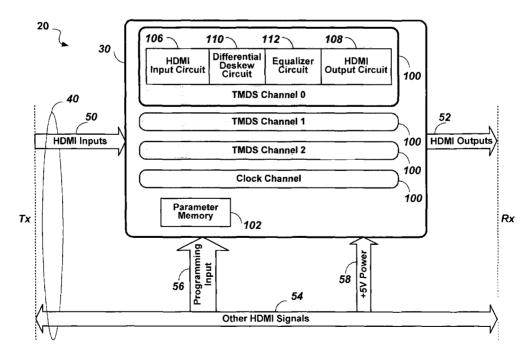

**Figure 4** shows an the HDMI system 10 including an improved HDMI cable 20 according to an embodiment of the present invention;

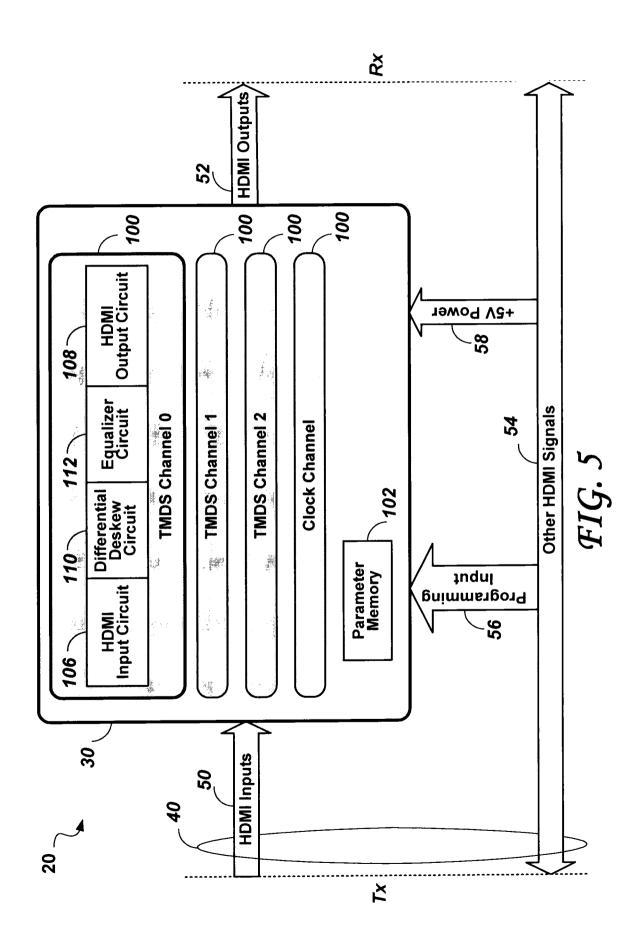

**Figure 5** is a block diagram illustrating the improved HDMI cable 20 of Fig. 4, including channel boost circuits 100;

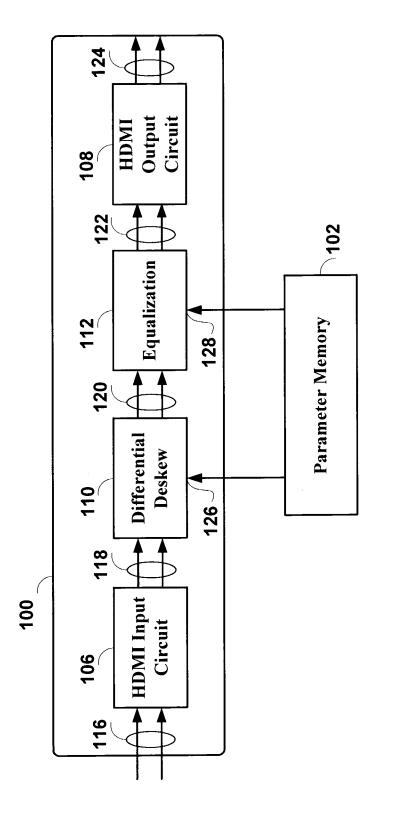

**Figure 6** is a more detailed block diagram of the channel boost circuit 100 of Fig. 5, including a Differential Deskew Circuit 110;

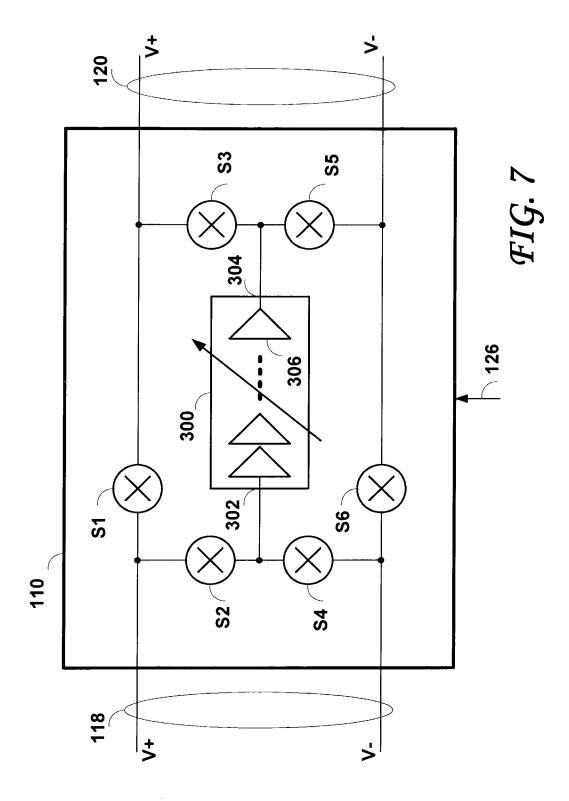

**Figure 7** shows a simplified block diagram of the Differential Deskew Circuit 110 of Fig. 6, including an adjustable delay block 300;

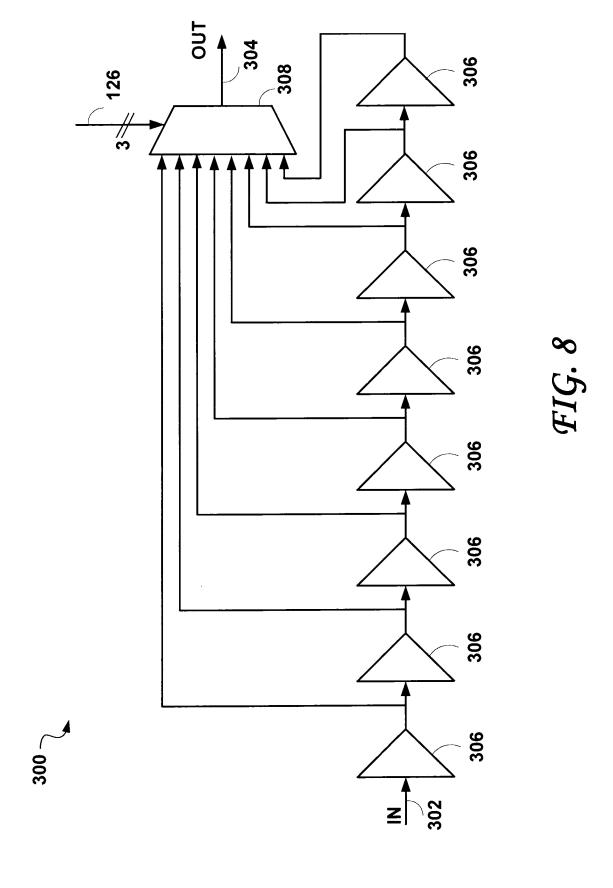

Figure 8 shows the preferred embodiment of the adjustable delay block 300 of Fig. 7;

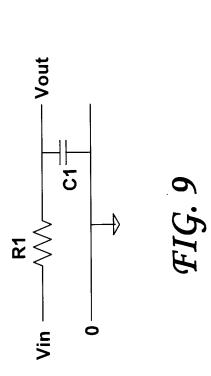

**Figure 9** shows a simple RC delay circuit that may be used to introduce the delay (Td) of Fig. 2B;

Figure 10 shows simulation results of the RC circuit of Fig. 9;

Figure 11 shows simulation results of the RC circuit of Fig. 9 with a reduced time constant;

Figure 12 shows a delay circuit made from a cascade of three RC stages;

Figure 13 shows the waveforms of the trapezoidal input pulse (Vin) and the waveforms of the delayed pulses after each stage of the circuit of Fig. 12;

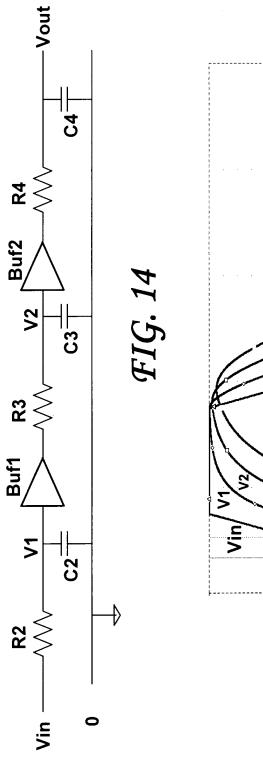

**Figure 14** shows the same cascaded delay circuit as in Fig. 12, with two buffers (amplifiers) added;

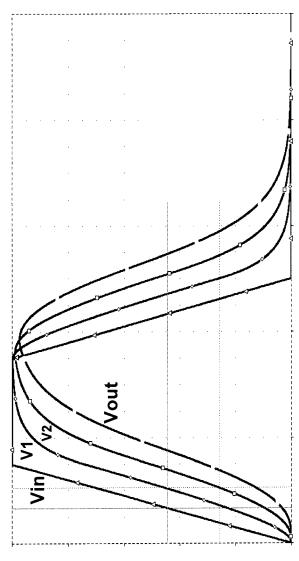

Figure 15 shows simulation results of the circuit arrangement of Fig. 14;

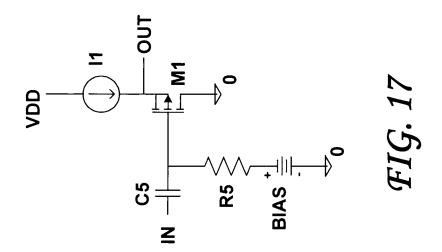

Figure 16 shows a simple follower circuit;

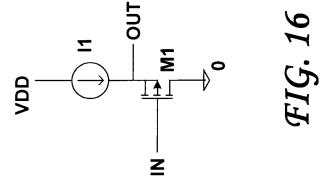

Figure 17 shows an AC-coupled follower circuit, derived from the simple follower circuit of Fig. 16;

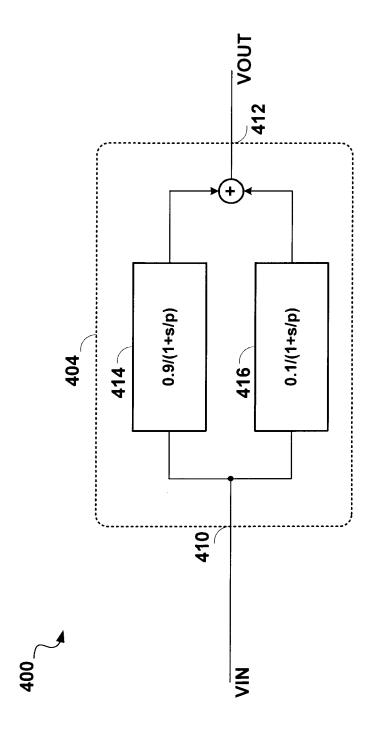

**Figure 18** illustrates a simplified block diagram of a buffered delay stage 400 which may be an embodiment of the delay unit 306 of the adjustable delay 300 of Fig. 6;

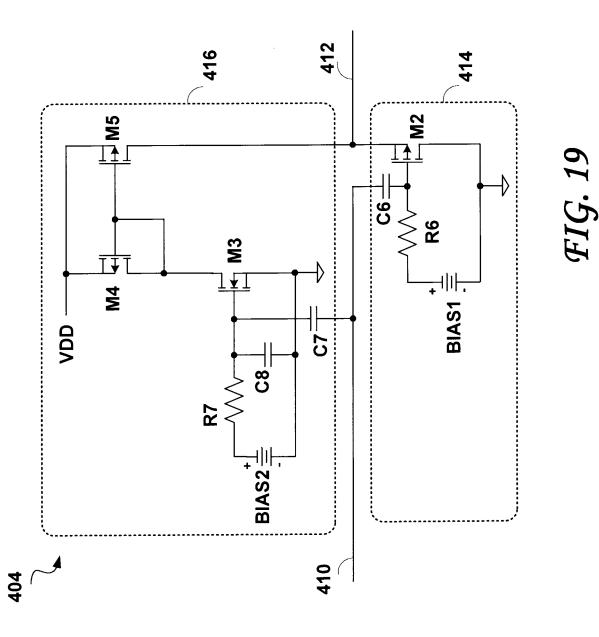

**Figure 19** shows the preferred embodiment of the buffer 404 of the buffered delay stage 400 of Fig. 18;

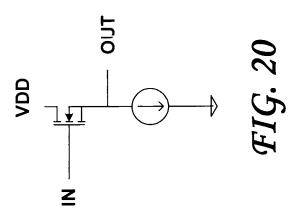

Figure 20 shows a simple N-channel follower;

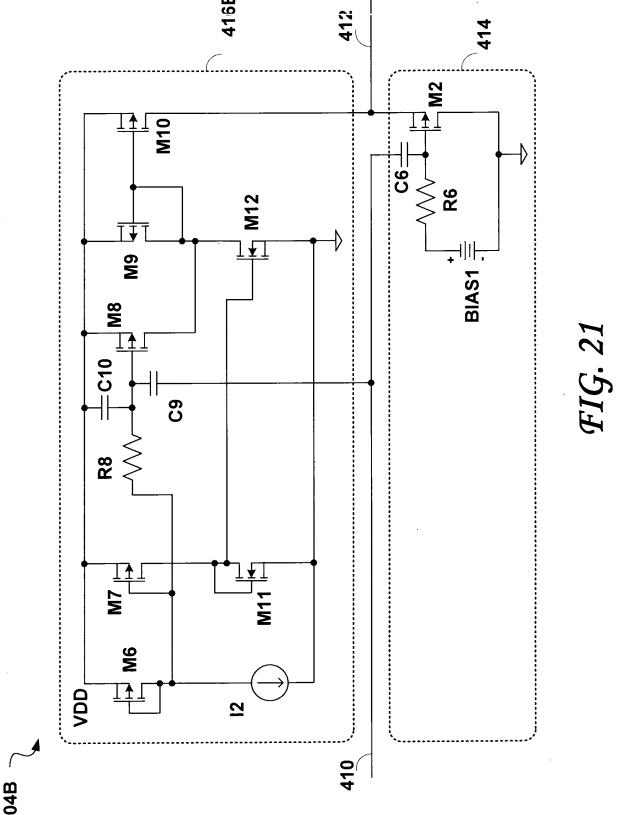

Figure 21 shows an alternative embodiment 404B of the delay stage 306;

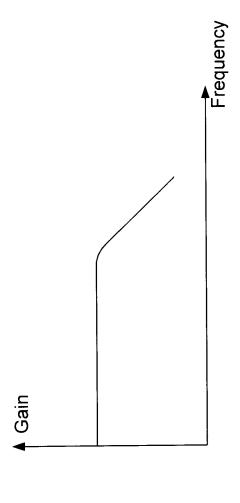

Figure 22 shows a simplified transfer function of a cable;

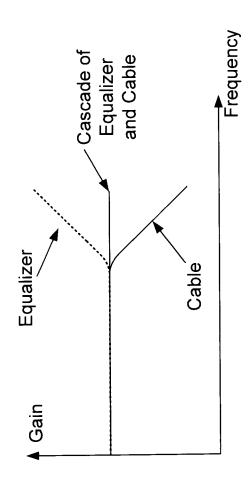

Figure 23 shows a simplified transfer function of a cascade of an equalizer and a cable;

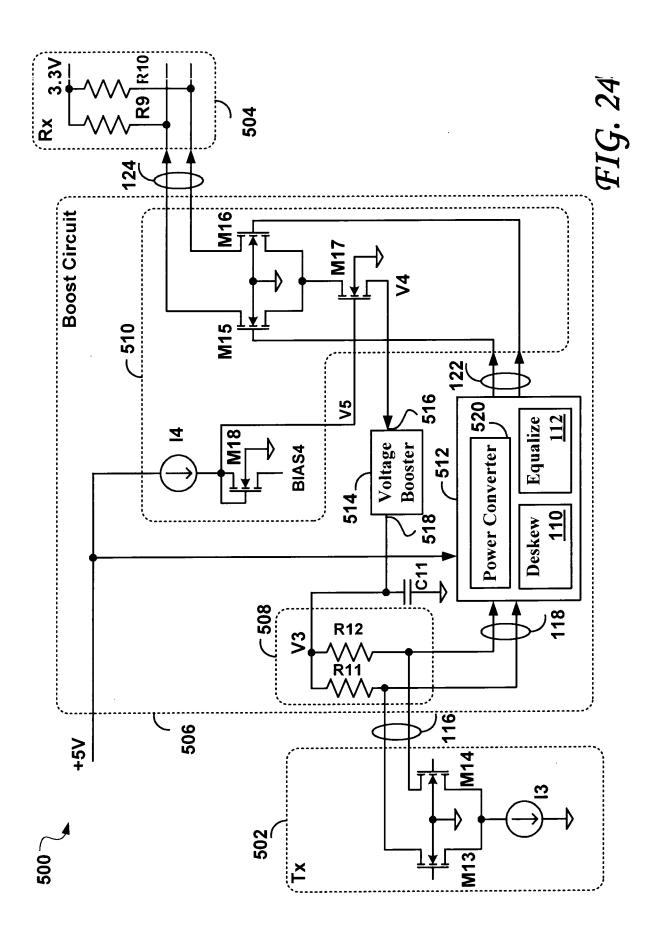

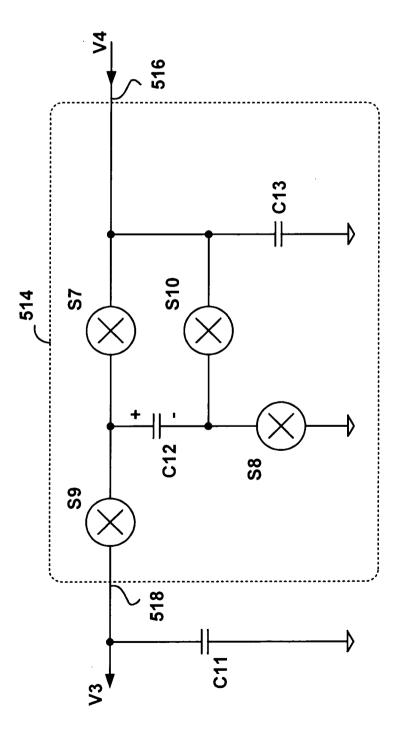

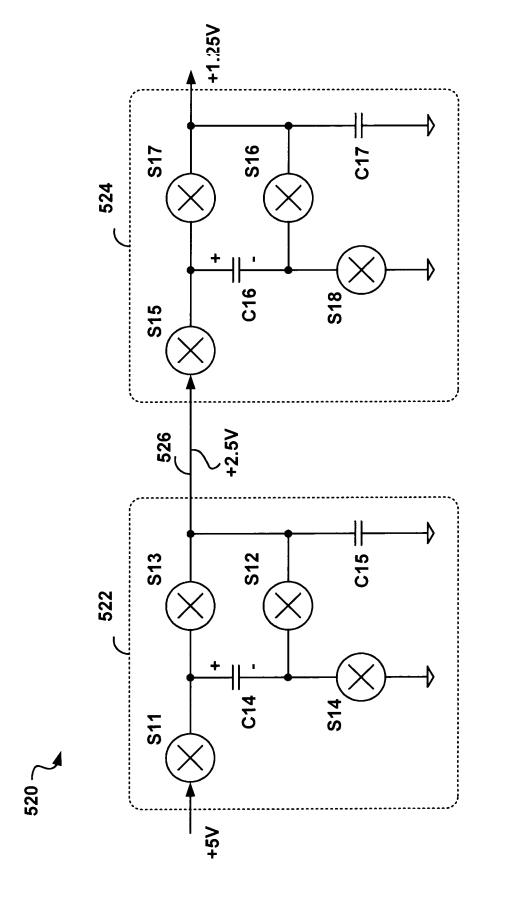

**Figure 24** shows a system diagram of a representative channel 500, including an optional voltage booster 514, and a power converter 520;

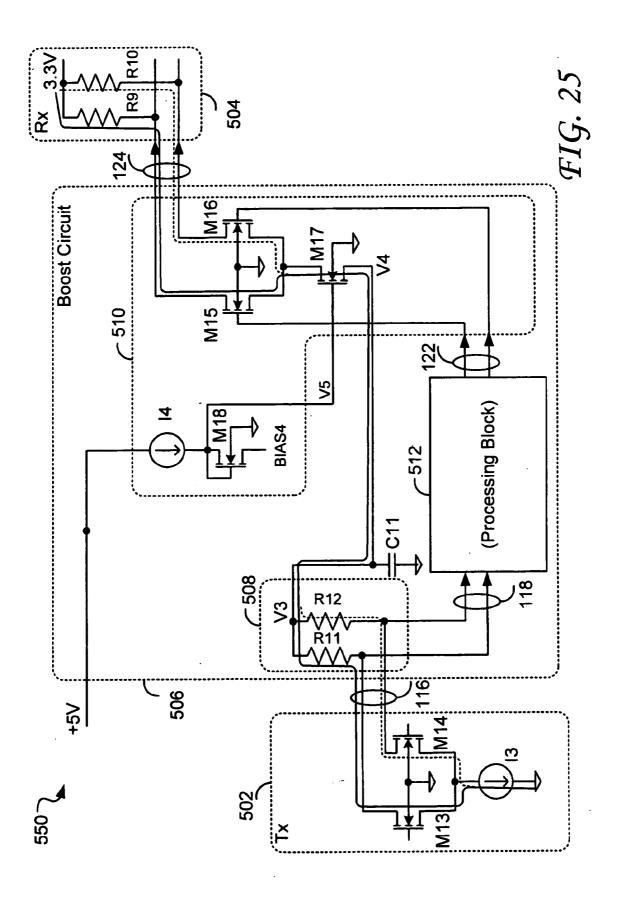

Figure 25 is a simplified copy 550 of the representative channel 500 of Fig. 24;

Figure 26 shows a block diagram of the optional voltage booster 514 of Fig. 24;

Figure 27 shows a block diagram of the power converter 520 of Fig. 24;

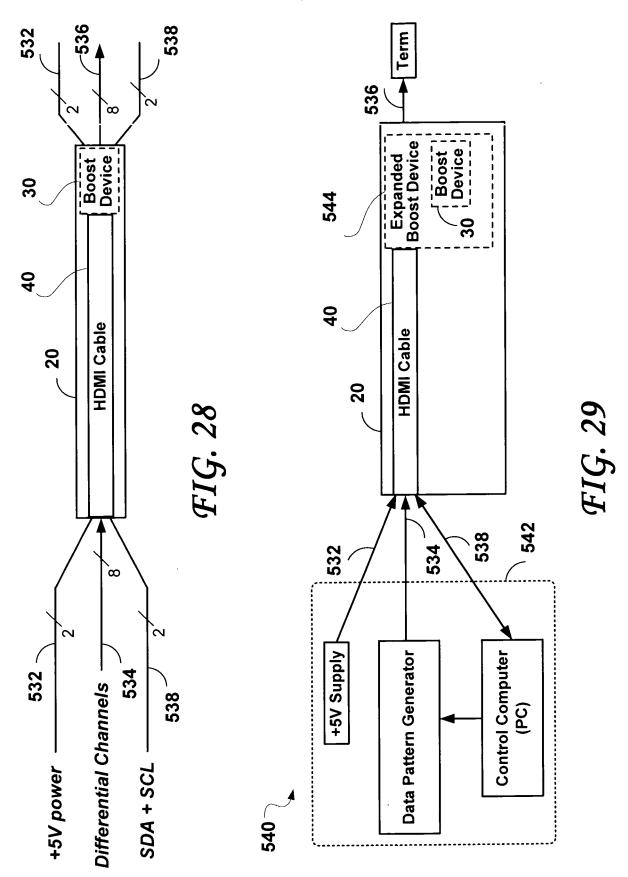

**Figure 28** illustrates the improved HDMI cable 20 of Fig. 4, showing external connections that are available for use in calibrating the cable;

Figure 29 shows a Real Time Configuration 540, including an expanded boost device 544 used

in the Real Time Cable Calibration method;

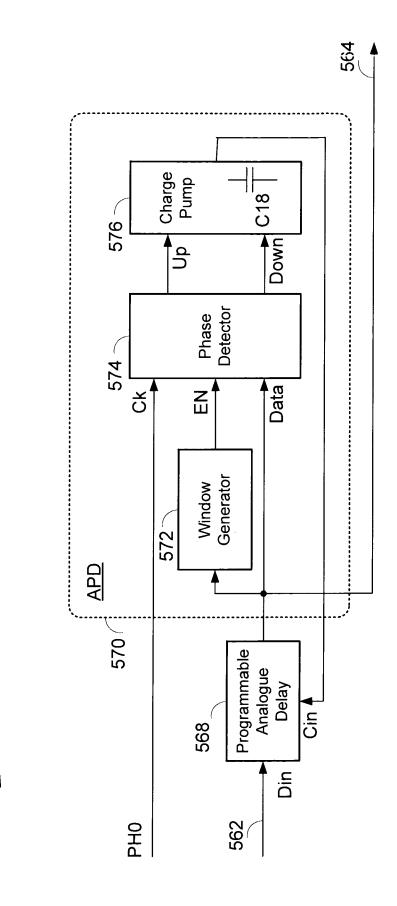

**Figure 30** shows a simplified block diagram of the expanded boost device 544 of Fig. 29, including a Linear Phase Compensator 554, an Oversampling and Reclocking block 556, and a Training Function 558;

Figure 31 shows a block diagram of an exemplary implementation of the Linear Phase Compensator 554 of Fig. 30, including a Programmable Analogue Delay 568;

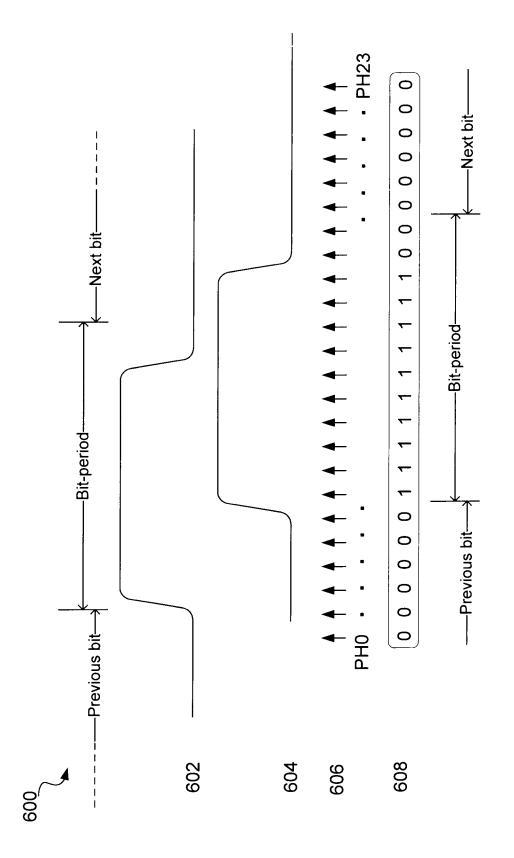

**Figure 32** illustrates data phase shifting in the Programmable Analogue Delay 568 of Fig. 31, and oversampling in the Oversampling and Reclocking block 556 of Fig. 30;

**Figure 33** shows a simplified block diagram of the preferred embodiment 700 of the Training Function 558 of Fig. 30;

Figure 34 shows a high level flow chart of a training run method 800, depicting the operation of the Training Function 558 of Fig. 30;

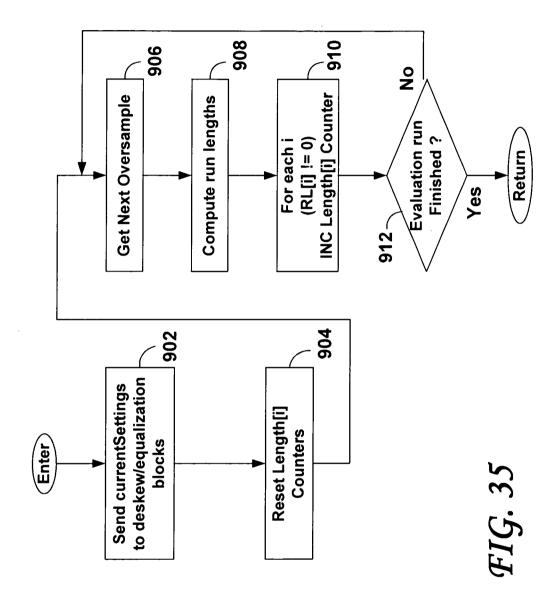

**Figure 35** shows a flow chart of an exemplary evaluation run method 900 further detailing the step 806 of the training run method 800 of Fig. 34;

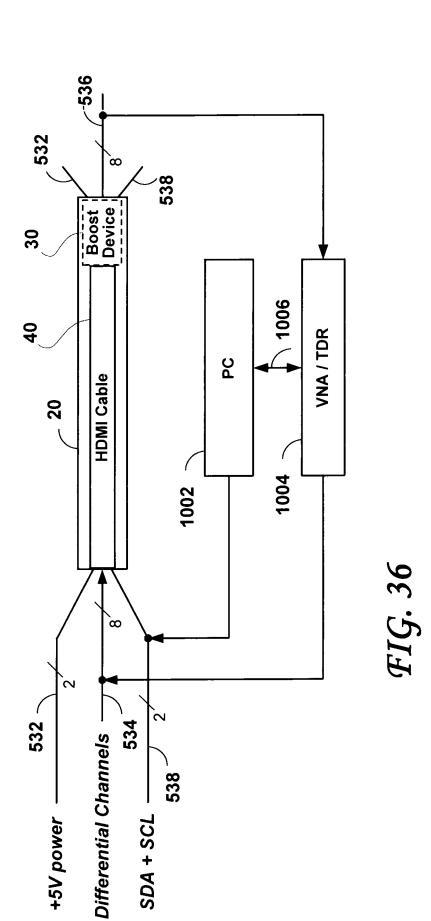

Figure 36 shows a generic test set up 1000 for Frequency Domain and Time Domain Calibration methods;

**Figure 37** shows a simplified high level flow chart of an calibration method 1100 that may be used with the generic test set up 1000 of Fig. 36 in calibrating the Boost Device 30 in the improved HDMI cable 20 of Fig. 4;

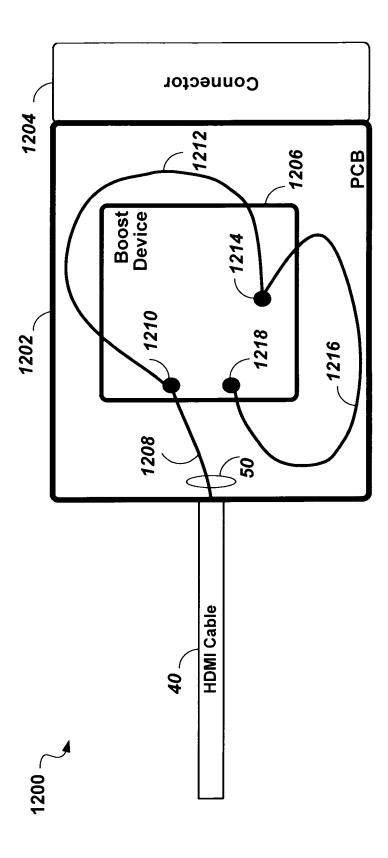

Figure 38 shows an alternative embodiment of the invention, in the form of a modified improved HDMI cable 1200; and

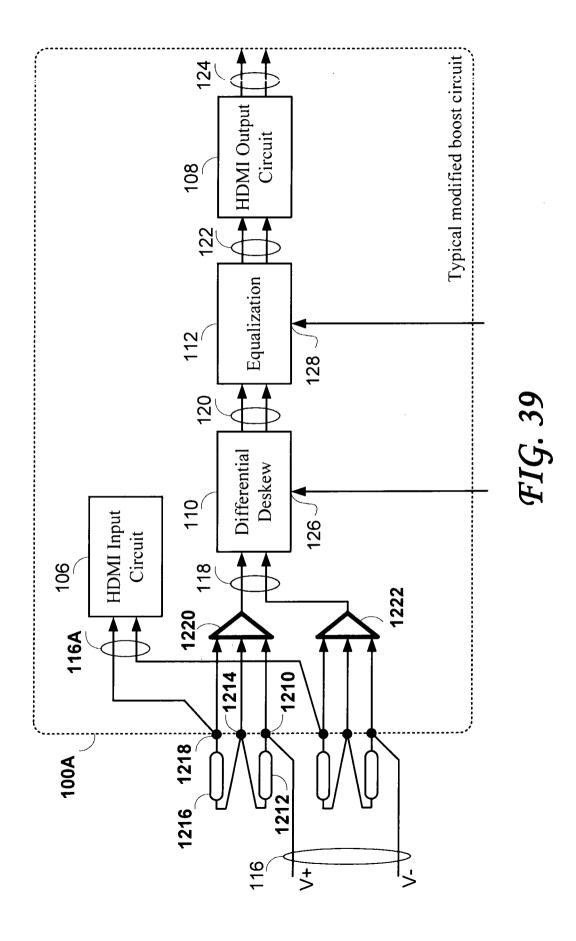

Figure 39 shows a modified boost circuit 100A of the modified boost device 1206.

## DETAILED DESCRIPTION OF THE EMBODIMENTS OF THE INVENTION

Figure 3 shows a prior art HDMI (High-Definition Multi-Media Interface) system, including a HDMI transmitter Tx (HDMI Source Device), a HDMI receiver Rx (HDMI Sink Device), and an HDMI cable connecting the Tx and the Rx.

**Figure 4** shows an HDMI system 10 including an improved HDMI cable 20 according to an embodiment of the present invention.

The HDMI system 10 includes the HDMI transmitter Tx (HDMI Source Device), the HDMI receiver Rx (HDMI Sink Device), and the improved HDMI cable 20 of the embodiment of the present invention, connecting the Tx and Rx.

The improved HDMI cable 20 comprises an embedded boost device 30, details of which are described in the following, and a basic (passive) HDMI cable 40. The boost device 30 is

- -

located near the end of the improved HDMI cable 20 closest to the HDMI receiver Rx. Without limiting the generality of the application, the improved HDMI cable 20 may be used to connect a DVD player (an example of an HDMI Source Device) to a Television Screen (an example of an HDMI Sink Device).

Figure 5 is a block diagram illustrating the improved HDMI cable 20 that extends between the HDMI transmitter Tx and the HDMI receiver Rx, including the boost device 30 of Fig. 4. Also shown are HDMI inputs 50 extending from the Tx to the boost device 30 through the basic HDMI cable 40, HDMI outputs 52 extending from the boost device 30 to the Rx, and a group of Other HDMI Signals 54 extending directly from the Tx to the Rx through the basic HDMI cable 40. The basic HDMI cable 40 includes the HDMI inputs 50 and the Other HDMI Signals 54.

The HDMI inputs 50 provide the connections that couple HDMI signals from the HDMI transmitter Tx (Fig. 4) over the wires of the basic HDMI cable 40 to inputs of the boost device 30. The HDMI inputs 50 include four (4) signal pairs:

- a Transition Minimized Differential Signaling (TMDS) Channel Input 0;

- a TMDS Channel Input 1;

- a TMDS Channel Input 2; and

- a Clock Channel Input.

Similarly, the HDMI outputs 52 include four (4) signal pairs of boosted HDMI signals:

- a TMDS Channel Output 0;

- a TMDS Channel Output 1;

- a TMDS Channel Output 2; and

- a Clock Channel Output.

The HDMI outputs 52 couple the boosted HDMI signals from the boost device 30 over a short connection to the HDMI receiver Rx.

A Programming input 56 and a +5V Power signal 58 is coupled from the Other HDMI Signals 54 to the boost device 30. Not shown in the figure are physical features such as device carrier(s) and connectors which may be part of the improved HDMI cable 20.

The boost device 30 includes a number of channel boost circuits 100, a parameter memory 102. In the preferred embodiment of the invention, the boost device includes four (4) channel boost circuits 100 as shown in Fig. 5, each to boost the signal of one of the TMDS Channel 0, the TMDS Channel 1, and the TMDS Channel 2.

Each channel boost circuit 100 includes an HDMI Input Circuit 106 and an HDMI Output Circuit 108. Each channel boost circuit 100 advantageously further includes a

Differential (intra-pair) Deskew Circuit 110 for adjusting an existing time skew of the two polarities of a differential data signal propagating through the basic HDMI cable 40 and an Equalizer Circuit 112 to compensate for the limited bandwidth characteristics of the basic HDMI cable 40. Each channel boost circuit thus provides a transfer function from the respective HDMI Input to the corresponding HDMI Output with characteristics designed to compensate for the degradation of the corresponding differential pair in basic cable 40.

The boost device 30 may be powered by the +5V Power signal 58, and by power derived from the HDMI Outputs 52 as will be described in detail below. The power for the operation of the boost device 30 is entirely derived from signals carried in the improved HDMI cable 20, and supplied by the HDMI transmitter Tx and/or the HDMI receiver Rx.

In a cable carrying differential signals, i.e. where each signal is carried over a pair of wires, manufacturing tolerances commonly result in slight differences between the lengths of the wires and connectors used for each channel. The result will be a different delay through the cable for each of the pair. Such differential (intra-pair) skew degrades the received signal (see Figures 2A and 2B above). Elimination of intra-pair skew may be accomplished by adding delay to the signal passing through the shorter of the pair of wires by the appropriate amount so that it is aligned with the signal passing through the longer of the pair. In accordance with the embodiments of present invention, intra-pair skew is eliminated with the help of the Differential Deskew Circuit 110, which is digitally programmable as will be described in the next sections. The parameter memory 102 is used to retain the deskew settings of the Differential Deskew Circuit 110, once they are determined in a programming (calibration) setup method.

Similarly, cables present different bandwidth characteristics, which depend on the length and the physical construction of the cable. The limited bandwidth may be compensated (to some extent) by the Equalizer Circuit 112 which is also digitally programmable. The equalizer settings may similarly be retained in the parameter memory 102. The proper settings for both the Differential Deskew Circuit 110 and the Equalizer Circuit 112 may be determined in a programming (calibration) setup at the time of production, and loaded into the parameter memory 102 through the Programming Input 56. The programming setup method will be described in more detail further below (Figs 29 to 37).

**Figure 6** shows a more detailed block diagram of a single instance of the channel boost circuit 100 of Fig. 5, comprising the HDMI Input circuit 106, the Differential Deskew circuit 110, the Equalization circuit 112, and the HDMI Output circuit 108.

The input to the HDMI Input circuit 106 is a raw input signal (pair) 116 (one of the HDMI Inputs 50, Fig. 5). The HDMI Input circuit 106 outputs a "recovered signal" (pair) 118

that is input to the Differential Deskew circuit 110. The Differential Deskew circuit 110 outputs a "deskewed signal" (pair) 120 that is input to the Equalization circuit 112. The Equalization circuit 112 outputs an "equalized signal" pair 122 that is input to the HDMI Output circuit 108. And finally, the HDMI Output circuit 108 outputs a "boosted signal" (pair) 124 that is one of the HDMI Outputs 52 (Fig. 5).

Also shown in Fig. 6 is the Parameter Memory 102, which is shared among all channel boost circuits 100 of the boost device 30. It is connected to a deskew parameter input 126 of the Differential Deskew circuit 110, and separately to an equalization parameter input 128 of the Equalization circuit 112.

### **Differential Deskewing Circuit 110**

As indicated above, the intra-pair differential skew delay may be compensated by inserting a delay element having a delay of Td in the path of V+ (in the case of the example of Fig. 2B), or in the path of V- in the opposite case (if the input V+ signal was delayed with respect to V-), or neither if there was no skew present.

Figure 7 shows a simplified block diagram of the Differential Deskew Circuit 110 of Fig. 6 in which the differential skew is removed (compensated). The same reference numerals are used to indicate the differential inputs and outputs (the recovered signal 118 and the deskewed signal 120 respectively, each with a positive [V+] and a negative [V-] terminal), and the control input for the deskew parameters (126).

As shown in Fig. 7, the Differential Deskew circuit 110 includes an adjustable delay 300 with a (single-ended) input 302 and an output 304, and six ON/OFF switches S1 to S6. The adjustable delay 300 includes a number of delay stages 306. The switch S1 is connected between the positive terminal of the differential input (the recovered signal 118 V+) and the positive terminal of the differential output (the deskewed signal 120 V+). Similarly, the switch S6 is connected between the negative terminal of the differential input (the recovered signal 118 V-) and the negative terminal of the differential output (the deskewed signal 120 V-). The switches S2 and S4 are connected between the input 302 of the adjustable delay 300 and the positive (V+) and negative (V-) terminals respectively of the recovered signal 118. Similarly, the switches S3 and S5 are connected between the output 304 of the adjustable delay 300 and the positive (V+) and negative (V-) terminals respectively of the deskewed signal 120.

The scheme allows the single adjustable delay 300 to correct for both positive and negative differential skew. In effect, the single adjustable delay 300 is sufficient to compensate positive or negative differential skew (where either the positive signal or the negative signal is

delayed with respect to the other), by switching it (the adjustable delay 300) into either the negative or the positive signal path respectively. For example, to pass the positive signal V+ through the adjustable delay 300 (which is made of a cascade of delay units, to be described in detail below) the switch states are as follows: S1=OFF, S2=ON, S3=ON, S4=OFF, S5=OFF, and S6=ON. To pass V- through the adjustable delay 300 the switch states are as follows: S1=ON, S2=OFF, S3=OFF, S4=ON, S5=ON, S6=OFF. To switch the adjustable delay 300 out of both the V- and the V+ paths, thus providing no adjustment of the differential delay, the switch states are as follows: S1=ON, S2=OFF, S3=OFF, S4=OFF, S5=OFF, S6=ON.

The solution of the deskew problem presents two challenges. The first is to make a suitable delay, the second is to tune the delay. Making the delay is a challenge because the unit should have a wide enough bandwidth to pass the signals but at the same time the delay block has to present a useful delay. The wide bandwidth of a single delay stage naturally results in little delay, so a cascade of stages is required to achieve a sufficient delay.

A cascade of digital delay stages, including digital switches and a decoder to provide binary addressable selection of the overall delay, are described in United States Patent 6,268,753. However, the present invention requires an adjustable delay circuit to delay a high-speed analog signal.

Issues to be solved with a cascade of analog delay stages in the proposed configuration of Fig. 7 for differential skew compensation, include the need to provide unity gain, as well as preserve the high bandwidth required.

Among the prior art, several digital delay compensation schemes are disclosed, but only few circuits providing adjustable delay for analog signals. For example, the use of a follower circuit in parallel with a gain stage to boost the high frequency response of a digital circuit is taught in United States Patent 5,739,713. United States Patent 6,525,568 teaches a phase shifting (delay) stage that includes an RC (resistor-capacitor) element followed by parallel gain stages of nominally -1 and +2 gain, their outputs added together to provide overall unity gain with a particular complex frequency transfer function. In the United States Patent Application 20050083130 a high performance amplifier is proposed which includes a delay element to compensate for signal propagation delay that may exist in alternative signal paths.

Figure 8 shows the preferred embodiment of the adjustable delay block 300 of Fig. 7 as a cascade of eight analog delay stages ("Delay Units") 306 in combination with an analog selector stage 308 as a solution to implement the adjustable delay 300. The eight delay units 306 are connected in series (cascaded), the output of each delay unit 306 being input to the analog selector stage 308. The first delay unit 306 of the cascade provides the input of the adjustable

delay 300 (IN 302).

The deskew parameters control signal (deskew parameter input 126) includes a 3-bit binary signal connected to the analog selector stage 308 for selecting one of its inputs to be switched through to the output of the adjustable delay 300 (OUT 304).

An exemplary complete circuit of the single delay unit 306, which may be cascaded to provide a unit of delay each, for the adjustable delay 300 is shown in Fig. 18 below.

To help in understanding the circuitry of the single delay unit 306, a step-by-step description of the issues to be solved, and possible solutions, is presented first.

Figure 9 shows a simple RC delay circuit that may be used to introduce the delay (Td) of Fig. 2B. The circuit of Fig. 9 is a single ended circuit comprising a resistor R1, a capacitor C1, and input and output terminals (signals Vin and Vout), as well as a ground (0). The capacitor C1 is connected between Vout and ground, and the resistor is connected between Vin and Vout. Making a circuit with an RC delay as shown in Fig. 9 will succeed in delaying the signal but it will also filter the signal.

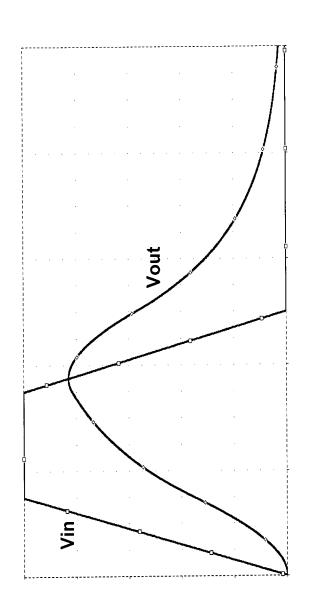

The impact of the RC circuit of Fig. 9 on a pulse is seen from simulation results shown in **Figure 10**. Fig. 10 shows two simulated wave forms, a trapezoid input pulse Vin, and an output pulse (Vout), that results from passing the trapezoid input pulse through the simple RC delay circuit of Fig. 9. The trapezoid input pulse (the signal Vin) is delayed and filtered (distorted) into the output signal Vout. The delay and the filtering action are clearly seen. While the delay is desirable, the filtering action causes dispersion and distortion of the pulse.

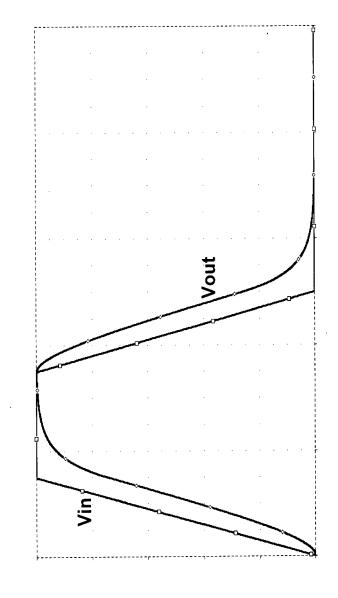

To reduce the filtering action of the circuit the RC time constant may be reduced. The simulated result is shown in **Figure 11**. The simulation shown in Fig. 11 is analogous to the simulation shown in Fig. 10, but with a reduced time constant in the simulated delay circuit. Reducing the time constant helps to increase or maintain the bandwidth (note the slopes of both the input and output pulses) but as shown in Fig. 11 the signal delay introduced is lower.

In the simulation of Fig. 11 the pulse width is 0.7 second and the RC time constant in the circuit is 79ms. The long pulse duration and the long RC time constant were chosen merely for convenience in the simulations to study the effects of circuit choices, and are not representative of the time scales of the embodiment.

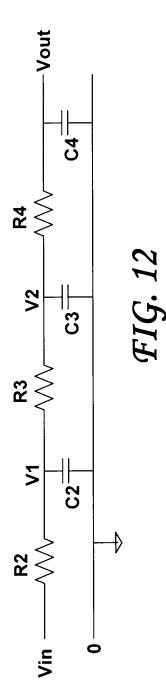

One method of attempting to regain the delay (as shown in Fig. 10 with respect to the circuit of Fig. 9 with the original time constant) is to cascade a number of RC stages. This is shown in **Figure 12**. Shown in Fig. 12 is a delay circuit made from a cascade of three RC stages, comprising the components R2, C2, R3, C3, R4, and C4, each RC stage having individually the same time constant of 79ms. The signals after the first and second stages are labeled V1 and V2

respectively. The input and output of the circuit as a whole are labeled Vin and Vout.

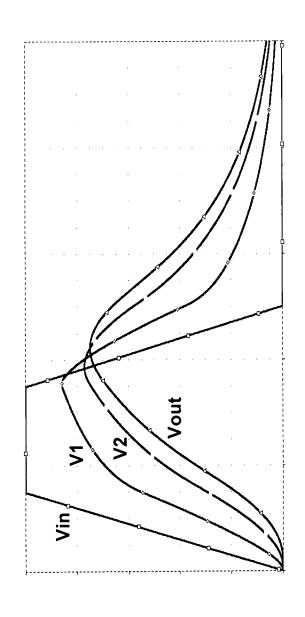

The result of simulating the circuit of Fig. 12 with a trapezoidal input pulse is shown in Figure 13 which shows the waveforms of the trapezoidal input pulse (Vin) and the waveforms of the delayed pulses after each stage of the circuit of Fig. 10 (V1, V2, and Vout). The resulting final waveform Vout is delayed but it is considerable reduced in amplitude and dispersed.

In order to remove the loading effect of subsequent stages, each stage may be buffered as shown in **Figure 14**. Shown in Fig. 14 is the same cascaded delay circuit as in Fig. 12, but two buffers (amplifiers) are inserted, a buffer "Buf1" between R1 and R2, and a buffer "Buf2" between R2 and R3. As a result, the intermediate signals V1 and V2 are not attenuated by the loads of the subsequent stages.

The simulation results for the circuit of Fig. 14 are shown in **Figure 15**. They show that the circuit arrangement of Fig. 14 achieves the desired goal of introducing significant delay while the distortion in the pulse is kept to a minimum. In this simulation, the 0.7 second trapezoidal input pulse is delayed by approximately 77ms per stage.

In a mathematical sense, the pulse has been transformed by a cascade of single pole unity gain stages, the transfer function of each stage being;

H(s) =

$$1/(1+s/p)$$

where p[Rads] =  $1/(RC)$

or p[HZ] is  $1/(2\pi RC)$

The goal of the circuitry is to delay the pulse by up to about half the pulse width (bit width). In the case illustrated in the simulation of Fig. 15, the required delay would be approximately 0.35 seconds. To achieve this delay with the scheme shown in Fig. 14, this would require approximately five stages. In the simulation shown in Fig. 15 the RC time constant is set to 79ms which sets the pole frequency at  $1/(2\pi79\text{ms}) = 2\text{Hz}$ . Thus, with a pulse width of 0.7 seconds (the input pulse Vin) a stage with a pole frequency of 2Hz will produce suitable delays with acceptable filtering on the pulse. A simple approximation to calculate the position of the pole for a system with a bit rate of N bits per second (Nbps) is to set the pole in each stage at 3\*N Hz. For example, with a data rate of 1Gbps, a stage with a pole at approximately 3GHz would be needed.

Having shown how an appropriate delay per stage may be achieved using simple RC stages, it remains to be shown how a suitable buffer amplifier (Buf1, Buf2 in Fig. 12) may be constructed. To make a unity gain buffer with unity gain up to 3GHZ is a challenge even on an advanced CMOS processes. A starting point would be to use a simple follower circuit as shown in **Figure 16**. The simple follower circuit of Fig. 16 includes an N-channel MOS field-effect

transistor (MOSFET) M1 connected in series with a current source I1. The drain of the transistor M1 is connected to ground (0), while the positive terminal of the current source I1 connects to the supply voltage VDD. The circuit input (IN) is connected to the gate of the transistor M1, and its source provides the circuit output (OUT).

In this weil-known circuit the output OUT follows the input IN with a gain of approximately one. The first limitation with this circuit is that the output is typically level shifted by 0.6 volts or so. This level shifting is a problem if a number of stages are to be cascaded because the successive level shifts will cause the output to rise to the supply voltage and thus the signal is clipped. To solve this limitation, AC-coupling is added to the simple follower as shown in Fig. 17. The circuit shown in **Figure 17** is an AC-coupled follower circuit, derived from the simple follower circuit of Fig. 16 by the addition of a capacitor C5 between the circuit input (IN) and the source of the transistor M1, and a resistor R5 between the source of the transistor M1 and a bias supply "BIAS" that provides a positive bias voltage.

With AC-coupling, the fact that the output of the stage is level shifted up from the bias level set by "BIAS" in Fig. 17 becomes unimportant when stages are cascaded, because this level shift is stored as a constant drop across the input capacitor of the next stage. This essentially resets the average input voltage at each stage to be the bias voltage set by the bias supply (BIAS) shown in Fig. 17.

A further limitation of this circuit comes from the non-zero output conductance of the transistor M1. The gain of the follower is given by gm1/(gm1+gds1). Here gm1 is the small signal transconductance and gds1 is the small signal output conductance of M1. Clearly, for all values of gds1 greater than zero the gain of the stage is less than one. When fast wideband circuits are required, the length of the MOSFET M1 is reduced to close to minimum. This causes gds1 to increase to a point where the gain is now tending to 0.9 or so. A cascade of these stages would dramatically reduce the magnitude of the incoming signal.

One possible architecture which corrects for this reduced stage gain is shown in **Figure** 18 which illustrates a simplified block diagram of a buffered delay stage 400, which may be an embodiment of the delay unit 306 of the adjustable delay 300 (Fig. 6).

The buffered delay stage 400 comprises a unit gain amplifier (buffer) 404. The buffer 404, having an input 410 and an output 412.

The buffer 404 includes two amplifiers in parallel, a follower stage 414, having a gain of approximately 0.9 and a supplementary stage 416 with a gain of approximately 0.1, both amplifiers having the same frequency response (expressed mathematically by the pole 1/(1+s/p). Both amplifiers (414 and 416) share the input 410 of the buffer 404, and their outputs are

summed into the output 412.

The buffered delay stage 400 provides an inherent delay (implicit in the poles p of the transfer functions), and by virtue of the amplifiers, provides the isolation from the next delay element in the cascade, as described earlier (Fig. 14). Note that in very high-speed operation, no explicit RC delay element is needed if the (by necessity limited) frequency response of the buffer 404 is designed to provide the required delay.

The buffered delay stage 400 receives the input signal VIN of the buffered delay stage 400 connected to the input 410 of the buffer 404; and the output 412 of the buffer 404 generates the output signal VOUT of the buffered delay stage 400.

The preferred embodiment of the buffer 404 including its component amplifiers (the follower stage 414 and the supplementary stage 416), is shown in detail in **Figure 19**, as a circuit based on an N-well CMOS process.

The follower stage 414 is an AC-coupled circuit, similar to the AC-coupled follower circuit of Fig. 17. It comprises a P-channel follower transistor M2, a biasing resistor R6, a coupling capacitor C6, and a bias supply "BIAS1".

The supplementary stage 416 includes a N-channel amplifying transistor M3, and two P-channel transistors M4 (functioning as a diode) and M5 (functioning as a current source); a biasing resistor R7; a coupling capacitor C7; a shunt capacitor C8; and a bias supply "BIAS2".

The bias voltages of "BIAS1" and "BIAS2" are adapted to the circuit functions and the technology as required.

The input 410 of the buffer 404 is connected through the coupling capacitor C6 to the gate of the transistor M2, and through the coupling capacitor C7 to the gate of the transistor M3. The positive terminal of the bias supply "BIAS1" is fed to the gate of the transistor M2 through the biasing resistor R6. Similarly, the positive terminal of the bias supply "BIAS2" is fed to the gate of the transistor M3 through the biasing resistor R7. The negative terminals of "BIAS1" and "BIAS2", the drain of the transistor M2, the source of the transistor M3, and one terminal of the shunt capacitor C8 are connected to ground. The other terminal of the shunt capacitor C8 is connected to the gate of the transistor M3. The source of the follower transistor M2 is connected to the drain of the current source transistor M5 and the output 412 of the buffer 404. The drains of the transistors M3 and M4 are connected together, and also to the gate of the transistor M4. The sources of the transistors M4 and M5 are connected to the supply voltage VDD.

Functionally, the signal of the input 410 of the buffer 404 is amplified by the follower stage 414 with a gain of about 0.9, the transistor M5 (in the supplementary stage 416) providing a current source load to the follower transistor M2. The function of the supplementary stage 416

is to amplify a portion of the same input signal (the portion being defined by the ratio of the coupling capacitor C7 to the shunt capacitor C8) in the transistor M3 into a varying current that is mirrored through the transistors M4 and M5, and so providing a varying current source load to the follower transistor M2. Thus, both the follower stage 414 and the supplementary stage 416 contribute to the signal at the output 412 of the buffer 404, their individual contributions effectively being added as indicated in Fig. 18 above.

The gain of the P-channel follower circuit (414) is essentially unity except for the output conductance (gds) of the P-channel device (M2). Because of the requirement for speed a short P-channel device is required and thus the device has a large output conductance and the gain falls toward 0.9. With a cascade of 5 stages the signal would have fallen to 60% of its original value. To boost the gain of the simple follower at channel data rates, the parallel signal path is provided in the form of the supplementary stage 416.

As described above, the buffer 404 includes a second path (the supplementary stage 416) for the input signal (410) to arrive at the output 412. This extra path is through C7, M3, M4, and M5. In this path, the high frequency input signal is passed though C7 and a fraction of the signal is presented at the gate of M3. This fraction is changed by changing the size of the shunt capacitor C8. The current in M3 is set to a nominal value with a bias circuit ("BIAS2"). When the input signal arrives at the gate of M3 it varies the current in M3. This current variation is sourced by the diode connected device (M4) which then mirrors the current change to M5. Finally M5 changes the current in M2 so the end result is that changing the input signal changes the current in M2. Changing the current level in M2 changes the overdrive in the device and thus changes the output voltage. In summary a positive change at the input 410 causes a positive change at the output 412 due to current steering in the parallel path. At the same time there is a positive change at the output due to the simple follower action through M2. The overall change in the output is calculated by summing the contributions from the Parallel (supplementary stage 416) and Main (follower stage 414) paths. If the main path is producing a gain of 0.9 the parallel path may be tuned to provide a gain of 0.1 by changing the value of C8. Once adjusted to unity, the gain of the stage remains stable over Process, Supply Voltage, and Temperature to within about two percent of its nominal value.

The buffer circuit 404 of Fig. 19 meets the following requirements.

- An overall gain of unity and thus cascading does not amplify or reduce the signal;

- Capable of very wideband operation (pole at 2GHz to 10GHz) for minimal distortion;

- Input and Output levels of a cascade of stages stay within a suitable range.

Some typical values for the implementation of the buffer 404 are: R6=200k, R7=200k, C6=200f, C7=200f, C8 is tuned to adjust the overall gain of the circuit to unity.

An embodiment of the buffer, equivalent to the buffer circuit 404 shown in Fig. 19, may be created by starting with a simple N-channel follower (instead of the P-channel follower of Fig.16, that has led to the complete buffer implementation shown here in Fig. 18). The simple N-channel follower is shown in **Figure 20**.

For a CMOS process with a P-Well technology the configuration shown in Fig. 19 would be the preferred implementation in that the bulk of the N-channel Mosfet would be free to be tied to the source as shown in Fig. 20. For the more standard CMOS processes with N-Well technology the circuit of the buffer of Fig. 19 would cause additional challenges because the bulk connection on the N-channel MOSFET is tied to ground. This grounded bulk causes a varying source-to-bulk potential in the transistor and further degrades the gain of the stage from 0.9 and this reduced gain makes it more difficult to maintain the overall gain of the stage at unity.

An alternative configuration for making the buffer stage for the delay stage 306 is shown in **Figure 21**, which shows a modified buffer 404B. The modified buffer 404B is similar to the buffer 404 and also uses two parallel paths for the input (410) to output (412) signal, i.e. the follower stage 414 and a modified supplementary stage 416B. The modified supplementary stage 416B performs the same function as the supplementary stage 416, but is implemented somewhat differently.

The supplementary stage 416B comprises five N-channel transistors (M6, M7, M8, M9, and M10) and two P-channel transistors (M11, M12), a biasing resistor R8, a coupling capacitor C9, a shunt capacitor C10, and a current sink I2.

The components of the supplementary stage 416B are variously connected to each other, ground, and VDD as listed in the following:

- the sources of the N-channel transistors (M6 to M10) and one lead of the shunt capacitor C10 are connected to VDD;

- the sources of the P-channel transistors (M11 and M12) as well as the negative terminal of the current sink I2 are connected to ground;

- the transistors M6, M9, and M11 are each connected in diode mode, i.e. their gates are shorted to their drains;

- the drain/gate of the transistor M6 is connected to the positive terminal of the current source I2, the gate of the transistor M7, and through the biasing resistor R8 to the gate of the transistor M8;

- the drain of the transistor M7 is connected to the drain/gate of the transistor M11 and to the

gate of the transistor M12;

- the gate of the transistor M8 is further connected to the shunt capacitor C10, and through the coupling capacitor C9 to the input signal (410);

- the drain of the transistor M8 is connected to the drain/gate of the transistor M9, to the gate of the transistor M10, and the drain of the transistor M12; and lastly

- the drain of the transistor M10 is connected to the drain of the transistor M2 of the follower stage 414 as well as the output 412.