(12)

## Patentschrift

(21) Aktenzeichen: **196 30 334.6**

(22) Anmelddetag: **26.07.1996**

(43) Offenlegungstag: **06.02.1997**

(45) Veröffentlichungstag

der Patenterteilung: **05.08.2010**

(51) Int Cl.<sup>8</sup>: **H01L 21/84 (2006.01)**

**H01L 27/12 (2006.01)**

**G02F 1/136 (2006.01)**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

7-219532      04.08.1995      JP

8-139456      08.05.1996      JP

(72) Erfinder:

Yamazaki, Shunpei, Tokio/Tokyo, JP; Koyama, Jun, Sagamihara, Kanagawa, JP

(73) Patentinhaber:

Semiconductor Energy Laboratory Co., Ltd.,

Atsugi, Kanagawa, JP

(56) Für die Beurteilung der Patentfähigkeit in Betracht

gezogene Druckschriften:

US      54 22 293

US      50 19 001

(74) Vertreter:

Grünecker, Kinkeldey, Stockmair &

Schwanhäusser, 80802 München

(54) Bezeichnung: **Verfahren zum Herstellen einer Halbleitervorrichtung**

(57) Hauptanspruch: Verfahren zum Herstellen einer Halbleitervorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten Verdrahtung (100) einschließlich einer Gateelektrode (110) für einen Dünnpfilmtransistor über einem Substrat;

Bilden eines Zwischenschichtisolators (206) auf der ersten Verdrahtung;

Bilden einer zweiten Verdrahtung (102) auf dem Zwischenschichtisolator, wobei die zweite Verdrahtung entweder mit einem Sourcebereich (211) oder einem Drainbereich des Dünnpfilmtransistors verbunden ist;

Bilden eines zweiten Zwischenschichtisolators (207) auf der zweiten Verdrahtung;

Bilden eines leitfähigen Films (214) auf dem zweiten Zwischenschichtisolator; und

Strukturieren des leitfähigen Films durch Ätzen;

wobei die erste und die zweite Verdrahtung wenigstens während der Erzeugung des zweiten Zwischenschichtisolators und des leitfähigen Films miteinander kurzgeschlossen sind;

wobei wenigstens eine der ersten und zweiten Verdrahtungen (100, 114) mit einer Entladungsstruktur (601, 602, 605, 701, 702, 703) versehen ist, die so gestaltet ist, dass sie lokal die Impedanz erhöht oder erniedrigt, um die Ausbreitung von Hochfrequenzimpulsen durch die...

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf ein Verfahren zum Herstellen einer integrierten Dünnfilm-Halbleitervorrichtung. Die hier offengelegte Erfindung bezieht sich ebenfalls auf ein Verfahren zum Herstellen einer Flüssigkristallanzeige des aktiven Matrixtyps.

**[0002]** Flüssigkristallanzeigen des aktiven Matrixtyps sind allgemein bekannt. Sie besitzen einen Aufbau, bei dem ein Dünnfilmtransistor an jeder Pixelelektrode vorgesehen ist, die auf einem Glas in einer Anzahl von mehreren Hunderttausenden angeordnet sind. Der für jede Pixelelektrode vorgesehene Dünnfilmtransistor besitzt die Funktion, die in die Pixelelektrode hineinfließende und aus der Pixelelektrode herausfließende Ladung zu steuern.

**[0003]** Ein weiterer Aufbau ist bekannt, in dem ein Dünnfilmtransistorschaltkreis (als "Treberschaltkreis" bezeichnet) zum Antreiben der Dünnfilmtransistoren, die für die Pixelelektroden vorgesehen sind, auf ein- und demselben Glassubstrat integriert ist. Dieser Aufbau wird als "peripher integrierter, aktiver Matrixtyp" bezeichnet.

**[0004]** Bei der Herstellung einer solchen Flüssigkristallanzeige des aktiven Matrixtyps tritt ein Problem auf, bei dem einige der auf dem Glassubstrat integrierten Dünnfilmtransistoren eine Fehlfunktion zeigen.

**[0005]** Die Erfinder haben dieses Problem aktiv studiert und folgendes herausgefunden. Wenn eine integrierte Halbleitervorrichtung, wie etwa eine Flüssigkristallanzeige des aktiven Matrixtyps, hergestellt wird, wird die Erzeugung von Isolierschichten und Verdrahtungen unter Verwendung von Plasma-CVD-Verfahren oder Kathodenstrahlzerstäubungsverfahrens und Plasmaätzen durchgeführt.

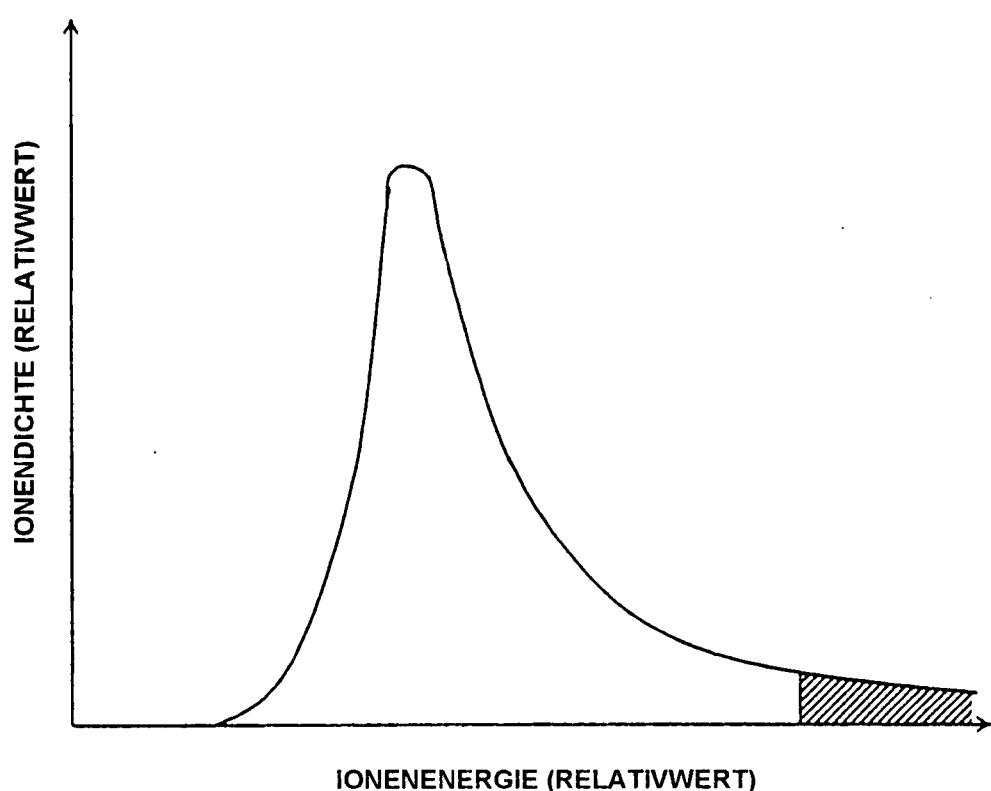

**[0006]** [Fig. 3](#) zeigt schematisch die Beziehung zwischen der Energie (Relativwert) und der Anzahl von Ionen (Relativwert) während der Plasmaerzeugung. Im allgemeinen gibt es nicht wenige hochenergetische Ionen, die eine Plasmabeschädigung des Substrats verursachen, wie durch den gestrichelten Bereich in [Fig. 3](#) gezeigt.

**[0007]** Weiterhin ist es eine Tatsache, dass ein Isolierfilm, der unter Verwendung eines Plasma-CVD- oder Kathodenstrahlzerstäubungsverfahrens hergestellt wurde, ungenügend ist und eine Stehspannung von weniger als einigen zehn Volt oder noch weniger besitzt. Weiterhin besteht insofern ein Problem, als das verwendete Substrat leicht aufgeladen wird, da das Substrat aus Glas oder Quarz besteht, die mehr oder weniger vollständig isolieren.

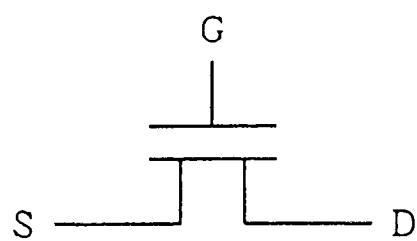

**[0008]** [Fig. 4\(B\)](#) zeigt einen Herstellungsschritt bei der Herstellung eines Dünnfilmtransistors, der symbolisch in [Fig. 4\(A\)](#) gezeigt ist. [Fig. 4\(B\)](#) zeigt einen Zustand bei der Herstellung einer Zwischenschichtisolierfilm 31.

**[0009]** Hier wird angenommen, dass die Zwischenschichtisolierfilm 31 unter Verwendung eines Plasma-CVD- oder Kathodenstrahlzerstäubungsverfahrens hergestellt wird. Es ist klar, dass Ionen mit hoher Energie, wie es in [Fig. 3](#) gezeigt ist, während der Herstellung der Schicht mit der Vorrichtung kollidieren.

**[0010]** Im allgemeinen sind die Sourceelektrode (S) und die Gateelektrode (G) nicht miteinander verbunden. Daher kann die Situation entstehen, dass, wenn auch nur lokal, die Potentialdifferenz zwischen der Sourceelektrode (S) und der Gateelektrode (G) während der Verwendung des Plasmas instantan einen Wert im Bereich von einigen zehn Volt bis zu einigen hundert Volt erreicht.

**[0011]** Die Source- und Gateelektroden sind mit einer aktiven Schicht 32 verbunden, wobei ein Gateisolator 30 dazwischen angeordnet ist. Die Stehspannung des Gateisolators 30, der unter Verwendung eines CVD- oder Kathodenstrahlzerstäubungsverfahrens hergestellt wird, beträgt einige zehn Volt oder weniger. Daher wird der Gateisolator 30 bei der oben beschriebenen Situation elektrisch zerstört.

**[0012]** Dies bewirkt eine Fehlfunktion des Dünnfilmtransistors. Dieses Problem kann durch einen elektrischen Kurzschluss der Source- mit der Gateelektrode gelöst werden, so dass beide während der Herstellung der Zwischenschichtisolierfilm 31 dasselbe elektrische Potential besitzen. Im endgültigen Betriebszustand der Vorrichtung dürfen die Source- und Gateelektrode nicht kurzgeschlossen sein.

**[0013]** Unter Berücksichtigung dieser Tatsache, müssen die Source- und die Gateelektrode in dem in [Fig. 4\(B\)](#) gezeigten Verfahren bis zum letzten Verfahrensschritt kurzgeschlossen sein, und dann müssen sie getrennt werden.

**[0014]** Das Stand-der-Technik-Dokument US 5,019,001 offenbart ein Verfahren zur Herstellung einer Flüssigkristallvorrichtung, wobei Adress- und Datenleitungen über einem Substrat bereitgestellt werden. Ein Bereich für Kurzschlusschaltkreise und ein Bereich, der kurzgeschlossen wird, wird bereitgestellt, um die Adress- und Datenleitungen kurzschließen.

**[0015]** Das Stand-der-Technik-Dokument US 5,422,293 offenbart ein Verfahren zur Herstellung einer TFT-Paneele. Es wird dargestellt, dass eine Metallschicht, die Datenleitungen DL und die Erdlei-

tungen EL bilden, auf einer isolierenden Schutzschicht ausgebildet wird. Danach, wenn die Metallschicht strukturiert wird um die Datenleitungen DL und die Erdleitungen EL zu bilden, wird die Metallschicht in einer Öffnung und ein Kurzschlussbereich einer Kurzschlussleitung geätzt und entfernt.

**[0016]** Es ist eine Aufgabe der vorliegenden Erfindung, eine Technik zur Verfügung zu stellen, die das Problem der Zerstörung von Halbleitervorrichtungen bei Herstellungsschritten, wie dem in [Fig. 4\(B\)](#) gezeigten, löst. Es ist insbesondere eine Aufgabe der vorliegenden Erfindung, eine Technik zu schaffen, die verhindert, dass Halbleitervorrichtung bei der Herstellung durch impulsartige, hohe Potentiale, die durch Plasmen angelegt werden (solche hohen Potentiale werden lokal und instantan erzeugt), zerstört werden.

**[0017]** Diese und weitere Probleme werden erfundungsgemäß durch die in den beigefügten Patentansprüchen definierte Verfahren gelöst.

**[0018]** Wie in einem speziellen Ausführungsbeispiel in den [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) gezeigt, ist die in dieser Anmeldung offengelegte Erfindung in einem ersten speziellen Gesichtspunkt dadurch gekennzeichnet, dass sie folgende Verfahrensschritte umfasst:

Bilden einer ersten Verdrahtung **100**, die sich bis zu einer Gateelektrode **101** eines Dünffilmtransistors erstreckt;

Bilden einer ersten Isolierschicht **206** auf der ersten Verdrahtung;

Bilden einer zweiten Verdrahtung **102**, die mit einem Sourcebereich **211** des Dünffilmtransistors auf der Isolierschicht verbunden ist;

Bilden einer zweiten Isolierschicht **207** auf der zweiten Verdrahtung; und

Bilden einer Leiterstruktur **214** auf der zweiten Isolierschicht;

wobei

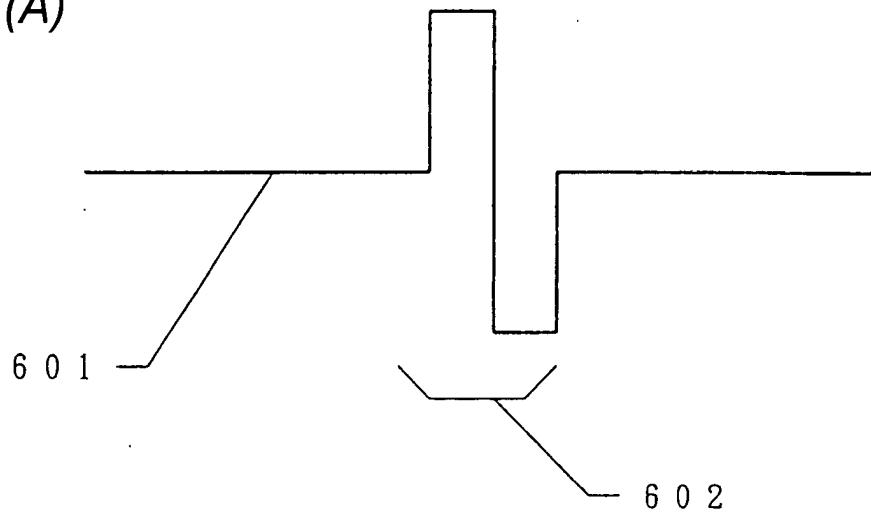

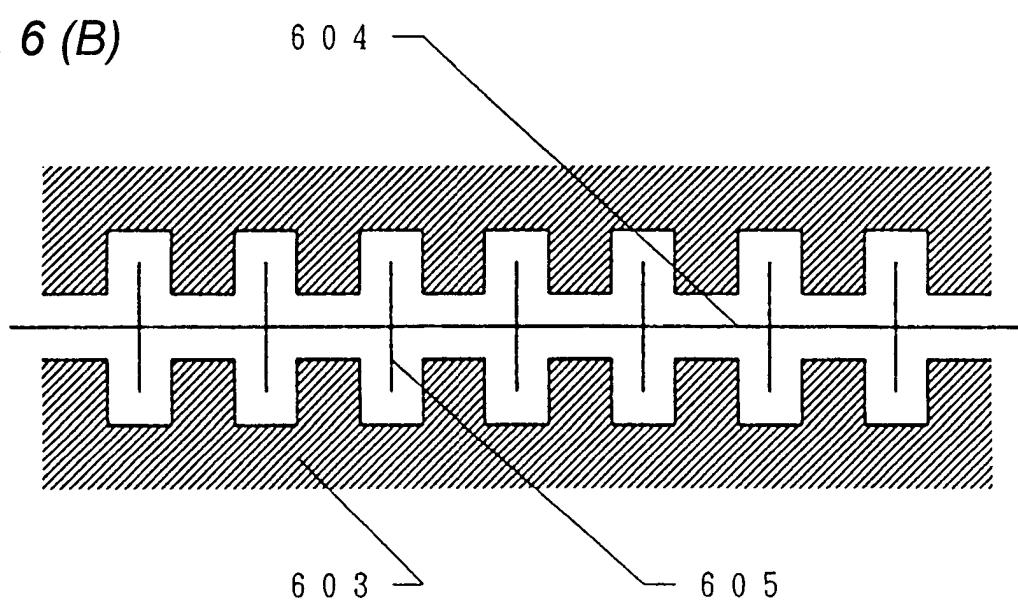

die erste und/oder die zweite Verdrahtung mit einer Entladungsstruktur (siehe [Fig. 6\(A\)](#) und [Fig. 6\(B\)](#) oder [Fig. 7](#)) erzeugt wird; und

die erste und/oder zweite Verdrahtung gleichzeitig mit der Herstellung der Leiterstruktur durchtrennt wird (siehe [Fig. 2\(E\)](#)).

**[0019]** In der oben beschriebenen Anordnung kann jede der Isolierschichten eine Mehrschichtstruktur besitzen.

**[0020]** Wie in einem speziellen Ausführungsbeispiel in den [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) gezeigt, wird entsprechend einem weiteren Gesichtspunkt der vorliegenden Erfindung ein Verfahren zum Herstellen eines aktiven Matrixschaltkreises (siehe [Fig. 1](#)) geschaffen, das dadurch gekennzeichnet ist, dass es folgende Verfahrensschritte umfasst:

Bilden einer ersten Mehrzahl von Verdrahtungen

**101;**

Bilden einer ersten Isolierschicht **206** auf der ersten Mehrzahl von Verdrahtungen;

Bilden einer zweiten Mehrzahl von Verdrahtungen **102**, die zur ersten Mehrzahl von Verdrahtungen in der Form eines Gitters auf der ersten Isolierschicht senkrecht verlaufen;

Bilden einer zweiten Isolierschicht **207** auf der zweiten Mehrzahl von Verdrahtungen; und

Bilden einer Leiterstruktur **214** auf der zweiten Isolierschicht;

wobei

die ersten und/oder die zweiten Verdrahtungen mit einer Entladungsstruktur (siehe [Fig. 6\(A\)](#) und [Fig. 6\(B\)](#) oder [Fig. 7](#)) erzeugt werden; und

die ersten und/oder zweiten Verdrahtungen gleichzeitig mit der Herstellung der Leiterstruktur durchtrennt wird (siehe [Fig. 2\(E\)](#)).

**[0021]** Entsprechend einem weiteren Gesichtspunkt ist die Erfindung dadurch gekennzeichnet, dass sie folgende Verfahrensschritte umfasst:

Bilden von Verdrahtungen, die einen aktiven Matrixschaltkreis bilden;

Bilden einer Isolierschicht auf den Verdrahtungen; und

Bilden einer Leiterstruktur auf der Isolierschicht;

wobei

die Verdrahtungen eine Entladungsstruktur umfassen; und

die Verdrahtungen mit der Entladungsstruktur durchtrennt werden, wenn die Leiterstruktur erzeugt wird.

**[0022]** Diese Anordnung wird zum Beispiel verwendet, wenn Entladungsstrukturen, wie sie in den [Fig. 6\(A\)](#), [Fig. 6\(B\)](#) und [Fig. 7](#) gezeigt sind, in mit **100** und **114** in [Fig. 1](#) gezeigten Kurzschlussverdrahtungen geformt werden und von den Verdrahtungen **101** und **102**, die in der Form einer Matrix angeordnet sind, während des Formens der Pixelelektrode **214** getrennt werden (siehe die [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#)).

**[0023]** Entsprechend einem weiteren Gesichtspunkt ist die Erfindung dadurch gekennzeichnet, dass sie folgende Verfahrensschritte umfasst:

Bilden von Verdrahtungen, die einen aktiven Matrixschaltkreis bilden;

Bilden einer Isolierschicht auf den Verdrahtungen; und

Bilden einer Leiterstruktur auf der Isolierschicht;

wobei

die Verdrahtungen eine Entladungsstruktur umfassen; und

die Entladungsstruktur von den Verdrahtungen, die den aktiven Matrixschaltkreis bilden, getrennt wird, wenn die Leiterstruktur geformt wird.

**[0024]** In dem in den [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) gezeigten Verfahren werden die Verdrahtungen **100** und **114** zum Verbinden der Verdrahtungen miteinander

während der Strukturierung der Pixelelektrode **214** durchtrennt, was ermöglicht, dass die Verdrahtungen vor der Strukturierung der Pixelelektrode kurzgeschlossen sind.

**[0025]** Dies ermöglicht es, das Phänomen zu unterdrücken, dass eine lokale, hohe Spannung an einer Isolierschicht der Halbleitervorrichtung während ihrer Herstellung unter Verwendung eines Plasmaverfahrens anliegt. Weiterhin kann durch Verwendung eines Schritts zum Durchtrennen eines solchen Kurzschlussbereichs während der Strukturierung der Pixelelektrode eine Anordnung verwendet werden, die keine zusätzlichen Herstellungsschritte erfordert.

**[0026]** Weiterhin kann ein durch die Verdrahtungen **100** und **114** mitten in einem Herstellungsschritt übertragenes Impulspotential durch Entladungsstrukturen, wie sie in den [Fig. 6](#) und [Fig. 7](#) gezeigt sind, reduziert oder beseitigt werden.

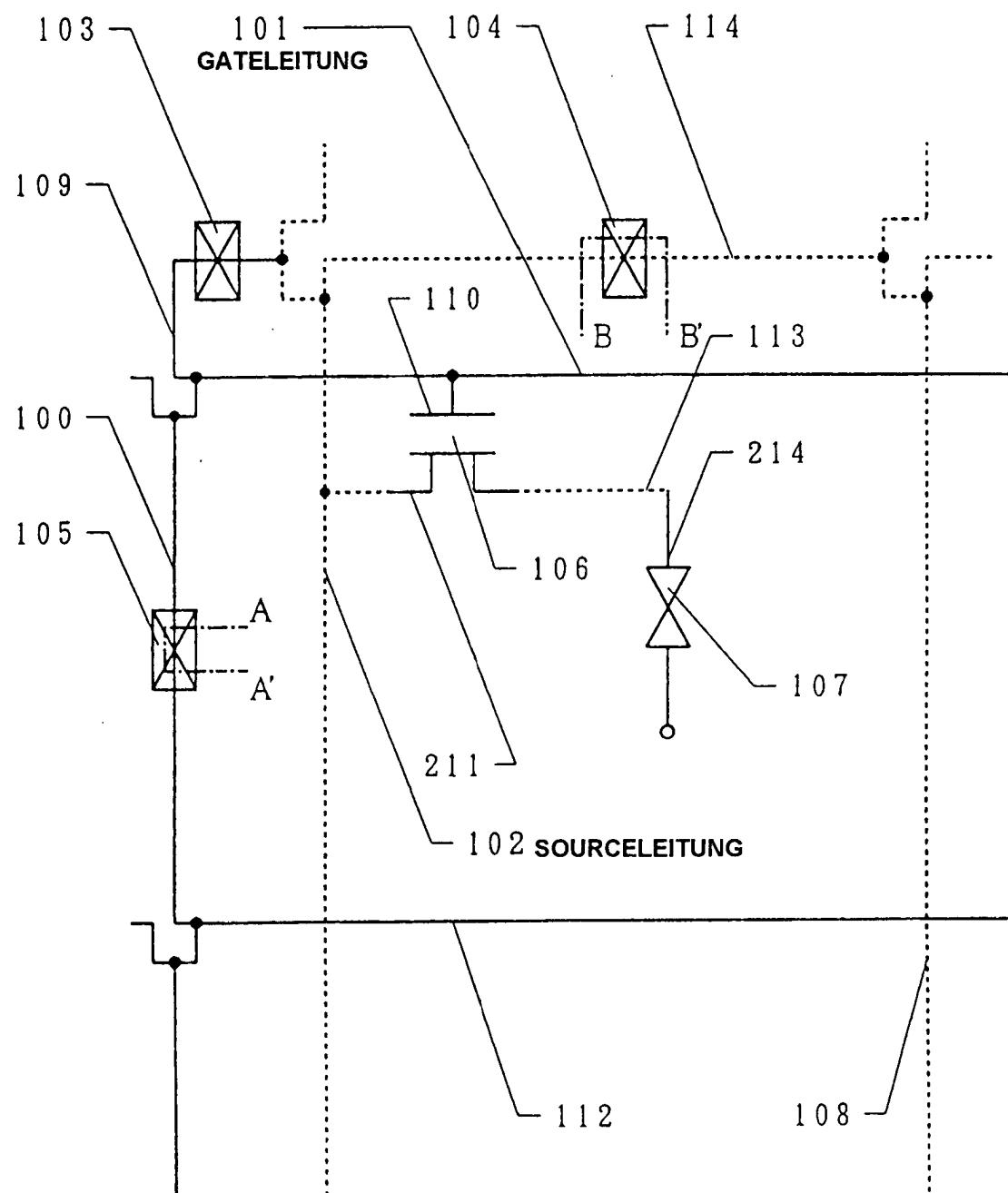

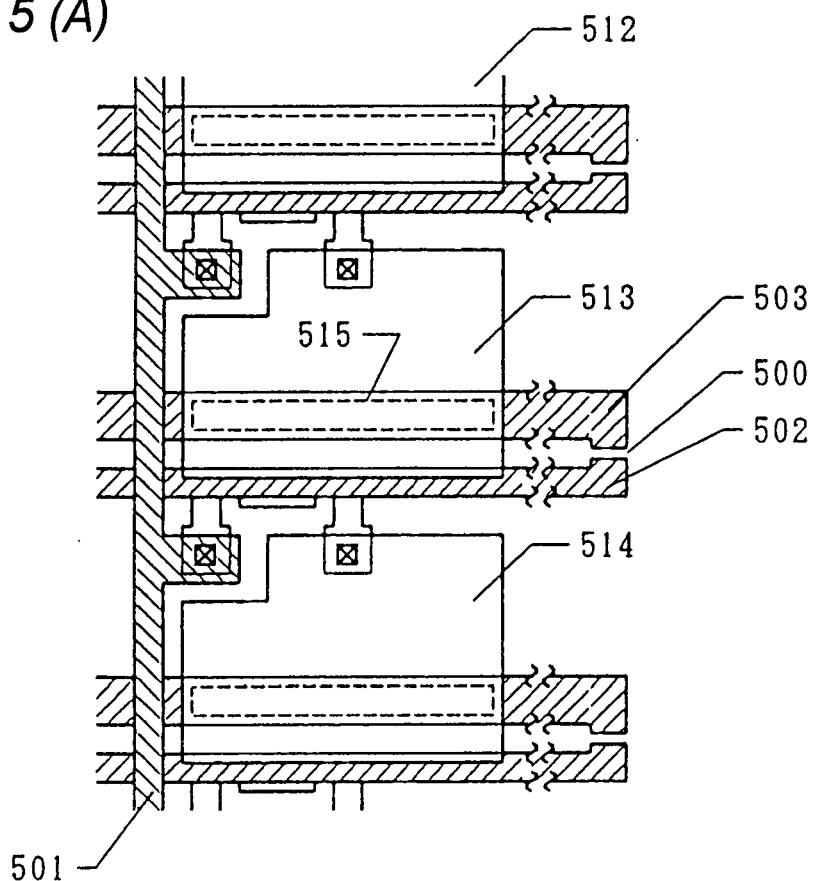

**[0027]** [Fig. 1](#) zeigt schematisch die Anordnung einer Flüssigkristallanzeige des aktiven Matrixtyps.

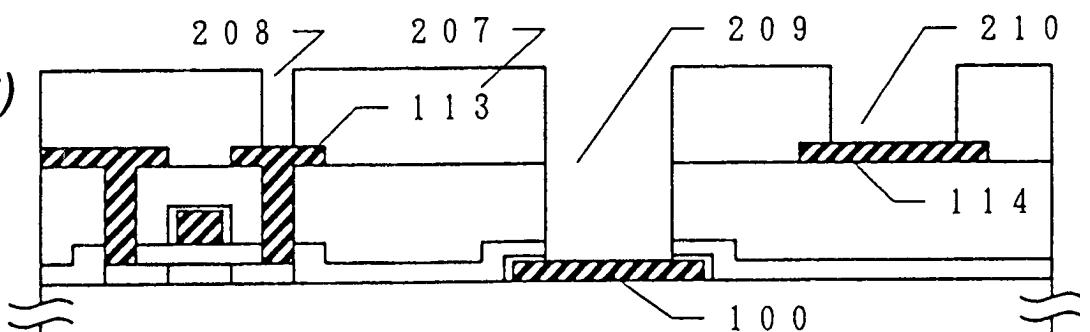

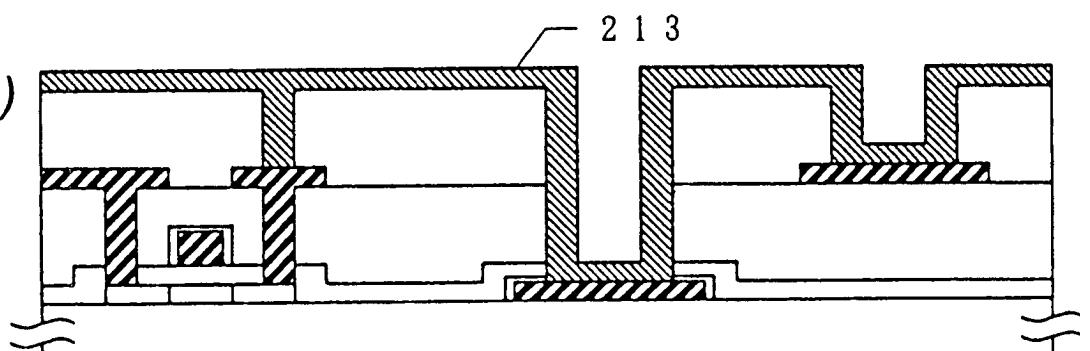

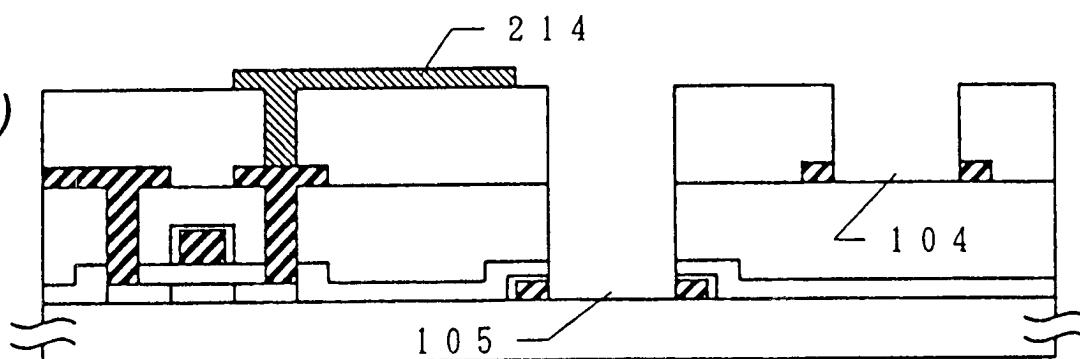

**[0028]** Die [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) zeigen Herstellungsschritte für einen Schaltkreis des aktiven Matrixtyps.

**[0029]** [Fig. 3](#) zeigt die Verteilung der Ionenenergie in einem Plasma.

**[0030]** Die [Fig. 4\(A\)](#) und [Fig. 4\(B\)](#) zeigen Herstellungsschritte für einen herkömmlichen Dünffilmtransistor.

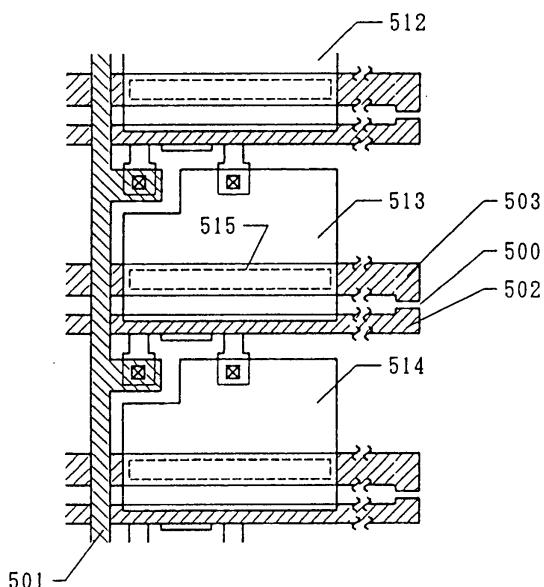

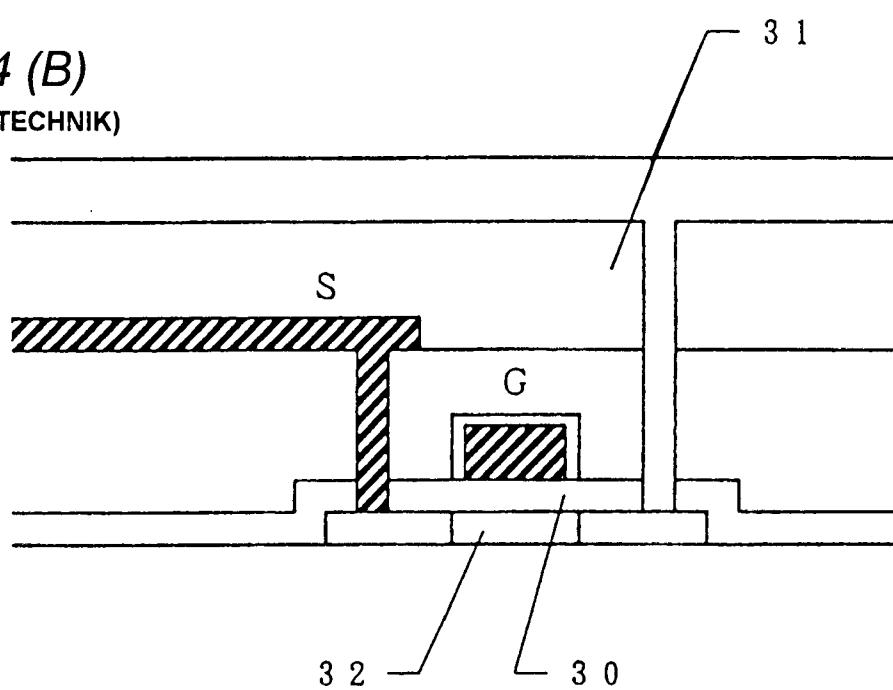

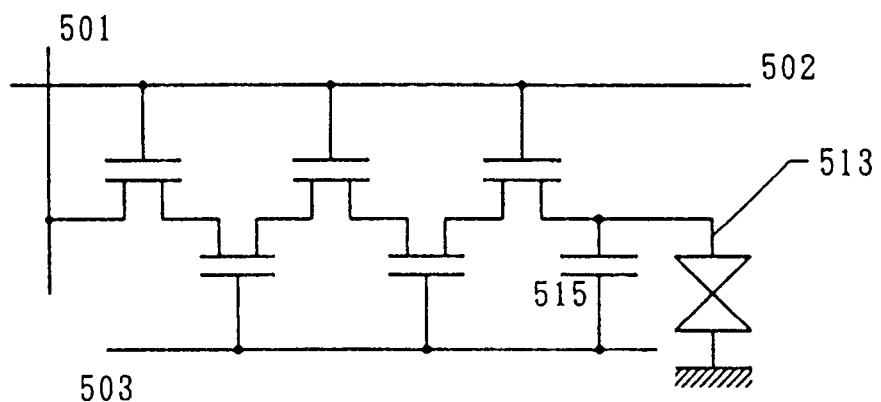

**[0031]** Die [Fig. 5\(A\)](#) und [Fig. 5\(B\)](#) zeigen ein Beispiel eines Schaltkreises des aktiven Matrixtyps.

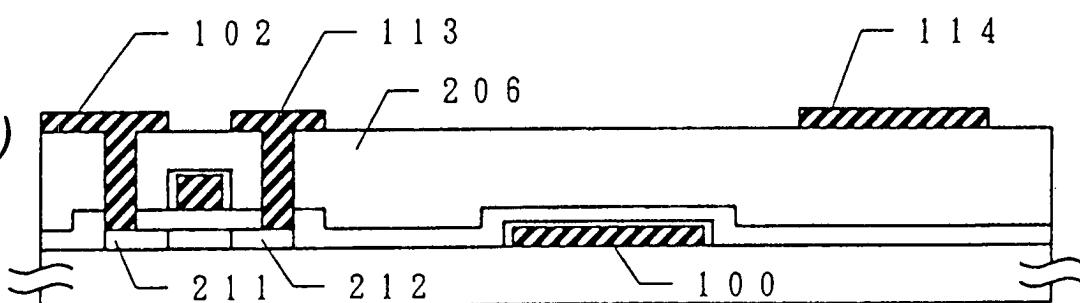

**[0032]** Die [Fig. 6\(A\)](#) und [Fig. 6\(B\)](#) zeigen Beispiele einer Entladungsstruktur nach einem Ausführungsbeispiel der vorliegenden Erfindung.

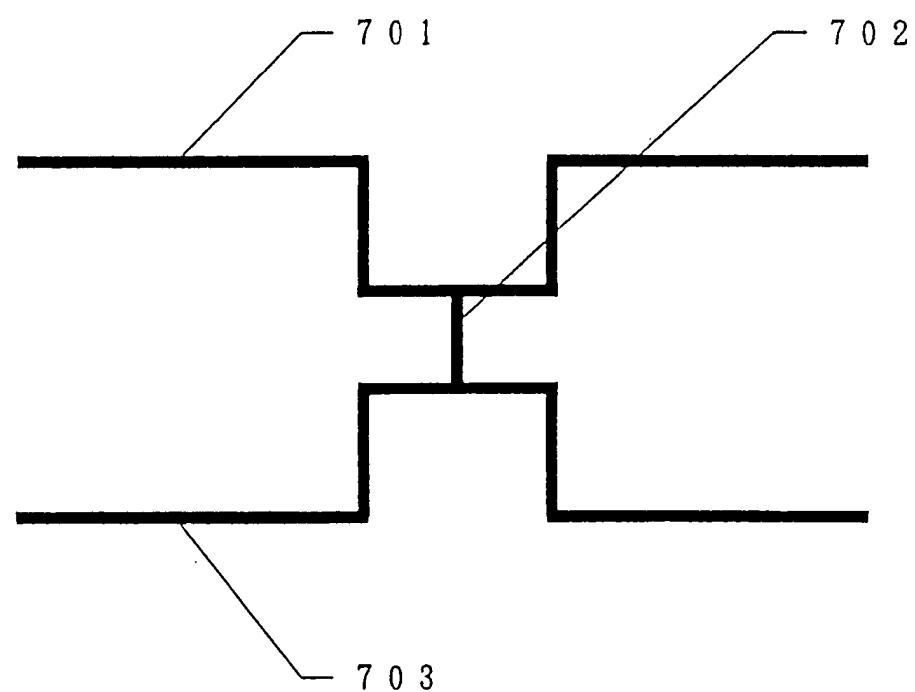

**[0033]** [Fig. 7](#) zeigt eine Verdrahtungsstruktur nach der vorliegenden Erfindung.

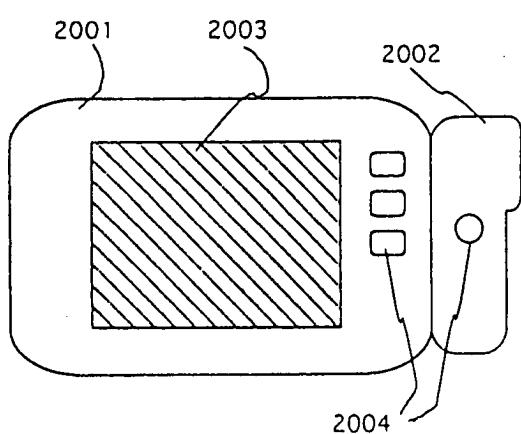

**[0034]** Die [Fig. 8\(A\)](#) bis [Fig. 8\(D\)](#) zeigen Anwendungsbeispiele, die die elektro-optische Vorrichtung nach der vorliegenden Erfindung verwenden.

**[0035]** Im folgenden wird ein erstes Ausführungsbeispiel der vorliegenden Erfindung beschrieben.

**[0036]** In einer Anordnung einer Flüssigkristallanzeige des aktiven Matrixtyps, wie sie in [Fig. 1](#) gezeigt ist, ist das vorliegende Ausführungsbeispiel dadurch gekennzeichnet, dass die mit **103**, **104** und **105** bezeichneten Bereiche bei der Strukturierung der Pixelelektrode (nicht in [Fig. 1](#) gezeigt) durch Ätzen entfernt werden.

**[0037]** Das vorliegende Ausführungsbeispiel wird unter Bezugnahme auf einen Schritt zum Trennen der Sourceverdrahtung und der Gateverdrahtung, die in einem aktiven Matrixbereich angeordnet sind und miteinander verbunden worden sind, in einem letzten Verfahrensschritt beschrieben.

**[0038]** In dem letzten Verfahrensschritt wird eine Pixelelektrode geformt, und nach der Herstellung der Pixelelektrode folgt kein weiterer Herstellungsschritt mehr, der ein Plasma verwendet. Daher kann der Schritt zur Herstellung der Pixelelektrode als der letzte Verfahrensschritt betrachtet werden, der ein Plasma verwendet.

**[0039]** In dem vorliegenden Ausführungsbeispiel werden zum Beispiel eine Gateverdrahtung **101** und eine Sourceverdrahtung **102** durch eine mit **109** bezeichnete Kurzschlussverdrahtung bis zu Herstellung der Pixelelektrode in Verbindung gehalten. (Diese Verdrahtung wird gleichzeitig mit der Herstellung der Gateverdrahtung hergestellt.)

**[0040]** Das bedeutet, dass die Source- und Gateverdrahtungen bis zum letzten Verfahrensschritt, in dem ein Plasma verwendet wird, elektrisch kurzgeschlossen sind. Das heißt, dass die Gateelektrode **110** und die Sourceelektrode **211** des Dünffilmtransistors **106** miteinander verbunden sind und sich auf demselben Potential befinden.

**[0041]** Dies verhindert, dass eine Spannung von einigen zehn Volt zwischen der Gateelektrode **110** und der Sourceelektrode **211** (die sich von der Sourceverdrahtung **102** in [Fig. 1](#) aus erstreckt) des Dünffilmtransistors **106** entsteht, auch wenn lokal eine hohe Spannung angelegt wird. Dies ermöglicht, die Zerstörung eines Dünffilmtransistors bei der Herstellung aufgrund eines hohen, durch ein Plasma induzierten Potentialimpulses zu verhindern.

**[0042]** Nach dem Abscheiden einer ITO-(Indium-Zinnoxyd)Schicht für die Pixelelektrode werden diese Verdrahtungen während der Strukturierung der Pixelelektrode in dem mit **103** bezeichneten Bereich getrennt, um die Herstellung des Schaltkreises zu beenden. [Fig. 1](#) zeigt weitere, mit **104** und **105** bezeichnete Bereiche, in denen diese Durchtrennung gleichzeitig durchgeführt wird.

**[0043]** Die in [Fig. 1](#) gezeigte Anordnung ermöglicht, dass die Gateverdrahtungen **101** und **112** und zusätzlich die Sourceverdrahtungen **102** und **108** während des Herstellungsverfahrens alle auf demselben Potential liegen. Weiterhin kann sie das Problem der Erzeugung einer unerwünschten Potentialdifferenz während eines Verfahrensschritts zur Filmherstellung oder eines Ätzschrittes, bei denen ein Plasma oder eine elektrische Entladung verwendet werden, lösen.

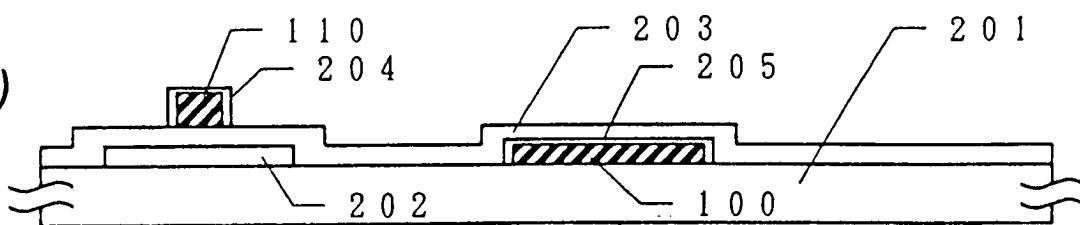

[0044] Die [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) sind Querschnitte, die die Herstellungsschritte für die in [Fig. 1](#) gezeigte Anordnung zeigen. Die [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) zeigen ein Herstellungsflussdiagramm für den Dünnpfilmtransistor **106** in der in [Fig. 1](#) gezeigten Anordnung im Querschnitt, ein Herstellungsflussdiagramm für die Kurzschlussleitung **101**, die sich von der Gateverdrahtung **101** entlang der Linie A-A' erstreckt im Querschnitt, und ein Herstellungsflussdiagramm für einen Abschnitt der Kurzschlussleitung **114**, die sich von der Sourceverdrahtung **102** entlang der Linie B-B' derselben Zeichnung erstreckt, im Querschnitt. (Die tatsächliche Querschnittsanordnung wird sich von den in den [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) gezeigten unterscheiden.)

[0045] Es folgt eine Beschreibung der in den [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) gezeigten Verfahrensschritte. Wie in [Fig. 2\(A\)](#) gezeigt, wird zunächst ein Siliziumoxydfilm (nicht gezeigt) als ein Basisfilm auf einem Glassubstrat **201** geformt. Die in [Fig. 1](#) gezeigte Struktur ist auf diesem Glassubstrat **201** geformt.

[0046] Als nächstes wird ein amorpher Siliziumfilm mit einer Dicke von 50 nm (500 Å) unter Verwendung von Plasma-CVD oder thermischer Niederdruck-CVD erzeugt. Die Dicke dieses amorphen Siliziumfilms kann zwischen etwa 20–200 nm (200–2000 Å) liegen. Dann wird eine Laserbestrahlung und/oder ein Erwärmungsvorgang für den Film durchgeführt. Als Ergebnis erhält man einen kristallisierten Siliziumfilm, der nicht in den Zeichnungen gezeigt ist.

[0047] Der (nicht gezeigte) kristallisierte Film wird strukturiert, so dass er eine aktive Schicht eines Dünnpfilmtransistors bildet, die in [Fig. 2\(A\)](#) mit **202** bezeichnet ist. Als nächstes wird ein Siliziumoxydfilm **203**, der als Gateisolator dient, unter Verwendung von Plasma-CVD oder Kathodenstrahlzerstäubung mit einer Dicke von 100 nm (1000 Å) erzeugt.

[0048] Ein Aluminiumfilm (nicht gezeigt) mit 0,2 Gewichtsprozent Scandium wird durch Kathodenstrahlzerstäubung mit einer Dicke von 500 nm (5000 Å) hergestellt. Der Zweck der Beimengung einer kleinen Menge von Scandium in dem Aluminiumfilm ist das Unterdrücken von Buckeln und Whiskern. Buckel und Whisker sind hornförmige oder dornenförmige Ausstülpungen, die als Ergebnis eines anomalen Wachstums von Aluminium auftreten.

[0049] Als nächstes wird der Aluminiumfilm strukturiert, um ein Gateverdrahtung **101** und eine Gateelektrode **110**, die sich von der Gateverdrahtung **101** aus erstreckt, zu erhalten. Weiterhin wird gleichzeitig eine Kurzschlussverdrahtung **100**, die sich von der Gateverdrahtung **101** aus erstreckt, geformt.

[0050] Auch wenn es in [Fig. 2](#) nicht gezeigt ist, wird die in [Fig. 1](#) mit **109** bezeichnete Kurzschlussver-

drahtung ebenfalls gleichzeitig mit diesem Schritt hergestellt. Die Gateverdrahtung **101**, die sich von der Gateverdrahtung aus erstreckende Gateelektrode **110** und die sich von der Gateverdrahtung **101** aus erstreckende Kurzschlussverdrahtung **100** werden als "erste Verdrahtungsschicht" bezeichnet.

[0051] Weiterhin wird, wie später unter Bezugnahme auf eine Ausführungsform im Detail beschrieben wird, die Kurzschlussverdrahtung mit einer solchen Struktur versehen, dass ein angelegter oder induzierter hoher Potentialimpuls vermieden wird.

[0052] Als nächstes wird eine Anodisierung in einer elektrolytischen Lösung durchgeführt, wobei die Gateelektrode **110**, die Gateverdrahtung **101** und die Kurzschlussverdrahtungen **100** und **109**, die sich von der Gateverdrahtung aus erstrecken, als Anode dienen. In diesem Schritt werden die [Fig. 2\(A\)](#) gezeigten, anodischen Oxydfilme **204** und **205** erzeugt.

[0053] Die anodischen Oxydfilme werden mit einer Dicke von 50 nm (500 Å) hergestellt. Die anodischen Oxydfilme sind wirkungsvoll bei der Unterdrückung von Buckeln, wodurch ein Kurzschluss zwischen den Verdrahtungen vermieden werden. Auf diese Weise wird der in [Fig. 2\(A\)](#) gezeigte Zustand erreicht.

[0054] In dem Anodisierungsschritt wird eine Äthylenglykollösung mit 3%-iger Weinsäure, die durch wässriges Ammoniak neutralisiert ist, als Elektrolytlösung verwendet. Weiterhin wird dieser Schritt durch Anlegen eines Stromes an diese Elektrolytlösung zwischen der Aluminiumstruktur und einer Platinalektrode, die als Anode beziehungsweise als Kathode dienen, durchgeführt.

[0055] Dann werden Verunreinigungen in dem in [Fig. 2\(A\)](#) gezeigten Zustand implantiert. Durch diesen Schritt werden ein Sourcebereich **211** und ein Drainbereich **212** selbstausgerichtet geformt ([Fig. 2\(B\)](#)).

[0056] Als nächstes wird ein Siliziumoxydfilm oder ein Siliziumnitridfilm als erster Zwischenschichtisolationsfilm **206** mit einer Dicke von 500 nm (5000 Å) mittels eines Plasma-CVD-Verfahrens hergestellt. Auch ein laminierter Film bestehend aus einem Siliziumoxydfilm und einem Siliziumnitridfilm oder aus einem Siliziumoxynitridfilm kann für diesen Zwischenschichtisolationsfilm verwendet werden. Ein Siliziumoxynitridfilm wird unter Verwendung eines Plasma-CVD-Verfahrens mit einer Mischung eines TEOS-Gases und eines N<sub>2</sub>O-Gases als Gasquelle geformt.

[0057] Als nächstes werden Kontaktlöcher unter Verwendung eines Trockenätzverfahrens geformt. Neueste Entwicklung in Richtung feinerer Strukturen begünstigen die Verwendung eines Trockenätzver-

fahrens, das anisotrop ist.

**[0058]** Auch wenn ein Trockenätzverfahren verwendet wird, kann die Zerstörung eines Dünnfilmtransistors bei seiner Herstellung durch ein durch ein Plasma induziertes hohes Potential vermieden werden. Dies ist deswegen der Fall, da die Verdrahtungen und Elektroden miteinander verbunden sind, so dass sie auf demselben Potential liegen, was das Entstehen einer Potentialdifferenz zum Beispiel über den Gateseparatorfilm **203** verhindert.

**[0059]** Als nächstes wird ein dreischichtiger Film bestehend aus einem Titanfilm, einem Aluminiumfilm und einem weiteren Titanfilm als zweite Verdrahtung erzeugt. Dieser dreischichtige Film wird unter Verwendung eines Kathodenstrahlzerstäubungsverfahrens erzeugt. Auch in diesem Fall wird die Erzeugung einer großen Potentialdifferenz zwischen den Verdrahtungen und Elektroden unterdrückt.

**[0060]** Der oben beschriebene, dreischichtige Film wird dann strukturiert, um die Sourceverdrahtung **102** (die sich bis zu einem Kontakt mit dem Sourcebereich **211** erstreckt), die Drainelektrode **113** und die Kurzschlussverdrahtung **113**, die sich von der Sourceverdrahtung **102** aus erstreckt, zu erzeugen ([Fig. 2\(B\)](#)).

**[0061]** Diese Elektroden und Verdrahtungen werden als "zweite Verdrahtungsschicht" bezeichnet. Die Beziehung zwischen den Positionen, an denen diese Elektroden und Verdrahtungen erzeugt werden, ist in [Fig. 1](#) gezeigt.

**[0062]** Wie aus den [Fig. 2\(A\)](#) bis [Fig. 2\(E\)](#) ersichtlich, ist die erste Verdrahtungsschicht (in [Fig. 1](#) durch eine durchgezogene Linie bezeichnet), die von der Gateelektrode **110**, die sich von der Gateverdrahtung **101** aus erstreckt (siehe [Fig. 1](#)), und der Verdrahtung **100**, die sich von der Gateverdrahtung **101** aus erstreckt, gebildet wird, in horizontaler Richtung durch den Zwischenschichtisolierfilm **206** von der zweiten Verdrahtungsschicht getrennt (in [Fig. 1](#) durch eine gepunktete Linie bezeichnet), die von der Sourceverdrahtung **102** und der sich von der Sourceverdrahtung aus erstreckenden Verdrahtung **114** gebildet wird. Jedoch sind diese Verdrahtungen miteinander durch die Kurzschlussverdrahtung **109** verbunden, wie in [Fig. 1](#) gezeigt.

**[0063]** Nach dem Erhalten des in [Fig. 2\(B\)](#) gezeigten Zustand, wird ein Siliziumoxydfilm oder ein Siliziumnitridfilm als zweiter Zwischenschichtisolationsfilm **207** erzeugt ([Fig. 2\(C\)](#)).

**[0064]** Wenn der zweite Zwischenschichtisolationsfilm **207** geformt wird, sind alle Elektroden und Verdrahtungen kurzgeschlossen. Daher ist es möglich, die Erzeugung einer unerwünschten Potentialdiffe-

renz unter der Einwirkung eines Plasmas zu verhindern. Weiterhin ist es möglich, die Erzeugung von Defekten aufgrund des lokalen Entstehens einer hohen Spannung zu vermeiden.

**[0065]** Dann wird ein Kontaktloch **208** zum Verbinden der Drainelektrode **113** mit einer später zu formenden Pixelelektrode **124** (siehe [Fig. 2\(E\)](#)) geformt.

**[0066]** Gleichzeitig wird eine Öffnung **209** geformt, um die Kurzschlussverdrahtung **100** offen zu legen, die sich von der Gateverdrahtung **101** im Bereich **105**, die eine erste Verdrahtungsschicht ist (siehe [Fig. 2\(E\)](#)), aus erstreckt.

**[0067]** Weiterhin wird gleichzeitig eine Öffnung **210** geformt, um die Kurzschlussverdrahtung **114** im Bereich **104** offen zu legen, die sich von der Sourceverdrahtung **102**, die eine zweite Verdrahtungsschicht ist (siehe [Fig. 2\(E\)](#)), aus erstreckt.

**[0068]** Diese Öffnungen werden ebenfalls unter Verwendung eines Trockenätzverfahrens erzeugt. Bei diesem Verfahrensschritt ist es wiederum möglich, den Einfluss eines hohen Potentials, das durch ein Plasma zwischen den Verdrahtungen und Elektroden induziert wird, zu unterdrücken, da die Verdrahtungen und Elektroden miteinander verbunden sind und auf demselben Potential liegen.

**[0069]** Wie aus [Fig. 2\(C\)](#) ersichtlich, werden die Öffnungen **209** und **210**, die sich bis zur ersten Verdrahtungsschicht **100** beziehungsweise bis zur zweiten Verdrahtungsschicht **114** erstrecken, in diesem Schritt gleichzeitig geformt.

**[0070]** Als nächstes wird ein ITO-Film **213** unter Verwendung von Kathodenstrahlzerstäubung zum Erzeugen der Pixelelektrode hergestellt. Während der Herstellung der Pixelelektrode ist es wiederum möglich, die Erzeugung einer unerwünschten Potentialdifferenz zwischen den Verdrahtungen und den Elektroden unter dem Einfluss eines Plasmas zu vermeiden, da sich die Verdrahtungen und Elektroden auf demselben Potential befinden.

**[0071]** Es ist besonders wichtig, dass die Isolationsfilme und die Pixelelektrode in einem Zustand erzeugt werden, in dem die Gateverdrahtung **101**, die zur ersten Verdrahtungsschicht gehört, die in [Fig. 1](#) durch die durchgezogene Linie gekennzeichnet ist, und die zweite Verdrahtungsschicht **102**, die durch die gepunktete Linie gekennzeichnet ist, kurzgeschlossen sind. Die Filmherstellung (und Trockenätzung) in einem solchen Zustand ermöglicht es, das Anlegen einer hohen Spannung zwischen den ersten und zweiten Verdrahtungsschichten zu verhindern.

**[0072]** Als Ergebnis ist es zum Beispiel möglich,

eine Situation zu vermeiden, in der eine hohe Spannung zwischen der Gateelektrode **110** und der aktiven Schicht **202** angelegt wird. Somit kann das Anlegen einer hohen Spannung über den Gateisolierfilm **203** vermieden werden.

**[0073]** Als nächstes wird der ITO-Film **213** strukturiert. Diese Strukturierung wird ebenfalls mittels Trockenätzung durchgeführt. Die Verdrahtungen **100** und **114** werden in den in [Fig. 2\(E\)](#) gezeigten Bereichen **105** und **104** durch diese Trockenätzung entfernt.

**[0074]** Somit werden die Verdrahtungen in den Bereichen **105** und **104** durchtrennt. [Fig. 2\(E\)](#) zeigt den Zustand, in dem diese Verdrahtungen in den Bereichen **104** und **105** durchtrennt sind. Weiterhin wird auch die Durchtrennung der Verdrahtung **109** in dem Bereich **103** gleichzeitig in demselben Verfahrensschritt durchgeführt.

**[0075]** Hiermit wird die Herstellung einer Schaltkreiskonfiguration eines Pixelbereichs einer Flüssigkristallanzeige des aktiven Matrixtyps beendet.

**[0076]** In dem vorstehenden Ausführungsbeispiel sind die Verdrahtungen und Elektroden, die auf unerwünschte Weise als Antennen funktionieren, elektrisch kurzgeschlossen, so dass sie während Verfahrensschritten, die ein Plasma verwenden, auf demselben Potential liegen. Daher ist es möglich, auch wenn lokal durch ein Plasma ein hohes Potential induziert wird, zu verhindern, dass ein Dünnfilmtransistor während seiner Herstellung zerstört wird.

**[0077]** Im folgenden wird ein zweites Ausführungsbeispiel der vorliegenden Erfindung beschrieben.

**[0078]** Diese Ausführungsbeispiel bezieht sich auf eine Anordnung eines Pixelbereichs eines Flüssigkristallanzeige des aktiven Matrixtyps mit einem äquivalenten Schaltkreis, wie er in [Fig. 5\(B\)](#) gezeigt ist. [Fig. 5\(A\)](#) zeigt eine Anordnung mit dem in [Fig. 5\(B\)](#) gezeigten, äquivalenten Schaltkreis in einer Draufsicht.

**[0079]** In den [Fig. 5\(A\)](#) und [Fig. 5\(B\)](#) bezeichnen die Bezugszeichen **502** eine Gateverdrahtung und **501** eine Sourceverdrahtung. Die Gate- und Sourceverdrahtungen sind in der Form einer Matrix angeordnet, und mit **512**, **513** und **514** bezeichnete Pixelelektroden sind in von den beiden Verdrahtungen umgebenen Bereichen angeordnet.

**[0080]** In der in [Fig. 5\(A\)](#) gezeigten Konfiguration überqueren die Gateverdrahtung **502** und eine Kondensatorverdrahtung **503** eine Halbleiterschicht (die aktive Schicht), die in der Form eines "M" angeordnet ist, so dass die in [Fig. 5\(B\)](#) gezeigte Schaltkreiskonfiguration erhalten wird.

**[0081]** Wie aus [Fig. 5\(B\)](#) ersichtlich, arbeitet der Schaltkreis nicht, wenn die Gateverdrahtung **502** und die Kondensatorverdrahtung **503** direkt miteinander verbunden sind. Die Gateverdrahtung **502** und die Kondensatorverdrahtung **503** werden durch Strukturierung desselben leitfähigen Films erhalten.

**[0082]** In einer solchen Anordnung besteht die Möglichkeit, dass eine hohe Spannung zwischen der Gateverdrahtung **502** und der Kondensatorverdrahtung **503** erzeugt wird, wenn zum Beispiel ein Isolationsfilm zur Bedeckung dieser Verdrahtungen geformt wird. Wie aus [Fig. 5\(B\)](#) ersichtlich, werden, wenn eine hohe Spannung zwischen der Gateverdrahtung **502** und der Kondensatorverdrahtung **503** angelegt wird, ein Transistor und ein dazwischen geformter MOS-Kondensator zerstört.

**[0083]** Unter Berücksichtigung dieser Tatsache ist der Aufbau des vorliegenden Ausführungsbeispiels dadurch gekennzeichnet, dass die Gateverdrahtung **502** und die Kondensatorverdrahtung **503** in einem mit **500** bezeichneten Bereich miteinander verbunden sind, bis eine Pixelelektrode **513** geformt ist (diese Pixelelektrode wird in dem letzten Herstellungsschritt geformt), und der Bereich **500** wird durchtrennt, wenn die Pixelelektrode **513** strukturiert wird.

**[0084]** Eine solche Anordnung ermöglicht es, das Anlegen einer hohen Spannung zwischen der Gateverdrahtung **502** und der Kondensatorverdrahtung **503** zu verhindern, ohne dass die Anzahl der Herstellungsschritte erhöht würde.

**[0085]** Im folgenden wird ein drittes Ausführungsbeispiel der vorliegenden Erfindung beschrieben.

**[0086]** Das vorliegende Ausführungsbeispiel bezieht sich auf die Form der Strukturen der Kurzschlussverdrahtungen **109**, **114** und **100** der [Fig. 1](#).

**[0087]** Ein impulsförmiges, hohes Potential, das von einem Plasma induziert wird, wird durch eine lokale, anomale Entladung erzeugt. Daher sind die Orte, an denen impulsförmige, hohe Potentiale induziert werden, unbestimmte, lokale Bereiche.

**[0088]** Im Falle eines aktiven Matrixbereichs mit einer großen Fläche, kann sich ein hoher Potentialimpuls, der von einem Plasma induziert wird, über eine lange Strecke ausbreiten. In einem solchen Fall ist der Einfluss des hohen Potentialimpulses, wie er oben beschrieben wurde, bedenklich, auch wenn die Verdrahtungen und Elektroden auf demselben Potential liegen.

**[0089]** Das vorliegende Ausführungsbeispiel bezieht sich auf einen Aufbau, der in einem solchen Fall wirkungsvoll ist. In dem vorliegenden Ausführungsbeispiel werden Strukturen, wie sie in den [Fig. 6\(A\)](#)

und [Fig. 6\(B\)](#) gezeigt sind, in einem Teil der Kurzschlussverdrahtungen **109**, **114** und/oder **100** geformt.

**[0090]** [Fig. 6\(A\)](#) zeigt eine Verdrahtungsstruktur zum Verringern oder Beseitigen eines hohen Potentialimpulses, der sich entlang einer Leitung **601** ausbreitet, in einem Bereich **602**. Der Zweck dieser Verdrahtungsstruktur dient dazu, ein Auftreffen des Impulses in dem mit **602** bezeichneten Bereich zu bewirken, um somit die Energie in diesem Bereich zu entladen.

**[0091]** Es ist wirkungsvoll, die in [Fig. 6\(A\)](#) gezeigte Struktur in der Mitte oder an einem Ende der mit **100** und **114** bezeichneten Kurzschlussverdrahtungen anzugeordnen. Dies verhindert wirkungsvoll, dass sich ein hoher Potentialimpuls mehrmals auf den Leitungen hin- und her bewegt.

**[0092]** [Fig. 6\(B\)](#) zeigt eine Leitung **604** mit einer Struktur **605** zum Entladen, die von einer gedruckten Leitung **603** auf Erdpotential umgeben ist.

**[0093]** Es ist ebenfalls wirkungsvoll, eine solche Struktur an einem Ende der mit **100** und **114** bezeichneten Kurzschlussverdrahtungen anzugeordnen. Eine solche Struktur ist außerdem wirkungsvoll, wenn sie in einer Verbindung zwischen einem aktiven Matrixbereich und einem peripheren Treiberschaltkreisbereich verwendet wird.

**[0094]** Die Struktur entsprechend dem vorliegenden Ausführungsbeispiel kann so verstanden werden, dass sich die Impedanz der Verdrahtung durch diese Struktur lokal ändert (zunimmt oder abnimmt), wodurch eine Ausbreitung der hochfrequenten Impulse durch die Verdrahtung verhindert wird.

**[0095]** In [Fig. 7](#) sind zwei benachbarte Leitungen **701** und **702** mittels einer Verdrahtungsstruktur **702** miteinander verbunden. Ein solcher Aufbau hat die Funktion, dass sich durch die Leitungen **701** und **703** ausbreitende Impulse hohen Potentials im Bereich der Struktur **702** kollidieren und sich dort entladen.

**[0096]** Es ist wirkungsvoll die in [Fig. 7](#) gezeigte Struktur an einem Ende der mit **100** und **114** bezeichneten Kurzschlussverdrahtungen in einem Bereich außerhalb des aktiven Matrixbereichs anzugeordnen. Durch Verwendung der in [Fig. 7](#) gezeigten Struktur ist es möglich, eine Ausbreitung von Impulsen hohen Potentials in allen Richtungen eines aktiven Matrixschaltkreises zu verhindern.

**[0097]** Die in dieser Anmeldung offengelegte Erfindung ermöglicht es, die Zerstörung einer Halbleitervorrichtung bei der Herstellung durch ein impulsförmiges, hohes Potential, das durch ein Plasma induziert wird, zu verhindern. Insbesondere kann dies er-

reicht werden, ohne einen speziellen Herstellungs-schritt hinzuzufügen.

**[0098]** Die aktive Matrixvorrichtung nach der vorliegenden Erfindung kann in einer elektro-optischen Vorrichtung, wie etwa einer Flüssigkristallanzeige oder einer Elektrolumineszenzanzeige verwendet werden. Die elektro-optische Vorrichtung kann in den folgenden elektronischen Geräten verwendet werden.

**[0099]** [Fig. 8\(A\)](#) zeigt eine sogenannte digitale oder Elektronenkamera. Die Vorrichtung hat zur Funktion, ein von einer CCD-Kamera photographiertes Bild elektronisch zu speichern. Die CCD-Kamera ist in einem Kamerateil **2002** angeordnet. Außerdem hat die Vorrichtung auch zur Funktion, das Bild in einer in dem Kamerakörper **2001** angeordneten Anzeigevorrichtung anzuzeigen. Darüber hinaus ist es wohl bekannt, dass die Vorrichtung alle Arten von Kommunikationsvorrichtungen und Informationsspeicherungsvorrichtung besitzt, damit sie als Informationsterminal verwendet werden kann. Der Betrieb der Vorrichtung wird durch Betätigung des Betriebsknopfes **2004** durchgeführt.

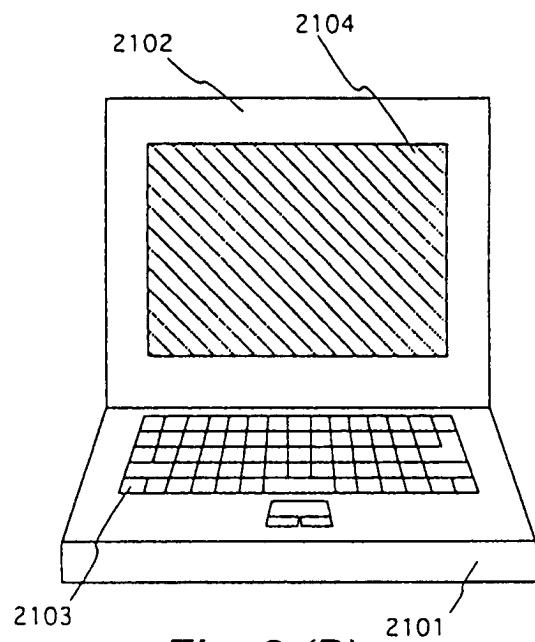

**[0100]** [Fig. 8\(B\)](#) zeigt einen tragbaren Personalcomputer. Die Vorrichtung umfasst eine Anzeigevorrichtung **2104** in dem Deckel **2102**, der sich öffnen und schließen kann, und alle Arten von Informationen können über eine Tastatur **2103** eingegeben und verschiedene Operationen können durchgeführt werden.

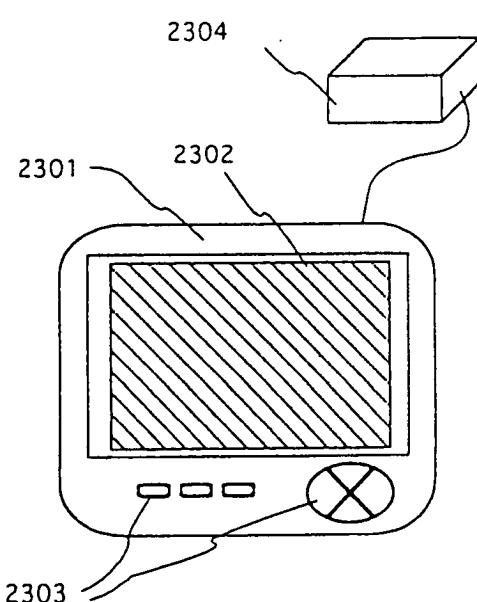

**[0101]** [Fig. 8\(C\)](#) zeigt ein Beispiel eines Fahrzeugnavigationssystems, das eine Flachbildschirmanzeige verwendet. Das Fahrzeugnavigationssystem besitzt einen Körper, der aus einem Antennenteil **2304** und einer Anzeigevorrichtung **2302** besteht. Das Durchspielen aller Arten von Informationen, die für die Navigation notwendig sind, wird durch einen Betriebsknopf **2303** durchgeführt. Außerdem werden verschiedene Betriebsvorgänge durch eine Fernsteuervorrichtung durchgeführt, die hier nicht gezeigt ist.

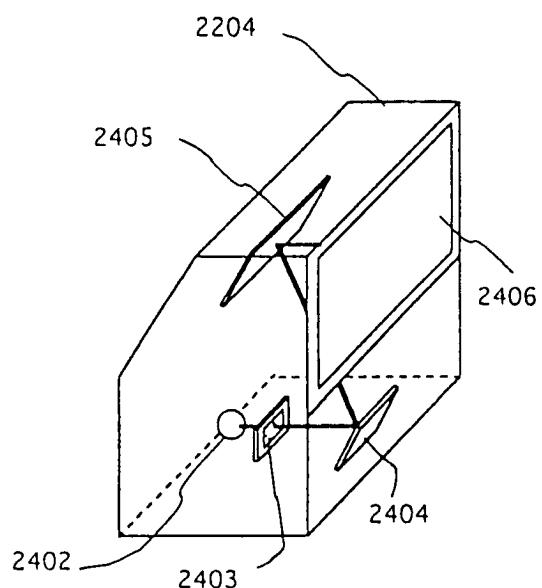

**[0102]** [Fig. 8\(D\)](#) zeigt ein Beispiel einer Flüssigkristallanzeigevorrichtung des Projektionstyps. In der Figur wird von einer Lichtquelle **2402** ausgestrahltes Licht optisch durch eine Flüssigkeitskristallanzeige **2403** moduliert, um ein Bild zu formen. Das Bild wird von Spiegeln **2404** und **2405** reflektiert und auf einen Schirm **2406** projiziert.

**[0103]** Während die vorliegende Erfindung in Verbindung mit bevorzugten Ausführungsbeispielen beschrieben wurde, ist klar, dass der Umfang der Erfindung nicht auf diese speziellen, in diesen Ausführungsbeispielen gezeigten Strukturen beschränkt sein soll.

## Patentansprüche

1. Verfahren zum Herstellen einer Halbleitervorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten Verdrahtung (100) einschließlich einer Gateelektrode (110) für einen Dünnpfilmtransistor über einem Substrat;

Bilden eines Zwischenschichtisolators (206) auf der ersten Verdrahtung;

Bilden einer zweiten Verdrahtung (102) auf dem Zwischenschichtisolator, wobei die zweite Verdrahtung entweder mit einem Sourcebereich (211) oder einem Drainbereich des Dünnpfilmtransistors verbunden ist;

Bilden eines zweiten Zwischenschichtisolators (207) auf der zweiten Verdrahtung;

Bilden eines leitfähigen Films (214) auf dem zweiten Zwischenschichtisolator; und

Strukturieren des leitfähigen Films durch Ätzen; wobei die erste und die zweite Verdrahtung wenigstens während der Erzeugung des zweiten Zwischenschichtisolators und des leitfähigen Films miteinander kurzgeschlossen sind; wobei wenigstens eine der ersten und zweiten Verdrahtungen (100, 114) mit einer Entladungsstruktur (601, 602, 605, 701, 702, 703) versehen ist, die so gestaltet ist, dass sie lokal die Impedanz erhöht oder erniedrigt, um die Ausbreitung von Hochfrequenzimpulsen durch die kurzgeschlossenen Leitungen zu verhindern, und wobei die ersten und zweiten Verdrahtungen (100, 114) bei dem Strukturierungsschritt voneinander getrennt werden.

2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass die Herstellung des zweiten Zwischenschichtisolators unter Verwendung eines Plasmas durchgeführt wird.

3. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass die Herstellung der leitenden Schicht unter Verwendung eines Plasmas durchgeführt wird.

4. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer Mehrzahl von ersten Verdrahtungen (100), die sich in Spaltenrichtung erstrecken;

Bilden eines Zwischenschichtisolators (206) auf der Mehrzahl von ersten Verdrahtungen;

Bilden einer Mehrzahl von zweiten Verdrahtungen (102), die sich in einer Zeilenrichtung senkrecht zur Spaltenrichtung erstrecken;

Bilden eines zweiten Zwischenschichtisolators (207) auf der Mehrzahl von zweiten Verdrahtungen;

Bilden eines leitfähigen Films (214) auf dem zweiten Zwischenschichtisolator; und

Strukturieren des leitfähigen Films durch Ätzen; wobei die Vielzahl der ersten Verdrahtungen untereinander über eine Kurzschlussverdrahtung (100) während der Herstellung des zweiten Zwischenschichtisolators kurzgeschlossen sind und durch den Strukturierungsschritt getrennt werden, und wobei wenigstens eine der Mehrzahl von ersten und zweiten Verdrahtungen (100, 114) mit einer Entladungsstruktur (601, 602, 605, 701, 702, 703) versehen ist, die so gestaltet ist, dass sie lokal die Impedanz erhöht oder erniedrigt, um die Ausbreitung von Hochfrequenzimpulsen durch die kurzgeschlossenen Leitungen zu verhindern.

tisolators kurzgeschlossen sind und durch den Strukturierungsschritt getrennt werden, und wobei wenigstens eine der Mehrzahl von ersten und zweiten Verdrahtungen (100, 114) mit einer Entladungsstruktur (601, 602, 605, 701, 702, 703) versehen ist, die so gestaltet ist, dass sie lokal die Impedanz erhöht oder erniedrigt, um die Ausbreitung von Hochfrequenzimpulsen durch die kurzgeschlossenen Leitungen zu verhindern.

5. Verfahren nach Anspruch 4, dadurch gekennzeichnet, dass die Mehrzahl von ersten Verdrahtungen elektrisch mit der Mehrzahl von zweiten Verdrahtungen verbunden ist und durch den Strukturierungsschritt des leitfähigen Films voneinander getrennt werden.

6. Verfahren nach Anspruch 1 oder 4, wobei ein Teil der Entladungsstruktur eine undulierende Struktur (602) aufweist.

7. Verfahren nach Anspruch 1 oder 4, wobei die Entladungsstruktur (605) von einer Leitung (603) mit Erdpotential umgeben ist, um einen hohen Potentialimpuls zwischen der Entladungsstruktur (605) und der Leitung (603) mit Erdpotential zu entladen.

8. Verfahren nach Anspruch 1 oder 4, wobei die Entladungsstruktur (701, 702, 703) mindestens zwei benachbarte Leitungen (701, 703) und eine Verdrahtungsstruktur (702), die die zwei benachbarten Leitungen (701, 703) verbindet, umfasst.

9. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten leitfähigen Schicht über einem Substrat; Strukturieren der ersten leitfähigen Schicht zumindest zu einer Gateverdrahtung und einer ersten Kurzschlussverdrahtung;

Bilden eines ersten Zwischenschichtisolators über dem Substrat, der Gateverdrahtung und der ersten Kurzschlussverdrahtung;

Bilden einer zweiten leitfähigen Schicht auf dem ersten Zwischenschichtisolator;

Strukturieren der zweiten leitfähigen Schicht zumindest zu einer Sourceverdrahtung und einer zweiten Kurzschlussverdrahtung, wobei die Gateverdrahtung und die Sourceverdrahtung kurzgeschlossen werden, indem die erste Kurzschlussverdrahtung mit der zweiten Kurzschlussverdrahtung verbunden wird;

Bereitstellen einer Verdrahtungsstruktur (601, 602), die zumindest mit einer der Gateverdrahtung und der Sourceverdrahtung verbunden ist;

Bilden eines zweiten Zwischenschichtisolators (207) auf dem ersten Zwischenschichtisolator und der Sourceverdrahtung;

Bilden einer Öffnung in dem ersten und zweiten Zwischenschichtisolator, um zumindest einen Teil der

ersten oder zweiten Kurzschlussverdrahtung freizulegen;

Bilden einer dritten leitfähigen Schicht auf dem zweiten Zwischenschichtisolator, wobei die dritte leitfähige Schicht auch auf dem zumindest teilweise freigelegten Teil der ersten oder zweiten Kurzschlussverdrahtung ausgebildet wird; und

Strukturieren der dritten leitfähigen Schicht, um eine Pixelelektrode auf dem zweiten Zwischenschichtisolator zu bilden;

wobei zumindest ein Teilbereich der ersten und die zweiten Kurzschlussverdrahtung in selbstausrichtender Art hinsichtlich der Öffnung entfernt wird, unmittelbar nach der Strukturierung der dritten leitfähigen Schicht, wobei die Gateverdrahtung elektrisch von der Sourceverdrahtung getrennt wird, und

wobei ein Teil der Verdrahtungsstruktur eine undulierende Struktur (**602**) aufweist.

10. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten leitfähigen Schicht über einem Substrat;

Strukturieren der ersten leitfähigen Schicht zumindest zu einer Gateverdrahtung und einer ersten Kurzschlussverdrahtung;

Bilden eines ersten Zwischenschichtisolators über dem Substrat, der Gateverdrahtung und der ersten Kurzschlussverdrahtung;

Bilden einer zweiten leitfähigen Schicht auf dem ersten Zwischenschichtisolator;

Strukturieren der zweiten leitfähigen Schicht zumindest zu einer Sourceverdrahtung und einer zweiten Kurzschlussverdrahtung, wobei die Gateverdrahtung und die Sourceverdrahtung kurzgeschlossen werden, indem die erste Kurzschlussverdrahtung mit der zweiten Kurzschlussverdrahtung verbunden wird; Bereitstellen einer Entladungsstruktur (**605**), die zumindest mit einer der Gateverdrahtung und der Sourceverdrahtung verbunden ist;

Bilden eines zweiten Zwischenschichtisolators (**207**) auf dem ersten Zwischenschichtisolator und der Sourceverdrahtung;

Bilden einer Öffnung in dem ersten und zweiten Zwischenschichtisolator, um zumindest einen Teil der ersten oder zweiten Kurzschlussverdrahtung freizulegen;

Bilden einer dritten leitfähigen Schicht auf dem zweiten Zwischenschichtisolator, wobei die dritte leitfähige Schicht auch auf dem zumindest teilweise freigelegten Teil der ersten oder zweiten Kurzschlussverdrahtung ausgebildet wird; und

Strukturieren der dritten leitfähigen Schicht, um eine Pixelelektrode auf dem zweiten Zwischenschichtisolator zu bilden;

wobei zumindest ein Teilbereich der ersten und die zweiten Kurzschlussverdrahtung in selbstausrichtender Art hinsichtlich der Öffnung entfernt wird, unmittelbar nach der Strukturierung der dritten leitfähigen

Schicht, wobei die Gateverdrahtung elektrisch von der Sourceverdrahtung getrennt wird, und wobei die Entladungsstruktur (**605**) von einer Leitung (**603**) mit Erdpotential umgeben ist, um einen hohen Potentialimpuls zwischen der Entladungsstruktur (**605**) und der Leitung (**603**) mit Erdpotential zu entladen.

11. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten leitfähigen Schicht über einem Substrat;

Strukturieren der ersten leitfähigen Schicht zumindest zu einer Gateverdrahtung und einer ersten Kurzschlussverdrahtung;

Bilden eines ersten Zwischenschichtisolators über dem Substrat, der Gateverdrahtung und der ersten Kurzschlussverdrahtung;

Bilden einer zweiten leitfähigen Schicht auf dem ersten Zwischenschichtisolator;

Strukturieren der zweiten leitfähigen Schicht zumindest zu einer Sourceverdrahtung und einer zweiten Kurzschlussverdrahtung, wobei die Gateverdrahtung und die Sourceverdrahtung kurzgeschlossen werden, indem die erste Kurzschlussverdrahtung mit der zweiten Kurzschlussverdrahtung verbunden wird;

Bereitstellen zumindest einer Entladungsstruktur (**701, 702, 703**), die zumindest mit einer der Gateverdrahtung und der Sourceverdrahtung verbunden ist;

Bilden eines zweiten Zwischenschichtisolators auf dem ersten Zwischenschichtisolator und der Sourceverdrahtung;

Bilden einer Öffnung in dem ersten und zweiten Zwischenschichtisolator, um zumindest einen Teil der ersten oder zweiten Kurzschlussverdrahtung freizulegen;

Bilden einer dritten leitfähigen Schicht auf dem zweiten Zwischenschichtisolator, wobei die dritte leitfähige Schicht auch auf dem zumindest teilweise freigelegten Teil der ersten oder zweiten Kurzschlussverdrahtung ausgebildet wird; und

Strukturieren der dritten leitfähigen Schicht, um eine Pixelelektrode auf dem zweiten Zwischenschichtisolator zu bilden;

wobei zumindest ein Teilbereich der ersten und die zweiten Kurzschlussverdrahtung in selbstausrichtender Art hinsichtlich der Öffnung entfernt wird, unmittelbar nach der Strukturierung der dritten leitfähigen Schicht, wobei die Gateverdrahtung elektrisch von der Sourceverdrahtung getrennt wird, und

wobei die Entladungsstruktur (**701, 702, 703**) mindestens zwei benachbarte Leitungen (**701, 703**) und eine Verdrahtungsstruktur (**702**), die die zwei benachbarten Leitungen (**701, 703**) verbindet, umfasst.

12. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten leitfähigen Schicht über einem

Substrat;

Strukturieren der ersten leitfähigen Schicht zumindest zu zwei Sourceverdrahtungen und einer Kurzschlussverdrahtung, wobei die zwei Sourceverdrahtungen durch die Kurzschlussverdrahtung miteinander kurzgeschlossen werden;

Bereitstellen einer Verdrahtungsstruktur (601, 602), die zumindest mit einer der zwei Sourceverdrahtungen verbunden ist;

Bilden eines Zwischenschichtisolators über dem Substrat, den zwei Sourceverdrahtungen und der Kurzschlussverdrahtung;

Bilden einer Öffnung in dem Zwischenschichtisolator, um einen Teil der Kurzschlussverdrahtung freizulegen;

Bilden einer zweiten leitfähigen Schicht über dem Zwischenschichtisolator, wobei die zweite leitfähigen Schicht auch auf dem freigelegten Teil der Kurzschlussverdrahtung ausgebildet ist;

Strukturieren der zweiten leitfähigen Schicht, um eine Pixelelektrode über dem Zwischenschichtisolator zu bilden;

wobei zumindest ein Teilbereich der Kurzschlussverdrahtung in selbstausrichtender Art hinsichtlich der Öffnung entfernt wird, unmittelbar nach der Strukturierung der zweiten leitfähigen Schicht, wobei die zumindest zwei Sourceverdrahtungen elektrisch von einander getrennt werden, und

wobei ein Teil der Verdrahtungsstruktur eine undulierende Struktur (602) aufweist.

13. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten leitfähigen Schicht über einem Substrat;

Strukturieren der ersten leitfähigen Schicht zumindest zu zwei Sourceverdrahtungen und einer Kurzschlussverdrahtung, wobei die zwei Sourceverdrahtungen durch die Kurzschlussverdrahtung miteinander kurzgeschlossen werden;

Bereitstellen einer Entladungsstruktur (605), die zumindest mit einer der zwei Sourceverdrahtungen verbunden ist;

Bilden eines Zwischenschichtisolators über dem Substrat, den zwei Sourceverdrahtungen und der Kurzschlussverdrahtung;

Bilden einer Öffnung in dem Zwischenschichtisolator, um einen Teil der Kurzschlussverdrahtung freizulegen;

Bilden einer zweiten leitfähigen Schicht über dem Zwischenschichtisolator, wobei die zweite leitfähigen Schicht auch auf dem freigelegten Teil der Kurzschlussverdrahtung ausgebildet ist;

Strukturieren der zweiten leitfähigen Schicht, um eine Pixelelektrode über dem Zwischenschichtisolator zu bilden;

wobei zumindest ein Teilbereich der Kurzschlussverdrahtung in selbstausrichtender Art hinsichtlich der Öffnung entfernt wird, unmittelbar nach der Strukturierung der zweiten leitfähigen Schicht, wobei die zumindest zwei Sourceverdrahtungen elektrisch von einander getrennt werden, und

wobei die Entladungsstruktur (605) von einer Leitung (603) mit Erdpotential umgeben ist, um einen hohen Potentialimpuls zwischen der Entladungsstruktur (605) und der Leitung (603) mit Erdpotential zu entladen.

14. Verfahren zum Herstellen einer aktiven Matrixvorrichtung, das folgende Verfahrensschritte umfasst:

Bilden einer ersten leitfähigen Schicht über einem Substrat;

Strukturieren der ersten leitfähigen Schicht zumindest zu zwei Sourceverdrahtungen und einer Kurzschlussverdrahtung, wobei die zwei Sourceverdrahtungen durch die Kurzschlussverdrahtung miteinander kurzgeschlossen werden;

Bereitstellen einer Entladungsstruktur (701, 702, 703), die zumindest mit einer der zwei Sourceverdrahtungen verbunden ist;

Bilden eines Zwischenschichtisolators über dem Substrat, den zwei Sourceverdrahtungen und der Kurzschlussverdrahtung;

Bilden einer Öffnung in dem Zwischenschichtisolator, um einen Teil der Kurzschlussverdrahtung freizulegen;

Bilden einer zweiten leitfähigen Schicht über dem Zwischenschichtisolator, wobei die zweite leitfähigen Schicht auch auf dem freigelegten Teil der Kurzschlussverdrahtung ausgebildet ist;

Strukturieren der zweiten leitfähigen Schicht, um eine Pixelelektrode über dem Zwischenschichtisolator zu bilden;

wobei zumindest ein Teilbereich der Kurzschlussverdrahtung in selbstausrichtender Art hinsichtlich der Öffnung entfernt wird, unmittelbar nach der Strukturierung der zweiten leitfähigen Schicht, wobei die zumindest zwei Sourceverdrahtungen elektrisch von einander getrennt werden, und

wobei die Entladungsstruktur (701, 702, 703) mindestens zwei benachbarte Leitungen (701, 703) und eine Verdrahtungsstruktur (702), die die zwei benachbarten Leitungen (701, 703) verbindet, umfasst.

15. Verfahren nach irgendeinem der Ansprüche 9 bis 11, worin die dritte leitfähige Schicht Indium-Zinn-Oxid umfasst.

16. Verfahren nach irgendeinem der Ansprüche 9 bis 11, worin die zweite leitfähige Schicht eine Mehrfach-Schicht umfasst, die eine Titanschicht, eine Aluminiumschicht und eine Titanschicht einschließt.

17. Verfahren nach irgendeinem der Ansprüche 9 bis 11, worin die erste leitfähige Schicht Aluminium umfasst.

18. Verfahren nach irgendeinem der Ansprüche

12 bis 14, worin die zweite leitfähige Schicht Indium-Zinn-Oxid umfasst.

19. Verfahren nach irgendeinem der Ansprüche 12 bis 14, worin der Zwischenschichtisolator mindestens zwei Isolierschichten umfasst, von denen jede ein Material umfasst, das aus der Gruppe, bestehend aus Siliziumoxid und Siliziumnitrid, ausgewählt wird.

20. Verfahren nach irgendeinem der Ansprüche 9 bis 14, worin die aktive Matrixvorrichtung in eine Digitalkamera für unbewegte Bilder oder eine elektronische Kamera, in einen tragbaren persönlichen Computer, in ein Autonavigationssystem, oder in einen Projektor vom Typ einer Flüssigkristallanzeigevorrichtung eingebaut wird.

21. Verfahren nach irgendeinem der Ansprüche 9 bis 11, worin die Gateverdrahtung mit einer Gateelektrode verbunden wird, um einen Dünnfilmtransistor zu bilden.

22. Verfahren nach irgendeinem der Ansprüche 9 bis 14, worin die Sourceverdrahtung mit sowohl einem Sourcebereich als auch einen Drainbereich verbunden ist, die einen Dünnfilmtransistor bilden.

Es folgen 8 Blatt Zeichnungen

## Anhängende Zeichnungen

Fig. 1

Fig. 2 (A)

Fig. 2 (B)

Fig. 2 (C)

Fig. 2 (D)

Fig. 2 (E)

*Fig. 3*

*Fig. 4 (A)*

(STAND DER TECHNIK)

*Fig. 4 (B)*

(STAND DER TECHNIK)

Fig. 5 (A)

Fig. 5 (B)

Fig. 6 (A)

Fig. 6 (B)

*Fig. 7*

Fig. 8 (A)

Fig. 8 (B)

Fig. 8 (C)

Fig. 8 (D)