(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5367434号

(P5367434)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月20日(2013.9.20)

|               |                         |

|---------------|-------------------------|

| (51) Int.Cl.  | F 1                     |

| HO 1 L 21/205 | (2006.01) HO 1 L 21/205 |

| HO 1 L 21/203 | (2006.01) HO 1 L 21/203 |

| HO 1 L 21/338 | (2006.01) HO 1 L 29/80  |

| HO 1 L 29/778 | (2006.01) H             |

| HO 1 L 29/812 | (2006.01)               |

請求項の数 7 (全 15 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-87933 (P2009-87933)    |

| (22) 出願日  | 平成21年3月31日 (2009.3.31)        |

| (65) 公開番号 | 特開2010-239066 (P2010-239066A) |

| (43) 公開日  | 平成22年10月21日 (2010.10.21)      |

| 審査請求日     | 平成24年3月26日 (2012.3.26)        |

|           |                                                          |

|-----------|----------------------------------------------------------|

| (73) 特許権者 | 000154325<br>住友電工デバイス・イノベーション株式会<br>社<br>神奈川県横浜市栄区金井町1番地 |

| (74) 代理人  | 100087480<br>弁理士 片山 修平                                   |

| (74) 復代理人 | 100137615<br>弁理士 横山 照夫                                   |

| (74) 復代理人 | 100134511<br>弁理士 八田 俊之                                   |

| (72) 発明者  | 眞壁 勇夫<br>山梨県中巨摩郡昭和町大字紙漉阿原100<br>0番地 ユーディナデバイス株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

Gaを含む半導体層の成長に用いた成長装置をクリーニングするクリーニング工程と、前記クリーニング工程においてクリーニングされた成長装置を用いて、Siからなる基板上に、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$  atoms/cm<sup>3</sup>以下の窒化物半導体からなる第1層を形成する第1工程と、

前記第1工程を複数の前記基板に行った後、前記第1層上に前記第1層の成長に使用した成長装置を用いて、Gaを含む窒化物半導体からなる第2層を形成する第2工程と、を有することを特徴とする半導体装置の製造方法。

## 【請求項 2】

Siからなる基板上に、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$  atoms/cm<sup>3</sup>以下の窒化物半導体からなる第1層を形成する第1工程と、

前記第1層の成長に使用した成長装置とは別の成長装置を用いて、前記第1層上にGaを含む窒化物半導体からなる第2層を形成する第2工程と、

前記第1工程の後であって前記第2工程の前に、前記第1層上に構成元素としてGaを含まない第3層を形成する第3工程と、を有し、

前記第2工程は前記第3工程と同じ成長装置を用いて、連続して行われ、

前記第2層は前記第3層上に形成されることを特徴とする半導体装置の製造方法。

## 【請求項 3】

前記第1工程の後であって前記第2工程の前に、前記第1層上に構成元素としてGaを

10

20

含まない第3層を形成する第3工程を有し、

前記第2工程は前記第3工程と連続して行われ、

前記第2層は前記第3層上に形成されることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記第3層は前記第1層と同一の構成元素からなることを特徴とする請求項3記載の半導体装置の製造方法。

【請求項5】

前記第1層はAlNからなることを特徴とする請求項1または2記載の半導体装置の製造方法。

10

【請求項6】

前記第2層はGaN、InGaN、AlGaN及びInAlGaNの少なくとも一つからなることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項7】

前記第1工程に用いられる前記成長装置がMOCVD装置である場合、Alの有機原料中のAlに対するGa含有量が2ppm以下であり、

前記第1工程に用いられる前記成長装置がMBE装置である場合、Alの有機原料中のAlに対するGa含有量が40ppm以下であることを特徴とする請求項1または2記載の半導体装置の成長方法。

【発明の詳細な説明】

20

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特にSi基板上にGaを含む窒化物半導体層を、気相成長法により形成する半導体装置の製造方法に関する。

【背景技術】

【0002】

Gaを構成元素とする窒化物半導体層(GaN系半導体層)を用いたHEMT(High Electron Mobility Transistor)等の半導体装置は、高周波用素子として注目されている。こうした半導体装置では、基板としてSiC(炭化珪素)やサファイアが多く用いられるが、これらの基板は高価であるため、Si基板上に半導体装置を作成する技術が求められている。MBE法(Molecular Beam

Epitaxy:分子線エピタキシー法)は、高真空中の成長であり、N原料の取り扱いが困難である。これに対し、MOCVD法(Metal Organic Chemical Vapor Deposition:有機金属気相成長法)は、減圧又は常圧下の成長であり、NH<sub>3</sub>やNH<sub>2</sub>をN原料として容易に使用できることから、広くGaN系半導体の成長に用いられている。特許文献1には、Si基板上にAlN(窒化アルミニウム)等からなるバッファ層を設け、バッファ層の上に半導体層(チャネル層)を、MOCVD法により形成する技術が開示されている。

30

【先行技術文献】

【特許文献】

40

【0003】

【特許文献1】特表2004-524250号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、Si基板上にMOCVD法やHYPE法(ハイドライド気相成長法)といった気相成長法でGaN系半導体を成長する場合、MBE法で成長する場合やGaaS系半導体を成長する場合と違い、900以上という高い成長温度を用いる。このため、Si基板にGaが拡散しやすく、基板内にGaを含んだ導電層が形成される場合がある。導電層が形成されると、寄生容量が大きくなり、高周波信号の損失が大きくなり、半導体装置の

50

特性悪化の原因となる恐れがある。

【0005】

本発明は、上記課題に鑑み、導電層の形成を抑制することで特性悪化を抑制可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、Gaを含む半導体層の成長に用いた成長装置をクリーニングするクリーニング工程と、前記クリーニング工程においてクリーニングされた成長装置を用いて、Siからなる基板上に、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$  atoms/cm<sup>3</sup>以下の窒化物半導体からなる第1層を形成する第1工程と、前記第1工程を複数の前記基板に行った後、前記第1層上に前記第1層の成長に使用した成長装置を用いて、Gaを含む窒化物半導体からなる第2層を形成する第2工程と、を有することを特徴とする半導体装置の製造方法である。本発明によれば、導電層の形成を抑制することで特性悪化を抑制可能な半導体装置の製造方法を提供することができる。

10

【0007】

本発明は、Siからなる基板上に、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$  atoms/cm<sup>3</sup>以下の窒化物半導体からなる第1層を形成する第1工程と、前記第1層の成長に使用した成長装置とは別の成長装置を用いて、前記第1層上にGaを含む窒化物半導体からなる第2層を形成する第2工程と、前記第1工程の後であって前記第2工程の前に、前記第1層上に構成元素としてGaを含まない第3層を形成する第3工程と、を有し、前記第2工程は前記第3工程と同じ成長装置を用いて、連続して行われ、前記第2層は前記第3層上に形成されることを特徴とする半導体装置の製造方法である。本発明によれば、導電層の形成を抑制することで特性悪化を抑制可能な半導体装置の製造方法を提供することができる。

20

【0008】

上記構成において、前記第1工程の後であって前記第2工程の前に、前記第1層上に構成元素としてGaを含まない第3層を形成する第3工程を有し、前記第2工程は前記第3工程と連続して行われ、前記第2層は前記第3層上に形成される構成とすることができる。この構成によれば、基板と第1層との熱膨張係数の差に起因する基板の反り及びクラックを抑制することができる。

30

【0009】

上記構成において、前記第3層は前記第1層と同一の構成元素からなる構成とすることができます。この構成によれば、基板と第1層との熱膨張係数の差に起因する基板の反り及びクラックを抑制することができる。

【0010】

上記構成において、前記第1層はAlNからなる構成とすることができます。

【0011】

上記構成において、前記第2層はGaN、InGaN、AlGaN及びInAlGaNのいずれかからなる構成とすることができます。この構成によれば、第1層成長時にGaが取り込まれ、基板上に導電層が形成されることが抑制される。

40

【0013】

上記構成において、前記第1工程に用いられる前記成長装置がMOCVD装置である場合、Alの有機原料中のAlに対するGa含有量が2ppm以下であり、前記第1工程に用いられる前記成長装置がMBE装置である場合、Alの有機原料中のAlに対するGa含有量が40ppm以下である構成とすることができます。この構成によれば、半導体装置の利得向上の効果を得ることができる。

【発明の効果】

【0017】

本発明によれば、導電層の形成を抑制することで特性悪化を抑制可能な半導体装置の製造方法を提供することができる。

50

## 【図面の簡単な説明】

## 【0018】

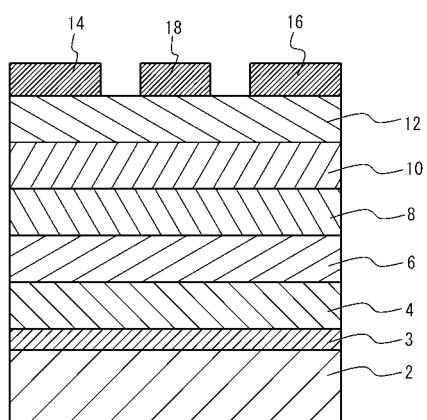

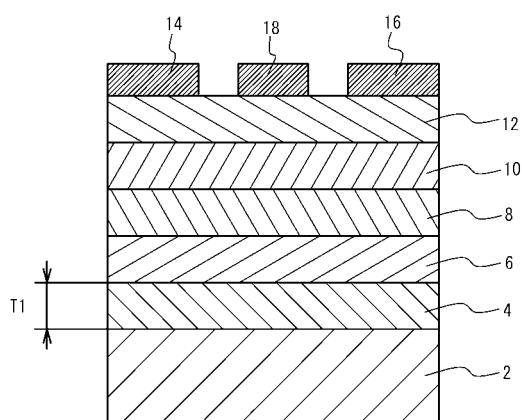

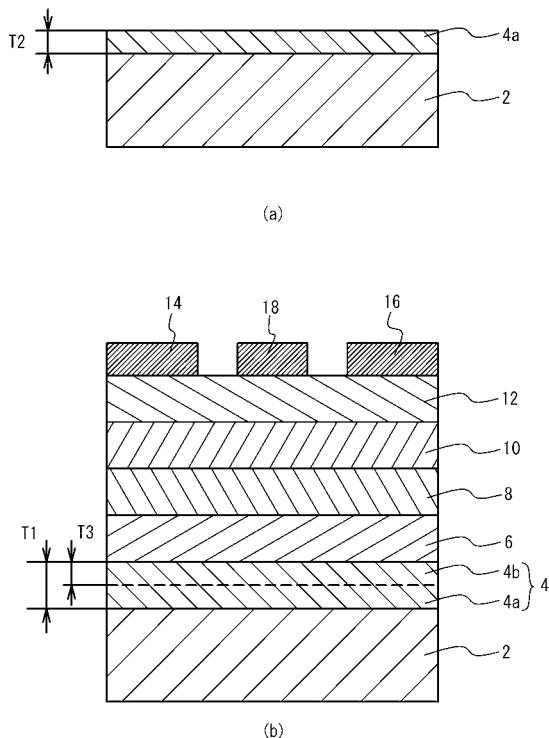

【図1】図1は比較例に係る半導体装置を例示する断面図である。

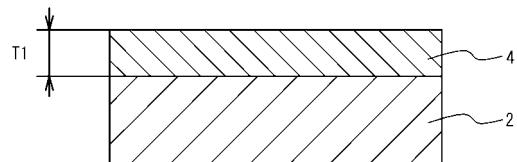

【図2】図2は実験に用いたサンプルを示す断面図である。

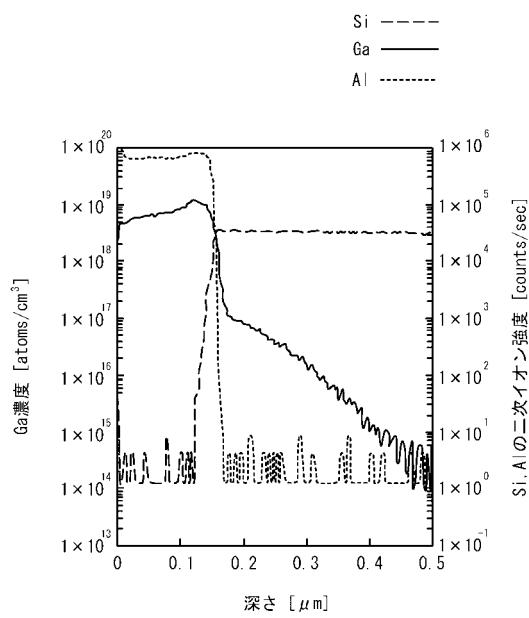

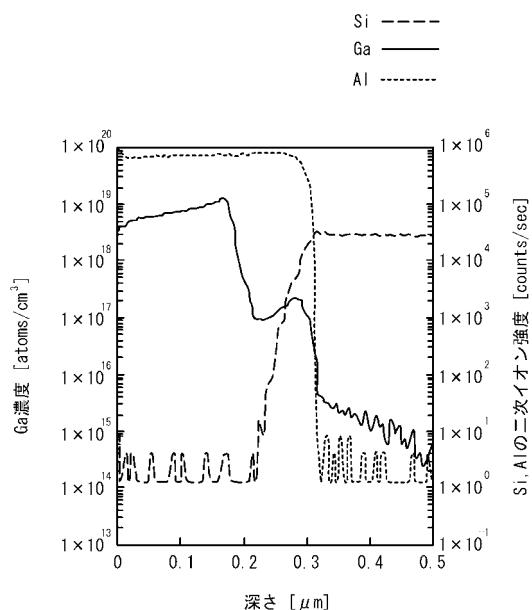

【図3】図3はサンプルAについて行ったSIMS分析の結果を示す図である。

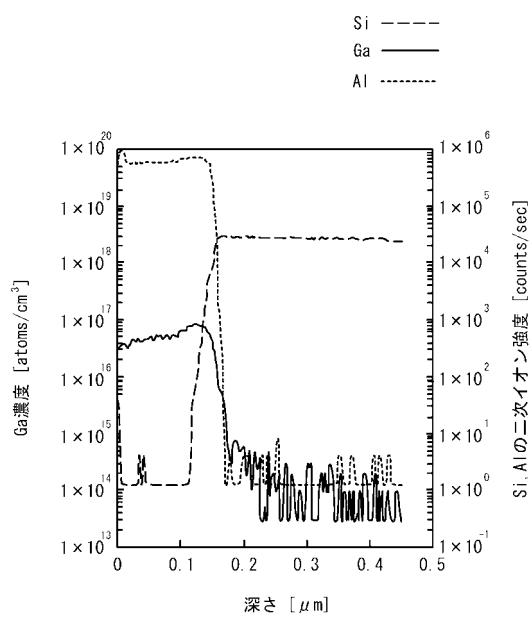

【図4】図4はサンプルBについて行ったSIMS分析の結果を示す図である。

【図5】図5は実施例1に係る半導体装置を例示する断面図である。

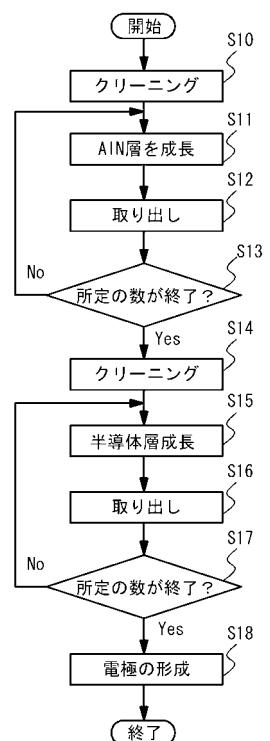

【図6】図6は実施例1に係る半導体装置の製造方法を例示するフローチャートである。

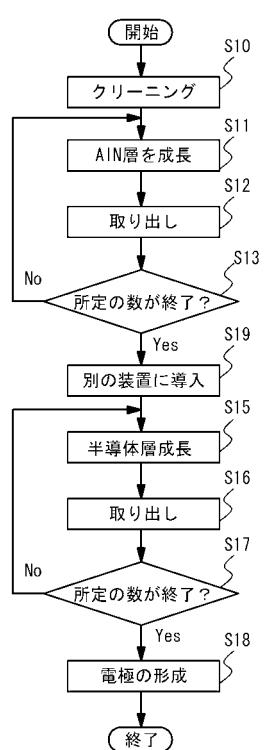

【図7】図7は実施例2に係る半導体装置の製造方法を例示するフローチャートである。

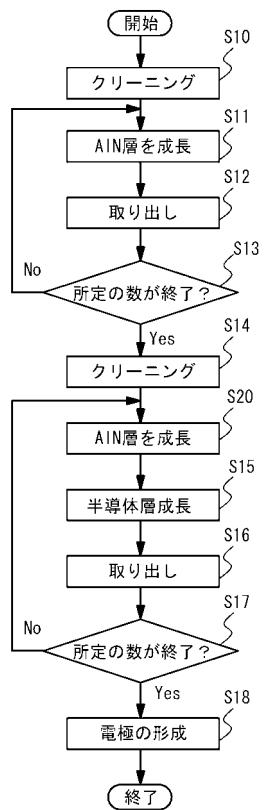

【図8】図8は実施例3に係る半導体装置の製造方法を例示するフローチャートである。

10

【図9】図9は実施例3に係る半導体装置を例示する断面図である。

【図10】図10は実施例3に係るSIMS分析の結果を示す図である。

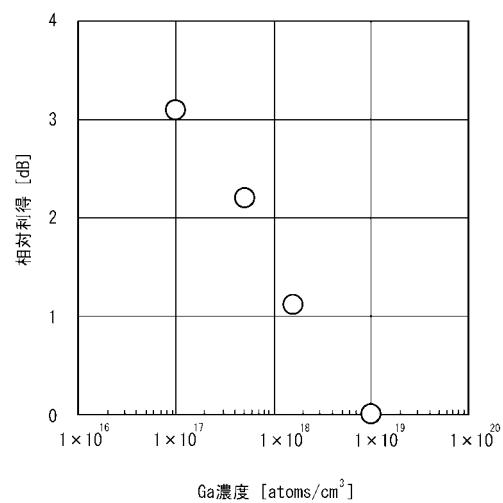

【図11】図11は半導体装置の利得評価結果を示す図である。

## 【発明を実施するための形態】

## 【0019】

実施例の前に、まず比較例について説明する。図1は比較例に係る半導体装置を例示する断面図である。

## 【0020】

図1に示すように、Siからなる基板2上に例えばAlNからなる、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{18}$ atoms/cm<sup>3</sup>以下のAlN層4が形成されている。AlN層4上には、構成元素としてGaを含む窒化物半導体層であるAlGaN層6が形成されている。AlGaN層6上には、GaN層8が設けられている。GaN層8上にはAlGaN層10、AlGaN層10上にはGaN層12が各々設けられている。GaN層12上にはソース電極14、ドレイン電極16、及びゲート電極18が設けられている。ソース電極14及びドレイン電極は、例えばGaN層12に近いほうから順にAuGe/Ni/Au等の金属からなる。ゲート電極18は、例えばGaN層12に近いほうから順にWSi/Ti/Au等の金属からなる。

20

## 【0021】

AlN層4及びAlGaN層6はバッファ層、GaN層8はチャネル層、AlGaN層10は供給層、GaN層12はキャップ層として、各々機能する。このように、図1に例示した半導体装置はHEMTである。本構造では、AlN層4はGaの拡散に対するバッファ層として機能し、GaN系半導体層のGaがSiからなる基板2内に拡散することを抑制する。

30

## 【0022】

しかしながら、比較例に係る半導体装置では、バッファ層が設けられているにも関わらず、基板2に導電層3が形成されている。このため、リーカパスが形成され、また寄生容量が大きくなることがある。この場合、高周波信号の損失が増大し、半導体装置の特性が悪化することがある。次に、導電層3が形成された原因について説明する。

## 【0023】

比較例に係る半導体装置の製造工程においては、AlN層4の形成工程とGaN系半導体層の形成工程とは連続して行われる。従って、複数のウェハーに繰り返してMOCVD成長工程を実施する場合、一度MOCVD装置に導入されたウェハーは、AlN層4とGaN系半導体層とが形成された後、MOCVD装置から取り出される。その後、別のウェハーがMOCVD装置に導入される。ここで、別のウェハーにAlN層を形成する際、MOCVD装置内にGaを含む不純物が残留していることがある。この場合、AlNの成長時にGaが取り込まれ、基板に拡散することがある。これにより、Gaを含んだ導電層3が形成されるものと考えられる。

40

## 【0024】

MOCVD装置内のGaを含む不純物の残留は、AlN層4の形成工程とGaN系半導体層の形成工程とを別個に行われる工程とし、AlN層4の形成工程を繰り返した後に、

50

GaN系半導体層の形成工程を行うことで抑制されると考えられる。

【0025】

次に、本発明の発明者が行った実験について説明する。図2は、実験に用いたサンプルを示す断面図である。

【0026】

図2に示すように、Siからなる基板2上に、厚さT1が300nmのAlN層4が設けられている。AlN層4はMOCVD法により成長したものである。AlN層4の原料は、Alに対するGaN含有量が0.1ppm以下であるTMA(トリメチルアルミニウム)と、純度が99.9999%以上であるNH<sub>3</sub>とを用いる。TMA供給量は10μmol/min、成長温度は1050、NH<sub>3</sub>の流量は0.5mol/min、成長圧力は200torrである。

【0027】

この実験では二種類のサンプルを用いている。AlN層の形成工程とGaN系半導体層の形成工程とを連続的に行つたものをサンプルAとする。AlN層4の形成工程とGaN系半導体層の形成工程とを別個に行い、両工程の間にMOCVD装置のクリーニングを行つたものをサンプルBとする。次に、実験の内容及び結果について説明する。

【0028】

実験は、各サンプルを対象にSIMS(Secondary Ion Mass Spectrometry)分析を行つたものである。図3は比較例についてのSIMS分析の結果を示す図であり、図4は実施例1についてのSIMS分析の結果である。それぞれの図において、横軸は表面からの深さ、左の縦軸はGaN濃度、右の縦軸はSi及びAlの二次イオン強度を示している。

【0029】

図3において、Al濃度が高い領域(深さ0~0.17μm付近)はAlN層4である。また、Si濃度がほぼ一定の領域(深さ0.17μmより深い領域)は基板2である。図3に示すように、AlN層4中のGaN濃度は $1 \times 10^{19}$ atoms/cm<sup>3</sup>であった。これは成長装置内における残留GaNがAlN層4の成長時に取り込まれ、拡散したものと考えられる。基板2中におけるGaN濃度は、基板2とAlN層4との界面付近で $1 \times 10^{17}$ atoms/cm<sup>3</sup>であり、AlN層4から離れるに従つて緩やかに減少するプロファイルを持っていた。この領域は導電層3(図1参照)として機能する領域である。

【0030】

一方、図4においては、Al濃度が高い領域(深さ0~0.14μm付近)はAlN層4である。また、Si濃度がほぼ一定の領域(深さ0.14μmより深い領域)は基板2である。図4に示すように、AlN層4中のGaN濃度は $9 \times 10^{16}$ atoms/cm<sup>3</sup>程度に抑えられていた。そして、基板2とAlN層4との界面付近でGaN濃度は急激に減少し、基板2中のGaN濃度は非常に低く抑えられていた。このことから、サンプルBでは導電層3(図1参照)の形成が抑制されていることが分かった。なお、図4において、AlN層4中にGaNが検出されたのは、分離されずにAl減量中に残留したGaNの混入によるものと考えられる。

【0031】

以上のように、GaNが除去された清浄な成長装置を用いて、基板2上にAlN層4を形成することは、AlN層4中のGaN濃度を下げる効果をもたらし、その結果、導電層3の形成が抑制された。

【0032】

次に、図面を用いて、本発明の実施例について説明する。

【実施例1】

【0033】

まず、実施例1に係る半導体装置の構成について説明する。図5は実施例1に係る半導体装置を例示する断面図である。なお、図1に例示した構成と同様の構成については説明を省略する。

10

20

30

40

50

## 【0034】

図5に示すように、Siからなる基板2上に例えばAlNからなる、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$ atoms/cm<sup>3</sup>以下のAlN層4が形成されている。AlN層4上には、構成元素としてGaを含む窒化物半導体層であるAlGaN層6が形成されている。また、基板2内にGaを含む導電層3(図1参照)が形成されていない。

## 【0035】

次に、実施例1に係る半導体装置の製造方法について説明する。図6は実施例1に係る半導体装置の製造方法を例示するフロー・チャートである。

## 【0036】

図6に示すように、最初にMOCVD装置内のクリーニングを行う(ステップS10)。具体的には、クリーニングの前の工程でGaが付着した反応管などをエッティング等の方法で清浄化を行うこと、また装置の部材の交換、さらにN<sub>2</sub>又はO<sub>2</sub>を流しながら例えば1150に加熱してベーキングを行うことで、MOCVD装置の治具、チャンバー、アクセプター等に付着したGa等の3属元素を含んだ不純物が極力除去された状態を実現する。なお、ベーキングの際の温度は、AlN層4やGaN系半導体層の成長温度よりも高い温度とすることが好ましい。

## 【0037】

ステップS10の後、クリーニングされたMOCVD装置にSiからなるウェハーを導入し、ウェハー上に例えばT1が300nmであるAlN層4を形成する。このときのTMA供給量は、例えば10μmol/minとする。言い換えれば、基板2上に構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$ atoms/cm<sup>3</sup>以下のAlN層4(第1層)を形成する(第1工程、図5のステップS11)。これにより、図2に示したものと同様の状態が形成される。

## 【0038】

ステップS11の後、ウェハーをMOCVD装置から取り出す(ステップS12)。つまり図2に示したような、基板2上にAlN層4が形成されたものをMOCVD装置から取り出す(ステップS12)。例えば、基板2及びAlN層4を大気中に暴露する。

## 【0039】

ステップS12の後、所定の数のウェハーにAlN層4が形成されたか判断する(ステップS13)。Noの場合、ステップS11に戻る。すなわち、基板2上にAlN層4を形成する工程を、複数回繰り返す。

## 【0040】

ステップS13においてYesの場合、ステップS14に進む。ここで、前処理としてのMOCVD装置のクリーニングを行う(ステップS14)。クリーニングの方法はステップS10と同じである。

## 【0041】

ステップS14の後、ステップS11及びS12の工程を経たウェハーを、ステップS11で使用したMOCVD装置に導入し、AlN層4上にGaN系半導体層(第2層)を形成する(第2工程、ステップS15)。すなわち、構成元素としてGaを含むAlGaN層6、GaN層8、AlGaN層10及びGaN層12を形成する。このとき、AlN層4と接触するようにGaN系半導体層は形成される。なお、各層の成長条件は次の通りである。

## 【0042】

AlGaN層6の原料は、TMG(トリメチルガリウム)及びTMAであり、TMG供給量及びTMA供給量は、ともに10μmol/minである。AlGaN層6の厚さは、例えば300nmである。GaN層8の原料はTMGであり、TMG供給量は120μmol/minである。GaN層8の厚さは、例えば1000nmである。AlGaN層10の原料はTMG及びTMAであり、TMG供給量及びTMA供給量は、それぞれ25μmol/min及び5μmol/minである。AlGaN層10の厚さは、例えば2

10

20

30

40

50

0 nmである。GaN層12の原料はTMGであり、TMG供給量は25 μmol/mi<sup>n</sup>である。GaN層12の厚さは、例えば5 nmである。なお、AlN層4の成長には、上記したものと同様に、Alに対するGaN含有量が0.1 ppm以下であるTMA(トリメチルアルミニウム)と純度が99.9999%以上であるNH<sub>3</sub>とを用いる。AlN層4の厚さは150 nmである。

#### 【0043】

ステップS15の後、ウェハーをMOCVD装置から取り出す(ステップS16)。ステップS16の後、所定の数のウェハーにGaN系半導体層が形成されたか判断する(ステップS17)。Noの場合、ステップS15に戻る。すなわち、AlN層4上にGaN系半導体層を形成する工程を、複数回繰り返す。

10

#### 【0044】

ステップS17の後、GaN層12上にソース電極14、ドレイン電極16、及びゲート電極18を形成する(ステップS18)。以上の工程により実施例1に係る半導体装置が完成する。

#### 【0045】

実施例1によれば、図6に示すように、AlN層4の形成工程(ステップS11)とGaN系半導体層の形成工程(ステップS15)とを別個に行われる工程とし、AlN層4の形成工程を複数回繰り返した後、GaN系半導体層の形成工程を実施する。このため、AlN層4形成工程前にMOCVD装置内にGaを含む不純物が残留することが抑制される。従って、AlN層4成長時にGaが取り込まれることが抑制される。よって、図1に示すような基板2上に導電層3が形成されることが抑制される。

20

#### 【0046】

また、Gaのみならず、他の3属元素の取り込みも抑制できる。これにより、高抵抗の基板として用いられている、Siからなる基板2の抵抗を高く維持できる。よって、半導体装置の特性の悪化が抑制される。

#### 【0047】

なお、GaN系半導体とは、GaやNを含む半導体である。GaN系半導体の例としてGaNやAlGaNを例に説明したが、他にInGaNやInAlGaN等、他のGaN系半導体を用いる場合でも、本発明は適用可能である。また、第1層として、構成元素としてGaを含まず、かつGa不純物濃度が2×10<sup>-8</sup> atoms/cm<sup>3</sup>以下の、AlN以外の窒化物半導体層を用いてもよい。窒化物半導体とは、窒素(N)を含む半導体である。

30

#### 【0048】

AlN層4の厚さT1は300 nmとしたが、これに限定されない。T1を例えば200 nmとすることで、後述するクラックの発生を抑制でき、かつバッファ層としての機能も得ることができる。

#### 【実施例2】

#### 【0049】

次に実施例2について説明する。図7は実施例2に係る半導体装置の製造方法を例示するフローチャートである。

40

#### 【0050】

図7に示すように、まずステップS10において、MOCVD装置内をクリーニングする。このクリーニングは、図6におけるステップS10とは異なり、通常の成長前クリーニングでよい。次に、ステップS11に示すように、AlN層4を成長し、ステップS12において、ウェハーをMOCVD装置から取り出す。ステップS13では、ウェハーの処理枚数が所定枚数に達するまで、ステップS11～S12を繰り返す。ステップS12～S13は、図6に示したものと同様である。

#### 【0051】

ステップS12終了後、ウェハーをステップS11に用いたMOCVD装置とは別のMOCVD装置に導入する(ステップS19)。ステップS19の後は図6に例示した工程

50

と同様に、ステップS15～S18を行う。すなわち、GaN系半導体層の形成工程は、AlN層4の形成工程に用いられたMOCVD装置とは別のMOCVD装置を用いて実施される。

#### 【0052】

実施例2によれば、AlN層4の形成工程（ステップS11）とGaN系半導体層の形成工程（ステップS15）とは別個に行われ、かつ異なるMOCVD装置を用いる工程としている。このため、MOCVD装置内にGaを含む不純物が混入することが抑制され、AlN層4成長時にGaが取り込まれることが抑制される。よって、基板2とAlN層4との界面にGaを含んだ導電層が形成されることが抑制され、半導体装置の特性の悪化が抑制される。

10

#### 【0053】

また、別のMOCVD装置を用いるため、AlN層4の形成工程とGaN系半導体層の形成工程とを並行して実施できる。従って、半導体装置の製造工程のスピードアップが可能となる。また、AlN層4やGaN系半導体層は、MOCVD法以外の成長方法を用いて成長してもよい。不純物を取り除くためには、GaN系半導体層の形成工程に用いられるMOCVD装置も、ステップS15の前にクリーニングすることが好ましい。

#### 【実施例3】

#### 【0054】

次に実施例3について説明する。図8は実施例3に係る半導体装置の製造方法を例示するフローチャートである。また、図9(a)は後述するステップS11実施後における半導体装置を例示する断面図であり、図9(b)はステップS18実施後における半導体装置を例示する断面図である。

20

#### 【0055】

図8に示すように、ステップS10の後、基板2上に、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$ atoms/cm<sup>3</sup>以下のAlN層4a(第1層)を形成する(ステップS11)。

#### 【0056】

図9(a)に示すように、ステップS11で形成されるAlN層4aの厚さT2は例えば150nmとし、半導体装置完成時のAlN層の厚さT1(図5及び図9(b)参照)の例えば半分とする。

30

#### 【0057】

ステップS11の後、AlN層4aを形成したウェハー、つまり図9(a)に例示する状態のものをMOCVD装置から取り出す(ステップS12)。例えば、基板2及びAlN層4aを大気中に暴露する。次に、ステップS13及びS14を実施する。ステップS10～S14は図6に例示した工程と同じである。

#### 【0058】

ステップS14の後、ステップS11で形成したAlN層4a上に、例えば厚さT3が150nmである、構成元素としてGaを含まず、かつGa不純物濃度が $2 \times 10^{-8}$ atoms/cm<sup>3</sup>以下のAlN層4b(第3層)を形成する(第3工程、ステップS20)。このとき、AlN層4aと接触するように、AlN層4bは形成される。

40

#### 【0059】

ステップS20の後、AlN層4b上にGaN系半導体層を形成する(ステップS15)。ステップS15の後に行われるステップS16～S18は、図6に例示した工程と同様の工程である。図9(b)に示すように、以上の工程により、実施例3に係る半導体装置が完成する。AlN層4aとAlN層4bとは、厚さT1が例えば300nmのAlN層4を形成する。各層の成長条件は、以下の通りである。

#### 【0060】

AlN層4aの原料及びAlN層4bの原料はTMAであり、TMA供給量は10μmol/minである。AlN層4aの厚さ及びAlN層4bの厚さは、例えば150nmである。AlGaN層6の原料は、TMG及びTMAであり、TMG供給量及びTMA供

50

給量は、ともに  $10 \mu\text{mol}/\text{min}$  である。AlGaN層6の厚さは、例えば  $300 \text{ nm}$  である。GaN層8の原料はTMGであり、TMG供給量は  $120 \mu\text{mol}/\text{min}$  である。GaN層8の厚さは、例えば  $1000 \text{ nm}$  である。AlGaN層10の原料は、TMG及びTMAであり、TMG供給量及びTMA供給量は、それぞれ  $25 \mu\text{mol}/\text{min}$  及び  $5 \mu\text{mol}/\text{min}$  である。AlGaN層10の厚さは、例えば  $20 \text{ nm}$  である。GaN層12の原料はTMGであり、TMG供給量は  $25 \mu\text{mol}/\text{min}$  である。GaN層12の厚さは、例えば  $5 \text{ nm}$  である。なお、AlN層4の成長には、上記したものと同様に、Alに対するGa含有量が  $0.1 \text{ ppm}$  以下であるTMA(トリメチルアルミニウム)と純度が  $99.9999\%$  以上であるNH<sub>3</sub>を用いた。AlN層4の厚さは  $150 \text{ nm}$  である。

10

#### 【0061】

実施例3によれば、実施例1と同様に、AlN層4aの形成工程(ステップS20)とGaN系半導体層の形成工程(ステップS15)とを別個に行われる工程とし、AlN層4aの形成工程を複数回繰り返した後、GaN系半導体層の形成工程を実施する。このため、MOCVD装置内にGaを含む不純物が残留することが抑制される。従って、基板2とAlN層4との界面にGaを含んだ導電層が形成されることが抑制され、半導体装置の特性の悪化が抑制される。

#### 【0062】

図10は、実施例3においてAlN層4bの成長が終了した状態におけるSIMS分析の結果を示す図である。Ga濃度が高い  $0.0.17 \mu\text{m}$  付近の領域はAlN層4bであり、Ga濃度が低下している  $0.17 \sim 0.3 \mu\text{m}$  付近の領域はAlN層4aである。また、Si濃度がほぼ一定である  $0.3 \mu\text{m}$  より深い領域は基板2である。

20

#### 【0063】

図10に示すように、AlN層4bのGa濃度は  $1 \times 10^{19} \text{ atoms/cm}^3$  程度であるが、AlN層4a中は  $2 \times 10^{17} \text{ atoms/cm}^3$  程度である。そして、基板2とAlN層4aとの界面付近では、 $1 \times 10^{16} \text{ atoms/cm}^3$  程度であり、深さ方向にGa濃度が急激に低下している。AlN層4bは、Gaを含む層を成長するMOCVD装置にて形成されることから、比較的Ga濃度が高い。しかし、AlN層4aにおいてGa濃度は低下している。このことから、AlN層4aは、Ga拡散を抑制する効果を発揮しているものと考えられる。

30

#### 【0064】

なお、Siからなる基板2とAlN層4とでは熱膨張係数に差がある。AlN層4が厚過ぎると、ウェハーをMOCVD装置から取り出し、基板2とAlN層4とを大気中に暴露した際に、基板2の反りが発生し、AlN層4にクラックが発生することもある。

#### 【0065】

実施例3によれば、半導体装置完成時のAlN層4よりも薄いAlN層4aを形成した後、ウェハーをMOCVD装置から取り出す(図7のステップS11及びS12)。また、AlN層4bの形成工程とGaN系半導体層の形成工程とは、連続して実施する工程としている。例えば、AlN層4bの形成工程の後、基板2及びAlN層4bを大気中に暴露することなくGaN系半導体層の形成工程を行う。従って、AlN層4に反りやクラックが発生しにくくなる。

40

#### 【0066】

また、AlN層4aを形成した後、AlN層4a上にAlN層4bが形成される(ステップS20)。従って、バッファ層として機能するために十分な厚さを有したAlN層4が基板2上に形成される。また、第3層はAlN層としたが、第1層同様に、構成元素としてGaを含まず、かつGa不純物濃度が  $2 \times 10^{18} \text{ atoms/cm}^3$  以下の、AlN以外の窒化物半導体層を用いてもよい。

#### 【0067】

AlN層4aの厚さT2は例えば  $150 \text{ nm}$  としたが、薄い方がクラックの抑制には好みしい。すなわち、T2を例えば  $100 \text{ nm}$  より薄くすることでよりクラックを抑制でき

50

、T<sub>2</sub>を50nmより薄くするとより好ましい。AlN層4aは薄すぎると成長が困難となるため、T<sub>2</sub>は10nm以上が好ましい。また、AlN層4bの厚さT<sub>3</sub>は150nmとしたが、AlN層4aの厚さT<sub>2</sub>に応じて適宜変更可能である。AlN層4がバッファ層として機能するためには、T<sub>3</sub>は150nmより厚いことが好ましく、T<sub>3</sub>を200nmより厚くすることで、より十分な厚さのバッファ層を確保することができる。

#### 【0068】

実施例3においても、実施例2のようにAlN層4aを形成する工程と、AlN層4bを形成する工程及びGaN系半導体層を形成する工程とは、別のMOCVD装置を用いてよい。

#### 【0069】

最後に、図11に本発明の実施例1に係る半導体装置の利得評価の結果を示す。これは、実施例1におけるクリーニング(図6のステップS10)の程度を変化させ、AlN層4中のGaN濃度を変えた基板を作成し、その上に半導体層及び電極までを形成した半導体装置の利得結果である(図5参照)。図11の横軸はAlN層4中のGaN濃度を示し、縦軸は比較例(図1参照)の利得を基準とした実施例1の相対利得を示す。

#### 【0070】

図11に示すように、比較例においては、AlN層4中のGaN濃度が $1 \times 10^{19}$ atoms/cm<sup>3</sup>程度であった。AlN層4中のGaN濃度が $2 \times 10^{18}$ atoms/cm<sup>3</sup>程度のときは、比較例に対して約1dBの利得の向上が確認された。同様に、AlN層4中のGaN濃度が $5 \times 10^{17}$ atoms/cm<sup>3</sup>程度のときは、約2dBの利得の向上が確認された。GaN濃度が $1 \times 10^{17}$ atoms/cm<sup>3</sup>程度のときには、約3dBの利得の向上が確認された。以上の結果から、本発明を実施しない状態(比較例)に対して1dB以上の利得向上の効果を得るために、 $2 \times 10^{18}$ atoms/cm<sup>3</sup>以下のGaN濃度が実現されていることが好ましい。

#### 【0071】

なお、 $2 \times 10^{18}$ atoms/cm<sup>3</sup>以下のGaN濃度を実現するためには、AlN層4を成長するためのAl原料の純度を考慮する必要がある。MOCVD法を利用してAlN層4を形成するためには、例えばTMAのようなAlの有機原料中のAlに対するGaNは、2ppm以下であることが好ましい。また、MBE法を利用してAlN層4を形成するためには、MBE法のソース原料であるAlに対するGaNが40ppm以下であることが好ましい。

#### 【0072】

また、AlN層4におけるGaN濃度を $5 \times 10^{17}$ atoms/cm<sup>3</sup>程度とする場合、MOCVD法を採用するときには、Alの有機原料中のAlに対するGaNは0.5ppm以下であることが好ましい。MBE法を採用するときには、ソース原料であるAlに対するGaNが10ppm以下とすることが好ましい。

#### 【0073】

さらに、AlN層4におけるGaN濃度を $1 \times 10^{17}$ atoms/cm<sup>3</sup>程度とする場合には、MOCVD法を採用するときには、Alの有機原料中のAlに対するGaNは0.1ppm以下であることが好ましい。MBE法を採用するときには、ソース原料であるAlに対するGaNが2ppm以下とすることが好ましい。

#### 【0074】

実施例において半導体装置はHEMTであるとしたが、HEMT以外の半導体装置、例えばFET等であってもよい。特に高周波デバイスに本発明を適用することで、リーグパスや寄生容量に起因する、特性の悪化を抑制することが可能となる。また、各層の成長方法としては、MOCVD法、MBE法の他に、HYPE法を用いてよい。各方法では、成長装置としてそれぞれMOCVD装置、MBE装置、及びHYPE装置を用いる。

#### 【0075】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形

・変更が可能である。

【符号の説明】

【0076】

|        |         |

|--------|---------|

| 基板     | 2       |

| 導電層    | 3       |

| A1N層   | 4、4a、4b |

| A1GaN層 | 6、10    |

| GaN層   | 8、12    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

---

フロントページの続き

(72)発明者 中田 健

山梨県中巨摩郡昭和町大字紙漉阿原1000番地 ユーディナデバイス株式会社内

(72)発明者 河内 剛志

山梨県中巨摩郡昭和町大字紙漉阿原1000番地 ユーディナデバイス株式会社内

審査官 和瀬田 芳正

(56)参考文献 国際公開第2008/048303 (WO, A1)

特開2009-7205 (JP, A)

特表2009-509341 (JP, A)

特開2009-231550 (JP, A)

特開2010-225710 (JP, A)

特開平11-112030 (JP, A)

(58)調査した分野(Int.Cl., DB名)

C23C 16/34

H01L 21/203 - 21/205

H01L 21/338

H01L 29/778

H01L 29/812