(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4530527号

(P4530527)

(45) 発行日 平成22年8月25日(2010.8.25)

(24) 登録日 平成22年6月18日(2010.6.18)

(51) Int.Cl.

|                |           |     |               |         |

|----------------|-----------|-----|---------------|---------|

| HO 1 L 21/8244 | (2006.01) | F 1 | HO 1 L 27/10  | 3 8 1   |

| HO 1 L 27/11   | (2006.01) |     | G 1 1 C 11/34 | 3 4 1 C |

| G 1 1 C 11/413 | (2006.01) |     | HO 1 L 21/82  | F       |

| HO 1 L 21/82   | (2006.01) |     | G 1 1 C 29/00 | 6 0 3 N |

| G 1 1 C 29/04  | (2006.01) |     | HO 1 L 27/04  | M       |

請求項の数 6 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2000-374261 (P2000-374261)

(22) 出願日

平成12年12月8日(2000.12.8)

(65) 公開番号

特開2002-176111 (P2002-176111A)

(43) 公開日

平成14年6月21日(2002.6.21)

審査請求日

平成19年10月17日(2007.10.17)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 將行

最終頁に続く

(54) 【発明の名称】スタティック型半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数行複数列に配置された複数のメモリセルと、各行に対応して設けられたワード線と、各列に対応して設けられたビット線対とを備え、不良な行または列をスペア行または列で置換する冗長方式が採用されたスタティック型半導体記憶装置であって、

各ワード線に対応して設けられて対応のワード線と基準電位のラインとの間に接続され、対応のワード線が選択されていない場合に導通して対応の各メモリセルを非活性状態にするための第1のスイッチング素子、

各行または列に対応して設けられ、その一方端が対応の行または列の各メモリセルの電源ノードに接続された電源配線、

各電源配線に対応して設けられて対応の電源配線の他方端と電源電位のラインとの間に接続され、前記第1のスイッチング素子の導通抵抗値よりも大きな予め定められた導通抵抗値を有する第2のスイッチング素子、および

各行または列に対応して設けられ、対応の行または列が不良である場合にブローされるヒューズを含み、該ヒューズがブローされたことに応じて前記第2のスイッチング素子を非導通にするプログラム回路を備える、スタティック型半導体記憶装置。

## 【請求項 2】

前記電源配線および前記プログラム回路は各列に対応して設けられ、

前記スタティック型半導体記憶装置は、

さらに、各ビット線に対応して設けられ、その一方電極が対応のビット線に接続された

10

20

ビット線負荷素子、および

各列に対応して設けられて対応の列の各ビット線負荷素子の他方電極と電源電位のラインとの間に接続された第3のスイッチング素子を備え、

前記プログラム回路は、前記ヒューズがブローされたことに応じて前記第2のスイッチング素子とともに前記第3のスイッチング素子も非導通にする、請求項1に記載のスタティック型半導体記憶装置。

【請求項3】

前記プログラム回路は、

第1のノードと第1の電位のラインとの間に接続され、リセット信号が第1のレベルから第2のレベルに変化したことに応じて導通し、前記第1のノードの電位を前記第1の電位にリセットするための第4のスイッチング素子、

10

前記第1のノードと第2の電位のラインとの間に前記ヒューズと直列接続され、前記リセット信号が前記第2のレベルから前記第1のレベルに変化したことに応じて導通し、前記ヒューズがブローされていない場合に前記第1のノードを前記第2の電位にするための第5のスイッチング素子、および

前記リセット信号が前記第2のレベルから前記第1のレベルに変化してから予め定められた時間だけ経過したことに応じて前記第1のノードの電位をラッチし、ラッチした電位が前記第1の電位の場合に前記第2のスイッチング素子を非導通にするためのラッチ回路を含む、請求項1または請求項2に記載のスタティック型半導体記憶装置。

【請求項4】

さらに、第1の導電形式の半導体基板、

前記半導体基板の表面に形成された第2の導電形式の半導体埋込層、

前記半導体埋込層の表面に形成された第1の導電形式の複数の第1のウェル、および

前記半導体埋込層の表面に前記複数の第1のウェルの間にそれぞれ形成された第2の導電形式の複数の第2のウェルを備え、

20

前記複数のメモリセルは、前記複数の第1のウェルおよび前記複数の第2のウェルの表面に形成されている、請求項1から請求項3のいずれかに記載のスタティック型半導体記憶装置。

【請求項5】

前記第2のスイッチング素子は、前記予め定められた導通抵抗値を有するトランジスタを含む、請求項1から請求項4のいずれかに記載のスタティック型半導体記憶装置。

30

【請求項6】

前記第2のスイッチング素子は、

前記予め定められた導通抵抗値を有する抵抗素子、および

前記電源配線の他方端と前記電源電位のラインとの間に前記抵抗素子と直列接続されたトランジスタを含む、請求項1から請求項4のいずれかに記載のスタティック型半導体記憶装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

40

この発明はスタティック型半導体記憶装置に関し、特に、不良な行または列をスペア行または列で置換する冗長方式が採用されたスタティック型半導体記憶装置に関する。

【0002】

【従来の技術】

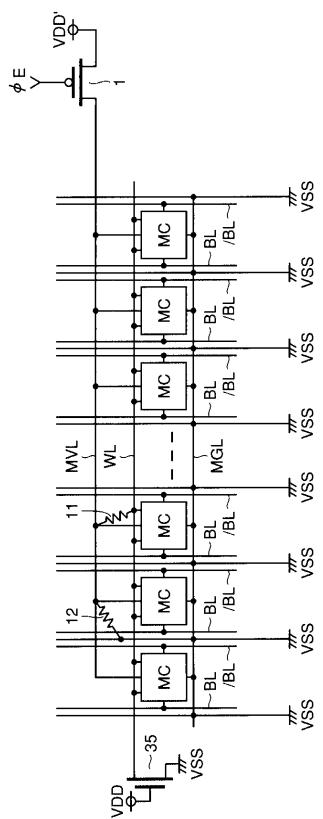

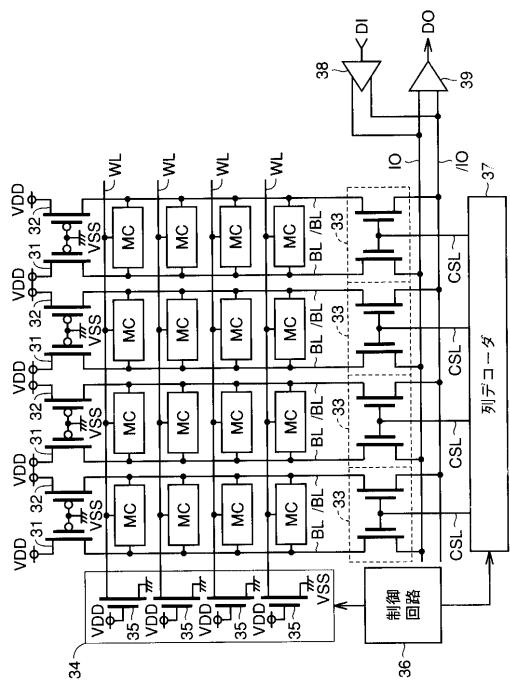

図10は、従来のスタティックランダムアクセスメモリ（以下、SRAMと称す）の構成を示す回路ブロック図である。

【0003】

図10において、このSRAMは、複数行複数列（図では4行4列）に配置された複数のメモリセルMCと、各行に対応して設けられたワード線WLと、各列に対応して設けられたビット線対BL, /BLとを備える。

50

## 【0004】

また、このS R A Mは、各ビット線対B L , / B Lに対応して設けられ、対応のビット線対B L , / B Lを「H」レベルに充電するためのビット線負荷3 1 , 3 2と、データ入出力線対I O , / I Oと、各ビット線対B L , / B Lに対応して設けられ、対応のビット線対B L , / B Lとデータ入出力線対I O , / I Oとを接続するための列選択ゲート3 3と、各ビット線対B L , / B Lに対応して設けられた列選択線C S Lとを備える。

## 【0005】

ビット線負荷3 1 , 3 2は、それぞれ電源電位V D Dのラインとビット線B L , / B Lの一方端との間に接続され、各々のゲートがともに接地電位V S Sのラインに接続された1対のPチャネルM O Sトランジスタを含む。列選択ゲート3 3は、それぞれビット線B L , / B Lの他方端とデータ入出力線I O , / I Oの一方端との間に接続され、各々のゲートがともに列選択線C S Lを介して列デコーダ3 7に接続された1対のNチャネルM O Sトランジスタを含む。

10

## 【0006】

さらに、このS R A Mは、行デコーダ3 4、制御回路3 6、列デコーダ3 7、書き回路3 8、および読み出回路3 9を備える。行デコーダ3 4は、外部から与えられる行アドレス信号に従って複数のワード線W Lのうちのいずれかのワード線W Lを選択し、そのワード線W Lを非選択レベルの「L」レベルから選択レベルの「H」レベルに立上げる。行デコーダ3 4は、各ワード線W Lに対応して設けられ、対応のワード線W Lを非選択レベルの「L」レベルにするためのNチャネルM O Sトランジスタ3 5を含む。図1 0では、各NチャネルM O Sトランジスタ3 5のゲートに電源電位V D Dが与えられ、各ワード線W Lが対応のNチャネルM O Sトランジスタ3 5を介して接地されている状態が示される。制御回路3 6は、外部から与えられる制御信号に従ってS R A M全体を制御する。列デコーダ3 7は、外部から与えられる列アドレス信号に従って複数の列選択線C S Lのうちのいずれかの列選択線C S Lを選択し、その列選択線C S Lを非選択レベルの「L」レベルから選択レベルの「H」レベルに立上げる。

20

## 【0007】

書き回路3 8および読み出回路3 9は、ともにデータ入出力線対I O , / I Oの他方端に接続される。書き回路3 8は、外部から与えられたデータD Iを行デコーダ3 4および列デコーダ3 7によって選択されたメモリセルM Cに書き込む。読み出回路3 9は、行デコーダ3 4および列デコーダ3 7によって選択されたメモリセルM Cからの読み出データD Oを外部に出力する。

30

## 【0008】

次に、図1 0に示したS R A Mの動作について説明する。書き動作時は、行アドレス信号に対応する行のワード線W Lが行デコーダ3 4によって選択レベルの「H」レベルに立上げられ、その行の各メモリセルM Cが活性化される。次いで、列アドレス信号に対応する列の列選択線C S Lが列デコーダ3 7によって選択レベルの「H」レベルに立上げられ、その列の活性化されたメモリセルM Cがビット線対B L , / B L、列選択ゲート3 3およびデータ入出力線対I O , / I Oを介して書き回路3 8に接続される。

40

## 【0009】

書き回路3 8は、外部から与えられたデータD Iに従ってデータ入出力線対I O , / I Oのうちの一方を「H」レベルにするとともに他方を「L」レベルにし、活性化されたメモリセルM CにデータD Iを書き込む。ワード線W Lおよび列選択線C S Lが非選択レベルの「L」レベルに立下げられると、そのメモリセルM Cにデータが記憶される。

## 【0010】

読み出動作時は、列アドレス信号に対応する列の列選択線C S Lが列デコーダ3 7によって選択レベルの「H」レベルに立上げられ、その列の各メモリセルM Cがビット線対B L , / B L、列選択ゲート3 3およびデータ入出力線対I O , / I Oを介して読み出回路3 9に接続される。次いで、行アドレス信号に対応する行のワード線W Lが行デコーダ3 4によって選択レベルの「H」レベルに立上げられ、その行の各メモリセルM Cが活性化される

50

。これにより、デコーダ37, 34によって選択されたメモリセルMCが記憶しているデータに応じてビット線対BL, /BLのうちの一方からそのメモリセルMCに電流が流入し、データ入出力線対IO, /IOのうちの一方の電位が低下する。読出回路39は、データ入出力線IOと/IOの電位を比較し、比較結果に応じたデータDOを外部に出力する。

#### 【0011】

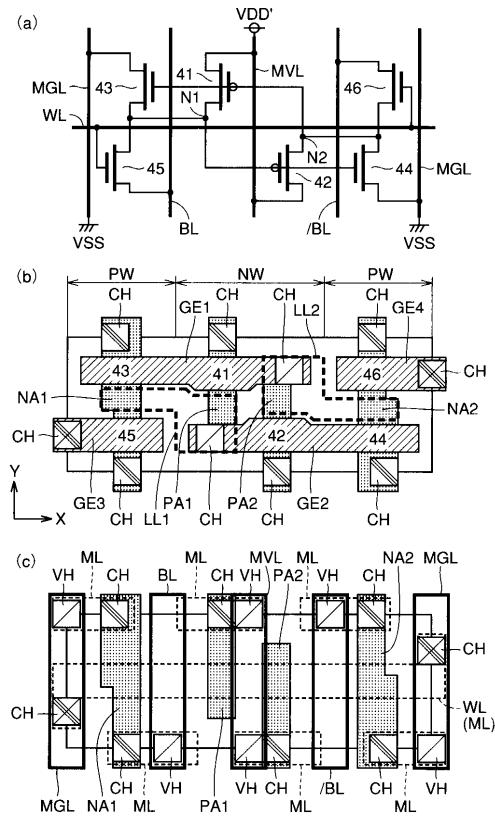

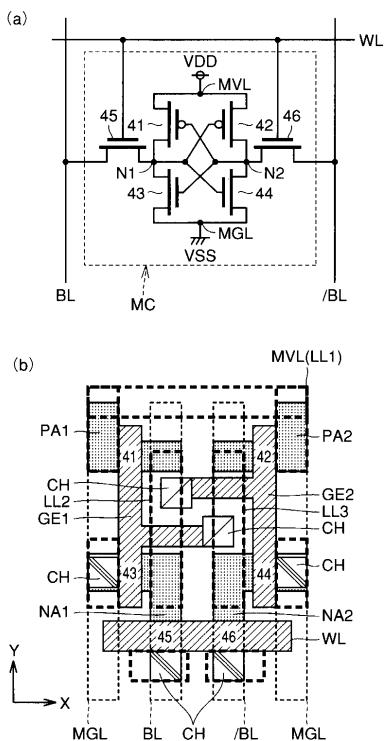

図11(a)はメモリセルMCの構成を示す回路図である。図11(a)において、このメモリセルMCは、負荷トランジスタ(PチャネルMOSトランジスタ)41, 42、ドライバトランジスタ(NチャネルMOSトランジスタ)43, 44およびアクセストランジスタ(NチャネルMOSトランジスタ)45, 46を含む。PチャネルMOSトランジスタ41, 42は、それぞれメモリセル電源配線MVLと記憶ノードN1, N2との間に接続され、各々のゲートはそれぞれノードN2, N1に接続される。メモリセル電源配線MVLには、電源電位VDDが供給される。NチャネルMOSトランジスタ43, 44は、それぞれ記憶ノードN1, N2とメモリセル接地配線MGLとの間に接続され、各々のゲートはそれぞれノードN2, N1に接続される。NチャネルMOSトランジスタ45, 46は、それぞれ記憶ノードN1, N2とビット線BL, /BLとの間に接続され、各々のゲートはともにワード線WLに接続される。

#### 【0012】

書込動作時は、書込データDIに応じてビット線BL, /BLのうちの一方が「H」レベルにされるとともに他方が「L」レベルにされる。次いで、ワード線WLが選択レベルの「H」レベルにされてNチャネルMOSトランジスタ45, 46が導通し、ビット線BL, /BLのレベルがそれぞれ記憶ノードN1, N2に与えられる。記憶ノードN1, N2にそれぞれ「H」レベルおよび「L」レベルが与えられた場合は、MOSトランジスタ41, 44が導通するとともにMOSトランジスタ42, 43が非導通になり、記憶ノードN1, N2のレベルがMOSトランジスタ41~44によってラッチされる。また、記憶ノードN1, N2にそれぞれ「L」レベルおよび「H」レベルが与えられた場合は、MOSトランジスタ42, 43が導通するとともにMOSトランジスタ41, 44が非導通になり、記憶ノードN1, N2のレベルがMOSトランジスタ41~44によってラッチされる。ワード線WLが非選択レベルの「L」レベルにされると、NチャネルMOSトランジスタ45, 46が非導通になって、記憶ノードN1, N2のレベルが保持される。

#### 【0013】

読出動作時は、図10のビット線負荷31, 32によってビット線BL, /BLの各々が「H」レベルに充電される。ワード線WLが選択レベルの「H」レベルにされると、NチャネルMOSトランジスタ45, 46が導通する。記憶ノードN1, N2にそれぞれ「H」レベルおよび「L」レベルがラッチされている場合は、ビット線/BLからNチャネルMOSトランジスタ46, 44を介してメモリセル接地線MGLに電流が流出し、ビット線BL, /BLはそれぞれ「H」レベルおよび「L」レベルになる。また、記憶ノードN1, N2にそれぞれ「L」レベルおよび「H」レベルがラッチされている場合は、ビット線BLからNチャネルMOSトランジスタ45, 43を介してメモリセル接地線MGLに電流が流出し、ビット線BL, /BLがそれぞれ「L」レベルおよび「H」レベルになる。ビット線BLと/BLのレベルを比較することにより、メモリセルMCの記憶データが読出される。ワード線WLが非選択レベルの「L」レベルにされると、NチャネルMOSトランジスタ45, 46が非導通になってデータの読出が終了する。

#### 【0014】

図11(b)は、メモリセルMCのレイアウトを示す図である。シリコン基板の表面に、図中Y方向に延在する2本のゲート電極GE1, GE2が平行に形成されるとともに、図中X方向に延在するワード線WLが形成される。ゲート電極GE1, GE2およびワード線WLは、ポリシリコン層で形成される。ゲート電極GE1, GE2の一方端部の一方側から他方側にかけてそれぞれP型活性層PA1, PA2が形成される。ゲート電極GE1の他方端部の一方側から他方側およびワード線WLの一方端部の一方側から他方側にかけ

10

20

30

40

50

てN型活性層NA1が形成される。ゲート電極GE2の他方端部の一方側から他方側およびワード線WLの他方端部の一方側から他方側にかけてN型活性層NA2が形成される。

【0015】

P型活性層PA1とゲート電極GE1、P型活性層PA2とゲート電極GE2は、それぞれPチャネルMOSトランジスタ41, 42を構成する。N型活性層NA1とゲート電極GE1、N型活性層NA2とゲート電極GE2は、それぞれNチャネルMOSトランジスタ43, 44を構成する。N型活性層NA1とワード線WL、N型活性層NA2とワード線WLは、それぞれNチャネルMOSトランジスタ45, 46を構成する。

【0016】

次に、複数のローカル配線LLが形成される。図11(b)において、ローカル配線LLと活性層が重なっている部分では、ローカル配線LLと活性層が導通している。活性層PA1, PA2の一方端部(PチャネルMOSトランジスタ41, 42のソース)は、ともにメモリセル電源配線MVLに接続される。メモリセル電源配線MVLは、ローカル配線LL1で構成されている。

10

【0017】

P型活性層PA1の他方端部(PチャネルMOSトランジスタ41のドレイン)は、ローカル配線LL2を介してN型活性層NA1の中央部(NチャネルMOSトランジスタ43, 45のドレイン)に接続される。P型活性層PA2の他方端部(PチャネルMOSトランジスタ42のドレイン)は、ローカル配線LL3を介してN型活性層NA2の中央部(NチャネルMOSトランジスタ44, 46のドレイン)に接続される。ローカル配線LL2, LL3は、それぞれコンタクトホールCH, CHを介してゲート電極GE2, GE1に接続される。

20

【0018】

さらに、第1アルミ配線層によって、図中Y方向に延在するビット線BL, /BLおよびメモリセル接地線MGL, MGLが平行に形成される。N型活性層NA1, NA2の一方端部(NチャネルMOSトランジスタ43, 44のソース)は、それぞれコンタクトホールCH, CHを介してメモリセル接地線MGL, MGLに接続される。N型活性層NA1, NA2の他方端部(NチャネルMOSトランジスタ45, 46のドレイン)は、それぞれコンタクトホールCH, CHを介してビット線BL, /BLに接続される。

30

【0019】

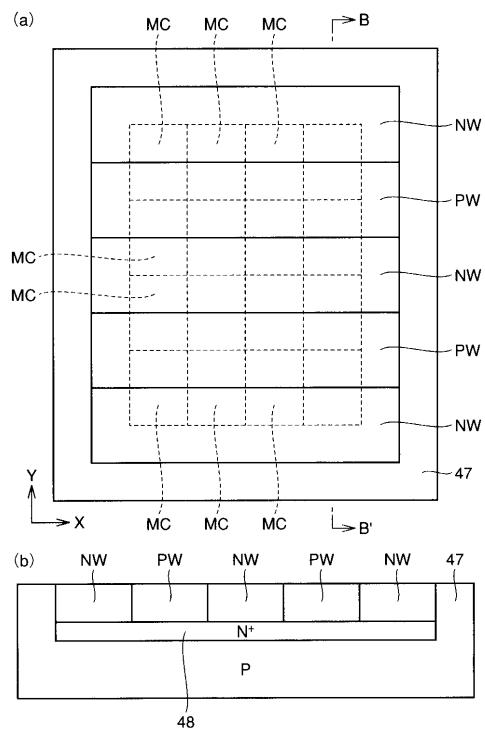

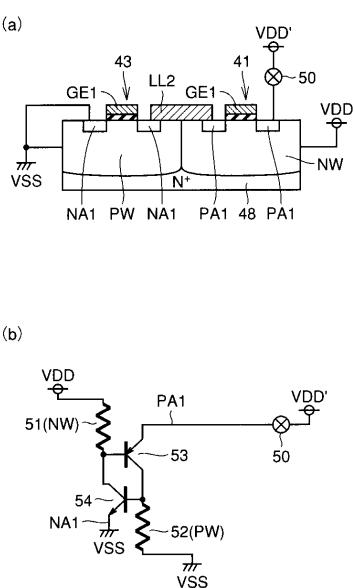

メモリセルMCの基板は、図12に示すように、トリプルウェル構造にされている。すなわち、P型シリコン基板47の表面にN<sup>+</sup>型埋込層48が形成され、さらにその表面に複数(図では3つ)のN型ウェルNWが形成され、3つのN型ウェルNWの間にそれぞれ2つのP型ウェルPWが形成される。各メモリセルMCは、隣接するN型ウェルNWおよびP型ウェルPWの表面に形成される。図10で示したP型活性層PA1, PA2は、N型ウェルNWの表面に形成され、N型活性層NA1, NA2はP型ウェルPWの表面に形成される。図12では、4行4列に配置された16個のメモリセルMCが示されている。トリプルウェル構造では、P型シリコン基板47で発生した電子-ホール対がN<sup>+</sup>型埋込層でトラップされるため、ソフトエラーの発生が抑制される。

40

【0020】

さて、このようなSRAMでは、製造中にメモリセルMCに異物が付着し、(1)記憶ノードN1, N2間のショート、(2)記憶ノードN1またはN2とメモリセル電源配線MVL間のショート、(3)記憶ノードN1またはN2とメモリセル接地配線MGL間のショート、(4)記憶ノードN1またはN2とワード線WL間のショート、(5)記憶ノードN1またはN2とビット線BLまたは/BL間のショート、(6)ビット線BLまたは/BLとワード線WL間のショート、(7)ワード線WLとメモリセル電源配線MVL間のショート、(8)ビット線BLまたは/BLとメモリセル接地配線MGL間のショート、(9)メモリセル電源配線MVLとメモリセル接地配線MGL間のショートが発生する場合がある。図11で示したメモリセルMCでは、ビット線BL, /BLとメモリセル接地配線MGL, MGLが平行に隣接して配置されているので、特に(8)のショートが発

50

生しやすい。

【0021】

このようなショートが発生したメモリセルMCは正常に動作しなくなる。そこで、SRA Mでは、不良なメモリセルMCを含む行または列と置換するためのスペア行または列と、不良な行または列のアドレスをプログラムするためのプログラム回路を設けておき、不良な行または列のアドレスが入力された場合は不良な行または列の代わりにスペア行または列を選択することにより、不良品を救済する冗長方式が採用されている。

【0022】

しかし、単に不良な行または列をスペア行または列と置換するだけでは、ショートした部分にリーク電流が流れ続け、スタンバイ電流が規格値をオーバーしてしまう。そこで、スタンバイ電流を低減化するため、種々の方法が提案されている。

10

【0023】

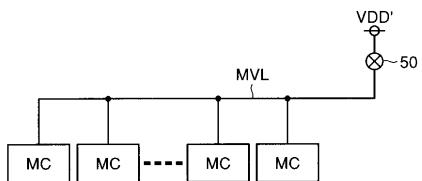

図13の方法では、各メモリセル行に対応してヒューズ50が設けられる。ヒューズ50は、対応の行のメモリセル電源配線MVLと電源電位VDDのラインとの間に接続され、対応の行が不良である場合はブローされる。ヒューズ50がブローされると、上記(1)～(4)(7)(9)のショートがある場合でも、電源電位VDDのラインからメモリセル電源配線MVLおよび不良メモリセルのショート部分に流出する電流が遮断されるので、スタンバイ電流が低減化される。このような方法は、たとえば特開平7-230699号公報に開示されている。

【0024】

20

【発明が解決しようとする課題】

しかし、この方法では、ヒューズ50のブローが不十分である場合は、スタンバイ電流の低減化も不十分になるという問題があった。

【0025】

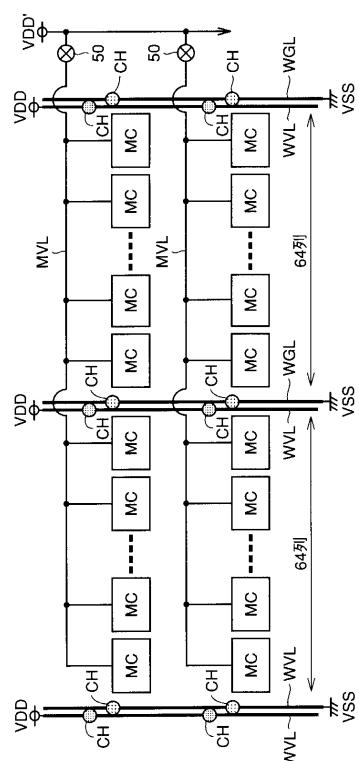

また、図14は、図13に示した方法が適用されたSRA Mをより詳細に示す図である。図14において、このSRA Mでは、複数列(図では64列)ごとにウェル電源配線WVLおよびウェル接地配線WGLが設けられる。各ウェル電源配線WVLは、電源電位VDDを受け、コンタクトホールCHを介して図12の各N型ウェルNWに接続される。各ウェル接地配線WGLは、接地電位VSSを受け、コンタクトホールCHを介して図12の各P型ウェルPWに接続される。これにより、MOSトランジスタの活性層PAまたはNAからウェルNWまたはPWに電流が流出するのを防止することができる。各メモリセル電源配線MVLは、ヒューズ50を介して電源電位VDD(VDD=VDD)のラインに接続される。電源電位VDD用のパッドと電源電位VDD用のパッドは別々に設けられている。これは、スタンバイ電流不良の解析を容易にするためである。

30

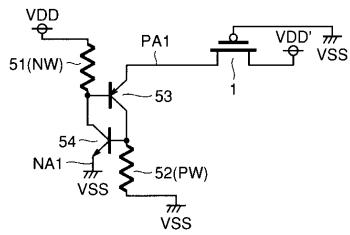

【0026】

しかし、このSRA Mは、ラッチアップに弱いという問題がある。すなわち、図15(a)(b)に示すように、N型ウェルNWおよびP型ウェルPWはそれぞれ抵抗素子51, 52を構成する。このSRA Mでは、図14で示したように、ウェル電源配線WVL, WVL間の距離およびウェル接地配線WGL, WGL間の距離が長いので、抵抗素子51, 52の各々の抵抗値は大きくなっている。また、PチャネルMOSトランジスタ41のP型活性層PA1とN型ウェルNWとP型ウェルPWとでPNPバイポーラトランジスタ53が構成され、N型ウェルNWとP型ウェルPWとNチャネルMOSトランジスタ43のN型活性層NA1とでNPNバイポーラトランジスタ54が構成される。

40

【0027】

何らかの原因でラッチアップトリガがN型ウェルNWまたはP型ウェルPWに発生してトランジスタ53, 54のベース-エミッタ間電圧が順バイアスになると、トランジスタ53のコレクタ電流は抵抗素子52(P型ウェルPW)に流入してトランジスタ54のベース-エミッタ間順バイアス電圧を増大させ、トランジスタ54のコレクタ電流もトランジスタ53のベース-エミッタ間順バイアス電圧を増大させる。これにより、電源電位VDD, VDDのラインから接地電位VSSのラインに大電流が流れ、SRA Mが破壊され

50

てしまう。なお、ヒューズ50の抵抗値は10以下と小さいので、トランジスタ53に流れる電流がヒューズ50によって制限されることはない。

#### 【0028】

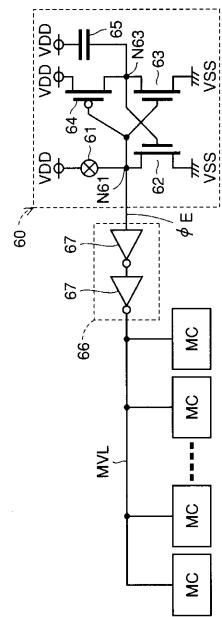

また、図16の方法では、各メモリセル行に対応してプログラム回路60および電源電位供給回路66が設けられる。プログラム回路60は、ヒューズ61、NチャネルMOSトランジスタ62、63、PチャネルMOSトランジスタ64およびキャパシタ65を含む。ヒューズ61およびNチャネルMOSトランジスタ62と、MOSトランジスタ64、63とは、それぞれ電源電位VDDのラインと接地電位VSSのラインとの間に直列接続される。MOSトランジスタ64、63のゲートは、ともにヒューズ61およびNチャネルMOSトランジスタ62間のノードN61に接続される。ノードN61に現われる信号は、このプログラム回路60の出力信号Eとなる。NチャネルMOSトランジスタ62のゲートは、NチャネルMOSトランジスタ63のドレイン（ノードN63）に接続される。キャパシタ65は、電源電位VDDのラインとノードN63との間に接続される。電源電位供給回路66は、プログラム回路60の出力ノードN61と対応のメモリセル電源配線MVLとの間に直列接続された偶数段（図では2段）のインバータ67を含む。

10

#### 【0029】

ヒューズ61がブローされていない場合は、電源電位VDDがヒューズ61を介してノードN61に与えられ、信号Eが「H」レベルになってメモリセル電源配線MVLに電源電位VDDが与えられる。ヒューズ61がブローされている場合は、電源投入時にキャパシタ65を介してノードN63に電源電位VDDが与えられ、MOSトランジスタ62、64が導通するとともにMOSトランジスタ63が非導通になり、信号Eが「L」レベルになってメモリセル電源配線MGLが接地される。したがって、（1）～（4）（7）（9）のショートがある場合でもスタンバイ電流が低減化される。このような方法は、たとえば特開平7-230699号公報に開示されている。

20

#### 【0030】

しかし、この方法では、ヒューズ61のブローが不十分である場合は、信号Eが「H」レベルになってメモリセル電源配線MVLに電源電位VDDが与えられるので、スタンバイ電流の低減化が図れないという問題がある。

#### 【0031】

また、不良な行のメモリセル電源配線MVLを接地電位VSSに固定するので、スタンバイ時に「H」レベルになる信号の信号配線と接地電位VSSにされたメモリセル電源配線MVLとがショートしている場合は、スタンバイ電流不良が発生してしまう。

30

#### 【0032】

また、図17の方法では、各メモリセル列に対応してヒューズ70が設けられる。ヒューズ70は、電源電位VDDのラインとPチャネルMOSトランジスタ31、32のソースとの間に介挿され、対応の列が不良である場合はブローされる。ヒューズ70がブローされると、（5）（6）（8）のショートがある場合でも電源電位VDDのラインからPチャネルMOSトランジスタ31、32およびビット線対BL、/BLを介して不良メモリセルのショート部分に流れる電流が遮断されるので、スタンバイ電流が低減化される。

#### 【0033】

40

しかし、この方法でも、ヒューズ70のブローが不十分である場合は、スタンバイ電流の低減化も不十分になるという問題があった。

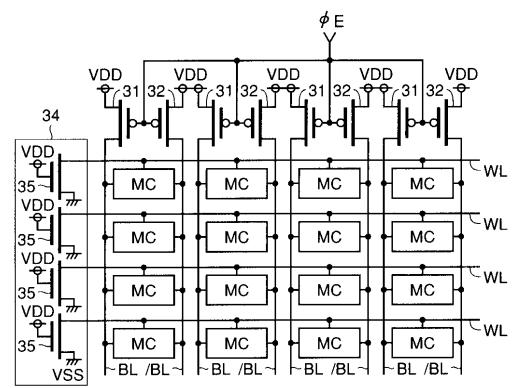

#### 【0034】

また、図18の方法では、PチャネルMOSトランジスタ31、32のゲートが接地電位VSSの代わりに信号Eを受ける。スタンバイ時は、信号Eが非活性化レベルの「H」レベルになってPチャネルMOSトランジスタ31、32が非導通になる。したがって、（5）（6）（8）のショートがある場合でも、電源電位VDDのラインからPチャネルMOSトランジスタ31、32およびビット線対BL、/BLを介してそのメモリセルMCのショート部分に流れる電流が遮断されるので、スタンバイ電流が低減化される。アクティブ時は、信号Eが活性化レベルの「L」レベルになってPチャネルMOSトラン

50

ジスタ31, 32が導通し、図10で示したS R A Mと同じ状態になる。

【0035】

しかし、この方法では、スタンバイ時は各ビット線対B L, / B Lがフローティング状態にされるので、スタンバイモードから読出モードに移行したときに各ビット線対B L, / B Lを「H」レベルに充電するための時間が必要となり、読出速度が遅延するという問題がある。

【0036】

また、図13～図18で示した方法では、(1)～(9)のショートのうちの一部のショートがあった場合にスタンバイ電流を低減化できても、他のショートがあった場合はスタンバイ電流を低減化できないという問題があった。たとえば図13の方法では、(1)～(4)(7)(9)のショートがあった場合はスタンバイ電流を低減化できるが、(6)のショートがある場合は「H」レベルのビット線B L, / B Lから「L」レベルのワード線W Lに電流がリークし、スタンバイ電流を低減化できない。また図17の方法では、(5)(6)(8)のショートがあった場合はスタンバイ電流を低減化できるが、(1)～(4)(7)(9)のショートがあった場合はメモリセル電源配線M V Lから接地電位V S Sのラインに電流がリークし、スタンバイ電流を低減化できない。

【0037】

それゆえに、この発明の主たる目的は、スタンバイ電流が小さく、ラッチアップに強いスタティック型半導体記憶装置を提供することである。

【0038】

【課題を解決するための手段】

この発明に係るスタティック型半導体記憶装置は、複数行複数列に配置された複数のメモリセルと、各行に対応して設けられたワード線と、各列に対応して設けられたビット線対とを備え、不良な行または列をスペア行または列で置換する冗長方式が採用されたスタティック型半導体記憶装置であって、各ワード線に対応して設けられて対応のワード線と基準電位のラインとの間に接続され、対応のワード線が選択されていない場合に導通して対応の各メモリセルを非活性状態にするための第1のスイッチング素子と、各行または列に対応して設けられ、その一方端が対応の行または列の各メモリセルの電源ノードに接続された電源配線と、各電源配線に対応して設けられて対応の電源配線の他方端と電源電位のラインとの間に接続され、第1のスイッチング素子の導通抵抗値よりも大きな予め定められた導通抵抗値を有する第2のスイッチング素子と、各行または列に対応して設けられ、対応の行または列が不良である場合にブローされるヒューズを含み、そのヒューズがブローされたことに応じて第2のスイッチング素子を非導通にするプログラム回路とを備えたものである。

【0039】

好ましくは、電源配線およびプログラム回路は各列に対応して設けられ、スタティック型半導体記憶装置は、さらに、各ビット線に対応して設けられ、その一方電極が対応のビット線に接続されたビット線負荷素子と、各列に対応して設けられて対応の列の各ビット線負荷素子の他方電極と電源電位のラインとの間に接続された第3のスイッチング素子とを備え、プログラム回路は、ヒューズがブローされたことに応じて第2のスイッチング素子とともに第3のスイッチング素子も非導通にする。

【0040】

また好ましくは、プログラム回路は、第1のノードと第1の電位のラインとの間に接続され、リセット信号が第1のレベルから第2のレベルに変化したことに応じて導通し、第1のノードの電位を第1の電位にリセットするための第4のスイッチング素子と、第1のノードと第2の電位のラインとの間にヒューズと直列接続され、リセット信号が第2のレベルから第1のレベルに変化したことに応じて導通し、ヒューズがブローされていない場合に第1のノードを第2の電位にするための第5のスイッチング素子と、リセット信号が第2のレベルから第1のレベルに変化してから予め定められた時間だけ経過したことに応じて第1のノードの電位をラッチし、ラッチした電位が第1の電位の場合に第2のスイッチ

10

20

30

40

50

ング素子を非導通にするためのラッチ回路とを含む。

【0041】

また好ましくは、さらに、第1の導電形式の半導体基板と、半導体基板の表面に形成された第2の導電形式の半導体埋込層と、半導体埋込層の表面に形成された第1の導電形式の複数の第1のウェルと、半導体埋込層の表面に複数の第1のウェルの間にそれぞれ形成された第2の導電形式の複数の第2のウェルとが設けられ、複数のメモリセルは、複数の第1のウェルおよび複数の第2のウェルの表面に形成されている。

【0042】

また好ましくは、第2のスイッチング素子は、予め定められた導通抵抗値を有するトランジスタを含む。

10

【0043】

また好ましくは、第2のスイッチング素子は、予め定められた導通抵抗値を有する抵抗素子と、電源配線の他方端と電源電位のラインとの間に抵抗素子と直列接続されたトランジスタとを含む。

【0044】

【発明の実施の形態】

[実施の形態1]

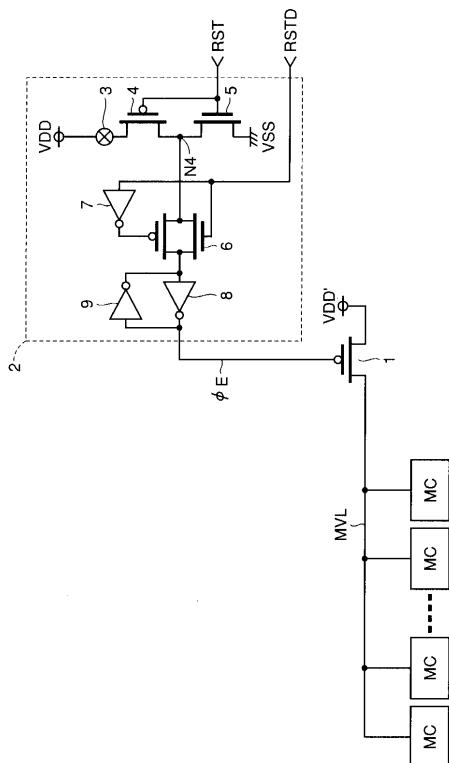

図1は、この発明の実施の形態1によるSRAMの要部を示す回路ブロック図であって、図13と対比される図である。

【0045】

20

図1において、このSRAMが図13のSRAMと異なる点は、ヒューズ50がPチャネルMOSトランジスタ1およびプログラム回路2で置換されている点である。PチャネルMOSトランジスタ1は、電源電位VDDのラインと対応のメモリセル電源配線MVLとの間に接続され、そのゲートはプログラム回路2の出力信号Eを受ける。PチャネルMOSトランジスタ1は、比較的大きな予め定められた導通抵抗値(10K程度以上)を有する。

【0046】

プログラム回路2は、ヒューズ3、PチャネルMOSトランジスタ4、NチャネルMOSトランジスタ5、トランസファゲート6およびインバータ7～9を含む。ヒューズ3、PチャネルMOSトランジスタ4およびNチャネルMOSトランジスタ5は、電源電位VDDのラインと接地電位VSSのラインとの間に直列接続される。PチャネルMOSトランジスタ4およびNチャネルMOSトランジスタ5のゲートは、リセット信号RSTを受ける。リセット信号RSTは、たとえば電源投入時に予め定められた時間T1だけ「H」レベルになる信号である。

30

【0047】

トランസファゲート6およびインバータ8は、MOSトランジスタ4,5の間のノードN4とPチャネルMOSトランジスタ1のゲートとの間に直列接続される。信号RSTDは、トランസファゲート6のNチャネルMOSトランジスタ側のゲートに直接入力されるとともに、インバータ7を介してPチャネルMOSトランジスタ側のゲートに入力される。信号RSTDは、リセット信号RSTを予め定められた時間T2だけ遅延させた信号である。インバータ9は、インバータ8に逆並列に接続される。トラン斯ファゲート6およびインバータ7～9は、ラッチ回路を構成する。

40

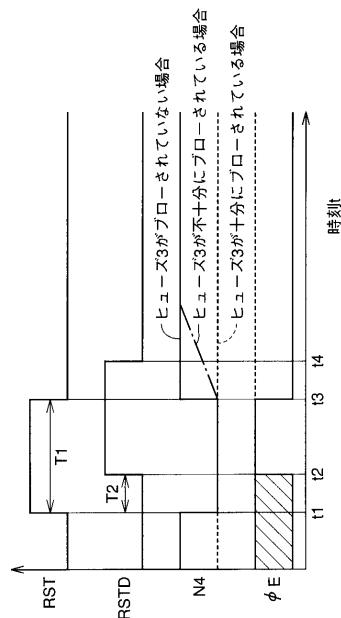

【0048】

図2は、図1に示したプログラム回路2の動作を示すタイムチャートである。図2において、初期状態では、信号RST, RSTDはともに「L」レベルになっており、PチャネルMOSトランジスタ4が導通するとともにNチャネルMOSトランジスタ5およびトラン斯ファゲート6は非導通になっている。ある時刻t1においてリセット信号RSTが「L」レベルから「H」レベルに立上げられると、PチャネルMOSトランジスタ4が非導通になるとともにNチャネルMOSトランジスタ5が導通し、ノードN4が「L」レベルにリセットされる。

50

## 【0049】

次いで時刻  $t_2$  において信号 R S T D が「L」レベルから「H」レベルに立上げられると、トランスマルチエクスパンダ 6 が導通して信号 E が「H」レベルにリセットされる。次に、時刻  $t_3$  においてリセット信号 R S T が「H」レベルから「L」レベルに立下げられると、P チャネルMOSトランジスタ 4 が導通するとともにN チャネルMOSトランジスタ 5 が非導通になる。

## 【0050】

このとき、ヒューズ 3 がブローされていない場合は、電源電位 V D D がヒューズ 3 および P チャネルMOSトランジスタ 4 を介してノード N 4 に与えられ、ノード N 4 が「L」レベルから「H」レベルに立上げられ、信号 E が「H」レベルから「L」レベルに立下げられる。また、ヒューズ 3 が十分にブローされている場合は、ノード N 4 は「L」レベルのまま変化せず、信号 E は「H」レベルのまま変化しない。また、ヒューズ 3 が不十分にブローされている場合は、不十分にブローされたヒューズ 3 が高い抵抗値を有するので、ノード N 4 の電位は徐々に上昇し、ノード N 4 の電位がインバータ 8 のしきい値電位を超えるのに長時間を要する。ノード N 4 の電位がインバータ 8 のしきい値電位を超えるまでは、信号 E は「H」レベルのまま変化しない。次いで時刻  $t_4$  において信号 R S T D が「H」レベルから「L」レベルに立下げられると、トランスマルチエクスパンダ 6 が非導通になり、信号 E のレベルがインバータ 8, 9 によってラッチされる。

## 【0051】

したがって、ヒューズ 3 がブローされていない場合は信号 E が「L」レベルになり、ヒューズ 3 が十分にブローされている場合およびヒューズ 3 が不十分にブローされている場合は信号 E が「H」レベルになる。

## 【0052】

次に、この S R A M の使用方法について説明する。まず、各メモリセル M C が正常か否かをテストし、不良なメモリセル M C を含むメモリセル行をスペアのメモリセル行と置換するとともに、不良なメモリセル M C を含むメモリセル行に対応するプログラム回路 2 のヒューズ 3 をブローする。

## 【0053】

ヒューズ 3 がブローされていないメモリセル行では、プログラム回路 2 の出力信号 E が「L」レベルになって P チャネルMOSトランジスタ 1 が導通する。これにより、電源電位 V D D のラインから P チャネルMOSトランジスタ 1 を介してその行のメモリセル電源配線 M V L に電源電位 V D D が与えられ、そのメモリセル行は正常に動作する。

## 【0054】

また、ヒューズ 3 が十分にブローされたメモリセル行およびヒューズ 3 が不十分にブローされたメモリセル行では、プログラム回路 2 の出力信号 E が「H」レベルになって P チャネルMOSトランジスタ 1 が非導通になる。これにより、その行のメモリセル電源配線 M V L はフローティング状態にされ、その行のメモリセル M C にショート部分がある場合でもそのショート部分に電流は流れないので、スタンバイ電流の低減化が図られる。

## 【0055】

また、不良なメモリセル行のメモリセル電源配線 M V L を図 16 の S R A M のように接地するのではなくフローティング状態にする。したがって、スタンバイ時に「H」レベルになる信号を伝達する信号線とメモリセル電源配線 M V L とがショートしている場合でも、その信号線とメモリセル電源配線 M V L の間には電流は流れないので、スタンバイ電流の低減化が図られる。

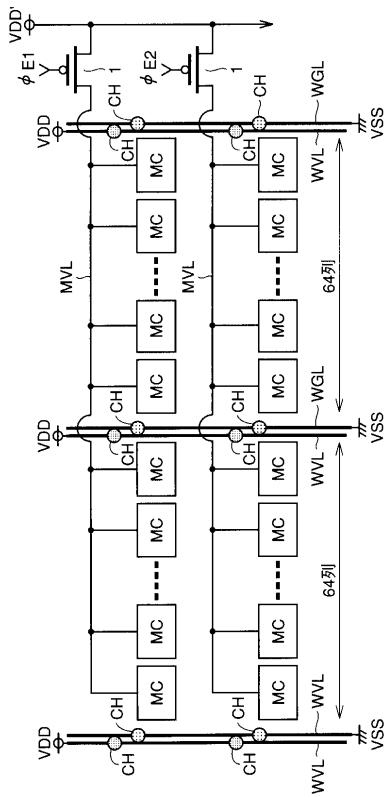

## 【0056】

また、図 3 は、この S R A M の構成をより詳細に示す図であって、図 14 と対比される図である。図 3 において、この S R A M が図 14 の S R A M と異なる点は、各ヒューズ 5 0 が P チャネルMOSトランジスタ 1 で置換され、各メモリセル行に対応して図 1 で示したプログラム回路 2 が設けられている点である。図 3 では、図面の簡単化のため 2 つのメモ

10

20

30

40

50

リセル行のみが示されている。2つのプログラム回路2(図示せず)の出力信号E1,E2は、それぞれ2つのメモリセル行のPチャネルMOSトランジスタ1,1のゲートに入力される。

#### 【0057】

このSRAMは、ラッチアップに強い構成になっている。すなわち、このSRAMでも、図15(b)で説明したように、ウェルNW,PWおよび活性層PA,NAによって抵抗素子51,52およびバイポーラトランジスタ53,54からなる放電回路が構成される。しかし、このSRAMでは、図4に示すように、電源電位VDDのラインとNPNバイポーラトランジスタ53のエミッタとの間に高い導通抵抗値を有するPチャネルMOSトランジスタ1が接続されているので、ラッチアップ現象が生じても電源電位VDDのラインから接地電位VSSのラインに流れる電流がPチャネルMOSトランジスタ1によって小さく制限される。たとえば、電源電位VDDを4Vとし、ヒューズ50の抵抗値を10とし、PチャネルMOSトランジスタ1の導通抵抗値を10Kとすると、ラッチアップ時に、図15(b)の回路では400mAの電流が流れるのに対し図4の回路では400μAの電流しか流れない。したがって、このSRAMは従来のSRAMよりもラッチアップに強い構成といえる。10

#### 【0058】

さらに、このSRAMは、(7)および(9)のショートを検出しやすい構成となっている。すなわち、図5に示すように、メモリセル電源配線MVLとワード線WLが低い抵抗値の異物11によってショートされている(7)の場合について考える(異物12については後述する)。PチャネルMOSトランジスタ1および行デコーダ34のNチャネルMOSトランジスタ35(図10参照)が導通している場合は、メモリセル電源配線MVLの電位は、電源電位VDDをPチャネルMOSトランジスタ1の導通抵抗値とNチャネルMOSトランジスタ35の導通抵抗値とで分圧した電位になる。ただし、異物11の抵抗値はNチャネルMOSトランジスタ35の導通抵抗値よりも十分に小さいものとする。20

#### 【0059】

したがって、PチャネルMOSトランジスタ1の導通抵抗値がNチャネルMOSトランジスタ35の導通抵抗値よりも十分に小さい場合は、メモリセル電源配線MVLの電位はほぼ電源電位VDDとなり、メモリセルMCの動作不良は生じない。このため、テストではこのメモリセル行は正常と判断され、スペアメモリセル行と置換されず、PチャネルMOSトランジスタ1は導通状態にされる。しかし、電源電位VDDのラインからPチャネルMOSトランジスタ1、メモリセル電源配線MVL、異物11、ワード線WLおよびNチャネルMOSトランジスタ35を介して接地電位VSSのラインに電流がリークするので、スタンバイ電流不良が生じる。30

#### 【0060】

しかし、このSRAMではPチャネルMOSトランジスタ1の導通抵抗値をNチャネルMOSトランジスタ35の導通抵抗値よりも大きくするので、メモリセル電源配線MVLの電位は電源電位VDDの1/2以下になり、メモリセルMCは正常に動作しない。このため、テストではこのメモリセル行は不良であると判断され、スペアメモリセル行と置換され、PチャネルMOSトランジスタ1は非導通にされる。したがって、異物11には電流は流れず、スタンバイ電流が低減化される。40

#### 【0061】

次に、メモリセル電源配線MVLとメモリセル接地配線MGLとが低い抵抗値の異物12によってショートされている(9)の場合について考える。PチャネルMOSトランジスタ1が導通している場合は、メモリセル電源配線MVLの電位は、電源電位VDDをPチャネルMOSトランジスタ1の導通抵抗値と異物12の抵抗値とで分圧した電位になる。

#### 【0062】

したがって、PチャネルMOSトランジスタ1の導通抵抗値が異物12の抵抗値よりも十分に小さい場合は、メモリセル電源配線MVLの電位はほぼ電源電位VDDとなり、メ50

モリセルMCの動作不良は生じない。このため、テストではこのメモリセル行は正常と判断され、スペアメモリセル行と置換されず、PチャネルMOSトランジスタ1は導通状態にされる。したがって、電源電位VDDのラインからPチャネルMOSトランジスタ1、メモリセル電源配線MVL、異物12およびメモリセル接地配線MGLを介して接地電位VSSのラインに電流がリークするので、スタンバイ電流不良が生じる。

#### 【0063】

しかし、このSRAMでは、PチャネルMOSトランジスタ1の導通抵抗値を比較的高い値にするので、異物12の抵抗値がPチャネルMOSトランジスタ1の導通抵抗値よりも小さい場合は、メモリセル電源配線MVLの電位は電源電位VDDの1/2以下になり、メモリセルMCは正常に動作しない。このため、テストではこのメモリセル行は不良であると判断され、スペアメモリセル行と置換され、PチャネルMOSトランジスタ1は非導通にされる。したがって、異物12には電流は流れず、スタンバイ電流が低減化される。

10

#### 【0064】

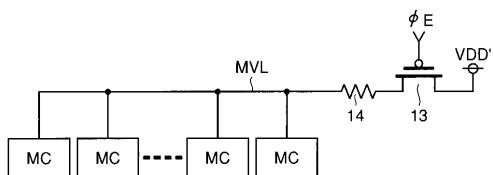

なお、この実施の形態1では、電源電位VDDのラインとメモリセル電源配線MVLとの間に高い導通抵抗値を有するPチャネルMOSトランジスタ1を接続したが、図6に示すように、電源電位VDDのラインとメモリセル電源配線MVLとの間に低い導通抵抗値を有するPチャネルMOSトランジスタ13と高い抵抗値(10K程度以上)を有する抵抗素子14とを直列接続しても同じ効果が得られる。この場合は、電源電位VDDのラインとメモリセル電源配線MVLとの間の抵抗値を容易かつ正確に設定することができる。

20

#### 【0065】

##### [実施の形態2]

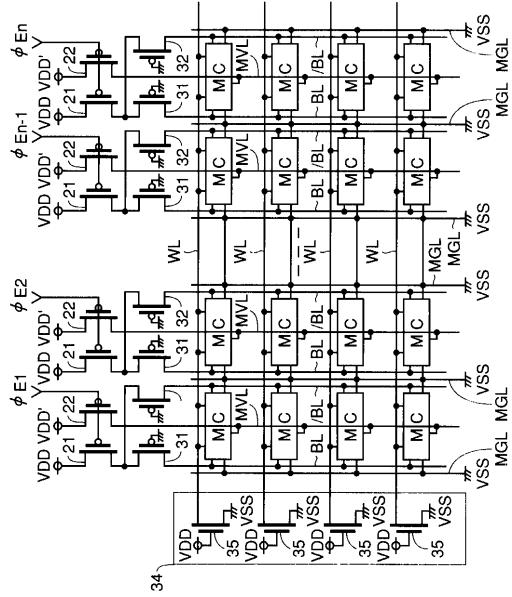

図7は、この発明の実施の形態2によるSRAMの要部を示す回路ブロック図であって、図10と対比される図である。

#### 【0066】

図7において、このSRAMが図10のSRAMと異なる点は、メモリセルMCが横長型であり、各ビット線対BL, /BLに対してPチャネルMOSトランジスタ21, 22が追加されており、メモリセル電源配線MVLが各列に対応して設けられてビット線対BL, /BLと同じ方向に延在し、各メモリセル列に対応して図1のプログラム回路2(図示せず)が設けられている点である。

30

#### 【0067】

PチャネルMOSトランジスタ21は、電源電位VDDのラインとPチャネルMOSトランジスタ31, 32のソースとの間に接続される。PチャネルMOSトランジスタ22は、図1のPチャネルMOSトランジスタ1と同様に比較的高い抵抗値(10K程度以上)を有し、電源電位VDDのラインとメモリセル電源配線MVLとの間に接続される。それぞれn列(ただし、nは自然数である)に対応して設けられたn個のプログラム回路2の出力信号E1 ~ Enの各々は、対応の列のPチャネルMOSトランジスタ21, 22のゲートに入力される。

#### 【0068】

40

横長型メモリセルMCは、図8(a)に示すように、図11(a)(b)で示した縦長型メモリセルMCと同様に、負荷トランジスタ(PチャネルMOSトランジスタ)41, 42、ドライバトランジスタ(NチャネルMOSトランジスタ)43, 44およびアクセストランジスタ(NチャネルMOSトランジスタ)45, 46を含む。横長型メモリセルMCと縦長型メモリセルMCでは、トランジスタ41 ~ 46などのレイアウトが異なる。

#### 【0069】

すなわち、横長型メモリセルMCは、図8(b)に示すように、1つのN型ウェルNWとその両側に配置されたP型ウェルPW, PWの表面に形成される。まず、N型ウェルNWから一方のP型ウェルPWにわたって図中X方向に延在するゲート電極GE1と、N型ウェルNWから他方のP型ウェルPWにわたって図中X方向に延在するゲート電極GE2と

50

、一方のP型ウェルPW上に図中X方向に延在するゲート電極GE3と、他方のP型ウェルPW上に図中X方向に延在するゲート電極GE4とがポリシリコン層によって形成される。

【0070】

次いで、一方のP型ウェルPWにおいてゲート電極GE1, GE3を横切るようにしてN型活性層NA1が形成され、他方のP型ウェルPWにおいてゲート電極GE2, GE4を横切るようにしてN型活性層NA2が形成され、N型ウェルNWにおいてそれぞれゲート電極GE1, GE2を横切るようにしてP型活性層PA1, PA2が形成される。

【0071】

ゲート電極GE1とP型活性層PA1、ゲート電極GE2とP型活性層PA2は、それぞれPチャネルMOSトランジスタ41, 42を構成する。ゲート電極GE1とN型活性層NA1、ゲート電極GE3とN型活性層NA1は、それぞれNチャネルMOSトランジスタ43, 45を構成する。ゲート電極GE2とN型活性層NA2、ゲート電極GE4とN型活性層NA2は、それぞれNチャネルMOSトランジスタ44, 46を構成する。

10

【0072】

次に、N型活性層NA1の中央部、P型活性層PA1の一方端部およびゲート電極GE2の一方端部にわたってローカル配線LL1が形成されるとともに、N型活性層NA2の中央部、P型活性層PA1の一方端部およびゲート電極GE1の一方端部にわたってローカル配線LL2が形成される。図8(b)において、ローカル配線LL1と活性層NA1, PA1とが重なっている部分は導通している。ローカル配線LL2と活性層NA2, PA2とが重なっている部分は導通している。ゲート電極GE2とローカル配線LL1、ゲート電極GE1とローカル配線LL2は、それぞれコンタクトホールCH, CHを介して互いに接続される。

20

【0073】

次に図8(c)に示すように、図中X方向に延在する複数のメタル配線MLが第1アルミ配線層によって形成され、さらにその上方に、図中Y方向に延在するメモリセル接地配線MGL、ピット線BL、メモリセル電源配線MVL、ピット線/BLおよびメモリセル接地線MGLが第2アルミ配線層によって形成される。複数のメタル配線MLのうちメモリセルMCの中央部を横切るメタル配線は、ワード線WLとなる。

30

【0074】

P型活性層PA1の一方端部(PチャネルMOSトランジスタ41のソース)は、コンタクトホールCH、メタル配線MLおよびビアホールVHを介してメモリセル電源配線MVLに接続される。P型活性層PA2の一方端部(PチャネルMOSトランジスタ42のソース)は、コンタクトホールCH、メタル配線MLおよびビアホールVHを介してメモリセル電源配線MVLに接続される。

【0075】

N型活性層NA1の一方端部(NチャネルMOSトランジスタ43のソース)は、コンタクトホールCH、メタル配線MLおよびビアホールVHを介してメモリセル接地配線MGLに接続される。N型活性層NA2の一方端部(NチャネルMOSトランジスタ44のソース)は、コンタクトホールCH、メタル配線MLおよびビアホールVHを介してメモリセル接地配線MGLに接続される。

40

【0076】

N型活性層NA1の他方端部(NチャネルMOSトランジスタ45のドレイン)は、コンタクトホールCH、メタル配線MLおよびビアホールVHを介してピット線BLに接続される。N型活性層NA2の他方端部(NチャネルMOSトランジスタ46のドレイン)は、コンタクトホールCH、メタル配線MLおよびビアホールVHを介してピット線/BLに接続される。ゲート電極GE3, GE4は、それぞれコンタクトホールCHを介してワード線WLに接続される。

【0077】

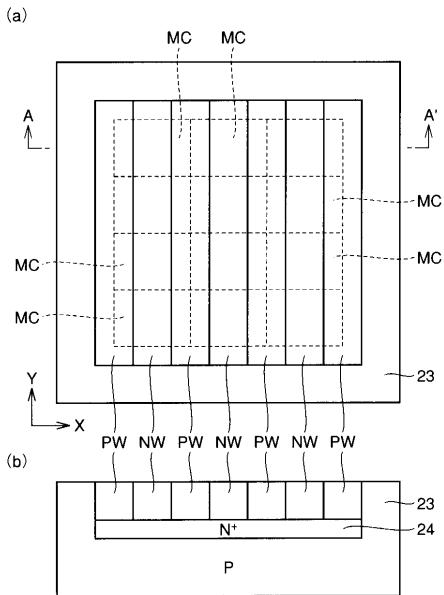

メモリセルMCの基板は、図9に示すように、トリプルウェル構造にされている。すなわ

50

ち、P型シリコン基板23の表面にN<sup>+</sup>型埋込層24が形成され、さらにその表面に複数(図では4つ)のP型ウェルPWが形成され、4つのP型ウェルPWの間にそれぞれ3つのN型ウェルNWが形成される。各メモリセルMCは、N型ウェルNWとその両側に隣接するP型ウェルPWの表面に形成される。P型ウェルPWは、図中X方向に隣接する2つのメモリセルMCで共用される。図9では、4行3列に配置された12個のメモリセルMCが示されている。

#### 【0078】

次に、このSRAMの使用法について説明する。まず、各メモリセルMCが正常か否かをテストし、不良なメモリセルMCを含むメモリセル列をスペアのメモリセル列と置換するとともに、不良なメモリセルMCを含むメモリセル列に対応するプログラム回路2のヒューズ3をブローする。10

#### 【0079】

ヒューズ3がブローされていないメモリセル列では、プログラム回路2の出力信号(たとえばE1～En-1)が「L」レベルになってPチャネルMOSトランジスタ21,22が導通する。これにより、電源電位VDDのラインからPチャネルMOSトランジスタ21,31,32を介してビット線BL, /BLに電源電位VDDが与えられるとともに、電源電位VDDのラインからPチャネルMOSトランジスタ22を介してメモリセル電源配線MVLに電源電位VDDが与えられ、各メモリセル列が正常に動作する。

#### 【0080】

ヒューズ3がブローされたメモリセル列では、プログラム回路2の出力信号(この場合はEn)が「H」レベルになってPチャネルMOSトランジスタ21,22が非導通になる。これにより、その列のビット線BL, /BLおよびメモリセル電源配線MVLはフローティング状態にされ、その列のメモリセルMCに(1)～(9)のショートが発生している場合でもショート部分に電流は流れない。したがって、このSRAMでは、1つのヒューズ3をブローするだけで、(1)～(9)のショートによって発生するリーク電流をなくすことができ、スタンバイ電流の低減化を図ることができる。20

#### 【0081】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内のすべての変更が含まれることが意図される。30

#### 【0082】

##### 【発明の効果】

以上のように、この発明に係るスタティック型半導体記憶装置では、各ワード線に対応して設けられて対応のワード線と基準電位のラインとの間に接続され、対応のワード線が選択されていない場合に導通して対応の各メモリセルを非活性状態にするための第1のスイッチング素子と、各行または列に対応して設けられ、その一方端が対応の行または列の各メモリセルの電源ノードに接続された電源配線と、各電源配線に対応して設けられて対応の電源配線の他方端と電源電位のラインとの間に接続され、第1のスイッチング素子の導通抵抗値よりも大きな予め定められた導通抵抗値を有する第2のスイッチング素子と、各行または列に対応して設けられ、対応の行または列が不良である場合にブローされるヒューズを含み、そのヒューズがブローされたことに応じて第2のスイッチング素子を非導通にするプログラム回路とが設けられる。したがって、不良な行または列に対応するプログラム回路のヒューズを切断することにより、第2のスイッチング素子を非導通にしてその行または列の電源配線をフローティング状態にすることができる。よって、メモリセルのショート部分に電流がリークしたり、電源配線と信号線の間に電流が流れるのを防止することができ、スタンバイ電流の低減化を図ることができる。また、第2のスイッチング素子が第1のスイッチング素子の導通抵抗値よりも大きな所定の導通抵抗値を有するので、電源配線がワード線などとショートしていることを容易に検出することができ、その電源配線をフローティング状態にすることによりスタンバイ電流の低減化を図ることができる40

。また、第2のスイッチング素子が比較的大きな所定の導通抵抗値を有しているので、ラッチャップ現象が発生した場合でもリーク電流を抑制することができる。

【0083】

好ましくは、電源配線およびプログラム回路は各列に対応して設けられ、スタティック型半導体記憶装置は、さらに、各ビット線に対応して設けられ、その一方電極が対応のビット線に接続されたビット線負荷素子と、各列に対応して設けられて対応の列の各ビット線負荷素子の他方電極と電源電位のラインとの間に接続された第3のスイッチング素子とを備え、プログラム回路は、ヒューズがブローされたことに応じて第2のスイッチング素子とともに第3のスイッチング素子も非導通にする。この場合は、不良な列に対応する1つのヒューズを切断することにより、その列の電源配線およびビット線対から流出する電流を遮断することができる。

【0084】

また好ましくは、プログラム回路は、第1のノードと第1の電位のラインとの間に接続され、リセット信号が第1のレベルから第2のレベルに変化したことに応じて導通し、第1のノードの電位を第1の電位にリセットするための第4のスイッチング素子と、第1のノードと第2の電位のラインとの間にヒューズと直列接続され、リセット信号が第2のレベルから第1のレベルに変化したことに応じて導通し、ヒューズがブローされていない場合に第1のノードを第2の電位にするための第5のスイッチング素子と、リセット信号が第2のレベルから第1のレベルに変化してから予め定められた時間だけ経過したことに応じて第1のノードの電位をラッチし、ラッチした電位が第1の電位の場合に第2のスイッチング素子を非導通にするためのラッチャ回路とを含む。この場合は、ヒューズが不十分にブローされている場合でも、ヒューズが十分にブローされている場合と同じ結果を得ることができる。

【0085】

また好ましくは、さらに、第1の導電形式の半導体基板と、半導体基板の表面に形成された第2の導電形式の半導体埋込層と、半導体埋込層の表面に形成された第1の導電形式の複数の第1のウェルと、半導体埋込層の表面に複数の第1のウェルの間にそれぞれ形成された第2の導電形式の複数の第2のウェルとが設けられ、複数のメモリセルは、複数の第1のウェルおよび複数の第2のウェルの表面に形成される。この場合は、半導体基板で発生した電子 - ホール対が半導体埋込層に吸収されるので、ソフトエラーの発生を抑制することができる。

【0086】

また好ましくは、第2のスイッチング素子は、予め定められた導通抵抗値を有するトランジスタを含む。この場合は、第2のスイッチング素子を容易に構成できる。

【0087】

また好ましくは、第2のスイッチング素子は、予め定められた導通抵抗値を有する抵抗素子と、電源配線の他方端と電源電位のラインとの間に抵抗素子と直列接続されたトランジスタとを含む。この場合は、第2のスイッチング素子の導通抵抗値を容易かつ正確に設定できる。

【図面の簡単な説明】

【図1】 この発明の実施の形態1によるS R A Mの要部を示す回路ブロック図である。

【図2】 図1に示したプログラム回路の動作を示すタイムチャートである。

【図3】 図1で説明したS R A Mをより詳細に示す回路ブロック図である。

【図4】 図3に示したS R A Mの効果を説明するための回路図である。

【図5】 図1に示したS R A Mの効果を説明するための回路ブロック図である。

【図6】 実施の形態1の変更例を示す回路ブロック図である。

【図7】 この発明の実施の形態2によるS R A Mの要部を示す回路ブロック図である。

【図8】 図7に示したメモリセルの構成およびレイアウトを示す図である。

【図9】 図8に示したメモリセルの基板を示す図である。

【図10】 従来のS R A Mの全体構成を示す回路ブロック図である。

10

20

30

40

50

【図11】 図10に示したメモリセルの構成およびレイアウトを示す図である。

【図12】 図11に示したメモリセルの基板を示す図である。

【図13】 従来の他のS R A Mの要部を示す回路ブロック図である。

【図14】 図13に示したS R A Mをより詳細に示す回路ブロック図である。

【図15】 図14に示したS R A Mの問題点を説明するための図である。

【図16】 従来のさらに他のS R A Mの要部を示す回路ブロック図である。

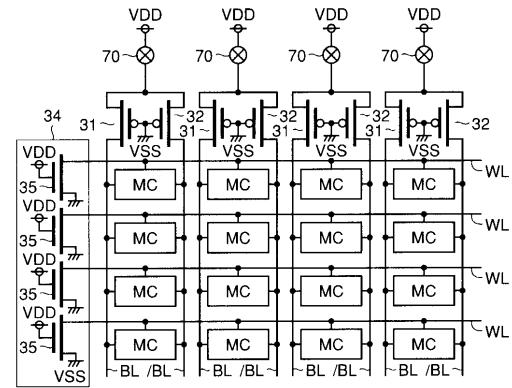

【図17】 従来のさらに他のS R A Mの要部を示す回路ブロック図である。

【図18】 従来のさらに他のS R A Mの要部を示す回路ブロック図である。

【符号の説明】

1, 4, 13, 21, 22, 41, 42, 64 P チャネルM O Sトランジスタ、2, 6 10

0 プログラム回路、3, 50, 61, 70 ヒューズ、5, 35, 43~46, 62, 63 N チャネルM O Sトランジスタ、6 トランスマジックゲート、7~9, 67 インバータ、11, 12 異物、14, 51, 52 抵抗素子、23, 47 P型シリコン基板、24, 48 N<sup>+</sup>型埋込層、31, 32 ピット線負荷、33 列選択ゲート、34 行デコーダ、36 制御回路、37 列デコーダ、38 書込回路、39 読出回路、53 P N Pバイポーラトランジスタ、54 N P Nバイポーラトランジスタ、66 電源電位供給回路、P W P型ウェル、N W N型ウェル、P A P型活性層、N A N型活性層、G E ゲート電極、M C メモリセル、W L ワード線、B L, / B L ピット線対、C S L 列選択線、I O, / I O データ入出力線対、M V L メモリセル電源配線、M G L メモリセル接地配線、W V L ウェル電源配線、W G L ウェル接地配線、C H 20 コンタクトホール、V H ビアホール、L L ローカル配線、M L メタル配線。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/822 (2006.01) H 01 L 27/10 4 8 1

H 01 L 27/04 (2006.01)

H 01 L 27/10 (2006.01)

(74)代理人 100111246

弁理士 荒川 伸夫

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 大林 茂樹

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 正山 旭

(56)参考文献 特開平09-265792 (JP, A)

特開平02-076244 (JP, A)

特開2000-021191 (JP, A)

特開平08-274266 (JP, A)

特開平11-261021 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8244

G11C 11/413

G11C 29/04

H01L 21/82

H01L 21/822

H01L 27/04

H01L 27/10

H01L 27/11