(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4549958号

(P4549958)

(45) 発行日 平成22年9月22日(2010.9.22)

(24) 登録日 平成22年7月16日(2010.7.16)

(51) Int.Cl.

F 1

H03L 7/081 (2006.01)

H03L 7/093 (2006.01)H03L 7/08

H03L 7/08J

E

請求項の数 14 (全 27 頁)

(21) 出願番号 特願2005-264131 (P2005-264131)

(22) 出願日 平成17年9月12日 (2005.9.12)

(65) 公開番号 特開2006-254401 (P2006-254401A)

(43) 公開日 平成18年9月21日 (2006.9.21)

審査請求日 平成20年2月21日 (2008.2.21)

(31) 優先権主張番号 特願2005-33625 (P2005-33625)

(32) 優先日 平成17年2月9日 (2005.2.9)

(33) 優先権主張国 日本国 (JP)

前置審査

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 英二

(74) 代理人 100115059

弁理士 今江 克実

(74) 代理人 100117581

弁理士 二宮 克也

最終頁に続く

(54) 【発明の名称】遅延ロックループ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックループ回路において、

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベ

10

20

ルとなる信号を生成するものであり、

前記チャージポンプ回路は、

前記第1の動作に係る第1の電流を供給する第1の電流源と、

前記第2の動作に係る第2の電流を供給する第2の電流源と、

前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチとを有するものあり、

前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従つて前記遅延量を減少し、他方に従つて前記遅延量を増大する制御を行うものである

10

### 【請求項2】

請求項1に記載の遅延ロックドループ回路において、

前記第1の電流の大きさは、前記第2の電流の大きさの2倍に相当することを特徴とする遅延ロックドループ回路。

### 【請求項3】

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従つて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

30

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成するものあり、

前記チャージポンプ回路は、

前記第1の動作に係る第1及び第4の電流をそれぞれ供給する第1及び第4の電流源と、

前記第2の動作に係る第2及び第3の電流をそれぞれ供給する第2及び第3の電流源と、

40

前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチと、

前記第1の信号が前記第1の論理レベルのとき、前記第3の電流を遮断し、前記第2の論理レベルのとき、前記第3の電流を通電する第3のスイッチと、

前記第2の信号が前記第1の論理レベルのとき、前記第4の電流を遮断し、前記第2の論理レベルのとき、前記第4の電流を通電する第4のスイッチとを有するものあり、

前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従つて前記遅延量を減少し、他方に従つて前記遅延量を増大する制御を行うものである

50

ことを特徴とする遅延ロックドループ回路。

**【請求項 4】**

請求項 3 に記載の遅延ロックドループ回路において、

前記第 2 から第 4 の電流の大きさはいずれも等しく、かつ、前記第 1 の電流の大きさは

、前記第 2 から第 4 の電流の大きさの 3 倍に相当する

ことを特徴とする遅延ロックドループ回路。

**【請求項 5】**

基準クロック信号の第 1 の論理レベルから第 2 の論理レベルへの第 1 の変化から遅延して、第 1 の論理レベルから第 2 の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

10

前記基準クロック信号の第 1 の変化、前記基準クロック信号の前記第 2 の論理レベルから前記第 1 の論理レベルへの第 2 の変化、及び前記遅延クロック信号の変化に応じて変化する第 1 及び第 2 の信号を生成する信号生成回路と、

前記第 1 及び第 2 の信号に従って、前記基準クロック信号の第 1 の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第 1 の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第 2 の変化までの間、プッシュ動作及びプル動作の他方である第 2 の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第 1 の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回路において、

20

前記信号生成回路は、前記第 1 の信号として、前記基準クロック信号の第 1 の変化から前記遅延クロック信号の変化までの間、第 1 の論理レベルとなり、これ以外のとき、第 2 の論理レベルとなる信号を生成し、前記第 2 の信号として、前記基準クロックの第 1 の変化から第 2 の変化までの間、第 1 の論理レベルとなり、これ以外のとき、第 2 の論理レベルとなる信号を生成するものであり、

前記チャージポンプ回路は、

前記第 1 の動作に係る第 1 、第 4 及び第 5 の電流をそれぞれ供給する第 1 、第 4 及び第 5 の電流源と、

30

前記第 2 の動作に係る第 2 及び第 3 の電流をそれぞれ供給する第 2 及び第 3 の電流源と、

前記第 1 の信号が前記第 1 の論理レベルのとき、前記第 1 の電流を通電し、前記第 2 の論理レベルのとき、前記第 1 の電流を遮断する第 1 のスイッチと、

前記第 2 の信号が前記第 1 の論理レベルのとき、前記第 2 の電流を通電し、前記第 2 の論理レベルのとき、前記第 2 の電流を遮断する第 2 のスイッチと、

前記第 1 の信号が前記第 1 の論理レベルのとき、前記第 3 の電流を遮断し、前記第 2 の論理レベルのとき、前記第 3 の電流を通電する第 3 のスイッチと、

前記第 2 の信号が前記第 1 の論理レベルのとき、前記第 4 の電流を遮断し、前記第 2 の論理レベルのとき、前記第 4 の電流を通電する第 4 のスイッチとを有するものであり、

前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従つて前記遅延量を減少し、他方に従つて前記遅延量を増大する制御を行うものである

40

ことを特徴とする遅延ロックドループ回路。

**【請求項 6】**

請求項 5 に記載の遅延ロックドループ回路において、

前記第 1 の電流の大きさと前記第 3 の電流の大きさとは等しく、前記第 2 、第 4 及び第 5 の電流の大きさはいずれも等しく、かつ、前記第 1 及び第 3 の電流の大きさは、前記第 2 、第 4 及び第 5 の電流の大きさの 2 倍に相当する

ことを特徴とする遅延ロックドループ回路。

**【請求項 7】**

基準クロック信号の第 1 の論理レベルから第 2 の論理レベルへの第 1 の変化から遅延し

50

て、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

10

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドロープ回路において、

前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の電圧となり、これ以外のとき、第2の電圧となる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、前記第2の電圧となり、これ以外のとき、前記第1の電圧となる信号を生成するものであり、

前記チャージポンプ回路は、

前記第1の信号を受ける第1の抵抗と、

20

前記第2の信号を受ける第2の抵抗と、

一端が前記第1及び第2の抵抗の接続箇所に接続され、他端に第3の電圧が与えられた第3の抵抗とを有するものであり、

前記ループフィルタは、

容量と、

負帰還部分に前記容量が接続され、反転入力端が前記チャージポンプ回路における第1から第3の抵抗の接続箇所に接続され、非反転入力端に第4の電圧が与えられた演算増幅器とを有するものあり、

前記遅延素子は、前記ループフィルタにおける演算増幅器の出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行うものである

30

ことを特徴とする遅延ロックドロープ回路。

#### 【請求項8】

請求項7に記載の遅延ロックドロープ回路において、

前記第2の電圧と前記第3の電圧とは等しく、

前記第4の電圧は、前記第1の電圧と前記第2の電圧との中間に相当する電圧であり、

前記第2の抵抗の抵抗値と前記第3の抵抗の抵抗値とは等しく、

前記第1の抵抗の抵抗値は、前記第2及び第3の抵抗の抵抗値の半分に相当することを特徴とする遅延ロックドロープ回路。

#### 【請求項9】

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

40

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

50

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1

の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回

路において、

前記遅延素子は、

直列に接続され、ゲートに前記基準クロック信号を受ける互いに逆極性の第1及び第2

のトランジスタ、及びこれらトランジスタの間に挿入されて接続され、ゲートに前記ルー

プフィルタの出力を受ける第3のトランジスタを有し、前記第1のトランジスタと前記第

3のトランジスタとの接続点の電圧を出力信号とする第1の回路と、

前記第1の回路の出力信号の波形を整形する第2の回路とを備えたものであり、

前記第1の回路は、前記第3のトランジスタに並列に接続された電流源を有する

ことを特徴とする遅延ロックドループ回路。

#### 【請求項10】

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延し

て、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延

素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルか

ら前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補

的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延ク

ロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作

を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、

プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1

の変化から前記遅延クロック信号の変化までの遅延量を制御する、遅延ロックドループ回

路において、

前記遅延素子は、

直列に接続され、ゲートに前記基準クロック信号を受ける互いに逆極性の第1及び第2

のトランジスタ、及びこれらトランジスタの間に挿入されて接続され、ゲートに前記ルー

プフィルタの出力を受ける第3のトランジスタを有し、前記第1のトランジスタと前記第

3のトランジスタとの接続点の電圧を出力信号とする第1の回路と、

前記第1の回路の出力信号の波形を整形する第2の回路とを備えたものであり、

前記第2の回路は、

前記第1の回路の出力信号を受けるインバータと、

前記インバータの入力及び出力をそれぞれドレイン及びゲートに受け、ソースに所定の

電圧が与えられたトランジスタを有する

ことを特徴とする遅延ロックドループ回路。

#### 【請求項11】

共通の基準クロック信号が与えられる第1及び第2の遅延ロックドループ回路と、

前記第1及び第2の遅延ロックドループ回路の出力クロック信号から、前記共通の基準

クロック信号の立ち上がりから遅延して立ち上がり及び立ち下がりのいずれか一方の変化

が生じる一方、前記共通の基準クロック信号の立ち下がりから遅延して立ち上がり及び立

ち下がりの他方の変化が生じる遅延クロック信号を生成するクロック生成回路とを備え、

前記第1及び第2の遅延ロックドループ回路は、それぞれ、

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延し

て、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延

素子と、

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルか

ら前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補

10

20

30

40

50

的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御することを特徴とする遅延ロックドループ回路。

#### 【請求項12】

10

請求項11に記載の遅延ロックドループ回路において、

前記第1の遅延ロックドループ回路は、前記共通の基準クロック信号の立ち上がりから、前記共通の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものであり、

前記第2の遅延ロックドループ回路は、前記共通の基準クロック信号の立ち下がりから、前記共通の基準クロック信号のオフデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものであることを特徴とする遅延ロックドループ回路。

#### 【請求項13】

20

第1の基準クロック信号が与えられる第1の遅延ロックドループ回路と、

前記第1の基準クロック信号とは逆位相の第2の基準クロック信号が与えられる第2の遅延ロックドループ回路と、

前記第1及び第2の遅延ロックドループ回路の出力クロック信号から、前記第1の基準クロック信号の立ち上がりから遅延して立ち上がり及び立ち下がりのいずれか一方の変化が生じる一方、前記第1の基準クロック信号の立ち下がりから遅延して立ち上がり及び立ち下がりの他方の変化が生じる遅延クロック信号を生成するクロック生成回路とを備え、

前記第1及び第2の遅延ロックドループ回路は、それぞれ、

基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、

30

前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、

前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、

前記チャージポンプ回路の出力を受けるループフィルタとを備え、

前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御することを特徴とする遅延ロックドループ回路。

40

#### 【請求項14】

請求項13に記載の遅延ロックドループ回路において、

前記第1の遅延ロックドループ回路は、前記第1の基準クロック信号の立ち上がりから、前記第1の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものであり、

前記第2の遅延ロックドループ回路は、前記第2の基準クロック信号の立ち上がりから、前記第2の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものであることを特徴とする遅延ロックドループ回路。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、遅延ロックドループ回路に関する。

**【背景技術】****【0002】**

遅延ロックドループ回路(DLL)は、メモリアクセスなどの際、データ信号に対してクロックの最適なストローブポイントを検出するために用いられる。例えば、遅延ロックドループ回路は、シングルデータレート(SDR)では基準クロック信号の1/2位相を検出し、ダブルデータレートDDRでは基準クロック信号の1/4位相や3/4位相を検出する。また、一般に、メモリなどでは、ワードラインやセンスアンプなどのタイミングシーケンス制御のために遅延ロックドループ回路が用いられる。10

**【0003】**

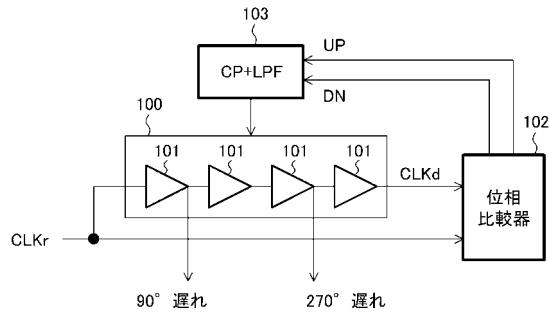

図16は、従来の遅延ロックドループ回路の構成を示す。遅延回路100は、直列に接続された4個の遅延素子101を有し、基準クロック信号CLKrを受け、一周期遅延した遅延クロック信号CLKdを出力する。位相比較器102は、基準クロック信号CLKrと遅延クロック信号CLKdとの位相を比較し、この比較結果に応じて信号UP及びDNを出力する。チャージポンプ回路(ループフィルタを含む)103は、信号UP及びDNに基づいて遅延回路100を制御する。上記構成の遅延ロックドループ回路は、遅延クロック信号CLKdの位相が基準クロック信号CLKrの位相から一周期遅延したときに安定し、このとき、遅延クロック信号CLKdの遅延がロックされる(例えば、特許文献1参照)。20

**【0004】**

上記構成の遅延ロックドループ回路では、遅延回路100における初段の遅延素子101から1/4位相(90°)遅れのクロック信号が出力される。また、3段目の遅延素子101から3/4位相(270°)遅れのクロック信号が出力される。

**【特許文献1】特開2000-82954号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

従来の遅延ロックドループ回路では、基準クロック信号CLKrと遅延素子101のドライブ能力や負荷容量が異なるため、1/4位相及び3/4位相の精度を上げにくいという問題がある。30

**【0006】**

また、従来の遅延ロックドループ回路では、遅延クロック信号は、基準クロック信号のデューティ比にかかわらず、基準クロック信号から1/4位相又は3/4位相遅れのクロック信号として生成される。このため、例えば、基準クロック信号のデューティ比が25%よりも小さい場合、基準クロック信号のオンデューティ中に1/4位相遅れのクロック信号の立ち上がり又は立ち上がりが発生しないため、DDRでは使用することができなくなる。このように、従来の遅延ロックドループ回路は、デューティ比が50%ではない基準クロック信号には対応できないおそれがある。40

**【0007】**

また、従来の遅延ロックドループ回路では、原理的に、遅延クロック信号CLKdの遅延がロックされた後も極めて短いパルス幅の信号UP及びDNが出力される。したがって、従来の遅延ロックドループ回路には定常ジッタが存在する。定常ジッタを抑制するには遅延ゲインを小さくすることが考えられるが、遅延ゲインを小さくすると、遅延がロックされるまでの応答速度、すなわち、ロッキングタイムが遅くなってしまう。また、ループフィルタの容量を大きくしてフィルタ時定数を大きくすることで定常ジッタを抑制することも考えられるが、この場合、回路規模が大きくなってしまう。

**【0008】**

上記問題に鑑み、本発明は、原理的に定常ジッタがなく、基準クロック信号のデューティ比にかかわらず高精度な遅延クロック信号を生成可能な遅延ロックドループ回路を実現することを課題とする。

【課題を解決するための手段】

【0009】

上記課題を解決するために本発明が講じた手段は、遅延ロックドループ回路として、基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化から遅延して、第1の論理レベルから第2の論理レベルへ変化する遅延クロック信号を生成する遅延素子と、前記基準クロック信号の第1の変化、前記基準クロック信号の前記第2の論理レベルから前記第1の論理レベルへの第2の変化、及び前記遅延クロック信号の変化に応じて相補的に変化する第1及び第2の信号を生成する信号生成回路と、前記第1及び第2の信号に従って、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、プッシュ動作及びプル動作のいずれか一方である第1の動作を行い、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、プッシュ動作及びプル動作の他方である第2の動作を行うチャージポンプ回路と、前記チャージポンプ回路の出力を受けるループフィルタとを備えたものとする。ここで、前記遅延素子は、前記ループフィルタの出力に基づいて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延量を制御する。

【0010】

この発明によると、信号生成回路によって、基準クロック信号の第1の論理レベルから第2の論理レベルへの第1の変化及びその逆の第2の変化、並びに、遅延素子によって遅延制御され生成された遅延クロック信号の第1の論理レベルから第2の論理レベルへの変化に応じて相補的に変化する第1及び第2の信号が生成され、これら第1及び第2の信号に従ってチャージポンプ回路がプッシュプル動作をし、その出力はループフィルタによって平滑化され、その平滑化された出力に基づいて、遅延素子によって遅延クロック信号の遅延制御が行われる。ここで、遅延クロック信号の変化は、基準クロック信号の第1の変化から、遅延素子によって制御される量だけ遅延して生じる。したがって、本発明に係る遅延ロックドループ回路では、遅延のロッキングポイントは、基準クロック信号の第1の変化から所定量だけ遅延した唯一のところとなり、また、基準クロック信号のデューティ比にかかわらず、基準クロック信号のオンデューティ又はオフデューティ中に立ち上がり又は立ち下がりが生じる遅延クロック信号が生成される。また、本発明に係る遅延ロックドループ回路では、原理的に、定常状態において、遅延クロック信号のジッタの原因となるパルスが出力されない。したがって、ジッタの抑制を目的としてフィルタ時定数を大きくする必要がなく、ループフィルタの小型化、ひいては遅延ロックドループ回路全体の小型化が実現される。

【0011】

具体的には、前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記遅延クロック信号の変化から前記基準クロック信号の第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成する。また、前記チャージポンプ回路は、前記第1の動作に係る第1の電流を供給する第1の電流源と、前記第2の動作に係る第2の電流を供給する第2の電流源と、前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチとを有する。また、前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行う。

【0012】

この発明によると、チャージポンプ回路のプッシュ動作及びプル動作に係る電荷量が平

10

20

30

40

50

衡となるように遅延ロックドループ回路が動作する。したがって、プッシュ動作及びプル動作のそれぞれに係る電流量を適宜設定することにより、所望のロッキングポイントを設定することができる。

#### 【0013】

より具体的には、前記第1の電流の大きさと前記第2の電流の大きさとは等しい。これにより、基準クロック信号のデューティ比にかかわらず、基準クロック信号のオンデューティ又はオフデューティの半分の時点で立ち上がり又は立ち下がりが生じる遅延クロック信号が生成される。

#### 【0014】

また、具体的には、前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成する。また、前記チャージポンプ回路は、前記第1の動作に係る第1の電流を供給する第1の電流源と、前記第2の動作に係る第2の電流を供給する第2の電流源と、前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチとを有する。また、前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行う。

10

20

#### 【0015】

この発明によると、チャージポンプ回路のプッシュ動作及びプル動作に係る電荷量が平衡となるように遅延ロックドループ回路が動作する。したがって、プッシュ動作及びプル動作のそれぞれに係る電流量を適宜設定することにより、所望のロッキングポイントを設定することができる。また、第2の信号として基準クロック信号をそのままか又はその反転を用いることができるため、信号生成回路の構成が比較的容易になり、回路規模が縮小する。

#### 【0016】

より具体的には、前記第1の電流の大きさは、前記第2の電流の大きさの2倍に相当する。これにより、基準クロック信号のデューティ比にかかわらず、基準クロック信号のオンデューティ又はオフデューティの半分の時点で立ち上がり又は立ち下がりが生じる遅延クロック信号が生成される。

30

#### 【0017】

また、具体的には、前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成する。また、前記チャージポンプ回路は、前記第1の動作に係る第1及び第4の電流をそれぞれ供給する第1及び第4の電流源と、前記第2の動作に係る第2及び第3の電流をそれぞれ供給する第2及び第3の電流源と、前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチと、前記第1の信号が前記第1の論理レベルのとき、前記第3の電流を遮断し、前記第2の論理レベルのとき、前記第3の電流を通電する第3のスイッチと、前記第2の信号が前記第1の論理レベルのとき、前記第4の電流を遮断し、前記第2の論理レベルのとき、前記第4の電流を通電する第4のスイッチとを有する。また、前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行う。

40

50

**【 0 0 1 8 】**

この発明によると、チャージポンプ回路のプッシュ動作及びプル動作に係る電荷量が平衡となるように遅延ロックドループ回路が動作する。したがって、プッシュ動作及びプル動作のそれぞれに係る電流流量を適宜設定することにより、所望のロッキングポイントを設定することができる。また、第2の信号として基準クロック信号又はその反転をそのまま用いることができるため、信号生成回路の構成が比較的容易になり、回路規模が縮小する。

**【 0 0 1 9 】**

より具体的には、前記第2から第4の電流の大きさはいずれも等しく、かつ、前記第1の電流の大きさは、前記第2から第4の電流の大きさの3倍に相当する。これにより、基準クロック信号のデューティ比にかかわらず、基準クロック信号のオンデューティ又はオフデューティの半分の時点で立ち上がり又は立ち下がりが生じる遅延クロック信号が生成される。

**【 0 0 2 0 】**

また、具体的には、前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、第1の論理レベルとなり、これ以外のとき、第2の論理レベルとなる信号を生成する。また、前記チャージポンプ回路は、前記第1の動作に係る第1、第4及び第5の電流をそれぞれ供給する第1、第4及び第5の電流源と、前記第2の動作に係る第2及び第3の電流をそれぞれ供給する第2及び第3の電流源と、前記第1の信号が前記第1の論理レベルのとき、前記第1の電流を通電し、前記第2の論理レベルのとき、前記第1の電流を遮断する第1のスイッチと、前記第2の信号が前記第1の論理レベルのとき、前記第2の電流を通電し、前記第2の論理レベルのとき、前記第2の電流を遮断する第2のスイッチと、前記第1の信号が前記第1の論理レベルのとき、前記第3の電流を遮断し、前記第2の論理レベルのとき、前記第3の電流を通電する第3のスイッチと、前記第2の信号が前記第1の論理レベルのとき、前記第4の電流を遮断し、前記第2の論理レベルのとき、前記第4の電流を通電する第4のスイッチとを有する。また、前記遅延素子は、前記ループフィルタの出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行う。

**【 0 0 2 1 】**

この発明によると、チャージポンプ回路のプッシュ動作及びプル動作に係る電荷量が平衡となるように遅延ロックドループ回路が動作する。したがって、プッシュ動作及びプル動作のそれぞれに係る電流流量を適宜設定することにより、所望のロッキングポイントを設定することができる。また、第2の信号として基準クロック信号又はその反転をそのまま用いることができるため、信号生成回路の構成が比較的容易になり、回路規模が縮小する。

**【 0 0 2 2 】**

より具体的には、前記第1の電流の大きさと前記第3の電流の大きさとは等しく、前記第2、第4及び第5の電流の大きさはいずれも等しく、かつ、前記第1及び第3の電流の大きさは、前記第2、第4及び第5の電流の大きさの2倍に相当する。これにより、基準クロック信号のデューティ比にかかわらず、基準クロック信号のオンデューティ又はオフデューティの半分の時点で立ち上がり又は立ち下がりが生じる遅延クロック信号が生成される。

**【 0 0 2 3 】**

また、具体的には、前記信号生成回路は、前記第1の信号として、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの間、第1の電圧となり、これ以外のとき、第2の電圧となる信号を生成し、前記第2の信号として、前記基準クロックの第1の変化から第2の変化までの間、前記第2の電圧となり、これ以外のとき、前記第1の電圧となる信号を生成する。また、前記チャージポンプ回路は、前記第1の信号を受ける

10

20

30

40

50

第1の抵抗と、前記第2の信号を受ける第2の抵抗と、一端が前記第1及び第2の抵抗の接続箇所に接続され、他端に第3の電圧が与えられた第3の抵抗とを有する。また、前記ループフィルタは、容量と、負帰還部分に前記容量が接続され、反転入力端が前記チャージポンプ回路における第1から第3の抵抗の接続箇所に接続され、非反転入力端に第4の電圧が与えられた演算増幅器とを有する。また、前記遅延素子は、前記ループフィルタにおける演算増幅器の出力電圧の増大及び減少のいずれか一方に従って前記遅延量を減少し、他方に従って前記遅延量を増大する制御を行う。

#### 【0024】

この発明によると、チャージポンプ回路のプッシュ動作及びプル動作の切り替えの際にスイッチングノイズが発生しないため、電流精度の劣化がない。また、チャージポンプ回路が比較的低電圧で動作可能となる。10

#### 【0025】

より具体的には、前記第2の電圧と前記第3の電圧とは等しく、前記第4の電圧は、前記第1の電圧と前記第2の電圧との中間に相当する電圧であり、前記第2の抵抗の抵抗値と前記第3の抵抗の抵抗値とは等しく、前記第1の抵抗の抵抗値は、前記第2及び第3の抵抗の抵抗値の半分に相当する。これにより、基準クロック信号のデューティ比にかかわらず、基準クロック信号のオンデューティ又はオフデューティの半分の時点で立ち上がり又は立ち下がりが生じる遅延クロック信号が生成される。

#### 【0026】

また、具体的には、前記遅延素子は、直列に接続され、ゲートに前記基準クロック信号を受ける互いに逆極性の第1及び第2のトランジスタ、及びこれらトランジスタの間に接続され、ゲートに前記ループフィルタの出力を受ける第3のトランジスタを有し、前記第1のトランジスタと前記第2のトランジスタとの間の所定ノードの電圧を出力信号とする第1の回路と、前記第1の回路の出力信号の波形を整形する第2の回路とを備えている。20

#### 【0027】

この発明によると、第1の回路の出力信号の電圧は基準クロック信号の変化に応じて変化し、この変化に係る遅延は、第3のトランジスタに形成されるチャネルに応じて変化する。ここで、当該チャネルの形成状態はループフィルタの出力に応じて変化するため、ループフィルタの出力に基づく、第1の回路の出力信号の遅延量が制御可能となる。第1の回路の出力信号には当該遅延に伴い波形に鈍りが生じるが、第2の回路によって波形整形され、また、リングングも抑制される。これにより、第2の回路から出力された信号は遅延クロック信号として利用可能となる。また、第3のトランジスタのゲート電圧の調整によって上記遅延量が制御できることから、極めて広いロックインレンジが達成される。30

#### 【0028】

好ましくは、前記第1の回路は、前記第3のトランジスタに並列に接続された電流源を有する。

#### 【0029】

この発明によると、第3のトランジスタに並列に接続された電流源によって、第1の回路の出力信号に係る電荷移動に最小値の制限が設けられ、特に、第3のトランジスタに流れる電流が比較的小さい場合に、ループフィルタの出力のほんのわずかな変動により遅延クロック信号の遅延量が大幅に変動することによる発振を防止することができる。40

#### 【0030】

また、具体的には、前記第2の回路は、前記第1の回路の出力信号を受けるインバータと、前記インバータの入力及び出力をそれぞれドレイン及びゲートに受け、ソースに所定の電圧が与えられたトランジスタを有する。

#### 【0031】

この発明によると、第1の回路の出力信号の電圧がインバータの閾値を超えたとき、インバータからその論理反転に相当する信号が出力され、インバータの入出力間に設けられたトランジスタによってインバータ出力が所定の電圧に固定され、第1の回路の出力信号が波形整形される。50

**【 0 0 3 2 】**

また、好ましくは、上記の遅延ロックドループ回路は、前記遅延素子の遅延量を漸増させて、前記基準クロック信号の第1の変化から前記遅延クロック信号の変化までの遅延をロックする。

**【 0 0 3 3 】**

この発明によると、基準クロック信号の第1の変化から遅延クロック信号の変化までの遅延が最小値から次第に増加していく方向に制御される。初期状態における遅延素子の遅延量は最小であり、所望の値と異なるものの、遅延ロックドループ回路の動作開始時からすぐに遅延クロック信号が得られることになる。

**【 0 0 3 4 】**

一方、本発明が講じた手段は、遅延ロックドループ回路として、共通の基準クロック信号が与えられる、上記の遅延ロックドループ回路である第1及び第2の遅延ロックドループ回路と、前記第1及び第2の遅延ロックドループ回路の出力クロック信号から、前記共通の基準クロック信号の立ち上がりから遅延して立ち上がり及び立ち下がりのいずれか一方の変化が生じる一方、前記共通の基準クロック信号の立ち下がりから遅延して立ち上がり及び立ち下がりの他方の変化が生じる遅延クロック信号を生成するクロック生成回路とを備えたものとする。

**【 0 0 3 5 】**

この発明によると、第1及び第2の遅延ロックドループ回路に与えられた共通の基準クロック信号のデューティ比にかかわらず、当該共通の基準クロック信号のオンデューティ及びオフデューティ中に論理レベルが変化する遅延クロック信号が生成される。

**【 0 0 3 6 】**

具体的には、前記第1の遅延ロックドループ回路は、前記共通の基準クロック信号の立ち上がりから、前記共通の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものとする。また、前記第2の遅延ロックドループ回路は、前記共通の基準クロック信号の立ち下がりから、前記共通の基準クロック信号のオフデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものとする。

**【 0 0 3 7 】**

この発明によると、共通の基準クロック信号のデューティ比にかかわらず、そのデューティ比が補正され、生成される遅延クロック信号のデューティ比は50%となる。

**【 0 0 3 8 】**

また、本発明が講じた手段は、遅延ロックドループ回路として、第1の基準クロック信号が与えられる、上記の遅延ロックドループ回路である第1の遅延ロックドループ回路と、前記第1の基準クロック信号とは逆位相の第2の基準クロック信号が与えられる、上記の記載の遅延ロックドループ回路である第2の遅延ロックドループ回路と、前記第1及び第2の遅延ロックドループ回路の出力クロック信号から、前記第1の基準クロック信号の立ち上がりから遅延して立ち上がり及び立ち下がりのいずれか一方の変化が生じる一方、前記第1の基準クロック信号の立ち下がりから遅延して立ち上がり及び立ち下がりの他方の変化が生じる遅延クロック信号を生成するクロック生成回路とを備えたものとする。

**【 0 0 3 9 】**

この発明によると、第1及び第2の遅延ロックドループ回路の極性を同一にすることができる、回路設計が容易になる。

**【 0 0 4 0 】**

具体的には、前記第1の遅延ロックドループ回路は、前記第1の基準クロック信号の立ち上がりから、前記第1の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものとする。また、前記第2の遅延ロックドループ回路は、前記第2の基準クロック信号の立ち上がりから、前記第2の基準クロック信号のオンデューティの半分に相当する期間遅延して、論理レベルが変化するクロック信号を出力するものとする。

10

20

30

40

50

**【0041】**

この発明によると、第1の基準クロック信号のデューティ比にかかわらず、そのデューティ比が補正され、生成される遅延クロック信号のデューティ比は50%となる。

**【発明の効果】****【0042】**

以上のように、本発明によると、原理的に定常ジッタがなく、基準クロック信号のデューティ比にかかわらず高精度な遅延クロック信号が生成される。このため、時定数の大きなループフィルタを特に設ける必要がなくなり、遅延ロックドロープ回路の回路規模が縮小する。

**【発明を実施するための最良の形態】**

10

**【0043】**

以下、本発明を実施するための最良の形態について、図面を参照しながら説明する。

**【0044】****(第1の実施形態)**

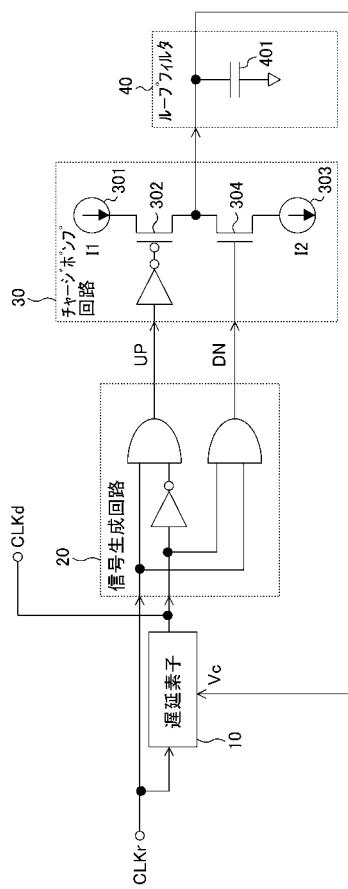

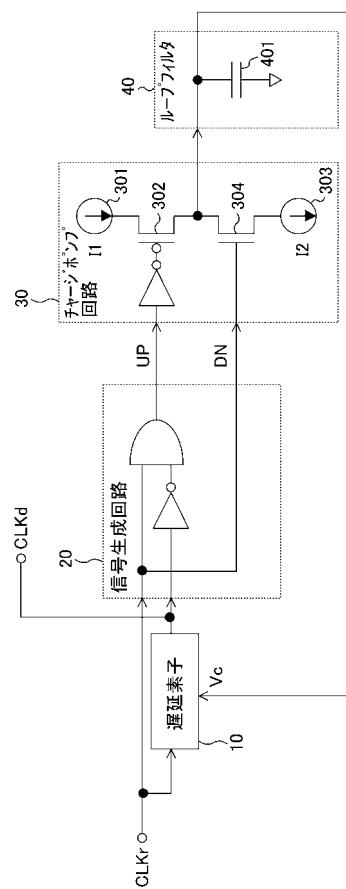

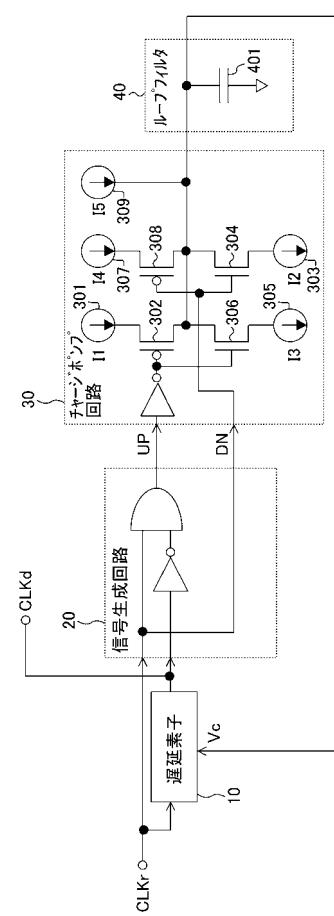

図1は、本発明の第1の実施形態に係る遅延ロックドロープ回路の構成を示す。本実施形態に係る遅延ロックドロープ回路は、遅延素子10、信号生成回路20、チャージポンプ回路30、及びループフィルタ40を備えている。遅延素子10は、基準クロック信号CLKrを受け、遅延クロック信号CLKdを出力する。遅延クロック信号CLKdの遅延量は、ループフィルタ40から出力された制御電圧Vcによって制御される。信号生成回路20は、基準クロック信号CLKrと遅延クロック信号CLKdの反転との論理積を信号UPとして、また、基準クロック信号CLKrと遅延クロック信号CLKdとの論理積を信号DNとして、それぞれ出力する。チャージポンプ回路30は、電流源301、電流源301が供給する電流I1の通電/遮断を信号UPに従って制御するスイッチ302、電流源303、及び、電流源303が供給する電流I2の通電/遮断を信号DNに従つて制御するスイッチ304を備え、信号UPがHiレベルのとき、電流I1を外部へ出力し(プッシュ動作)、信号DNがHiレベルのとき、電流I2を外部から引き込む(プル動作)。ループフィルタ40は、容量401を備え、チャージポンプ回路30の出力を受け、これを積分して制御電圧Vcを生成する。

20

**【0045】**

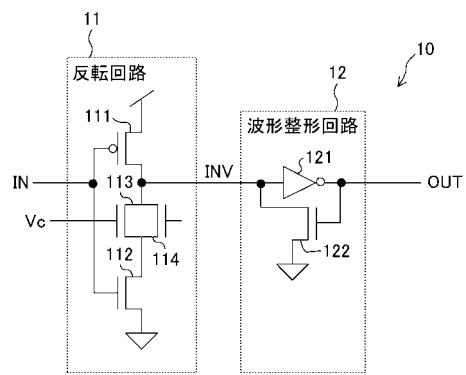

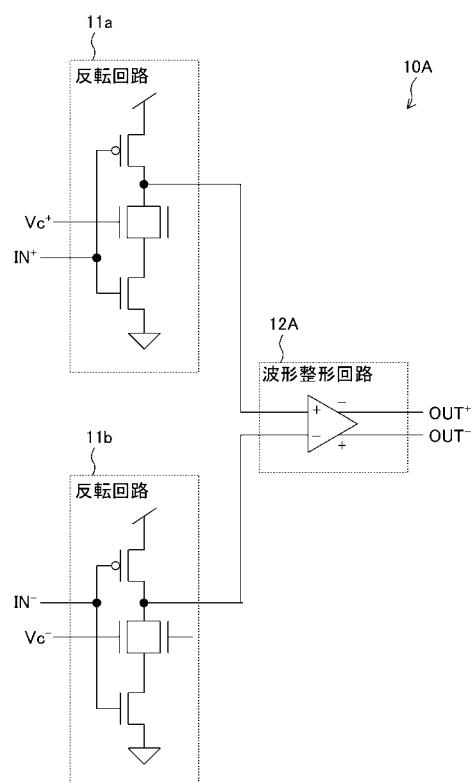

図2は、遅延素子10の構成を示す。遅延素子10において、反転回路11は、遅延素子10の入力信号INを受け、これを論理反転して信号INVを出力する。具体的には、反転回路11は、直列に接続されたPMOSトランジスタ111及びNMOSトランジスタ112、これら二つのトランジスタの間に接続されたNMOSトランジスタ113、及びトランジスタ113に並列に接続されたNMOSトランジスタ114を備えている。トランジスタ111及び112のそれぞれのゲートには信号INが与えられ、トランジスタ111及び113の接続箇所から信号INVが出力される。また、トランジスタ113のゲートにはループフィルタ40から出力された制御電圧Vcが与えられ、トランジスタ114のゲートには所定の電圧が与えられる。一方、波形整形回路12は、信号INVの波形を整形し、遅延素子10の出力信号OUTを生成する。具体的には、波形整形回路12は、信号INVを受け、信号OUTを出力するインバータ121、及びドレイン及びゲートがそれぞれインバータ121の入力端及び出力端に接続され、ソースに所定の電圧、例えば、グランド電圧が与えられたNMOSトランジスタ122を備えている。

30

**【0046】**

反転回路11において、信号INがLoレベルのとき、スイッチとしてのトランジスタ111及び112はそれぞれ導通状態及び非導通状態となり、反転回路11の出力先には電源ノードから電荷が供給され、信号INVはHiレベルとなる。一方、信号INがHiレベルのとき、トランジスタ111及び112はそれぞれ非導通状態及び導通状態となり、出力先に供給された電荷は接地ノードに引き抜かれ、信号INVはLoレベルとなる。

40

**【0047】**

図3は、遅延素子10のタイミングチャートを示す。信号INが立ち下がると、信号I

50

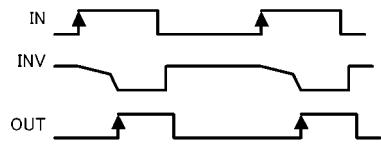

NVは、すぐさまLoレベルからHiレベルへ変化する。これに対して、信号INが立ち上がっても、信号INVは、すぐにはHiレベルからLoレベルへ変化せずに比較的なだらかに変化する。これは、トランジスタ113及び114によって、接地ノードへの電荷引き抜きに制限が加えられることによる。このように波形に鈍りがある信号INVは、波形整形回路12によって波形整形され、急峻な立ち上がり及び立ち下がりを有する信号OUTとなって出力される。また、波形整形回路12は、信号INVに生じるリンギングを抑制するといった効果を奏する。

#### 【0048】

上述したように、トランジスタ113及び114によって接地ノードへの電荷引き抜きに制限が加えられた結果、信号OUTの立ち上がりは、信号INが立ち上がってからある程度遅延して発生する。ここで、制御電圧Vcを適宜調整することによって、トランジスタ113に形成されるチャネルの状態が変化し、信号INVのHiレベルからLoレベルへの変化の速度が変化し、結果として、信号OUTの遅延量が調整される。なお、トランジスタ114は一定の大きさの電流を引き込む電流源として動作する。すなわち、接地ノードへの電荷引き抜きに関して最小値の制限を設けている。この制限がない場合、トランジスタ113に流れる電流が比較的小さい場合に、制御電圧Vcがほんのわずか変化することにより、遅延クロック信号CLKdの遅延量が大幅に変化してしまい、発振してしまうおそれがあるからである。

#### 【0049】

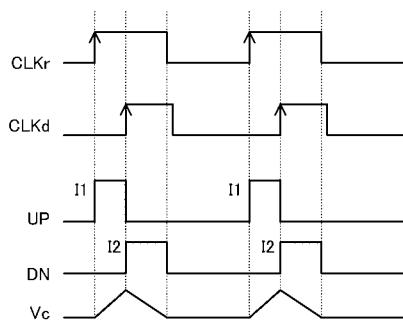

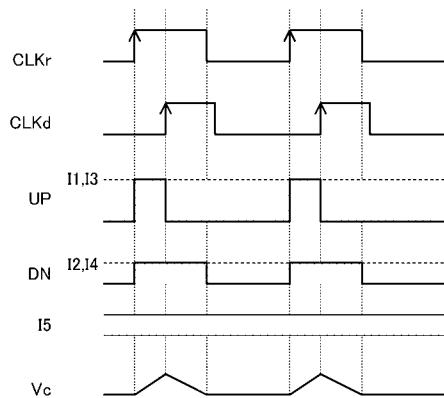

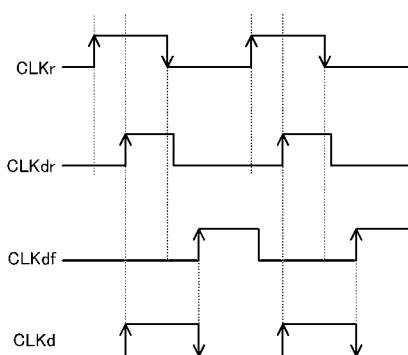

図4は、本実施形態に係る遅延ロックドロープ回路のタイミングチャートを示す。基準クロック信号CLKr及び遅延クロック信号CLKdは、それぞれ、図3に示した信号IN及びOUTに相当する。信号UPは、基準クロック信号CLKrの立ち上がりから遅延クロック信号CLKdの立ち上がりまでの期間、Hiレベルとなる。信号DNは、遅延クロック信号CLKdの立ち上がりから基準クロック信号CLKrの立ち下がりまでの期間、Hiレベルとなる。すなわち、信号UP及びDNは、遅延クロック信号CLKdの立ち上がりを境として、基準クロック信号CLKrのオンデューティの前半及び後半の期間、それぞれHiレベルとなる。なお、図4に示したタイミングチャートにおいて、信号UP及びDNに重ねて、チャージポンプ回路30から外部に向かって流れる電流（プッシュ電流）及び外部からチャージポンプ回路30に向かって流れる電流（プル電流）をその大きさとともに平行斜線で表示している。

#### 【0050】

基準クロック信号CLKrが立ち上ると信号UPがHiレベルとなり、チャージポンプ回路30からループフィルタ40に電流I1が供給され、制御電圧Vcは漸増する。制御電圧Vcが比較的低い場合、遅延クロック信号CLKdの遅延量は比較的大きく、逆に、制御電圧Vcが比較的高い場合、遅延クロック信号CLKdの遅延量は比較的小さい。したがって、制御電圧Vcの増大は、遅延クロック信号CLKdの遅延量を減少させる方向に働き、基準クロック信号CLKrが立ち上がってからある程度の時間が経過したときに、遅延クロック信号CLKdが立ち上がる。この結果、信号DNがHiレベルとなり、ループフィルタ40からチャージポンプ回路30に電流I2が引き込まれ、制御電圧Vcは漸減して元のレベルに戻る。

#### 【0051】

本実施形態に係る遅延ロックドロープ回路では、遅延クロック信号CLKdの立ち上りは、基準クロック信号CLKrのオンデューティをある比率で内分した時点で発生するが、この比率は、電流I1及びI2の関係によって決まる。すなわち、本実施形態に係る遅延ロックドロープ回路では、チャージポンプ回路30によるプッシュ動作及びプル動作に係る電荷量が平衡するようにフィードバックシステムが作用し、信号UPと信号DNとのHi期間の比が電流I1と電流I2の逆数比となったところでシステムが安定する。したがって、電流I1及びI2の大きさを適宜設定することによって、遅延クロック信号CLKdが基準クロック信号CLKrのオンデューティを所望の比率で内分する時点で立ち上るように調整することができる。

10

20

30

40

50

## 【0052】

特に、電流  $I_1$  及び  $I_2$  を等しく設定した場合、遅延クロック信号  $C_{LKd}$  の立ち上がりは、基準クロック信号  $C_{LKr}$  のオンデューティのちょうど半分の時点で生じる。すなわち、基準クロック信号  $C_{LKr}$  のデューティ比が 50 % であるか否かにかかわらず、基準クロック信号  $C_{LKr}$  のオンデューティの半分の時点で立ち上がりが生じる遅延クロック信号  $C_{LKd}$  を得ることができる。

## 【0053】

また、従来の遅延ロックドループ回路では定常状態において信号  $U_P$  及び  $D_N$  が出力されないのが理想であるが、原理上、実際にはごく短いパルスが出力され、これが定常ジッタの原因となっていたのに対して、本実施形態に係る遅延ロックドループ回路では、定常状態において、チャージポンプ回路 30 によるプッシュ動作及びプル動作に係る電荷量が平衡となるように信号  $U_P$  及び  $D_N$  が常に出力される。これにより、制御電圧  $V_c$  は、図 4 に示したように漸増、漸減を繰り返すが、遅延素子 10 の遅延量は、漸増部分の電圧軌跡で決定される。したがって、本実施形態に係る遅延ロックドループ回路では、原理上、定常ジッタの原因が発生せず、ジッタ特性に極めて優れた出力、すなわち、遅延クロック信号を得ることができる。

## 【0054】

以上、本実施形態によると、原理的に定常ジッタがなく、基準クロック信号のデューティ比にかかわらず高精度な遅延クロック信号を生成することができる。

## 【0055】

なお、遅延ロックドループ回路を、上記説明とは逆の論理で動作するように構成してもよい。

## 【0056】

## (第 2 の実施形態)

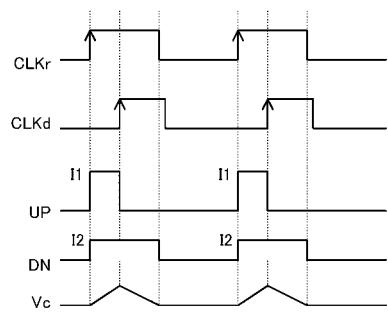

図 5 は、本発明の第 2 の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第 1 の実施形態とは異なる構成の信号生成回路 20 を備えている。本実施形態に係る信号生成回路 20 は、基準クロック信号  $C_{LKr}$  と遅延クロック信号  $C_{LKd}$  の反転との論理積を信号  $U_P$  として、また、基準クロック信号  $C_{LKr}$  を信号  $D_N$  として、それぞれ出力する。以下、本実施形態に係る遅延ロックドループ回路について、第 1 の実施形態に係る遅延ロックドループ回路と異なる点のみを説明する。

## 【0057】

図 6 は、本実施形態に係る遅延ロックドループ回路のタイミングチャートを示す。信号  $U_P$  は、基準クロック信号  $C_{LKr}$  の立ち上がりから遅延クロック信号  $C_{LKd}$  の立ち上がりまでの期間、 $H_i$  レベルとなる。信号  $D_N$  は、基準クロック信号  $C_{LKr}$  と同じである。なお、図 6 に示したタイミングチャートにおいて、信号  $U_P$  及び  $D_N$  に重ねて、チャージポンプ回路 30 から外部に向かって流れる電流（プッシュ電流）及び外部からチャージポンプ回路 30 に向かって流れる電流（プル電流）をその大きさとともに平行斜線で表示している。

## 【0058】

基準クロック信号  $C_{LKr}$  が立ち上ると信号  $U_P$  及び  $D_N$  が  $H_i$  レベルとなり、チャージポンプ回路 30 におけるスイッチ 302 及び 304 が閉じ、チャージポンプ回路 30 からループフィルタ 40 に、電流  $I_1$  と電流  $I_2$  との差分電流が供給され、制御電圧  $V_c$  は漸増する。そして、基準クロック信号  $C_{LKr}$  が立ち上がってからある程度の時間が経過したときに、遅延クロック信号  $C_{LKd}$  が立ち上がる。この結果、信号  $U_P$  のみが  $L_o$  レベルとなり、スイッチ 302 のみが開き、ループフィルタ 40 からチャージポンプ回路 30 に電流  $I_2$  が引き込まれ、制御電圧  $V_c$  は漸減して元のレベルに戻る。したがって、電流  $I_1$  及び  $I_2$  の大きさを適宜設定することによって、遅延クロック信号  $C_{LKd}$  が基準クロック信号  $C_{LKr}$  のオンデューティを所望の比率で内分する時点で立ち上がるよう調整することができる。

10

20

30

40

50

**【0059】**

特に、電流  $I_1$  を電流  $I_2$  の 2 倍に相当する大きさとなるように設定した場合、チャージポンプ回路 30 におけるスイッチ 302 及び 304 がいずれも閉じたときに供給される電流の大きさと、スイッチ 304 のみが閉じたときに引き込まれる電流の大きさとが等しくなり、遅延クロック信号  $CLK_d$  の立ち上がりは、基準クロック信号  $CLK_r$  のオンデューティのちょうど半分の時点で生じる。

**【0060】**

以上、本実施形態によると、第 1 の実施形態と比較して信号生成回路 20 の構成が容易になり、遅延ロックドループ回路全体としての回路規模が縮小する。

**【0061】**

10

**(第 3 の実施形態)**

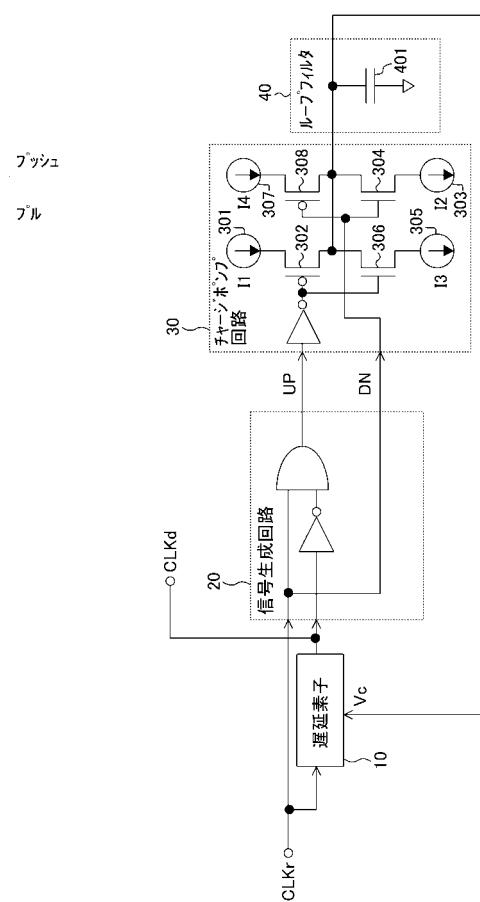

図 7 は、本発明の第 3 の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第 2 の実施形態とは異なる構成のチャージポンプ回路 30 を備えている。本実施形態に係るチャージポンプ回路 30 は、第 2 の実施形態に係るチャージポンプ回路 30 に、さらに、電流源 305、電流源 305 が供給する電流  $I_3$  の通電 / 遮断を信号  $UP$  に従って制御するスイッチ 306、電流源 307、及び、電流源 307 が供給する電流  $I_4$  の通電 / 遮断を信号  $DN$  に従って制御するスイッチ 308 を備えている。以下、第 2 の実施形態と異なる点についてのみ説明する。

**【0062】**

20

図 8 は、本実施形態に係る遅延ロックドループ回路のタイミングチャートを示す。なお、図 8 に示したタイミングチャートにおいて、信号  $UP$  及び  $DN$  に重ねて、チャージポンプ回路 30 から外部に向かって流れる電流（プッシュ電流）及び外部からチャージポンプ回路 30 に向かって流れる電流（プル電流）をその大きさとともに平行斜線で表示している。

**【0063】**

基準クロック信号  $CLK_r$  が立ち上ると信号  $UP$  及び  $DN$  が  $H_i$  レベルとなり、チャージポンプ回路 30 におけるスイッチ 302 及び 304 が閉じ、チャージポンプ回路 30 からループフィルタ 40 に、電流  $I_1$  と電流  $I_2$  との差分電流が供給され、制御電圧  $V_c$  は漸増する。そして、基準クロック信号  $CLK_r$  が立ち上がってからある程度の時間が経過したときに、遅延クロック信号  $CLK_d$  が立ち上がる。この結果、信号  $UP$  のみが  $L_o$  レベルとなり、スイッチ 302 は開き、代わりにスイッチ 306 が閉じ、ループフィルタ 40 からチャージポンプ回路 30 に、電流  $I_2$  と電流  $I_3$  との合計電流が引き込まれ、制御電圧  $V_c$  は漸減して元のレベルに戻る。そして、基準クロック信号  $CLK_r$  が立ち下がったとき、信号  $DN$  は  $L_o$  レベルとなり、スイッチ 304 は開き、代わりにスイッチ 308 が閉じ、ループフィルタ 40 に、電流  $I_3$  と電流  $I_4$  との差分電流が供給される。ここで、電流  $I_3$  と電流  $I_4$  とが等しいとき、プッシュ電流とプル電流とは相殺され、基準クロック信号  $CLK_r$  が  $L_o$  レベルにある間は、チャージポンプ回路 30 のプッシュプル動作は見かけ上停止する。

30

**【0064】**

40

本実施形態に係る遅延ロックドループ回路においても、電流  $I_1 \sim I_4$  の大きさを適宜設定することによって、遅延クロック信号  $CLK_d$  が基準クロック信号  $CLK_r$  のオンデューティを所望の比率で内分する時点で立ち上るように調整することができる。特に、電流  $I_2 \sim I_4$  の大きさをいずれも等しくし、電流  $I_1$  を電流  $I_2 \sim I_4$  の大きさの 3 倍に相当する大きさとなるように設定した場合、チャージポンプ回路 30 におけるスイッチ 302 及び 304 が閉じたときにループフィルタ 40 に供給される電流の大きさと、スイッチ 304 及び 306 が閉じたときにループフィルタ 40 から引き込まれる電流の大きさとが等しくなり、遅延クロック信号  $CLK_d$  の立ち上がりは、基準クロック信号  $CLK_r$  のオンデューティのちょうど半分の時点で生じる。

**【0065】**

以上、本実施形態によると、第 1 の実施形態と比較して信号生成回路 20 の構成が容易

50

になり、遅延ロックドループ回路全体としての回路規模が縮小する。

#### 【0066】

(第4の実施形態)

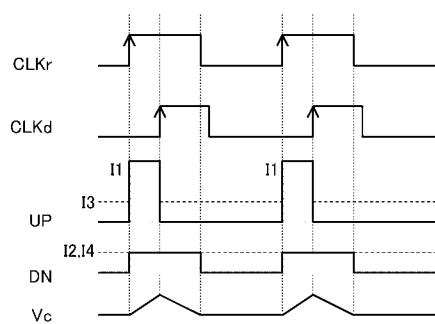

図9は、本発明の第4の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、第2及び3の実施形態とは異なる構成のチャージポンプ回路30を備えている。本実施形態に係るチャージポンプ回路30は、第3の実施形態に係るチャージポンプ回路30に、さらに、電流源301と同極性の電流I5を供給する電流源309を備えている。すなわち、本実施形態に係るチャージポンプ回路30では、信号UP及びDNの状態にかかわらず、電流源309から電流I5が常時供給されている。以下、第3の実施形態と異なる点についてのみ説明する。

10

#### 【0067】

図10は、本実施形態に係る遅延ロックドループ回路のタイミングチャートを示す。なお、図10に示したタイミングチャートにおいて、信号UP及びDNに重ねて、チャージポンプ回路30から外部に向かって流れる電流(プッシュ電流)及び外部からチャージポンプ回路30に向かって流れる電流(プル電流)をその大きさとともに平行斜線で表示している。

#### 【0068】

基準クロック信号CLKrが立ち上ると信号UP及びDNがHiレベルとなり、チャージポンプ回路30におけるスイッチ302及び304が閉じ、チャージポンプ回路30からループフィルタ40に、電流I1と電流I5との合計電流と電流I2との差分電流が供給され、制御電圧Vcは漸増する。そして、基準クロック信号CLKrが立ち上がってからある程度の時間が経過したときに、遅延クロック信号CLKdが立ち上がる。この結果、信号UPのみがLoレベルとなり、スイッチ302は開き、代わりにスイッチ306が閉じ、ループフィルタ40からチャージポンプ回路30に、電流I2と電流I3との合計電流と電流I5との差分電流が引き込まれ、制御電圧Vcは漸減して元のレベルに戻る。そして、基準クロック信号CLKrが立ち下がったとき、信号DNはLoレベルとなり、スイッチ304は開き、代わりにスイッチ308が閉じ、ループフィルタ40に、電流I4と電流I5との合計電流と電流I3との差分電流が供給される。ここで、電流I4と電流I5との合計電流と電流I3とが等しいとき、プッシュ電流とプル電流とは相殺され、基準クロック信号CLKrがLoレベルにある間は、チャージポンプ回路30のプッシュ・プル動作は見かけ上停止する。

20

#### 【0069】

本実施形態に係る遅延ロックドループ回路においても、電流I1～I5の大きさを適宜設定することによって、遅延クロック信号CLKdが基準クロック信号CLKrのオンデューティを所望の比率で内分する時点で立ち上るよう調整することができる。特に、電流I1及びI3の大きさを等しくし、電流I2、I4及びI5の大きさを等しくし、かつ、電流I1及びI3を電流I2、I4及びI5の大きさの2倍に相当する大きさとなるように設定した場合、チャージポンプ回路30におけるスイッチ302及び304が閉じたときにループフィルタ40に供給される電流の大きさと、スイッチ304及び306が閉じたときにループフィルタ40から引き込まれる電流の大きさとが等しくなり、遅延クロック信号CLKdの立ち上がりは、基準クロック信号CLKrのオンデューティのちょうど半分の時点で生じる。

30

#### 【0070】

以上、本実施形態によると、第1の実施形態と比較して信号生成回路20の構成が容易になり、遅延ロックドループ回路全体としての回路規模が縮小する。

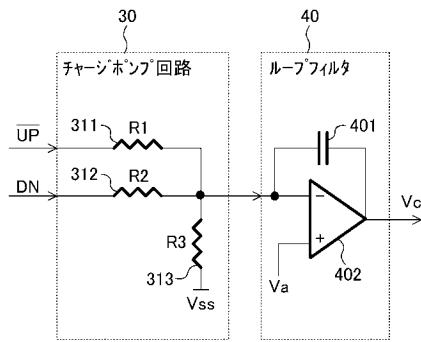

#### 【0071】

ところで、本実施形態に係るチャージポンプ回路30では、信号UP及びDNのそれぞれに従つて同じ大きさの電流がその向きを変えつつ連続的に流れるため、電流の通電／遮断のスイッチング制御はもはや不要となり、図11に示したような回路構成が可能となる。すなわち、チャージポンプ回路30は、信号UPの反転(以下、「信号／UP」と表す

40

50

) を受ける抵抗 311 ( 抵抗値 R1 ) 、信号 DN を受ける抵抗 312 ( 抵抗値 R2 ) 、及び、一端が抵抗 311 及び 312 の接続箇所に接続され、他端にグランド電圧 Vss が与えられた抵抗 313 ( 抵抗値 R3 ) を備えており、また、ループフィルタ 40 は、容量 401 、及び、負帰還部分に容量 401 が接続され、反転入力端がチャージポンプ回路 30 における抵抗 311 ~ 313 の接続箇所に接続され、非反転入力端に電圧 Va が与えられた演算增幅器 402 を備えている。

#### 【 0072 】

図 11において、信号 / UP 及び DN の Hi レベルの電圧を電源電圧 Vdd 、 Lo レベルの電圧をグランド電圧 Vss (= 0) としたとき、基準クロック信号 CLKr が立ち上がるとき信号 / UP 及び DN はそれぞれグランド電圧 Vss 及び電源電圧 Vdd となる。ここで、次の条件、

$$R2 = R3 = 2R1 = R, \text{かつ}, Va = (Vdd - Vss) / 2 = Vdd / 2$$

を満たすように、抵抗 311 ~ 313 の抵抗値、及び、電圧 Va をそれぞれ設定すると、信号 / UP 及び DN がそれぞれグランド電圧 Vss 及び電源電圧 Vdd となつたとき、抵抗 311 から信号 / UP の入力端に、大きさが Vdd / R の電流が流れ出し、信号 DN の入力端から抵抗 312 に、大きさが Vdd / 2 / R の電流が流れ込む。また、抵抗 311 ~ 313 の接続点からグランドノードには、大きさが Vdd / 2 / R の電流が流れている。したがって、キルヒホッフの法則により、演算增幅器 402 の出力側から抵抗 311 ~ 313 の接続点に、容量 401 を介して電流 Vdd / R が流れ込む。この結果、制御電圧 Vc は漸増する。

#### 【 0073 】

そして、基準クロック信号 CLKr が立ち上がってからある程度の時間が経過したときに、遅延クロック信号 CLKd が立ち上がり、信号 / UP が電源電圧 Vdd となり、信号 / UP の入力端から抵抗 311 に、大きさが Vdd / R の電流が流れ込む。したがって、キルヒホッフの法則により、抵抗 311 ~ 313 の接続点から演算增幅器 402 の出力側に、容量 401 を介して電流 Vdd / R が流れ出す。この結果、制御電圧 Vc は漸減して元のレベルに戻る。

#### 【 0074 】

その後、基準クロック信号 CLKr が立ち下がったとき、信号 DN はグランド電圧 Vss (= 0) となり、抵抗 312 から信号 DN の入力端に、大きさが Vdd / 2 / R の電流が流れ出す。したがって、信号 / UP の入力端から抵抗 311 に流れ込む電流は、抵抗 312 及び 313 を通じて流れ出し、ループフィルタ 40 には流れ込まなくなる。すなわち、基準クロック信号 CLKr が Lo レベルにある間は、チャージポンプ回路 30 のプッシュパブル動作は見かけ上停止する。

#### 【 0075 】

以上のように、図 11 に示したチャージポンプ回路 30 及びループフィルタ 40 を備えた遅延ロックドループ回路は、図 9 に示した本実施形態に係る遅延ロックドループ回路と同様の動作をする。しかも、図 11 に示した変形例ではスイッチを用いていないためスイッチングノイズに起因する電流精度の劣化がなく、また、図 9 に示した遅延ロックドループ回路よりも低電圧での動作が可能となる。

#### 【 0076 】

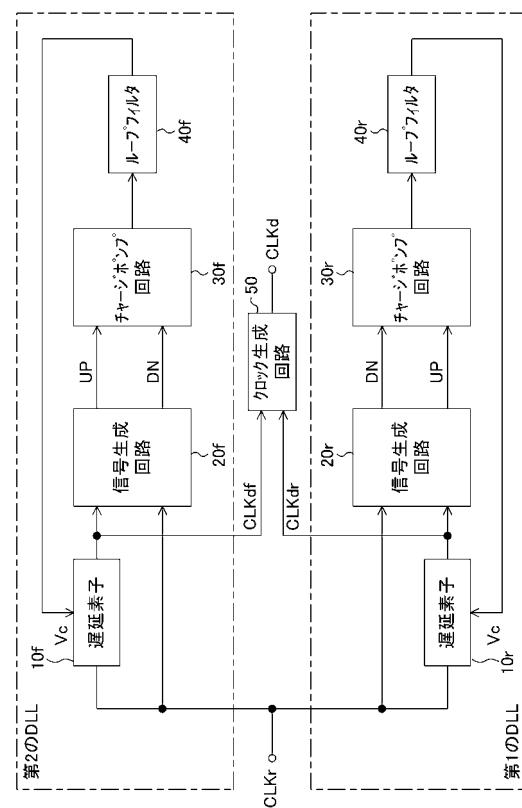

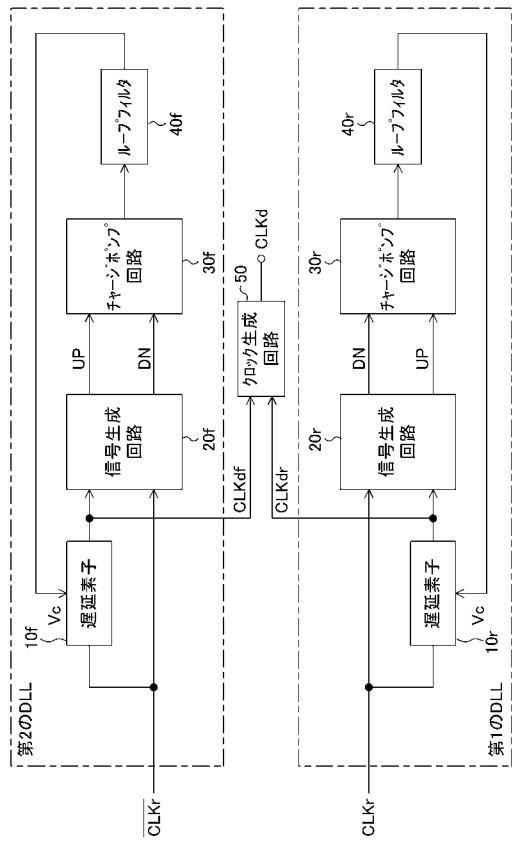

##### ( 第 5 の実施形態 )

図 12 は、本発明の第 5 の実施形態に係る遅延ロックドループ回路の構成を示す。本実施形態に係る遅延ロックドループ回路は、上記の第 1 から第 4 の実施形態に係る遅延ロックドループ回路のいずれか二つを組み合わせた構成をしており、第 1 の遅延ロックドループ回路は、遅延素子 10r 、信号生成回路 20r 、チャージポンプ回路 30r 、及びループフィルタ 40r を備え、第 2 の遅延ロックドループ回路は、遅延素子 10f 、信号生成回路 20f 、チャージポンプ回路 30f 、及びループフィルタ 40f を備えている。第 1 及び第 2 の遅延ロックドループ回路は、それぞれ、基準クロック信号 CLKr の立ち上がり及び立ち下がりから遅延して論理レベルが変化する遅延クロック信号 CLKdr 及び C

10

20

30

40

50

$L_Kd_f$  を出力する。第 1 及び第 2 の遅延ロックドループ回路の具体的構成は、第 1 から第 4 の実施形態で説明した通りである。また、本実施形態に係る遅延ロックドループ回路はクロック生成回路 50 を備えている。以下、本実施形態に特徴的な部分についてのみ説明する。

#### 【0077】

クロック生成回路 50 は、遅延クロック信号  $CLKdr$  及び  $CLKdf$  から遅延クロック信号  $CLKd$  を生成する。図 13 は、本実施形態に係る遲延ロックドループ回路のタイミングチャートを示す。遲延クロック信号  $CLKd$  の生成方法はさまざまであるが、例えば、図 13 に示したように、遲延クロック信号  $CLKd$  は、遲延クロック信号  $CLKdr$  が立ち上ることによって立ち上がり、遲延クロック信号  $CLKdf$  が立ち上ることによって立ち下がるようにすればよい。

10

#### 【0078】

特に、遲延クロック信号  $CLKdr$  及び  $CLKdf$  がそれぞれ基準クロック信号  $CLKr$  のオンデューティ及びオフデューティのちょうど半分の時点で立ち上るよう、第 1 及び第 2 の遲延ロックドループ回路を構成することによって、遲延クロック信号  $CLKd$  は、基準クロック信号  $CLKr$  のオンデューティのちょうど半分の時点で立ち上がり、オフデューティのちょうど半分の時点で立ち下がる。ここで、基準クロック信号  $CLKr$  の周期を  $T$ 、デューティ比を  $\_$  とすると、遲延クロック信号  $CLKd$  のオンデューティの時間は、

$$T / 2 + (1 - \_) T / 2 = T / 2$$

20

となり、基準クロック信号  $CLKr$  のちょうど半分の周期 ( $T / 2$ ) となる。すなわち、基準クロック信号  $CLKr$  のデューティ比にかかわらず遲延クロック信号  $CLKd$  のデューティ比は 50 % となる。

#### 【0079】

以上、本実施形態によると、基準クロック信号  $CLKr$  から 1 / 4 位相 ( $90^\circ$ ) 遅れ及び 3 / 4 位相 ( $270^\circ$ ) 遅れで論理レベルが変化する遲延クロック信号  $CLKd$  が生成される。また、基準クロック信号  $CLKr$  のデューティ比が補正される。

#### 【0080】

さらに、本実施形態においては、遲延素子 10r と遲延素子 10f を、差動回路で構成すれば、ノイズに対してより強い構成となる。具体的には、図 14 で示す差動回路で構成可能である。図 14 に示した遲延素子 10A は、図 2 に示した反転回路 11 と同様の反転回路 11a 及び 11b、及び、差動増幅器を有する波形整形回路 12A を備えている。反転回路 11a 及び 11b は、それぞれ、差動入力信号として信号  $IN^+$  及び  $IN^-$  を受ける。波形整形回路 12A は、反転回路 11a 及び 11b の出力を受けて波形整形し、信号  $OUT^+$  及び  $OUT^-$  を出力する。図 14 に示した差動回路を図 12 に示した遲延ロックドループ回路に適用する場合は、信号  $IN^+$  として基準クロック信号  $CLKr$  を、信号  $IN^-$  として基準クロック信号  $CLKr$  の反転信号を入力し、信号  $OUT^+$  及び  $OUT^-$  を遲延クロック信号  $CLKdr$  及び  $CLKdf$  にそれぞれ対応させればよい。このように、遲延素子を差動回路で構成することにより、電源などで発生する同相位相ノイズがキャンセルされ、より高精度の遲延クロック信号を生成することができる。

30

#### 【0081】

##### (第 6 の実施形態)

図 15 は、本発明の第 6 の実施形態に係る遲延ロックドループ回路の構成を示す。本実施形態に係る遲延ロックドループ回路は、第 5 の実施形態に係る遲延ロックドループ回路における第 1 及び第 2 の遲延ロックドループ回路に、互いに逆位相関係にある基準クロック信号  $CLKr$  及びその反転（以下、「基準クロック信号 /  $CLKr$ 」と表す）を与える構成となっている。

#### 【0082】

第 1 及び第 2 の遲延ロックドループ回路は、それぞれ、基準クロック信号  $CLKr$  及び  $/ CLKr$  の立ち上がり（又は立ち下がり）から遲延して論理レベルが変化する遲延クロ

40

50

ック信号 C L K d r 及び C L K d f を出力する。すなわち、第 2 の遅延ロックループ回路は、実質的に、基準クロック信号 C L K r の立ち下がり（又は立ち上がり）から遅延して論理レベルが変化する遅延クロック信号 C L K d f を出力するものであり、クロック生成回路 50 によって生成される遅延クロック信号 C L K d は第 5 の実施形態の場合と同様である。

#### 【 0 0 8 3 】

本実施形態では、第 1 及び第 2 の遅延ロックループ回路の極性を同一にすることができます。したがって、第 1 及び第 2 の遅延ロックループ回路として同じものを使用することができるため、回路設計が容易になる。

#### 【 0 0 8 4 】

なお、第 5 及び第 6 の実施形態では、遅延素子 10 r 及び 10 f のそれぞれによって生成された遅延クロック信号 C L K d r 及び C L K d f から新たな遅延クロック信号 C L K d を生成しているが、本発明はこれに限定されるものではない。遅延クロック信号 C L K d は、遅延クロック信号 C L K d r 及び C L K d f 以外にも、遅延クロック信号 C L K d r 及び C L K d f に基づいて生成された信号であって基準クロック信号 C L K r 及び / C L K r の立ち上がり（又は立ち下がり）から所定位相だけ遅延して論理レベルが変化する信号、例えば、信号生成回路 20 r 及び 20 f のそれぞれによって生成された信号 U P 又は信号 D N から生成するようにしてもよい。

#### 【 0 0 8 5 】

同様に、第 1 から第 4 の実施形態に係る遅延ロックループ回路の出力クロック信号は、遅延素子 10 によって生成された遅延クロック信号 C L K d に限られず、例えば、信号生成回路 20 によって生成された信号 U P 又は第 1 の実施形態の場合には信号 D N であつてもよい。信号 U P は遅延クロック信号 C L K d が波形整形されたものであるから、むしろ信号 U P を遅延ロックループ回路の出力とした方が好ましい。

#### 【 0 0 8 6 】

また、図 4 その他のタイミングチャートに示したような、基準クロック信号 C L K r のオンデューティ（又はオフデューティ）中に、一旦増加（又は減少）した後元のレベルに戻るといった制御電圧 V c の変化は、基準クロック信号 C L K r の立ち上がり及び立ち下がり並びに遅延クロック信号 C L K d の立ち上がり（遅延クロック信号 C L K d が基準クロック信号 C L K r の立ち上がり及び立ち下がりのいずれか一方から遅延して立ち下がる場合には当該立ち下がり）に応じて相補的に変化する信号 U P 及び D N に基づいて、実現可能である。したがって、上記各実施形態で説明した信号生成回路 20 及びチャージポンプ回路 30 以外にもさまざまな回路構成が実現可能である。例えば、図 6 のタイミングチャートにおいて、信号 U P が遅延クロック信号 C L K d の立ち上がりから基準クロック信号 C L K r の立ち下がりまでの間に論理レベル H i となるように信号生成回路 20 及びチャージポンプ回路 30 の構成を変更しても、本発明が奏する効果に何ら違いはない。

#### 【 産業上の利用可能性 】

#### 【 0 0 8 7 】

本発明に係る遅延ロックループ回路は、基準クロック信号のデューティ比にかかわらず高精度かつ定常ジッタがない遅延クロック信号を生成するため、DDR（ダブル・データ・レート）規格のインターフェースに、特に有用である。

#### 【 図面の簡単な説明 】

#### 【 0 0 8 8 】

【 図 1 】本発明の第 1 の実施形態に係る遅延ロックループ回路の構成図である。

【 図 2 】遅延素子の構成図である。

【 図 3 】遅延素子のタイミングチャートである。

【 図 4 】本発明の第 1 の実施形態に係る遅延ロックループ回路のタイミングチャートである。

【 図 5 】本発明の第 2 の実施形態に係る遅延ロックループ回路の構成図である。

【 図 6 】本発明の第 2 の実施形態に係る遅延ロックループ回路のタイミングチャートで 50

ある。

【図7】本発明の第3の実施形態に係る遅延ロックドループ回路の構成図である。

【図8】本発明の第3の実施形態に係る遅延ロックドループ回路のタイミングチャートである。

【図9】本発明の第4の実施形態に係る遅延ロックドループ回路の構成図である。

【図10】本発明の第4の実施形態に係る遅延ロックドループ回路のタイミングチャートである。

【図11】図9に示したチャージポンプ回路及びループフィルタの変形例である。

【図12】本発明の第5の実施形態に係る遅延ロックドループ回路の構成図である。

【図13】本発明の第5の実施形態に係る遅延ロックドループ回路のタイミングチャート 10 である。

【図14】差動回路として構成した場合の遅延素子の構成図である。

【図15】本発明の第6の実施形態に係る遅延ロックドループ回路の構成図である。

【図16】従来の遅延クロックループ回路の構成図である。

#### 【符号の説明】

##### 【0089】

10, 10A, 10r, 10f 遅延素子

11, 11a, 11b 反転回路(第1の回路)

12, 12A 波形整形回路(第2の回路)

20, 20r, 20f 信号生成回路

30, 30r, 30f チャージポンプ回路

40, 40r, 40f ループフィルタ

50 クロック生成回路

111 トランジスタ(第1のトランジスタ)

112 トランジスタ(第2のトランジスタ)

113 トランジスタ(第3のトランジスタ)

114 トランジスタ(電流源)

121 インバータ

122 トランジスタ

301 電流源(第1の電流源)

30

302 スイッチ(第1のスイッチ)

303 電流源(第2の電流源)

304 スイッチ(第2のスイッチ)

305 電流源(第3の電流源)

306 スイッチ(第3のスイッチ)

307 電流源(第4の電流源)

308 スイッチ(第4のスイッチ)

309 電流源(第5の電流源)

311 抵抗(第1の抵抗)

312 抵抗(第2の抵抗)

313 抵抗(第3の抵抗)

401 容量

402 演算増幅器

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(74)代理人 100131200

弁理士 河部 大輔

(74)代理人 100131901

弁理士 長谷川 雅典

(74)代理人 100132012

弁理士 岩下 嗣也

(74)代理人 100141276

弁理士 福本 康二

(74)代理人 100143409

弁理士 前田 亮

(74)代理人 100157093

弁理士 間脇 八藏

(74)代理人 100163186

弁理士 松永 裕吉

(74)代理人 100163197

弁理士 川北 憲司

(74)代理人 100163588

弁理士 岡澤 祥平

(72)発明者 崎山 史朗

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 道正 志郎

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 徳永 祐介

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 岩田 徹

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 平田 貴士

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 土居 康之

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 吉井 英喜

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 服部 慎

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 上田 智志

(56)参考文献 特開平11-008552(JP,A)

実公昭60-036908(JP,Y1)

特開平11-205131(JP,A)

特開2000-082954 (JP, A)

特開平08-180678 (JP, A)

特公昭56-019769 (JP, B1)

実開昭63-072937 (JP, U)

## (58)調査した分野(Int.Cl., DB名)

H03L 7/00 - 7/23,

H03K 5/06,

G11C 11/407