(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4869593号

(P4869593)

(45) 発行日 平成24年2月8日(2012.2.8)

(24) 登録日 平成23年11月25日(2011.11.25)

(51) Int.Cl.

B&amp;1B 3/00 (2006.01)

F 1

B&amp;1B 3/00

請求項の数 10 外国語出願 (全 15 頁)

(21) 出願番号 特願2004-380343 (P2004-380343)

(22) 出願日 平成16年12月28日 (2004.12.28)

(65) 公開番号 特開2005-193374 (P2005-193374A)

(43) 公開日 平成17年7月21日 (2005.7.21)

審査請求日 平成19年12月25日 (2007.12.25)

(31) 優先権主張番号 10/748,920

(32) 優先日 平成15年12月29日 (2003.12.29)

(33) 優先権主張国 米国(US)

(73) 特許権者 390041542

ゼネラル・エレクトリック・カンパニイ

アメリカ合衆国、ニューヨーク州、スケネ

クタディ、リバーロード、1番

(74) 代理人 100137545

弁理士 荒川 智志

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100106541

弁理士 伊藤 信和

(74) 代理人 100129779

弁理士 黒川 俊久

(72) 発明者 ロウエル・スコット・スマス

アメリカ合衆国、ニューヨーク州、スケネ

クタディ、チェシャー・プレイス、24番

最終頁に続く

(54) 【発明の名称】コンプライアント支持構造体を有する微細加工超音波トランステューサセル

## (57) 【特許請求の範囲】

## 【請求項 1】

基材内又は基材上に微細加工された機械的構造体を含むデバイスであって、前記機械的構造が、コンプライアント支持構造体(22又は24)と、該コンプライアント支持構造体によって支持された部材(8)とを含み、前記コンプライアント支持構造体が前記部材の運動中にサイズ又は形状が変化し、

前記部材が膜と、該膜によって支持された第1の電極(12)とを含み、前記第1の電極から一定距離に配置されて、該第1の電極との間に配置されるキャビティと共にキャパシタを形成する第2の電極(10)を更に含み、前記コンプライアント支持構造体が、前記膜の振動中にサイズ又は形状が変化し、

前記コンプライアント支持構造体が、第1の壁(26)と、内側周縁部分及び外側周縁部分を有し且つこれらの方方が前記第1の壁上に形成されたリング状構造体(28)と、前記内側周縁部分と外側周縁部分の他方上に形成され且つ前記膜に接続された第2の壁(30)とを含むことを特徴とするデバイス。

## 【請求項 2】

台座(32)を更に含み、前記第2の電極が前記台座によって支持されていることを特徴とする請求項1に記載のデバイス。

## 【請求項 3】

前記リング状構造体の表面上に形成された第3の電極(10b)を更に含むことを特徴とする請求項1に記載のデバイス。

**【請求項 4】**

前記膜がピストン様に振動するように、前記支持構造体のコンプライアンス及び前記膜の堅さが選択されていることを特徴とする請求項 1 乃至 3 のいずれかに記載のデバイス。

**【請求項 5】**

基材(4)と、

複数のコンプライアント支持構造体(22又は24)と、

前記コンプライアント支持構造体によりキャビティ上で支持される膜(8)と、

前記膜によって支持される第1の電極(12)と、

前記第1の電極と共にキャパシタンスを形成する第2の電極(10)と、

を含み、

前記キャビティが前記第1の電極と第2の電極との間に配置され、前記コンプライアント支持構造体の各々が前記膜の振動中にサイズ又は形状が変化し、

前記コンプライアント支持構造体が、第1の壁(26)と、内側周縁部分及び外側周縁部分を有し且つこれら的一方が前記第1の壁上に形成されたリング状構造体(28)と、前記内側周縁部分と外側周縁部分の他方上に形成され且つ前記膜に接続された第2の壁(30)とを含むことを特徴とする c M U T セル。

**【請求項 6】**

基材内又は基材上に微細加工された機械的構造体を含むデバイスであって、前記機械的構造が、コンプライアント支持構造体(22又は24)と、該コンプライアント支持構造体によって支持された部材(8)とを含み、前記コンプライアント支持構造体が前記部材の運動中にサイズ又は形状が変化し、

前記部材が膜と、該膜によって支持された第1の電極(12)とを含み、前記第1の電極から一定距離に配置されて、該第1の電極との間に配置されるキャビティと共にキャパシタを形成する第2の電極(10)を更に含み、前記コンプライアント支持構造体が、前記膜の振動中にサイズ又は形状が変化し、

前記コンプライアント支持構造体が、

第1の壁(32)と、

内側周縁部分と外側周縁部分とを有し、前記第1のリング状構造体の前記内側周縁部分及び外側周縁部分の一方が前記第1の壁上に形成された第1のリング状構造体(34)と、前記第1のリング状構造体の内側周縁部分及び外側周縁部分の他方の上に形成された第2の壁(36)と、

前記第1のリング状構造体の上方にあって、内側周縁部分と外側周縁部分とを有し、前記第2のリング状構造体の内側周縁部分及び外側周縁部分の一方が前記第2の壁上に形成された第2のリング状構造体(38)と、

前記第2のリング状構造体の内側周縁部分及び外側周縁部分の他方の上に形成され、且つ前記膜に接続されている第3の壁(40)と、

を含むことを特徴とするデバイス。

**【請求項 7】**

前記第1及び第2のリング状構造体の表面上に形成された第3の電極(10b)を更に含むことを特徴とする請求項 6 に記載のデバイス。

**【請求項 8】**

台座(32)を更に含み、前記第2の電極が前記台座によって支持されていることを特徴とする請求項 6 に記載のデバイス。

**【請求項 9】**

前記膜がピストン様に振動するように、前記支持構造体のコンプライアンス及び前記膜の堅さが選択されていることを特徴とする請求項 6 に記載のデバイス。

**【請求項 10】**

基材(4)と、

複数のコンプライアント支持構造体(22又は24)と、

前記コンプライアント支持構造体によりキャビティ上で支持される膜(8)と、

10

20

30

40

50

前記膜によって支持される第1の電極(12)と、

前記第1の電極と共にキャパシタンスを形成する第2の電極(10)と、

を含み、

前記キャビティが前記第1の電極と第2の電極との間に配置され、前記コンプライアント支持構造体の各々が前記膜の振動中にサイズ又は形状が変化し、

前記コンプライアント支持構造体が、

第1の壁(32)と、

内側周縁部分と外側周縁部分とを有し、前記第1のリング状構造体の前記内側周縁部分及び外側周縁部分の一方が前記第1の壁上に形成された第1のリング状構造体(34)と、

前記第1のリング状構造体の内側周縁部分及び外側周縁部分の他方の上に形成された第2の壁(36)と、

10

前記第1のリング状構造体の上方にあって、内側周縁部分と外側周縁部分とを有し、前記第2のリング状構造体の内側周縁部分及び外側周縁部分の一方が前記第2の壁上に形成された第2のリング状構造体(38)と、

前記第2のリング状構造体の内側周縁部分及び外側周縁部分の他方の上に形成され、且つ前記膜に接続されている第3の壁(40)と、

を含むことを特徴とするcMUTセル。

### 【発明の詳細な説明】

#### 【技術分野】

20

#### 【0001】

本発明は、一般的に、バルク基材に伝達される機械的力に対して前面に加わる機械的刺激の影響を遮断することが望まれるあらゆる微細加工構造体に関する。本発明は、表面微細加工及びバルク微細加工の両方に対して効果的である。

#### 【背景技術】

#### 【0002】

最近、容量型(cMUT)又は圧電型(pMUT)の種類のものとすることができます微細加工超音波トランステューサ(MUT)として知られる形式の超音波トランステューサを製造するために、半導体プロセスが使用されている。cMUTは、受信超音波信号の音響振動を変調された静電容量に変換する電極を備えた微細なダイアフラム状デバイスである。送信では、容量性電荷を変調してこの装置のダイアフラムを振動させ、これにより音波を送信する。

30

#### 【0003】

MUTの1つの利点は、「微細加工」として分類される微細製造プロセスなどの半導体製造プロセスを用いてこれらを作ることができる点である。米国特許第6,359,367号には、「微細加工とは、(A)パターン形成ツール(一般に投影アライナー又はウエーハステッパーなどのリソグラフィ)、(B)PVD(物理的蒸着)、CVD(化学気相蒸着)、LPCVD(低圧化学気相蒸着)、PECVD(プラズマ化学気相蒸着)などの堆積ツール、(C)湿式化学エッティング、プラズマエッティング、イオンミリング、スパッタエッティング、又はレーザー-エッティングなどのエッティングツールの組合せ又はこれらの一部を使用した微視的構造の形成である。微細加工は、典型的には、シリコン、ガラス、サファイア、又はセラミックから作られた基材又はウエーハ上で行われる。このような基材又はウエーハは一般に、極めて平坦且つ滑らかであり、数インチの横方向寸法を有する。これらは通常、カセット中のグループとしてプロセスツール毎に移動しながら処理される。各基材は有利には、(必ずしもそうとは限らないが)多数の製品コピーを組み込むことができる。微細加工には2つの一般的なタイプがあり、すなわち、1)ウエーハ又は基材の厚みの大きな部分が蝕刻されるバルク微細加工と、2)一般に蝕刻が表面、特に表面上に堆積された薄膜フィルムに限定される表面微細加工である。本明細書で使用される微細加工の定義は、従来型又は既知の微細加工可能な材料の使用を含み、これには、シリコン、サファイア、あらゆる形式のガラス材料、ポリマー類(ポリイミドなど)、ポリシリコン

40

50

、シリコン窒化物、シリコン酸化窒化物、アルミニウム合金、銅合金、及びタングステンなどの薄膜金属、スピンドルガラス（SOG）、埋め込み可能な又は拡散型のドーパント、及びシリコン酸化物又はシリコン窒化物などの成長フィルムが含まれる。」と説明されている。

#### 【0004】

本明細書においても上記と同じ微細加工の定義を採用する。このような微細加工プロセスによって得られるシステムは、通常「微細加工電気機械システム（MEMS）」と呼ばれる。

#### 【0005】

従来のcMUTは、静電的に「拍動する」微細なドラムに似ている。このドラムヘッドが振動して超音波の送信と受信の両方を行う。cMUTプローブは、各々が複数の個々のcMUTセルを含む多数の素子のアレイからなる。

#### 【0006】

典型的なcMUTセルは、上に金属電極が覆う薄膜（例えば、シリコン又は窒化ケイ素から作られる）を含み、シリコン基材の上又は内部に形成されたキャビティ（普通は真空中にされる）上に懸架される。下面電極は、シリコン基材内又はその上に形成される。cMUTセルのグループは、上面電極を互いに配線することにより電気的に接続することができる。膜を撓ませるための駆動力は、上面及び下面電極間に電圧が印加された時に両電極間で生じる静電的引力である。交流電圧が膜を駆動する場合には、結果として有意な超音波が発生する。逆に、膜が適正にバイアスされており、到来する超音波を受けた場合には、有意な検出電流が発生される。膜厚及びキャビティギャップは通常、0.5ミクロン程度である。2から15MHzの周波数でそれぞれ動作するcMUTアレイの場合、cMUTセルの横方向寸法は、100ミクロンから30ミクロンまでの範囲である。

#### 【0007】

ほとんどのcMUTは、全体的にタイル状の多数の小さなドラムヘッド膜を含む。これらの膜は、典型的には個々のcMUTセルの周り及び該セル間の固定壁によって支持される。膜間のこの固定支持構造体は、トランステューサアレイの有効面積を減少させ、トランステューサ素子間の望ましくない構造的共振及びクロストークの原因となる可能性がある。ドラムヘッドの撓みは、不均一であり、中央部において最も大きく、縁部においてゼロである。

#### 【0008】

各cMUTセルのトランスタクション性能は、電極間の距離、支持体のコンプライアンス、及び膜の堅さ（並びに膜の密度及びポアソン比などの因子）に依存する。堅い支持体と可撓性膜とを用いると、この構造体は、ドラムヘッド、すなわち従来のcMUTのような挙動を示す。従来のcMUTアレイの性能を改善する新規のcMUT構造体に対する必要性が存在する。

#### 【特許文献1】米国特許第6,359,367号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

本発明は、コンプライアント支持構造体を有するcMUTセルに関する。このコンプライアント支持構造体は、各cMUTセルの非膜外表面を支持基材から離隔する。従来の超音波cMUTは、小さなダイアフラム（直径100ミクロン程度）を有するように構成されているが、本明細書で提案される方法は、ミリメートル範囲のはるかに大きな構造体であって、更に広い周波数範囲に対して感度を維持する構造体の製造を可能にするはずである。

#### 【0010】

比較的堅い膜と組み合せた場合、コンプライアント支持構造体は、1)入射音圧又は印加電気励起の単位当たりのより大きな膜変位を可能にし、従って電気信号と超音波間とをより効果に変換し、2)より均一な膜変位、つまり多数の小面積ドラムヘッドの代わりに

10

20

30

40

50

大面積のピストン様変位を可能にし、3) 従来のトランステューサの1つ又は複数の素子の多数のcMUTセル間にある比較的剛直な変位しない支持壁を排除することによって、トランステューサの有効面積を増大させ、及び4) 音場とcMUTトランステューサ基材との間の結合を低減することにより、クロストークと基材における構造的共振の影響を低減させる。

#### 【0011】

表面又はバルク微細加工によりコンプライアント支持構造体を形成することができる。本明細書では、表面微細加工コンプライアント支持構造体の実施例が開示される。バルク微細加工においては、基材の一部分(第1のウエーハ)を除去してキャビティを形成し、次に膜及び他の除去可能な材料を組み込んだ第2のウエーハを第1のウエーハに接合して、バルク基材内に形成されたキャビティ上に膜を覆うことにより、コンプライアント支持構造体を形成することができる。10

#### 【課題を解決するための手段】

#### 【0012】

本発明の1つの態様は、基材内又は基材上に微細加工された機械的構造体を含むデバイスであって、該機械的構造体は、コンプライアント支持構造体と、該コンプライアント支持構造体によって支持された部材とを含み、該コンプライアント支持構造体が部材の運動中にサイズ又は形状が変化する。一実施形態においては、部材は、膜と、該膜によって支持された第1の電極とを含み、第1の電極から一定距離に配置されて該第1の電極との間に配置されるキャビティと共にキャパシタを形成する第2の電極を更に含む。この場合、コンプライアント支持構造体は、膜の圧縮/膨張中にサイズ又は形状が変化する。20

#### 【0013】

本発明の別の態様は、cMUTセルアレイであって、このcMUTセルアレイは、コンプライアント支持構造体と、該コンプライアント支持構造体により第1のキャビティ上で支持される第1の膜と、該第1の膜によって支持される第1の電極と、該第1の電極と共にキャパシタを形成し、該第1の電極との間に第1のキャビティが配置された第2の電極と、コンプライアント支持構造体により第2のキャビティ上で支持された第2の膜と、該第2の膜によって支持され、且つ第1の電極に電気的に接続された第3の電極と、第2の電極に電気的に接続され、且つ第3の電極と共にキャパシタを形成するように配置された第4の電極とを含み、第2のキャビティが第3の電極と第4の電極との間に配置され、コンプライアント支持構造体の一部分が、第1のキャビティと第2のキャビティとの間に配置されている。30

#### 【0014】

本発明の更に別の態様は、基材の上方でcMUTセルの膜を支持するための支持構造体を製造する方法であって、この方法は、(a) 第1のリング形状を有する基材の第1の領域上に第1の厚さを有する第1の永久材料から成る第1の層を堆積させる段階と、(b) 該第1の領域と接する第2のリング形状を有する基材の第2の領域上及び該第2の領域と接する第3のリング形状を有する基材の第3の領域上に、第1の厚さを有する除去可能な材料から成る第1の層を堆積させる段階と、(c) 第1から第3の領域を覆う区域内で第1の層上に第2の厚さを有する第2の永久材料から成る第1の層を堆積させる段階と、(d) 第3の領域を覆う区域内で第2の永久材料から成る第1の層の上に第3の厚さを有する第1の永久材料から成る第2の層を堆積させる段階と、(e) 第1及び第2の領域を覆う区域内で第2の永久材料から成る第1の層の上に第3の厚さを有する除去可能な材料から成る第2の層を堆積させる段階と、(f) 第1の永久材料から成る第2の層及び除去可能な材料から成る第2の層の上に膜材料から成る層を堆積させる段階であって、膜材料から成る層が第1から第3の領域並びに第1から第3の領域によって囲まれる第4の領域の上を覆うようにする段階と、(g) 第1及び第2の永久材料又は膜材料を除去することなく除去可能な材料を除去する段階であって、段階(a)から(f)の後で行われる段階とを含む。40

#### 【0015】

50

本発明の更に別の態様は、基材内又は基材上に微細加工された機械的構造体を含むデバイスであって、該機械的構造体は、複数のコンプライアント支持構造体と、該複数のコンプライアント支持構造体によって支持された部材とを含み、該コンプライアント支持構造体は、部材の運動中にサイズ又は形状が変化する。別の実施形態においては、部材は、膜と、該膜によって支持された第1の電極と、該第1の電極から一定距離に配置されて、該第1の電極との間に配置されるキャビティと共にキャパシタを形成する第2の電極とを含む。この場合、コンプライアント支持構造体は、膜の圧縮／膨張中にサイズ又は形状が変化する。

#### 【0016】

本発明の更に別の態様は、基材の上方でcMUTセルの膜を支持するための支持構造体を製造する方法であって、この方法は、(a)基材の第1の領域上に第1の厚さを有する第1の永久材料から成る第1の層を堆積させる段階と、(b)該第1の領域と接する基材の第2の領域上に第1の厚さを有する除去可能な材料から成る第1の層を堆積させる段階と、(c)第1及び第2の領域を覆う区域内で第1の層上に第2の厚さを有する第2の永久材料から成る層を堆積させる段階と、(d)第2の領域の第1の部分を覆う区域内で第2の永久材料から成る第1の層の上に第3の厚さを有する第1の永久材料から成る第2の層を堆積させる段階と、(e)第1領域と第2の領域の第2の部分とを覆う区域内で第2の永久材料から成る層の上に第3の厚さを有する除去可能な材料から成る第2の層を堆積させる段階であって、該第2の領域の第1及び第2の部分が互いに重なり合わないようとする段階と、(f)第1の永久材料から成る第2の層及び除去可能な材料から成る第2の層の上に膜材料から成る層を堆積させる段階であって、膜材料から成る層が第1及び第2の領域、及びこれら第1及び第2の領域の外側にある第3の領域を覆うようにする段階と、(g)第1及び第2の永久材料又は膜材料を除去することなく、除去可能な材料を除去する段階であって、段階(a)から(f)の後で行われる段階とを含む。

#### 【0017】

本発明の更に別の態様は、トランスデューサ素子であって、該素子は、膜と、該膜の周縁部が取り付けられる固定周縁壁と、該固定周縁壁の内側に配置された複数のトランスデューサセルとを含み、これらのセルの各々は、膜のそれぞれの部分に接続されたそれぞれのコンプライアント支持構造体を含む。

#### 【0018】

本発明の他の態様は、以下に開示すると共に請求項において請求する。

#### 【発明を実施するための最良の形態】

#### 【0019】

次に、図面を参照して説明する。図面では異なる図面で類似の要素に同じ参照番号を付す。

#### 【0020】

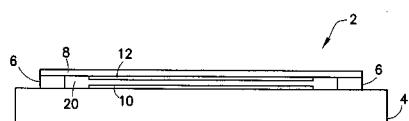

容量性微細加工超音波トランスデューサ(cMUT)は、超音波エネルギーを送受することのできる小型の(例えば $50\mu m$ )容量性「ドラムヘッド」又はセルを含むシリコンベースのデバイスである。図1には、典型的なMUTトランスデューサセル2の断面図が示されている。このようなMUTトランスデューサセルのアレイは、典型的にはシリコンウエーハのような基材4内(バルク微細加工)、又は基材4上(表面微細加工)に作製される。各MUTトランスデューサセルでは、薄い可撓性膜又はダイアフラム8がキャビティ20上に懸架されている。膜8は、その周縁部上で絶縁支持体6によって支持されている。絶縁支持体6は、典型的には膜8の下方でキャビティ20を取り囲む比較的剛体の垂直壁を含む。1個のcMUTセルは、典型的にはその隣接するセルと壁部分を共有する。膜8と基材4との間のキャビティ20は、空気又はガスが充填されてもよいし、あるいは完全又は部分的に真空であってもよい。アルミニウム合金又は他の適当な導電性材料のような導電性材料のフィルム又は層が、薄膜8上で電極12を形成し、導電性材料で作られたもう1つのフィルム又は層が、基材4上で電極10を形成している。代替的には、基材をドープして下面電極を形成してもよい。また、電極12は、図1に示すように下面では

10

20

30

40

50

なく膜 8 の上面にあってもよい。

**【 0 0 2 1 】**

2つの電極 10 及び 12 は、キャビティ 20 によって離隔され、キャパシタンスを形成する。入射する音響信号が膜 8 を振動させると、付属する電子回路（図 1 には図示せず）を使用してキャパシタンスの変化を検出することができ、これにより音響信号を電気信号に変換する。逆に、一方の電極に印加された A C 信号が電極上の電荷を変調し、次いでこれが電極間の容量力に変調を引き起こし、前記変調によりダイアフラムが移動することにより音響信号を送信する。

**【 0 0 2 2 】**

作動時には、c M U T セルは通常、電極両端に印加される時変電圧  $v(t)$  よりも有意に高い D C バイアス電圧  $V_{bias}$  を有する。このバイアスは、クーロン力により上面電極を下面に向かって引き付ける。強くバイアスされたこの場合には、c M U T ドラムヘッドは、次式で与えられる膜変位  $u$  を生じる。

$$u(t) = ( / d^2) * V_{bias} * v(t) \quad (1)$$

式中、 $d$  は電極間すなわちキャパシタのプレート間の距離、 $/$  はセルの実行誘電率である。c M U T セルの感度は、バイアス電圧が高く且つ両電極が互いに近接している場合に最大となることが分かっている。

**【 0 0 2 3 】**

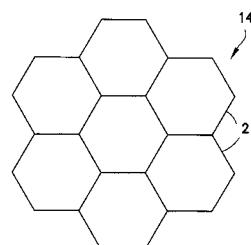

典型的な c M U T セルの寸法はミクロンサイズであるので、多数の c M U T セルが通常は極めて近接して製造されて単一のトランステューサ素子を形成する。個々のセルは、円形、矩形、六角形、又は他の外周形状を有することができる。六角形の形状は、トランステューサ素子の c M U T セルを高密度に充填することができる。

**【 0 0 2 4 】**

説明の目的で、図 2 は、7 個の六角形状 c M U T セル 2 から形成された「デイジー」素子 14 を示しており、6 個のセルのリングが 1 個の中央セルを取り囲み、リングの各セルが中央セルのそれぞれの側面とリングの隣接するセルとに接している。素子の各セルの上面電極は、互いに配線されている。各セルの下面電極も同様に互いに電気的に接続され、7 倍の大きさの容量性素子を形成する。

**【 0 0 2 5 】**

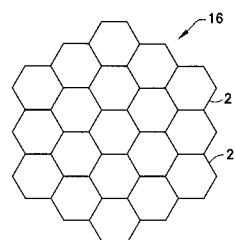

図 3 には、別の「六角形状」素子 16 が示され、19 個の c M U T セルから構成されている。各グループのセルの上面電極は互いに配線され、同様に各グループの下面電極が接続され、このようにしてより大きな容量性素子を形成している。M U T セルは非常に小型に作ることができるので、極微細なピッチのモザイク型アレイを完成することができる。

**【 0 0 2 6 】**

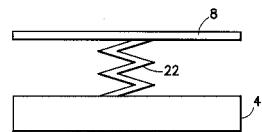

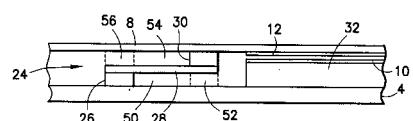

図 4 は、c M U T セルアレイの膜 8 を支持するためのペローズ 22 形のコンプライアント構造体を示す。このコンプライアント構造体は、図 9 を参照しながら後でより詳細に説明するように、シリコンウエーハなどの基材 4 上、又は C M O S 電子回路上に構成することができる。図 2 及び 3 に示す六角形パターンの場合には、各素子のコンプライアント構造体は、同一のパターンに従って構成されることになり、従って内側のセルが 6 個の隣接セルと六角形壁のそれぞれの部分を共有するようになる。図 4 は、基本的にコンプライアント構造体 22 の一部分を通る断面だけを示していることを理解されたい。膜 8 は、素子を構成する複数のセル上にわたって延びる比較的堅い膜材料から成る連続層によって形成することができ、これにより振動中に隣接するセルの膜がピストン状に同時に移動する。ペローズ 22 は、膜と基材との間の結合（すなわち音響伝達）を低減させる。またペローズは、膜の周縁部を密閉して、c M U T セル内部のガス又は真空を外部の音響媒体から隔離することができる。

**【 0 0 2 7 】**

あるいは、本明細書で開示された各 c M U T セル用のコンプライアント支持体は、このような c M U T セルのグループから成る素子の周縁壁から離隔することができる。この場合、コンプライアント支持体は、密閉には関係しない。図 2 を参照すると、この図は、7

10

20

30

40

50

個の個別セルから形成された素子を表している。各セル膜は、該構造がどのようなものであってもセル周縁部に取り付けられる。素子の周縁壁は、セルの周縁壁と同じ構造を有する必要はない。詳細には、素子の内部であって図4に示す構造に類似の壁が存在するが、素子の周縁壁は剛直である。ドラムヘッドは、多くの振動モードを有する。最も低い振動数モードは、円対称的であって、単一の半波長が直径全体をカバーする。これは、cMUTセルにとってほぼ最も望ましいモードである。より高い振動数モードは、直径にわたってより大きな波長と対称であるか、又は対称性が少ない可能性がある。例えば、直径にわたってノードラインで振動すると、左側が高くなり、右側が低くなる。コンプライアント内部壁を用いることにより、低振動数モードが個々のセルに対して維持されると同時に、素子の振動を構成セルの調整された特定の組合せに制約する。特に運動は、セルの同相又はコヒーレント運動に制約される。従って、非対称的（望ましくない）モードを抑制することができる。

#### 【0028】

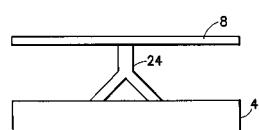

図5は、本発明の別の実施形態によるcMUTセルアレイの一部分の断面を示す。この場合も同様に、コンプライアント構造体は、セルの内部を外部音響媒体から密閉する閉じた壁である。この実施形態においては、コンプライアント支持構造体の断面は逆Y字形であり、すなわちこの構造体は、基部に逆V字形状のアーチと、このアーチの頂点から上方へ延びる壁とを備える。隣接するセルの膜8は、この壁の頂部によって支持される。この場合もまた、膜層8は比較的堅く、一方支持構造体は、比較的コンプライアントであって、膜がピストン様に振動することができる。単純な垂直壁からこのような構造の支持体に変更することにより、壁及び基材の共振を、トランステューサが使用することになる周波数の帯域外にずらすことができる。

#### 【0029】

図6は、本発明の別の実施形態によるcMUTセルアレイの一部分の断面を示す。2個の隣接するcMUTセルの一部が示されている。この構造は、MEMS技術を使用してcMUTセルが上に作製される基材4を含む。膜8は、片持ち梁に似た断面を有するコンプライアント支持構造体によって支持される。片持ち梁構造は、膜支持体のコンプライアンスを増大させ、MEMS技術を使用して作製することができる。各セルは、それぞれのセル膜の下側にある領域内で基材上に構築される台座32（図6の左側セルの台座は図示せず）を更に含む。金属層10は、台座32の上面の電極を形成し、別の金属層12は、膜8上の電極を形成する。電極10及び12は、キャパシタを形成する。膜下方の台座の高さは、キャパシタギャップを減少させることにより、感度を増大させる。電極10及び12は、隣接するcMUTセルの対応する電極（図示せず）にそれぞれ配線される。

#### 【0030】

図6に部分的に示す片持ち梁形のコンプライアント支持構造体は、基材4上に構成されたリング状（例えば、六角形状）壁26と、この壁26により一方の周縁部に沿って支持されたリング状（例えば、六角形状）プレート28と、このプレート28の他方の周縁部上に構成されたリング状（例えば、六角形状）壁30とを含む。膜8は、壁30によって支持され、プレート28のコンプライアンスにより垂直方向に変位することができる。プレート28は、壁26及び30を形成する材料よりもよりコンプライアントな材料で製造することができる。膜の材質が十分に堅い場合には、隣接セルの膜は、振動時にピストン様に同時に動くことができる。コンプライアントプレート28は、壁30を基材4から分離する。ここでも同様に、各セルの壁26、30、及びプレート28は、セルの内部を外部から密閉する閉じた構造を形成することができる。

#### 【0031】

図6に部分的に示すcMUTセル構成は、MEMS技術を用いて以下のように製造することができる。第1の厚さを有する例えば酸化ケイ素又は窒化ケイ素の第1の層が、第1のリング形状を有する基材の第1の領域上に堆積される。この酸化ケイ素又は窒化ケイ素の第1の層は、最終構造体における壁26となる。同様に、第1の厚さを有する除去可能な（例えばエッティング可能な）材料から成る第1の層は、第2のリング形状を有する基材

10

20

30

40

50

の第2の領域上で且つ第3のリング形状を有する該基材の第3の領域を覆って堆積される。第1の領域は第2の領域と接し、第2の領域は第3の領域と接している。この除去可能な材料によって占有され且つ基材上の上記第2及び第3の領域の上にあるそれぞれの空間は、図6においては点線で示され、それぞれ参照符号50及び52で示されている。その後、第2の厚さを有するコンプライアント材料から成る層が、第1から第3の領域の上にある区域の前記第1の層上に堆積される。コンプライアント材料は、酸化ケイ素又は窒化ケイ素、あるいはコンプライアンスがより大きな材料を含むことができる。コンプライアント材料の層は、最終製品におけるプレート28になる。微細製造の次の段階においては、第3の厚さを有する前記酸化ケイ素又は窒化ケイ素の第2の層が、第3の領域の上にある区域（すなわち空間52の上方）のプレート28上に堆積される。この酸化ケイ素又は窒化ケイ素の第2の層は、最終構造体における壁30となる。更に、第3の厚さを有する除去可能な材料から成る第2の層が、それぞれ第1及び第2の領域の上にある空間56及び54のプレート28上に堆積される。

#### 【0032】

更に台座32は、上記第1から第3の領域によって囲まれた基材の第4の領域の真上に形成される。次に第1の金属層が、台座の上面に堆積され、この層が最終構造体における電極10を形成する。除去可能な材料が、台座の金属化された表面の上面、並びに台座を周囲のコンプライアント支持構造体から離隔するほぼリング形状のすき間空間に堆積される。第2金属層が、電極10の上面に堆積された除去可能な材料から成る層の上面に堆積される。第2金属層は、最終構造体における電極12を形成することになる。

#### 【0033】

上記工程の全てが実行された後、膜材料から成る層が製造された構造体上に堆積される。膜材料は、電極12、壁30、及び残りの空間内を満たす除去可能な材料を覆う。次に、除去可能な材料が例えればエッティングによって取り除かれ、図6に示す微細加工構造体が残る。

#### 【0034】

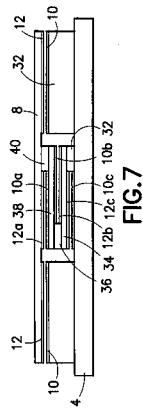

図7は、本発明の更に別の実施形態によるcMUTセルアレイの一部分の断面を示す。ここでも同様に2個の隣接するcMUTセルの一部が示されている。二重片持ち梁に似た断面を有するコンプライアント支持構造体が、隣接するセルのそれぞれの台座32間に堆積される。二重片持ち梁構造は、コンプライアント膜支持体を提供し、本明細書で上述した支持構造体と同様のMEMS法を使用して製造することができる。この場合もまた、各膜の下方にあるそれぞれの台座の高さがキャパシタギャップを低減することにより感度が増大し、他方1つのcMUTセルの電極10及び12は、隣接するcMUTセルの対応する電極にそれぞれ配線される。

#### 【0035】

図7に部分的に示す二重片持ち梁形コンプライアント支持構造体は、基材4上に形成されたリング状壁32、この壁32により一方の周縁部に沿って支持されたリング状プレート34、このプレート34の他方の周縁部上に構成されたリング状壁30、プレート34の上にあり、該プレート34との間にある壁36により一方の周縁部に沿って支持されたリング状プレート38と、プレート38の他方の周縁部上に形成されたリング状壁40とを含む。膜8は、壁40によって支持され、支持構造体のコンプライアンスによって垂直方向に変位することができる。プレート34及び38は、壁32、36、及び40が作られる材料よりもコンプライアンスの大きな材料で作ることができる。上で検討したように、膜材料が十分に堅い場合には、隣接するセルの膜は、振動時にピストン状に同時に動くことができる。コンプライアントプレート34及び38は、壁40を基材4から分離する。また、各々に対する壁32、36、40及びプレート34、38は、セルの内部を外部から密閉する閉じた構造体を形成することができる。

#### 【0036】

図7に示す実施形態は、二重片持ち梁形支持構造体に組み込まれた複数の平行プレートキャパシタを更に含み、圧縮及び膨張中に各ギャップの静電容量を付加的に変化させるこ

10

20

30

40

50

とにより受信時の感度を増大させる。これにより、片持ち梁形コンプライアント構造体が静電アクチュエータとしても機能することが可能になる。コンプライアント構造体内に組み込まれた第1のキャパシタは、プレート38の上面に形成された電極10aと、膜8の下面に形成された電極12aとを含む。電極12aは、各電極12の一方又は両方に配線され、電極10aは、各電極10の一方又は両方に配線される。第2のキャパシタは、プレート38の下面に形成された電極10bと、プレート34の上面に形成された電極12bとを含む。電極12bは、電極12aに配線することができ、電極10bは、電極10aに配線することができる。第3のキャパシタは、基材4の上面に形成された電極10cと、プレート34の下面に形成された電極12cとを含む。電極12cは、電極12bに配線することができ、電極10cは、電極10bに配線することができる。これらのキャパシタの各々は、コンプライアント支持体の圧縮／膨張中に追加的な電荷を発生することになる。この電荷は、圧縮／膨張中に電極10及び12によって発生される電荷に付加される。同様のキャパシタを図6に示す片持ち梁形コンプライアント構造体に付加することもできる。10

#### 【0037】

図7に部分的に示すcMUTセル構成は、図6に示す実施形態の製造に関して説明された同じMEMS技術を用いて製造することができるが、以下の相違点がある。すなわち、(1)コンプライアント材料から成る第2の層が堆積されて、プレート38を形成し、(2)酸化ケイ素又は窒化ケイ素から成る第3の層が堆積されて、壁40を形成し、(3)除去可能な材料から成る第3の層が堆積されて、二重片持ち梁形構造体内に第3のギャップを形成し、及び(4)金属の層が、除去可能な材料の各層上及び各対向する面上に堆積された後、除去可能な材料から成るそれぞれの層が堆積される。種々の層を堆積すべき順序は、図7に示す実施形態において種々のギャップ及び層が積み重ねられる順序によって主として規定される。20

#### 【0038】

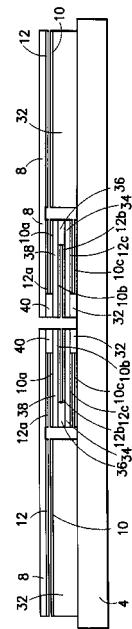

図8は、隣接するcMUT素子、すなわち二重片持ち梁形コンプライアント膜支持構造体を有する素子のそれぞれの一部分を示す。図8は、図7が1つ又は複数の素子の隣接する2個のセルにより共有された内部壁の一部分を示しており、図8は隣接する1つ又は複数の素子のセルのそれぞれの外壁のそれぞれの部分を示している点で図7と相違している。図8に示すコンプライアント支持構造体は、各素子又は複数の素子の外周縁部に沿って置かれ、図7に示す実質的に同一のコンプライアント支持構造体は、素子の内部にある。30

#### 【0039】

上に開示したコンプライアント膜支持体の各々は、各セルの周縁部を密閉する閉じた構造を有し、各cMUTセル内のガス又は真空を外部の音響媒体から分離する。代替として、上に開示した実施形態の構造は、各cMUTセルの内部と外部との間でガスを入れ替えることを可能にする開口又はギャップを備えるように変更してもよい。

#### 【0040】

コンプライアント支持体の他の実施形態は、膜を支持するために複数の点で配置された「コイルバネ」状構造体、点支持体として使用される片持ち梁、及び線又は縁部支持体として使用される片持ち梁を含む。例えば、片持ち梁断面を有する連続リングの形態のコンプライアント支持構造体の代わりに、同一の片持ち梁状断面を有する複数の離間配置の構造体を形成することによって、すなわち連続リングの複数の部分のみを製造することによってコンプライアント支持構造体を形成することができる。このような場合には、各セル膜は、連続周縁部に沿ってではなく、複数の離散的位置において支持される。このような支持構造体を作るために、同じパターン形成、蒸着、及びエッティング技術を使用することができる。40

#### 【0041】

別の実施形態によれば、複数のコンプライアント支持体は、膜を支持し且つ膜の下方にキャビティを形成する周縁壁と結合することができる。この場合には、支持体は壁の周縁部内に配置され、この複数のコンプライアント支持体はまた、膜のそれぞれの変位可能部50

分（すなわち周縁壁に取り付けられていない部分）を支持するように機能する。

**【0042】**

別の変形形態によれば、コンプライアント膜支持構造体は、膜下方の容積と外部媒体又はリザーバ容積との間の流体連通を可能にする制御開口を備えることができる。開口のサイズ、膜の下にあるガス又は流体の特性、膜によって変位する膜下方の容積、及びリザーバ容積は、膜の減衰に強い影響を及ぼすことになる。MEMS内を流れる流体（ガス又は液体）用バルブは、ダイアフラムバルブで構成される場合が多い。

**【0043】**

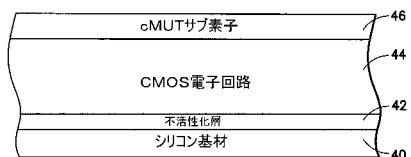

上記の実施形態は、シリコン基材上に形成することができるが、これらはまた、例えばCMOS電子回路等の電子回路の層を組み込む基材上に形成することもできる。再構成可能なビームフォーミング素子を提供するために、高帯域幅cMUTアレイをシリコンウェーハ上の従来のCMOSスイッチ及び増幅器/バッファ回路と一体化することができる。このような一体型構造においては、トランステューサ素子のサイズが、アレイ真下のシリコン内の超小型電子回路のためのセル寸法を規定する。図9には、このような一体型構造が一般的に示されている。不活性化層42（例えば、酸化物で作られる）が、シリコン基材40上に配置される。CMOS電子回路44が、不活性化層42上に製造される。次いで、cMUT素子46が、CMOS電子回路上に製造される。cMUT素子46は、上記で開示された実施形態のいずれかによるコンプライアント膜支持構造で製造することができる。

**【0044】**

ほんどの既存のcMUTが抱えている1つの問題は、これらが高いDCバイアス電圧及び高いAC駆動電圧を必要とすることである。cMUTの利点を最大限に引き出すためには、送受信電子回路をトランステューサ装置と密接に一体化することが望ましい。しかし、高電圧トランジスタは、大きな面積を必要とし、また入手可能な供給元が極めて少ない。コンプライアント支持体は、cMUTを駆動するのに必要な電圧を有意に低減することができ、従って小形で高性能の超音波トランステューサを得るためにcMUTとの電子回路の一体化を大いに助ける。

**【0045】**

本明細書に開示された特定の実施形態は、微細加工超音波トランステューサアレイである。しかしながら本発明は、一般に、バルク基材に伝達される機械的力に対する前面に加わる機械的刺激の影響を遮断することが望まれるあらゆる微細加工構造体に関するものであると理解されるべきである。

**【0046】**

更に、好ましい実施形態を参照しながら本発明を説明してきたが、本発明の範囲から逸脱することなく、様々な変更を行い得ること、及び本発明の要素を均等物と置き換えることは当業者には理解されるであろう。更に、本発明の本質的な範囲から逸脱することなく、本発明の教示に対して特定の状況に適応させるよう多くの変更を加えることが可能である。従って本発明は、該本発明を実施するための最良の形態として開示された特定の実施形態に限定されるものではなく、添付の請求項の範囲に包含される全ての実施形態を含むものと理解されるべきである。

**【図面の簡単な説明】**

**【0047】**

【図1】典型的なcMUTセルの断面図。

【図2】上面電極及び下面電極をそれぞれ互いに配線した7個の六角形状cMUTセルで形成された「デイジー」素子を示す図。

【図3】上面電極及び下面電極をそれぞれ互いに配線した19個の六角形状cMUTセルで形成された「六角形状」素子を示す図。

**【図4】**本発明の一実施形態によるcMUTセルアレイの一部分の断面図。

**【図5】**本発明の別の実施形態によるcMUTセルアレイの一部分の断面図。

**【図6】**本発明の更に別の実施形態によるcMUTセルアレイの一部分の断面図。

10

20

30

40

50

【図7】本発明の第4の実施形態によるcMUTセルアレイの一部分の断面図。

【図8】図7に示す実施形態による隣接するcMUT素子の一部分の断面図。

【図9】本明細書に開示されたコンプライアントcMUT膜支持構造体のいずれかを組み込むことができる微細加工構造体の様々な層を示す図。

【符号の説明】

【0048】

2 典型的なMUTトランスデューサセル

4 基材

6 絶縁支持体

8 膜又はダイアフラム

10 10 基材4上の電極、下面電極、

12 膜8上の電極、上面電極

20 キャビティ

10

【図1】

FIG.1

【図2】

FIG.2

【図3】

FIG.3

【図4】

FIG.4

【図5】

【図6】

FIG.6

FIG.5

【図7】

【図8】

【図9】

FIG.9

---

フロントページの続き

(72)発明者 ダグラス・グレン・ワイルズ

アメリカ合衆国、ニューヨーク州、ボールストン・レイク、グレーテル・テラス、52番

審査官 太田 良隆

(56)参考文献 国際公開第01/097559 (WO, A2)

国際公開第01/097562 (WO, A2)

特表平09-500247 (JP, A)

国際公開第03/031321 (WO, A2)

特開2003-005102 (JP, A)

米国特許第6025951 (US, A)

国際公開第02/005413 (WO, A2)

米国特許第6329738 (US, B1)

国際公開第02/015636 (WO, A2)

(58)調査した分野(Int.Cl., DB名)

B81B1/00 - 7/04

B81C1/00 - 99/00

B06B1/00 - 3/04

H04R19/00