(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3956242号

(P3956242)

(45) 発行日 平成19年8月8日(2007.8.8)

(24) 登録日 平成19年5月18日(2007.5.18)

(51) Int.C1.

F 1

HO 4 N 1/028 (2006.01)

HO 4 N 1/028

A

請求項の数 5 (全 26 頁)

(21) 出願番号 特願平9-828

(22) 出願日 平成9年1月7日(1997.1.7)

(65) 公開番号 特開平10-136149

(43) 公開日 平成10年5月22日(1998.5.22)

審査請求日 平成15年12月26日(2003.12.26)

(31) 優先権主張番号 591076

(32) 優先日 平成8年1月25日(1996.1.25)

(33) 優先権主張国 米国(US)

(73) 特許権者 506076606

アバゴ・テクノロジーズ・ジェネラル・ア

イピー(シンガポール)プライベート・リ

ミテッド

シンガポール国シンガポール768923

, イーシュン・アベニュー・7・ナンバー

1

(74) 代理人 100087642

弁理士 古谷 聰

(74) 代理人 100076680

弁理士 溝部 孝彦

(74) 代理人 100121061

弁理士 西山 清春

最終頁に続く

(54) 【発明の名称】受光装置信号に対するオフセット除去及び空間周波数帯域フィルタリング回路及び方法

## (57) 【特許請求の範囲】

## 【請求項1】

読み出し動作及びリセット動作の間で周期的に切り替えられる差動回路(46)にオフセット補正を提供する方法において、前記差動回路は、第1及び第2の回路入力(74及び76)と、前記回路入力における電圧状態に応答する出力電圧状態を有する回路出力(108)とを含み、前記方法は、少なくともいくつかの前記リセット動作に対して実行され、

前記差動回路が読み出し動作からリセット動作に切り替えられる時に、前記第1の回路入力を前記第2の回路入力に接続するステップ(78、80、82、及び84)と、

前記差動回路が前記読み出し動作から前記リセット動作に切り替えられる時に、前記回路出力を固定電圧状態である電源(114)に接続するステップ(116)と、

前記リセット動作の第1の時間セグメントに続いて前記電源から前記回路出力を切断するステップ(116)であって、それにより、前記回路の出力が前記固定電圧状態から自由に浮動する、前記リセット動作の第2の時間セグメントを開始することからなるステップと、

前記電源から前記回路出力を切断して前記第2の時間セグメントを開始する時の前記回路出力における電圧状態のシフトに応答して、オフセット補正信号を形成するステップ(136)

を含む方法。

## 【請求項2】

10

20

前記電源(114)から、前記回路出力(108)を切斷する前記ステップ(116)と、前記オフセット補正信号を形成する前記ステップ(136)は、前記リセット動作の一部のみに対して実行され、

前記方法は、前記リセット動作中に決定された前記オフセット補正信号を電気的に格納するステップ(156、158、及び160)と、その格納された前記オフセット補正信号を前記読み出し動作中に前記差動回路(46)に提供するステップとを更に含むことからなる、請求項1の方法。

【請求項3】

前記回路出力(108)を電源(114)に接続する前記ステップ(116)は、前記回路出力を正電圧の電源に接続するステップである、請求項1又は2の方法。

10

【請求項4】

前記オフセット補正信号を形成する前記ステップ(136)は、前記電源(114)の前記固定電圧状態を前記第2の時間セグメント中に、前記回路出力(108)における前記電圧状態と比較するステップを含む、請求項1乃至3のいずれかの方法。

【請求項5】

前記第1の回路入力(74)を前記第2の回路入力(76)に接続する前記ステップ(78、80、82、及び84)は、前記第1及び第2の回路入力を固定電圧である第2の電源(88)に接続するステップである、請求項1乃至4のいずれかの方法。

【発明の詳細な説明】

【0001】

20

【発明の属する技術分野】

本発明は、一般に、信号転送回路に関し、とりわけ、受光装置アレイからの個々の信号を計算回路に転送するための回路構成に関する。

【0002】

【従来の技術】

さまざまな用途において、ある表面を横切る装置経路を正確に判定することが重要である。例えば、走査原稿の画像の忠実な再現を獲得すべき場合、原稿に沿った走査装置の走行に関する正確な情報がなければならない。一般に、スキャナによって得られる捕捉画像は、デジタル・フォーマットでメモリに記憶される画素データ列である。歪みのない画像には、画素データ列への原稿画像の忠実なマッピングが必要とされる。

30

【0003】

本発明の譲受人に譲渡された、ErteI他に対する米国特許第5,149,980号に記載されているところでは、相互関関数を用いて、所定の方向への原稿と光電素子アレイとの間の相対移動が判定される。該特許に言及されているところによれば、1次元手法を拡張して、原稿と光電素子アレイとの間の2次元相対移動を判定し、それにより、2次元平面における並進、回転、及び変倍が追跡可能となる。

【0004】

ErteI他に対する特許に記載されているところによれば、光センサ・アレイを用いて、原稿のある形態の「識別特性」が収集される。この識別特性は、原稿の表面質感または他の光学特徴を照射して、画像形成することによって得ることができる。光強度は、表面質感の変化に伴いピクセル毎に変動する。原稿の表面の相互関画像によって、アレイと原稿との間の相対移動を突き止めることができる。

40

【0005】

【発明が解決しようとする課題】

ErteI他によって解説されているようなシステムの設計に関する厳密な要素は、原稿の識別特性を確実に判定するのに十分な高レベルに、各光電素子のS/N比を維持する回路である。信号が、白紙の紙質のわずかな変化の結果として、画素から画素への反射率の差である場合、反射率の変化は、約6パーセントになる可能性がある。サンプル速度目標、及び可能性のある後続の信号平均化量を考慮すると、有効な情報を得ようとすれば、信号におけるノイズ条件は、紙反射率変動信号の6パーセント未満でなければならない。

50

## 【0006】

従って、ノイズは、受光装置アレイにおける光電素子からの信号に処理を加えるまでの問題の1つである。別の問題は、製造段階で導入される、処理回路の性能のばらつきである。電気的に並列な転送回路の性能がばらつくと、ある画素から他の画素への反射率の差の計算に頼る動作は、エラーを被りやすい。理想的には、信号転送回路の性能のばらつきに起因した画素間の信号差がなく、そのため、画素信号間の差が、光電素子における受光の差だけに帰属する。しかし、回路デバイスには、そのデバイスが、同じ製造プロセスによって形成された場合であっても、性能にばらつきがある。

## 【0007】

更に他の問題には、画素の1つ近傍における画素間では一貫しているが、画素近傍同志の間では異なるような、画像に影響を及ぼす考慮事項が存在する場合に、画像形成される表面に関する有効な情報を確実に得ることが含まれる。例えば、照射光学装置によって、画像形成すべき表面の、近傍間における照度変動を一貫させることができる。不均一な照度は、人為物を生じさせることになる。一貫した局所的パターンの他の例として、光電素子アレイの一部が、暗い背景を有する表面領域に向けられており、一方、光電素子の残りの部分は、表面の陰影のない領域に向けられているパターンがある。

## 【0008】

従って、本発明の目的は、製造段階で導入されるデバイスのばらつきにより、また光電素子信号の多数画素パターン発生及び/又は処理により生じるエラーに対する感受性を低減した、受光装置配列に接続するための転送回路を提供することである。

## 【0009】

## 【課題を解決するための手段】

上記目的は、本発明の1つの実施例の場合、周期的オフセット補正を受けて、転送増幅器間における性能の差に対して信号処理の感受性を低減する、並列転送増幅器を含む、光電素子アレイから計算回路に信号を転送するための回路及び方法により達成される。

## 【0010】

上記目的は、本発明の他の実施例の場合、光電素子アレイにおける光受信の多数光電素子パターンのような人為物の影響を抑制する空間周波数帯域フィルタリング増幅器を含む、信号転送回路によって達成される。

## 【0011】

以下の開示において、「DC除去」という用語は、空間周波数帯域フィルタリングを表すための簡略用語として用いられる。ここで理解されたいのは、本明細書で用いるような「DC除去」という用語には、DC空間成分の除去だけでなく、低周波数と高周波数の一方または両方における、空間周波数成分の除去も又包含される、ということである。

## 【0012】

転送増幅器レベルにおいて、読み出しモードの場合、各転送増幅器は第1の入力を有し、これは、光電素子で受けた光を表す信号を受信するように接続される。アレイ内の光電素子は、列と行をなすように配列され、特定の列における光電素子は、特定の転送増幅器の第1の入力に順次接続されるが、これは厳密ではない。各転送増幅器は、基準電圧源（例えば、1.75ボルト）に接続される第2の入力を有する。転送増幅器は、差動回路として機能するので、出力は、第1と第2の入力における電圧状態間の差に応答することになる。しかし、読み出し期間の間のリセット期間時には、第1と第2の入力は、両方とも、基準電圧源に接続される。さらに、転送増幅器の出力は、瞬間にリセット電圧源（例えば、3.25ボルト）に接続される。オフセット低減回路が設けられて、出力がリセット電圧源から切断された後に、リセット電圧と出力での電圧状態との間の電圧差の検出に応答して、オフセット調整信号が発生される。このようにして、調整信号を問題となる転送増幅器に加えることによって、その転送増幅器と他の転送増幅器との間における性能差を低減、又は削除することが可能になる。

## 【0013】

オフセット調整型の転送増幅器の利点は、デバイス間のばらつき及び $1/f$ ノイズの影響

10

20

30

40

50

が考慮されるという点にある。アレイ全体を読み出すためのサイクル時間は、 $50 \mu s$  程度である。高回路密度と共に低電力動作を達成するためには、CMOS回路が望ましいが、仮に  $1/f$  ノイズが抑制されないとすれば、こうしたノイズによって、増幅器の出力に大幅な揺らぎを生じる可能性がある。本発明の他の利点は、各転送増幅器には、オフセット調整信号を格納するサンプル／ホールド構成が含まれているため、各転送増幅器に必要なのは、周期的にリフレッシュされることだけとなる点にある。従って、オフセット調整信号を決める单一回路を全ての転送増幅器に用いることが可能になる。光電素子信号読み出し間における期間を延長することなく、周期的なリフレッシュを実現するタイミング・シーケンスが規定される。

## 【0014】

各転送増幅器には、サンプル／ホールド構成が含まれているので、転送増幅器は3つの動作モードを備えている。読み出しモードの場合、第2の入力が基準電圧源に接続され、一方、第1の入力が光電素子に接続される。結果として、電荷が、動作上関連する積分コンデンサに転送される。増幅器出力電圧は、次いで、下流の処理回路に供給される。内部のサンプル／ホールド構成によって、オフセット補正が施される。第2の動作モードは、受動リセット・モードである。オフセット調整信号が更新されないので、このリセットは「受動」である。第1の能動オフセット調整動作が実行されるまで、受動リセット・モードは低品質である。受動リセット・モードの場合、転送増幅器の2つの入力が互いに接続され、その出力は、リセット電圧源に接続されたままである。第3の動作モードは、能動リセット・モードである。受動リセット・モードのように、転送増幅器の2つの入力が基準電圧源に接続される。しかし、その出力は、瞬間にリセット電圧源に接続されるだけである。出力は、切斷されると、オフセット調整回路に接続され、適正なオフセット調整信号が決定されて、次の能動リセット動作まで、サンプル／ホールド構成によって記憶される。

## 【0015】

オフセット調整信号の周期的更新の間に、各転送増幅器は、交互に読み出しモードと受動リセット・モードになる。 $1/f$  オフセット・ドリフト成分は、十分に低速のため、光電素子アレイの各8番目の読み出し後の更新でも、十分な速度である。

## 【0016】

前記のように、本発明には、多数光電素子光パターン、及び他の人為物を抑制するDC除去増幅器も含まれている。DC除去増幅器によって、転送増幅器の出力から、低周波数と高周波数の両方の空間周波数成分が除去される。DC除去増幅器と転送増幅器は、1対1の対応とすることができます。各DC除去増幅器には、特定の光電素子から問題となる信号を受信するように接続された、一次入力が含まれている。各DC除去増幅器には、特定の光電素子に近接した光電素子から出力信号を受信するように接続された、少なくとも1つの二次入力も含まれている。要するに、二次入力の平均化が行われて、結果得られる平均値が一次入力から減算される。DC除去増幅器は、低空間周波数成分を除去する以外に、画素間隔の2倍に相当する周波数において固有の低域通過特性を備えている。従って、DC除去増幅器は、本質的に帯域通過特性を備えている。帯域通過特性の固有の低域通過要素は、平均化の前に、二次入力を異なる重み係数で乗算することによって修正することができる。重み係数は、正または負の数となり得る。

## 【0017】

DC除去増幅器は、第1と第2の差動セルから形成され、第2の差動セルは、その出力からその入力への負帰還ループを備えている。第2の差動セルは又、下流の差動動作を容易にする中間範囲の電圧を確立するために、DC入力も備える。本発明にとって不可欠ではないが、DC除去増幅器が、オフセット補正を含むこともでき、またスイッチング・ネットワークを含むこともでき、これによりユーザが、入力をDC除去増幅器に切り換えたり、又は増幅器の動作をテスト・モードに設定したりすることが可能となる。

## 【0018】

## 【発明の実施の形態】

10

20

30

40

50

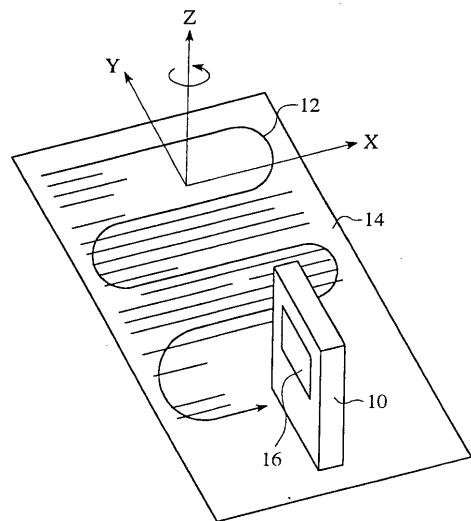

図1を参照すると、原稿14に沿った曲がりくねった経路12を辿った、携帯用手持ち式走査装置10が示されている。原稿は、1枚の紙とすることもできるが、本発明は、他の画像を保持する基体に用いることもできる。手持ち式走査装置を利用する場合、紙の纖維といった固有の構造特徴の位置を追跡して、結果得られる位置情報をを利用して、画像データを修正することができる。しかしながら、本発明は、他の用途でも利用することができる。

#### 【0019】

走査装置10は、自立式で、バッテリで動作することが望ましい。しかし、該装置には、外部電源、あるいは、コンピュータ又はネットワークのデータ・ポートに対する接続部を含めることもできる。この走査装置には、画像ディスプレイ16が含まれている。該ディスプレイによって、捕捉した画像をほぼ瞬時に見ることが可能になる。ただしディスプレイは、不可欠ではない。

#### 【0020】

走査装置10は、3つの自由度を可能にし、その2つは並進であり、1つは回転である。第1の自由度は、原稿14に沿った横への移動(X軸移動)である。第2の自由度は、原稿に沿った上下方向の移動(Y軸移動)である。第3の自由度は、原稿14のエッジに対して、画像センサ素子の線形アレイが回転不整合(Z軸移動の結果としての不整合)となるように、該装置を動作させる能力である。すなわち、必ずしも画像形成素子の線形アレイを装置の並進方向と垂直に維持する必要はない。

#### 【0021】

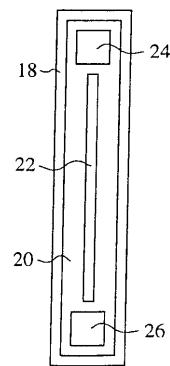

次に、図1及び2を参照すると、走査装置10の底側18には、原稿14と撮像センサ22の間の適切な接触を維持する際に手助けとなる、枢動部材20が含まれている。航行センサ24及び26が、撮像センサの対向端に配置されている。航行センサは枢動部材に装着されているので、航行センサは撮像センサに対して固定位置にある。

#### 【0022】

物理的に小型化するために、撮像センサ22は、接触式の画像形成装置が望ましいが、小型化がそれほど問題でない、又は更に小さい画像が所望される用途の場合、投射光学装置を用いたセンサを使用することもでき、これは倍率が1未満である。接触式の画像形成装置は、一般に、日本板硝子社の米国連邦登録商標であるSELFOCの商標名で販売されているレンズを使用する。あまり慣用的ではないが、結像レンズを用いずに、光源のインターリープ型アレイ素子と近接センサを利用して、接触式の画像形成をなすことが可能である。走査用途のための慣用的な撮像センサを用いることもできる。撮像センサは、やはり照明光源、照明光学装置、及び像伝送光学装置を含む1つのユニットの一部とすることもできる。

#### 【0023】

図1には、4つと何分の1かの帯状部分、すなわち原稿14を横切る側方パスからなる、曲がりくねった経路12が示されている。大部分の用途にとって有効な撮像センサ22は、25mm~100mmの範囲内の長さを有する。帯状部分には、重複した領域が含まれるべきであり、その結果、ステッチ・プロセスを利用して、被走査原稿の忠実な再現を得ることができる。

#### 【0024】

##### 航行センサ

走査装置10には、少なくとも1つの航行センサ24又は26が含まれている。好適な実施例の場合、該装置には、1対の航行センサが含まれ、これらのセンサは、撮像センサ22の対向端に配置される。互いに直交して装着される光電素子の1次元アレイを利用することができるが、更に好適な実施例の場合、各航行センサは、光電素子の2次元アレイである。航行センサ24及び26を用いて、原稿に対する走査装置10の移動が追跡される。

#### 【0025】

各航行センサは、読み出し及び信号処理回路を含む集積回路基板に形成される、光電素子

10

20

30

40

50

のアレイである。40 μmの画素距離の範囲にわたって必要な位置精度は、2.0 μmである。非常に高い位置精度には、素子間で十分に異なる信号を獲得するために、長さ数十ミクロン以下の個別の光電素子が必要になる。好適な実施例の場合、紙の原稿14上で所望される画素サイズは、40 μmであり、画像形成光学装置によって、1.5の倍率が得られるので、航行センサ24及び26の受光素子は、60 μm × 60 μmになる。光学倍率が大きくなると、より大きい画素の利用が可能になる。しかし、必要とされるシリコンの総面積、従って、アレイのコストを最小限に抑えるためには、性能目標に合うように、画素サイズをできるだけ小さく保つことが望ましい。各航行センサは、64個の列と32個の行を備えたアレイとすることができます。しかし、これらの数字のどれも、本発明にとって重要なものではない。

10

#### 【0026】

航行センサ24及び26の動作時、所望の信号は、原稿14の表面に沿った変化によって生じる、画素間の反射率の差である。表面変化が、白紙に沿った紙質の変化である場合、反射率は、白紙の基本反射率の約6パーセントだけしか変動しない。従って、以下で説明するような回路は、ノイズを最小限に抑え、電圧安定性を確保するように設計しなければならない。

#### 【0027】

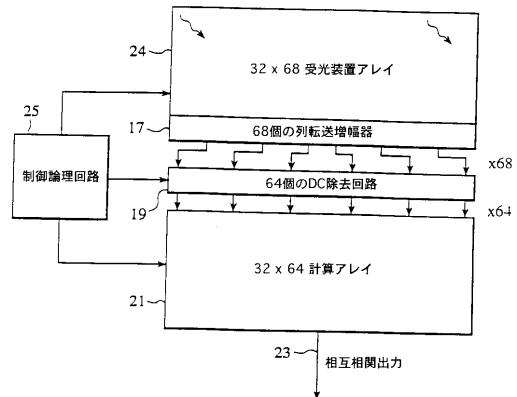

図3は、単一の集積回路チップに形成される回路のブロック図である。このチップは、2次元画像を捕捉して処理を施し、それにより不図示の外部コントローラに相互関情報と供給するように設計された、アナログ信号処理チップである。上記の実施例の場合、コントローラは、画像相互関値を用いて、X-Y位置情報を導出する。次に、X-Y位置情報を用いて、図2の撮像センサ22を利用して収集した画像データから、線形画像が正確に再構成される。

20

#### 【0028】

図3の実施例の場合、航行センサ24は、32個の行と68個の列を光電素子を備えたアレイである。アレイをなす68個の列転送増幅器17によって、航行センサ24から、アレイをなす64個のDC除去回路19に、行から行へというように信号が転送される。低コストの画像捕捉システムの場合、撮像すべき全体領域にわたって完全に一定した光強度で、目標領域を照射するのは困難である。均一な照射を行う能力は、光学装置及び光源のコストに比例する場合が多い。さらに、慣用的な集積型光センサのセル毎の較正がなければ、集積回路処理技術の制限の結果として、ある程度の感度のばらつきが生じることになる。図3のアナログ信号処理チップが用いられる航行システムの場合、入射画像と、撮像アレイに対して異なる位置で以前に捕捉された画像との間で、相互関を計算する必要がある。照度及び光電素子感度にばらつきがあると、相関信号が劣化することになる。従って、図3の空間DC除去回路19は、相関信号の完全性を維持し、同時に、システムのコストを比較的低く抑えるように設計されている。別様であれば相関信号を損なうことになる、照度及び光電素子感度における低い空間周波数の変化が、航行画像から除去される。さらに、DC除去回路には、固有の低域通過特性も備わっている。計算アレイ21は、DC除去回路19からデータを受信し、該データの局所的な差分計算を実施した後、チップ内蔵でないコントローラに相互関出力23を転送する。また、図3には、チップの各種構成要素のための制御論理の供給源25も示されている。

30

#### 【0029】

##### 光電素子回路

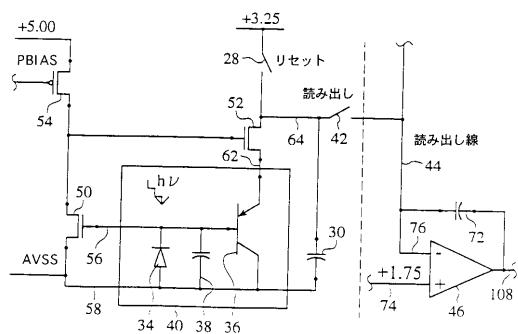

図4は、光電素子回路の概略図である。図5は、光電素子対の更に詳細な回路図である。入射光は、サンプル期間中に積分される電流へと変換される。記憶値は、処理シーケンスにおける次のステップに利用することができるよう、周期的に読み出される。積分サイクルの開始時に、図4におけるリセット・スイッチ28が「オン」になり、瞬間に積分コンデンサ30を3.25ボルトにリセットする。図5に示すように、リセット・スイッチ28は、pチャネル・トランジスタであり、第1のリセット線32を介してトランジスタのゲートに論理低を加えることによって「オン」となる。フォトダイオード34によっ

40

50

て発生する光電流は、P N Pトランジスタ3 6によって増幅される。フォトダイオード及びトランジスタは、寄生容量3 8と共に、光電素子4 0を規定する。増幅された光電流は、トランジスタ5 2を介して、1 . 7 5ボルトのレベルに向かう下方へと積分コンデンサ3 0を充電する。サンプル期間の終了時には、読み出しスイッチ4 2が「オン」になり、記憶値が、読み出し線4 4に沿って転送増幅器4 6に出力される。図5に示すように、読み出しスイッチは、nチャネル・トランジスタであり、読み出し制御線4 8によって制御される。

#### 【0030】

光電素子4 0のフォトダイオード3 4は、光子の受容に応答して電流を発生する。フォトダイオードは、P N Pトランジスタ3 6のベースに接続されている。フォトダイオードは、トランジスタがフォトトランジスタになるように、トランジスタのベース／コレクタ部分とすることができる。逆バイアスのダイオードは、0 . 1 6 p Fである寄生容量3 8を有する。3 2 × 6 8の光電素子アレイがある上記の実施例の場合、フォトダイオードにおける光電力は、1 . 1 n Wに決定されている。この結果、ダイオード電流源に0 . 6 n Aの電流が生じることになる。電流レベルが低いので増幅が必要になるが、これは、表面質感が、関心事の画像である用途の場合に、ベース光電流の約6パーセントにしかすぎない光変動信号によって、ノイズと区別するのに十分な電圧差が生成されるのを保証するためである。

#### 【0031】

光電素子4 0のP N Pトランジスタ3 6によって、光電流が増幅される。トランジスタによって増幅されると、積分コンデンサの利用が可能になり、光電素子間の再現性が促進される。増幅されなければ、フォトダイオード3 4からの小電流で、2ボルトの振れ幅を得るためにには、積分器として、例えば1 0 f Fといった極めて小さいコンデンサが必要になる。これは、寄生容量のため、素子毎に再現するのが困難であろう。ダイオードから基板P N Pデバイスに光電素子のレイアウトを変更するのが、電流を増幅させるのに好都合な方法である。1 8の電流増幅率値によって、出力エミッタ電流が1 1 . 4 n Aに増大される。従って、0 . 2 0 p Fの積分コンデンサを用いることが可能になる。これにより、再現性が促進されるが、余分な領域を必要とするほど大きくはならない。

#### 【0032】

図4の回路に関する問題は、電流増幅率従属性が、直接的に出力電流の決定に、従って積分コンデンサ電圧の決定に係わることである。しかし、テストの結果明らかになつたのは、ユニット間におけるデバイスの整合が良好であるため、電流増幅率従属性の影響は微小であった。

#### 【0033】

サーボ回路が、3つのM O Sトランジスタ5 0、5 2、及び5 4によって形成される。3つのM O Sトランジスタは、フォトトランジスタ3 6の出力用の共通ゲート段5 2を備えた増幅器を形成する。光電素子4 0に発生した電流を積分コンデンサ3 0に適正に転送できるようにするため、フォトダイオードの逆電圧（すなわち、トランジスタのベース電圧）は、ほぼ一定のレベルに保たれなければならない。ベース・ノード5 6における電圧のシフトが可能になると、光電流は、基板P N Pトランジスタ3 6によって増幅される電流を供給するのではなく、ダイオードの寄生容量3 8、又はトランジスタのベース・コレクタ容量を充電及び放電する際に、少なくとも部分的に消費されることになる。

#### 【0034】

ノード5 6におけるトランジスタ・ベース電圧は、3つのトランジスタ5 0、5 2、及、5 4によってほぼ一定のレベルに保たれる。所望の動作を実現するのに不可欠ではないが、図4及び5の実施例の場合、実質的に一定の電圧レベルは、コレクタ・ノード5 8でのA V S Sを超えるN M O Sしきい値レベルにほぼ等しい。3つのM O Sトランジスタは、P N Pトランジスタのエミッタ・ノード6 2に対するソース・フォロワとして機能するトランジスタ5 2によって、負帰還ループとして動作する。従って、ベース電圧は、トランジスタのエミッタ電圧によって制御される。これが可能な理由は、ベース電圧、すなわち

10

20

30

40

50

コンデンサ 3 0 におけるフォトダイオード出力が、非常に高いインピーダンス・レベルを有するためである。トランジスタ 5 2 は、共通ゲート段として機能し、これには追加の利点として、PHTO1 ノード 6 4 の電圧揺動から、トランジスタのエミッタ・ノード 6 2 とベース・ノード 5 6 をさらに分離する、という利点がある。

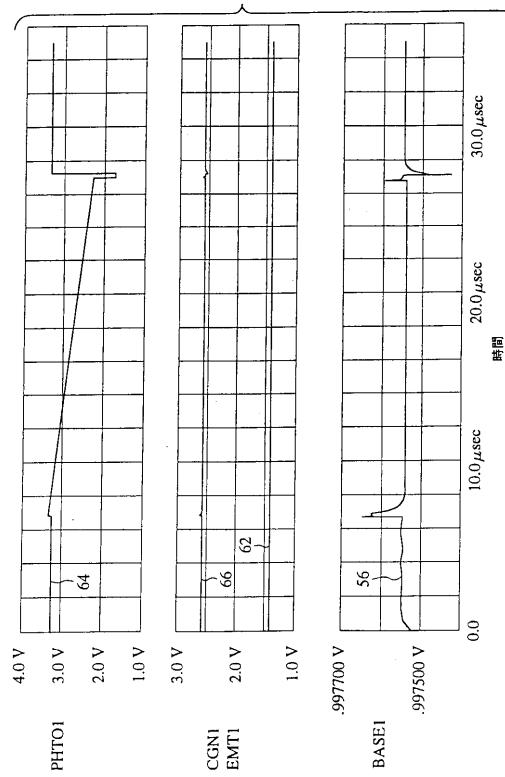

#### 【0035】

次に、図 4、5、及び 6 を参照すると、リセット期間の間、PHTO1 ノード 6 4 における出力電圧は、リセット・スイッチング・トランジスタ 2 8 によって 3.25 ボルト、すなわち VBB 1 に保持される。スイッチング・トランジスタを電気的に「オン」にすると、CGN1 ノード 6 6 は、約 2.6 ボルトに保持され、エミッタ・ノード 6 2 は、約 1.4 ボルトに保持される。ノード 5 6 におけるベース電圧は、1.0 ボルトに近い。

10

#### 【0036】

問題となる媒体を照射する光源が「オン」になると、約 0.6 nA の光電流が、トランジスタ 3 6 のベースから AVSS に接続されたコレクタ・ノード 5 8 に流れる。図 6 のタイミング・シーケンスの開始から 7.0 μs の時点において、第 1 のリセット線 3 2、すなわち RST1B におけるリセット信号が論理的に高に移行され、それにより、リセット・スイッチ 2 8 が「オフ」になる。結果として、フォトトランジスタ 3 6 のエミッタ電流が、第 2 の n チャネル・トランジスタ 7 0 と並列の第 1 の n チャネル・トランジスタ 6 8 のゲート・チャネル間容量によって形成される容量構造から引き出されるにつれて、PHTO1 ノード 6 4 の出力が、直線的にランプ状で低下する。図 5 のトランジスタ 6 8 及び 7 0 は、図 4 における積分コンデンサ 3 0 によって表される。問題となる電圧の範囲は、3.25 ボルト ~ 1.75 ボルトである。従って、第 1 と第 2 の n チャネル・トランジスタ 6 8 及び 7 0 のゲートは、デバイスのゲート・チャネル間容量が、デバイスのしきい値レベルを超えるのに十分高く保持される。

20

#### 【0037】

リセット・スイッチ 2 8 が「オフ」である積分時間中、エミッタ・ノード 6 2 とベース・ノード 5 6 における電圧は、上述の負帰還ループによって安定化された状態のままである。ベース・ノードの電圧は、約 2 mV の範囲内にとどまる。

#### 【0038】

このシミュレーション実行のため、積分時間の約 20 マイクロ秒後に、読み出し制御線 4 8 によって、正に向かうゲート・パルスがトランジスタ 4 2 に加えられて、読み出しスイッチ 4 2 が「オン」になる。正のゲート・パルスは、約 200 n s 間持続する。転送増幅器 4 6 の動作によって、PHTO1 ノード 6 4 が 1.75 ボルトに引き下げられる。これにより、転送増幅器において図 4 の積分コンデンサ 3 0 からコンデンサ 7 2 への信号の転送が実現する。転送プロセスが終結すると、読み出し制御線 4 8 は論理低に戻され、第 1 のリセット・線 3 2 も論理低になる。これにより、リセット・スイッチ 2 8 が「オン」になり、PHTO1 ノード 6 4 が引き上げられて、3.25 ボルトに戻される。

30

#### 【0039】

##### 電荷転送

図 4 を参照して、特定の列転送増幅器 4 6 の基本動作について説明する。転送増幅器が読み出しモードにない場合、読み出し線 4 4 は、増幅器の第 2 の入力 7 4 に対して分路される。すなわち、2 つの入力が、1.75 ボルトに保持される。同時に、出力線 108 が、第 2 の定電圧源に接続される。重要ではないが、出力線 108 における電圧は 3.25 ボルトである。積分コンデンサ 3 0 も、リセット・スイッチ 2 8 によって 3.25 ボルトに接続される。

40

#### 【0040】

図 4 及び 5 を参照すると、リセット・スイッチ 2 8 が開放されると、積分コンデンサ 3 0 における電荷が、光電素子 4 0 において発生する光電流に依存して変動することになる。約 40 μs の積分期間の後、転送増幅器の第 1 の入力線 7 6 と出力線 108 が、それぞれ、1.75 ボルトと 3.25 ボルトの定電圧源から切離される。読み出しスイッチ 4 2 を「オン」にして、積分コンデンサ 3 0 を第 1 の入力線 7 6 に接続すると、正の摂動が、転

50

送増幅器の第1の入力線において受信される。増幅器の出力は負に移行し、それにより電荷が、転送コンデンサ72を介して読み出し線44から引き出され、電圧値が1.75ボルトに戻される。これは、増幅器の利得によって生じる。電荷は保存されるので、積分コンデンサ30を、その最終積分値から第2の入力線74の電位、すなわち1.75ボルトにするのに必要な電荷量が、積分コンデンサ30から転送コンデンサ72に引き出される。積分及び電荷転送の動作を左右する式は、次の通りである。

#### 【0041】

$$\text{out} = V_{\text{out}} - [ (V_{\text{cap}} - I_{\text{ph}} ( + 1 ) T_{\text{int}} / C_{\text{int}} ) - V_{\text{bott}} ] C_{\text{int}} / C_{\text{tran}}$$

ここで、outは、転送動作の終了時における転送増幅器の出力電圧であり、 $V_{\text{out}}$ は、出力線108における開始電圧（すなわち、3.25ボルト）であり、 $V_{\text{cap}}$ は、積分コンデンサ用の開始電圧（すなわち、3.25ボルト）であり、 $I_{\text{ph}}$ は、フォトダイオード電流（すなわち、0.6nA）であり、 $\alpha$ は、フォトトランジスタ36の電流増幅率（すなわち18）であり、 $T_{\text{int}}$ は、受光装置のための積分時間（すなわち、40μs）であり、 $C_{\text{int}}$ は、積分コンデンサの値（すなわち、0.2pF）であり、 $V_{\text{bott}}$ は、転送増幅器の第2の入力74におけるバイアス値（すなわち、1.75ボルト）であり、 $C_{\text{tran}}$ は、転送コンデンサの値（すなわち、0.4pF）である。

#### 【0042】

前記のように、図3の計算アレイ21の演算は、相関演算である。相関演算の初期部分を考えると、2つの最も近接した光電素子の信号間における差の減算が行われる。データの正確な解釈には、計算アレイに対する入力信号が、受光装置アレイ24の様々な光電素子で受ける光の照度の差に強く依存することが必要になる。従って、デバイスの製造段階での差に起因するデバイスの不整合によって、精度が悪くなる。さらに、光電素子の積分時間が40μsであり、アレイ全体の読み出しには、50μs程度のサイクル時間を要する。高い回路密度と共に小電力動作を実現するには、CMOS回路が望ましいので、1/fノイズも問題になる。解析によって、転送増幅器46のオフセットにおけるドリフトが、この時間フレーム中に生じやすいことが明らかになった。従って、列転送増幅器の全てを実質的に同じオフセット値に整合させるメカニズムによって、後続の処理動作を更に正確にすることが可能になる。結果として、以下で説明するが、オフセット制御動作がもたらされる。

#### 【0043】

##### オフセット補償

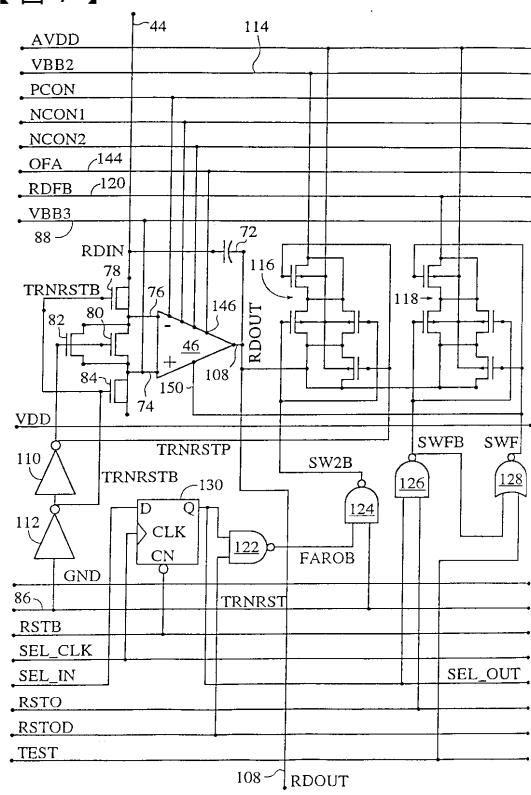

次に図7を参照すると、列転送増幅器46が示されており、これは、4つのトランジスタ素子78、80、82、及び84によって、選択的に共に分路される第1の入力74と第2の入力76を備える。これらのトランジスタのうちの2つはスイッチとして機能し、一方、他の2つは、ある程度の電荷注入補償を与える。トランジスタ素子のスイッチングは、TRNRST線86における信号によって制御される。線86上の信号が論理高の場合、入力74及び76は、両方とも、VBB3線88を介して定電圧源に接続される。上例の場合、VBB3電圧は、1.75ボルトである。インバータ110及び112が、トランジスタ78-84に適正な信号レベルを供給する。

#### 【0044】

列転送増幅器46が読み出し動作間にある場合、線86上の信号によって、転送増幅器はリセット・モードになる。転送リセット信号によって、入力74及び76が共に接続され、同時に、出力線108が線114を介してVBB2の電源に接続される。4つのトランジスタ素子からなる第2のバンク116が、出力線108とVBB2の電源を接続又は切断するために、TRNRST線86上の転送リセット信号によって制御される。上記の実施例の場合、VBB2電圧は3.25ボルトである。入力電圧及び出力電圧の選択によって、出力電圧を、後続段のために、動作電源電圧のほぼ中間範囲に中心決めすることが保証される。トランジスタ素子の第2のバンク116内において、素子のうちの2つは、電荷注入補償を実現するために設けられている。

#### 【0045】

10

20

30

40

50

4つのトランジスタ素子からなる第3のバンク118が、転送増幅器46の出力線108を読み出し帰還線120に選択的に接続するために含まれている。第3のバンク118及び読み出し帰還線120は、オフセット調整ループの一部を形成する。やはり、そのバンク内のトランジスタのうちの2つは、電荷注入補償のためだけに設けられている。複数のゲート122、124、126、及び128と、クロック装置130が、第2のバンク116及び第3のバンク118の適正な動作を与えるように接続される。これらのデバイスは、それぞれ、慣用的な仕方で動作するものであり、当業者には明らかなように、他の慣用的な回路に簡単に置き換えることもできる。

#### 【0046】

転送増幅器46がリセット・モードにある場合、2つの入力74及び76は、トランジスタ78-84の第1のバンクによって、1.75ボルトに接続され、また出力線108は、トランジスタ素子の第2のバンク116によって、一時的に3.25ボルトに接続される。オフセット制御動作中、トランジスタ素子の第3のバンク118は、第2のバンク116が「オフ」なった後、出力線を読み出し帰還線120に接続する。次に、図8を参照すると、複雑さを軽減するため、図7の回路構成が、單一ブロック132に簡略化されている。また、ブロック形式で示されるのは、電圧源134であり、この目的は、回路を動作させるのに必要な各種のバイアス及びリセット電圧のためである。最後に、図8には、オフセット調整増幅器136が示され、これは、VBB2線114に接続された第1のノード138と、帰還線120に接続された第2のノード140とを有する。

#### 【0047】

オフセット調整増幅器136は、図3の受光装置アレイ24の列転送増幅器17の全てに共通している。しかし、図8の第2のノード140は、所定時間に1つの転送増幅器だけに接続される。実際、68個の列転送増幅器が、同時に読み出しモードになると、第2のノード140は、転送増幅器からのどんな信号受信からも電気的に分離されることになる。

#### 【0048】

オフセット調整増幅器136の動作時、読み出し帰還線120における電圧状態が、VBB2線114における定電圧と比較される。理想の場合には、ノード138及び140における電圧状態は等しくなるため、出力ノード142及びOFA線144における電圧が、公称出力バイアス・レベルになる。しかし、デバイス製造段階でのばらつき、及び他の性能メカニズムによって、オフセットが生じることになる。結果として、ノード138及び140における電圧状態が異なることになり、それによって、OFA線144を介して回路ブロック132に伝達されるオフセット信号が生成される。図7に示すように、線144は、列転送増幅器46に接続されて、転送増幅器のオフセット補償をもたらす。

#### 【0049】

OFA線144は、図7に示すように、オフセット補正ポート146において転送増幅器46に接続される。図9を参照すると、転送増幅器46の内部回路が示されている。図9の回路構成の一部は、慣用的なものであり、当業者には容易に理解されるものである。かかる慣用的な回路については、ここでは説明しない。しかし、慣用的な回路に、オフセット・サンプル／ホールド回路148が追加されており、これは、転送増幅器のオフセット補正ポート146によってアクセスされる。特定の転送増幅器が、図8のオフセット調整増幅器136に接続されるリセット動作が終了すると、サンプル／ホールド回路がリフレッシュされる。転送増幅器のリフレッシュ・ポート150において受信される信号が、オフセット補正ポート146をOFA M線154に接続するための、トランジスタ素子の第4のバンク152を適切にバイアスする。OFA M線154は、1対のトランジスタに通じ、これは、オフセット調整信号用の記憶コンデンサとして機能すべく結合している。第3のトランジスタ160が、オフセット補正信号によってバイアスされて、転送増幅器の慣用的な回路に対してオフセット補償を施す。

#### 【0050】

動作時に、オフセット補正は、転送増幅器46の出力線に始まり、転送増幅器のオフセッ

10

20

30

40

50

ト補正ポート 146まで続くループを形成することによって達成される。図 7 を参照すると、増幅器の第 1 の入力 74、及び第 2 の入力 76 が VBB3（例えば、1.75 ボルト）に接続され、またトランジスタ素子の第 2 のバンク 116 によって、出力線 108 が VBB2（例えば、3.25 ボルト）に接続され、次いで VBB2 から切断されると、オフセット制御動作は、トランジスタ素子の第 3 のバンク 118 によって、出力線 108 を読み出し帰還線 120 に接続することによって開始される。オフセット補正の必要がなければ、読み出し帰還線 120 における電圧状態は VBB2 と等しくなる。次に、図 8 を参照すると、オフセット調整増幅器 136 は、読み出し帰還線 120 における電圧を、予測される電圧状態、すなわち VBB2 電圧と比較する。増幅器 136 は、差動セルであり、オフセット調整線 144 に接続された出力ノード 142 を有する。このオフセット調整線は、図 8 及び 9 に示すように、転送増幅器 46 のオフセット補正ポート 146 に接続することによってループを完成する。リフレッシュ間隔の間、トランジスタ素子の第 4 のバンク 152 が、トランジスタ 156 及び 158 による、オフセット補正ポート 146 における信号の記憶を可能にする。記憶された電荷によって、次のリフレッシュ間隔まで、転送増幅器回路にオフセット補正が与えられる。

10

#### 【0051】

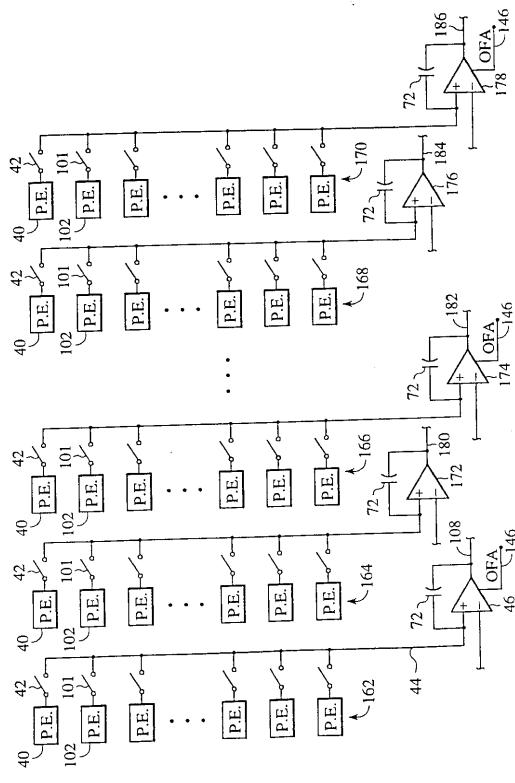

前記のように、各列転送増幅器 46 は、光電素子の特定行内の光電素子に順次接続される。1つの実施例において、光電素子の 68 個の列と 32 個の行が存在する。図 10 には、列のうちの 5つ 162、164、166、168、及び 170 が示されており、その各々は、異なる転送増幅器 46、172、174、176、及び 178 に選択的に接続される。

20

#### 【0052】

図 5 について簡単に言及すると、図 4 の光電素子 40 が、同じ列からの第 2 の光電素子 102 と対をなすように示されている。従って、各光電素子は、読み出しスイッチ 42 及び 101 を「オン」にすることによって、同じ読み出し線 44 に接続される。読み出し制御線 48 及び 90 は、転送増幅器に同時に 2 つの光電素子が接続されることがないように、読み出しスイッチの個々の制御を与える。また、リセット・デバイス 28 及び 92 も示されており、これらは、独立したリセット線 32 及び 94 と、独立した PHTO ノード 64 及び 96 に接続される。第 2 の光電素子には、それ自体の共通ゲート構成が含まれ、これは、第 1 の光電素子 40 の MOS トランジスタ 50、52、及び 54 と同様に動作する、MOS トランジスタ 98、99、及び 100 によって与えられる。最後に、第 2 の光電素子には、第 2 の光電素子ための積分コンデンサの働きをする容量性記憶トランジスタ 104 及び 106 が含まれている。

30

#### 【0053】

図 10 の回路の動作時、各列 162 - 170 における光電素子 40 及び 102 の積分時間は、約  $40 \mu s$  である。積分期間の後に続いて、光電素子 40 の第 1 行の読み出しスイッチ 42 が閉じられ、その結果、各種の転送増幅器 46、172、174、176、及び 178 は、第 1 行の光電素子 40 に当たる光エネルギーに対応する電荷を受ける。受け取った電荷は、出力線 108、180、182、184、及び 186 を介して、後続の処理回路に転送される。単一行の読み出し時間は、 $200 \text{ ns}$  から  $300 \text{ ns}$  の間であると推定される。第 1 行の読み出しに続いて、読み出しスイッチ 42 が開放されて、光電素子 102 の第 2 列の読み出しスイッチ 101 が閉じられる。この行程は、光電素子の各行が読み出されるまで繰り返される。

40

#### 【0054】

上記のオフセット調整動作には、多くて  $4 \mu s$  しか必要としない。従って、少なくとも 8 つの転送増幅器 46 及び 172 - 178 を、転送増幅器が転送動作間の遊休状態になる  $40 \mu s$  の各積分期間毎に、順次的に、図 8 のオフセット調整増幅器 136 に接続することが可能である。図 9 に示すように、各転送増幅器のサンプル / ホールド回路 148 は、トランジスタ 156 及び 158 によって与えられる記憶容量において、ほとんど電圧垂下がないことが保証されるように設計されている。従って、リセットは、光電素子信号の転送

50

に関して時間を犠牲にすることなく発生可能である。

【0055】

D C 除去回路

図3の計算アレイ21を介した光電素子の航行アレイ24からの信号処理における問題には、光電素子の近隣内で共通である特性の結果として、処理が潜在的に損なわれることが伴う。例えば、スキャナは、原稿に対して移動する際に、基体を照射するための光源を備える。照度にばらつきがなく、全視野領域を照射するのは困難である。信号処理は、こうしたばらつきによって悪影響を受ける可能性がある。

【0056】

図3のDC除去回路19は、光電素子の近隣内の低い空間周波数の変動を除去する基本機能を備えている。上記のように、DC除去回路は又、高周波数の空間周波数成分を除去するように設定される、低域通過特性を有する。従って、DC除去回路は、帯域通過特性を有することが可能である。DC除去回路は、原稿画像を局部的差分からなる画像に変換する。局部的差分手法は、結果として原稿画像の破壊を生じることになるが、原稿に対するスキャナの移動を測定するような用途の場合、これは重要ではない。低い空間周波数の除去によって、相関信号の完全性が維持される。さらに、局部的差分手法には、実際に画像相互関を計算する、計算アレイ21のダイナミック・レンジの必要条件を低減するという付加的利点もある。

【0057】

航行センサ24の検分を受ける基体の照度ばらつきの悪影響を克服する以外に、低い空間周波数を除去することによって、走査を受ける原稿の陰影の付いた領域における紙の纖維が、アレイの主たる領域の1つの視界内に入るが、アレイの第2の部分の視界内に入る紙の纖維は、陰影の付いた領域の外側となるように、航行センサが位置決めされるといったことに対して、航行動作が、影響されにくくなる。

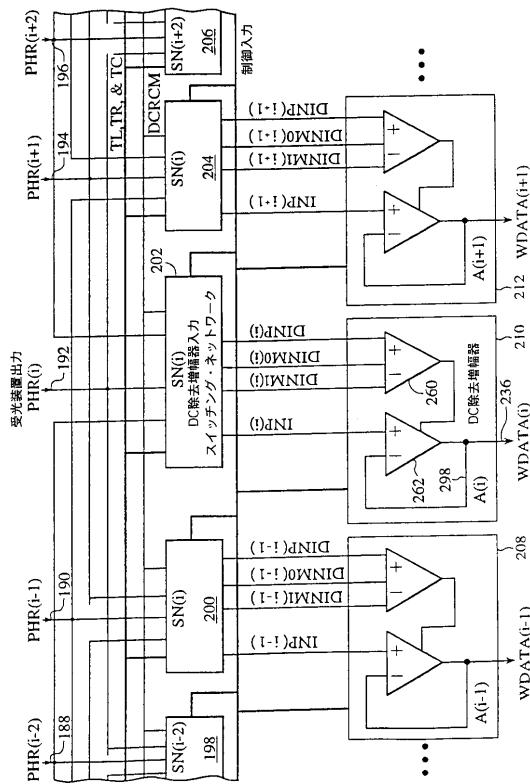

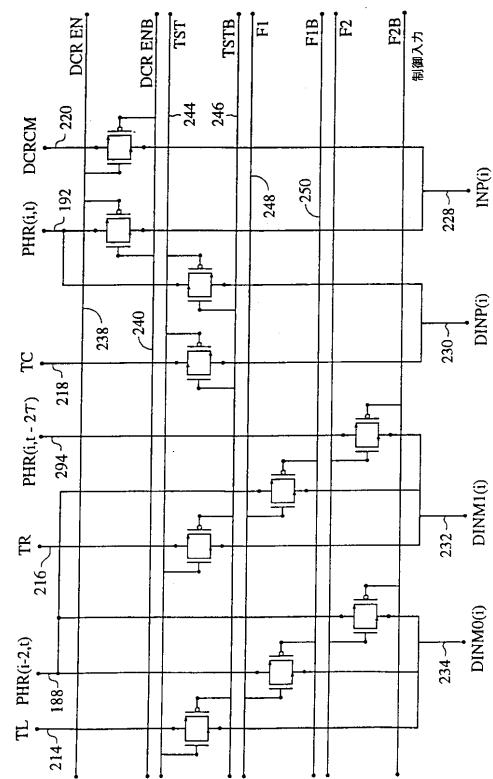

【0058】

列転送増幅器17は、時間多重化方式で行毎に捕捉画像データを転送するので、DC除去は並列処理で行うことができる。図11の場合、5つの異なる列転送増幅器からの5つの受光装置の出力188、190、192、194、及び196が、スイッチング・ネットワーク198、200、202、204、及び206に伝達される。各スイッチング・ネットワークは、図3の制御論理回路25からのデジタル制御入力によって制御される一連のスイッチを介して、その入力にゲート制御を施す。各スイッチング・ネットワーク198-206の出力は、関連するDC除去増幅器208、210、及び212に接続されている。スイッチング・ネットワークに依存して、DC除去回路は、テスト・モード及びDC除去禁止モードを含む多数のモードのうちの任意の1つにすることができる。

【0059】

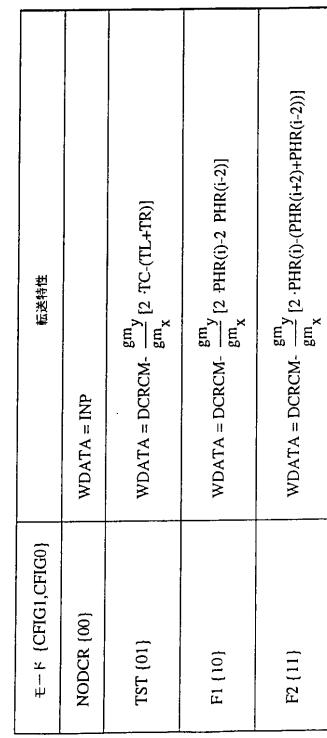

図15について簡単に言及すると、図11のDC除去増幅器210の可能な4つの動作モードの一例が特徴付けられている。NODCR(非DC除去)モードの場合、増幅器210の出力236は、スイッチング・ネットワーク202によって受光装置出力線192に直接接続される、入力INPと同じである。TST(テスト)モードの場合、DC除去増幅器の出力信号は、3つの既知のテスト出力、すなわちTC、TL、及びTRに依存する。

【0060】

F1及びF2のDC除去モードの場合、線192における受光装置の出力PHR(i)の低い空間周波数成分が除去される。以下で詳細に説明するのは、受光装置の出力192から、線188における受光装置の出力を減算する図11の回路の実施例である。DCRCMという用語は、WDATA(i)線236からのアナログ信号の後続の処理を可能にするために、正の中間範囲の電圧値を設定するために選択されたDC値を表している。図15のF2モードは、受光装置出力PHR(i)の両側におけるその受光装置の出力の選択において、F1モードとは異なっている。スイッチング・ネットワーク202は、最も近傍の受光装置には接続されていないので、低周波数情報を除去するためのより広いサンプ

10

20

30

40

50

リング値が収集される。F1及びF2モードにおける「一次入力」は、PHR(i)出力であり、局部的差分は、PH(i+2)及びPHR(i-2)から二次入力を減算することによって得られる。2次元DC除去を可能にする実施例については、以下で図16及び17を参照する際に説明する。

#### 【0061】

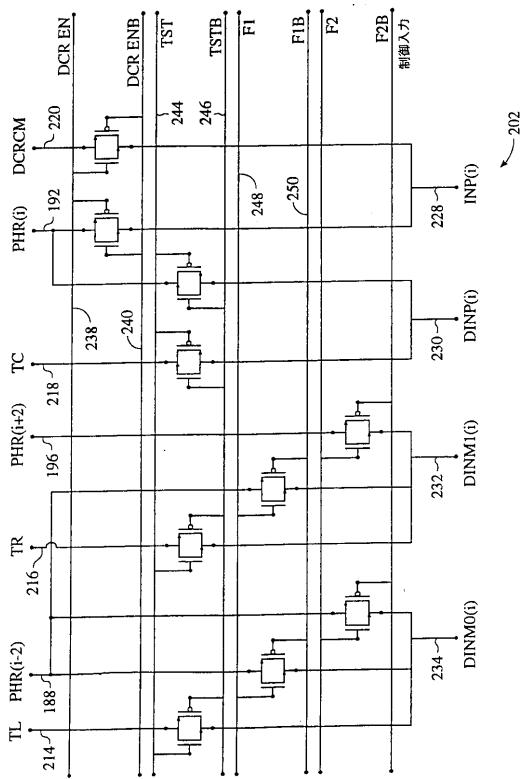

中心スイッチング・ネットワーク202の機能について、図11、12、及び13を参照して更に詳細に説明する。動作上関連する受光装置PHR(i)に対する接続192以外に、スイッチング・ネットワーク202は、問題となる受光装置から2だけ除去される受光装置である、受光装置の出力188及び196からの入力を受信する。受光装置の出力は、前に説明した転送増幅器を介して受信される。

10

#### 【0062】

各スイッチング・ネットワーク202による電位出力に対する他の入力は、テスト入力TL214、TR216、及びTC218である。テスト入力は、図3の制御論理回路25から受信される。最後に、DC除去コモン・モード(DCRCM)入力220は、関連するDC除去増幅器210への電位出力のために、各スイッチング・ネットワークに接続される。DCRCMはコモン・モード信号であり、これは、画像信号が、後続回路要素の動作範囲内で変化するのを可能にする、本質的にDC項の追加である。例えば、図3の計算アレイ21に、入力として0ボルトと5ボルトの間でのみ線形に動作する演算増幅器が含まれている場合、コモン・モード信号は、2.5ボルトになるように選択される。

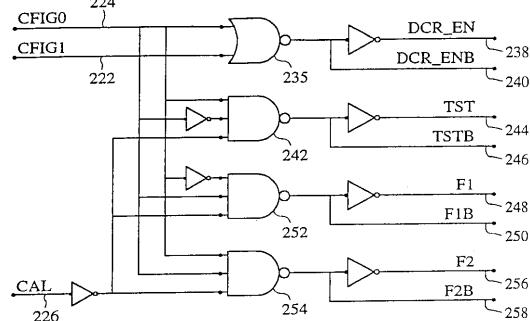

#### 【0063】

次に、図13を特定して参照すると、スイッチング・ネットワークは、2進入力対CFI G1 222及びCFIG0 224を、可能な4つの組み合わせの1つにセットすることによって構成される。さらに、較正信号が、CAL線226において受信される。CAL信号は、INP(i)線228だけが、スイッチング・ネットワーク202からの信号をDC除去増幅器210に伝達する条件を与えるために用いられる。従って、CAL信号は、転送増幅器のオフセット制御動作とは別個であるオフセット補正動作時に、DIN出力230、232、及び234を切り離す。

20

#### 【0064】

図11-13の回路は、線222及び224における構成信号を制御することによって、4つの方法の1つで構成可能である。第1のモードの場合、DC除去が禁止される。このモードの場合、線192における受光装置の出力は、INP(i)線228を介してW DATA(i)出力236まで経路指定される。すなわち、DC除去増幅器210は、PHR(i)=INP(i)=W DATA(i)となる、利得が1の増幅器として機能する。図13のゲート242及び252が、線244-250、256、及び258において必要とされるDC除去許可信号を供給しないので、出力230、232、及び234に沿ったDIN信号はこのモードでは利用されない。

30

#### 【0065】

第2のモードの場合、線222及び224における構成信号が、テスト・モードゲートを規定し、この場合、ゲート242が、線244及び246において許可信号を供給する。この状態において、DCRCMコモン・モード入力220は、スイッチング・ネットワーク202を介してINP(i)線228に送られる。テスト入力TL214、TR216、及びTC218は、それぞれ、出力234、232、及び230に送られる。テスト入力は、DC除去増幅器210の完全な特徴付けを可能にする、既知の信号である。

40

#### 【0066】

スイッチング・ネットワーク202の第3の構成を、DC除去機能1モードと呼ぶ。このF1モードの場合、INP(i)線228は、DCRCM線220に接続されて、DINP(i)=PHR(i)、DINM0(i)=PHR(i-2)、及びDINM1(i)=PHR(i-2)になる。この第3のモードは、ゲート252によって線250に論理高を供給し、線248に論理低を供給することによって許可される。

#### 【0067】

50

第4の構成を、DC除去機能2モードと呼ぶ。このF2モードの場合、出力228、230、及び232における信号は、F1モードの信号と同じである。すなわち、INP(i) = DCRCM、DINP(i) = PHR(i)、及びDINM0(i) = PHR(i-2)になる。しかし、F2モードでは、DINM1(i)出力232が、PHR(i+2)線196に接続される。ゲート254が、F2モードを許可するため、線256及び258に沿って適正な信号をトリガする。

#### 【0068】

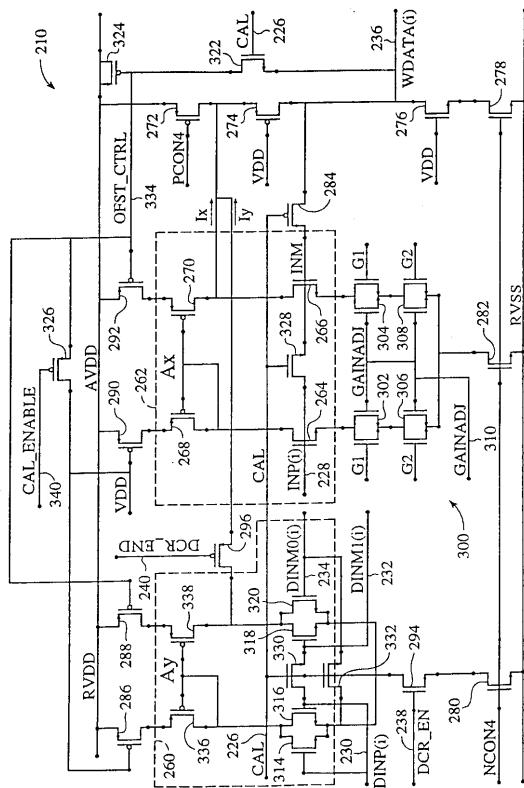

図14には、DC除去増幅器210が示されている。この増幅器には、第1の差動セルAy260と第2の差動セルAx262が含まれる。INP(i)出力228が、第2の差動セルにおいて受信され、一方、図12からの他の3つの出力230、232、及び234は、第1の差動セルにおいて受信される。

10

#### 【0069】

第2の差動セル262には、トランジスタ264及び266の差動対が含まれる。トランジスタ268及び270は、トランジスタ264及び266に対して電流ミラー負荷を与える。折重ねカスコード出力段が、4つの直列接続トランジスタ272、274、276、及び278によって形成される。トランジスタ272及び278に加えて、トランジスタ280及び282が、電圧NCON4及びPCON4によりバイアスされて、定電圧源として機能する。これら2つの電圧は、バイアス電圧VBP及びVBNと同様、定電圧源によって発生及び供給される。

#### 【0070】

以下で更に十分説明するように、DC除去増幅器210には、オフセット補正回路が含まれる。トランジスタ284は、利得1の帰還を実現するためのスイッチとして機能する。オフセット補正トランジスタ286、288、290、及び292が、三極管領域においてバイアスされると、オフセット補正が増幅器に導入される。

20

#### 【0071】

DC除去動作は、図13を参照して前に説明した信号線238及び240を利用して、トランジスタ294及び296を「オン」にすることによって許可される。一方、DC除去は、スイッチ294及び296が「オフ」になる場合に禁止され、その結果、増幅器210は、出力WDATA(i) = INP(i)である単純な利得1のバッファ増幅器になる。

30

#### 【0072】

DC除去モードの場合、第1の差動セル260は、下記に等しい電流(Iy)を発生する。

#### 【0073】

$$I_y = g m_y (2 \cdot DINP - (DINM0 + DINM1)) \quad (1)$$

同様に、第2の差動セル262は、下記に等しい電流(Ix)を発生する。

#### 【0074】

$$I_x = g m_x (INP - WDATA) \quad (2)$$

第2の差動セルには、図11に帰還線298として簡単に示される負帰還が含まれるので、電流Ixは、強制的に -Iy になる。従って、DC除去が許可されると、以下のようになる。

40

#### 【0075】

$$g m_y (2 \cdot DINP - (DINM0 + DINM1)) = -g m_x (INP - WDATA) \quad (3)$$

式(3)は、次のように書き直すことができる。

#### 【0076】

$$WDATA = INP + g m_y (2 \cdot DINP - (DINM0 + DINM1))$$

$$/ g m_x \quad (4)$$

50

相互コンダクタンス  $g m_x$  は、8つのトランジスタのバンク300によって変調される。バンク内のトランジスタのうちの4つが、三極管領域で、電圧GAINADJによりバイアスされて、トランジスタ264及び266の差動対に対する利得縮退抵抗器として機能する。バンク300内の他の4つのトランジスタは、利得縮退の抵抗性トランジスタに選択的に分路するためのスイッチとして利用され、G1及びG2デジタル利得制御入力の制御下にある。G1及びG2電圧は、図3に示す制御論理回路25によって設定される。

## 【0077】

8つのトランジスタのバンク300内で、4つの抵抗性トランジスタ302、304、306、及び308を、それぞれ、 $r_{302}$ 、 $r_{304}$ 、 $r_{306}$ 、及び $r_{308}$ と呼ぶことにする。利得縮退抵抗の影響を含めると、第2の差動セル262の相互コンダクタンスは、以下のようになる。

## 【0078】

## 【数1】

$$gm_x = gm_{x0} \left( \frac{1}{1 + gm_{x0} \left( \frac{1}{G1r_{302}} + \frac{1}{G2r_{304}} \right)} \right)$$

## 【0079】

ここで、 $gm_{x0}$ は、第2の差動セルの非縮退 $gm$ であり、この場合、 $r_{302} = r_{304}$ 、及び $r_{306} = r_{308}$ となる。値/G1及び/G2は、デジタル制御入力G1及びG2のブール補数であり、0または1の値を有する。縮退抵抗器の値 $r_{302} - r_{308}$ は、線310における制御電圧入力GAINADJを変化させることによって変調される。

## 【0080】

$r_{264}$ 及び $r_{302}$ を用いて、トランジスタ264及び302に対する $u_0 C_{ox} W / 2L$ を表し、 $VDS_{302}$ 及び $VDS_{304}$ を無視すると、 $gm_{x0} r_{302}$ は、次のように表すことができる。

## 【0081】

## 【数2】

$$gm_{x0} r_{302} = \frac{\beta_{264} (VGS_{264} - VT)}{\beta_{302} (VGS_{302} - VT)} = \frac{\beta_{264} (VGS_{264} - VT)}{\beta_{302} (GAINADJ - INP + VGS_{264} - VT)}$$

同様に、 $VDS_{306}$ と $VDS_{308}$ を無視すると、 $gm_{x0} r_{306}$ は次のように表現できる。

$$gm_{x0} r_{306} = \frac{\beta_{264} (VGS_{264} - VT)}{\beta_{306} (VGS_{306} - VT)} = \frac{\beta_{264} (VGS_{264} - VT)}{\beta_{306} (GAINADJ - INP + VGS_{264} - VT)}$$

## 【0082】

$gm_y = gm_{x0}$ 、 $r_{264} / r_{302} = 4$ 及び $r_{264} / r_{306} = 8$ とすると、 $gm_y / gm_x$ は、式(5)、(6)、及び(7)を用いて次のように表すことができる。

## 【0083】

## 【数3】

10

20

30

40

$$\frac{gm_y}{gm_x} = 1 + (4\overline{G1} + 8\overline{G2}) \frac{(VGS_{264} - VT)}{(GAINADJ - INP + VGS_{264} - VT)}$$

公称バイアス条件で、且つ GAINADJ = 5 ボルトの場合、式(8)は次のように簡略化できる。

$$\frac{gm_y}{gm_x} = 1 + 0.75 \cdot \overline{G1} + 1.50 \cdot \overline{G2}$$

10

## 【 0 0 8 4 】

式(8)を式(4)に代入すると、以下のような増幅器の公称転送特性が得られる。

## 【 0 0 8 5 】

## 【 数 4 】

$$WDATA = INP + (1 + 0.75 \cdot \overline{G1} + 1.50 \cdot \overline{G2})(2 \cdot DINP - (DINM0 + DINM1))$$

## 【 0 0 8 6 】

上記のように、図12及び13のスイッチング・ネットワーク202を用いて、DC除去増幅器210が、4つのモードの任意の1つに設定される。図15は、4つのモードの各自における転送特性を要約した表である。F1及びF2のDC除去モードにおいて、図11の受光装置の出力192における低い空間周波数成分が、DC除去増幅器210によって受信された、2つ以上の受光装置からの信号の平均を問題となる信号から減算することによって効果的に除去される。F1モードの場合、問題となる信号は、線192からのPHR(i)信号である。この信号は、図14のDINP(i)線230において受信される。DINP(i)は、トランジスタ314とトランジスタ316の両方に接続されるので、PHR(i)は、図示のように、F1モードの式において2倍される。このモードの場合、PHR(i-2)からの信号は、DINM1(i)線232とDINM0(i)線234の両方に切り換えられるので、PHR(i-2)も2倍される。差分値は、 $gm_y/gm_x$ 倍され、DCRCM値から減算される。やはり、DCRCM値は、WDATA(i)線236における後続のアナログ信号処理のために、正の中間範囲の電圧値を設定すべく選択される。

20

【 0 0 8 7 】

図15のF2モードの場合、INP(i)線228、DINP(i)線230、及びDINM0(i)線234における信号は、同じままであるが、DINM1(i)線232は、PHR(i-2)出力線188との接続からPHR(i+2)線196に切り換えられる。共通成分のフィルタリングが行われるが、その共通性は、2つの受光装置ではなく、3つの受光装置に関するものである。受光装置PHR(i)は、トランジスタ314及び316を制御する。受光装置PHR(i-2)は、トランジスタ318を制御し、一方、受光装置PHR(i+2)は、トランジスタ320を制御する。

30

## 【 0 0 8 8 】

各受光装置によって制御されるトランジスタの数またはこうしたトランジスタの面積を変更して、異なる受光装置の重み付けを変更可能である。

## 【 0 0 8 9 】

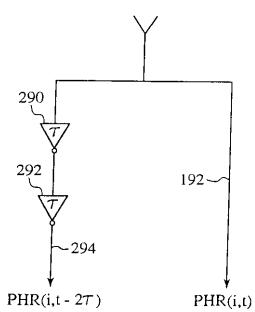

図16及び17の回路は、F2モードの変形例を提供する。図16の場合、受光装置からの信号は、遅延を伴わずに、線192に伝達される。この192に沿った信号は実時間(t)である。1対の遅延回路290及び292が、第2の線294に沿って直列に接続されている。線294における信号は、2の遅延を伴う受光装置の出力である。

40

50

## 【0090】

第2の線294に沿った遅延回路290及び292は、2次元DC除去を可能にする。すなわち、DC除去用の二次入力が、一次入力の供給源と同じ列内の異なる行からとられる。F2モードは、従って、次のようになる。

## 【0091】

$$WDATA = DRCM - g_{m_y} [2 \cdot PHR(i, t) - PHR(i-t-2 \\ \tau) + PHR(i-2, t)] / g_{m_x}$$

図17の回路は、F2動作モードを実施するために用いられる。図12及び17の共通線は、同じ参照番号によって識別される。図17の回路は、線192の一次入力及び線188の二次入力の一方に関して同じままである。しかし、線294における二次入力は、線192における一次入力と同じ転送増幅器からのものである。この入力は、同じ列からのものであるが、2の遅延の結果、二次入力は異なる行からのものになる。好適には、遅延は、転送増幅器のサンプリング時間に等しい。

## 【0092】

図16における遅延回路290及び292の利用は、2次元DC除去機能の動作にとって重要ではない。例えば、ラウンド・ロビン式に動作するサンプル／ホールド回路によって、適切な二次入力を供給することも可能である。

## 【0093】

図12-14、及び図16と17の回路は、受光装置アレイによる検分を受ける基体の照度ばらつきの悪影響を効率的に克服する。さらに、上記のように、航行情報の供給に本発明を利用する場合、航行アレイの一部が、走査を受ける原稿の陰影付き領域における紙の纖維を検分し、一方、アレイの第2の部分が検分する紙の纖維が、原稿の陰影付き領域の外側であるといったことによって、航行動作はあまり影響を受けない。

## 【0094】

重要ではないが、図14のDC除去増幅器210には、オフセット補正が含まれて、製造段階で導入されるデバイスのパラメータのばらつきによって発生するような、電圧オフセットが低減される。トランジスタ322、324、326、328、330、及び332を用いて、オフセット補正が実施される。オフセット補正サイクルを実施するために、トランジスタ322が、線226におけるCAL入力信号によって「オン」にされ、それにより、DC除去増幅器出力WDATA(i)がOFS\_T\_CTRLノード334に接続される。図11に線298で示された、第2の差動セル262における負帰還が、トランジスタ284をオフにすることによって切断される。セル260及び262に対する差動入力は、分路スイッチ・トランジスタ328、330、及び332によって短絡させられる。該入力が短絡すると、DC除去増幅器210は、入力オフセットを増幅する。オフセット補正トランジスタ286、288、290、及び292は、三極管領域においてバイアスされる。OFS\_T\_CTRLノード334における電圧が、バイアス電圧VBPに等しくなければ、トランジスタ268及び270とトランジスタ336及び338によって得られる電流ミラーは、不平衡であり、WDATA(i)出力236において付加電圧を発生する。A<sub>01</sub>を慣用的な入力からの増幅器210の開ループ利得とすると、増幅器は、OFS\_T\_CTRLノードと出力236との間ににおいて下記の関係を有するように設計される。

## 【0095】

$$WDATA(i) = A_{01} (v_{bs} - OFST_CTRL) / 100 \quad (11)$$

増幅器の出力が、トランジスタ322を介してOFS\_T\_CTRLノードに接続されると、新たな負帰還経路が導入される。OFS\_T\_CTRLノードから増幅器出力への利得は、慣用的な入力から出力への利得の約100分の1になるので、トランジスタ322によって形成される一時的な負帰還経路によって、入力オフセットの100倍に等しい信号が、OFS\_T\_CTRLとバイアス電圧VBPの間に生じることになる。

## 【0096】

10

20

30

40

50

較正サイクルの終了時には、C A L 入力は論理低になり、その結果、O F S T \_ C T R L ノード334は、W D A T A ( i ) 出力236から切斷される。トランジスタ324は、約300fFに等しいコンデンサとして用いられる。補正サイクル中に発生するオフセット補正信号は、トランジスタ324のゲートに電荷として記憶される。所望ならば、線340を介してトランジスタ326のゲートを論理低に駆動することによって、オフセット補正を禁止することもでき、それによって、O F S T \_ C T R ノード334は、バイアス入力V B Pに分路される。

【 0 0 9 7 】

以下に、本発明の実施態様を列挙する。

【 0 0 9 8 】

1 . 読み出し動作とリセット動作の間で周期的に切り換えられる差動回路に、オフセット補正を与える方法であって、上記差動回路は、第1及び第2の回路入力と、出力電圧状態が前記回路入力における電圧状態に応答する回路出力とを備え、前記方法は、前記リセット動作の少なくとも幾つかに対して実行される、方法において、

前記差動回路が、読み出し動作からリセット動作に切り換えられる場合、前記第1の回路入力を前記第2の回路入力に接続するステップと、

前記差動回路が、前記読み出し動作から前記リセット動作に切り換えられる場合、前記回路出力を固定電圧状態の電源に接続するステップと、

前記リセット動作の第1の時間セグメントの後に続いて、前記電源から前記回路出力を切斷し、それによって、前記回路出力が、前記固定電圧状態から自由に浮動する、前記リセット動作の第2の時間セグメントを開始するステップと、

前記第2の時間セグメントの間に、前記回路出力における電圧状態のシフトに応答して、オフセット補正信号を形成するステップと、

を含むことを特徴とする方法。

【 0 0 9 9 】

2 . 前記電源から前記回路出力を切斷する前記ステップ、及び前記オフセット補正信号を形成する前記ステップは、前記リセット動作の一部に対してのみ実行され、前記方法はさらに、前記読み出し動作中に前記差動回路に加えるために、前記オフセット補正信号を記憶するステップを含むことを特徴とする、前項1に記載の方法。

【 0 1 0 0 】

3 . 前記回路出力を電源に接続する前記ステップは、前記回路出力を正の電圧源に接続するステップであることを特徴とする、前項1に記載の方法。

【 0 1 0 1 】

4 . 前記オフセット補正信号を形成する前記ステップは、前記第2の時間セグメントの間に、前記電源の前記固定電圧状態を、前記回路出力における前記電圧状態と比較するステップを含むことを特徴とする、前項1に記載の方法。

【 0 1 0 2 】

5 . 前記第1の回路入力を前記第2の回路入力に接続する前記ステップは、前記第1と第2の入力を第2の固定電圧源に接続するステップであることを特徴とする、前項1に記載の方法。

【 0 1 0 3 】

6 . 受光装置アレイにおいて、

光電素子が、計算回路への光電流信号の転送に関して、動作的にグループ化され、それにより、複数の光電素子グループを規定する光電素子アレイと、

各転送増幅器が、1つの光電素子グループと動作的に関連するように、前記光電素子グループと1対1の対応を有する、複数の転送増幅器であって、各転送増幅器は、第1の入力及び第2の入力を備え、また該第1の入力と第2の入力の電圧状態の差を表す出力を備え、前記第2の入力は、基準電圧源に接続されている、複数の転送増幅器と、

前記グループ内の前記光電素子を、前記グループが動作的に関連している前記転送増幅器の前記第1の入力に順次接続し、また、前記光電素子のどれも前記入力に接続されていな

10

20

30

40

50

いリセット期間を与えるための、各光電素子グループに対する第1のスイッチング手段と、

前記第1と第2の入力における電圧状態が等しい前記リセット期間中に、前記第1の入力を前記第2の入力に接続するための、各転送増幅器に対する第2のスイッチング手段と、

前記リセット期間の少なくともいくつかの第1の部分の間、前記出力をリセット電圧源に接続し、また、前記リセット期間の第2の部分の間、前記出力を前記リセット電圧源から切断するための、各転送増幅器に対する第3のスイッチング手段と、

各転送増幅器に対する、前記出力への前記第1の入力の容量性結合と、

前記時間期間の1つの第2の部分の間、前記リセット電圧と、前記転送増幅器の前記出力の1つにおける電圧状態との間の電圧差の検出に応答して、前記転送増幅器にオフセット調整信号を供給するためのオフセット手段と、

からなる受光装置アレイ。

## 【0104】

7. 各光電素子グループは、前記光電素子アレイが、複数の列と行を有するように配列された、光電素子の1つの列であり、前記転送増幅器の各々は、単一列の光電素子に選択的に接続されることを特徴とする、前項6に記載の受光装置アレイ。

## 【0105】

8. 前記リセット期間中に、1度に1つずつ、前記オフセット手段を前記転送増幅器に接続するための第3のスイッチング手段から更になり、前記オフセット手段は、前記オフセット調整信号を発生するための回路を備えることを特徴とする、前項7に記載の受光装置アレイ。

## 【0106】

9. 前記オフセット手段は、前記リセット電圧源に接続された第1の入力ノードを有し、また、前記転送増幅器の前記出力に選択的に接続された第2の入力ノードを有する、1つの差動増幅器を備え、該差動増幅器は1つの出力ノードを有し、前記転送増幅器の各々は、前記差動増幅器の前記出力ノードに接続された1つのオフセット入力を有することを特徴とする、前項7に記載の受光装置アレイ。

## 【0107】

10. 各転送増幅器は、前記オフセット調整信号を記憶するために、前記オフセット入力に接続されたサンプル／ホールド手段を備えることを特徴とする、前項9に記載の受光装置アレイ。

## 【0108】

11. 信号を転送するための回路構成において、

前記回路構成の各々が1つの出力を有する、複数の信号発生回路と、

該信号発生回路の前記出力から、空間周波数成分を除去するための複数のDC除去手段であって、各DC除去手段は、1つの特定の信号発生回路と動作的に関連しており、また前記特定の信号発生回路の出力から、問題となる信号を受信するように接続された一次入力を有し、前記各DC除去手段は、前記特定の信号発生回路に近接する前記信号発生回路の1つから出力された信号を受信するように接続された、少なくとも1つの二次入力を備え、前記各DC除去手段は、前記問題となる信号と、前記少なくとも1つの二次入力において受信された前記信号出力との間のアナログ信号差に応答して、1つの出力信号を供給するための差動手段を備える、複数のDC除去手段と、

からなる信号を転送するための回路構成。

## 【0109】

12. 各DC除去手段は、前記一次入力と前記少なくとも1つの二次入力を有する第1の差動セルを含み、該第1の差動セルは、前記一次入力と前記少なくとも1つの二次入力との間の信号差に応答する1つの出力ノードを有することを特徴とする、前項11に記載の回路構成。

## 【0110】

13. 各DC除去手段は、前記第1の差動セルの前記出力ノードに接続された第1の入力

10

20

30

40

50

を有し、また第2の入力及び信号出力ノードを有する、第2の差動セルを含み、前記第2の入力は、負帰還ループによって前記信号出力ノードに接続されることを特徴とする、前項12に記載の回路構成。

【0111】

14. 各第2の差動セルは、固定コモン・モード信号の供給源に選択的に接続される1つの正の入力を有することを特徴とする、前項13に記載の回路構成。

【0112】

15. 前記信号発生回路は、光電素子の第1の行を形成するように配列された光電素子であり、前記特定の信号発生回路は、前記第1の行内における光電素子であり、また、前記第1の行内の中間光電素子によって、前記少なくとも1つの二次入力に接続される全ての光電素子から離隔されることを特徴とする、前項11に記載の回路構成。10

【0113】

16. 各DC除去手段は、前記第1の行内の異なる光電素子と動作的に関連していることを特徴とする、前項15に記載の回路構成。

【0114】

17. 前記第1の行と共に、光電素子の列を規定するように配列される複数の第2の行から更になり、前記DC除去手段の各々は、光電素子の異なる列と動作的に関連していることを特徴とする、前項16に記載の回路構成。

【0115】

18. 前記信号発生回路は、行と列に配列された光電素子であり、各DC除去手段は、前記一次入力に接続された光電素子と同じ行の光電素子から、二次入力を受信するように接続され、また、前記一次入力に接続された前記光電素子と同じ列の光電素子から、二次入力を受信するように接続されることを特徴とする、前項11に記載の回路構成。20

【0116】

19. 各DC除去手段は、1つの負帰還ループと、オフセット信号を記憶するための1つのサンプル／ホールド構成とを有する、1つのオフセット補正回路を含むことを特徴とする、前項11に記載の回路構成。

【0117】

20. 前記複数のDC除去手段と1対1に対応する、複数のスイッチング・ネットワークから更になり、各スイッチング・ネットワークは、前記複数の信号発生回路の異なる回路を含む、異なる信号源への前記一次入力及び二次入力の接続を選択的に変更するための複数のスイッチを有することを特徴とする、前項11に記載の回路構成。30

【0118】

21. 前記DC除去手段は、前記特定の信号発生回路の前記出力からの問題となる前記信号に対して、前記特定の信号発生回路に近接する前記信号発生回路のうちの前記1つから出力された前記信号を重み付けするための手段を含むことを特徴とする、前項11に記載の回路構成。

【0119】

【発明の効果】

本発明は上述のように、オフセット低減回路が設けられて、出力がリセット電圧源から切断された後に、リセット電圧と出力での電圧状態との間の電圧差の検出に応答して、オフセット調整信号が発生される。このようにして、オフセット調整信号を問題となる転送增幅器に加えることによって、その転送增幅器と他の転送增幅器との間における性能差を低減、又は削除することが可能になる。40

【0120】

また、オフセット調整型の転送增幅器により、デバイス間のばらつき及び $1/f$ ノイズの影響が低減されるという効果がある。

【図面の簡単な説明】

【図1】原稿上で曲がりくねった経路を辿る、手持ち式走査装置の斜視図である。

【図2】図1の走査装置の画像形成及び航行センサの底面図である。

【図 3】本発明による受光装置アレイ及び処理回路のブロック図である。

【図 4】本発明による転送増幅器に接続された光電素子回路である。

【図 5】本発明による光電素子対の概略図である。

【図 6】図 5 の回路に関するタイミング図である。

【図 7】図 4 の転送増幅器を動作させるための回路の概略図である。

【図 8】図 7 の転送増幅器に対してオフセット調整を決定するための回路の概略図である

。

【図 9】図 4 の転送増幅器の概略図である。

【図 10】本発明による光電素子と転送増幅器からなるアレイのブロック図である。

【図 11】本発明に従って、図 10 の転送増幅器から出力を受信して処理を施す、スイッ 10 チング・ネットワーク及び DC 除去増幅器からなるアレイのブロック図である。

【図 12】図 11 の DC 除去増幅器に伝送される信号を切り換えるための回路の概略図である。

【図 13】図 12 のスイッチング回路を構成するための回路の概略図である。

【図 14】図 11 の DC 除去増幅器の概略図である。

【図 15】図 13 の構成回路により実現されるような、図 14 の DC 除去増幅器に対する 4 つの動作モードの各々の転送特性表である。

【図 16】後続の 2 次元 DC 除去のための信号関係を確立するように、受光装置の出力が 2 つの並列線の一方だけに沿って遅延される回路の概略図である。

【図 17】図 16 の回路に接続するための 2 次元 DC 除去回路の概略図である。 20

【符号の説明】

10 走査装置

12 経路

14 原稿

16 画像ディスプレイ

17 列転送増幅器

19 DC 除去回路

21 計算アレイ

22 撮像センサ

24, 26 航行センサ

30

25 制御論理回路

28 リセット・スイッチ

40 光電素子

42 読み出しスイッチ

46 転送増幅器

136 オフセット調整増幅器

148 サンプル／ホールド回路

198-206 スイッチング・ネットワーク

208-212 DC 除去増幅器

260 第 1 の差動セル A y

40

262 第 2 の差動セル A x

【 図 1 】

【 図 2 】

【 図 3 】

【図4】

【図5】

【図6】

【図7】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

### 【図14】

【 図 15 】

【 図 1 6 】

【 図 1 7 】

---

フロントページの続き

(72)発明者 ブラロック, トロヴィス, エヌ

アメリカ合衆国カリフォルニア州95051, サンタ・クララ, ポメロイ・アヴェニュー・110

0

(72)発明者 バウムガートナー, リチャード, エイ

アメリカ合衆国カリフォルニア州94303, パロ・アルト, ネウェル・ロード・1860

(72)発明者 ホーナック, トーマス

アメリカ合衆国カリフォルニア州94028, ポートラ・ヴァレイ, コエイミン・ビュー・1

(72)発明者 ベアード, デイヴィス

アメリカ合衆国カリフォルニア州94306, パロ・アルト, ロス・ロビース・842

審査官 渡辺 努

(56)参考文献 特開昭60-052159(JP, A)

特開昭61-052012(JP, A)

米国特許第04884039(US, A)

(58)調査した分野(Int.Cl., DB名)

H04N 1/024-1/207