(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6219656号

(P6219656)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

|             |              |                  |      |       |     |

|-------------|--------------|------------------|------|-------|-----|

| <b>H05B</b> | <b>33/26</b> | <b>(2006.01)</b> | H05B | 33/26 | Z   |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | H01L | 33/14 | A   |

| <b>H05B</b> | <b>33/12</b> | <b>(2006.01)</b> | H05B | 33/12 | B   |

| <b>H01L</b> | <b>27/32</b> | <b>(2006.01)</b> | H01L | 27/32 |     |

| <b>G09F</b> | <b>9/30</b>  | <b>(2006.01)</b> | G09F | 9/30  | 365 |

請求項の数 11 (全 14 頁)

(21) 出願番号

特願2013-202935 (P2013-202935)

(22) 出願日

平成25年9月30日 (2013.9.30)

(65) 公開番号

特開2015-69830 (P2015-69830A)

(43) 公開日

平成27年4月13日 (2015.4.13)

審査請求日

平成28年8月29日 (2016.8.29)

(73) 特許権者

502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人

110000154

特許業務法人はるか国際特許事務所

(72) 発明者

大岡 浩

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

(72) 発明者

坂元 博次

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

(72) 発明者

佐藤 敏浩

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

最終頁に続く

(54) 【発明の名称】有機EL表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

基板と、

前記基板上に配置された複数の画素と、

前記複数の画素の各々に備えられた下部電極、発光層、及び上部電極と、

前記複数の画素を区画し、前記下部電極の第1領域を露出する隔壁と、

前記基板と前記下部電極との間に位置する配線と、

前記配線と前記下部電極との間に位置する絶縁膜と、

前記複数の画素の少なくとも一つの画素に配置され、前記発光層を貫通し前記下部電極の第2領域を露出する貫通孔と、

前記絶縁膜に配置され、前記貫通孔とは異なるコンタクトホールとを備え、

前記貫通孔は、前記第1領域の上に位置し、前記絶縁膜へは突出せず、

前記コンタクトホールは、平面的に見て前記貫通孔と重なり、前記配線の一部を露出し

、

前記下部電極は前記配線と前記コンタクトホールで直に接し、

前記上部電極は前記下部電極と前記貫通孔で直に接し、且つ前記下部電極を介して前記配線と電気的に接続していることを特徴とする有機EL表示装置。

## 【請求項2】

前記上部電極は、前記複数の画素に共通して配置され、

前記配線は、前記上部電極に共通電圧を供給することを特徴とする請求項1に記載の有

10

20

機 E L 表示装置。

【請求項 3】

前記少なくとも一つの画素は、発光部を備える第 1 サブピクセルと、前記貫通孔に対応する非発光部を備え、発光部を備えない第 2 サブピクセルとを有することを特徴とする請求項 1 又は請求項 2 に記載の有機 E L 表示装置。

【請求項 4】

前記隔壁は、前記発光部を露出する第 1 開口と前記非発光部を露出する第 2 開口とを、前記少なくとも一つの画素に有することを特徴とする請求項 3 に記載の有機 E L 表示装置。

【請求項 5】

前記複数の画素は、複数の第 1 の画素と複数の第 2 の画素を含み、

前記第 1 の画素は前記貫通孔を備えず、

前記第 2 の画素は、前記貫通孔を備えない第 1 サブピクセルと、前記貫通孔を備える第 2 サブピクセルとを含むことを特徴とする請求項 1 又は請求項 2 に記載の有機 E L 表示装置。

【請求項 6】

前記発光層は、平面的に見て前記貫通孔の外周に相当する端部を有し、

前記隔壁は、前記第 1 領域を囲う側面を有し、

前記端部は前記側面の上に位置していることを特徴とする請求項 1 から請求項 5 の何れか 1 項に記載の有機 E L 表示装置。

【請求項 7】

基板と、

前記基板上に配置された複数の画素と、

前記複数の画素の各々に備えられた下部電極、発光層、及び上部電極と、

前記複数の画素を区画し、前記下部電極の第 1 領域を露出する隔壁と、

前記基板と前記下部電極との間に位置する配線と、

前記配線と前記下部電極との間に位置する絶縁膜とを備え、

前記複数の画素は、複数の第 1 の画素と複数の第 2 の画素を含み、

前記複数の第 1 の画素の各々は、平面的に見て前記第 1 領域と重なる発光部を有し、

前記複数の第 2 の画素の各々は、前記発光層を貫通し前記下部電極の第 2 領域を露出する貫通孔を有し、

前記貫通孔は、前記第 1 領域の上に位置し、前記絶縁膜へは突出せず、

前記複数の第 2 の画素の各々において、前記上部電極は前記下部電極と前記貫通孔で直に接し、且つ前記下部電極を介して前記配線と電気的に接続していることを特徴とする有機 E L 表示装置。

【請求項 8】

前記上部電極は、前記複数の画素に共通して配置され、

前記配線は、複数本配置されて、前記上部電極に共通電圧を供給し、

複数の前記配線の各々は第 1 の方向に延びると共に、前記複数の画素のうち前記第 1 の方向に配列した複数個の画素と重なり、

前記複数個の画素は、前記第 2 の画素を少なくとも一つ含むことを特徴とする請求項 7 に記載の有機 E L 表示装置。

【請求項 9】

前記絶縁膜には、前記貫通孔とは異なるコンタクトホールが配置され、

前記コンタクトホールは、平面的に見て前記貫通孔と重なり、前記配線の一部を露出し、

前記下部電極は前記配線と前記コンタクトホールで直に接することを特徴とする請求項 7 又は請求項 8 に記載の有機 E L 表示装置。

【請求項 10】

前記複数の第 1 の画素の各々は前記貫通孔を備えず、

10

20

30

40

50

前記複数の第2の画素の各々は、前記貫通孔を備えない第1サブピクセルと、前記貫通孔を備える第2サブピクセルとを含むことを特徴とする請求項7から請求項9の何れか1項に記載の有機EL表示装置。

【請求項11】

前記発光層は、平面的に見て前記貫通孔の外周に相当する端部を有し、

前記隔壁は、前記第1領域を囲う側面を有し、

前記端部は前記側面の上に位置していることを特徴とする請求項7から請求項10の何れか1項に記載の有機EL表示装置。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は有機エレクトロルミネッセンス(electroluminescence: EL)表示装置に関し、特に有機発光素子の電極のうち表示領域に配列された複数画素に共通に形成される電極における電位の均一化に関する。

【背景技術】

【0002】

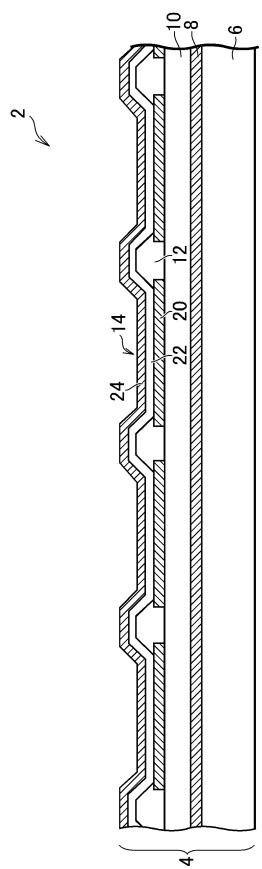

有機EL表示装置はTFT基板と対向基板とを貼り合わせた構造を有する。図7は従来の有機EL表示装置2のTFT基板4の表示領域の模式的な部分断面図であり、表示領域の水平方向に沿った垂直断面を示している。TFT基板4は例えば、ガラス基板6上に回路層8、絶縁膜10、バンク12、有機発光ダイオード(Organic Light-Emitting Diode: OLED)14及び封止膜16などを積層される。

20

【0003】

表示領域には複数の画素が二次元配列される。カラー表示を行う有機EL表示装置では、各画素は互いに異なる色で発光する複数のサブピクセルからなる。例えば、画素は赤色(R)で発光するRサブピクセル、緑色(G)で発光するGサブピクセル、青色(B)で発光するBサブピクセルで構成することができ、またこれらに白色(W)で発光するWサブピクセルを加えた4サブピクセルで1画素を構成することも行われる。

【0004】

OLED14はサブピクセルごとにバンク12(隔壁)で囲まれた開口領域に形成され、下部電極20、有機層22(有機材料層)及び上部電極24を含んで構成される。下部電極20及び上部電極24はそれぞれOLEDのアノード電極(陽極)、カソード電極(陰極)を構成し、これらの間に印加される電気信号により有機層22での発光が制御される。上部電極24は基本的に表示領域全体の画素に共通に形成され、表示領域の縁にて給電線に接続され駆動部から共通電圧を印加される。一方、下部電極20は画素ごとに形成され、回路層8に形成される各画素の画素回路及び駆動電源線を介して駆動部から映像信号に応じた電流を供給される。

30

【0005】

バンク12はOLED、特に有機層22をサブピクセルごとに区切って形成するための隔壁としての機能を有する。またバンク12は絶縁層で形成され、開口領域ごとに形成される下部電極20間の短絡を防止する。

40

【0006】

上部電極24及び下部電極20は例えば、IZO(Indium Zinc Oxide)やITO(Indium Tin Oxide)等の透明導電材を用いて形成される。特に、トップエミッション型の有機EL表示装置では、消費電力低減の観点から上部電極24の光の透過率は高いことが望ましい。ここで、透明導電材を薄くすれば上部電極24の透過率は上がるが、その反面、上部電極24の導電率が低下し、OLEDに流れる電流に起因する電圧降下が大きくなる。具体的には上部電極24において給電線に近い位置と遠い位置との電位差が大きくなる。その結果、給電線から遠い位置ほどOLEDの電流密度が低下して輝度が低下するシェーディング(輝度傾斜)が生じる。すなわち、発光輝度が表示領域内で一様でなくなり表示むらを生じるという問題がある。この問題は表示パネルが大面積化するほど顕著と

50

なる。

#### 【0007】

そこで、抵抗値の低い材料を用いて導通を補助する給電配線を形成し、バンク12に形成したコンタクトホールを介して上部電極24と給電配線とを接続することで、上部電極24の実質的な低抵抗化を図ることが提案されている（特許文献1）。

#### 【0008】

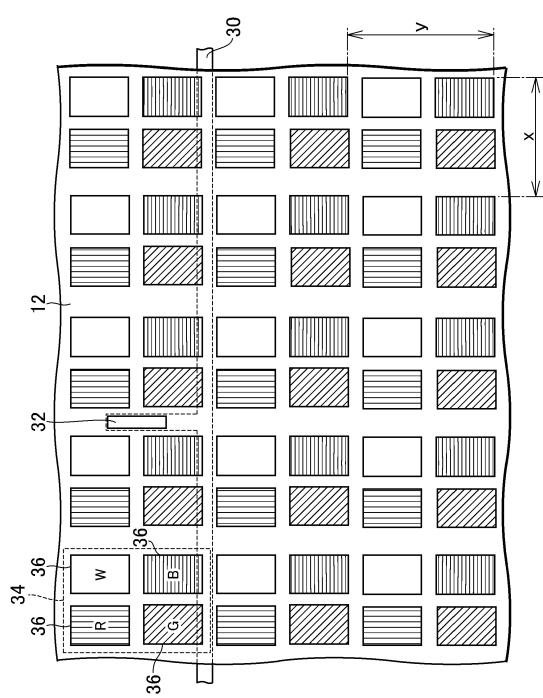

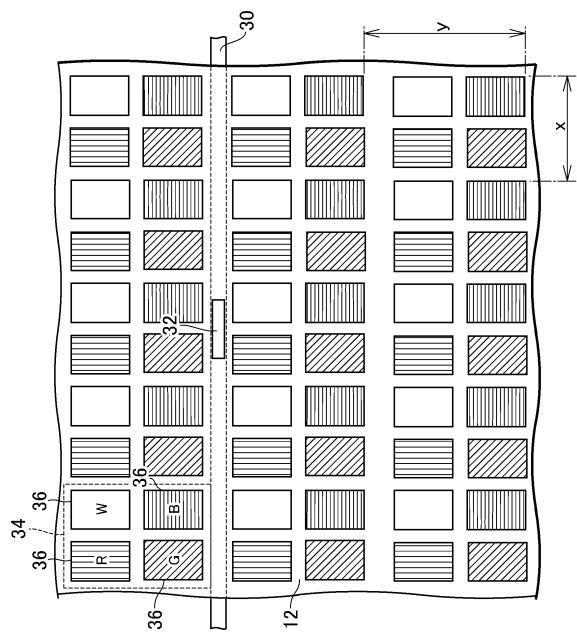

図8、図9は上部電極24と給電配線30とを接続するコンタクトホール32をバンク12に形成した有機EL表示装置の表示領域の一部分の平面図である。ここでは各画素34がRGBWの4つのサブピクセル36からなる例を示している。図8は水平方向に隣接する画素34の間のバンク12にコンタクトホール32を配置する場合を示しており、図9は垂直方向に隣接する画素34の間のバンク12にコンタクトホール32を配置する場合を示している。10

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

#### 【特許文献1】特開2009-199868号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

図8、図9に示すようにコンタクトホール32を配置するバンク12は、コンタクトホール32を配置しない場合のバンクより大きな幅を要する部分を生じる。すなわち、上部電極24と給電配線30とを接続するコンタクトホール32をバンク12に形成する構成では、バンク12の幅はバンク12の本来の機能から必要とされる以上のサイズとなりバンク12の微細化が制限されるので、有機EL表示装置の高精細化に不利であるという問題があった。20

#### 【0011】

また、図8、図9に示すように、コンタクトホール32は上部電極24の導電率によっては必ずしも画素ごとに設けなくてもよい。しかし、画像表示装置では表示品質確保のため画素の配列ピッチを表示領域内にて一様にするので、電気特性上、コンタクトホール32を配置する必要がない位置のバンク12の幅、面積がコンタクトホール32を設ける位置のバンク12と同様に大きく形成され、無駄な非発光領域が大きくなる。30

#### 【0012】

具体的には、図8、図9に示すマトリクス状の画素配列にて水平方向の画素ピッチをx、垂直方向の画素ピッチをyとすると、図8に示す構成では、バンク12にコンタクトホール32を配置しない場合よりもxが大きくなり、図9に示す構成では、バンク12にコンタクトホール32を配置しない場合よりもyが大きくなる。画素ピッチの増加は高精細化に不利であることを意味し、また当該増加はバンク12の幅の増加によるものであり、非発光領域の増加を意味する。

#### 【0013】

本発明は上記問題点を解決するためになされたものであり、画素の開口率を高く維持しつつ、シェーディングを抑制し高品位の画質が得られる有機EL表示装置を提供することを目的とする。40

#### 【課題を解決するための手段】

#### 【0014】

(1) 本発明に係る有機EL表示装置は、隔壁で囲まれた開口領域に形成された有機発光素子を少なくとも1つ含み共通の形を有する複数の画素を二次元配列され、基板の上に形成され前記有機発光素子の駆動の基準電位を供給される給電配線を有し、前記有機発光素子は、前記給電配線が形成された前記基板の上に形成され、下から順に下部電極、有機材料層、及び前記複数の画素に共通の上部電極が積層された構造を有し、前記複数の画素のうちの一部の画素は、前記有機材料層を貫通して前記上部電極と前記給電配線とを電気

50

的に接続する垂直配線を前記開口領域内に形成された変則画素であるものである。

【0015】

(2) 上記(1)に記載する有機EL表示装置において、前記画素は、赤色、緑色、青色及び白色で発光する4つの前記開口領域を含み、前記変則画素は、白色発光の前記開口領域の全部又は一部に、前記有機発光素子の構造に代えて前記垂直配線を形成される構成とすることができる。

【0016】

(3) 上記(1)に記載する有機EL表示装置において、前記画素は赤色、緑色及び青色で発光する3つの前記開口領域からなり、前記変則画素は、青色発光の前記開口領域の全部又は一部に、前記有機発光素子の構造に代えて前記垂直配線を形成される構成とすることができる。

10

【0017】

(4) 上記(1)から(3)に記載する構成は、前記上部電極が透明導電膜からなる有機EL表示装置に好適である。

【発明の効果】

【0018】

本発明によれば、表示領域内にて上部電極を給電配線に接続することでシェーディングを抑制できる。上部電極と給電配線との接続は一部の画素の開口領域で行われるので、バンクの幅を大きくする必要がなく、表示領域全体としてみて画素の開口率を高く維持することができ、また解像度の向上を図れる。

20

【図面の簡単な説明】

【0019】

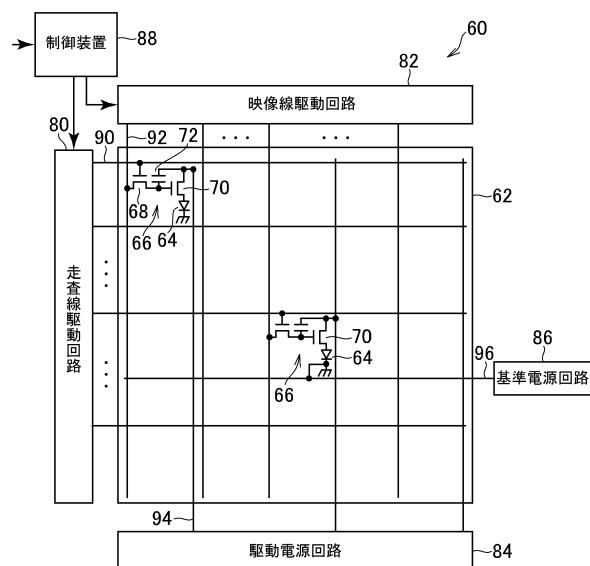

【図1】本発明の実施形態に係る有機EL表示装置の概略の構成を示す模式図である。

【図2】本発明の第1の実施形態に係る有機EL表示装置の画素アレイ部の模式的な部分平面図である。

【図3】本発明の第1の実施形態に係る有機EL表示装置の画素アレイ部の模式的な部分断面図である。

【図4】カソードコンタクトの形成方法を説明する概略のプロセスフロー図である。

【図5】本発明の第2の実施形態に係る有機EL表示装置の変則画素の模式的な平面図である。

30

【図6】本発明の第3の実施形態に係る有機EL表示装置の画素アレイ部の模式的な部分平面図である。

【図7】従来の有機EL表示装置のTFT基板の表示領域の模式的な部分断面図である。

【図8】OLEDの上部電極と給電配線とを接続するコンタクトホールを水平方向に隣接する画素間のバンクに形成する従来の有機EL表示装置の表示領域の一部分の平面図である。

【図9】OLEDの上部電極と給電配線とを接続するコンタクトホールを垂直方向に隣接する画素間のバンクに形成する従来の有機EL表示装置の表示領域の一部分の平面図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態(以下実施形態という)について、図面に基づいて説明する。

。

【0021】

[第1の実施形態]

有機EL表示装置は、アクティブマトリックス型表示装置であり、テレビ、パソコン、携帯端末、携帯電話等に表示パネルとして搭載される。図1は、第1の実施形態に係る有機EL表示装置60の概略の構成を示す模式図である。有機EL表示装置60は、画像を表示する表示領域である画素アレイ部62と、当該画素アレイ部を駆動する駆動部とを備える。

50

**【0022】**

画素アレイ部62には画素（又はサブピクセル）に対応してOLED64及び画素回路66がマトリクス状に配置される。画素回路66は複数の薄膜トランジスタ（Thin Film Transistor: TFT）68, 70やキャパシタ72で構成される。OLED64のアノード電極は駆動TFT70に接続される。また、全OLED64のカソード電極は後述するように共通の電極で構成される。

**【0023】**

一方、駆動部は走査線駆動回路80、映像線駆動回路82、駆動電源回路84、基準電源回路86及び制御装置88を含み、画素回路66を駆動しOLED64の発光を制御する。

10

**【0024】**

走査線駆動回路80は画素の水平方向の並び（画素行）ごとに設けられた走査信号線90に接続されている。走査線駆動回路80は制御装置88から入力されるタイミング信号に応じて走査信号線90を順番に選択し、選択した走査信号線90に、点灯TFT68をオンする電圧を印加する。

**【0025】**

映像線駆動回路82は画素の垂直方向の並び（画素列）ごとに設けられた映像信号線92に接続されている。映像線駆動回路82は制御装置88から映像信号を入力され、走査線駆動回路80による走査信号線90の選択に合わせて、選択された画素行の映像信号に応じた電圧を各映像信号線92に出力する。当該電圧は、選択された画素行にて点灯TFT68を介してキャパシタ72に書き込まれる。駆動TFT70は書き込まれた電圧に応じた電流をOLED64に供給し、これにより、選択された走査信号線90に対応する画素のOLED64が発光する。

20

**【0026】**

制御装置88は、CPU（Central Processing Unit）などの演算処理回路、及びROM（Read Only Memory）やRAM（Random Access Memory）などのメモリ素子からなる記憶部を備えている。制御装置88は映像信号を入力される。例えば、有機EL表示装置60がコンピュータや携帯端末の表示部を構成する場合には、映像信号は本体のコンピュータ等から有機EL表示装置60に入力される。また、有機EL表示装置60がテレビジョン受信機を構成する場合には、映像信号は不図示のアンテナやチューナで受信される。制御装置88はCPUがメモリに格納されたプログラムを読み出して実行することにより各種の処理を実行する。具体的には、制御装置88は当該映像信号に対して色調整などの各種の画像信号処理を行って映像線駆動回路82へ出力する。また、制御装置88は入力された映像信号に基づいて、走査線駆動回路80や映像線駆動回路82が同期を取るためのタイミング信号を生成し、それら回路に向けて出力する。

30

**【0027】**

駆動電源回路84は画素列ごとに設けられた駆動電源線94に接続され、駆動電源線94及び選択された画素行の駆動TFT70を介してOLED64に電流を供給する。

**【0028】**

基準電源回路86は、OLED64のカソード電極を構成する共通電極（図示せず）と、基準電源線96とに基準電位を与える。基準電位は例えば、接地電位とすることができる。

40

**【0029】**

基準電源線96（給電配線）は画素アレイ部62を横切って配置され、画素アレイ部62内の一部のOLED64のカソード電極に接続される。基準電源回路86からOLED64のカソード電極までの配線抵抗を小さくするために、基準電源線96は画素アレイ部62の短辺に沿った方向に延在するのが好適である。本実施形態では画素アレイ部62が縦長の矩形であるとし、これに対応して基準電源線96は水平方向に配置している。図1では、上述のように基準電源線96を一部のOLED64にしか接続しない構成の例示として、画素アレイ部62にて1本の基準電源線96を配し、1つのOLED64に接続さ

50

れる構成を示している。なお、基準電源線 9 6 は両端を基準電源回路 8 6 に接続することができるが、図 1 では図示の都合上、一方端だけが基準電源回路 8 6 に接続されているように示している。

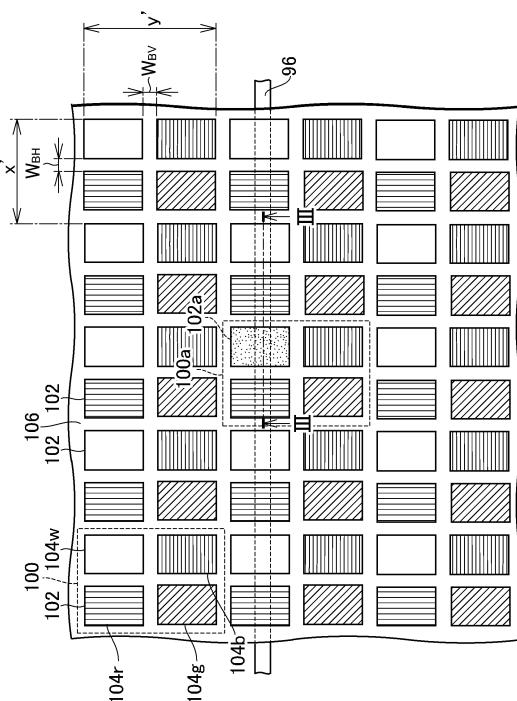

#### 【 0 0 3 0 】

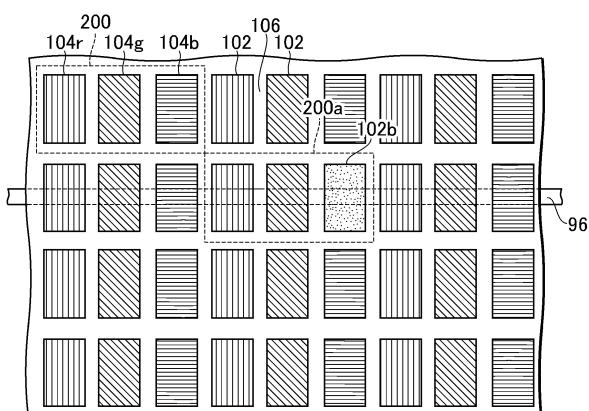

この基準電源線 9 6 を用いた O L E D 6 4 のカソード電極への基準電位の供給についてさらに詳述する。図 2 は有機 E L 表示装置 6 0 の画素アレイ部 6 2 の模式的な部分平面図である。各画素 1 0 0 はベイヤー配列された R G B W の 4 つのサブピクセルからなる。具体的には、水平方向、垂直方向にそれぞれ 2 つ並んだ 4 つの開口領域 1 0 2 が当該 4 つのサブピクセル 1 0 4 に対応し、4 つの開口領域が形成する矩形の 1 つの対角線上に R サブピクセル 1 0 4 r と B サブピクセル 1 0 4 b とが配置され、もう 1 つの対角線上に G サブピクセル 1 0 4 g と W サブピクセル 1 0 4 w とが配置される。なお、本実施形態では各開口領域 1 0 2 は同一の形状・大きさに設計されている。10

#### 【 0 0 3 1 】

開口領域 1 0 2 にはそれぞれ 1 つの O L E D 6 4 が形成される。ここで、サブピクセル 1 0 4 ごとに異なる 4 種類の発光色は、異なる色で発光する 4 種類の O L E D 6 4 を形成するか、例えば、白色発光の O L E D 6 4 とカラーフィルタとを組み合わせることで得られる。

#### 【 0 0 3 2 】

開口領域 1 0 2 を囲んでバンク 1 0 6 が形成される。すなわち、バンク 1 0 6 は水平方向に隣接する開口領域 1 0 2 間を区切り、また垂直方向に隣接する開口領域 1 0 2 間を区切る。バンク 1 0 6 の幅は、O L E D 6 4 を分離して形成するための隔壁としてのバンクの機能を果たすのに足りるだけの大きさに設定することができ、従来技術で述べたようなコンタクトホールを形成できる大きさにする必要はない。バンク 1 0 6 のうち水平方向に並ぶ開口領域 1 0 2 間を区切る部分の幅  $w_{B_H}$  、及び垂直方向に並ぶ開口領域 1 0 2 間を区切る部分の幅  $w_{B_V}$  はそれぞれ任意の開口領域 1 0 2 間で同一とすることができ、また  $w_{B_H}$  と  $w_{B_V}$  とは基本的には同じ値に設定することができる。20

#### 【 0 0 3 3 】

さて、上述した画素 1 0 0 が画素アレイ部 6 2 における基本的な画素であり、画素アレイ部 6 2 を構成する画素の少なくとも過半数は基本画素 1 0 0 からなる。一方、画素アレイ部 6 2 の一部の画素は基本画素 1 0 0 に変更を加えた構造を有した変則画素 1 0 0 a とされる。変則画素 1 0 0 a は、O L E D 6 4 を構成する有機材料層を貫通して上部電極であるカソード電極と基準電源線 9 6 とを電気的に接続する垂直配線（カソードコンタクト）を変則画素 1 0 0 a 内の開口領域に形成される。本実施形態の変則画素 1 0 0 a は基本画素 1 0 0 における W サブピクセル 1 0 4 w に対応する開口領域 1 0 2 a に、有機発光素子の構造に代えてカソードコンタクトを形成される。これ以外の点では変則画素 1 0 0 a は基本画素 1 0 0 と同じ構成である。よって、水平方向の画素ピッチ  $x'$  及び垂直方向の画素ピッチ  $y'$  は画素アレイ部 6 2 にて均一である。30

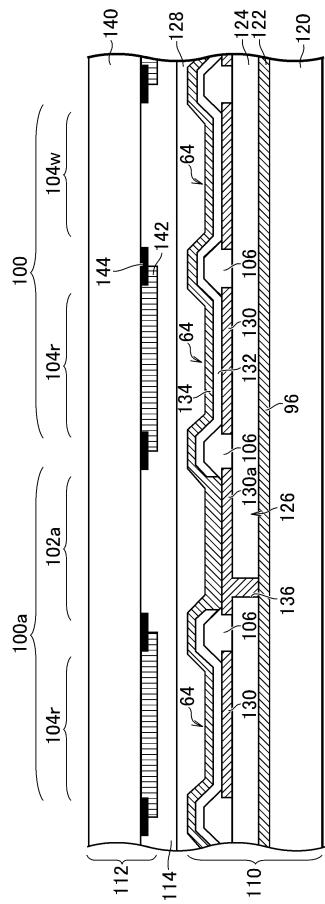

#### 【 0 0 3 4 】

図 3 は有機 E L 表示装置 6 0 の画素アレイ部 6 2 の模式的な部分断面図であり、図 2 に示す水平方向の III - III 線に沿った画素アレイ部 6 2 の垂直断面を表している。有機 E L 表示装置 6 0 は T F T 基板 1 1 0 と対向基板 1 1 2 とを、間に充填層 1 1 4 を挟んで貼り合わせた構造を有する。本実施形態において画素アレイ部はトップエミッション型であり、T F T 基板 1 1 0 上に発光部となる O L E D 6 4 が形成され、O L E D で生じた光を対向基板 1 1 2 から出射する。すなわち、図 3 において O L E D の光は上向きに出射する。また、図 3 に示す有機 E L 表示装置 6 0 におけるカラー化方式はカラーフィルタ方式であり、O L E D にて白色光を生成し、当該白色光をカラーフィルタを通して R G B 各色を得る。なお、W サブピクセル 1 0 4 w はカラーフィルタを配置せず O L E D の白色光をそのまま取り出す。40

#### 【 0 0 3 5 】

T F T 基板 1 1 0 は例えば、ガラス基板 1 2 0 上に回路層 1 2 2 、絶縁膜 1 2 4 、バン

ク 1 0 6 、 O L E D 6 4 、 カソードコンタクト 1 2 6 及び封止膜 1 2 8 などを積層される。

#### 【 0 0 3 6 】

回路層 1 2 2 は上述した画素回路 6 6 、走査信号線 9 0 、映像信号線 9 2 、駆動電源線 9 4 、基準電源線 9 6 などからなり、ガラス基板 1 2 0 の表面に形成される。図 3 には回路層 1 2 2 のうち基準電源線 9 6 のみが表されている。回路層 1 2 2 はトップエミッション型の有機 E L 表示装置 6 0 において、表示面である対向基板 1 1 2 側から見て O L E D 6 4 より後方に位置するので、不透明な材料を用いて構成することができる。特に、基準電源線 9 6 等の各種配線は、 I T O ( Indium Tin Oxide ) や I Z O ( Indium Zinc Oxide ) 等の透明導電材に比べて導電率が高い金属を用いて形成し低抵抗とすることができます。

10

#### 【 0 0 3 7 】

O L E D 6 4 は下から順に下部電極 1 3 0 、有機材料層 1 3 2 及び上部電極 1 3 4 を積層された構造を有する。有機材料層 1 3 2 は正孔輸送層、発光層、電子輸送層等を含んで構成される。

#### 【 0 0 3 8 】

本実施形態では下部電極 1 3 0 及び上部電極 1 3 4 はそれぞれ O L E D 6 4 のアノード電極、カソード電極を構成し、これらの間に印加される電気信号により発光層での発光が制御される。

#### 【 0 0 3 9 】

下部電極 1 3 0 は画素ごとに分離して形成される。下部電極 1 3 0 は I T O 、 I Z O などで形成される。下部電極 1 3 0 はコンタクトホール（図示せず）を介して、回路層 1 2 2 に形成される T F T （図 1 に示す駆動 T F T 7 0 ）に電気的に接続され、駆動部及び画素回路により映像信号に応じた電流を供給される。

20

#### 【 0 0 4 0 】

なお、本実施形態では有機 E L 表示装置 6 0 はトップエミッション方式であり、下部電極 1 3 0 は光反射率が高い材料で形成された反射層上に透明導電膜を積層した 2 層構造とすることができる。例えば、反射層はアルミニウム ( A l ) や銀 ( A g ) 等で形成することができ、発光層からの光を表示面、つまり対向基板 1 1 2 側へ反射させる。

#### 【 0 0 4 1 】

上部電極 1 3 4 は基本的に画素アレイ部 6 2 全体の画素に亘ってつながって形成された共通電極である。上部電極 1 3 4 は I T O 、 I Z O などの透明電極材料で形成される。

30

#### 【 0 0 4 2 】

上部電極 1 3 4 の端部は配線を介して図 1 に示す基準電源回路 8 6 に接続され、基準電源回路 8 6 から基準電位を供給される。

#### 【 0 0 4 3 】

さらに、上部電極 1 3 4 は変則画素 1 0 0 a にて W サブピクセルに対応する位置の開口領域 1 0 2 a に形成されるカソードコンタクト 1 2 6 により基準電源線 9 6 に接続され、基準電源線 9 6 を介して基準電源回路 8 6 から基準電位を供給される。上述したように基準電源線 9 6 は金属で低抵抗とすることができます、基準電源回路 8 6 とカソードコンタクト 1 2 6 との間での基準電源線 9 6 による電圧降下は上部電極 1 3 4 での電圧降下より小さい。そこで、カソードコンタクト 1 2 6 を介した基準電位の供給により画素アレイ部 6 2 での上部電極 1 3 4 の電位の一様性が向上するように変則画素 1 0 0 a が配置され、 O L E D 6 4 の輝度のシェーディングを抑制する。

40

#### 【 0 0 4 4 】

上述のようにカソードコンタクト 1 2 6 及び基準電源線 9 6 を用いることで、上部電極 1 3 4 を薄くしてもシェーディングを抑制することが可能となる。よって、上部電極 1 3 4 を薄くして上部電極 1 3 4 の透過率を向上させることができるので、所望の表示輝度を得るための O L E D 6 4 の駆動電力を低減できる。

#### 【 0 0 4 5 】

カソードコンタクト 1 2 6 は絶縁膜 1 2 4 を貫通するコンタクトホール 1 3 6 に充填さ

50

れた導電材と、下部電極 130a と、有機材料層 132 を貫通する孔に充填された上部電極 134 の導電材とで構成される。

#### 【0046】

封止膜 128 は OLED 64 を形成した画素アレイ部 62 の全面に積層される。封止膜 128 は充填層 114 に含まれる水分などの透過を阻止し、OLED を保護する機能を有する。

#### 【0047】

対向基板 112 は例えば、ガラス基板 140 などの透明な基板にカラーフィルタ 142 などが積層された構造を有する。例えば図 3 に示す断面では、R サブピクセル 104r の位置に赤色の波長帯域を透過するカラーフィルタ 142 が配置される。なお、既に述べたように、W サブピクセル 104w にはカラーフィルタ 142 は配置されない。カラーフィルタ 142 の境界にはブラックマトリクス 144 が配置される。10

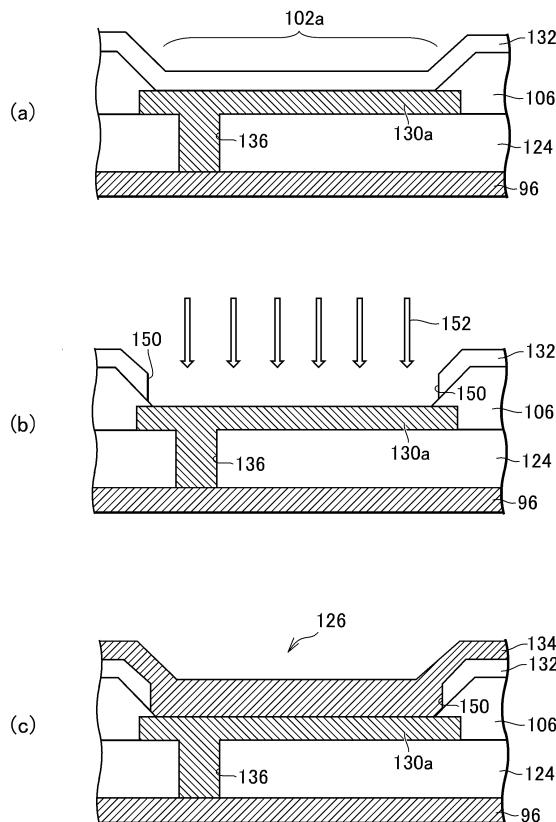

#### 【0048】

図 4 は、カソードコンタクト 126 の形成方法を説明する概略のプロセスフロー図であり、同図は図 3 の変則画素 100a の開口領域 102a にてカソードコンタクト 126 に関連する部分の主な製造工程における模式的な垂直断面図を示している。

#### 【0049】

図 4 (a) はガラス基板 120 の上に回路層 122 、絶縁膜 124 、下部電極 130 、バンク 106 及び有機材料層 132 を順次形成した状態を示している。これら各層の形成は基本的に OLED 64 が形成される通常の開口領域 102 、又は従来技術と同様に行うことができる。開口領域 102a では下部電極 130a の下に回路層 122 として基準電源線 96 が配置され、絶縁膜 124 には基準電源線 96 の上にコンタクトホール 136 が形成される。ちなみに、通常の開口領域 102 では絶縁膜 124 に、下部電極 130 を駆動 TFT 70 に接続するためのコンタクトホールが形成されるが、開口領域 102a には当該コンタクトホールに代えてコンタクトホール 136 が形成される。なお、通常の開口領域のコンタクトホールと開口領域 102a のコンタクトホール 136 とは同一工程で形成することができる。コンタクトホール 136 には導電材が充填される。20

#### 【0050】

絶縁膜 124 にコンタクトホール 136 を形成した後、絶縁膜 124 の表面に下部電極 130 を構成する導電膜を積層し、フォトリソグラフィ技術によりパターニングして隣接する開口領域 102 の下部電極 130 とは分離した下部電極 130a を形成する。ちなみに、上述のコンタクトホール 136 への導電材の充填は、下部電極 130a を構成する導電材料の積層工程で行うことが可能である。すなわち、下部電極 130a を構成する導電材を絶縁膜 124 の表面と共にコンタクトホール 136 に充填して基準電源線 96 と下部電極 130a との間を電気的に接続することができる。30

#### 【0051】

下部電極 130a の形成後、バンク 106 が形成され、有機材料層 132 が積層される。図 4 (a) は当該工程まで完了した状態を示している。

#### 【0052】

次に、開口領域 102a の有機材料層 132 に貫通孔 150 を開ける (図 4 (b))。貫通孔 150 は例えば、レーザービーム 152 を照射して有機材料層 132 を除去することで形成できる。貫通孔 150 を形成した後、導電膜を積層して上部電極 134 を形成する (図 4 (c))。上部電極 134 を構成する導電膜は貫通孔 150 に充填され、貫通孔 150 の底面に露出する下部電極 130a に電気的に接続される。これにより、有機材料層 132 を貫通して上部電極 134 と基準電源線 96 とを電気的に接続する垂直配線となるカソードコンタクト 126 が開口領域 102a に形成される。40

#### 【0053】

なお、インクジェット方式で各開口領域 102 ごとに有機材料層 132 を塗り分ける場合には、変則画素 100a の開口領域 102a には予め有機材料層 132 を形成しないことで、その除去工程を省略することができる。また、例えば、蒸着で有機材料層 132 を50

形成する場合には、ファインメタルマスクを用いて開口領域 102a を有機材料層 132 の非成膜領域とすることができる。

#### 【0054】

上述の有機 E L 表示装置 60 は画素アレイ部 62 に二次元配列される画素の一部が変則画素 100a である。画素アレイ部 62 における変則画素 100a の位置は制御装置 88 のメモリに予め格納される。制御装置 88 は入力される映像信号に基づいて各画素のサブピクセル 104 の輝度値を表す信号を生成して映像線駆動回路 82 へ出力する。その際、制御装置 88 は、メモリに格納された変則画素 100a の位置の情報を参照して、入力映像信号が表す画素が基本画素 100 であるか変則画素 100a であるかを判断する。そして、制御装置 88 は、基本画素 100 の位置に対応する映像信号を R G B W の 4 種類の色成分信号に変換し、一方、変則画素 100a の位置に対応する映像信号を R G B の 3 種類の色成分信号に変換する。当該変換では、入力映像信号が表す色・輝度が、基本画素 100 では R G B W 色の発光の合成で表現されるように R G B W 各成分信号の強度が定められ、変則画素 100a では R G B 色の発光の合成で表現されるように R G B 各成分信号の強度が定められる。これにより、基本画素 100 と変則画素 100a とで基本的に同じ表示特性が実現される。10

#### 【0055】

##### [第2の実施形態]

以下、本発明の第2の実施形態に係る有機 E L 表示装置 60 を説明する。本実施形態の構成要素のうち上記第1の実施形態と共通のものには同一の符号を付して基本的に当該構成要素についての説明を省略し、主として第1の実施形態との相違点を説明する。20

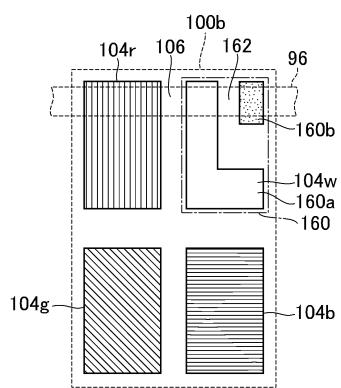

#### 【0056】

第2の実施形態における基本画素 100 は第1の実施形態と同様、ベイラー配列された R G B W の 4 つのサブピクセルからなる。第2の実施形態と第1の実施形態との相違点は変則画素の構造にある。図5は第2の実施形態の変則画素 100b の模式的な平面図である。変則画素 100b は基本画素 100 の W サブピクセル 104w の開口領域に対応する領域 160 の一部分に、有機発光素子の構造に代えてカソードコンタクト 126 を形成される。具体的には、領域 160 をバンク 162 で 2 つの領域 160a, 160b に区画し、例えば領域 160a には基本画素 100 と同様に白色発光の O L E D 64 を形成する一方、領域 160b には有機材料層 132 を設けず、カソードコンタクト 126 を形成する30。

#### 【0057】

本実施形態では制御装置 88 は変則画素 100b の位置に対応する映像信号を R G B W の 4 種類の色成分信号に変換する。その際、変則画素 100b の W サブピクセル 104w の面積が基本画素 100 より小さいことを考慮する。例えば、W サブピクセル 104w の面積が小さい分の輝度低下を、R G B サブピクセル 104 の発光強度を上げて補償することもできるし、W サブピクセル 104w の O L E D の電流密度を増加させて補償することもできる。

#### 【0058】

##### [第3の実施形態]

以下、本発明の第3の実施形態に係る有機 E L 表示装置 60 を説明する。本実施形態の構成要素のうち上記第1の実施形態と共通のものには同一の符号を付して基本的に当該構成要素についての説明を省略し、主として第1の実施形態との相違点を説明する。40

#### 【0059】

図6は本実施形態の有機 E L 表示装置 60 の画素アレイ部 62 の模式的な部分平面図である。本実施形態は、基本画素 200 が R G B の 3 つのサブピクセルからなる点、及びカソードコンタクト 126 が変則画素 200a にて B サブピクセルに対応する位置の開口領域 102b に形成される点で第1の実施形態と相違する。

#### 【0060】

本実施形態では変則画素 200a は R G の 2 つのサブピクセルからなる。そのため、力50

ソードコンタクト 126 を設けたことによる B サブピクセルの欠損を信号処理で補償することはできないが、B は R G B のうち最も視感度が低い色であるので、B サブピクセルをカソードコンタクト 126 の形成領域とする構成は画質の劣化が少ない。特に、変則画素 200a が画素アレイ部 62 のうちごく少数である場合には、画質劣化は目立たない。一方、カソードコンタクト 126 を設けることにより、第 1、第 2 の実施形態と同様、シェーディングが抑制され、また O L E D での消費電力を低減できる効果が得られる。

#### 【0061】

なお、上記各実施形態では有機 E L 表示装置 60 はトップエミッション型としたが、ボトムエミッション型の有機 E L 表示装置 60 においても基準電源線 96 及びカソードコンタクト 126 を用いた上部電極 134 の実質的な低抵抗化を図る本発明を適用することができる。例えば、大面積の表示装置において、本発明の構成を適用することで、上部電極 134 を厚くして低抵抗化を図るだけよりも一層好適にシェーディングを抑制することが可能となる。

#### 【符号の説明】

#### 【0062】

60 有機 E L 表示装置、62 画素アレイ部、64 O L E D、66 画素回路、68 点灯 T F T、70 駆動 T F T、72 キャパシタ、80 走査線駆動回路、82 映像線駆動回路、84 駆動電源回路、86 基準電源回路、88 制御装置、90 走査信号線、92 映像信号線、94 駆動電源線、96 基準電源線、100, 200 基本画素、100a, 100b, 200a 変則画素、102 開口領域、104 サブピクセル、106 バンク、110 T F T 基板、112 対向基板、114 充填層、120, 140 ガラス基板、122 回路層、124 絶縁膜、126 カソードコンタクト、128 封止膜、130 下部電極、132 有機材料層、134 上部電極、136 コンタクトホール、142 カラーフィルタ、144 ブラックマトリクス、150 貫通孔。

【図 1】

【図 2】

【図3】

【 図 4 】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

---

フロントページの続き

審査官 中村 博之

(56)参考文献 特開2012-151103(JP,A)

特開2008-047515(JP,A)

特開2005-149800(JP,A)

特開2007-287354(JP,A)

特開2003-295792(JP,A)

国際公開第2007/148540(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H05B 33/26

H01L 51/50

H05B 33/12