**(12) STANDARD PATENT

(19) AUSTRALIAN PATENT OFFICE**

**(11) Application No. AU 2006314714 B2**

(54) Title **A readout chip for single photon counting**

(51) International Patent Classification(s)

**H01L 27/146** (2006.01)      **H03K 21/12** (2006.01)

(21) Application No: **2006314714**      (22) Date of Filing: **2006.11.20**

(87) WIPO No: **WO07/057213**

(30) Priority Data

(31) Number **05025326.9**      (32) Date **2005.11.21**      (33) Country **EP**

(43) Publication Date: **2007.05.24**

(44) Accepted Journal Date: **2010.11.11**

(71) Applicant(s)

**Paul Scherrer Institut**

(72) Inventor(s)

**Schmitt, Bernd**

(74) Agent / Attorney

**Spruson & Ferguson, Level 35 St Martins Tower 31 Market Street, Sydney, NSW, 2000**

(56) Related Art

**WO 2004/064168**

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

24 May 2007 (24.05.2007)

PCT

(10) International Publication Number

WO 2007/057213 A1(51) International Patent Classification:

H01L 27/146 (2006.01) H03K 21/12 (2006.01)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/EP2006/011098(22) International Filing Date:

20 November 2006 (20.11.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

05025326.9 21 November 2005 (21.11.2005) EP

(71) Applicant (for all designated States except US): PAUL SCHERRER INSTITUT [DE/DE]; CH-5232 Villigen PSI (CH).

(72) Inventor; and

(75) Inventor/Applicant (for US only): SCHMITT, Bernd [DE/CH]; Im Tiergarten 59, CH-8055 Zürich (CH).

(74) Agent: FISCHER, Michael; c/o Siemens AG, Postfach 22 16 34, 80506 München (DE).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Declaration under Rule 4.17:

— of inventorship (Rule 4.17(iv))

[Continued on next page]

(54) Title: A READOUT CHIP FOR SINGLE PHOTON COUNTING

(57) **Abstract:** It is the aim of the present invention to improve the properties and the speed of readout electronic significantly without losing accuracy of the counting in photon-counting imaging devices. This aim is achieved according to the present invention by a readout chip (2) for single photon counting, comprising: a) a plurality of N individually working channels each assigned to a respective detector diode; each channel comprising a counter ( $8_1$  to  $8_{128}$ ) being designed as a binary counter having a length of M bits and a number of programmable bits (pb1 to pb128); b) a serial or parallel data input shift register (4) for entering values for the counter ( $8_1$  to  $8_{128}$ ) and the programmable bits (pb1 to pb128); and c) a number of data output shift register (16); each having a number of K data outputs (20), whereby means (18) are provided for selectively multiplexing each of the K data outputs (20) onto a selectable bit of the data output shift register (16). These features allow a much faster readout of the counter since the counter can be readout in parallel groups of K bits each cycle. Further, a variable length of selectable bits for each counter in each channel can be readout advantageously by multiplexing the K data outputs to the bits of interest which increases the speed of readout tremendously.

WO 2007/057213 A1

**Published:**

— *with international search report*

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**A readout chip for single photon counting**

The present invention relates to a readout chip for single photon counting.

5 X-ray diffraction patterns are useful in the analysis of both organic and inorganic crystallographic structures. Especially organic materials, such as protein crystals, impose stringent requirements on x-ray detectors, particularly where the x-ray source is high flux synchrotron radiation that enables and

10 requires, due to the radiation damage, an experiment to be done rapidly. Furthermore, an important and developing field is time-resolved diffraction experiments using synchrotron radiation, such as crystallography and/or powder diffraction analysis. Monitoring a time-dependent reaction in a sample,

15 i.e. a crystal or a powder, can elucidate the time-dependent crystal/molecular changes that occur in a chemical reaction. High time resolution is often critical in such monitoring.

20 A fast single photon-counting imaging device for the above-mentioned purposes has been disclosed in the international patent application WO 2004/064168. This reference teaches in detail a photon-counting imaging device for single x-ray counting which comprises:

- 25 a) a layer of photosensitive material;

- b) a source of bias potential;

- c) a source of threshold voltage supply;

- d) an NxM array of photodetector diodes arranged in said layer of photosensitive material; each of said photodetector diodes having a bias potential interface and a diode output interface, said bias potential interface of each photodetector diode being connected to said bias potential;

- 30 e) an NxM array of high gain, low noise readout unit cells, one readout unit cell for each photodetector diode;

- f) each readout unit cell comprising an input interface connected to said diode output interface, a high-gain voltage amplifying means comprising a comparator unit, a

digital counter unit, comprising a digital counter, and a digital counter output interface connected in series, each digital counter unit counting an output signal of the comparator unit; said digital counter output signal is proportional to the number of absorbed incident photons in the respective photodetector diode,

5 g) a multiplexing means comprising a row select and a column select allowing to access each of the readout cell units, i.e. to read out the digital data as actually stored in the digital counter to the digital counter output interface;

h) each digital counter output interface connected to an output bus;

10 i) said output bus being connected to a data processing means controlling the multiplexing means.

According to these measures, a photon counting imaging device is created having an architecture of the readout circuitry that allows to be tolerant with respect to a local defect of a detector diode and/or readout unit cell and that allows to control and 15 redesign the program and/or the status of each detector diode and/or readout unit cell in order to achieve a fast photon counting imaging device.

However, even for this fast photon counting imaging device it is desirable to increase the speed of the data readout. So far, the counter in the reference cited above has been 20 designed as a pseudo-random counter, such as an 18 bit shift register with an XOR feedback. The data from this counter is serially transmitted on one digital output pin during readout. For an 18 bit shift register a readout time of at least 1+18+1 cycles is required.

25 Therefore, a need exists to improve the properties and the speed of readout electronic significantly without losing accuracy of the counting.

According to a first aspect of the present disclosure, there is provided a readout chip for single photon counting which comprises:

30 a) a plurality of N individually working channels each assigned to a respective detector diode; each channel comprising a counter being designed as a binary counter having a length of M bits and a number of programmable bits, wherein said binary counter enables a variable length of selectable bits to be readout;

b) a serial shift register or parallel data input register for entering values for the counter and the programmable bits; the binary counter enables a variable length readout since for a low number of counts not all bits have to be read out (in contrast to e.g. a pseudo random counter realized as a shift register with an X-or feedback) and

5 c) a number of data output shift register; each having a number of K data outputs, whereby means are provided for selectively multiplexing each of the K data outputs onto a selectable bit of the data output shift register.

These features allow a much faster readout of the counter since the counter can be

10 readout in parallel groups of K bits. Further, for each counter in each channel only a variable length of selectable bits can be readout by multiplexing the K data outputs to the bits of interest which increases the readout speed tremendously, i.e. considering in crystallographic investigations some rare regions with higher counting rates and the gross part of regions with comparably low counting rates due to the regular lattice

15 structure of the probe.

In order to further speed up the operation, the data input shift register, the data output shift register as well as the channel select shift register and the counters comprise a CLEAR and a SET CONTROL signal which allows to clear and set the registers within

20 one cycle per signal. To simplify the generation of control signals and to reduce their number the control signals are multiplexed to the data input-, data output- and channel select shift registers as well as the counter. However the signals needed for the readout are also available non multiplexed in order not to compromise the readout speed.

25 In order to be able to interfere with the analogue part of the readout electronic, the programmable bits can be used for a DAC, i.e. for fine-tuning of a comparator threshold, enabling/disabling of a calibration pulse, for enabling/disabling the analogue output of a channel and for enabling the output of the channels comparator.

30 In a preferred embodiment of the present disclosure, the data input shift register and the data output shift register may have at least the length of the counter. Preferably, the data input shift register has additionally a number of bits for the programmable bits which are used as explained above. Of course, the length of the counter may be an odd or an

even multiple of the number K of the data outputs. According to the value of the multiple a respective number of integer cycles is used to read out the complete data output shift register. For example, assuming a 24 bit binary counter and a 4 bit parallel data output, six cycles for reading the 24 bit string counting value plus three cycles for selecting, controlling and resetting the data output shift register are required to readout the counter value of one channel. In case only four bits are necessary to be read out, like the four minor important bits 0 through 3, only 4 cycles are required in total. These features allow to cut down the readout time by more than 50% for those "channels of minor interest" (lower counting rates).

10

Further advantageous features of the preferred embodiments of the present disclosure can be learned from the other depending claims.

15

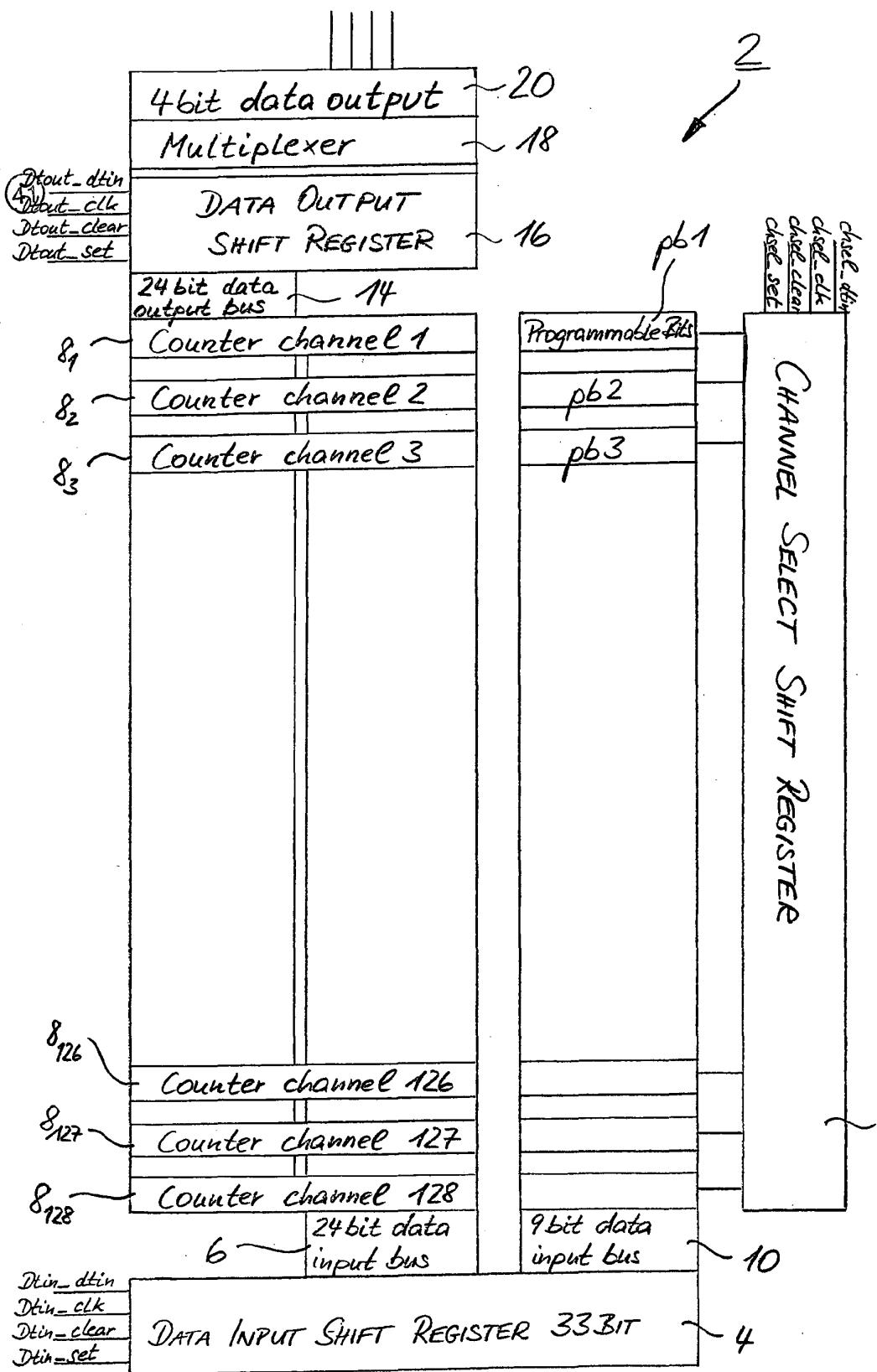

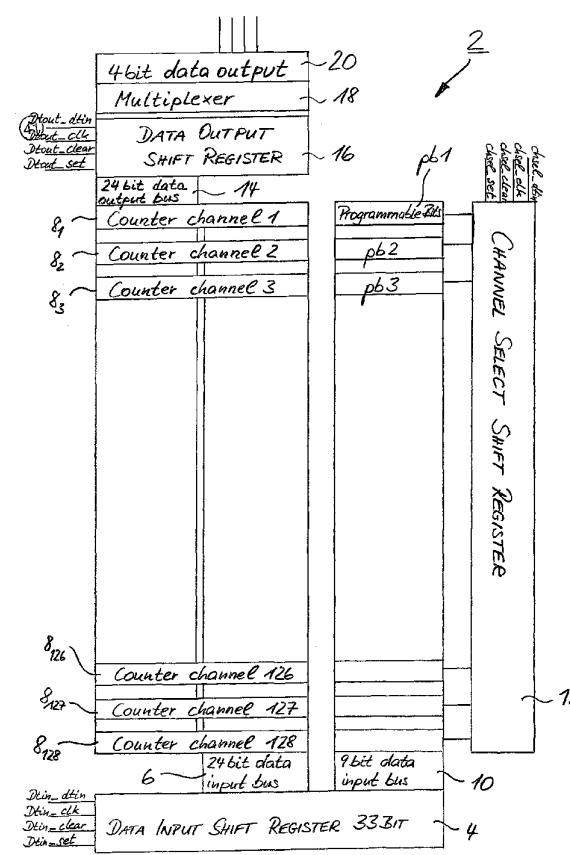

Examples of the present invention will be described in detail with reference to the following drawing. The figure depicts a schematic view on the architecture of a readout chip 2 for

use in a photon-counting imaging device. In the present example, the readout chip 2 comprises a data input shift register 4 having a length of 33 bits. 24 bits of the data input shift register 4 is associated with a 24 bit data input bus 6 which connects to selectable counters  $8_1$  to  $8_{128}$ . The remaining nine bits of the data input shift register 4 are associated via a 9-bit data input bus 10 with the programmable bits pb1 to pb128 of each of the 128 channels. For selecting the channel, a channel select shift register 12 is provided. The programmable bits pb1 to pb128 are used for example for enabling/disabling the respective channel, for forwarding the analogue signal (which reflects the number and energy of the incident photons on each diode) to the analogue output of the chip (i.e. for calibration and debugging purposes), other bits are used for programming the DAC (6 bits), for fine-tuning of the comparator threshold, for enabling/disabling of a calibration pulse etc.

The counter  $8_1$  to  $8_{128}$  are selectively connectable via a 24-bit data output bus 14 to a data output shift register 16. By a multiplexer 18 the 24 bits of the data output shift register can be selectively assigned to a 4-bit data output 20 which allows in the present example to readout in parallel four selectable bits of the data output shift register 16. The multiplexer, in the present example, is controlled by bits of the data input shift register. Considering exemplarily the diffraction pattern of a probe having a regular crystalline lattice, most of the channels will have comparably small counting rates where a readout of 4 or 8 bits appear to be sufficient for these channels; only those channels having positions corresponding to the lattice structure of the probe will receive significantly higher counting rates which will lead to the readout of all 24 bits of the counter of the respective channels. In order to further speed up the operation, all the registers 4, 12,  $8_1$ - $128$  and 16 comprise a leg for a CLEAR and a SET CONTROL signal. These control signals are further multiplexed which

means that the number of control signals is reduced while further simplifying the operation. This can be done for example by mode multiplexing of the respective control signals.

5

The example shown in the drawing comprises a basic layout of the readout chip 2 which also allows various modifications. One preferred modification can be the multiplication of the architecture with respect to the data output shift register 10 16 for which several data output shift register could be provided. This feature enables a readout of several channels simultaneously, for example a second data output shift register enables the set-up to readout 2 X 64 channels instead of 1 X 128 channels. The channels could also be 15 organized as a 2 dimensional matrix (e.g. for 2-dimensional detectors).

Another preferred modification may propose a data output 20 having more than 4 bits up to the maximal length of the 20 counter  $8_1$  to  $8_{128}$  which would allow to readout the counter much faster and in parallel mode in case of the same length for both the counter and the data output within only one cycle (plus control signal cycles).

25 The counter of a distinct channel can be set to an arbitrary value. The values for the programmable bits and the counter value can be entered into the readout chip 2 by the serial data input shift register 4 which could be also be a parallel data input register for the complete length of the counters. 30 The input shift register also serves to program the multiplexer for the data output.

**The claims defining the invention are as follows:**

1. A readout chip for single photon counting, comprising:

- a) a plurality of N individually working channels each assigned to a respective detector diode; each channel comprising a counter being designed as a binary counter having a length of M bits and a number of programmable bits, wherein said binary counter enables a variable length of selectable bits to be readout;

- b) a serial shift register or parallel data input register for entering values for the counter and the programmable bits; and

- c) a number of data output shift register; each having a number of K data outputs, whereby means are provided for selectively multiplexing each of the K data outputs onto a selectable bit of the data output shift register.

2. The readout chip according to claim 1, wherein the data input shift register and the data output shift register as well as a channel select shift register and counter comprise a CLEAR and a SET CONTROL signal leg.

3. The readout chip according to either one of claims 1 and 2, wherein control signals are multiplexed and the ones needed for the readout are also available non multiplexed.

4. The readout chip according to any one of the preceding claims, wherein the programmable bits are used for a DAC.

- 25 5. The readout chip according to claim 4, wherein the programmable bits are used for at least one of: fine-tuning of a comparator threshold, enabling/disabling of a calibration pulse, for enabling/disabling the analogue output of a channel, and for enabling the output of the channels comparator

- 30 6. The readout chip according to any one of the preceding claims, wherein the data input shift register and the data output shift register have at least the length of the counter.

7. The readout chip according to any one of the preceding claims, wherein the length of the counter is an odd or an even multiple of the number K of the data outputs.

- 8 -

8. A readout chip for single photon counting, said readout chip being substantially as described herein with reference to the accompanying drawing.

DATED this thirteenth Day of April, 2010

**Paul Scherrer Institut**

Patent Attorneys for the Applicant

SPRUSON & FERGUSON