본 발명은 반도체 패키지의 제조방법에 관한 것으로, 특히 반도체 칩이 부착되는 리드프레임을 열을 방출하는 히트싱크로서 기능하도록 한 에리어 어레이형(Area array type) 반도체 패키지에 관한 것이다.

일반적으로 비지에이(BGA:Ball Grid Array) 반도체 패키지는 주어진 면적에서 다핀화를 실현할 수 있고, 외부단자의 길이가 짧아서 외부충격으로부터 휙발생이 방지되며, 전기적인 신호 전달의 용이함과 아울러 마더보드(mother board)에 패키지를 실장시, 로(furnace)에서 일시에 리플로우(reflow)시켜서 실장(mounting)함으로서 시간이 절감되어 널리 사용되어져 왔다.

이와같은 종래 비지에이 패키지에 대해 설명하면 다음과 같다.

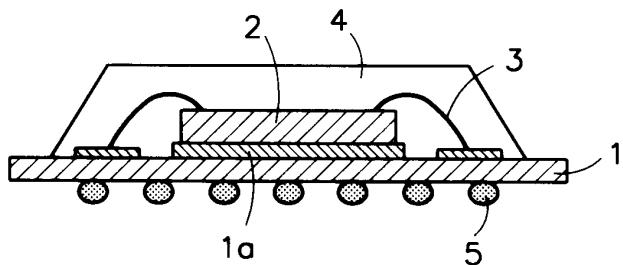

도 1은 종래 비지에이 반도체 패키지의 종단면도로서, 이에 도시된 바와 같이, 다수개의 메탈패턴(미도시)이 형성된 인쇄회로기판(Printed Circuit Board : 이하 PCB라 한다.)(1)과, 상기 PCB상(1)에 접착제(1a)를 매개로 부착된 다수 개의 본딩패드(미도시)가 형성된 반도체 칩(2)과, 상기 본딩패드들과 상기 메탈패턴을 각각 전기적으로 연결하기 위한 금속와이어(3)와, 상기 반도체 칩(2)과 금속와이어(3)를 포함하는 상기 PCB(1)상의 일정면적을 밀봉한 물당수지(4)와, 상기 PCB(1)의 하면상에 부착된 외부 단자인 솔더볼(5)로 구성된다.

상기 메탈패턴은 상기 PCB(1)의 상하면에 노출되도록 형성되고, 또한 상기 PCB(1)의 상,하부를 전기적으로 연결하는 전기적 통로가 된다.

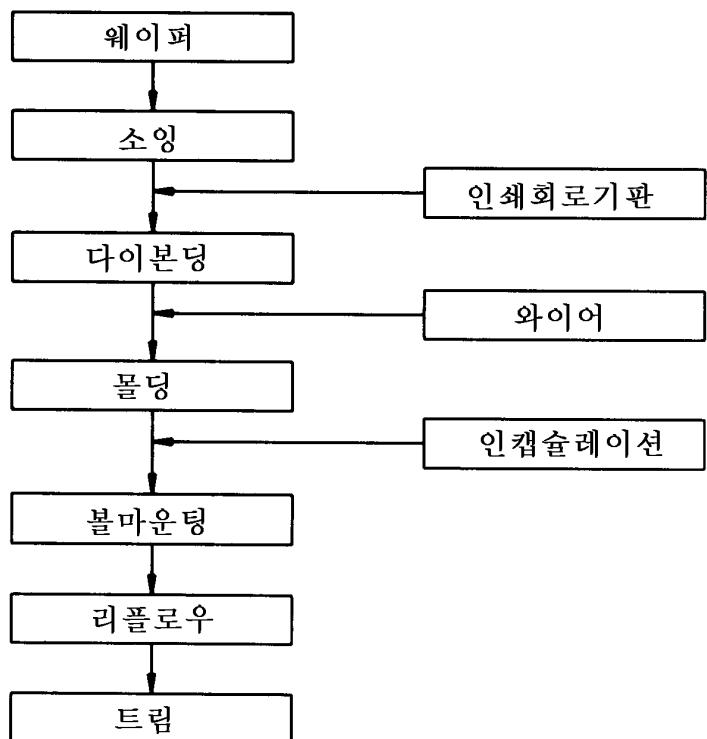

도 2는 종래 비지에이 반도체 패키지의 제조방법을 설명하기 위한 공정 플로우차트(flow chart)로서, 이에 도시된 바와 같이, 웨이퍼(wafer)내에 형성된 복수의 반도체 소자를 개개의 반도체 칩으로 분리하는 소잉(sawing)공정과, 상기 개개로 분리된 반도체 칩(chip)들을 PCB상에 각각 부착시키는 다이본딩(die bonding)공정과, 상기 각 반도체 칩의 본딩패드들과 PCB의 메탈패턴간을 복수의 와이어로 연결하는 와이어본딩(wire bonding)공정과, 상기 반도체 칩과 와이어를 포함한 PCB상의 일정면적을 물당수지로 밀봉하는 물당(molding)공정과, 상기 PCB의 하면상에 외부출력단자인 솔더(solder)를 형성하는 볼마운팅(ball mounting)공정과, 이렇게 패키징(packaging)된 반도체 패키지를 로(furnace)에서 리플로우하는 리플로우(reflow)공정을 포함하여 만들어지고, 이와같이 제조된 종래 비지에이 반도체 패키지는 트림공정을 거쳐 바로 마더보드에 직접 마운팅되어진다.

상기와 같이 구성된 종래 비지에이 반도체 패키지는 출력단자로 사용되는 솔더볼이 반도체 칩의 활성표면(즉, 반도체 칩의 상면)의 반대쪽에 위치하므로 반도체 칩에서 와이어를 거쳐 인쇄회로기판까지의 높이로 인해 반도체 패키지의 크기를 축소시키는데에 제한이 있다는 문제점이 있었다.

또한, 반도체 칩에서 발생하는 열의 외부 방출이 효과적이지 못하여 고성능 반도체 소자의 패키징에 적합치 않은 문제점이 있었다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 이와같은 문제점을 해결하기 위해 반도체 칩이 부착되는 일반적인 리드프레임을 열을 방출하는 히트싱크로 작용토록 함으로서 고열을 방출하는 고성능 반도체 소자의 패키징에 적합한 에리어 어레이형 반도체 패키지의 제조방법을 제공하는데 그 목적이 있다.

상기와 같은 목적을 달성하기 위하여 본 발명에 따른 에리어 어레이형 반도체 패키지는 다이패들과 그의 단부에 일정간격으로 형성된 다수개의 리드를 포함하는 리드프레임과; 상기 리드프레임의 다이패들상에 부착된 상면에 다수개의 본딩패드를 가진 반도체 칩과; 상기 반도체 칩의 각 본딩패드상에 형성된 범프와; 상기 범핑된 반도체 칩을 포함한 상기 리드프레임상의 일정면적을 밀봉한 물당수지로 구성된 것을 특징으로 한다.

또한, 상기와 같은 목적을 달성하기 위한 본 발명에 따른 에리어 어레이형 반도체 패키지의 제조방법은 다수개의 리드를 가진 리드프레임의 다이패들상에 다수개의 본딩패드를 가진 반도체 칩을 부착하는 공정과; 상기 각 본딩패드상에 범프를 형성하는 공정과; 상기 범핑된 반도체 칩을 포함한 상기 리드프레임상의 일정면적을 물당수지로 물당하는 공정과; 상기 리드와 다이패들의 일부분을 상방 또는 하방 중 어느 하나로 절곡하는 공정을 포함하여 이루어지는 것을 특징으로 한다.

### 발명의 구성 및 작용

이하, 본 발명에 따른 에리어 어레이형 반도체 패키지 및 그 제조방법에 대해 첨부된 도면을 참조하여 설명한다.

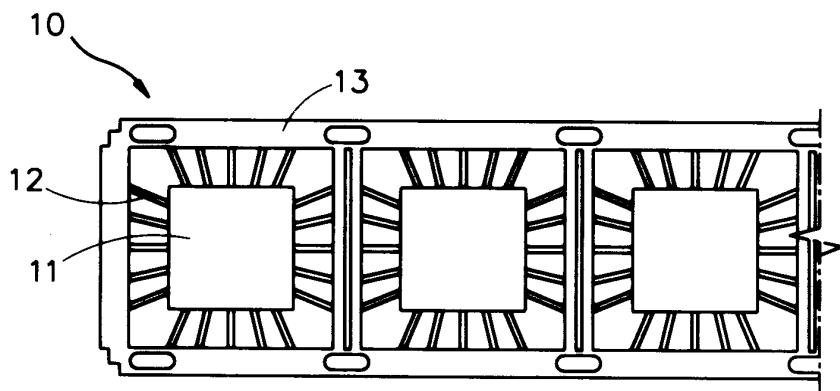

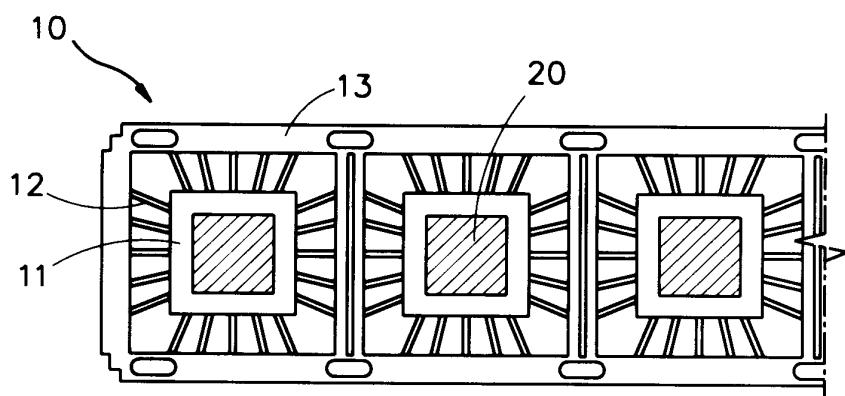

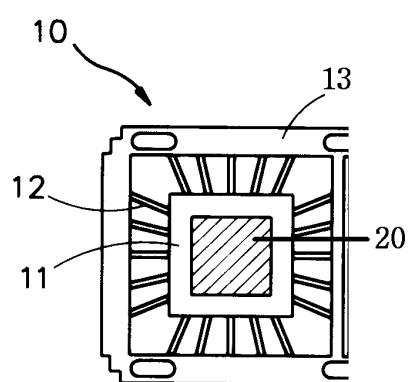

도 3은 본 발명에 따른 리드프레임(10)의 평면도로서, 이에 도시된 바와 같이, 반도체 칩이 놓여지는 사각형상의 다이패들(11)과, 상기 다이패들(11)의 각 단부에 일정간격으로 형성된 다수개의 리드(12)와, 상기 각 리드(12)들을 지지하는 지지부재(13)로 구성된다. 상기 리드프레임(10)은 구리, 구리합금, 텁스텐 합금 등으로 만들어지고, 상기 지지부재(13)에는 요철 또는 훌이 형성되어 있다.

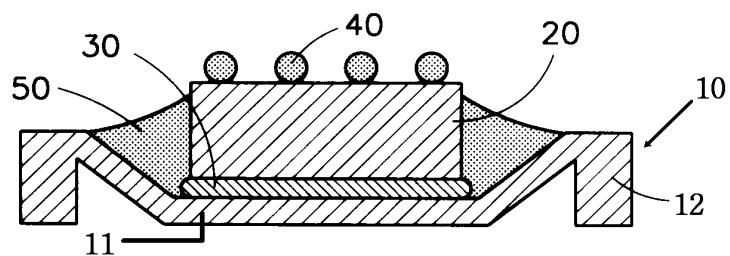

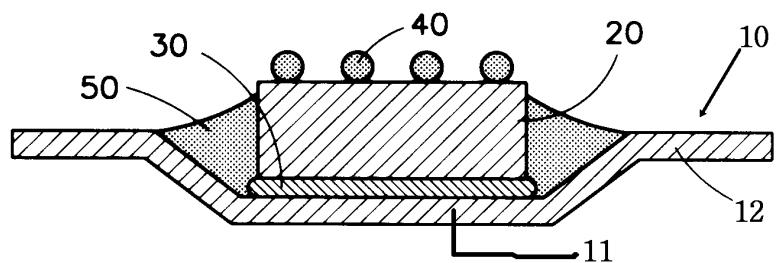

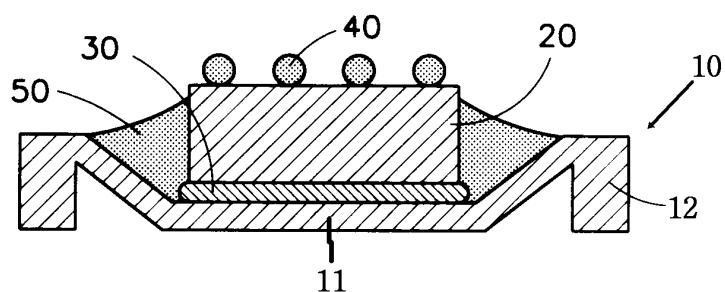

도 4은 본 발명에 따른 에리어 어레이형 반도체 패키지의 종단면도로서, 이에 도시된 바와 같이, 다수개의 리드(12)를 가진 리드프레임(10)의 다이패들(11)상에 부착된 상면에 다수개의 본딩패드(미도시)를 가진 반도체 칩(20)과; 상기 반도체 칩(20)의 각 본딩패드상에 부착된 범프(40)와; 상기 범핑된 반도체 칩(20)을 포함한 상기 리드프레임상의 일정면적을 밀봉한 물당수지(50)로 구성된다.

상기 반도체 칩(20)이 놓여진 부분 이외의 상기 다이패들(11) 부분은 상방으로 절곡되어 있고, 상기 각 리드(12)의 일부도 하방으로 절곡되어 있으며, 상기 리드프레임(10)의 다이패들(11) 하면과 하방으로 절곡된 상기 각 리드(12)의 하면은 동일선상에 있다.

상기 도 4의 미설명 부호 30은 열전도성 접착부재이다.

도 5a 내지 도 5d 는 본 발명에 따른 에리어 어레이형 반도체 패키지의 제조방법을 순차적으로 도시한 것

으로서, 도 5a 는 평면도이고, 도 5c 내지 도 5e 는 종단면도이며, 이에 대한 상세한 설명은 다음과 같다.

먼저, 도 5a 에 도시된 바와 같이, 리드프레임(10)의 각 다이패들(11)상에 반도체 칩(20)을 열전도성 접착부재(30)를 매개로 각각 부착한다. 상기 각 반도체 칩(20)은 그 상면에 다수개의 본딩패드(미도시)가 형성되어 있다.

다음, 도 5b에 도시된 바와 같이, 상기 반도체 칩(20)의 각 본딩패드(미도시)상에 범프(40)를 형성한 다음, 상기 리드프레임(10)을 절단하여 개개로 분리한다.

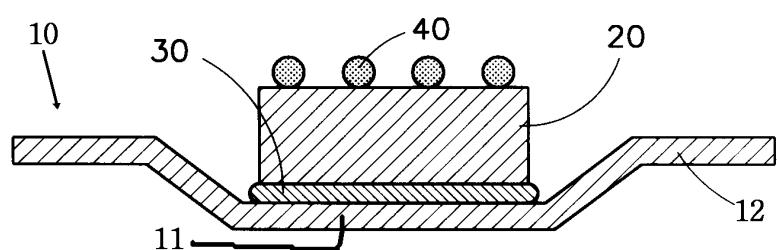

다음, 도 5c 에 도시된 바와 같이, 상기 분리된 리드프레임(10)의 다이패들(11) 중 반도체 칩(20)이 차지한 이외의 부분을 상방으로 절곡하여 형성한다.

다음, 도 5d 에 도시된 바와 같이, 상기 반도체 칩(20)을 포함한 상기 리드프레임(10)상의 일정면적을 올딩수지(50)로 물딩한다. 이때, 상기 반도체 칩(20)의 본딩패드(미도시)상에 형성된 범프(40)는 노출된다.

마지막으로, 도 5e 에 도시된 바와 같이, 상기 리드(12)를 하방으로 절곡하여 형성함으로서 본 발명에 따른 에리어 어레이형 반도체 패키지가 완성된다. 상기 다이패들(11)의 하면과 상기 리드(12)의 하면이 동일선상에 있는 것을 특징으로 한다.

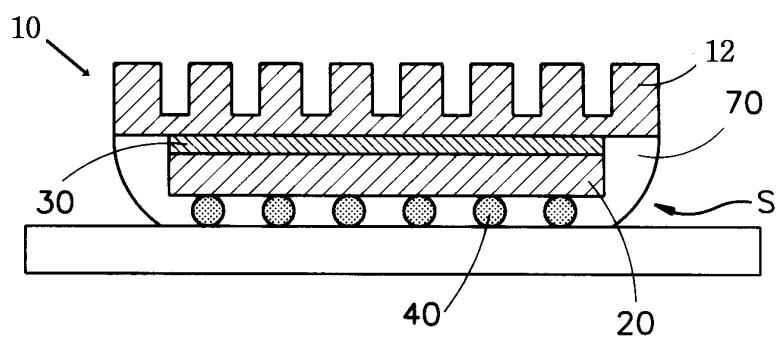

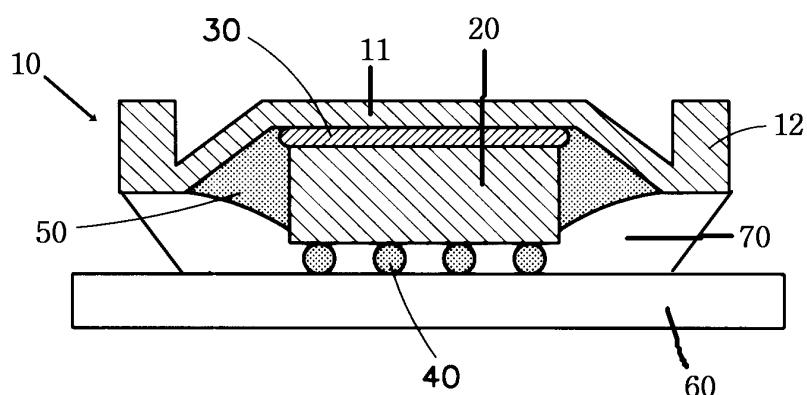

도 6는 PCB상에 실장된 본 발명에 따른 에리어 어레이 반도체 패키지의 종단면도를 도시한 것으로서, 이에 도시된 바와 같이, 반도체 칩(20)의 본딩패드(미도시)상에 형성된 범프(40)를 매개로 PCB(60)상에 실장되어 있으며, 상기 PCB(60)의 상면과 리드프레임(10)간의 공간(S)을 언더필(underfill)(70)함으로서 솔더 조인트 특성의 안정을 기하였다.

도 7은 PCB상에 실장된 본 발명에 따른 에리어 어레이 반도체 패키지의 횡단면도를 도시한 것으로서, 이에 도시된 바와 같이, 리드프레임(10)이 반도체 칩(20)에서 발생하는 열을 외부로 방출하는 히트싱크로서 사용됨을 보여주고 있다.

### **발명의 효과**

상기와 같이 제조된 본 발명에 따른 에리어 어레이 반도체 패키지는 반도체 칩이 부착되는 리드프레임을 히트싱크로 사용함으로서 고열(高熱 : high fever)이 발생하는 고성능 반도체 칩의 패키징에 적합하여 반도체 패키지의 열방출특성이 향상되는 효과가 있다.

또한, 반도체 칩에 저장된 정보를 PCB에 전달하였던 금속와이어를 사용하였던 종래 반도체 패키지와는 달리 반도체 칩의 본딩패드상에 상기 반도체 칩에 저장된 정보를 외부로 전달하는 출력단자로서 범핑을 형성함으로서 경박단소화되어지고, 소자회로설계시 본딩패드의 설계가 용이해지고, 전기적 특성이 향상되는 효과가 있다.

또한, PCB상에 본 발명에 따른 에리어 어레이 반도체 패키지를 실장한 다음, 리드프레임과 PCB 사이에 반도체 칩과 범프를 포함한 일정한 면적을 언더필함으로서 솔더 조인트 신뢰성이 향상되는 효과가 있다.

### **(57) 청구의 범위**

#### **청구항 1**

다이패들(11)과 그의 단부에 일정간격으로 형성된 다수개의 리드(12)를 포함하는 리드프레임(10)과;

상기 리드프레임(10)의 다이패들(11)상에 부착된 상면에 다수개의 본딩패드를 가진 반도체 칩(20)과;

상기 반도체 칩(20)의 각 본딩패드상에 형성된 범프(40)와;

상기 범핑된 반도체 칩(20)을 포함한 상기 리드프레임(10)상의 일정면적을 밀봉한 물딩수지(50)로 구성된 것을 특징으로 하는 에리어 어레이형 반도체 패키지.

#### **청구항 2**

제 1 항에 있어서, 상기 리드프레임(10)의 리드(12) 일부분이 하방 또는 상방 중 어느 하나로 절곡된 것을 특징으로 하는 에리어 어레이형 반도체 패키지.

#### **청구항 3**

제 1 항에 있어서, 상기 리드프레임(10)의 다이패들(11)의 면적은 그 위에 놓여지는 상기 반도체 칩(20)의 면적보다 큰 것을 특징으로 하는 에리어 어레이형 반도체 패키지.

#### **청구항 4**

제 3 항에 있어서, 상기 다이패들(11)의 일부분이 상방으로 절곡된 것을 특징으로 하는 에리어 어레이형 반도체 패키지.

#### **청구항 5**

다수개의 리드(12)를 가진 리드프레임(10)의 다이패들(11)상에 다수개의 본딩패드를 가진 반도체 칩(20)을 부착하는 공정과;

상기 각 본딩패드상에 범프(40)를 형성하는 공정과;

상기 범핑된 반도체 칩(20)을 포함한 상기 리드프레임(10)상의 일정면적을 물딩수지(50)로 물딩하는 공정과,

상기 리드(12)와 다이패들(11)의 일부분을 절곡하여 형성하는 공정을 포함하여 이루어지는 것을 특징으로 하는 에리어 어레이 반도체 패키지의 제조방법.

### 도면1

### 도면2

### 도면3

도면4

도면5a

도면5b

도면5c

도면5d

도면5e

도면6

도면7