# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2007/0228464 A1 Wang et al.

### Oct. 4, 2007 (43) Pub. Date:

## (54) MOS TRANSISTOR

(76) Inventors: Hsiang-Ying Wang, Chia-Yi Hsien (TW); Chin-Cheng Chien, Tainan Hsien (TW); Tsai-Fu Hsiao, Hsin-Chu City (TW); Ming-Yen Chien, Kao-Hsiung Hsien (TW); Chao-Chun Chen, Kao-Hsiung City (TW)

> Correspondence Address: NORTH AMERICA INTELLECTUAL PROPERTY CORPORATION P.O. BOX 506 **MERRIFIELD, VA 22116 (US)**

(21) Appl. No.: 11/748,479

(22) Filed: May 14, 2007

## Related U.S. Application Data

(62) Division of application No. 11/278,434, filed on Apr. 3, 2006.

## **Publication Classification**

(51) Int. Cl.

H01L 29/772 (2006.01)

(52)

#### (57)ABSTRACT

A method of forming a MOS transistor, in which a coimplantation is performed to implant an implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect. The implant comprises carbon, a hydrocarbon, or a derivative of the hydrocarbon, such as one selected from a group consisting of C,  $C_xH_y+$ , and  $(C_xH_y)_n+$ , wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000.

Fig. 1 Prior Art

$Fig. \infty$

## MOS TRANSISTOR

# CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This is a divisional application of U.S. patent application Ser. No. 11/278,434 filed on Apr. 3, 2006, and the contents of which are included herein by reference.

## BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates a method of forming a MOS transistor, and particularly a method of forming a MOS transistor having an improved short channel effect, comprising a step of co-implantation using an implant comprising carbon, hydrocarbon, or a derivative thereof.

[0004] 2. Description of the Prior Art

[0005] Field effect transistors (FETs) are important electronic devices in the fabrication of integrated circuits, and as the size of the semiconductor device becomes smaller and smaller, the fabrication of the transistors also improves and is constantly enhanced for fabricating transistors with smaller sizes and higher quality.

[0006] In the conventional method of fabricating transistors, a gate structure is first formed on a substrate, and a lightly doped drain (LDD) is formed on the two corresponding sides of the gate structure. Next, a spacer is formed on the sidewall of the gate structure and an ion implantation process is performed to form a source/drain region within the substrate by utilizing the gate structure and spacer as a mask. Finally, an anneal process is performed.

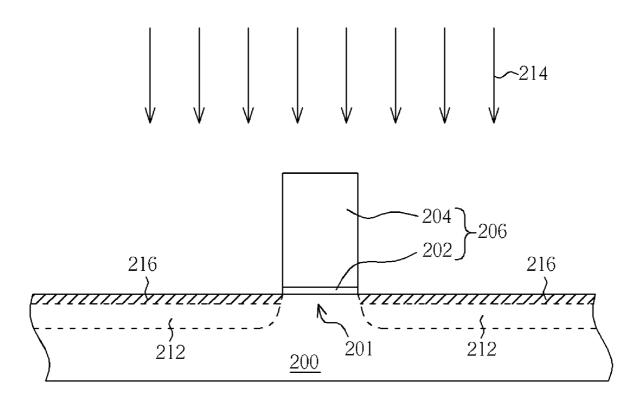

[0007] Refer to FIG. 1, a schematic diagram showing a conventional field effect transistor. As shown in FIG. 1, a gate structure 106 having a gate dielectric layer 102 and a gate electrode 104 is first formed on a substrate 100. Next, an ion implantation process is performed to form a lightly doped drain 110 in the substrate 100. Next, a spacer 108 is formed on the sidewall of the gate structure 106 and another ion implantation is performed to form a source/drain region 112 in the substrate 100. Subsequently, a rapid thermal process (RTP) is performed to obtain a FET.

[0008] With the device scaling down, it's difficult to control the junction depth  $(X_j)$  and also reduce the access resistance. The short channel effect (SCE) noticeably depends on the junction depth. The junction depth for the source/drain of a transistor must be reduced to avoid the short channel effect of the MOS arisen from the shrinkage of the MOS size to increase the integration of the device. A lot of papers have demonstrated many approaches to improve the pFET SCE. But from 65 nm node and beyond, the conventional As implantation and spike RTP can hardly meet the nFET SCE requirement.

[0009] From the above viewpoint, the shallower as-implant depth by heavy ions or less diffusion activation tool is needed. Unfortunately the advanced activation tools (for example, flash or laser anneal) are under development and not mature.

[0010] A method of manufacturing a PMOS transistor has been disclosed to implant fluorine in a source/drain extension region or source/drain region to be with the dopants

thereat together. The diffusion for the dopants can be improved during a subsequent annealing process, to alleviate the SCE.

[0011] However, due to transistors with smaller sizes and higher quality are constantly desired, an FET with an improved SCE and a good junction profile and a method of manufacturing it are still needed.

## SUMMARY OF THE INVENTION

[0012] One object of the present invention is to provide a method of forming a MOS transistor with an improved short channel effect.

[0013] The method of forming a MOS transistor according to the present invention comprises the steps as follows. First, a substrate having a gate thereon, a source region and a drain region therein with a channel region under the gate therebetween is provided. Next, the source region and the drain region are pre-amorphized to form amorphized regions. Subsequently, a first ion implantation is performed to implant a first dopant in the source region and the drain region to form a first doped region. At least a spacer is formed on the sidewalls of the gate. A second ion implantation is performed to implant a second dopant in the source region and the drain region to form a second doped region. The source region and the drain region are annealed to activate the first dopant, regrow the amorphized regions to a substantially crystalline form, and form a junction profile. Among these steps, a co-implantation process is performed after pre-amorphizing the source region and the drain region and before annealing the source region and the drain region, to implant an implant in the source region and the drain region, wherein the implant comprises carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound.

[0014] In another embodiment of the present invention, the method of forming a MOS transistor comprises the steps as follows. First, a substrate having a gate thereon, a source region and a drain region therein with a channel region under the gate therebetween is provided. Next, an implant is implanted into the source region and the drain region for achieving both pre-amorphization and co-implantation of the source region and the drain region to form amorphized regions with the implant, wherein the implant comprises carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound. Next, a first ion implantation is performed to implant a first dopant in the source region and the drain region to form a first doped region. At least one spacer is formed on the sidewalls of the gate. A second ion implantation is performed to implant a second dopant in the source region and the drain region to form a second doped region. Finally, the source region and the drain region are annealed to activate the first dopant, regrow the amorphized regions to a substantially crystalline form, and form a junction profile.

[0015] Furthermore, the MOS transistor according to the present invention comprises a substrate having a gate thereon, a source region and a drain region therein with a channel region under the gate therebetween; at least a spacer disposed on a side wall of the gate; a light doped source region and a light doped drain region disposed in the source region and the drain region; a source and a drain disposed respectively in the source region and the drain region at a

side of the light doped source region and a side the light doped drain region; and a halo implanted region formed between the channel region and the source region and between the channel region and the drain region, wherein the halo implanted region comprises an implant comprising carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound.

[0016] In another embodiment according to the present invention, the MOS transistor comprises a substrate having a gate thereon, a source region and a drain region therein with a channel region under the gate therebetween; at least a spacer disposed on a side wall of the gate; a light doped source region and a light doped drain region disposed in the source region and the drain region; a source and a drain disposed respectively in the source region and the drain region at a side of the light doped source region and a side the light doped drain region; and a halo implanted region formed between the channel region and the source region and between the channel region and the drain region, wherein the halo implanted region comprises an implant comprising carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound.

[0017] The method of forming a MOS transistor comprises a step of co-implantation to implant carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound, such as one selected from a group consisting of C,  $C_xH_y+$ , and  $(C_xH_y)_p+$ , wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000, within substantially the same place as that of the lightly doped drain or source, the source region and the drain region, or the halo implanted region. Therefore, after a rapid thermal process is performed, for example, by a conventional implanter and a spike annealing tool, the diffusion of dopants co-existing with the implants from the co-implantation can be reduced. That is, the diffusion of the dopants within the lightly doped drain or source, the source region and the drain region, or the halo implanted region can be effectively controlled, to obtain a good junction profile and an improved short channel effect.

[0018] These and other objectives of the present invention will no doubt become obvious to those of ordinary skill in the art after reading the following detailed description of the preferred embodiment that is illustrated in the various figures and drawings.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0019] FIG. 1 is a schematic structural diagram showing a conventional field effect transistor;

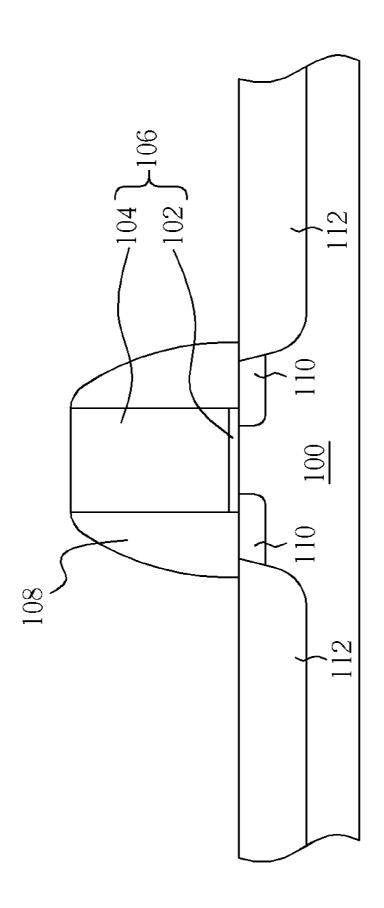

[0020] FIG. 2 is a flow chart showing the method of forming a MOS transistor according to the present invention:

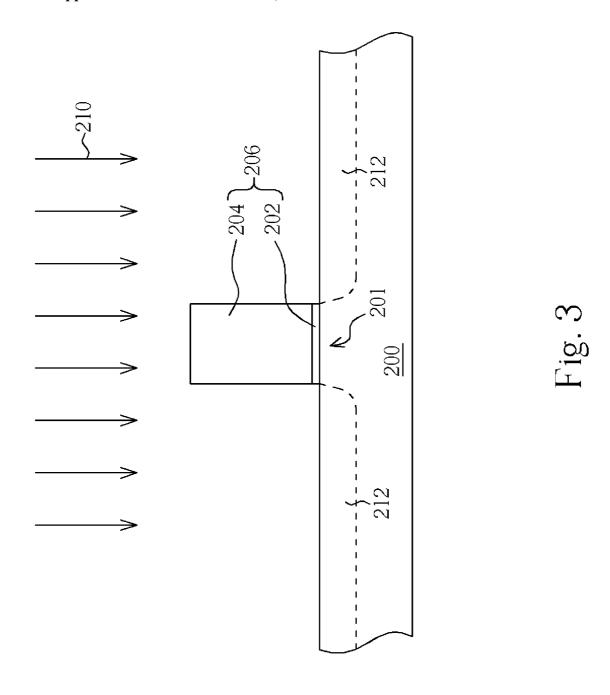

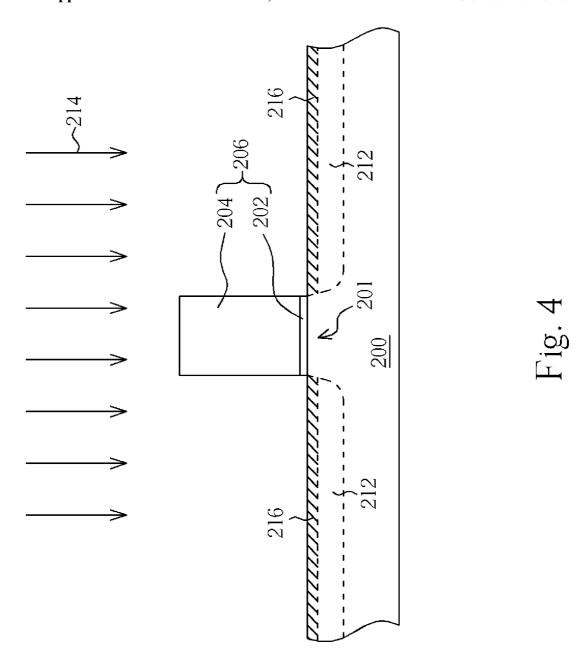

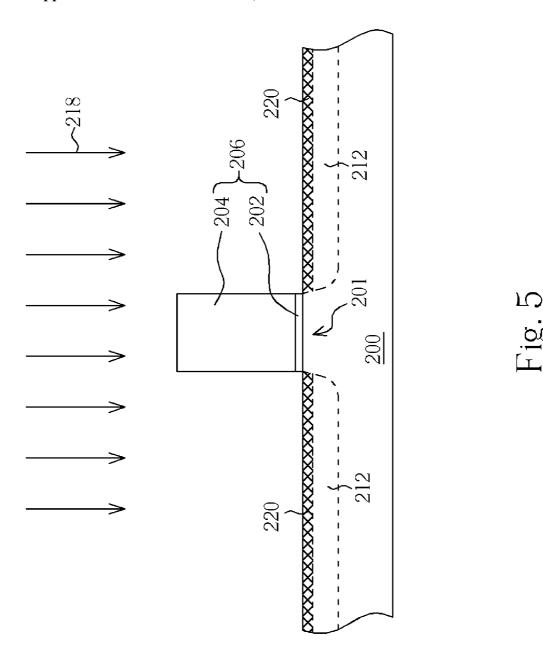

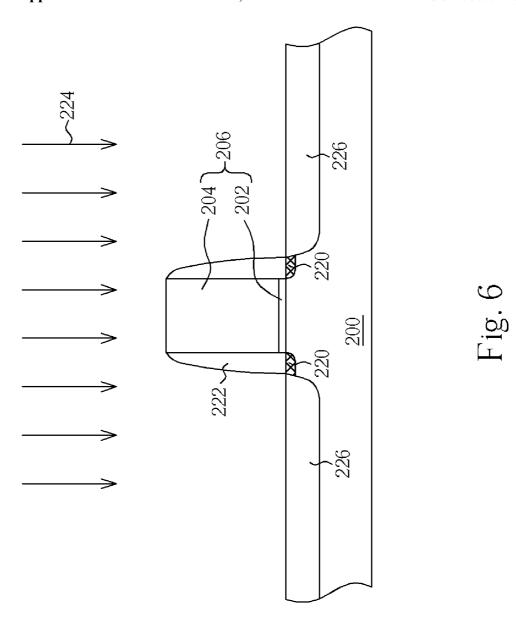

[0021] FIGS. 3 to 6 show cross sectional views for the method of forming a MOS transistor according to the present invention;

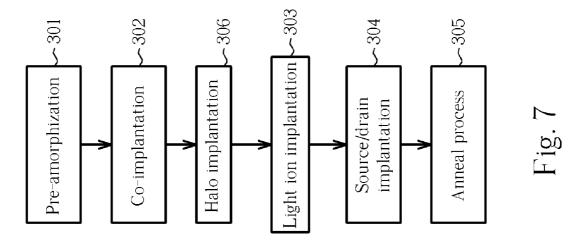

[0022] FIG. 7 is a flow chart showing another embodiment of the method of forming a MOS transistor according to the present invention:

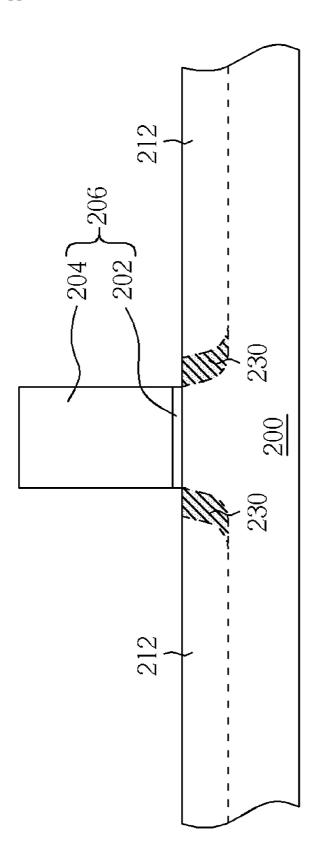

[0023] FIG. 8 shows a cross sectional view for the method of forming a MOS transistor according to the present invention, in which the halo implanted region comprises dopants and implants;

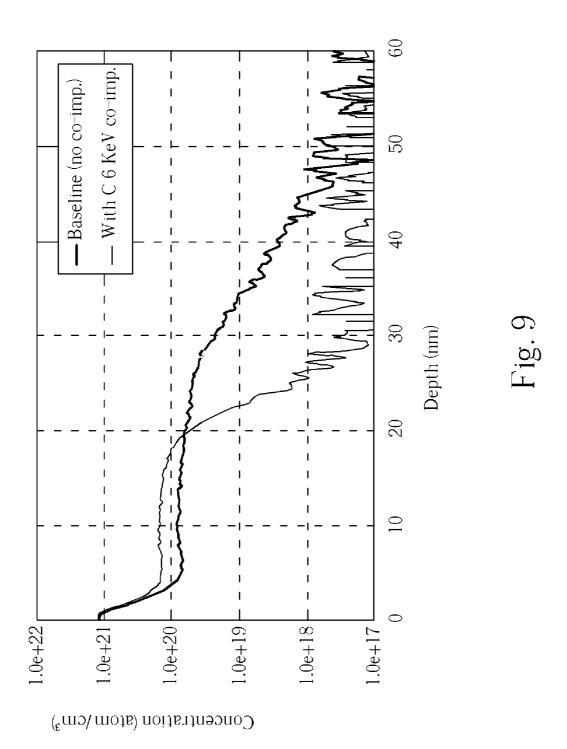

[0024] FIG. 9 shows the B profile comparison by a secondary ion mass spectroscopy of PLDD made using the method according to the present invention and PLDD made by a conventional method; and

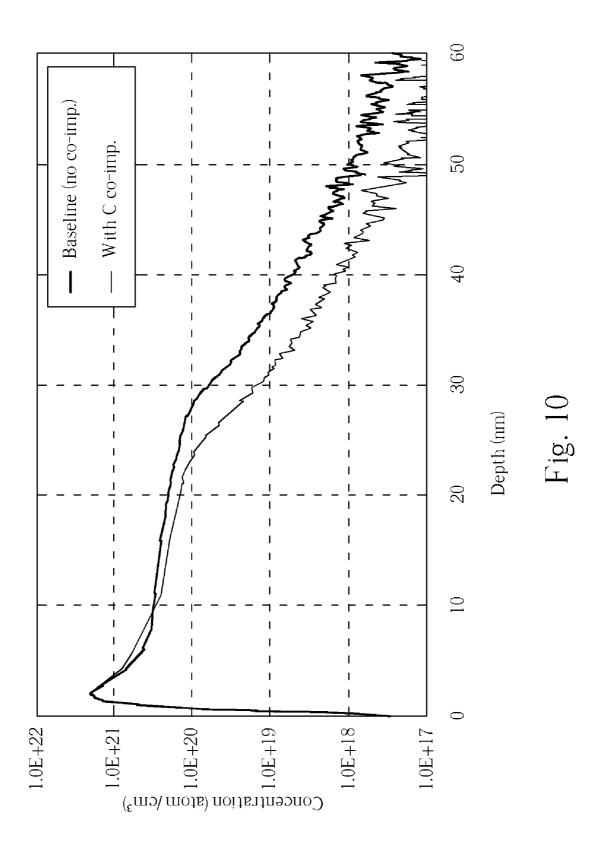

[0025] FIG. 10 shows the As profile comparison by a secondary ion mass spectroscopy of NLDD made using the method according to the present invention and NLDD made by a conventional method.

## DETAILED DESCRIPTION

[0026] Refer to FIGS. 2 to 6 for illustration of an embodiment according to the present invention. FIG. 2 is a flow chart showing the method of forming a MOS transistor according to the present invention. The method of forming a MOS transistor of the embodiment according to the present invention comprises the steps of follows. A substrate having a gate, a source region and a drain region, and a channel region is provided. A pre-amorphization 301 is performed to form an amorphized region in the source region and the drain region, respectively. A co-implantation 302 is performed to implant an implant within the source region and the drain region. A light ion implantation 303 is performed to form a doped region in the source region and the drain region. A spacer is formed on the sidewall of the gate. A source/drain ion implantation 304 is performed to form a doped region. An anneal process 305 is performed to activate the dopants, regrow the amorphized regions to a substantially crystalline form, and form a junction profile.

[0027] FIGS. 3 to 6 show cross sectional views for the method of forming a MOS transistor according to the present invention. As shown in FIG. 3, first, a substrate 200 is provided. A gate structure 206 comprises a gate dielectric layer 202 and a gate electrode 204 on the substrate 200. The gate dielectric layer 202 comprises dielectric material such as silicon oxide. The gate electrode 204 comprises a conductive material such as doped polysilicon. A source region and a drain region are defined at two sides of the gate structure 206, and a channel region 201 is under the gate structure 206. Next, the pre-amorphization 301 is performed to form an amorphized region 212 in the source region and the drain region, respectively, to destroy the lattice of the silicon crystalline into an amorphous structure. The preamorphizing implantation is performed by an ion implantation 210 through implant an implant into the source region and a drain region. The dopant may be, but not limited to, for example, silicon (Si), antimony (Sb), germanium (Ge), or arsenic (As). For example, a Ge implant having a dose of about 5.0×10<sup>14</sup> atoms/cm<sup>2</sup> with an implantation energy of about 40 KeV may be employed, or an As implant having a dose of about 3.0×10<sup>15</sup> atoms/cm<sup>2</sup> with an implantation energy of about 40 KeV may be employed. The implantation may be perpendicular to the implanted surface of with an angle as desired. An implantation angle of about 3 to 10 degrees may be used to generate an amorphized region extending to under the gate.

[0028] The co-implantation 302 is performed to implant an implant into the source region and the drain region. For example, as shown in FIG. 4, the co-implantation is performed by an ion implantation 214 to form a co-doped region 216 in the light doped drain/source predetermined region. The place for the co-implant in the substrate is not limited to the substantially same place as that of the subse-

quent dopant implanted by an LDD implantation, and it may be the substantially same place as that of the subsequent dopant implanted by a source/drain implantation. Thus, the short channel effect due to over diffusion of the dopants implanted by the subsequent processes during the anneal process such as the rapid thermal process can be reduced. The implantation energy may depend on the implant position in the substrate, such as 3 KeV to 20 KeV. The dose may be  $1\times10^{15}$  to  $3\times10^{15}$  atoms/cm<sup>3</sup>. The implant may comprise carbon, hydrocarbon compound, or a derivative of the hydrocarbon compound, such as one selected from C,  $C_xH_v+$ , and  $(C_xH_v)_n+$ , wherein x is a number of 1 to 10, and preferably 1; y is a number of 4 to 20, and preferably 4; and n is a number of 1 to 1000, and preferably 800. The implantation may be perpendicular to the implanted surface or with an angle as desired.

[0029] Referring to FIG. 5, the LDD implantation 303 is performed by an ion implantation 218 using the gate 204 as a mask to implant a light dopant into the amorphized region 212 to form a light source/drain region (LDD) 220. In this embodiment, there is an implant from the co-implantation in LDD 220. The dopant used in the light ion implantation may be described as follows. When C is used as an implant, a dopant such as As or P can be used as a light dopant for the source/drain region, to form an n-type LDD (NLDD), and a dopant such as B or BF<sub>2</sub> can be used as a light dopant for the source/drain region, to form an p-type LDD (PLDD). When  $C_xH_y+$  or  $(C_xH_y)_n+$  is used as an implant, a dopant such as B, BF2, boron hydride, or a derivative thereof (such as  $B_w H_z \text{+, or } (B_w H_z)_m \text{+)}$  can be used as a light dopant for the source/drain region, to form an PLDD, in which, w is a number of 2 to 30, and preferably 18, z is a number of 2 to 40, and preferably 22, and m is a number of 10 to 1000, and preferably 800. The dose for the light dopant may be, for example,  $10^{17}$  to  $10^{20}$  atoms/cm<sup>3</sup>.

[0030] After the LDD implantation, a spike rapid thermal process may be further performed to activate dopants. Alternatively, the spike rapid thermal process is not performed at this manufacturing stage, and an anneal process is performed after the source/drain implantation.

[0031] Subsequently, the source/drain implantation 304 is performed. As shown in FIG. 6, a spacer 222 is formed on the sidewall of the gate structure 206. The spacer may be a single layer or a multi-layered structure. For example, the spacer may be composed of a lining layer (such as silicon oxide) and a silicon nitride layer or the spacer may be composed of a silicon oxide offset spacer and a silicon intride spacer. Thereafter, an ion implantation 224 is performed to implant a heavy dopant within the source region and the drain region to form a heavily doped source/drain 226. The implantation dose of the heavy dopant may be for example 10<sup>20</sup> to 10<sup>21</sup> atoms/cm<sup>3</sup>.

[0032] Finally, the anneal process 305 is performed, such as a rapid thermal process, or a spike anneal process to activate the dopant in the substrate 200 at a high temperature of, for example, 1000 to 1050° C. to form a desired junction profile and regrow the damaged lattice structure of the surface of the substrate 200 caused by ion implantations to a substantially crystalline form.

[0033] In the flow chart shown in FIG. 2, the co-implantation 302 is performed after the pre-amorphization 301 and before the light ion implantation 303; however, it is noted that the diffusion of dopants in the substrate can be well controlled as long as the co-implantation 302 is performed

before the anneal process 305. Accordingly, the co-implantation 302 may be performed after the pre-amorphization 301 and before the light ion implantation 303; or after the light ion implantation 303 and before the source/drain implantation 304; or after the source/drain implantation 304 and before the anneal process 305. Therefore, the implant is implanted in the substrate 200 at a place substantially the same as that of the light dopant in the lightly doped region or that of the heavy dopant in the source/drain.

[0034] Referring to FIG. 7, a flow chart showing another embodiment of the method of forming a MOS transistor according to the present invention has the same steps as the above-described embodiment, except that a halo implantation is further comprised. A halo implant, also called a "pocket implant," has been used to reduce "punch through", i.e., to limit lateral diffusion of the source and the drain dopants in MOS transistors. It is generally performed after the gate is defined and before the source/drain diffusion. Due to the masking effect of the gate, the halo implant peak concentration is near the source/drain region. Away from the source/drain edge, under the gate, the depth of the peak halo concentration falls quickly.

[0035] As shown in FIG. 7, the halo implantation 306 is performed after the co-implantation 302 and before the light ion implantation 303. Nevertheless, it also can be performed after the pre-amorphization 301 and before the co-implantation 302. The halo implant is of the conductivity type opposite to that of the source and drain of the MOS device. For example, As is used as a dopant in LDD and B or BF2 may be used as a halo implant to form an nFET. B or BH<sub>2</sub> is used as a dopant in LDD and As or P may be used as a halo implant to form a pFET. The concentration of the halo implant in the halo implanted region depends on the device size. The concentration is higher as the size is larger. The concentration may be between  $1 \times 10^{17}$  atoms/cm<sup>3</sup> and  $1 \times 10^{1}$ atoms/cm<sup>3</sup>, for example. The ion flux may be at an implant angle of 0 to about 30 degree, or greater, from normal (perpendicular) to the substrate, to provide a halo implant which extends slightly under the gate.

[0036] In case the halo implantation is included to form the transistor, the implant of the co-implantation may be implanted in the substrate at a place substantially the same as that of the halo implant, in addition to the place substantially the same as that of the light dopant in the lightly doped region or that of the heavy dopant in the source/drain. FIG. 8 shows an embodiment in which the halo implanted region 230 comprises an implant from the co-implantation, in addition to the halo implant. Thus, the diffusion of the halo implant can be well controlled to form a better junction profile.

[0037] When carbon, hydrocarbon, or a derivative thereof is implanted as an implant into the doped region and exists with dopants together, the diffusion of the dopants (such as, B or P) can be controlled because the implant occupies the interstitials of the silicon crystalline structure. This situation facilitates the control for the diffusion of dopants, and thus a good junction profile can be obtained.

[0038] The method of forming a MOS transistor according to the present invention can be used to form a pPFET or an nFET. For example, when carbon is used as a co-implant in the light doped drain/source, an NLDD can be formed using, for example, As or P as a light dopant in the source region and the drain region, and a PLDD can be formed using, for example, B or BF $_2$  as a light dopant in the source region and the drain region. When  $C_xH_v+$  or  $(C_xH_v)_n+$  is used as a

co-implant in the light doped drain/source, a PLDD can be formed using, for example,  $B, BF_2, B_wH_z+$ , or  $(B_wH_z)_m+$  as a light dopant in the source region and the drain region.

[0039] According to still another embodiment according to the present invention, using hydrocarbon or a derivative thereof (such as  $C_xH_y$ + or  $(C_xH_y)_n$ +) as a co-implant, and in such situation, the process flow is the same as that shown in FIG. 2 or 7, except that the pre-amorphization 301 and the co-implantation 302 are performed by one step. That is, C<sub>x</sub>H<sub>y</sub>+ or (C<sub>x</sub>H<sub>y</sub>)<sub>n</sub>+ is used as the implant for the preamorphization instead of Si, Ge, etc. and as a co-implant in the implanted regions subsequently formed, to simultaneously achieve the amorphization of the source/drain region in the substrate and the control for the diffusion of the dopants implanted in the subsequent processes, to obtain a good junction profile. The equal energy for such co-implant is preferably less than the implant energy for the source/ drain, and for example less than 40 KeV. The dose may be  $1\times10^{15}$  atoms/cm<sup>3</sup> to  $3\times10^{15}$  atoms/cm<sup>3</sup>. The dopant for the light doped drain/source region may be boron hydride or a derivative thereof, such as  $B_wH_z$ + or  $(B_wH_z)_m$ + to obtain a more preferred shallow junction profile.

[0040] FIG. 9 shows the B profile comparison by a secondary ion mass spectroscopy (SIMS) of PLDD made in one embodiment of the method of forming a MOS transistor according to the present invention, with a co-implantation using a C implant, and PLDD made by a conventional method, without a co-implantation. Both used BF<sub>2</sub> of 3 KeV as a dopant for the PLDD implantation, but in the embodiment according to the present invention, a co-implantation was further performed using a C implant 0 f 6 KeV. As shown in FIG. 9, C was used as a co-implant with B to reduce the diffusion of B for forming a shallower and a sharper junction. In comparison with the conventional co-implantation using fluorine, the method of the present invention is more effective on the reduction of B diffusion.

[0041] FIG. 10 shows the As profile comparison by a secondary ion mass spectroscopy (SIMS) of NLDD made in one embodiment of the method of forming a MOS transistor according to the present invention, with a co-implantation using a C implant, and PLDD made by a conventional method, without a co-implantation. Both used As of 4 KeV as a dopant in a dose of 1.5×10<sup>15</sup> atoms/cm³ for the NLDD implantation, but in the embodiment according to the present invention, a co-implantation was further performed using a C implant 0 f 3 KeV. As shown in FIG. 10, C was used as a co-implant with As to reduce the diffusion of As for forming a shallower and a sharper junction.

[0042] Those skilled in the art will readily observe that numerous modifications and alterations of the device and method may be made while retaining the teachings of the invention. Accordingly, the above disclosure should be construed as limited only by the metes and bounds of the appended claims.

What is claimed is:

- 1. A MOS transistor, comprising:

- a substrate having a gate thereon, a source region and a drain region therein with a channel region under the gate therebetween;

- at least a spacer disposed on a side wall of the gate;

- a light doped source region and a light doped drain region disposed in the source region and the drain region; and

- a source and a drain disposed respectively in the source region and the drain region at a side of the light doped source region and a side the light doped drain region;

- wherein one of the light doped source region, the light doped drain region, the source region, and the drain region comprises an implant comprising carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound.

- 2. The MOS transistor as claimed in claim 1, further comprising a halo implanted region formed between the channel region and the source region and between the channel region and the drain region.

- 3. The MOS transistor as claimed in claim 1, wherein the implant comprises one selected from the group consisting of C,  $C_xH_y$ +, and  $(C_xH_y)_n$ +, wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000.

- **4**. The MOS transistor as claimed in claim 1, wherein the implant comprises C and the light doped source region and the light doped drain region comprise As or P.

- 5. The MOS transistor as claimed in claim 1, wherein the implant comprises C and the light doped source region and the light doped drain region comprise B or BF<sub>2</sub>.

- **6**. The MOS transistor as claimed in claim 1, wherein the implant comprises  $C_xH_y+$  or  $(C_xH_y)_n+$  and the light doped source region and the light doped drain region comprise B, BF<sub>2</sub>,  $B_wH_z+$ , or  $(B_wH_z)_m+$ , wherein w is a number of 2 to 30, z is a number of 2 to 40, and m is a number of 10 to 1000.

- 7. A MOS transistor, comprising:

- a substrate having a gate thereon, a source region and a drain region therein with a channel region under the gate therebetween;

- at least a spacer disposed on a side wall of the gate;

- a light doped source region and a light doped drain region disposed in the source region and the drain region;

- a source and a drain disposed respectively in the source region and the drain region at a side of the light doped source region and a side the light doped drain region; and

- a halo implanted region formed between the channel region and the source region and between the channel region and the drain region, wherein the halo implanted region comprises an implant comprising carbon, a hydrocarbon compound, or a derivative of the hydrocarbon compound.

- **8**. The MOS transistor as claimed in claim 7, wherein the implant comprises one selected from the group consisting of C,  $C_xH_y$ +, and  $(C_xH_y)_n$ +, wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000.

- 9. The MOS transistor as claimed in claim 7, wherein the light doped source region and the light doped drain region comprise B, BF<sub>2</sub>,  $B_wH_z+$ , or  $(B_wH_z)_m+$ , wherein w is a number of 2 to 30, z is a number of 2 to 40, and m is a number of 10 to 1000.

\* \* \* \* \*