#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2017/070459 A1

(43) International Publication Date 27 April 2017 (27.04.2017)

(51) International Patent Classification:

G11C 5/14 (2006.01) G11C 16/30 (2006.01)

G11C 11/56 (2006.01) G11C 16/34 (2006.01)

G11C 16/10 (2006.01) G11C 16/04 (2006.01)

(21) International Application Number:

PCT/US2016/058092

(22) International Filing Date:

21 October 2016 (21.10.2016)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

62/244,942 22 October 2015 (22.10.2015) US 15/299,338 20 October 2016 (20.10.2016) US

- (71) Applicant: SANDISK TECHNOLOGIES LLC [US/US]; 6900 Dallas Parkway, Suite 325, Plano, Texas 75024 (US).

- (72) Inventors: MOKHLESI, Nima; 951 SanDisk Drive, Milpitas, California 95035 (US). AL-SHAMMA, Ali; 951 SanDisk Drive, Milpitas, California 95035 (US).

- (74) Agent: MAGEN, BURT; Vierra Magen Marcus LLP, 575 Market Street, Suite 3750, San Francisco, California 94105 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: THREE DIMENSIONAL NON-VOLATILE MEMORY WITH POWER SUPPLY CURRENT SENSING TO DETERMINE PROGRAMMING STATUS

Figure 21

(57) Abstract: A non-volatile memory system includes a plurality of non-volatile memory cells, one or more control circuits that perform programming of the memory cells, a power supply line that provides a supply used during a programming operation of the memory cells, and a current measurement circuit. The current measurement circuit senses an indication of current on the power supply line. The one or more control circuits determine whether the programming of the memory cells is successful based on the indication of current.

# THREE DIMENSIONAL NON-VOLATILE MEMORY WITH POWER SUPPLY CURRENT SENSING TO DETERMINE PROGRAMMING STATUS

#### **BACKGROUND**

[0001] Recently, ultra high density storage devices have been proposed using a three dimensional (3D) stacked memory structure sometimes referred to as a Bit Cost Scalable (BiCS) architecture. For example, a 3D NAND stacked memory device can be formed from an array of alternating conductive and dielectric layers. A memory hole is drilled in the layers to define many memory layers. A NAND string is then formed by filling the memory hole with appropriate materials. A straight NAND string (I-BiCS) extends in one memory hole, while a pipe- or U-shaped NAND string (P-BiCS) includes a pair of vertical columns of memory cells which extend in two memory holes and which are joined by a bottom back gate. Control gates of the memory cells are provided by the conductive layers. However, various challenges are presented in operating such memory devices.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

- [0002] Like-numbered elements refer to common components in the different figures.

- [0003] Figure 1A is a perspective view of a portion of a 3D stacked non-volatile memory.

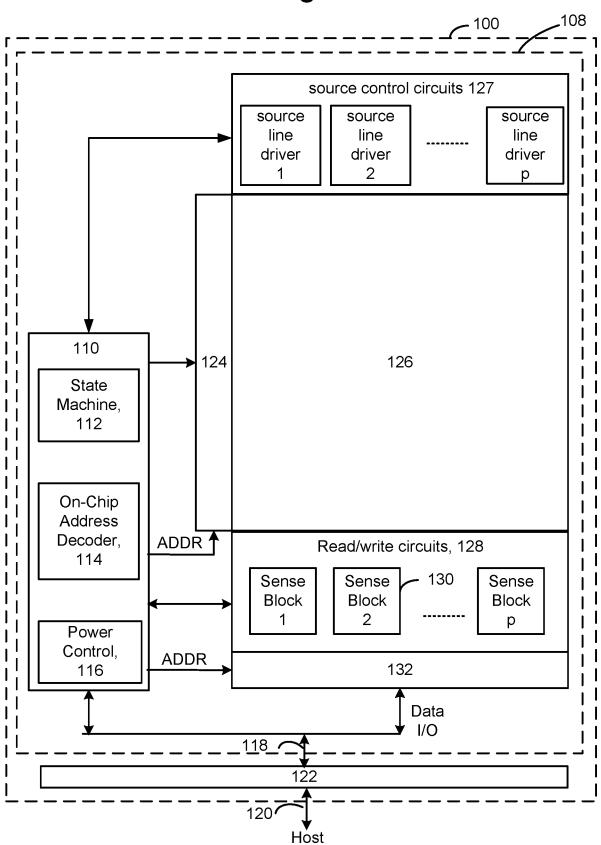

- [0004] Figure 1B is a functional block diagram of a memory system that includes the 3D stacked non-volatile memory of FIG. 1A.

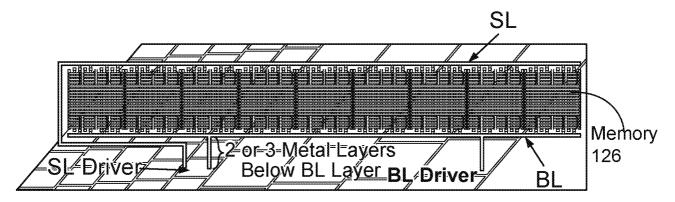

- [0005] Figure 1C and Figure 1D show the positioning of the memory array, source line drivers and bit line drivers.

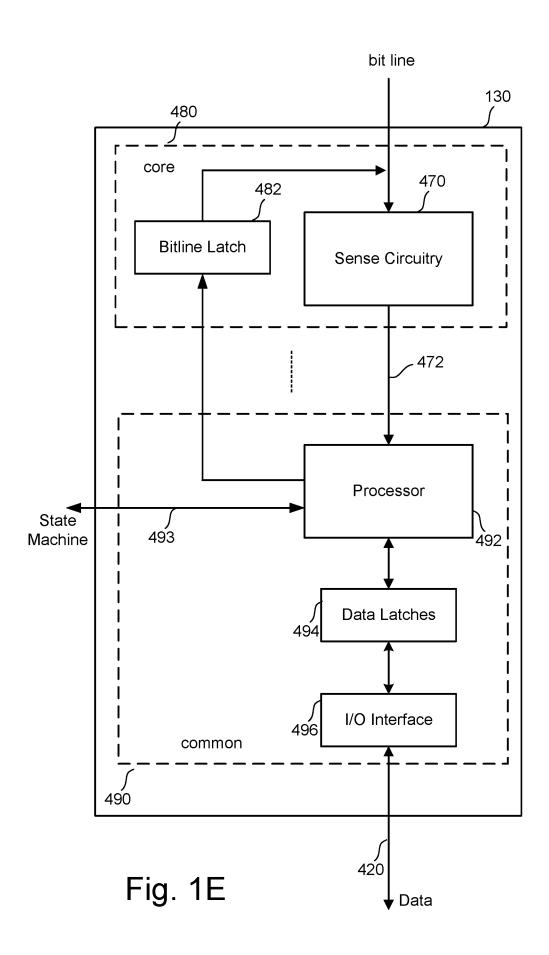

- [0006] Figure 1E is a block diagram of a sense block.

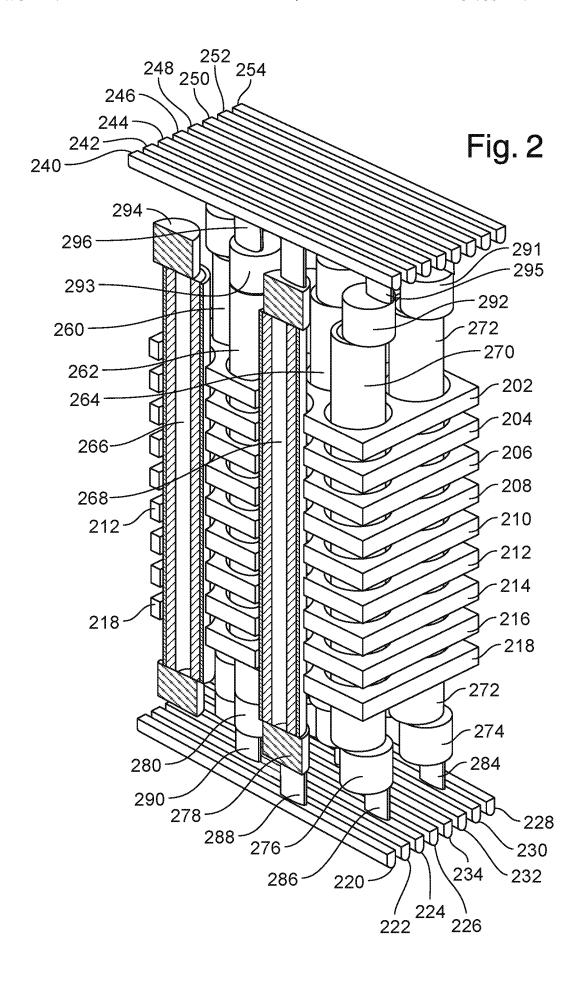

- [0007] Figure 2 is a perspective view of a portion of a 3D stacked non-volatile memory.

- [0008] Figure 3 is a side view of a portion of a 3D stacked non-volatile memory.

- [0009] Figure 4 is a cross sectional and perspective view of a column of the 3D stacked non-volatile memory.

- [0010] Figure 5 is a block diagram of a 3D memory array.

## WO 2017/070459 PCT/US2016/058092 -2-

- [0011] Figure 6 is a top view of one layer of the 3D stacked non-volatile memory.

- [0012] Figure 7 is a side view of a portion of a 3D stacked non-volatile memory.

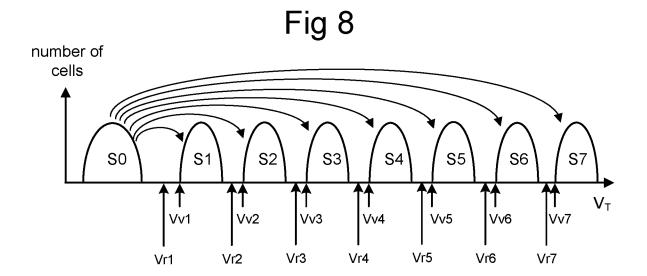

- [0013] Figure 8 depicts a set of threshold voltage distributions representing data states.

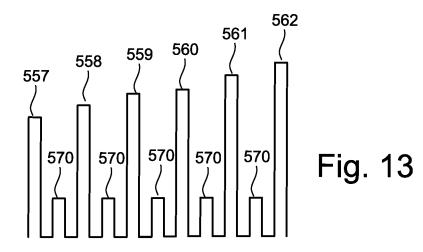

- [0014] Figures 9A-9E depict a programming process.

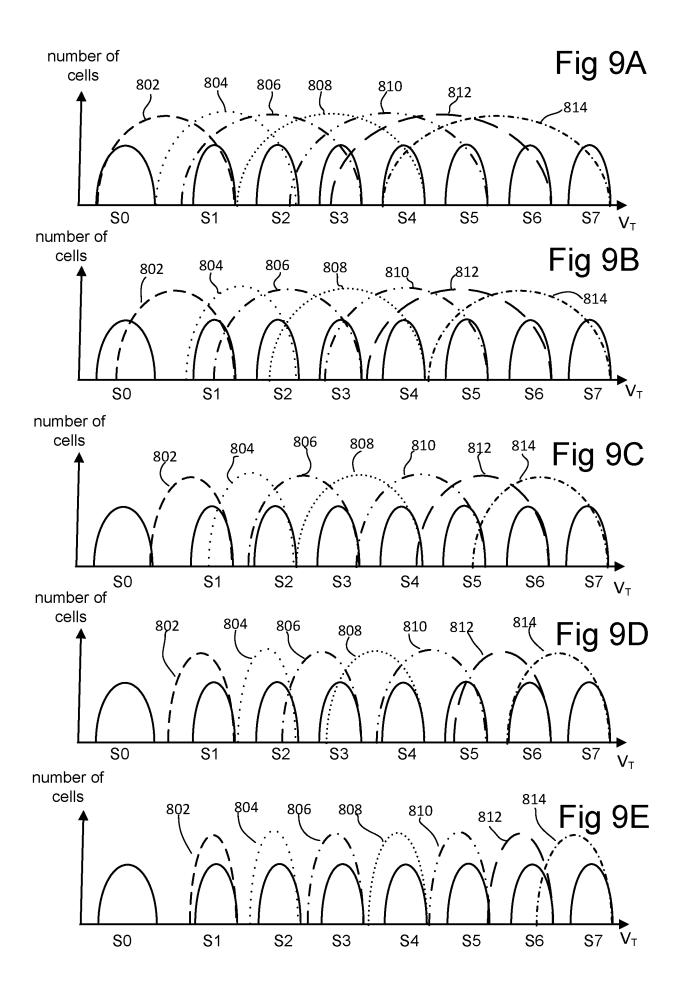

- [0015] Figure 10 is a flow chart describing one embodiment of a process for programming.

- [0016] Figure 11 is a table identifying various voltages applied to the individual source lines and bit lines.

- [0017] Figure 12 is a table identifying various voltages applied to word lines and select gate lines.

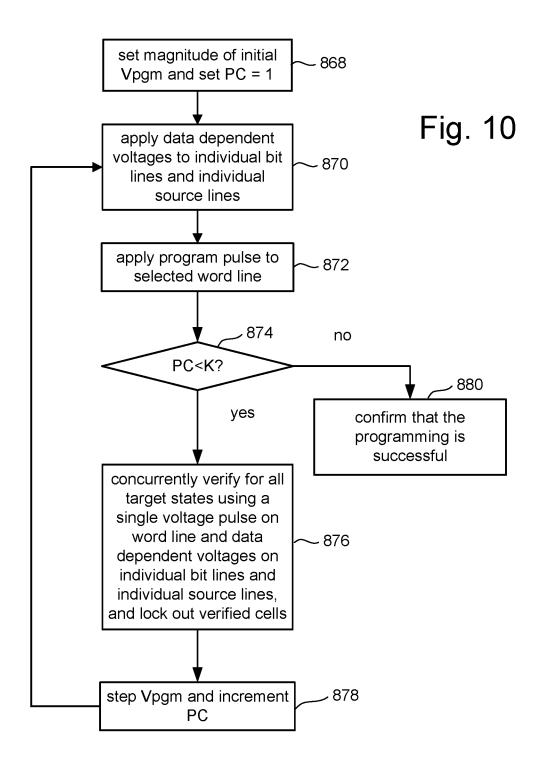

- [0018] Figure 13 depicts the voltage applied to the selected word line during a programming process.

- [0019] Figure 14 is a flow chart describing one embodiment of a process for verifying.

- [0020] Figure 15 is a flow chart describing one embodiment of a process for reading.

- [0021] Figure 16 is a table of voltages used during one embodiment of programming and verification of programming.

- [0022] Figure 17A depicts threshold voltages and programming a first pass of a multi-pass programming process that programs high states first.

- [0023] Figure 17B depicts threshold voltages and programming a second pass of a multipass programming process that programs high states first.

- [0024] Figure 18 is a table of voltages used for a first pass of a multi-pass programming process that programs high states first.

- [0025] Figure 19 is a table of voltages used for a second pass of a multi-pass programming process that programs high states first.

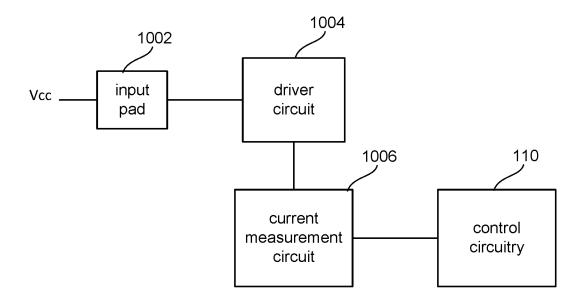

- [0026] Figure 20 is a block diagram of one embodiment of a subset of components on a memory die.

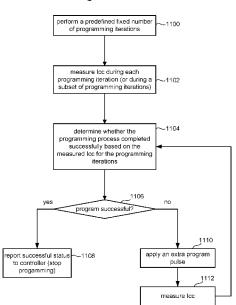

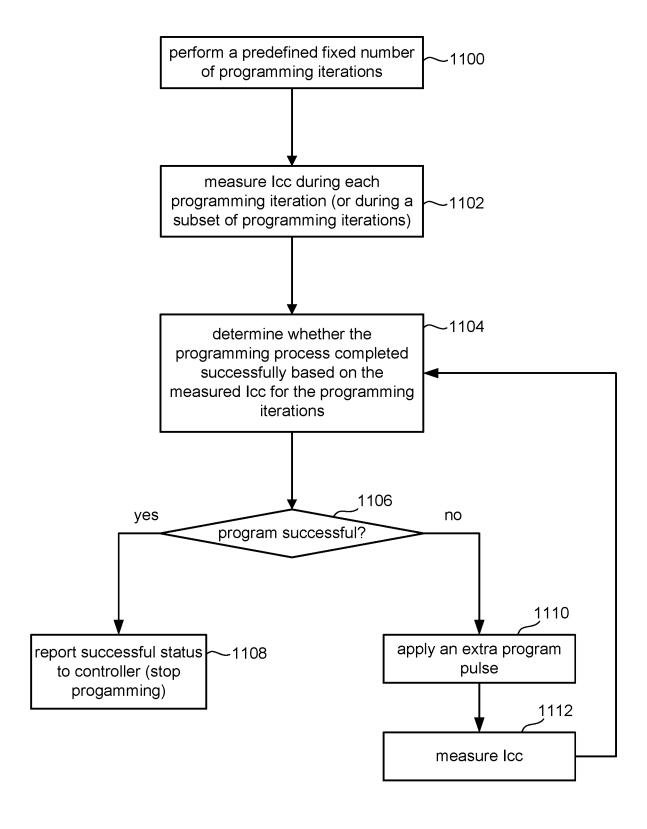

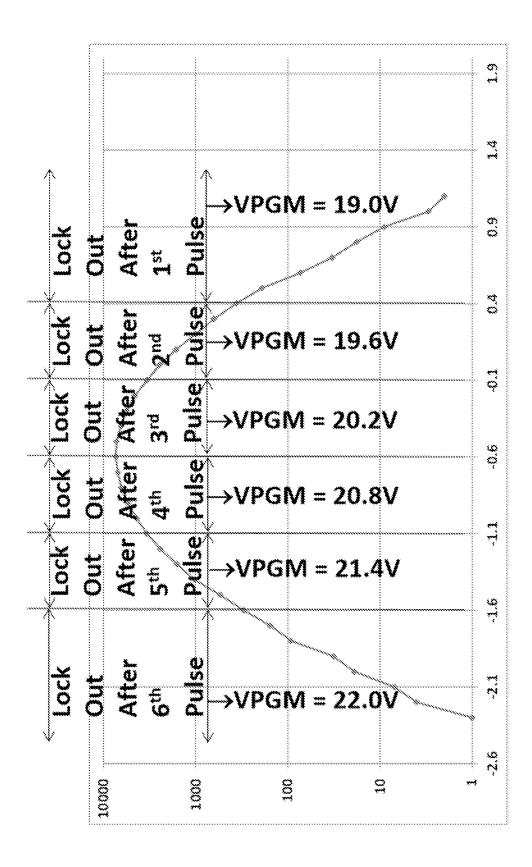

[0027] Figure 21 is a flow chart describing one embodiment of a process for determining whether enough memory cells have been successfully programmed so that a programming process is complete.

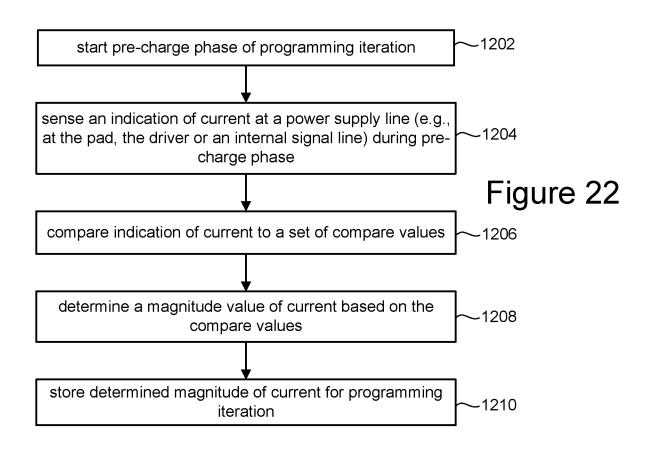

[0028] Figure 22 is a flow chart describing one embodiment of a process for measuring current.

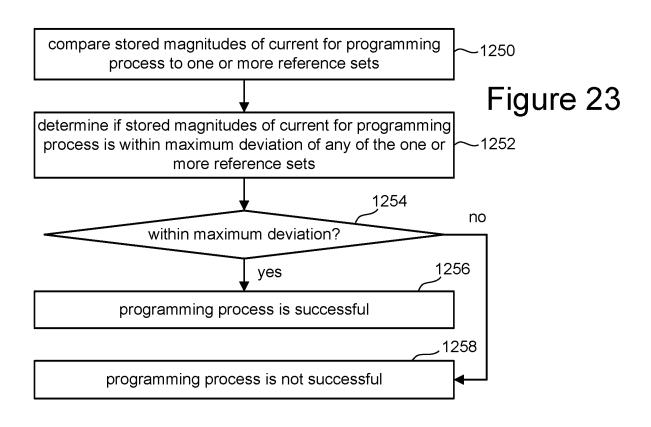

[0029] Figure 23 is a flow chart describing one embodiment of a process for determining whether the programming process completed successfully based on the measured current for the programming iterations.

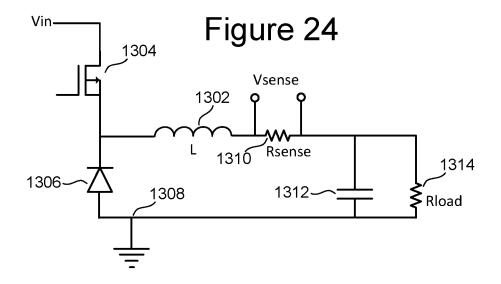

- [0030] Figure 24 is a schematic of one embodiment of a circuit that measures current.

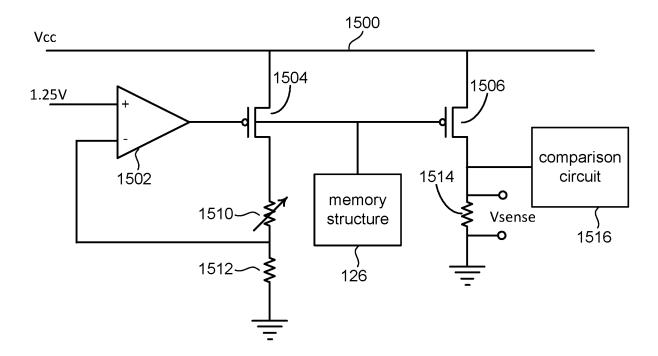

- [0031] Figure 25 is a schematic of one embodiment of a circuit that measures current.

- [0032] Figure 26 is a schematic of one embodiment of a circuit that measures current.

- [0033] Figure 27 depicts the natural distribution of threshold voltages for programming.

#### DETAILED DESCRIPTION

In the selected memory cells as set of programming pulses. Between programming pulses, typical memory systems verify whether each of the selected memory cells have reached their target data state (ie the target of the programming operation). Those memory cells that are verified to have reached their target data state are locked out from additional programming. Many non-volatile memory systems lock out memory cells from additional programming by raising an associated bit line to a lockout voltage. After verifying whether each of the selected memory cells have reached their target data state, and prior to the next programming pulse, typical memory systems will perform a scan operation that includes counting the number of memory cells that have been successfully programmed (e.g., have reached their target data state). When enough memory cells have been successfully programmed, the programming process is finished. While this scheme works well, the scan operation is time consuming and uses power.

[0035] To increase performance and save power, it is proposed to program non-volatile memory cells (including verifying the programing) without performing a scan operation.

During the portion of the programming process when memory cells transition from being programmed to being locked out, the memory system can monitor Icc. For a memory system, Icc is the total current coming into the memory die from one or more off die supplies. As a memory cell transitions from being programmed to being locked out, its associated bit line will be moved to a higher voltage (ie the lockout voltage) which draws more current. Therefore, monitoring current drawn by the memory die will be indicative of the number of memory cells transitioning from being programmed to being locked out. The memory system can keep track of the current monitored after several verify operations and feed these monitored current values into an algorithm for comparing the monitored current values into an algorithm for comparing the monitored current values into an algorithm for comparing the monitored current values into an algorithm for comparing the monitored current values into an algorithm for comparing the monitored current values into an algorithm for comparing the monitored current values indicate that enough memory cells have been successfully programmed so that the programming process is complete.

[0036] One embodiment of a suitable memory system includes a the three dimensional stacked non-volatile memory structure that comprises alternating dielectric layers and conductive layers in a stack, a plurality of bit lines below the stack, and a plurality of source lines above the stack. There is a separate source line associated with each bit line, rather than one source line for an entire block, plane or array. Each source line is connected to a different subset of NAND strings. Each bit line is connected to a different subset of NAND strings. Because the bit lines are below the stack, there is no need for signal lines to carry signals from the substrate surface to the top of the stack for the bit lines and no crowding of lines occurs as bit lines try to pass through source lines when they are both at minimum pitch. Since bit line driver circuits are bigger than source line driver circuits, one embodiment locates bit lines underneath the memory array so that the bit line drivers residing on the silicon surface under the memory array have direct access to the bit lines. In one embodiment, the source line drivers, being smaller in size, are placed on the side of the memory array. Since the source line drivers are smaller than the bit line drivers and also smaller than the traditional sense amp circuits, this arrangement shrinks the memory die size by saving the area which is traditionally reserved for sense amplifiers (the traditional bit line drivers).

[0037] The three dimensional stacked memory device comprises a plurality of memory cells arranged in blocks. Each block includes memory holes (or pillars) which extend vertically in the stack, and comprise a column of memory cells such as, for example, in a NAND string.

WO 2017/070459 PCT/US2016/058092 -5-

The three dimensional stacked non-volatile memory device includes N layers. The memory holes are divided into four groups at each level of a block and each group has a separate set of source side and drain side select signals so that a subset of memory holes can be active at any given time. Because of the concurrency in the programming and verifying, the number of programming and verify pulses is reduced and the overall programming process is faster than other architectures. This is enabled because each memory channel/hole in a selected group has its own dedicated source line in addition to having its own dedicated bit line. With this architecture each memory channel can be driven to its own designated voltage at both its source line and its bit line. This provides full control of the channel potential. Each channel can have one of a number of different potentials applied to it based on what data state is to be programmed on the memory cell that is along that channel and belongs to the selected word line. A data state is a condition of the memory cell which correlates to storing a predefined pattern of data. The meaning of a data state can change based on the type of memory technology used in various embodiments. For example, in a multi-level memory cell different threshold voltage levels for the cell may correlate to a particular data pattern that represents data settings on two or more logical levels of data stored in the multi-level memory cell. In another example, the data state may comprise the level of resistance for a filament formed in the cell. In another example, the data state may comprise the magnetic orientation of a magnetic layer in a Spintransfer torque random access memory cell (STT-RAM).

[0038] The proposed structure allows for multiple data states to be verified concurrently, as is explained below. Memory cells are concurrently programmed to different data states, with memory cells being programmed to lower data states having their programming slowed by applying appropriate source line voltages and bit line voltages. In one embodiment, reading is performed sequentially for the data states.

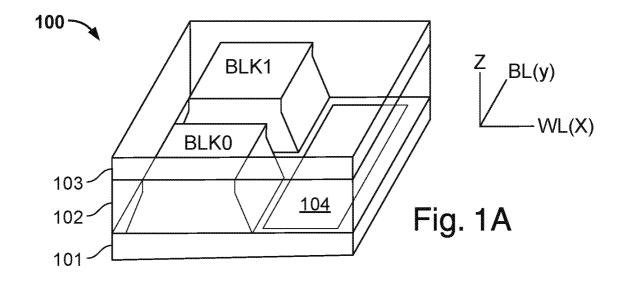

[0039] Figure 1A is a perspective view of a portion of a 3D stacked non-volatile memory device. The memory device 100 includes a substrate 101. On the substrate are example blocks BLK0 and BLK1 of memory cells and a peripheral area 104 with circuitry for use by the blocks. The substrate 101 can also carry circuitry under the blocks, along with one or more metal layers lower than the bit line layer which are patterned in conductive paths to carry signals of the circuitry. The blocks are formed in an intermediate region 102 of the memory device. In an upper region 103 of the memory device, one or more upper metal layers are patterned in conductive paths to carry signals of the circuitry. Each block comprises a stacked area of

memory cells, where alternating levels of the stack represent word lines. While two blocks are depicted in Figure 1A as an example, additional blocks can be used, extending in the x- and/or y-directions.

**[0040]** In one possible approach, the length of the plane, in the x-direction, represents a direction in which word lines extend, and the width of the plane, in the y-direction, represents a direction in which bit lines extend. The z-direction represents a height of the memory device.

[0041] Figure 1B is a functional block diagram of the 3D stacked non-volatile memory device 100 of Figure 1A. The memory device 100 may include one or more memory die 108. The memory die 108 includes a memory array (or other memory structure) 126 of memory cells. Memory array 126 is a monolithic three dimensional memory array in which multiple memory levels are formed above (and not in) a single substrate, such as a wafer, with no intervening substrates. Memory array 126 may comprise any type of nonvolatile memory that is monolithically formed in one or more physical levels of memory cells having active areas disposed above a silicone substrate. In one embodiment, memory array 126 implements NAND flash memory.

[0042] Memory array 126 is addressable by word lines via a row decoder 124 and by bit lines via a column decoder 132. The read/write circuits 128 include multiple sense blocks 130 (sensing circuitry) and allow a page (or other unit) of memory cells to be read or programmed in parallel. In some embodiments, a controller 122 is included in the same memory device 100 (e.g., a removable storage card) as the one or more memory die 108. In other embodiments, controller 122 is separated from the memory die 108. Commands and data are transferred between the host and controller 122 via lines 120 and between the controller and the one or more memory die 108 via lines 118.

[0043] The control circuitry 110 cooperates with the read/write circuits 128 to perform memory operations on the memory array 126, and includes a state machine 112, an on-chip address decoder 114, and a power control module 116. The state machine 112 provides chip-level control of memory operations. The on-chip address decoder 114 provides an address interface between that used by the host or a memory controller to the hardware address used by the decoders 124 and 132. The power control module 116 controls the power and voltages supplied to the word lines and bit lines during memory operations. It can include drivers for word lines, source side select lines (SGS) and drain side select lines (SGD) and source lines.

WO 2017/070459 PCT/US2016/058092 -7-

The sense blocks 130 include bit line drivers and circuits for sensing. Control circuitry 110 is also in communication with source control circuits 127, which includes source line driver circuit 1, source line driver circuit 2, ..., source line driver circuit p. The source line driver circuits are used to drive different (or the same) voltages on the individual source lines. The present architecture provides individual control of one source line per active memory cell. Hundreds of thousands (for example about 300,000) of source line driver circuits are required in addition to the same number of bit line driver circuits.

[0044] In some implementations, some of the components can be combined. In various designs, one or more of the components (alone or in combination) of Figure 1B, other than memory array 126, can be thought of as one or more control circuits. For example, one or more control circuits may include any one of, or a combination of, control circuitry 110, state machine 112, decoders 114/124/132, power control module 116, sense blocks 130, source control circuits 127, read/write circuits 128, and controller 122, and so forth. In one embodiment, the one or more control circuits are connected to the memory cells of memory array 126 and configured to perform programming (including verify) and reading of the memory cells.

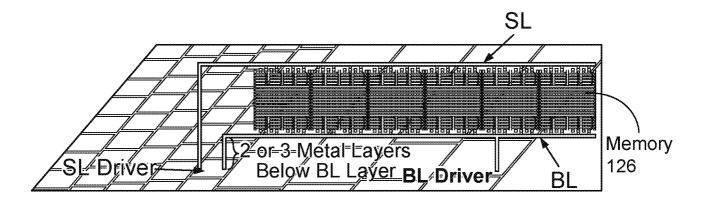

Figure 1C and Figure 1D show the positioning of the memory array 126, source line [0045] drivers (SL Driver) and bit line drivers (BL Driver). Figure 1C shows an embodiment where bit line drivers (BL Driver) are below the memory array 126 and source line drivers (SL Driver) are to the side of memory array 126. Figure 1C also shows an example source line SL above memory array 126 and an example bit line BL below memory array 126. In one embodiment, the SL Driver includes a unity gain buffer for matching BL voltage during programming and a low Vth single transistor amp (source follower) for subtracting ~0.5V from VBL to apply to SL at other times. Figure 1D shows the embodiment where bit line drivers (BL Driver) and source line drivers (SL Driver) are below memory array 126. One of the metal layers bellow the memory layer will be consumed. In one embodiment, there would be 3 available metal layers, for example, for connecting the bit line drivers, but only two layers available for connecting the source line drivers. It also means that the layer below the bit line layer becomes a critical layer at minimum pitch (in one example implementation). Figures 1 C/D show how bit lines and source lines can coexist without any difficulty encountered when one set try to pass through the other set. No such difficulty exists because one set does not need to try to pass through the other set. Figures 1C/D illustrate that both sets can be comfortably connected to WO 2017/070459 PCT/US2016/058092 -8-

their drivers without having to cross each other's metal layers. Any 3D memory architecture that has vertical channels as well as channels fabricated above metal layers (e.g. poly silicon channels as opposed to crystalline silicon channel) can benefit from the attributes of this architecture. Note that crystalline channels require crystalline seed layer of silicon from which the crystalline silicon channel can be grown by epitaxy.

[0046] Figure 1E is a block diagram of an individual sense block 130 partitioned into a core portion, referred to as a sense module 480, and a common portion 490. In one embodiment, there will be a separate sense module 480 for each bit line and one common portion 490 for a set of multiple sense modules 480. In one example, a sense block will include one common portion 490 and eight sense modules 480. Each of the sense modules in a group will communicate with the associated common portion via a data bus 472.

[0047] Sense module 480 comprises sense circuitry 470 that determines whether a conduction current in a connected bit line is above or below a predetermined level. In some embodiments, sense module 480 includes a circuit commonly referred to as a sense amplifier. Sense module 480 also includes a bit line latch 482 that is used to set a voltage condition on the connected bit line. For example, a predetermined state latched in bit line latch 482 will result in the connected bit line being pulled to a state designating program inhibit (e.g., 2\*Vdd or just under 2\*Vdd).

[0048] Common portion 490 comprises a processor 492, a set of data latches 494 and an I/O Interface 496 coupled between the set of data latches 494 and data bus 420. Processor 492 performs computations. For example, one of its functions is to determine the data stored in the sensed memory cell and store the determined data in the set of data latches. The set of data latches 494 is used to store data bits determined by processor 492 during a read operation. It is also used to store data bits imported from the data bus 420 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface 496 provides an interface between data latches 494 and the data bus 420.

[0049] During sensing (i.e. read or verify), the operation of the system is under the control of state machine 112 that controls the supply of different control gate voltages to the addressed cell. As it steps through one or more predefined control gate voltages (the read reference voltages or the verify reference voltages) corresponding to the various memory states supported by the memory, the sense module 480 may trip at one of these voltages and an output will be

provided from sense module 480 to processor 492 via bus 472. At that point, processor 492 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 493. It then computes a binary encoding for the memory state and stores the resultant data bits into data latches 494. In another embodiment of the core portion, bit line latch 482 serves double duty, both as a latch for latching the output of the sense module 480 and also as a bit line latch as described above.

loosol During program or verify, the data to be programmed is stored in the set of data latches 494 from the data bus 420. The program operation, under the control of the state machine, comprises a series of programming voltage pulses (with increasing magnitudes) each of which is concurrently applied to the control gates of a set of addressed memory cells so that the memory cells are programmed at the same time. Each programming pulse is followed by a verify process to determine if the memory cell has been programmed to the desired state. Processor 492 monitors the verified memory state relative to the desired memory state. When the two are in agreement, processor 492 sets the bit line latch 482 so as to cause the bit line to be pulled to a lockout voltage, which prevent additional programming. This inhibits the memory cell coupled to the bit line from further programming even if it is subjected to programming pulses on its control gate. In other embodiments the processor initially loads the bit line latch 482 and the sense circuitry sets it to an inhibit value during the verify process.

[0051] Data latch stack 494 contains a stack of data latches corresponding to the sense module. In one embodiment, there are three (or four or another number) data latches per sense module 480. In some implementations (but not required), the data latches are implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus 420, and vice versa. In one preferred embodiment, all the data latches corresponding to the read/write block of memory cells can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/write modules is adapted so that each of its set of data latches will shift data into or out of the data bus in sequence as if they are part of a shift register for the entire read/write block.

[0052] During a memory operation (such as programming, verifying or reading), sense circuitry 470 is responsible for applying a bit voltage to the respective bit line. As discussed below, during programming and verification, the bit line voltages are data dependent based on

the target data state that the relevant memory cell connected to the bit line is being programmed to. Processor 492 reads the data being programmed from data latches 494 and configures sense circuitry 470 to drive the appropriate data dependent voltage on the bit line based on the data read from the data latches 494.

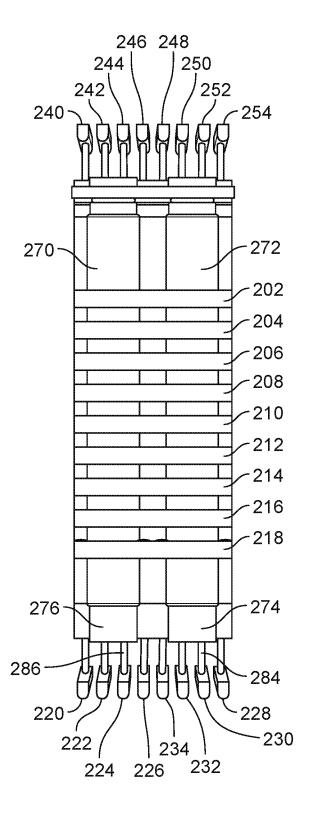

Figure 2 is a perspective view of a portion of one embodiment of memory array 126 [0053] that is a three dimensional stacked non-volatile memory comprising alternating dielectric layers and conductive layers in a stack, a plurality of bit lines below the stack, and a plurality of source lines above the stack. For example, Figure 2 shows conductive layers 202, 204, 206, 208, 210, 212, 214, 216, and 218, each of which operates as a word line and, therefore, can be referred to as a word line layer. To allow the drawing to fit on one page and be readable, not all of the conductive layers are depicted. For example, Figure 2 does not show any of the conductive layers operating as source side select layers (SGSs) and drain side select layers (SGDs). One embodiment may include 60 conductive layers, with 48 conductive layers operating as word line layers, two layers above the 48 word line layers as dummy layers on the source side, four layers above dummy source layers operating as source side select layers (SGS), two layers below the 48 word line layers as dummy layers on the drain side, four layers below dummy drain layers operating as drain side select layers (SGDs). Other embodiments can implement different numbers of word line layers, dummy layers, source side select layers and drain side select layers.

**[0054]** Between the conductive layers are dielectric layers. Many different dielectric materials can be used. One example of a suitable dielectric material is SiO2. Note that Figure 2 does not show the dielectric material between the conductive layers.

**[0055]** Below the stack of alternating dielectric layers and conductive layers are multiple separate and isolated bit lines 220, 222, 224, 226, 228, 230, 232, and 234. Although Figure 2 only shows eight bit lines, the memory system is likely to have many more than eight bit lines (e.g. 300,000).

[0056] Above the stack of alternating dielectric layers and conductive layers are multiple separate and isolated source lines 240, 242, 244, 246, 248, 250, 252 and 254. Although Figure 2 only shows eight source lines, the memory system is likely to have many more than eight source lines (e.g. 300,000). In one embodiment, bit line drivers (which include the sense amps) are located below the memory array (stack of layers) while the source line drivers are located

WO 2017/070459 PCT/US2016/058092 -11-

to the side of the memory array. In another embodiment, both bit line drivers and source line drivers are located under the memory array. This provides further die size savings at the expense of consuming one of a number of available metal layers over the source line drivers and under the bit lines for connecting the source line drivers to the source lines. The number of available metal layers above the silicon surface and below the bit line layer in certain embodiments is either three or four. This does not include the contact and via layers. If we also count these contact and via layers, the number of metal layers below memory array (including the bit line layer plus its via layer below it, and its via layer above it) add up to nine layers in one embodiment or to eleven layers in another embodiment. Contact and via layers typically provide vertical connectivity in Z direction, whereas the other metal layers provide both vertical and horizontal connectivity within the plane of the chip.

[0057] The stack of alternating dielectric layers and conductive layers includes memory holes or pillars which extend vertically in the stack, and comprise a column of memory cells such as in a NAND string. Figure 2 shows columns/holes/pillars 260, 262, 264, 266, 268, 270, and 272. Although Figure 2 only shows seven columns, the memory system is likely to have many more than seven columns. As depicted, each conductive layer will surround a set of columns, with one memory cell residing at the intersection of each column and each of the conductive layers designated to be function as word lines.

[0058] Each bit line is connected to a subset of columns. For example, Figure 2 shows bit line 230 connected to column 272, bit line 224 connected to column 270, bit line 220 connected to column 268 (note that column 268 is only partially depicted), and bit line 222 connected to column 262. Note that the terms "connected," "coupled" and "in communication with" include direct connections and connections via other components. The bit lines connect to the columns through a combination of vias and plugs. For example, bit line 230 is connected to column 272 by via 284 and plug 274, bit line 224 is connected to column 270 by via 286 and plug 276, bit line 220 is connected to column 268 by via 288 and plug 278, and bit line 222 is connected to column 262 by via 290 and plug 280.

[0059] Each source line is connected to a subset of columns. In one embodiment, the source lines connect to the columns through vias and plugs. Figure 2 shows plugs 291, 292, 293 and 294, as well as vias 295 and 296. Many of the via for the source lines are hidden due to the

WO 2017/070459 PCT/US2016/058092 -12-

perspective view. However, Figure 2 does show column 270 connected to source line 244 by via 295 and plug 292.

[0060] The source lines are not connected together and can carry different signals. In one embodiment, each source line is associated with a bit line to create a source line/bit line pair. The system includes many source line/bit line pairs. Each bit line is associated with a different and separate source line. A source line is connected to the same column as its associated bit line of the source line/bit line pairs. For example, bit line 230 is associated with source line 252 and both are connected to column 272, bit line 224 is associated with source line 244 and both are connected to column 270, bit line 220 is associated with source line 240 and both are connected to column 268, and bit line 222 is associated with source line 242 and both are connected to column 262. In one embodiment, the bit lines are made of Tungsten, the source lines are made of Copper or Tungsten, the vias are made of Tungsten and the plugs are made of polysilicon. In one embodiment, the conductive word line layers are made of Tungsten. Tungsten may be preferable as it can withstand the process thermal budget associated with processing the layers above it, and the required dopant activation or polysilicon channel grain size expansion anneal steps that follow the deposition of the Tungsten.

**[0061]** Figure 3 is a side view of the structure depicted in Figure 2. Like Figure 2, although Figure 3 shows conductive layers 202, 204, 206, 208, 210, 212, 214, 216, and 218, Figure 3 does not explicitly depict the dielectric layers between the conductive layers. Furthermore, Figure 3 (like Figure 2) only shows a subset of the conductive layers.

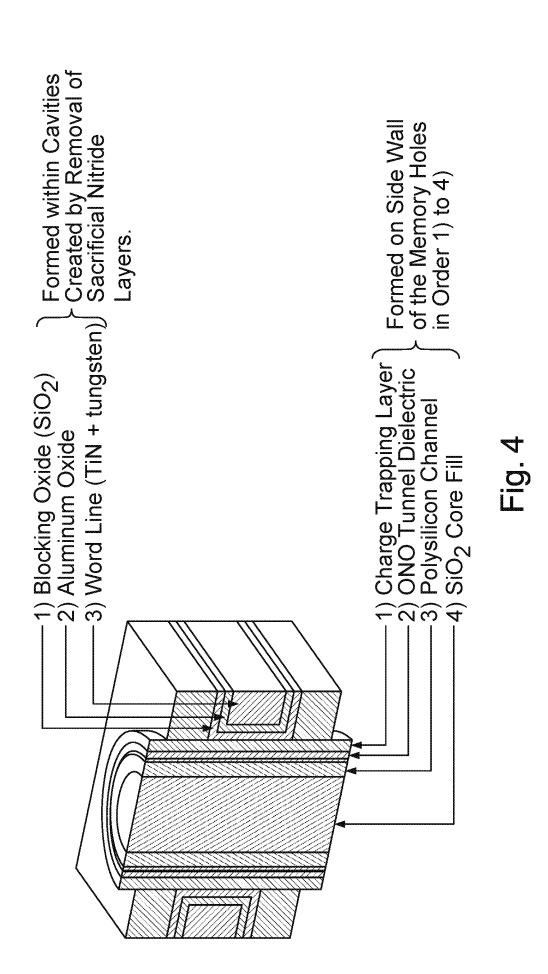

[0062] Figure 4 is a perspective view of a cross section of a column from the memory array 126 (stack) described above. Each column includes a number of layers which are deposited along the sidewalls of the column. These layers formed on the sidewall of the memory holes can include, from the outer perimeter of the hole moving radially in toward the center, a charge trapping layer such as a specially formulated silicon nitride that increases trap density, followed by oxide-nitride-oxide (O-N-O) stack layer that acts as a band gap engineered tunnel dielectric, followed by polysilicon layer(s), followed by the inner most dielectric such as silicon oxide core fill. These layers are deposited using methods such as atomic layer deposition, chemical vapor deposition, or physical vapor deposition. There are many other intermediary steps such as anneals, densifications and sacrificial layers that are temporarily deposited and later removed. The inner most oxide of the ONO tunnel dielectric that is in contact with the

polysilicon channel can be created by converting some thickness of the deposited nitride layer to oxide by methods such as ISSG (In-Situ Steam Generation). Other layers of the memory cell structure can be formed by depositions into the horizontal voids left behind after the sacrificial nitride layers are etched out, as opposed to deposition in the memory hole. Such layers can include the silicon oxide blocking layer and the aluminum oxide high K transition layer between the silicon oxide blocking layer and the word line. The word line deposition can start with a titanium nitride layer deposited on aluminum oxide followed by a tungsten seed layer deposition and then the remainder of the cavities for word line fingers can be filled with tungsten. Inside the cavities between word line layers, for example, a blocking oxide (SiO2) can be deposited. The Blocking Oxide surrounds the charge trapping layer. Surrounding the Blocking Oxide, and between the Blocking Oxide and the Word Line (TiN + Tungsten) is an Aluminum Oxide layer. In other embodiments, not shown in Figure 2, the blocking oxide can be the first layer formed in the memory hole as opposed to the first layer formed in the cavities left behind after the sacrificial nitride layers are removed. The polysilicon channel is connected to a bit line at the bottom of the column and connected to the associated source line at the top of the column through intermediary deposited patterned layers including a metal via and a doped polysilicon plug, as discussed above. The polysilicon plugs can be n-type, preferably doped with some combination of Arsenic or phosphorus, or they can be p-type preferably doped with some combination of Boron or indium. In some embodiments Arsenic and indium are preferable because they diffuse more slowly during high temperature anneals which are required for poly crystalline grain size changes and other purposes.

[0063] When a memory cell is programmed, electrons are stored in a portion of the charge trapping layer which is associated with the memory cell. These electrons are drawn into the charge trapping layer from the polysilicon channel, and through the ONO tunnel dielectric. The threshold voltage (Vth) of a memory cell is increased in proportion to the amount of stored charge.

**[0064]** Each of the memory holes is thus filled with a plurality of annular layers comprising sometimes a blocking layer, usually a charge trapping layer, a usually tunnel dielectric multilayers structure and a channel layer. A core region of each of the memory holes is filled with a body material, and the plurality of annular layers are between the core region and the WL that surround each of the memory holes.

**[0065]** Looking back at Figure 2, memory system 100 includes a memory array 126 having the structure depicted in Figures 2, 3, and 4. Figure 5 is a block diagram explaining the organization of memory array 126, which is divided into two planes 502 and 504. Each plane is then divided into N blocks. In one example, each plane has approximately 2000 blocks. However, different numbers of blocks and planes can also be used.

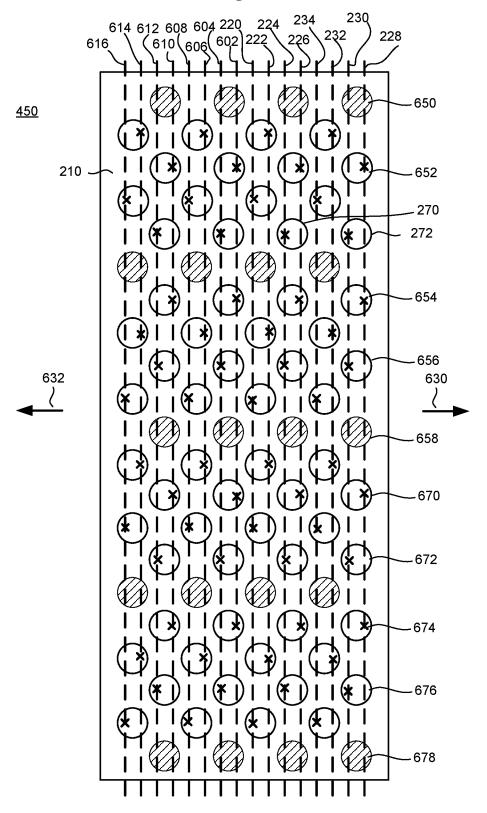

[0066] Figure 6 is a block diagram depicting a portion of a top view of one layer of one block. The portion of the block depicted in Figure 6 corresponds to box 450 in block 2 of Figure 5. As can be seen from Figure 5, the block depicted in Figure 6 extends in the direction of arrow 632 and in the direction of arrow 630. In one embodiment, the memory array will have 48 memory layers; therefore, each block will have 48 layers. However, Figure 6 only shows one layer. Each layer of a block has only one word line. For example, the layer of block 2 depicted in Figure 6 includes word line 210 (see Fig. 2) surrounding a plurality of circles. Each circle represents a column (see Fig. 4). Figure 6 has reference numbers for columns 270 (see Fig. 2), 272 (see Fig. 2), 650, 652, 654, 656, 658, 670, 672, 674, 676 and 678. Not all columns are provided with reference numbers in order to keep Figure 6 readable. Some of the circles are shaded to indicate that those columns will not be used to store data, and are sacrificed to provide spacing.

**[0067]** Figure 6 also shows dashed vertical lines. These are the bit lines. Figure 6 shows sixteen bit lines: 220, 222, 224, 226, 228, 230, 232, 234, 604, 606, 608, 610, 612, 614 and 616. The lines are dashed to indicate that the bit lines are not part of this layer, rather they are below the stack. Each of the non-shaded circles has an "x" to indicate its connection to a bit line.

[0068] Figure 6 does not show the source lines in order to keep the drawing readable. However, the source lines would be in the same position as the bit lines, but located above the stack rather than below. The source lines would connect to the columns in the same manner as the bit lines. Therefore, a source line and its associated bit line of a source line/bit line pair connect to the same column. In this manner, the structure of the source lines is symmetrical to the structure of the bit lines. Thus, for every active column, there is a dedicated bit line and source line. If multiple columns are active at the same time, then each of the active columns has a unique dedicated bit line and a unique dedicated source line.

[0069] As can be seen from Figure 6, each block has sixteen rows of active columns and each bit line connects to four columns in each block. For example, bit line 228 is connected to

WO 2017/070459 PCT/US2016/058092 -15-

columns 652, 654, 670 and 674. Since all of these columns 652, 654, 670 and 674 are connected to the same word line 210, the system uses the source side select lines and the drain side select lines to choose one (or another subset) of the four to be subjected to a memory operation (program, verify, read, and/or erase).

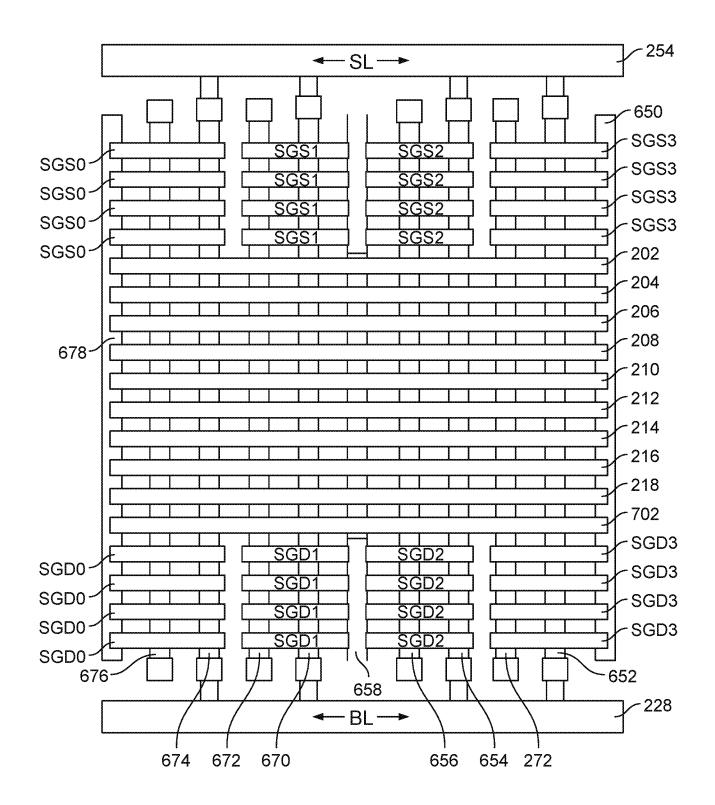

[0070] Figure 7 is a side cutaway view of a portion of the memory array, along bit line 228 and source line 254. Note that bit line 228 is the associated bit line for source line 254, therefore, forming a source line/bit line pair. Figure 7 shows that while the word line layers extend across the entire block, the source side select lines and the drain side select lines are broken up into four sections. In one embodiment, each source side select line is implemented as four vertical layers connected together. Within each block, there are source side select lines: SGS0, SGS1, SGS2 and SGS3. Similarly, the drain side select lines are implemented as four vertical layers connected together. Within each block, there are four drain side select lines: SGD0, SGD1, SGD2 and SGD3. In one embodiment, SGS0 and SGD0 are used to control columns 674 and 676, SGS1 and SGD1 are used to control columns 672 and 670, SGS2 and SGD2 are used to control columns 672 and 670, SGS2 and SGD2 are used to control columns 672 and 672.

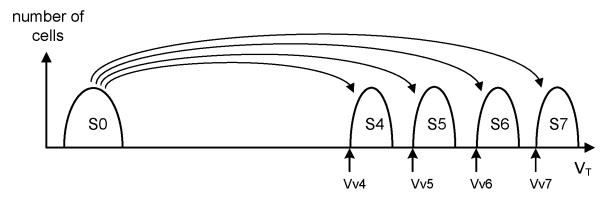

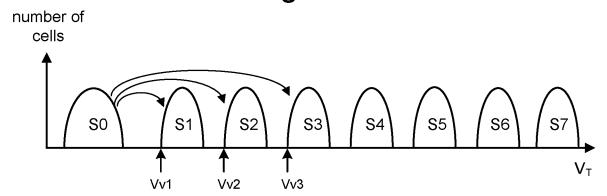

[0071] Figure 8 illustrates example threshold voltage distributions for the memory cell array when each memory cell stores three bits of data. Other embodiments, however, may use more or less than three bits of data per memory cell (e.g., such as two bits of data per memory cell, or four bits of data per memory cell). In the example of Figure 8, there are eight valid threshold voltage distributions, also called data states (or target states): S0, S1, S2, S3, S4, S5, S6 and S7. In one embodiment, data state S0 is below 0 volts and data states S1-S7 are above 0 volts. In other embodiments, all eight data states are above 0 volts, or other arrangements can be implemented. In one embodiment, the threshold voltage distribution for S0 is wider than for S1-S7. In one embodiment, S0 is for erased memory cells. Data is programmed from S0 to S1-S7.

[0072] Each data state corresponds to a unique value for the three data bits stored in the memory cell. In one embodiment, S0=111, S1=110, S2=101, S3=100, S4=011, S5=010, S6=001 and S7=000. Other mapping of data to states S0-S7 can also be used. The specific relationship between the data programmed into the memory cell and the threshold voltage levels of the cell depends upon the data encoding scheme adopted for the cells. For example,

WO 2017/070459 PCT/US2016/058092 -16-

U.S. Patent No. 6,222,762 and U.S. Patent Application Publication No. 2004/0255090, "Tracking Cells For A Memory System," filed on June 13, 2003, describe various data encoding schemes for multi-state flash memory cells. In one embodiment, data values are assigned to the threshold voltage ranges using a Gray code assignment so that if the threshold voltage of a floating gate erroneously shifts to its neighboring threshold voltage distribution, only one bit will be affected. However, in other embodiments, Gray code is not used.

[0073] In one embodiment, all of the bits of data stored in a memory cell are stored in the same logical page. In other embodiments, each bit of data stored in a memory cell corresponds to different logical pages. Thus, a memory cell storing three bits of data would include data in a first page, data in a second page and data in a third page. In some embodiments, all of the memory cells connected to the same word line would store data in the same three pages of data. In some embodiments, the memory cells connected to a word line can be grouped into different sets of pages (e.g., by odd and even bit lines, or by other arrangements).

[0074] In some devices, the memory cells will be erased to state S0. From state S0, the memory cells can be programmed to any of states S1-S7. In one embodiment, known as full sequence programming, memory cells can be programmed from the erased state S0 directly to any of the programmed states S1-S7. For example, a population of memory cells to be programmed may first be erased so that all memory cells in the population are in erased state S0. While some memory cells are being programmed from state S0 to state S1, other memory cells are being programmed from state S0 to state S3, state S0 to state S4, state S0 to state S5, state S0 to state S6, and state S0 to state S7. Full sequence programming is graphically depicted by the seven curved arrows of Fig. 8. In other embodiments, memory cells can be programmed using a coarse/fine methodology or other scheme.

[0075] Figure 8 shows a set of verify target levels Vv1, Vv2, Vv3, Vv4, Vv5, Vv6, and Vv7. These verify levels are used as comparison levels (also known as target levels and/or compare levels) during the programming process. For example, when programming memory cells to state S1, the system will check to see if the threshold voltages of the memory cells have reached Vv1. If the threshold voltage of a memory cell has not reached Vv1, then programming will continue for that memory cell until its threshold voltage is greater than or equal to Vv1. If the threshold voltage of a memory cell has reached Vv1, then programming will stop for that memory cell. Verify target level Vv2 is used for memory cells being programmed to state S2.

WO 2017/070459 PCT/US2016/058092 -17-

Verify target level Vv3 is used for memory cells being programmed to state S3. Verify target level Vv4 is used for memory cells being programmed to state S4. Verify target level Vv5 is used for memory cells being programmed to state S5. Verify target level Vv6 is used for memory cells being programmed to state S6. Verify target level Vv7 is used for memory cells being programmed to state S7.

[0076] Figure 8 also shows a set of read compare levels Vr1, Vr2, Vr3, Vr4, Vr5, Vr6, and Vr7. These read compare levels are used as comparison levels during the read process. By testing whether the memory cells turn on or remain off in response to the read compare levels Vr1, Vr2, Vr3, Vr4, Vr5, Vr6, and Vr7 being separately applied to the control gates of the memory cells, the system can determine for which states that memory cells are storing data. In one embodiment, Vr1=0.2v, Vr2=1.0v, Vr3=1.8v, Vr4=2.6v, Vr5=3.4v, Vr6=4.2v and Vr7=5.0v. However, other values can also be used.

In general, during verify operations and read operations, the selected word line is [0077] connected to a voltage, a level of which is specified for each read operation (e.g., see read compare levels Vr1, Vr2, Vr3, Vr4, Vr5, Vr6, and Vr7, of Fig. 8) or verify operation (e.g. one voltage is used to verify all states, as discussed below) in order to determine whether a threshold voltage of the concerned memory cell has reached such level. After applying the word line voltage, the conduction current of the memory cell is measured to determine whether the memory cell turned on (conducted current) in response to the voltage applied to the word line. If the conduction current is measured to be greater than a certain value, then it is assumed that the memory cell turned on and the voltage applied to the word line is greater than the threshold voltage of the memory cell. If the conduction current is not measured to be greater than the certain value, then it is assumed that the memory cell did not turn on and the voltage applied to the word line is not greater than the threshold voltage of the memory cell. During a read or verify process, the unselected memory cells on selected columns (i.e. NAND chains) corresponding to a selected word line (i.e. finger) are provided with one or more read pass voltages at their control gates so that these memory cells will operate as pass gates (e.g., conducting current regardless of whether they are programmed or erased).

[0078] There are many ways to measure the conduction current of a memory cell during a read or verify operation. In one example, the conduction current of a memory cell is measured by the rate it discharges or charges a dedicated capacitor in the sense amplifier while

maintaining a specified bit line voltage. In another example, the conduction current of the selected memory cell allows (or fails to allow) the NAND string that includes the memory cell to discharge a corresponding bit line. The voltage on the bit line is measured after a period of time to see whether it has been discharged or not. Note that the technology described herein can be used with different methods known in the art for verifying/reading. Other read and verify techniques known in the art can also be used.

**[0079]** In some embodiments, the program voltage applied to the control gate includes a series of pulses that are increased in magnitude with each successive pulse by a predetermined step size (e.g. 0.2v, 0.3v, 0.4v, 0.6v, or others). Between pulses, some memory systems will verify whether the individual memory cells have reached their respective target threshold voltage ranges.

[0800]Figures 9A-9E depict one example programming process that uses a predefined/fixed number of program pulses. In the embodiment depicted in Figures 9A-9E, six Vpgm program pulses are applied on the selected word line to achieve threshold voltage distributions as per Figure 8. Initially, in one embodiment, all memory cells being programmed are erased to data state S0. After erasing, a first Vpgm program pulse is applied. In one embodiment, the first Vpgm program pulse is at 19v; however, other voltages can be used. All memory cells being programmed will receive that same Vpgm program pulse. However, data dependent voltages are individually applied to the different bit lines and the different source lines so that memory cells being programmed to higher data states (e.g., S7) will increase in threshold voltage more quickly and memory cells being programmed to lower data states (e.g., S1) will increase in threshold voltage slower. The voltages applied to the bit lines and source lines are based on the target data state. Therefore, all memory cells being programmed to S1 will be subjected to a first bit line voltage and a first source line voltage, all memory cells being programmed to S2 will be subjected to a second bit line voltage and a second source line voltage, all memory cells being programmed to S3 will be subjected to a third bit line voltage and a third source line voltage, all memory cells being programmed to S4 will be subjected to a fourth bit line voltage and a fourth source line voltage, all memory cells being programmed to S5 will be subjected to a fifth bit line voltage and a fifth source line voltage, all memory cells being programmed to S6 will be subjected to a six bit line voltage and a six source line voltage, and all memory cells being programmed to S7 will be subjected to a seventh bit line voltage and a seventh source line voltage.

[0081] Figure 9A depicts the results of applying the first Vpgm program pulse. Figure 9A shows the target data states in solid lines and shows the actual threshold voltage distributions in dashed lines 802, 804, 806, 808, 810, 812 and 814. Actual threshold voltage distribution 802 represent the threshold voltage distribution for memory cells being programmed to data state S1. Actual threshold voltage distribution 804 represent the threshold voltage distribution for memory cells being programmed to data state S2. Actual threshold voltage distribution 806 represent the threshold voltage distribution for memory cells being programmed to data state S3. Actual threshold voltage distribution 808 represent the threshold voltage distribution for memory cells being programmed to data state S4. Actual threshold voltage distribution 810 represent the threshold voltage distribution for memory cells being programmed to data state S5. Actual threshold voltage distribution 812 represent the threshold voltage distribution for memory cells being programmed to data state S6. Actual threshold voltage distribution 814 represent the threshold voltage distribution for memory cells being programmed to data state S7. Note that the height/magnitude of the actual threshold voltage distributions 802, 804, 806, 808, 810, 812 and 814 is somewhat exaggerated in Figures A-E in order to make the drawings easier to read.

[0082] Figure 9B depicts the results of applying the second Vpgm program pulse. As depicted, actual threshold voltage distributions 802, 804, 806, 808, 810, 812 and 814 have moved toward higher voltages. The second Vpgm pulse is applied to all of the memory cells being programmed. The system is not programming in six iterations to successively move memory cells from lower states to successively higher states, as the initial Vpgm program pulse already moved memory cells to each of the distributions (802-814). Certain memory cells will be in the target data state after the first Vpgm program pulse. The system is using multiple programming iterations to tighten up the threshold voltage distributions for each data state, not to progressively move higher data state memory cells to those higher data states.

**[0083]** Figure 9C depicts the results of applying the third Vpgm program pulse. As depicted, actual threshold voltage distributions 802, 804, 806, 808, 810, 812 and 814 have moved toward higher voltages.

**[0084]** Figure 9D depicts the results of applying the fourth Vpgm program pulse. As depicted, actual threshold voltage distributions 802, 804, 806, 808, 810, 812 and 814 have moved toward higher voltages.

WO 2017/070459 PCT/US2016/058092 -20-

**[0085]** Figure 9E depicts the results of applying the fifth Vpgm program pulse. As depicted, actual threshold voltage distributions 802, 804, 806, 808, 810, 812 and 814 have moved toward higher voltages. After the sixth Vpgm program pulse, the actual threshold voltage distributions should be the same (or close) to the threshold voltage distributions depicted in Figure 8.

**[0086]** Figure 10 is a flow chart describing one embodiment of a process for performing programming on memory cells connected to a common word line to one or more targets (e.g., data states or threshold voltage ranges). The process of Figure 10 is one example of how to implement the behavior depicted in Figure 9. The process of Figure 10 can also be used to implement programming strategies different than that of Figure 9.

[0087] Typically, the program voltage applied to the control gate during a program operation is applied as a series of program pulses. Between programming pulses the system will perform verification. In many implementations, the magnitude of the program pulses is increased with each successive pulse by a predetermined step size. In step 868 of Figure 10, the programming voltage (Vpgm) is initialized to the starting magnitude (e.g., ~19V or another suitable level) and a program counter PC maintained by state machine 112 is initialized at 1. In step 870, data dependent voltages are individually applied to the different bit lines and the different source lines. Data dependent voltages are voltages that vary based on the data pattern being programmed. More details of step 870 are discussed below with respect to Figure 11. In step 872, a program pulse of the program signal Vpgm is applied to the selected word line (the word line selected for programming). In one embodiment, the group of memory cells being programmed concurrently are all connected to the same word line (the selected word line). In step 872, the program pulse is concurrently applied to all memory cells connected to the selected word line.

[0088] In step 874, it is determined whether the program counter PC is less than K. In one embodiment, K=6, which means that the programming process will apply six programming pulses. The number 6 is based on the assumption that the natural VT distribution is about 3V wide and that the average VT shift up per program pulse is 0.5V. then 3.0/0.5=6 pulses. If the step size is changed or the assumption about the width of the natural distribution is wrong, then more or less pulses are needed. The technology described herein can be used with K>6 and K<6. The natural distribution is the response (i.e. new VT distribution) of a group of cells to a single program pulse when the same program pulse (or the same sequence of program pulses)

WO 2017/070459 PCT/US2016/058092 -21-

is (are) applied to all of cells. The group of cells can be composed of, for example, all cells to be programmed on a word line, all cells to be programmed to a particular state on a word line, all cells on a block, all cells on a chip, all cells across many chips depending on the context in which the term natural VT distribution is used. Generally the larger the group of cells under consideration, the wider the natural distribution from end to end. Figure 9A shows seven different natural distributions (one per program state) where each one is the outcome for cells to be programmed to a particular state, and these outcomes are different due to the fact that lower states' programming is retarded by virtue of applied higher voltages to the cell's source line and bit line. The lower the state, the higher the retarding potential transferred to its channel by application of these higher voltages to bit lines and source lines.

[0089] If the program counter PC is less than K, then the process continues at step 876, during which all of the memory cells being programmed are concurrently verified for all target data states using a single read voltage pulse on the selected word line and data dependent voltages on individual bit lines and individual source lines. Memory cells that verify successfully will be locked out from further programming for the remainder of the programming process. In step 878, the Program Counter PC is incremented by 1 and the program voltage Vpgm is stepped up to the next magnitude. After step 878, the process loops back to step 870 and another program pulse is applied to the selected word line. In one embodiment, the six program pulses are at 19v, 19.6v, 20.2v, 20.8v, 21.4v and 22v.

**[0090]** If, in step 874, it is determined that the program counter is not less than K (i.e. PC=K) then programming should be complete and in step 880 the system confirms that the programming was successful.

[0091] In one embodiment, there is no verification performed for the last program pulse. In other embodiments, verification can be performed for the last program pulse.

**[0092]** Steps 870-878 implement a loop of applying programming and then verifying (except for the last program pulse, which has no verify). This process is performed in an iterative fashion to avoid over programming. Thus, each iteration of steps 870-878 is referred to as a programming iteration.

[0093] Figure 11 is a table that identifies one embodiment of data dependent source line voltages and bit line voltages for programming, verifying and reading. Step 870 of Figure 10 includes applying data dependent voltages to individual source lines and bit lines for

WO 2017/070459 PCT/US2016/058092 -22-

programming. The second column of Figure 11 (header of "Program") identifies the data dependent voltages applied to individual source lines and the seventh column of Figure 11 (header of "Program") identifies the data dependent voltages applied to individual bit lines. For example, if a memory cell is being programmed to state S1, then in step 870 the source line receives 4.8 volts and the bit line receives 4.8 volts. If a memory cell is being programmed to state S2, then in step 870 the source line receives 4.0 volts and the bit line receives 4.0 volts. If a memory cell is being programmed to state S3, then in step 870 the source line receives 3.2 volts and the bit line receives 3.2 volts. If a memory cell is being programmed to state S4, then in step 870 the source line receives 2.4 volts and the bit line receives 2.4 volts. If a memory cell is being programmed to state S5, then in step 870 the source line receives 1.6 volts and the bit line receives 1.6 volts. If a memory cell is being programmed to state S6, then in step 870 the source line receives 0.8 volts and the bit line receives 0.8 volts. If a memory cell is being programmed to state S7, then in step 870 the source line receives 0.0 volts and the bit line receives 0.0 volts. If the memory cell is to remain in the erased state S0, then in step 870 the source line receives 6.0 volts and the bit line receives 6.0 volts. Once a decision has been made based on one of the verify operations to lock out any particular cell from further programming (due to cell's VT exceeding its verify level), then from that point on the cell/column will be treated the same way as an erased cell (i.e. it will be locked out of further programming by boosting or other methods that inhibit programming).

loo94] Step 876 of Figure 10 includes applying data dependent voltages to individual source lines and bit lines for verifying. The fourth column of Figure 11 (second row has header of "Verify") identifies the data dependent voltages applied to individual source lines and the ninth column of Figure 11 (second row has header of "Verify") identifies the data dependent voltages applied to individual bit lines. For example, if a memory cell is being programmed to state S1, then in step 876 the source line receives 4.8 volts and the bit line receives 5.3 volts. If a memory cell is being programmed to state S2, then in step 876 the source line receives 4.0 volts and the bit line receives 4.5 volts. If a memory cell is being programmed to state S3, then in step 876 the source line receives 3.2 volts and the bit line receives 2.4 volts and the bit line receives 2.9 volts. If a memory cell is being programmed to state S4, then in step 876 the source line receives 2.6 volts and the bit line receives 2.7 volts. If a memory cell is being programmed to state S5, then in step 876 the source line receives 1.6 volts and the bit line receives 2.1 volts. If a memory cell is being programmed to state S6, then in step 870 the source line receives 0.8 volts and the bit line receives 1.3 volts.

WO 2017/070459 PCT/US2016/058092 -23-

If a memory cell is being programmed to state S7, then in step 874 the source line receives 0.0 volts and the bit line receives 0.5 volts. If the memory cell is to remain in the erased state S0, then in step 874 the source line receives 6.0 volts and the bit line receives 6.0 volts.

**[0095]** Step 870 of Figure 10 also include locking out memory cells that have been successfully verified to have reached their target data state. The fifth column of Figure 11 (second row has header of "Lockout") identifies the lockout voltages applied to individual source lines and the tenth column of Figure 11 (second row has header of "Lockout") identifies the lockout voltages applied to individual bit lines. In all cases, when a memory cell is locked out from additional programming (see step 876 of Figure 10) the source line and bit line are set at 6 volts.

[0096] Any memory cell that should be inhibited from programming has its source line and bit line set to 6.0 volts, as per the third and eighth columns of Figure 11 (second row has header of "Inhibit"). Note that the numerical values listed in Figure 11 are examples, and other values can also be used.

**[0097]** Because memory cells being programmed to lower states receive higher source line voltages and bit line voltages, the programming pulses will cause the memory cells being programmed to lower states to increase threshold voltage at a lower rate, as per the graphs of Figures 9A-E. Similarly, because memory cells being verified for lower states receive higher source line voltages and bit line voltages, the verification test can use the same single verification voltage pulse on the selected word line. Figure 13 shows a sample voltage signal applied to a selected word line. There are six Vpgm program pulses 557, 558, 559, 560, 561 and 562 that increase in magnitude, as described above. One of the program pulses is applied during each iteration of step 872 of Figure 10. Between the Vpgm program pulses are verify pulses 570. That is, between any two Vpgm program pulses is one verify pulse that is used to concurrently verify all data states by using different source line and bit line voltages as per the table of Figure 11. Concurrently verifying all data states saves considerable time during a programming process. One verify pulse 570 is applied during each iteration of step 874.

**[0098]** Figure 12 is a table that provides example voltages for the drain side select signal (VSGD), source side select signal (VSGS), selected word line (WL N), unselected word lines on the source side of the selected word line (WL#  $\leq$  N-1), and unselected word lines on the drain side of the selected word line (WL#  $\geq$  N+1). For example, during verify operations the

WO 2017/070459 PCT/US2016/058092 -24-

selected word line receives one voltage pulse at 5.2 volts, while the unselected word lines, source side select signal for the selected NAND string, and drain side select signal for the selected NAND string receive 6 volts, and while the unselected word lines on the source side receive 12 volts. Other voltages than 6V can be applied, and engineering optimization will determine the best voltages to apply to unselected word lines, various source side select gates, and various drain side select gates during both verify and program operations. During programming, the selected word line receives Vpgm (see Fig. 13), while the unselected word lines on the drain side, the source side select signal for the selected NAND string, and the drain side select signal for the selected NAND string receive 6 volts, and while the unselected word lines on the source side receive 12 volts. During reading, the selected word line receive Vcgr (ie Vr1, Vr2, Vr3, Vr4, Vr5, Vr6 or Vr 7), the source side select signal for the selected NAND string receives 4 volts, the drain side select signal for the selected NAND string receives 4 volts, and all unselected word lines receive 7 volts. Note that the numerical values listed in Figure 12 are examples, and other values can also be used.

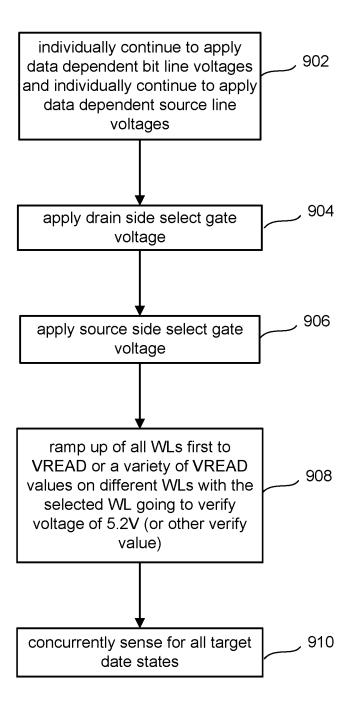

[0099] Figure 14 is a flow chart describing one embodiment of a process for verifying that is performed as part of step 876 of Fig. 10. The process of Figure 14 is one way to concurrently verify all data states, which is much faster than previous approaches which verify data states serially one data state at a time. In step 902, the individual bit lines receive a data dependent signal, as discussed above, and the individual source lines receive a data dependent signal, as discussed above. In some embodiments the system continues to apply the voltage (i.e. hold the voltage from the program pulse phase), rather than bring down the voltages applied to bit lines and source lines at the end of a program pulse by discharging them, only to recharge them back up to the same (or similar) voltage for following verify operation. This saves energy.

**[00100]** In step 904, the drain side selection signal is applied. In step 906, the source side selection signal is applied. Steps 904 and 906 can be performed concurrently or sequentially. If performed sequentially, either 904 or 906 can be performed first. In step 910, the set of sense amplifiers concurrently perform sensing operation for all (or a subset) of the memory cells for all data states. That is, the system will sense for S0, S1, S2, S3, S4, S5, S6 and S7 at the same time. Note that in some embodiments, for verifying after the first program pulse, WLs, SGSs, SGDs, BLs, & SLs can all start to rise together in order to save time. They will reach final voltage values at different times.

WO 2017/070459 PCT/US2016/058092 -25-

[00101] In another embodiment, the system can start ramping up (raising the voltage of) the word lines, the select gates, the bit lines, and the source lines all together for the selected finger (i.e. word line portion of a word line). The bit lines and the source lines can be slower to rise due to either their RC time constants being longer or the energy requirements being more (which would necessitate an intentional controlled ramp up of these ~600,000 lines in order not to exceed maximum allowed instantaneous currents), in some embodiments word lines and select gates will reach high voltages before bit lines and source lines reach high voltages. Note that one embodiment charges the bit lines and the source lines in two stages: stage 1 takes lines to Vcc or less, and stage 2 takes those lines that have to go to higher than Vcc values from Vcc to these higher values. Each stage is allotted a minimum of 20 micro seconds based on worst case bit line or source line RC time constants. The maximum time for each stage is based on how many memory cells will require their bit lines and source lines to be raised in voltage during the BL/SL charging phase which occurs before each program pulse. Some program pulses will have very few numbers of BLs and SLs charging up to high voltages (e.g. charge ups for program pulses #2 & #6, for which the circuit is RC dominated and 20us per stage will be adequate. But there are other charging phases when the system needs to allow more than 20us per one or both stages of charge up before the associated program pulse. Thus, there is a pulse by pulse control of ramp up time and pulse dependent charge up times. There may be a lot of BL & SL charge up activity prior to program pulse #1.

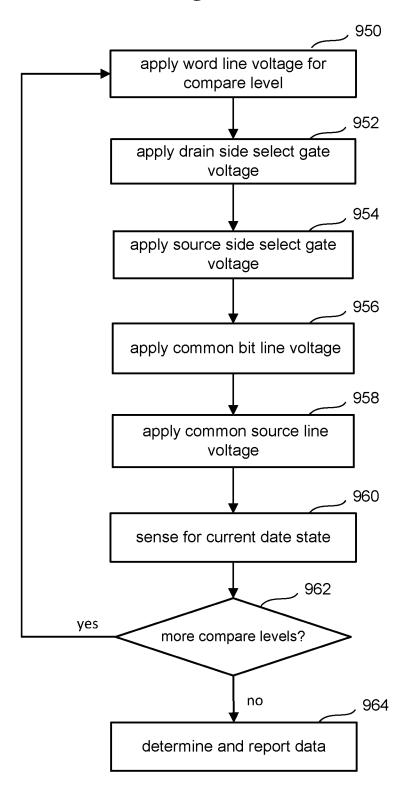

[00102] Figure 15 is a flow chart describing one embodiment of a process for reading. Unlike verification, reading is performed sequentially. That is, the system will perform a read operation for one data state at a time. In one embodiments, the system will first read to determine which memory cells are in S0, then S1, then S2, ... S7. In other embodiments, other orders can be implemented. Each data state is associated with its own word line voltage, referred to as Vcgr (ie Vr1, Vr2, Vr3, Vr4, Vr5, Vr6 or Vr 7). In step 950, the Vcgr voltage for the compare level (ie Vr1, Vr2, Vr3, Vr4, Vr5, Vr6 or Vr 7) is applied to the selected word line. Additionally, the unselected word line receive the voltages indicated in Figure 14. In step 952, the drain side selection signal is applied. In step 954, the source side selection signal is applied. In step 956, the common bit line voltage is applied to all bit lines. In step 958, the common source line voltage is applied to all source lines. In step 960, the sense amplifiers will sense data for the Vcgr applied in step 950. If there are more compare levels to apply (step 962), then the process loops back to step 950. In one set of embodiments, there are seven

WO 2017/070459 PCT/US2016/058092 -26-

compare levels, so there will be seven iteration of steps 950-960. When there are no more compare levels to evaluate (step 962), then the process continues at step 964 the system determines which data state each memory cell read is in and what the corresponding data stored is. That data is reported to the host.

**[00103]** Note that the processes of Figures 10 (programming), 14 (verifying) and 15 (reading) can be performed together in any combination, separate, concurrently, serially or in another manner.

**[00104]** In one embodiment, erasing is performed in the same manner as in the prior art. In another embodiment, erasing is performed by taking advantage of Gate Induced Drain Leakage ("GIDL"). In another embodiment, erasing is performed by the "gated diode effect," which comprises electron-hole generation assisted by bias across a PN junction and a nearby gate's assisting in increasing the electric field needed to generate electron hole pairs.

[00105] In one embodiment, immediately after programming, a read operation is performed to make sure that the bit error rate is sufficiently low. Note that ECC can be used to fix a number of bit errors.

[00106] Figure 16 is a table of voltages used during programming and verification of programming for selected word lines (WLn) in selected block for program/verify and shows the transition of waveforms for the first two program pulses and the associated verify operations. The remaining operations are the same as the second program pulse (i.e. repeats of stages 2.1 to 2.7). The last program pulse (6th pulse in this example) does not require a verify in some embodiments and its stages 6.1 to 6.5 are similar to other program pulses' corresponding stages. An addition step 6.6 during which all lines are brought back to ground will bring the program verify sequence to an end. The voltages and timings serve as examples and can be different in various scenarios. Even the sequence of events can be changed to some extent. Other than the first column of labels, each column shows voltages during a different stage of operation. The first program pulse has seven stages: 1.1, 1.2, 1.3, 1.4, 1.5, 1.6 and 1.7. The second program pulse also has seven stages: 2.1, 2.2, 2.3, 2.4, 2.5, 2.6 and 2.7. Stages 1.1, 1.2 as well as 2.1 and 2.2 are an example implementation of step 870 of Figure 10. Stages 1.4 and 1.5 as well as 2.4 and 2.5 are example implementation of step 872 of Figure 10. Stages 1.7 and 2.7 are example implementations of step 876 of Figure 10, as well as the process of Figure 14. The table shows voltages for the four source side select lines (SGS0, SGS1, SGS2,

WO 2017/070459 PCT/US2016/058092 -27-

SGS3), the four drain side select lines (SGD0, SGD0, SGD0, SGD3), the two drain side dummy word lines (WLDD1, WLDD2), the two drain side dummy word lines (WLDS1, WLDS2), the selected word line WLN, unselected word lines (WL0, WL<N-1, WLN-1, WLN+1, WL>N+1, WL47), source lines and bit line. With respect to the stage number, the digit to the left of the decimal point indicates the program pulse associated with the iteration of the programming process and the digit to the left of the decimal point refers to the sub stage (.1-.7).

[00107] The first two sub stages for the first program pulse include setting the various bit line and source voltages to their data dependent values. This is done in two stages, with the first stage (1.1) bringing the bit lines and source line to the lower of their target or VCC ( $\sim$ 3.1v). The other signals are depicted to transition from 0 to the values noted. For example, SGS0 shows " $0 \rightarrow 8$ " which represents a transition from 0 volts to 8 volts. In the second stage (1.2), the bit lines and source lines are raised from VCC to their targets (if they were not already at their targets). In third stage (1.3), the drain side select lines and source side select lines are lowered. The third stages (i.e. 1.3, 2.3, ...,6.3) can be eliminated in some embodiments for all program verify pulses. If they are to be eliminated, then select gate source and drain voltages are raised only to 6v as opposed to 8v in the first stages (i.e. 1.1, 2.1, ...,6.1). In the fourth stage, the word lines are raised to Vpass (e.g., 7-10 volts) to boost unselected NAND strings and prevent program disturb. In the fifth stage (1.5), the program pulse is applied. In the sixth stage (1.6), the system transitions to verify without bringing all of the signals down to 0 volts. In one embodiment, the system transitions to verify without bringing any of the listed signals down to 0 volts (or another resting or transition voltage). In the seventh stage, concurrent verification is performed. The stages for the second and subsequent program pulses are similar to the first program pulse, except in the first stage (e.g., 2.1, 3.1, 4.1, 5.1, and 6.1), the transition of voltages is from the previous verify voltage levels rather than 0. For some of the sub stages, the bit line voltage shows "x or 6" which represents applying the data dependent value x or 6 volts because the memory cell is locked out.

**[00108]** Note that chart of Figure 16 shows the voltages for SGS0, SGS1, SGS2, and SGS3 as well as SGD0, SGD0, SGD0, and SGD3. The depicted voltages are for the instances when the particular select lines are selecting the NAND strings that include the selected memory cells. Typically, only one of SGS0, SGS1, SGS2, and SGS3 and only one of SGD0, SGD0, SGD0, and SGD3 will be turned on. In some embodiments SGS0, SGS1, SGS2, and SGS3 are

WO 2017/070459 PCT/US2016/058092 -28-

tied to each other in any one block and can simply be referred to as SGS. In such case WL selection can be achieved by selectively turning on one of the 4 SGDs. In some embodiments SGD0, SGD1, SGD2, and SGD3 are tied to each other in any one block and can simply be referred to as SGD. In such case WL selection can be achieved by selectively turning on one of the 4 SGSs.

[00109] In one embodiment, the memory system does not necessarily have to have its bit lines below memory layers and its source line above. There can be embodiments with bit lines above the memory and source lines below the memory.

**[00110]** There is a description above of two stage charging for the bit lines and source lines. In other embodiments, three stage charging can be used for the bit lines and source lines. Three stage charging could become useful, if Vcc < 6/2 = (BL/SL voltage for inhibit)/2. Then stage 1 takes the lines to Vcc or below, stage 2 to takes the lines to slightly lower than 2\*Vcc, and stage 3 takes the lines to voltages above slightly lower than 3\*Vcc.

[00111] The above-described architecture reduces the number of program pulses and verify pulses, which results in an increase in performance of the memory system. As described, the time needed for verification is dramatically reduced as all states are verified simultaneously. Additionally, because the bit lines are below the stack, there is no need for bit line interconnects that run from below to above the stack, which saves space. Since there is only one word line per block per level, as opposed to multiple word lines on a level, the word line RC is reduced and less space is needed. Additionally, locating the bit line drivers (sense amplifiers) below the stack also save room on the integrated circuit.

[00112] If, in some embodiments, programming all states concurrently or verifying all states concurrently proves too costly (e.g. too much leakage or disturb or too complex BL drivers), the system can instead deploy a scheme that would break each program pulse into two sets: one set geared for states A, B, and C, and the other set geared for states D, E, F, and G for example. For A to C states the Vpgm pulse will start at 16.2V, and when E to G are to be programmed the first pulse for these states starts at 19V. Verify can also be broken up into two sets. This provides semi-concurrency. It will reduce the performance gain and may increase energy per bit programmed, but it may be the last resort to some leakage, or disturb problem due to very high bit line and source line voltages of full concurrent program and verify, or reducing the number of transistor in each of the ~300,000 bit line drivers. Also, since it will

reduce bit line and source line voltage requirements, it will be able to eliminate or significantly reduce the need to pump up the bit line and source line voltages that have to charge up and maintain voltages significantly higher than VCC.