(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4793320号

(P4793320)

(45) 発行日 平成23年10月12日(2011.10.12)

(24) 登録日 平成23年8月5日(2011.8.5)

(51) Int.Cl.

H04N 7/30 (2006.01)

H04N 1/41 (2006.01)

F 1

H04N 7/133

H04N 1/41Z

B

請求項の数 8 (全 51 頁)

(21) 出願番号 特願2007-131866 (P2007-131866)

(22) 出願日 平成19年5月17日 (2007.5.17)

(65) 公開番号 特開2008-288883 (P2008-288883A)

(43) 公開日 平成20年11月27日 (2008.11.27)

審査請求日 平成22年3月17日 (2010.3.17)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(72) 発明者 安藤 勝俊

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 福原 隆浩

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 畑中 高行

最終頁に続く

(54) 【発明の名称】情報処理装置および方法

## (57) 【特許請求の範囲】

## 【請求項1】

画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理手段と、

前記分析フィルタ処理手段により、帯域毎に分割された前記周波数成分を可変長符号化する符号化手段と、

前記分析フィルタ処理手段を制御し、画像データが2ライン入力される毎に、前記リフティング演算の、実行可能な演算を実行させ、さらに、前記符号化手段を制御し、前記演算が終了してから、次の画像データ2ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させる制御手段と

を備える情報処理装置。

## 【請求項2】

前記制御手段は、

前記分析フィルタ処理手段に、実行可能な演算のうち、より高域の周波数成分を生成する演算を、より先に実行させ、

前記符号化手段に、符号化可能な周波数成分のうち、より低域の周波数成分であり、かつ、同じ帯域の中では、より先に生成された周波数成分を、より先に可変長符号化させる

請求項1に記載の情報処理装置。

## 【請求項3】

10

20

前記制御手段は、前記符号化手段に、常に、前記リフティング演算により直前に生成された最低域の周波数成分より先に生成された周波数成分を可変長符号化させる

請求項 2 に記載の情報処理装置。

【請求項 4】

前記符号化手段により前記周波数成分が符号化されて得られた符号化データを保持する符号化データ保持手段をさらに備え、

前記制御手段は、前記リフティング演算により最低域の周波数成分が生成されるよりも先に、前記最低域の周波数成分に対応する、前記最低域の周波数成分よりも高域の周波数成分を符号化させ、得られた符号化データを前記符号化データ保持手段に保持させ、前記最低域の周波数成分が生成され符号化され出力された後に、前記符号化データ保持手段に保持されている前記符号化データを所定の順に出力させる

請求項 2 に記載の情報処理装置。

【請求項 5】

前記分析フィルタ処理手段により帯域毎に分割された周波数成分を保持する周波数成分保持手段をさらに備え、

前記符号化手段は、前記周波数成分保持手段に保持されている前記周波数成分を可変長符号化する

請求項 1 に記載の画像処理装置。

【請求項 6】

情報処理装置の情報処理方法であって、

画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理部を制御し、前記画像データが 2 ライン入力される毎に、前記リフティング演算の、実行可能な演算を実行させ、

帯域毎に分割された前記周波数成分を可変長符号化する符号化部を制御し、前記演算が終了してから、次の画像データ 2 ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させる

ステップを含む情報処理方法。

【請求項 7】

画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理手段と、

前記分析フィルタ処理手段により、帯域毎に分割された前記周波数成分を可変長符号化する符号化手段と、

前記符号化手段を制御し、入力された複数ラインの画像データを用いて行われた、前記リフティング演算の実行可能な演算が終了してから、次の画像データの複数ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させる制御手段と

を備える情報処理装置。

【請求項 8】

情報処理装置の情報処理方法であって、

リフティング演算によって帯域毎に分割された画像データの周波数成分を可変長符号化する符号化部を制御し、分析フィルタ処理部において前記画像データが 2 ライン入力される毎に行われる、前記リフティング演算の、実行可能な演算が終了してから、次の画像データ 2 ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させる

ステップを含む情報処理方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置および方法に関し、特に、ウェーブレット変換処理および符号化処理を効率よく行うようにし、負荷をより低減させることができるようとした情報処理装置および方法に関する。

【背景技術】

10

20

30

40

50

**【 0 0 0 2 】**

従来の代表的な画像圧縮方式として、ISO ( International Standards Organization ) によって標準化されたJPEG(Joint Photographic Experts Group)がある。これは離散コサイン変換(Discrete Cosine Transform ; DCT)を用い、比較的高いビットが割り当てられる場合には、良好な符号化画像および復号画像を供することが知られている。

**【 0 0 0 3 】**

近年では画像をフィルタバンクと呼ばれるハイパス・フィルタとローパス・フィルタとを組み合わせたフィルタによって複数の帯域に分割し、帯域毎に符号化を行う方式の研究が盛んになっている。その中でも、ウェーブレット変換符号化は、DCT変換で問題になる高圧縮でのブロック歪みが無いことから、DCTに代わる新たな技術として有力視されている。

10

**【 0 0 0 4 】**

2001年1月に国際標準化が完了したJPEG 2 0 0 0 は、このウェーブレット変換に高能率なエントロピ符号化(ビットプレーン単位のビット・モデリングと算術符号化)を組み合わせた方式を採用しており、JPEGに比べて符号化効率の大きな改善を実現している。

**【 0 0 0 5 】**

ウェーブレット変換処理(例えば特許文献1参照)は基本的に画像データを入力して、水平方向のフィルタリングと垂直方向のフィルタリングを行いながら、低域成分を階層的に分割する手段を用いる。

**【 0 0 0 6 】**

20

このウェーブレット変換処理により画像データが変換された係数データ(周波数成分)を、元の画像データに変換するウェーブレット逆変換処理は、最上位の分割レベルから最下位の分割レベルまで高域成分と低域成分を合成フィルタ処理しながら、最終的に画像を復元する処理を行う。

**【 0 0 0 7 】**

このようなウェーブレット変換・ウェーブレット逆変換を利用した符号化システムは、例えばTV会議システムやビデオゲームシステム等のように、画像データの伝送を行うシステムに利用されることが多い。つまり、送信側において、画像データがウェーブレット変換され、得られた係数データがエントロピ符号化されて符号化データとして受信側に伝送される。受信側においては、取得した符号化データがエントロピ復号されて、得られた係数データがウェーブレット逆変換されて元の画像データが復元される。このような処理の流れが一般的である。

30

**【 0 0 0 8 】**

このような画像伝送システムにおいては、画像データの伝送を低遅延で行うことが望ましい場合が多く、ウェーブレット変換処理、エントロピ符号化、ウェーブレット逆変換処理、エントロピ復号処理等の各処理に対して遅延時間の低減が求められる。

**【 0 0 0 9 】**

ところで、ウェーブレット変換処理およびエントロピ符号化処理を行うエンコーダをソフトウェアプログラムにより実現するソフトウェアエンコーダや、エントロピ復号処理やウェーブレット逆変換処理を行うデコーダをソフトウェアプログラムにより実現するソフトウェアデコーダがある。

40

**【 0 0 1 0 】**

これらのソフトウェアエンコーダやソフトウェアデコーダは、そのソフトウェアプログラムがパーソナルコンピュータ等の情報処理装置において実行されることにより、エンコーダやデコーダとしての機能が実現される。

**【 0 0 1 1 】**

【特許文献1】特開平10-283342号公報

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 1 2 】**

50

しかしながら、通常の場合、エンコーダには多様な処理が含まれており、その処理の数は、ソフトウェアプログラムを実行するCPU(Central Processing Unit)の数よりも多い。つまり、ソフトウェアエンコーダの場合、1つのCPUにおいて多様な処理を実行することになる。換言すれば1つの演算処理部を複数の処理で共有することになる。

【0013】

従って、エンコーダ機能を実現する各処理を効率よく行うように適切に実行させなければ、CPUの使用効率が低下したり、処理に必要なメモリ容量が増大したりして、負荷が増大してしまう恐れがあった。負荷の増大は、コストや遅延時間の増大に繋がる恐れもある。

【0014】

本発明は、このような従来の実情に鑑みて提案されたものであり、ウェーブレット変換処理および符号化処理をより効率よく実行させることにより、ハードウェアに負荷をより低減させることができるようにするものである。

【課題を解決するための手段】

【0015】

本発明の第1の側面は、画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理手段と、前記分析フィルタ処理手段により、帯域毎に分割された前記周波数成分を可変長符号化する符号化手段と、前記分析フィルタ処理手段を制御し、画像データが2ライン入力される毎に、前記リフティング演算の、実行可能な演算を実行させ、さらに、前記符号化手段を制御し、前記演算が終了してから、次の画像データ2ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させる制御手段とを備える情報処理装置である。

【0016】

前記制御手段は、前記分析フィルタ処理手段に、実行可能な演算のうち、より高域の周波数成分を生成する演算を、より先に実行させ、前記符号化手段に、符号化可能な周波数成分のうち、より低域の周波数成分であり、かつ、同じ帯域の中では、より先に生成された周波数成分を、より先に可変長符号化させることができる。

【0017】

前記制御手段は、前記符号化手段に、常に、前記リフティング演算により直前に生成された最低域の周波数成分より先に生成された周波数成分を可変長符号化させることができる。

【0018】

前記符号化手段により前記周波数成分が符号化されて得られた符号化データを保持する符号化データ保持手段をさらに備え、前記制御手段は、前記リフティング演算により最低域の周波数成分が生成されるよりも先に、前記最低域の周波数成分に対応する、前記最低域の周波数成分よりも高域の周波数成分を符号化させ、得られた符号化データを前記符号化データ保持手段に保持させ、前記最低域の周波数成分が生成され符号化され出力された後に、前記符号化データ保持手段に保持されている前記符号化データを所定の順に出力させることができる。

前記分析フィルタ処理手段により帯域毎に分割された周波数成分を保持する周波数成分保持手段をさらに備え、前記符号化手段は、前記周波数成分保持手段に保持されている前記周波数成分を可変長符号化することができる。

【0019】

本発明の第1の側面はまた、情報処理装置の情報処理方法であって、画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理部を制御し、前記画像データが2ライン入力される毎に、前記リフティング演算の、実行可能な演算を実行させ、帯域毎に分割された前記周波数成分を可変長符号化する符号化部を制御し、前記演算が終了してから、次の画像データ2ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させるステップを含む情報処理方法である。

【0021】

本発明の第2の側面は、画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理手段と、前記分析フィルタ処理手段により、帯域毎に分割された前記周波数成分を可変長符号化する符号化手段と、前記符号化手段を制御し、入力された複数ラインの画像データを用いて行われた、前記リフティング演算の実行可能な演算が終了してから、次の画像データの複数ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させる制御手段とを備える情報処理装置である。

本発明の第2の側面はまた、情報処理装置の情報処理方法であって、リフティング演算によって帯域毎に分割された画像データの周波数成分を可変長符号化する符号化部を制御し、分析フィルタ処理部において前記画像データが2ライン入力される毎に行われる、前記リフティング演算の、実行可能な演算が終了してから、次の画像データ2ラインが入力されるまでの間に、符号化可能な周波数成分を可変長符号化させるステップを含む情報処理方法である。

#### 【0022】

本発明の第1の側面においては、画像データの周波数成分をリフティング演算により帯域毎に分割する分析フィルタ処理部が制御され、画像データが2ライン入力される毎に、リフティング演算の、実行可能な演算が実行され、帯域毎に分割された周波数成分を可変長符号化する符号化部が制御され、演算が終了してから、次の画像データ2ラインが入力されるまでの間に、符号化可能な周波数成分が可変長符号化される。

#### 【0023】

本発明の第2の側面においては、リフティング演算によって帯域毎に分割された画像データの周波数成分を可変長符号化する符号化部が制御され、分析フィルタ処理部において画像データが2ライン入力される毎に行われる、リフティング演算の、実行可能な演算が終了してから、次の画像データ2ラインが入力されるまでの間に、符号化可能な周波数成分が可変長符号化される。

#### 【発明の効果】

#### 【0024】

本発明によれば、ウェーブレット変換処理および符号化処理を行うことができる。特に、より高効率にウェーブレット変換処理および符号化処理を行うことができ、ハードウェアにかかる負荷をより低減させることができる。

#### 【発明を実施するための最良の形態】

#### 【0033】

以下、本発明の実施の形態について説明する。まず、符号化側の構成および動作について説明する。

#### 【0034】

以下、本発明の実施の形態について説明する。まず、本発明に用いるウェーブレット変換およびウェーブレット逆変換を利用した符号化・復号システムの構成および動作について説明する。

#### 【0035】

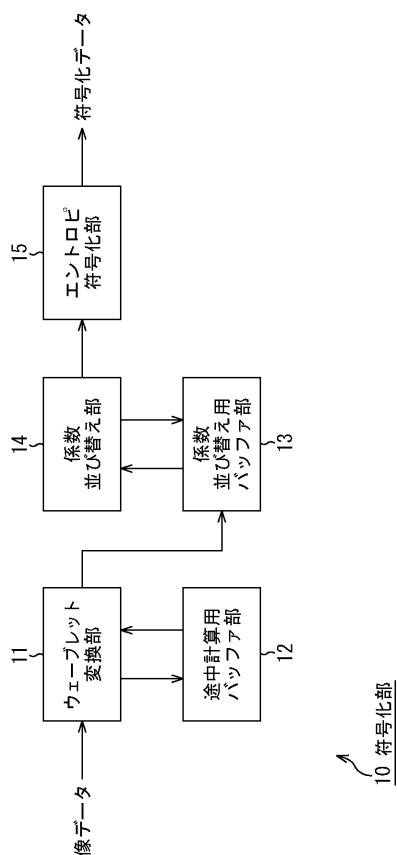

図1は、ソフトウェアプログラムにより構成され、画像データを符号化するソフトウェアエンコーダが有する機能を模式的に示した機能ブロック図である。図1に示される符号化部10は、ソフトウェアエンコーダであり、ソフトウェアプログラムがCPU(Central Processing Unit)により実行されることにより、ウェーブレット変換部11、途中計算用バッファ部12、係数並び替え用バッファ部13、係数並び替え部14、およびエントロピ符号化部15の機能を有する。

#### 【0036】

ウェーブレット変換部11は、符号化部10に入力された画像データに対して、画像データの周波数成分をその帯域毎に分離させるウェーブレット変換処理を行う。詳細については後述するが、ウェーブレット変換部11は、分析フィルタ処理により、周波数成分を低域成分と高域成分に分離する。また、ウェーブレット変換部11は、得られた低域成分に対して分析フィルタ処理を再帰的に繰り返し行うことにより、周波数成分を帯域毎に階

10

20

30

40

50

層的に分割する。なお、以下において、この周波数成分を、ウェーブレット係数、ウェーブレット係数データ、係数データ、または係数と称する。また、以下において、周波数成分分割の階層を分割レベルと称する。

【0037】

分析フィルタ処理を繰り返す際ににおいて、ウェーブレット変換部11は、次回の分析フィルタ処理に利用する係数データや画像データを途中計算用データとして途中計算用バッファ部12に保持させる。つまり、ウェーブレット変換部11は、途中計算用バッファ部12に保持させている途中計算用データ（画像データや係数データ）を読み出し、その途中計算用データを用いて、外部より入力された画像データに対してウェーブレット変換処理を行う。

10

【0038】

ウェーブレット変換部11は、各分割レベルにおいて得られた高域成分（係数データ）、および、予め定められた最終的な分割レベル（最上位レベル）の低域成分（係数データ）を、係数並び替え用バッファ部13に書き込む。

【0039】

係数並び替え部14は、係数並び替え用バッファ部13に書き込まれた係数データを所定の順序で読み出し、エントロピ符号化部15に供給する。詳細については後述するが、係数データは、ウェーブレット変換処理における生成順と、ウェーブレット逆変換処理における利用順とが異なる。そこで、係数並び替え部14は、係数並び替え用バッファ部13より係数データを、ウェーブレット逆変換処理において利用される順に読み出すことにより、係数データの並び替えを行う。

20

【0040】

エントロピ符号化部15は、供給された係数データを、所定の方法で量子化し、例えばハフマン符号化や算術符号化といった所定のエントロピ符号化方式で符号化する。つまり、エントロピ符号化部15は、係数データを、ウェーブレット逆変換処理において利用される順に符号化する。エントロピ符号化部15は、生成した符号化データを符号化部10の外部に出力する。

【0041】

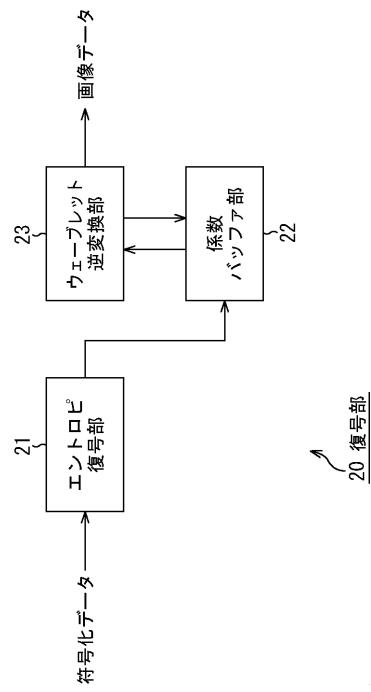

図2は、ソフトウェアプログラムにより構成され、図1の符号化部10に対応するソフトウェアデコーダが有する機能を模式的に示した機能ブロック図である。この復号部20は、符号化部10において画像データが符号化されて得られた符号化データを復号し、画像データを復元する処理部であり、エントロピ復号部21、係数バッファ部22、およびウェーブレット逆変換部23の機能を有する。

30

【0042】

符号化データが入力されると、エントロピ復号部21は、その符号化データに対して、図1のエントロピ符号化部15に対応する方法でエントロピ復号を行い、係数データを復元する。エントロピ復号部21は、得られた係数データを係数バッファ部22に保持させる。ウェーブレット逆変換部23は、係数バッファ部22に保持されている係数データに対して、図1のウェーブレット変換部11が行ったウェーブレット変換処理の逆変換処を行い、元の画像データを復元する。

40

【0043】

つまり、ウェーブレット逆変換部23は、ウェーブレット変換部11により階層的に分割された周波数成分に対して、最上位の分割レベルから順に、低域成分と高域成分を合成する合成フィルタ処理を行い、周波数成分の分割レベルを1つずつ下げていき、最終的にベースバンドの画像データを復元する。ウェーブレット逆変換部23は、生成した画像データを復号部20の外部に出力する。

【0044】

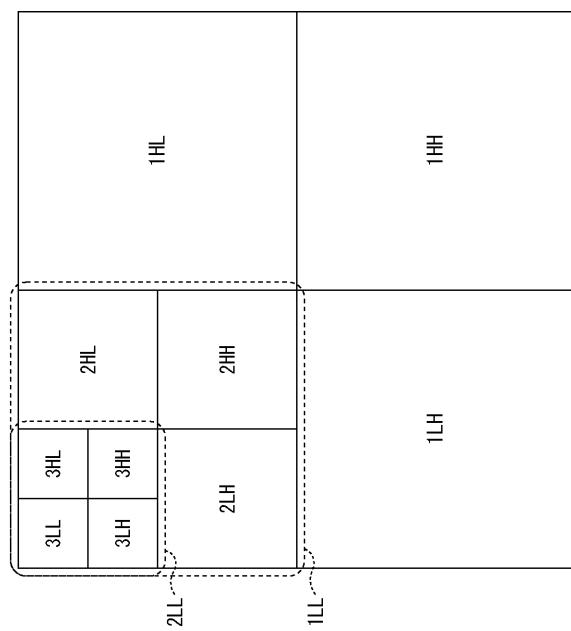

次に、このような符号化部10および復号部20を用いるシステムにおいて利用されるウェーブレット変換処理について説明する。画像データに対するウェーブレット変換では、図3に概略的に示されるように、画像データを空間周波数の高い帯域と低い帯域とに分

50

割する処理を、分割の結果得られる空間周波数の低い帯域のデータに対して再帰的に繰り返す。

【0045】

分析フィルタには、画像データに対して画面水平方向に分析フィルタ処理を行う水平分析フィルタと、画面垂直方向に分析フィルタ処理を行う垂直分析フィルタとがあり、各方向に対して1回ずつ分析フィルタ処理が行われることにより、画像データは4つの帯域（サブバンド）に分割される。図1のウェーブレット変換部11は、分析フィルタ処理結果の、水平方向および垂直方向のいずれにおいても空間周波数の低い帯域に対して、上述した水平方向および垂直方向の分析フィルタ処理が再帰的に繰り返す（つまり階層的に分割する）。

10

【0046】

図3は、分析フィルタ処理が3回繰り返された場合の例を概略的に示す図である。図3の例では、水平方向および垂直方向の分析フィルタ処理が再帰的に3回繰り替えされることにより、1ピクチャの画像データの周波数成分（係数データ）が、10個の階層的なサブバンドに分割されている。

【0047】

図3において、実線の四角および点線の角丸四角のそれぞれは、分析フィルタ処理により生成されるサブバンドを示しており、各サブバンドに表記される数字は、そのサブバンドの階層のレベル（分割レベル）を示す。つまり、ベースバンドの画像データに対して何回分析フィルタ処理することにより得られるサブバンドであるかを示している。また、各サブバンドに表記される「L」および「H」は、それぞれ低域成分および高域成分を表しており、左側が水平方向の分析フィルタ処理結果、右側が垂直方向の分析フィルタ処理結果を示している。

20

【0048】

図3の例では、ベースバンドの画像データに対して1回目の分析フィルタ処理が行われて、分割レベル1の4つのサブバンド（1LL、1LH、1HL、および1HH）が生成され、そのサブバンドのうち、水平方向および垂直方向の両方に対して低域成分であるサブバンド「1LL」に対して2回目の分析フィルタ処理が行われ、分割レベル2の4つのサブバンド（2LL、2LH、2HL、および2HH）が生成され、その水平方向および垂直方向の両方に対して低域成分であるサブバンド「2LL」に対して3回目の分析フィルタ処理が行われ、分割レベル3の4つのサブバンド（3LL、3LH、3HL、および3HH）が生成されている。

30

【0049】

このように、低域成分に対して繰り返し変換および分割を行うのは、図4に示されるように、より上位（低域成分）のサブバンドほど、画像のエネルギーが低域成分に集中しているためである。このように分析フィルタ処理を再帰的に処理を行い、階層的なサブバンドを生成し、空間周波数の低い帯域のデータをより小さな領域に追いつめていくことで、エントロピ符号化を行う際に効率的な圧縮符号化を可能とする。

【0050】

なお、以下において、分析フィルタ処理により生成される4つのサブバンドのうち、再度分析フィルタ処理が行われる、水平方向および垂直方向の両方に対して低域成分であるサブバンド「LL」を低域サブバンドと称し、それ以上分析フィルタ処理が行われないその他のサブバンド「LH」、「HL」、および「HH」を高域サブバンドと称する。

40

【0051】

このようなウェーブレット変換処理をピクチャ全体に対してまとめて行う方法もあるが、1ピクチャの画像データを数ライン毎に分割し、それについてウェーブレット変換処理を互いに独立して行う方法もある。前者の場合よりも後者の場合の方が、1回のウェーブレット変換処理で処理される画像データのデータ量が少ないので、ウェーブレット変換処理の処理結果の出力開始タイミングをより早くすることができる。つまり、ウェーブレット変換処理による負荷や遅延時間を低減させることができる。

50

## 【0052】

なお、この場合のウェーブレット変換処理の処理単位となるライン数は、ウェーブレット変換処理の、予め定められた分割レベルにおいて、最上位レベルのサブバンドの係数データ1ラインを得るために必要なライン数に基づく。

## 【0053】

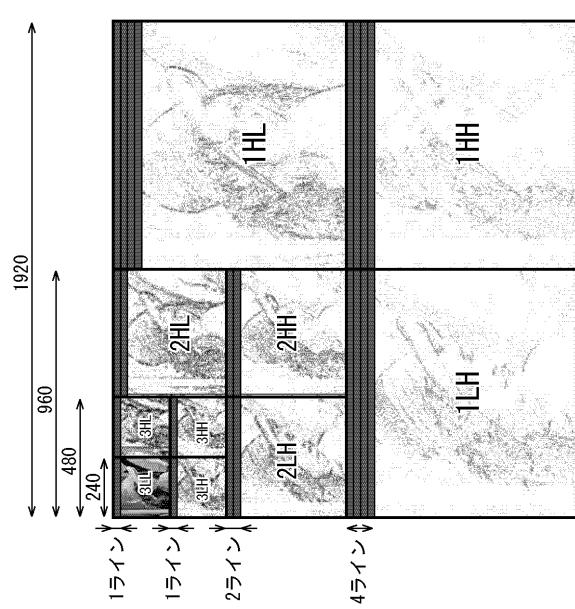

分析フィルタ処理により、データは4分割されるので、図4に示されるように、分割レベル1では4ラインであったものが、分割レベル2では2ラインとなり、分割レベル3では1ラインとなる。つまり、分割レベルが1つ上がるとともにライン数は半減する。換言すると、分割レベル3のウェーブレット変換処理の場合、最上位レベルのサブバンド(3LL、3LH、3HL、および3HH)の係数データを1ライン得るためにには、8ラインのベースバンドの画像データが必要になる。従ってこの場合、ウェーブレット変換処理は、ベースバンドの画像データ8ライン以上を処理単位としてウェーブレット変換処理が行われる。

## 【0054】

このように、最上位レベルの低域サブバンド「LL」の係数データを1ライン生成するために必要なベースバンドの画素データの集合、若しくは、その画像データより得られる係数データの集合をプレシンクト(Precinct)(またはラインブロック)と称する。

## 【0055】

なお、図4に示されるように、水平方向のデータ数は、分割レベルが1つ上がるとともに半減する。つまり、ベースバンドの画像データの水平方向の画素数が1920画素の場合、分割レベル1の係数データの水平方向のデータ数は960となり、分割レベル2の係数データの水平方向のデータ数は480となり、分割レベル3の係数データの水平方向のデータ数は240となる。

## 【0056】

ウェーブレット変換処理およびウェーブレット逆変換処理は、基本的に、ピクチャ全体ではなく、このプレシンクトを単位として行われる。つまり、1ピクチャの画像データは、それぞれが複数ラインからなる複数のプレシンクトに分割され、そのプレシンクト毎に複数回に分けて処理される。従って、基本的にはウェーブレット変換処理およびウェーブレット逆変換処理は、そのプレシンクト毎に完結する。例えば、1プレシンクトのベースバンドの画像データに対してウェーブレット変換処理が行われると、最低域成分(最上位の分割レベルの係数データ)が少なくとも1ライン以上からなる、周波数帯域毎に階層的に分割された係数データ群が得られ、その係数データ群に対してウェーブレット逆変換処理が行われると、元の1プレシンクト分のベースバンドの画像データが得られる。

## 【0057】

このように、ピクチャよりも細かいプレシンクトを単位としてウェーブレット変換処理やウェーブレット逆変換処理を行うことにより、ウェーブレット変換処理やウェーブレット逆変換処理を行うために蓄積させる画像データや係数データのデータ量(蓄積量)を低減させることができる。つまり、より早いタイミングで変換後の係数データや画像データを出力させることができ、ウェーブレット変換処理やウェーブレット逆変換処理による負荷や遅延時間を低減させることができる。

## 【0058】

なお、さらに画像データの各ラインを複数に分割したブロックを処理単位としてウェーブレット変換処理やウェーブレット逆変換処理を行う方法も考えられるが、その場合、水平同期タイミング以上に細かい単位で制御を行わなければならず、プレシンクトを処理単位とする場合よりも、制御が高速かつ複雑になり負荷が増大する恐れがある。また、ブロックを構成するライン数の最小数は、プレシンクトと同様に分割レベルにより制限される。1ピクチャの画像データは、ライン毎に、画面上のラインから順に供給されるので、ブロックを処理単位とする場合も、プレシンクトを処理単位とする場合と略同程度の画像データや係数データを蓄積させる必要がある。従って、ウェーブレット変換処理やウェーブレット逆変換処理の遅延時間は、どちらの場合もほとんど変化しない。

10

20

30

40

50

## 【0059】

なお、1プレシンクトのライン数はピクチャ内において、各プレシンクトで互いに同一でなくてもよい。

## 【0060】

ウェーブレット変換には例えば $5 \times 3$  フィルタや $9 \times 7$  フィルタ等の分析フィルタが用いられる。 $5 \times 3$  フィルタを用いた方法は、JPEG 2000 規格でも採用されており、少ないフィルタタップ数でウェーブレット変換を行うことができる点で、優れた方法である。

## 【0061】

$5 \times 3$  フィルタのインパルス応答(  $Z$  変換表現 ) は、下記の式( 1 ) および式( 2 ) に示す様に、低域フィルタ  $H_0(z)$  と、高域フィルタ  $H_1(z)$  とから構成される。 $H_0(z)$  は 5 タップで、 $H_1(z)$  は 3 タップであることがわかる。

## 【0062】

$$H_0(z) = (-1 + 2z^{-1} + 6z^{-2} + 2z^{-3} - z^{-4}) / 8 \quad \dots \quad (1)$$

$$H_1(z) = (-1 + 2z^{-1} - z^{-2}) / 2 \quad \dots \quad (2)$$

## 【0063】

これら式( 1 ) および式( 2 ) によれば、低域成分および高域成分の係数を、直接的に算出することができる。このようなフィルタを用いる分析フィルタ処理における演算方法で最も一般的な演算方法は、畳み込み演算と呼ばれる方法である。この畳み込み演算は、デジタルフィルタの最も基本的な実現手段であり、フィルタのタップ係数に実際の入力データを畳み込み乗算するものである。しかしながら、この畳み込み演算ではタップ長に応じて計算負荷が増大するので、論文「W. Sweldens, "The lifting scheme : A custom-design construction of Biorthogonal wavelets.", Appl. Comput. Harmon. Anal., vol3, no.2, pp.186-200, 1996」で紹介されたリフティング技術を用いてフィルタ処理の演算を行う方法がある。

## 【0064】

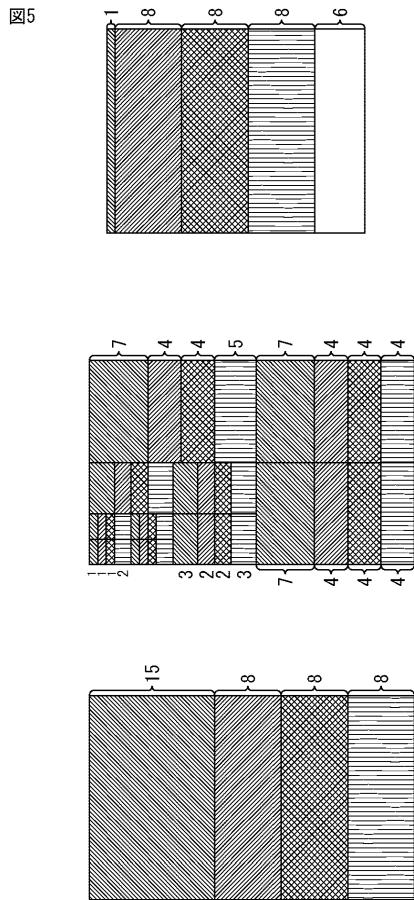

図 5 は、ウェーブレット変換処理およびウェーブレット逆変換処理によるデータの変化の様子の例を示す模式図である。図 5 A は、ウェーブレット変換されるベースバンドの画像データを模式的に示し、図 5 B は、図 5 A の画像データが分割レベル 3 でウェーブレット変換されて得られる係数データを模式的に示し、図 5 C は、図 5 B の係数データがウェーブレット逆変換されて得られるベースバンドの画像データを模式的に示している。

## 【0065】

図 5において、各模様で示される領域はそれぞれプレシンクトを示している。また、図 5 A 乃至図 5 C において同じ模様のプレシンクトは、互いに対応するプレシンクトを示している。例えば、図 5 A において右上左下の斜め線で示されるベースバンドの画像データがウェーブレット変換されると、図 5 B において右上左下の斜め線で示される、帯域毎に階層的に分割された係数データが生成され、さらにそれらの係数データがウェーブレット逆変換されると、図 5 C において右上左下の斜め線で示されるベースバンドの画像データが生成される。なお、説明の簡略化のため、図 5 においては、1ピクチャのライン数を 3 1 ラインとする。

## 【0066】

詳細については後述するが、図 5 A に示されるように、リフティング技術を用いてフィルタ処理の演算を行う場合、一般的に、ピクチャの一番上のプレシンクトは、上から 2 番目以降のプレシンクトよりも多くのライン数を必要とする。また、図 5 B に示されるように、リフティング技術を用いてフィルタ処理の演算を行う場合、一般的に、ピクチャの一番上のプレシンクトと一番下のプレシンクトは、各分割レベルにおける係数データのライン数が他のプレシンクトと異なる。

## 【0067】

さらに、リフティング技術を用いてフィルタ処理の演算を行う場合、図 5 A および図 5 C に示されるように、あるプレシンクトについて、ベースバンドの画像データをウェーブレット変換し、さらにウェーブレット逆変換すると、変換前のライン番号と異なるライン

10

20

30

40

50

番号のベースバンドの画像データが復元される。つまり、ウェーブレット変換時のプレシンクトと、そのプレシンクトに対応するウェーブレット逆変換時のプレシンクトとでは、ベースバンドの画像データのライン番号が互いに異なる。

【0068】

また、ピクチャの一番上のプレシンクトの場合、ウェーブレット変換前のベースバンドの画像データと、ウェーブレット逆変換後に得られるベースバンドの画像データとでライン数が異なる。従って、図5Aおよび図5Cに示されるように、ベースバンドの画像データをウェーブレット変換し、さらにウェーブレット逆変換するとライン数が減少する。従って、図5Cに示されるように31ラインの画像データを復元するためには、図5Aに示されるように31ラインより多くのラインの画像データをウェーブレット変換する必要がある。つまり、ウェーブレット変換時にはベースバンドの画像データにダミーデータが附加される。なお、図5Cに示されるピクチャの一番下のプレシンクトの画像データを復元するために、ウェーブレット逆変換処理においてもダミーデータが利用される。

【0069】

次に、リフティング技術について説明する。

【0070】

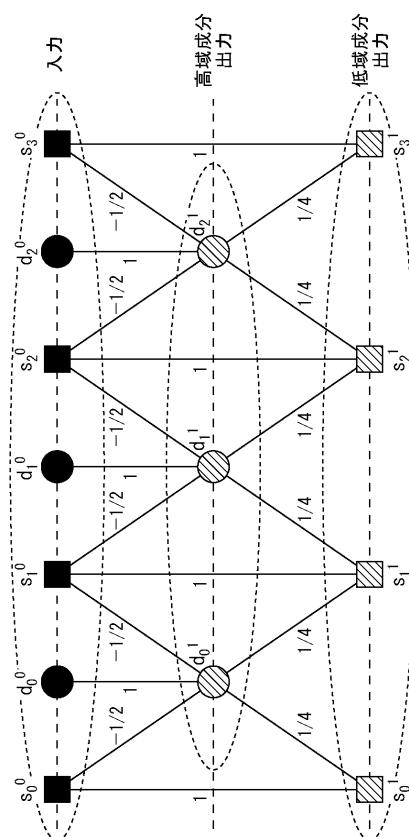

図6は、 $5 \times 3$  フィルタのリフティングを用いた例を示したものである。以下、このフィルタリング方法について説明する。

【0071】

図6において、最上段部、中段部および最下段部は、それぞれ入力画像の画素列、高域成分出力および低域成分出力を示す。最上段は、入力画像の画素列に限らず、先のフィルタ処理で得られた係数でもよい。ここでは、最上段部が入力画像で画素列であるものとし、四角印( )が偶数番目(最初を0番目とする)の画素またはライン、丸印( )が奇数番目の画素またはラインとする。

【0072】

先ず第1段階として、次式(3)により入力画素列から高域成分の係数  $d_i^1$  を生成する。

【0073】

$$d_i^1 = d_i^0 - 1/2 (s_i^0 + s_{i+1}^0) \quad \dots (3)$$

【0074】

次に第2段階として、この生成された高域成分の係数と、入力画像の奇数番目の画素とを用いて、次式(4)により低域成分の係数  $s_i^1$  を生成する。

【0075】

$$s_i^1 = s_i^0 + 1/4 (d_{i-1}^1 + d_i^1) \quad \dots (4)$$

【0076】

分析フィルタ側では、このようにして、フィルタリング処理により入力画像の画素データを低域成分と高域成分とに分解する。

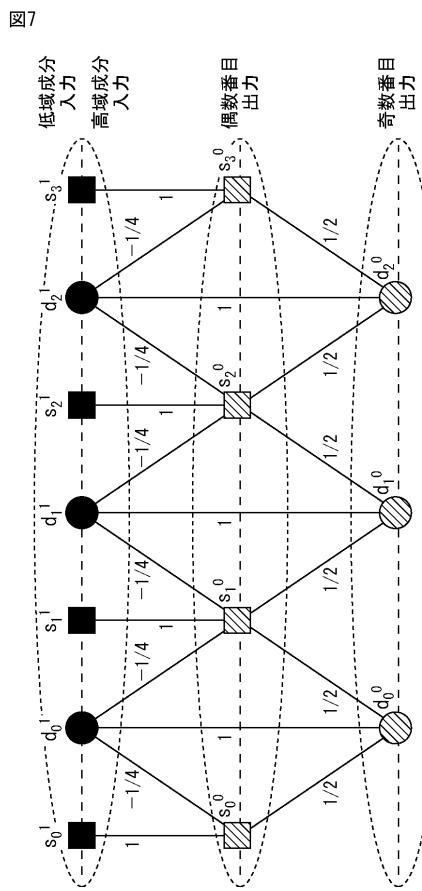

【0077】

次に、このようなウェーブレット変換により生成された係数を復元するウェーブレット逆変換を行う合成フィルタ側の処理について、図7を参照して概略的に説明する。この図7は、上述の図6と対応し、 $5 \times 3$  フィルタを用い、リフティング技術を適用した例を示す。図7において、最上段部は、ウェーブレット変換により生成された入力係数を示し、丸印( )が高域成分の係数、四角印( )が低域成分の係数をそれぞれ示す。

【0078】

先ず第1段階として、次式(5)に従い、入力された低域成分および高域成分の係数から、偶数番目(最初を0番目とする)の係数  $s_i^0$  が生成される。

【0079】

$$s_i^0 = s_i^1 - 1/4 (d_{i-1}^1 + d_i^1) \quad \dots (5)$$

【0080】

次に第2段階として、次式(6)に従い、上述の第1段階で生成された偶数番目の係数

10

20

30

40

50

$s_i^0$  と、入力された高域成分の係数  $d_i^{-1}$  から、奇数番目の係数  $d_i^0$  が生成される。

【0081】

$$d_i^0 = d_i^{-1} + 1/2 (s_i^0 + s_{i+1}^0) \quad \dots (6)$$

【0082】

合成フィルタ側では、このようにして、フィルタリング処理により低域成分および高域成分の係数を合成し、ウェーブレット逆変換を行う。

【0083】

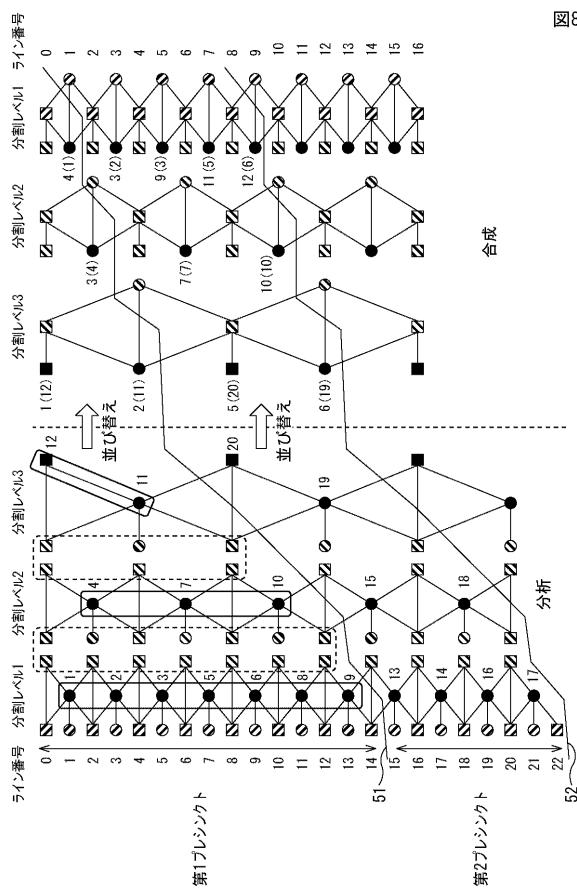

図8は、 $5 \times 3$  フィルタのリフティングによるフィルタリングを分解レベル3まで実行したときの分析フィルタ処理および合成フィルタ処理の様子の例を示す模式図である。図8の左側は分析フィルタ処理におけるリフティング演算の様子の例を示しており、図8の右側は合成フィルタ処理におけるリフティング演算の様子の例を示している。

10

【0084】

より具体的に説明すると、図8の丸や四角は、画像データまたは係数データを示しており、それらを結ぶ直線は、リフティング演算における画像データや係数データの関係を示している。つまり、図8においては、丸や四角の3列毎に1つのリフティング演算が示されており、各3列のうち、最も左の列の丸や四角がリフティング演算の入力データを示し、中央の列および最も右の列の丸や四角がリフティング演算の出力データを示している。各入力データがリフティング演算されることにより、その入力データと直線で結ばれる出力データが生成される。換言すれば、各出力データは、その出力データと直線で結ばれる入力データを用いて生成される。

20

【0085】

図8の中央縦方向の点線の左側において、左から1列目乃至3列目の丸、四角、およびそれらを結ぶ直線は分割レベル1の分析フィルタ処理のリフティング演算の様子を示し、左から4列目乃至6列目の丸、四角、およびそれらを結ぶ直線は分割レベル2の分析フィルタ処理のリフティング演算の様子を示し、左から7列目乃至9列目の丸、四角、およびそれらを結ぶ直線は分割レベル3の分析フィルタ処理のリフティング演算の様子を示している。また、図8の中央縦方向の点線の右側において、左から1列目乃至3列目の丸、四角、およびそれらを結ぶ直線は分割レベル3の合成フィルタ処理のリフティング演算の様子を示し、左から4列目乃至6列目の丸、四角、およびそれらを結ぶ直線は分割レベル2の合成フィルタ処理のリフティング演算の様子を示し、左から7列目乃至9列目の丸、四角、およびそれらを結ぶ直線は分割レベル1の合成フィルタ処理のリフティング演算の様子を示している。

30

【0086】

図8において、左上右下の斜め線模様で示される丸は、ベースバンドの画像データの、ライン番号が奇数のライン（奇数ライン）を示し、左上右下の斜め線模様で示される四角は、ベースバンドの画像データの、ライン番号が偶数のライン（偶数ライン）を示している。なお、ライン番号は、画像の一番上のラインを「0」とし、上から下に向かう順にインクリメントされる。

【0087】

また図8において、左下右上の斜め線模様で示される丸と四角は、それぞれ、リフティング演算の途中の計算に利用される途中計算用の奇数番目の係数と偶数番目の係数を示しており、図8において黒丸（○）と黒四角（□）は、それぞれ、リフティング演算結果として得られる高域成分と低域成分（周波数成分）を示している。

40

【0088】

なお、図8では、説明の簡略化のため、垂直方向についてのフィルタ処理のみ説明しており、水平方向の分析フィルタ処理および合成フィルタ処理については省略している。

【0089】

より具体的に説明する。図8の中央縦方向の点線の左側において、左から1列目に示される画像データが入力されると、ウェーブレット変換部11は、それらの画像データに対して分割レベル1の分析フィルタ処理（リフティング演算）を行い、左から2列目に示さ

50

れる分割レベル 1 の高域成分と、左から 3 列目に示される分割レベル 1 の低域成分を生成する。この左から 2 列目に示される分割レベル 1 の高域成分は、これ以上分析フィルタ処理が行われず、係数並び替え用バッファ部 1 3 に供給されて保持される。また、左から 3 列目に示される分割レベル 1 の低域成分は、再度分析フィルタ処理を行うために、途中計算用データとして途中計算用バッファ部 1 2 に供給されて保持される。

#### 【 0 0 9 0 】

次に、ウェーブレット変換部 1 1 は、途中計算用バッファ部 1 2 に保持させた途中計算用データに対して、図 8 の中央縦方向の点線の左側において、左から 4 列目乃至 6 列目に示されるように、分割レベル 2 の分析フィルタ処理（リフティング演算）を行う。左から 4 列目の丸および四角は、それぞれ、左から 3 列目の同じ行の四角と同じ係数データを示しており、丸が奇数ラインの係数データを示し、四角が偶数ラインの係数データを示している。

#### 【 0 0 9 1 】

ウェーブレット変換部 1 1 は、左から 4 列目に示される係数データに対して分割レベル 2 の分析フィルタ処理（リフティング演算）を行い、左から 5 列目に示される分割レベル 2 の高域成分と、左から 6 列目に示される分割レベル 2 の低域成分を生成する。この左から 5 列目に示される分割レベル 2 の高域成分は、これ以上分析フィルタ処理が行われず、係数並び替え用バッファ部 1 3 に供給されて保持される。また、左から 6 列目に示される分割レベル 2 の低域成分は、再度分析フィルタ処理を行うために、途中計算用データとして途中計算用バッファ部 1 2 に供給されて保持される。

#### 【 0 0 9 2 】

次に、ウェーブレット変換部 1 1 は、途中計算用バッファ部 1 2 に保持させた途中計算用データに対して、図 8 の中央縦方向の点線の左側において、左から 7 列目乃至 9 列目に示されるように、分割レベル 3 の分析フィルタ処理（リフティング演算）を行う。左から 7 列目の丸および四角は、それぞれ、左から 6 列目の同じ行の四角と同じ係数データを示しており、丸が奇数ラインの係数データを示し、四角が偶数ラインの係数データを示している。

#### 【 0 0 9 3 】

ウェーブレット変換部 1 1 は、左から 7 列目に示される係数データに対して分割レベル 3 の分析フィルタ処理（リフティング演算）を行い、左から 8 列目に示される分割レベル 3 の高域成分と、左から 9 列目に示される分割レベル 3 の低域成分を生成する。分割レベル 3 は、予め最上位レベルとして設定されており、これ以上分析フィルタ処理は行われない。従って、左から 8 列目に示される分割レベル 3 の高域成分も、左から 9 列目に示される分割レベル 3 の低域成分も、係数並び替え用バッファ部 1 3 に供給されて保持される。

#### 【 0 0 9 4 】

つまり、図 8 の中央縦方向の点線の左側において、左から 3 列目および 4 列目の係数データを囲む点線の角丸四角、並びに、左から 5 列目および 6 列目の係数データを囲む点線の角丸四角は、途中計算用バッファ部 1 2 を示しており、左から 2 列目、5 列目、8 列目、および 9 列目の係数データをそれぞれ囲む実線の角丸四角は、係数並び替え用バッファ部 1 3 を示している。

#### 【 0 0 9 5 】

以上のように、ウェーブレット変換部 1 1 は、ウェーブレット変換処理により、分割レベル 1 から分割レベル 3 に向かう順にリフティング演算を行うことにより、高域から低域に向かう順に各分割レベルの係数データを生成する。ただし、詳細については後述するが、実際には、画像データは 1 ラインずつ入力されるので、ウェーブレット変換部 1 1 は、画像データが 2 ライン入力される毎にリフティング演算を行うことができる。つまり、入力された画像データや、係数並び替え用バッファ部 1 3 に保持させる係数データも、次のリフティング演算に利用する場合がある。従って、そのような画像データは、入力されたときのリフティング演算に使用されるだけでなく、途中計算用データとして途中計算用バ

10

20

30

40

50

ツファ部12に保持され、次のラインが入力されたときに行われるリフティング演算にも利用される。係数データも同様に、係数並び替え用バッファ部13に保持されるだけでなく、途中計算用データとして途中計算用バッファ部12に保持され、後に行われるリフティング演算にも利用される。

#### 【0096】

ウェーブレット変換部11は、上述したリフティング演算により、リフティング演算結果の係数データ（黒丸（○）と黒四角（△））を、それぞれの左側に付した番号順に生成する。

#### 【0097】

これに対して、図8中央縦方向の点線の右側には、ウェーブレット逆変換部23による合成フィルタ処理におけるリフティング演算の様子が示される。 10

#### 【0098】

図8の中央縦方向の点線の右側において、左から1列目に示される係数データ（黒丸（○）と黒四角（△））は、それぞれ、自分自身と同じ行の、図8の中央縦方向の点線の左側の左から8列目または9列目の係数データと同じデータである。つまり、ウェーブレット逆変換部23は、図8の中央縦方向の点線の右側において左から1列目に示される分割レベル3の低域成分（黒四角（△））と高域成分（黒丸（○））を合成する、分割レベル3の合成フィルタ処理（リフティング演算）を行い、左から2列目に示される分割レベル2の低域成分の偶数ラインの係数データと、左から3列目に示される分割レベル2の低域成分の奇数ラインの係数データを生成する。 20

#### 【0099】

この左から2列目および3列目に示される分割レベル2の低域成分と、新たに供給された分割レベル2の高域成分に対して、ウェーブレット逆変換部23は、再度リフティング演算（分割レベル2の合成フィルタ処理）を行う（左から4列目乃至6列目）。左から4列目の左下右上の斜線模様の四角は、それぞれ自分自身と同じ行の、左から2列目の四角または左から3列目の丸と同じ係数データを示している。また、左から4列目の黒丸（○）は、それぞれ自分自身と同じ行の、図8の中央縦方向の点線の左側において左から5列目の黒丸（○）と同じ係数データ、すなわち、新たに供給された分割レベル2の高域成分を示している。 30

#### 【0100】

ウェーブレット逆変換部23は、図8の中央縦方向の点線の右側において左から4列目に示される分割レベル2の低域成分と高域成分を合成する、分割レベル2の合成フィルタ処理（リフティング演算）を行い、左から5列目に示される分割レベル1の低域成分の偶数ラインの係数データと、左から6列目に示される分割レベル1の低域成分の奇数ラインの係数データを生成する。

#### 【0101】

この左から5列目および6列目に示される分割レベル1の低域成分と、新たに供給された分割レベル1の高域成分に対して、ウェーブレット逆変換部23は、再度リフティング演算（分割レベル1の合成フィルタ処理）を行う（左から7列目乃至9列目）。左から7列目の左下右上の斜線模様の四角は、それぞれ自分自身と同じ行の、左から5列目の四角または左から6列目の丸と同じ係数データを示している。また、左から7列目の黒丸（○）は、それぞれ自分自身と同じ行の、図8の中央縦方向の点線の左側において左から2列目の黒丸（○）と同じ係数データ、すなわち、新たに供給された分割レベル1の高域成分を示している。 40

#### 【0102】

ウェーブレット逆変換部23は、図8の中央縦方向の点線の右側において左から7列目に示される分割レベル1の低域成分と高域成分を合成する、分割レベル1の合成フィルタ処理（リフティング演算）を行い、左から8列目に示されるベースバンドの画像データの偶数ラインと、左から9列目に示されるベースバンドの画像データの奇数ラインを生成する。 50

## 【0103】

以上のような分析フィルタ処理および合成フィルタ処理のリフティング演算の関係から、プレシンクトは、曲線51および曲線52に示されるように区切られる。つまり、ウェーブレット変換時においては、ピクチャの一番上のプレシンクトである第1プレシンクトの画像データは、ライン番号0乃至ライン番号14の15ラインが必要であり、ピクチャの上から2番目のプレシンクトである第2プレシンクトの画像データは、ライン番号15乃至ライン番号22の8ラインが必要である。なお図8に示されるように実際には、第2プレシンクトの分析フィルタ処理において、第1プレシンクトの画像データや係数データも利用される。

## 【0104】

また、ウェーブレット逆変換時においては、第1プレシンクトの係数データより、ライン番号0の1ラインの画像データが生成され、第2プレシンクトの係数データより、ライン番号1乃至ライン番号8の8ラインの画像データが生成される。なお図8に示されるように実際には、第2プレシンクトの合成フィルタ処理において、第1プレシンクトの画像データや係数データも利用される。

## 【0105】

図8の中央縦方向の点線の右側において、黒丸(○)および黒四角(□)の左側に付した番号は、それぞれの係数データが合成フィルタ処理において利用される順序を示している。また、その数字の横に示される括弧内の数字は、その係数データが分析フィルタ処理において生成された順序を示している。つまり、図8の中央縦方向の点線の右側において示される括弧内の数字は、図8の中央縦方向の点線の左側に示される数字と対応する。

## 【0106】

つまり、分析フィルタにおける係数データの生成順と、合成フィルタにおける係数データの利用順は互いに異なる。従って図8の中央において白抜き矢印で示されるように、分析フィルタ処理において生成された係数データは、合成フィルタ処理が行われる前に、その順序を並び替えられる必要がある。

## 【0107】

係数並び替え部14は、係数並び替え用バッファ部13に保持された係数データを、合成フィルタ処理における利用順に読み出すことにより、この係数データの並び替えを行う。つまり、エントロピ符号化部15は、合成フィルタ処理における利用順に係数データを符号化する。

## 【0108】

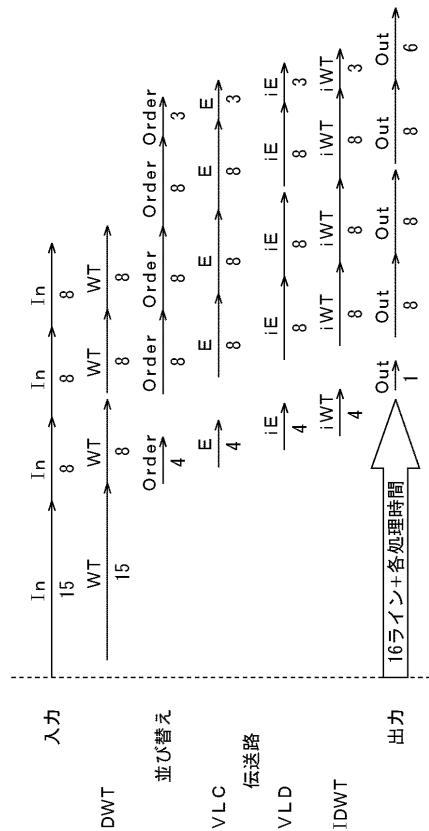

符号化部10および復号部20の各部は、それぞれの処理を、図9に模式的に示されるように、互いに並列的に実行する。つまり、符号化部10による、画像データの入力、ウェーブレット変換(DWT)、係数の並び替え、およびエントロピ符号化(VLC)の各処理と、復号部20による、エントロピ復号(VLD)、ウェーブレット逆変換(IDWT)、および画像データ出力の各処理は、図9の矢印に示されるように、互いに並行して実行される。各矢印は1プレシンクトに対する処理を示しており、各矢印の下に付された数字は、その矢印において処理されるライン数を示している。例えば、各処理において一番左の矢印で示される第1プレシンクトの場合、15ラインの画像データが入力され、4ラインの係数データにウェーブレット変換されて符号化され、さらに復号された後ウェーブレット逆変換されて1ラインの画像データとして出力される。これは図8を参照して行った説明と一致する。

## 【0109】

このように並行して処理を行うことにより、入力から出力までの遅延時間を、図9において白抜き矢印に示されるように、15ライン分の時間と各処理の処理時間の合計にすることができる。これに対して例えば1ピクチャ全体を対象としてウェーブレット変換する場合、1ピクチャ分以上の遅延時間が発生する。従って、プレシンクト単位で各処理を行い、かつ、図9に示されるように各処理を互いに並行して実行させることにより、入力から出力までの遅延時間を大幅に低減させることができる。

10

20

30

40

50

## 【0110】

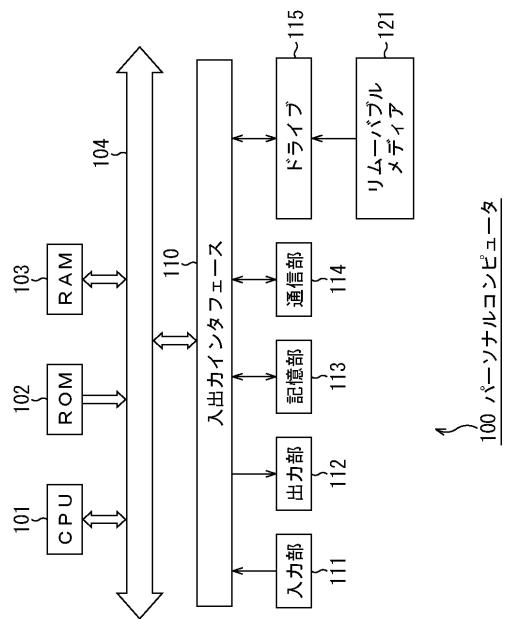

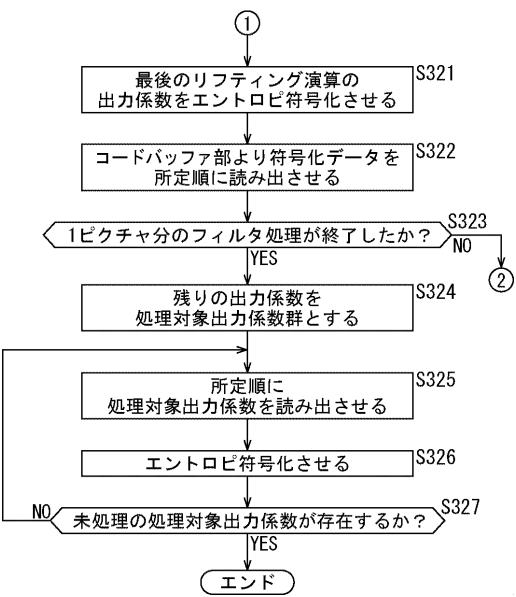

しかしながら、ソフトウェアエンコーダやソフトウェアデコーダの場合、図10に示されるようなパーソナルコンピュータにおいてソフトウェアプログラムが実行されることにより実現される。

## 【0111】

図10は、パーソナルコンピュータの構成例を示すブロック図である。

## 【0112】

図10において、パーソナルコンピュータ100のCPU101は、ソフトウェアプログラムを実行することにより、各種の処理を実行する演算処理部である。CPU101は、共有バスであるバス104を介してROM(Read Only Memory)102およびRAM(Random Access Memory)103と相互に接続されている。ROM102には予めソフトウェアプログラムやデータが格納されている。RAM103には、ROM102や記憶部113に格納されているソフトウェアプログラムやデータがロードされる。RAM103にはまた、CPU101が各種の処理を実行する上において必要なデータなども適宜記憶される。

10

## 【0113】

CPU101、ROM102、およびRAM103は、バス104を介して相互に接続されている。このバス104にはまた、入出力インターフェース110も接続されている。

## 【0114】

入出力インターフェース110には、キーボード、マウスなどよりなる入力部111、CRT(Cathode Ray Tube)、LCD(Liquid Crystal Display)などよりなるディスプレイ、並びにスピーカなどよりなる出力部112、ハードディスクなどより構成される記憶部113、モデムなどより構成される通信部114が接続されている。通信部114は、例えばインターネットに代表されるネットワークを介しての通信処理を行う。

20

## 【0115】

入出力インターフェース110にはまた、必要に応じてドライブ115が接続され、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリなどのリムーバブルメディア121が適宜装着され、それらから読み出されたコンピュータプログラムが、必要に応じて記憶部113にインストールされる。

## 【0116】

なお、図示は省略するが、CPU101の内部には、キャッシュメモリが設けられている。このキャッシュメモリは、RAM103に比べて高速に動作するものの、RAM103に比べて容量が小さい。つまり、このキャッシュメモリには、一度に格納可能なデータ量が制限される。従って、CPU101は、使用頻度の高いデータや、近いうちに使用する予定のあるデータをこのキャッシュメモリに格納し、使用頻度が少ないデータや当面利用する予定の無いデータ等をRAM103に保持させる。

30

## 【0117】

図10に示されるように、パーソナルコンピュータ100には、演算処理部はCPU101の1つしか存在しない。従って、図1に示される符号化部10のようなソフトウェアエンコーダの各処理を図9に示されるように、実際に並列に実行させることはできない。そのため、各処理が擬似的に並列に実行されているようにするために、CPU101を時分割して各処理に割り当てる必要がある。その場合、時分割の単位として、プレシンクトを用いる方法が考えられる。

40

## 【0118】

つまり、図1に示されるように、供給される画像データに対して、1プレシンクトを対象としてウェーブレット変換処理を行い、係数を並び替え、エントロピ符号化処理を施すようにする。これをプレシンクト毎に複数回繰り返すことにより、1ピクチャの画像データを処理するようにする。このようにすることにより、ピクチャ全体を対象としてウェーブレット変換する場合よりも、ウェーブレット変換処理の負荷や遅延時間を低減させることができる。

## 【0119】

50

しかしながら、単純に1プレシンクト全体を対象としてウェーブレット変換処理を行う場合、入力される画像データを1プレシンクト分蓄積しなければならず、メモリ量が増大し、回路規模やコストが増大するだけでなく、負荷や遅延時間も増大してしまう恐れがある。

【0120】

そこで、上述したようにウェーブレット変換部11がリフティング演算を用いてウェーブレット変換処理を行うことに着目し、1プレシンクトの画像データに対して行うウェーブレット変換処理を効率よく行うことにより、この画像データの蓄積量を低減させるようする。

【0121】

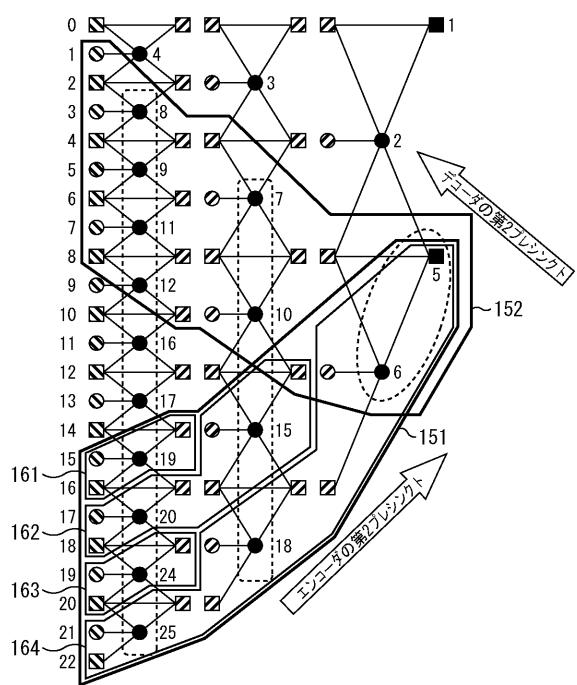

図11にウェーブレット変換処理におけるリフティング演算の手順の例を示す。図11においては、ピクチャの上から2番目のプレシンクトである第2プレシンクトを例に説明する。第1プレシンクトや第3プレシンクト以降のプレシンクトの場合も基本的には同様である。

【0122】

図11は、基本的に図8と同様の図であり、分析フィルタ処理として $5 \times 3$ フィルタを用いたときのリフティング演算の様子の例を示す図である。従って図11の詳細についての説明は省略する。なお、黒丸(○)と黒四角(△)の右横または下に付された番号は、各係数データの合成フィルタ処理される順序を示している。

【0123】

図11において、曲線151により囲まれる部分が符号化部10における第2プレシンクト(第2プレシンクトに対するリフティング演算の様子)を示している。図8を参照して説明したように、リフティング演算は、白抜き矢印で示されるように、図中左から右へ、すなわち、より高域の周波数成分を生成するリフティング演算をより先に実行するよう進む。従って、第2プレシンクトに対するリフティング演算は、画像データが2ライン入力される度に、曲線161乃至曲線164に示されるように行うことができる。つまり、ウェーブレット変換部11は、ライン番号15および16の画像データが入力されると、曲線161に囲まれる部分のリフティング演算を行い、19番目に合成フィルタ処理される係数データを生成し、ライン番号17および18の画像データが入力されると、曲線162に囲まれる部分のリフティング演算を行い、20番目に合成フィルタ処理される係数データを生成し、さらに、15番目に合成フィルタ処理される係数データを生成する。

【0124】

続いて、ウェーブレット変換部11は、ライン番号19および20の画像データが入力されると、曲線163に囲まれる部分のリフティング演算を行い、24番目に合成フィルタ処理される係数データを生成し、ライン番号21および22の画像データが入力されると、曲線164に囲まれる部分のリフティング演算を行い、25番目に合成フィルタ処理される係数データを生成し、さらに、18番目に合成フィルタ処理される係数データを生成し、最後に、6番目に合成フィルタ処理される係数データと5番目に合成フィルタ処理される係数データを生成する。

【0125】

このように、2ライン画像データが入力される毎に、実行可能なリフティング演算を順次行うことにより、ウェーブレット変換部11は、1プレシンクト分の画像データを蓄積する必要がなくなり、必要なメモリ容量を低減させ、回路規模や製造コストを低減させることができるだけでなく、ウェーブレット変換処理の負荷や遅延時間を低減させることができる。

【0126】

なお、この符号化部10における第2プレシンクトに対応する、復号部20における第2プレシンクトは、図11の曲線152により囲まれる部分に示されており、係数データに付された番号で示されるように、合成フィルタ処理は、白抜き矢印で示されるように、図中右から左に向かう向き、すなわち、分析フィルタ処理により帯域毎に分割された各周

10

20

30

40

50

波数成分のうち、より低域の周波数成分であり、かつ、同じ帯域の中では、より先に生成された周波数成分を、より先に処理するように進められる。符号化部10において、エントロピ符号化の処理順は、上述したように、ウェーブレット逆変換（合成フィルタ処理）の処理順と同じである。つまり、このエントロピ符号化も、分析フィルタ処理により帯域毎に分割された各周波数成分のうち、より低域の周波数成分であり、かつ、同じ帯域の中では、より先に生成された周波数成分を、より先に処理するように進められる。

#### 【0127】

黒丸や黒四角で示される、ウェーブレット変換部11より出力される係数データは、係数並び替え部14により、その番号順にエントロピ符号化部15に供給される。エントロピ符号化部15は、その供給順に各係数データに対してエントロピ符号化を行い、それぞれの符号化データを得る。つまり、エントロピ符号化部15は、ウェーブレット変換処理により、図11において点線の機能で囲まれた、5番目に合成フィルタ処理される係数データと6番目に合成フィルタ処理される係数データが生成されるまで、復号部20における第2プレシンクトの係数データに対してエントロピ符号化を開始することができない。

10

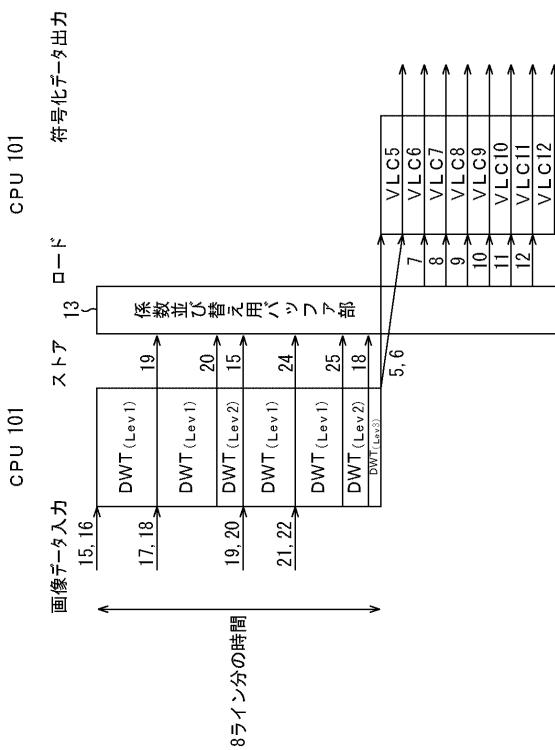

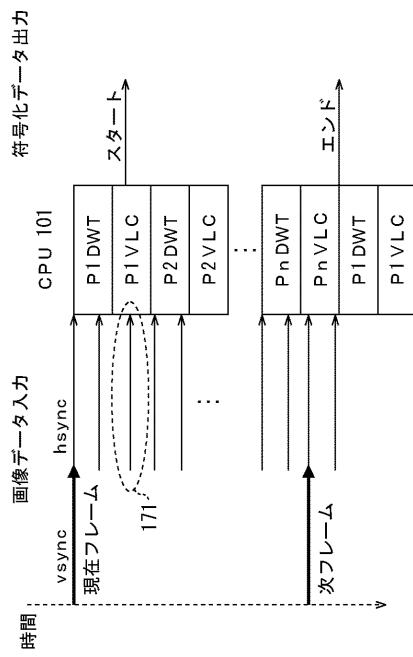

#### 【0128】

従って、CPU101においては、図12に示されるように符号化部10の各処理が進められる。図12において、CPU101は、ソフトウェアプログラムを実行することにより符号化部10の機能を実現する。なお、そのCPU101に対して符号化される画像データが、通常再生の速度、つまりビデオ信号の同期タイミングに合わせて入力される。つまり、CPU101には画像データが1ラインずつ、ビデオ信号の水平同期タイミングに合わせて略一定の間隔で供給される。

20

#### 【0129】

CPU101は、符号化部10における第2プレシンクトについて、画像データが2ライン入力される毎に実行可能なリフティング演算（分析フィルタ処理）を行う（DWT（Lev1）乃至DWT（Lev3））。

#### 【0130】

図12において、「DWT（Lev1）」と記述された四角は、CPU101に分割レベル1の合成フィルタ処理が割り当てられる時間の例を示しており、「DWT（Lev2）」と記述された四角は、CPU101に分割レベル2の合成フィルタ処理が割り当てられる時間の例を示しており、「DWT（Lev3）」と記述された四角は、CPU101に分割レベル3の合成フィルタ処理が割り当てられる時間の例を示している。つまり、図中、一番上の段の四角（DWT（Lev1））に示される時間（ライン番号16（および15）の画像データが入力されてから、ライン番号18（および17）の画像データが入力されるまでの間）において、CPU101が図11の曲線161に囲まれた部分のリフティング演算を行い、上から2段目の四角（DWT（Lev1））と3段目の四角（DWT（Lev2））に示される時間（ライン番号18（および17）の画像データが入力されてから、ライン番号20（および19）の画像データが入力されるまでの間）において、CPU101が図11の曲線162に囲まれた部分のリフティング演算を行い、上から4段目の四角（DWT（Lev1））に示される時間（ライン番号20（および19）の画像データが入力されてから、ライン番号22（および21）の画像データが入力されるまでの間）において、CPU101が図11の曲線163に囲まれた部分のリフティング演算を行い、上から5段目の四角（DWT（Lev1））と6段目の四角（DWT（Lev2））と7段目の四角（DWT（Lev3））に示される時間（ライン番号22（および21）の画像データが入力された後の時間）において、CPU101が図11の曲線164に囲まれた部分のリフティング演算を行うことが示されている。

30

40

#### 【0131】

CPU101は、各リフティング演算において、符号化する係数データを生成すると、それを順次係数並び替え用バッファ部13に保持させる。この係数並び替え用バッファ部13は、例えば、CPU101内のキャッシュメモリやRAM103により構成される。

#### 【0132】

そして、5番目に合成フィルタ処理される係数データと6番目に合成フィルタ処理され

50

る係数データを生成すると、CPU 101 は、復号部 20 における第 2 プレシンクトの係数データに対してエントロピ符号化を開始する。なお、このとき最後に生成された、5 番目に合成フィルタ処理される係数データと 6 番目に合成フィルタ処理される係数データは、データ量も少なく、かつ直ぐに使用するので、CPU 101 において保持したまま、係数並び替え用バッファ部 13 に保持させずに、エントロピ符号化処理を開始する。

#### 【0133】

このように、最後に生成された係数データを最初に符号化するという、係数並び替えの特徴を利用して、5 番目に合成フィルタ処理される係数データと 6 番目に合成フィルタ処理される係数データの、係数並び替え用バッファ部 13 への保持を省略することにより、係数並び替え用バッファ部 13 として必要なメモリ容量を低減させることができる。これにより、回路規模および製造コストを低減させることができるのでなく、係数並び替え用バッファ部 13 への書き込みおよび読み出しの回数が低減されるので、ウェーブレット変換処理および符号化の負荷や遅延時間を低減させることができる。10

#### 【0134】

エントロピ符号化を開始したCPU 101 は、5 番目乃至 12 番目に合成フィルタ処理される係数データをその番号順に 1 ラインずつ符号化し、得られた符号化データを順次出力する。

#### 【0135】

図 12 において、「VLC 5」と記述された四角は、CPU 101 に、5 番目に合成フィルタ処理される係数データを符号化するエントロピ符号化処理が割り当てられる時間の例を示している。「VLC 6」乃至「VLC 12」も同様に、6 番目乃至 12 番目に合成フィルタ処理される係数データを符号化するエントロピ符号化処理が、それぞれ割り当てられる時間の例を示している。20

#### 【0136】

なお、図 12 において、図中縦方向上から下に向かう向きに時間の流れを示しているが、その縦方向の長さ（スケール）が、時間の長さを正確に示しているわけではない。例えば、図 12 において、画像データの入力が 2 ラインずつ入力され、さらに、各入力の間隔が一定でないよう示されているが、実際には、画像データはビデオ信号の水平同期タイミングに合わせた略一定の周期で 1 ラインずつ入力される。

#### 【0137】

また、上述したように、図 12 に示される各四角（係数並び替え用バッファ部 13 を除く）は、リフティング演算やエントロピ符号化等の処理がCPU 101 に割り当てられる時間を示しているが、これは、CPU 101 がその四角に示される時間において割り当てられた処理を行うことを示すものであり、CPU 101 による各処理の処理時間を示すものではない。つまり、CPU 101 が四角に示される時間のうち一部の時間で処理を終了させる場合もある。また、上述したように図 12 において縦方向の長さが時間の長さを示しているわけではなく、四角の縦方向の長さも処理の割り当て時間を正確に示すものではない。30

#### 【0138】

図 12 のような処理の流れの場合、ウェーブレット変換処理 (DWT) を行っている期間中に入力される画像データに対しては、CPU 101 は、分析フィルタ処理をリアルタイム（即時的）に行うことができるが、エントロピ符号化処理 (VLC) を行っている期間に入力される入力される画像データに対しては、分析フィルタ処理をリアルタイム（即時的）に行うことができない。40

#### 【0139】

つまり、図 13 に示されるように、通常の再生速度のビデオ信号のように、所定の速度で入力される画像データは、そのビデオ信号の垂直同期信号 (vsync) の同期タイミングに同期してピクチャ毎に入力される。各ピクチャの画像データは、ビデオ信号の水平同期信号 (hsync) の同期タイミングに同期してライン毎に入力される。つまり、画像データは略定期的に（略一定のペースで）1 ラインずつ入力される。これに対して、CPU 101 は、図 13 に示されるようにプレシンクト毎にウェーブレット変換処理 (DWT) とエント

ロピ符号化処理（VLC）を交互に実行する。

【0140】

従って、例えば、図13において点線の橢円171に囲まれる矢印のように、CPU101が第1プレシンクトの係数データを符号化中（P1VLC）に発生する水平同期タイミングに合わせて入力される画像データに対して、CPU101はリアルタイム（即時的）にウェーブレット変換処理（DWT）を行うことができない（符号化（VLC）中なので）。そこで、その画像データについては、CPU101が次の第2プレシンクトに対するウェーブレット変換処理（P2DWT）を開始するまでバッファする（保持しておく）必要がある。

【0141】

仮に、水平同期タイミング間に1プレシンクト分の符号化処理を全て終了させることができるのであれば、CPU101は、画像データのバッファリングを不要とし、リアルタイムにウェーブレット変換処理を行うことができる。しかしながら、このような方法の場合、CPU101にかかる負荷が極めて大きく、このような方法を実現するためには、CPU101の動作周波数を非常に高くする必要があり、コストが増大してしまう恐れがあるので現実的ではない。現実的なコストで調達可能なCPUの処理速度で画像データを処理するためには、上述したように入力画像データのバッファリングが必要になる。

10

【0142】

なお、図13は、画像データ入力とCPU101において実行される処理のタイミングの関係を模式的に示す図であり、図13に示される水平同期信号（hsync）の矢印は、説明にのための代表的な水平同期タイミングを概略的に示したものであり、全ての水平同期タイミングを正確に示すものではない。また、図13においても、図12の場合と同様に、縦方向上から下向きに時間の流れが示されているが、その縦方向の長さが時間の長さを正確に示しているわけではない。

20

【0143】

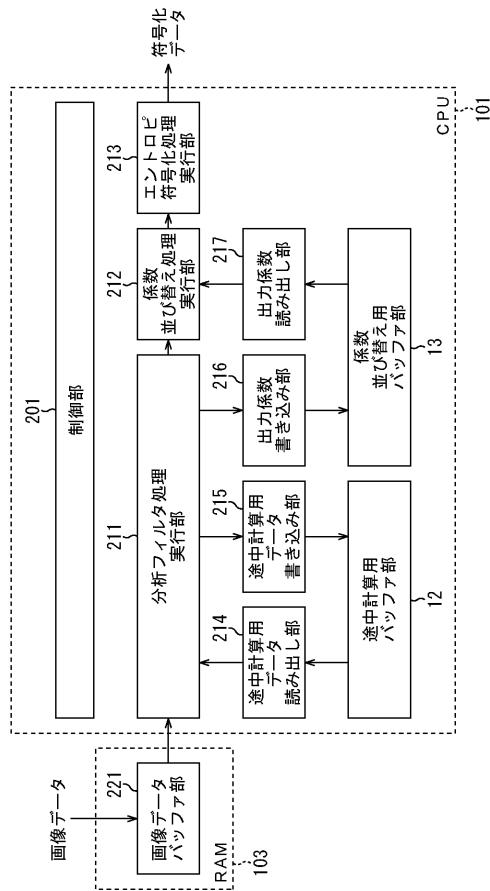

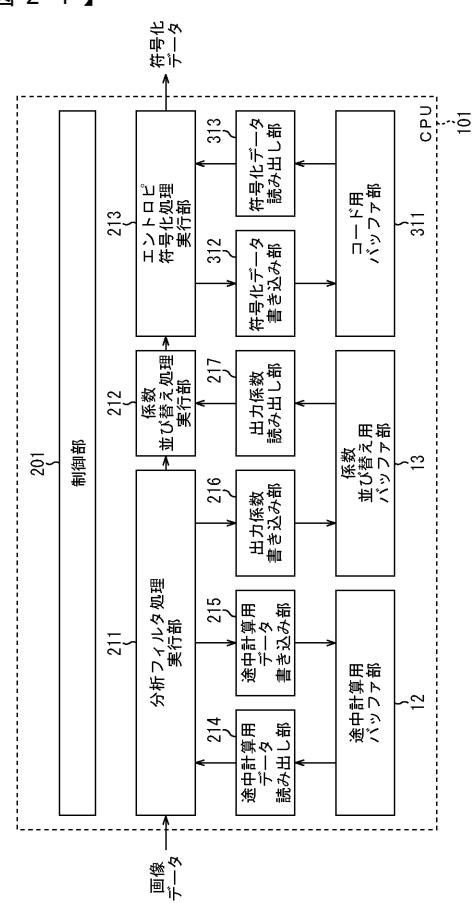

次に、このような流れで処理を実行する符号化部10の実現化について、より具体的に説明する。図14は、上述した流れで処理を実行する符号化部10を実現するソフトウェアプログラムを実行するCPU101が有する機能を示す機能ブロック図である。

【0144】

図14において、CPU101は、制御部201、分析フィルタ処理実行部211、係数並び替え処理実行部212、エントロピ符号化処理実行部213、途中計算用データ読み出し部214、途中計算用データ書き込み部215、出力係数書き込み部216、および出力係数読み出し部217を有する。

30

【0145】

制御部201は、分析フィルタ処理実行部211乃至出力係数読み出し部217の各部の動作を制御することにより、符号化部10の各処理の流れを制御する。また、制御部201は、後述する画像データバッファ部221のデータ入出力も制御する。

【0146】

分析フィルタ処理実行部211は、制御部201に制御されて、入力される画像データに対して分析フィルタ処理（リフティング演算）を行う、図1のウェーブレット変換部11の機能を実現する分析フィルタ処理を実行する。その分析フィルタ処理を実行する際、分析フィルタ処理実行部211は、次のリフティング演算に必要な途中計算用データ（画像データや係数データ）を、途中計算用データ読み出し部214を介して途中計算用バッファ部12より取得する。また、分析フィルタ処理実行部211は、リフティング演算により得られた途中計算用データを、途中計算用データ書き込み部215を介して途中計算用バッファ部12に供給し、保持させる。さらに、分析フィルタ処理実行部211は、リフティング演算により得られた、分析フィルタ処理をこれ以上行わない係数データ（最上位の分割レベルの低域成分および高域成分、並びに、最上位以外の分割レベルの高域成分）を、出力係数として、出力係数書き込み部216を介して係数並び替え用バッファ部13に供給し、保持させる。

40

【0147】

50

係数並び替え処理実行部 212 は、制御部 201 に制御されて、係数並び替え用バッファ部 13 に保持されている出力係数を読み出してエンタロピ符号化部 15 に供給する、図 1 の係数並び替え部 14 の機能を実現する係数並び替え処理を実行する。係数並び替え処理実行部 212 は、係数並び替え用バッファ部 13 に保持されている出力係数を、符号化順（合成フィルタ処理順）に、出力係数読み出し部 217 を介して取得し、それをエンタロピ符号化処理実行部 213 に供給することにより、係数の並び替えを行う。

#### 【0148】

エンタロピ符号化処理実行部 213 は、制御部 201 に制御されて、係数並び替え部 14 より供給される係数データをその供給順に符号化する図 1 のエンタロピ符号化部 15 の機能を実現するエンタロピ符号化処理を実行する。エンタロピ符号化処理実行部 213 は、係数並び替え処理実行部 212 より供給された係数データ（出力係数）を、その供給順に符号化し、得られた符号化データを、RAM 103、出力部 112、記憶部 113、通信部 114、またはリムーバブルメディア 121 等のCPU 101 の外部に出力する。

10

#### 【0149】

途中計算用データ読み出し部 214 および途中計算用データ書き込み部 215 は、制御部 201 に制御されて、キャッシュメモリ（図示せず）またはRAM 103 等に対して、途中計算用データの読み出しや書き込みを行うことにより、図 1 の途中計算用バッファ部 12 を、キャッシュメモリ（図示せず）またはRAM 103 等の記憶領域に形成させる。途中計算用データ読み出し部 214 は、途中計算用バッファ部 12 に保持されている途中計算用データ群の中から必要なものを読み出して分析フィルタ処理実行部 211 に供給する。途中計算用データ書き込み部 215 は、分析フィルタ処理実行部 211 より供給される途中計算用データを途中計算用バッファ部 12 に書き込む（保持させる）。

20

#### 【0150】

出力係数書き込み部 216 および出力係数読み出し部 217 は、制御部 201 に制御されて、キャッシュメモリ（図示せず）またはRAM 103 等に対して、出力係数の読み出しや書き込みを行うことにより、図 1 の係数並び替え用バッファ部 13 を、キャッシュメモリ（図示せず）またはRAM 103 等の記憶領域に形成させる。出力係数書き込み部 216 は、分析フィルタ処理実行部 211 より供給される出力係数を係数並び替え用バッファ部 13 に書き込む（保持させる）。出力係数読み出し部 217 は、係数並び替え用バッファ部 13 に保持されている出力係数を、係数並び替え処理実行部 212 に指定された順に読み出して係数並び替え処理実行部 212 に供給する。

30

#### 【0151】

画像データバッファ部 221 は、入力される画像データを一時的に保持するバッファ部であり、制御部 201 の制御により、例えばRAM 103 に形成される。画像データバッファ部 221 は、制御部 201 の制御されて、略定期的に 1 ラインずつ供給される画像データを一時的に保持し、所定のタイミングに合わせて、その保持している画像データを 1 ラインずつ分析フィルタ処理実行部 211 に供給する。

#### 【0152】

なお、図 14においては、途中計算用バッファ部 12 と係数並び替え用バッファ部 13 をCPU 101 内部のキャッシュメモリ（図示せず）に形成し、画像データバッファ部 221 をRAM 103 に形成しているが、これは一例であり、途中計算用バッファ部 12、係数並び替え用バッファ部 13、および画像データバッファ部 221 は、いずれも、任意の記憶領域に形成することができる。ただし、上述したようにキャッシュメモリは、高速にアクセス可能であるものの、容量がRAM 103 に比べて小さいので、不要な負荷や遅延時間の増大を招く恐れのあるバッファ溢れ等を生じさせないようにするために、高頻度で読み書きされるデータや、近い将来に使用予定のあるデータのみを記憶させるようにするのが望ましい。例えば、アクセス頻度の多い途中計算用バッファ部 12 は、キャッシュメモリに形成し、アクセス頻度の少ない画像データバッファ部 221 や係数並び替え用バッファ部 13 は、RAM 103 に形成するようにしてもよい。

40

#### 【0153】

50

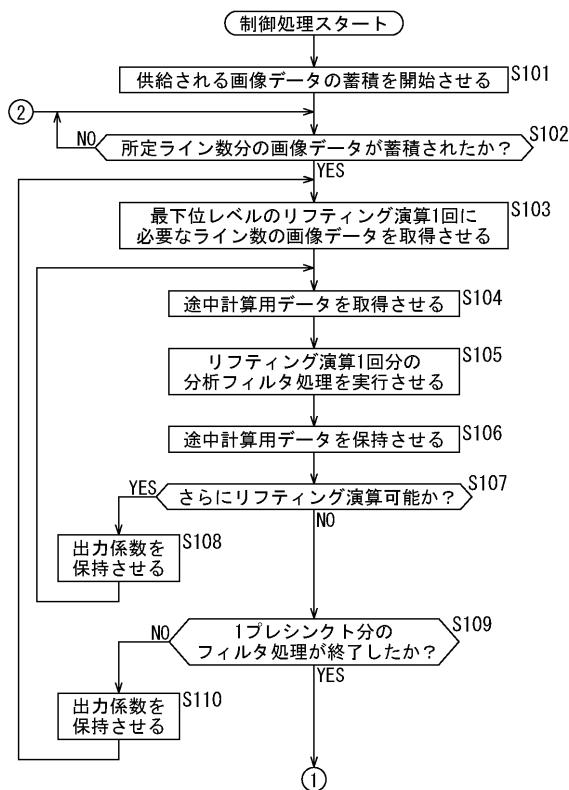

図14の制御部201は、図1の符号化部10を実現するために、各部を制御する制御処理を実行する。図15および図16のフローチャートを参照して、その制御処理の流れの例を説明する。

#### 【0154】

制御処理が開始されると、制御部201は、ステップS101において、画像データバッファ部221を、例えばRAM103に形成させ、供給される画像データの蓄積を開始させる。このように制御された画像データバッファ部221は、これ以降、制御処理が終了されるまで、1ラインずつ供給される画像データを一時的に保持する。

#### 【0155】

ステップS102において、制御部201は、画像データバッファ部221に、所定ライン数分の画像データが蓄積されたか否かを判定し、蓄積されたと判定するまで待機する。分析フィルタ処理実行部211においてリフティング演算が可能な程度、画像データが蓄積されたと判定した場合、制御部201は、処理をステップS103に進める。

#### 【0156】

ステップS103において、制御部201は、分析フィルタ処理実行部211を制御し、画像データバッファ部221より、最下位レベルのリフティング演算1回、つまり、分割レベル1の分析フィルタ処理のリフティング演算1回に必要なライン数（例えば、2ラインまたは3ライン）の画像データを取得させる。この制御により、分析フィルタ処理実行部211は、画像データバッファ部221より、最下位レベルのリフティング演算1回に必要なライン数の画像データを、ライン番号順に取得する。

#### 【0157】

ステップS104において、制御部201は、分析フィルタ処理実行部211を制御し、途中計算用バッファ部12より、これから行うリフティング演算に必要な途中計算用データを取得させる。この制御により、分析フィルタ処理実行部211は、途中計算用データ読み出し部214を制御して、これから行うリフティング演算に必要な途中計算用データを、途中計算用バッファ部12より読み出させ、供給させる（つまり、途中計算用データを取得する）。この制御により、途中計算用データ読み出し部214は、要求された途中計算用データを途中計算用バッファ部12より読み出し、分析フィルタ処理実行部211に供給する。

#### 【0158】

ステップS105において、制御部201は、分析フィルタ処理実行部211を制御し、リフティング演算1回分の分析フィルタ処理を実行させる。この制御により、分析フィルタ処理実行部211は、図11を参照して説明したように、実行可能な分析フィルタ処理のリフティング演算（曲線で囲まれた部分の演算）を1回分実行する。

#### 【0159】

リフティング演算が行われると、制御部201は、ステップS106において、分析フィルタ処理実行部211を制御し、リフティング演算に用いられた画像データや係数データ、およびリフティング演算により得られた係数データのうち、次回以降のリフティング演算に利用するデータを途中計算用データとして途中計算用バッファ部12に保持させる。この制御により、分析フィルタ処理実行部211は、途中計算用データ書き込み部215に途中計算用データを供給するとともに、その途中計算用データ書き込み部215を制御し、供給した途中計算用データを途中計算用バッファ部12に書き込ませる。この制御により、途中計算用データ書き込み部215は、分析フィルタ処理実行部211より供給された途中計算用データを、途中計算用バッファ部12に書き込み、保持させる。

#### 【0160】

ステップS107において、制御部201は、新たな画像データの入力無しに、さらにリフティング演算が可能であるか否かを判定する。可能であると判定した場合、制御部201は、処理をステップS108に進め、分析フィルタ処理実行部211を制御し、リフティング演算により得られた出力係数を、係数並び替え用バッファ部13に保持させる。この制御により、分析フィルタ処理実行部211は、出力係数書き込み部216に出力係

10

20

30

40

50

数を供給するとともに、その出力係数書き込み部 216 を制御し、供給した出力係数を係数並び替え用バッファ部 13 に書き込ませる。この制御により、出力係数書き込み部 216 は、分析フィルタ処理実行部 211 より供給された出力係数を、係数並び替え用バッファ部 13 に書き込み、保持させる。

【0161】

ステップ S108 の処理が終了すると、制御部 201 は、処理をステップ S104 に戻し、それ以降の処理を繰り返す。つまり、制御部 201 は、ステップ S104 乃至ステップ S108 の処理を繰り返すことにより、図 11 を参照して説明したように、入力された画像データに対応する、実行可能なリフティング演算を全て行わせる。

【0162】

そして、ステップ S107において、実行可能なリフティング演算が無くなつたと判定した場合、制御部 201 は、処理をステップ S109 に進める。

【0163】

ステップ S109において、制御部 201 は、1 プレシンクト分のフィルタ処理が終了したか否かを判定し、終了していないと判定した場合、処理をステップ S110 に進め、ステップ S108 の場合と同様に、分析フィルタ処理実行部 211 を制御し、リフティング演算により得られた出力係数を係数並び替え用バッファ部 13 に保持させる。ステップ S110 の処理が終了すると、制御部 201 は、処理をステップ S103 に戻し、それ以降の処理を繰り返す。つまり、制御部 201 は、ステップ S103 乃至ステップ S110 の処理を繰り返すことにより、図 11 を参照して説明したように、リフティング演算を 1 プレシンクト分実行させる。

【0164】

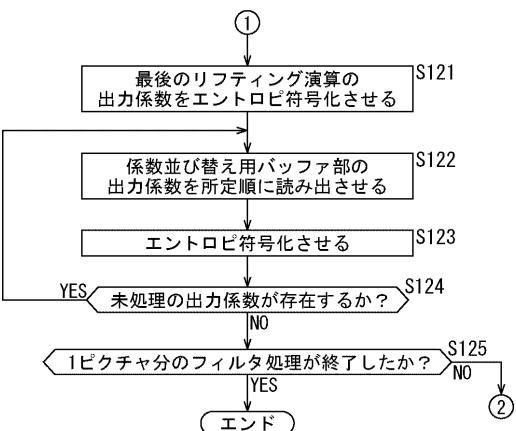

そして、ステップ S109において、1 プレシンクト分のフィルタ処理が終了したと判定した場合、制御部 201 は、処理を図 16 のステップ S121 に進める。図 16 のステップ S121において、制御部 201 は、エントロピ符号化処理実行部 213 を制御し、最後のリフティング演算の出力係数をエントロピ符号化させる。「最後のリフティング演算の出力係数」とは、上述した図 11 の説明において 5 番目に合成フィルタ処理される係数データおよび 6 番目に合成フィルタ処理される係数データに相当する。つまり、この最後のリフティング演算の出力係数は、係数並び替え用バッファ部 13 を介さずにエントロピ符号化させる。制御部 201 がこのように制御することにより、係数並び替え用バッファ部 13 として必要なメモリ量を低減させることができるとともに、負荷や遅延時間を低減させることができる。

【0165】

ステップ S121 の制御により、エントロピ符号化処理実行部 213 は、5 番目に合成フィルタ処理される係数データおよび 6 番目に合成フィルタ処理される係数データを順に符号化し、得られた符号化データを順次出力する。

【0166】

その符号化処理が終了すると、制御部 201 は、ステップ S122 において、係数並び替え処理実行部 212 を制御し、係数並び替え用バッファ部 13 の出力係数を所定順に読み出させる。この制御により、係数並び替え処理実行部 212 は、出力係数読み出し部 217 を制御し、係数並び替え用バッファ部 13 に保持されている係数データを、合成フィルタ処理を行う順に読み出させて供給させる。この制御により、出力係数読み出し部 217 は、係数並び替え用バッファ部 13 に保持されている係数データを、合成フィルタ処理を行う順に読み出し、読み出した係数データを係数並び替え処理実行部 212 に供給させる。係数並び替え処理実行部 212 は、供給された係数データを順次エントロピ符号化処理実行部 213 に供給する。

【0167】

ステップ S123 において、制御部 201 は、エントロピ符号化処理実行部 213 を制御し、係数並び替え用バッファ部 13 より読み出された係数データをエントロピ符号化させる。この制御により、エントロピ符号化処理実行部 213 は、読み出された係数データ

10

20

30

40

50

を符号化し、得られた符号化データを出力する。

【0168】

ステップS124において、制御部201は、係数並び替え用バッファ部13に、符号化処理していない出力係数が存在するか否かを判定し、存在すると判定した場合、処理をステップS122に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS122乃至ステップS124の処理を繰り返すことにより、係数並び替え用バッファ部13に保持されている全ての出力係数に対して符号化処理を実行させる。ステップS121の処理が開始された時点において、係数並び替え用バッファ部13には、1プレシンクト分の出力係数（最後のリフティング演算の出力係数は除く）が蓄積されている。制御部201は、この出力係数全てについて符号化処理を実行させる。

10

【0169】

ステップS124において、係数並び替え用バッファ部13に未処理の出力係数が存在しないと判定した場合、制御部201は、処理をステップS125に進める。

【0170】

ステップS125において、制御部201は、1ピクチャ分の分析フィルタ処理が終了したか否かを判定する。つまり、制御部201は、ピクチャ内の全てのプレシンクトについて分析フィルタ処理（およびエントロピ符号化処理）を行ったか否かを判定する。未処理のプレシンクトが存在すると判定した場合、制御部201は、処理を図15のステップS102に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS102乃至ステップS125の各処理を繰り返し実行することにより、全てのプレシンクトに20

20

【0171】

そして、ステップS125において、1ピクチャ分の分析フィルタ処理が終了したと判定した場合、制御部201は、制御処理を終了する。なお、この制御処理は、画像データのピクチャ毎に繰り返し実行される。

【0172】

以上のように制御処理を行うことにより、制御部201は、分析フィルタ処理を効率よく行い、画像データバッファ部221として必要なメモリ容量を低減させる。また、制御部201は、最後のリフティング演算の出力係数を係数並び替え用バッファ部13に蓄積させないようにすることにより、係数並び替え用バッファ部13として必要なメモリ量を30

30

【0173】

なお、図15および図16においては、制御処理の流れの例を説明したが、分析フィルタ処理実行部211乃至出力係数読み出し部217は、上述したように、この制御処理の各ステップに対応して制御部201の制御に対応する処理を実行する。従って、図15および図16のフローチャートに示される制御処理の各ステップは、上述したとおりに、分析フィルタ処理実行部211乃至出力係数読み出し部217のそれぞれが実行する処理も表しているものとし、各部が実行する処理の図示は省略する。

【0174】

次に、他の処理進行方法について説明する。

40

【0175】

図11を参照して説明したように、復号部20における第2プレシンクトに対する符号化処理は、符号化部10における第2プレシンクトに対するウェーブレット変換処理が終了するまで開始することができない。そのため、図12を参照して説明したように、CPU101は、ウェーブレット変換処理とエントロピ符号化処理をプレシンクト単位で交互に実行することになる。しかしながら、例えば、CPU101が各分析フィルタ処理をより高速に処理し、画像データ入力タイミング（水平同期タイミング）の間隔よりも早く終了させることができる場合、次の水平同期タイミング（分析フィルタ処理開始タイミング）まで待機時間が生じてしまい、CPU101の使用効率が低下してしまう。

【0176】

50

例えば、図12においても、ライン番号21（およびライン番号20）の画像データが入力されてから、分析フィルタ処理は3回行われるのに対し、ライン番号16（およびライン番号15）の画像データが入力されたときは、分析フィルタ処理は1回しか行われない。つまり、次のライン番号18（およびライン番号17）の画像データが入力されるまでに待機時間が生じる。このような待機時間が生じると、CPU101の使用効率が低下することになり、その効率が低い分だけ、処理実行時のCPU101にかかる負荷が増大することになる。従って、その分高性能なCPUを用いなければならず、製造コストや消費電力の増大にも繋がる。つまり、CPU101にかかる負荷を低減させるためには、CPU101の使用効率をより向上させる（より効率よくCPU101を動作させる）ことが求められる。

【0177】

10

そこで、このような待機時間の発生を抑制し、CPU101の使用効率を向上させるために、図17に示されるように、エントロピ符号化処理を行うプレシンクトを、ウェーブレット変換処理を行うプレシンクトよりも1つ遅延させる。換言すれば、符号化処理が、常に、リフティング演算により最後に生成された最低域の周波数成分よりも先に生成された周波数成分を符号化するようにする。さらに換言すれば、符号化処理の進行に対してウェーブレット変換処理の進行を、図11を参照して説明した例の場合よりも早めるようにし、符号化処理が最低域の周波数成分を符号化する前に、ウェーブレット変換処理がその最低域の周波数成分を生成しているようにし、符号化処理が常に次の周波数成分を符号化することができるようとする。

【0178】

20

図17の例においては、符号化部10における第3プレシンクトに対してウェーブレット変換処理を行いながら、復号部20における第2プレシンクトに対して符号化処理を行う様子を示している。もちろん、他のプレシンクトについても同様であるのでその説明は省略する。

【0179】

30

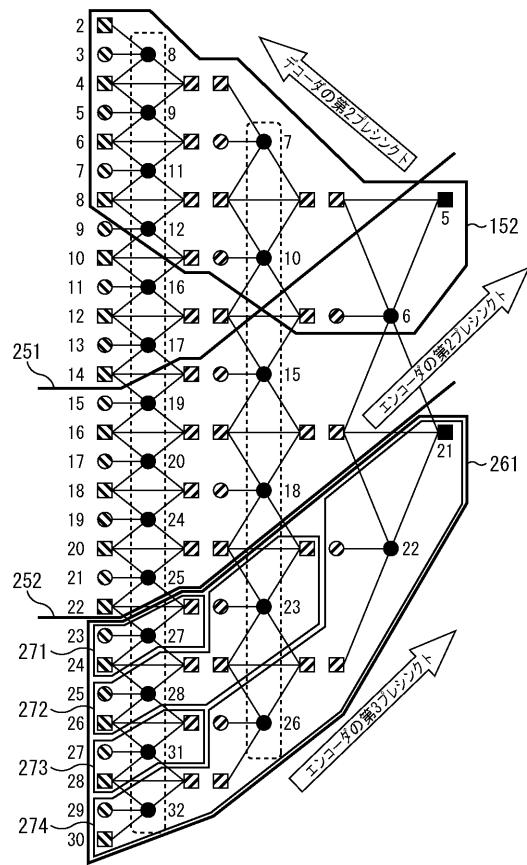

なお、図17は、図11に対応する図であるので、その詳細についての説明は省略する。図17において、曲線251は、符号化部10における第1プレシンクト（ライン番号0乃至ライン番号14）と第2プレシンクト（ライン番号15乃至ライン番号22）との境界を示し、曲線252は、符号化部10における第2プレシンクト（ライン番号15乃至ライン番号22）と第3プレシンクト（ライン番号23乃至ライン番号30）との境界を示している。

【0180】

図17に示されるように、符号化部10における第3プレシンクトに対するウェーブレット変換処理により生成される出力係数（曲線261において囲まれる部分の黒丸（○）や黒四角（△））と、復号部20における第2プレシンクトに対するエントロピ符号化において処理される出力係数（曲線152において囲まれる部分の黒丸（○）や黒四角（△））とは、互いに重複しない。従って、符号化部10における第3プレシンクトに対するウェーブレット変換処理と、復号部20における第2プレシンクトに対するエントロピ符号化を同時並行的に行うことができる。なお、CPU101は1つの演算処理部であるため、ここでいう「同時並行的」とは、2つの処理を実際に同時に並行して行うことではなく、2つの処理の開始から終了までの時間が互いに重複することを示す。より具体的に説明すると、CPU101を時分割して、ウェーブレット変換処理とエントロピ符号化処理のそれぞれを、より細かい処理単位で交互に実行させる。このようにすることにより、ウェーブレット変換処理の開始から終了までの時間と、エントロピ符号化処理の開始から終了までの時間が互いに重複するので、CPU101は、見かけ上、2つの処理を「同時並行的に」実行することができる。

【0181】

40

つまり、図17の例においては、CPU101は、符号化部10における第3プレシンクトに対するウェーブレット変換処理として、ライン番号23およびライン番号24の画像データが入力されると、曲線271により囲まれるリフティング演算を行い、ライン番号

50

25 およびライン番号26の画像データが入力されると、曲線272により囲まれるリフティング演算を行い、ライン番号27およびライン番号28の画像データが入力されると、曲線273により囲まれるリフティング演算を行い、ライン番号29およびライン番号30の画像データが入力されると、曲線274により囲まれるリフティング演算を行う。これらの各処理の間に発生するCPU101の待機時間中に、曲線152により囲まれる部分の、復号部20における第2プレシンクトに対するエントロピ符号化処理を、処理可能なライン数分だけCPU101に実行させるようとする。

#### 【0182】

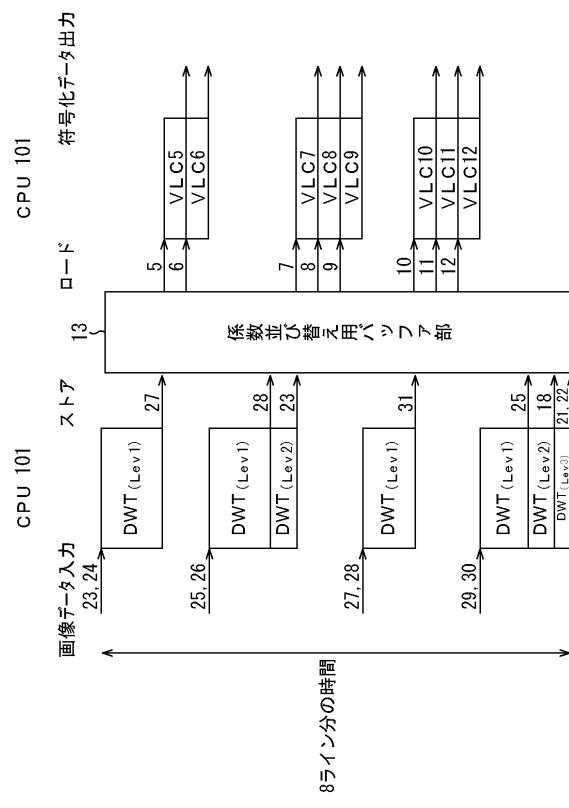

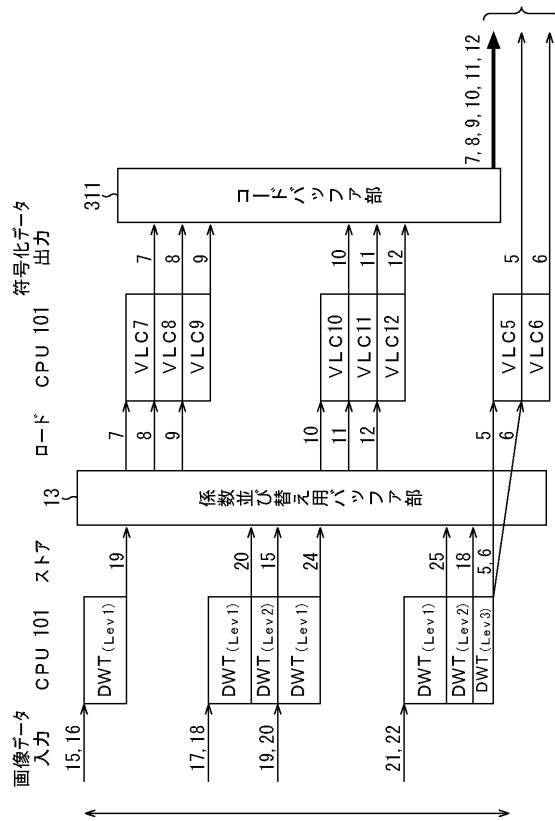

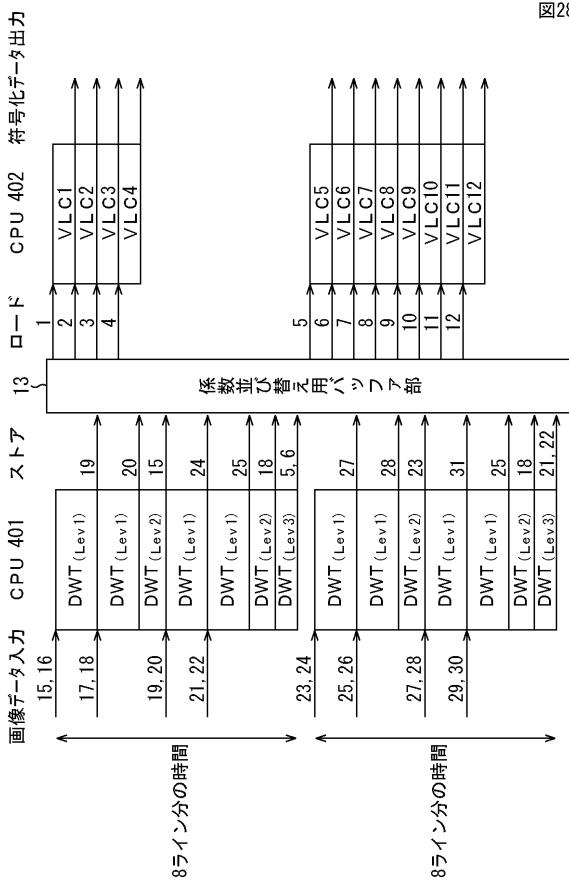

図18に、この場合の、CPU101において実行される処理の流れを模式的に示す。図18は、図12に対応する図であり、基本的には図12と同様の構成であるので、その詳細についての説明は省略する。 10

#### 【0183】

図18においても、CPU101は、図12の場合と同様に、符号化部10における第3プレシンクトについて、画像データが2ライン入力される毎に実行可能なリフティング演算（分析フィルタ処理）を行う（DWT（Lev1）乃至DWT（Lev3））。ただし、図18の場合、CPU101は、リフティング演算終了後、次の2ラインが入力されるまでの間に（次のリフティング演算実行開始タイミングまでの間に）、復号部20における第2プレシンクトに対するエントロピ符号化処理を、係数データのライン単位で実行する。

#### 【0184】

つまり、図18において、ライン番号24（および23）の画像データが入力されると、CPU101は、図17の曲線271に囲まれた部分のリフティング演算DWT（Lev1）を行い、27番目に合成フィルタ処理される係数データを生成し、それを係数並び替え用バッファ部13に保持させる。この後、CPU101は、次のリフティング演算実行開始タイミングまでの時間を利用して、5番目および6番目に合成フィルタ処理される係数データを順次エントロピ符号化し（VLC5およびVLC6）、それぞれの処理において得られた符号化データを順次出力する。 20

#### 【0185】

そして、ライン番号26（および25）の画像データが入力されると、CPU101は、図17の曲線272に囲まれた部分のリフティング演算DWT（Lev1）およびDWT（Lev2）を行い、それぞれの処理において28番目に合成フィルタ処理される係数データと23番目に合成フィルタ処理される係数データを生成し、それらを順次係数並び替え用バッファ部13に保持させる。その後、CPU101は、次のリフティング演算実行開始タイミングまでの時間を利用して、7番目乃至9番目に合成フィルタ処理される係数データを順次エントロピ符号化し（VLC7、VLC8、およびVLC9）、それぞれの処理において得られた符号化データを順次出力する。 30

#### 【0186】

次に、ライン番号28（および27）の画像データが入力されると、CPU101は、図17の曲線273に囲まれた部分のリフティング演算DWT（Lev1）を行い、31番目に合成フィルタ処理される係数データを生成し、それを係数並び替え用バッファ部13に保持させる。その後、CPU101は、次のリフティング演算実行開始タイミングまでの時間を利用して、10番目乃至12番目に合成フィルタ処理される係数データを順次エントロピ符号化し（VLC10、VLC11、およびVLC12）、それぞれの処理において得られた符号化データを順次出力する。 40

#### 【0187】

そして、ライン番号30（および29）の画像データが入力されると、CPU101は、図17の曲線274に囲まれた部分のリフティング演算DWT（Lev1）、DWT（Lev2）、およびDWT（Lev3）を行い、それぞれの処理において25番目に合成フィルタ処理される係数データ、18番目に合成フィルタ処理される係数データ、21番目に合成フィルタ処理される係数データ、および22番目に合成フィルタ処理される係数データを生成し、それらを順次係数並び替え用バッファ部13に保持させる。 50

## 【0188】

このように、エントロピ符号化処理の処理対象プレシンクトを、ウェーブレット変換処理の処理対象プレシンクトに対して1つ遅らせる、すなわち、符号化処理が、常に、リフティング演算により最後に生成された最低域の周波数成分より先に生成された周波数成分を符号化するようにすることにより、CPU101は、ウェーブレット変換処理の空き時間を利用して、エントロピ符号化処理を実行することができ、見かけ上、ウェーブレット変換処理とエントロピ符号化処理を同時並行的に実行することができる。このようにすることにより、CPU101の待機時間を低減させることができ、CPU101の使用効率を向上させることができる。

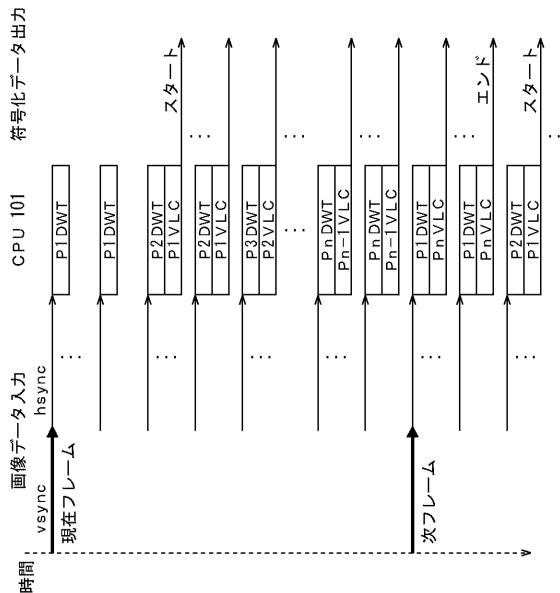

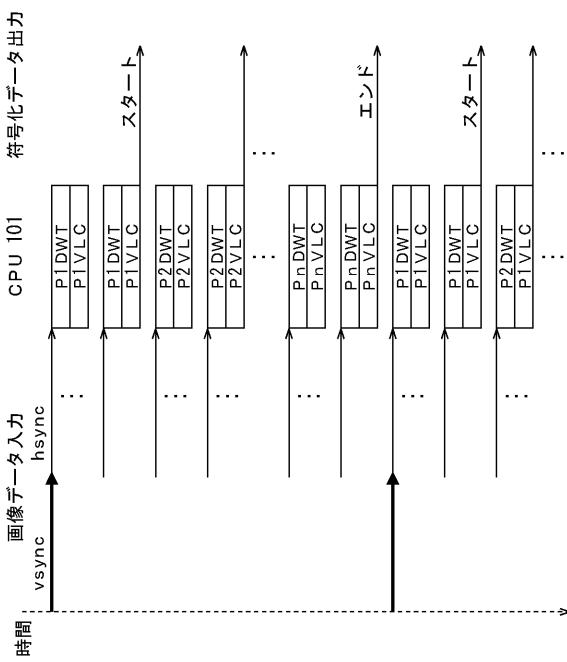

## 【0189】

また、これにより、CPU101は、容易に分析フィルタ処理をリアルタイム（即時的）に行うことができる。図19に示されるように、CPU101は、2ライン分の画像データの入力タイミング（hsync）に合わせて、1プレシンクトに対するウェーブレット変換処理を複数回に分けて実行する（P1DWT、P2DWT、P3DWT、・・・、PnDWT）。CPU101は、これらのウェーブレット変換処理の空き時間に、各出力係数に対する符号化処理を全て行う（P1VLC、P2VLC、・・・、Pn-1VLC、PnVLC）。このようにエントロピ符号化処理を、各出力係数に対する処理を処理単位として、ウェーブレット変換処理の空き時間に行うことにより、高性能なCPU101でなくても、容易にウェーブレット変換をリアルタイム（即時的）に行うことができる。

## 【0190】

従って、この場合、入力される画像データをバッファする必要が無く、画像データバッファ部221が不要になる。従って、図12乃至図16を参照して説明した方法の場合よりも、符号化部10が行う処理に必要なメモリ量を低減させることができるだけでなく、画像データをバッファする時間を省略することができるので、ウェーブレット変換処理およびエントロピ符号化処理の負荷や遅延時間を低減させることができる。

## 【0191】

なお、図12の場合と図18の場合を比較すると、図18の場合の方が、ライン番号24（および23）の画像データが入力された後に行われるリフティング演算DWT（Lev1）の分だけ、5番目に合成フィルタ処理される係数データを符号化して得られる符号化データの出力タイミングが遅く、また、5番目、6番目、および27番目に合成フィルタ処理される係数データの分だけ、係数並び替え用バッファ部13に蓄積されるデータ量が多い。しかしながら、このリフティング演算DWT（Lev1）は、分割レベル1のリフティング演算1回分の遅延時間であり、図18に示されるように2ライン分の画像データの入力タイミング（hsync）の間隔よりは短い。また、係数並び替え用バッファ部13に蓄積される5番目に合成フィルタ処理される係数データは分割レベル3の低域成分1ライン分であり、6番目に合成フィルタ処理される係数データは分割レベル3の高域成分1ライン分であり、27番目に合成フィルタ処理される係数データは分割レベル1の高域成分1ライン分であるので、そのデータ量は画像データ1ライン分より少ない（図4参照）。

## 【0192】

図12の方法において、エントロピ符号化によりウェーブレット変換処理をリアルタイムに行うことができない場合、1プレシンクト分のエントロピ符号化処理の処理時間は、2ライン分の画像データの入力タイミング（hsync）の間隔より長い。また、そのときの画像データバッファ部221に蓄積される画像データのデータ量は、画像データ2ライン分以上である。

## 【0193】

従って、この入力画像データのバッファ分まで含めて比較すると、図18の場合の方が、図12の場合よりも、必要とするメモリ容量が少なく、かつ、遅延時間が短い。また、図12の場合よりもCPU101の使用効率が高いため、より小さな負荷で、所定の速度で入力される画像データをリアルタイムに処理することができる。

## 【0194】

10

20

30

40

50

なお、図18の例の場合、5番目と6番目に合成フィルタ処理される係数データを係数並び替え用バッファ部13に蓄積するように説明したが、図12の場合と同様に、これらの係数データを係数並び替え用バッファ部13に蓄積させずにエントロピ符号化処理するようにしてもよい。つまり、この場合、CPU101は、符号化部10における第2プレシンクトの最後のリフティング演算終了後、第3プレシンクトに対するウェーブレット変換を開始する前に、復号部20における第2プレシンクトに対するエントロピ符号化処理を開始することができる。このようにすることにより、CPU101は、5番目に合成フィルタ処理される係数データを符号化して得られる符号化データの出力タイミングをさらに早くすることができ、また、係数並び替え用バッファ部13として必要なメモリ容量をさらに低減させることができる。

10

#### 【0195】

また、図18の例の場合、図19に示されるように符号化データの出力タイミングが分散される。従って、後段の処理の負荷を均一化させることができるので、再生ビデオ信号のように略一定の速度で入力される画像データ（1ラインずつ所定の間隔で入力される画像データ）に対してリアルタイムに処理を行うことが容易になる。例えば、符号化部10の後段の処理として符号化データをパケット化する場合、図18の例のように符号化データの生成レートが略一定であると、そのパケット化処理の負荷の変化量が低減されるので、パケット処理が容易になる。これに対して、図12の例の場合、符号化データの出力タイミングは、エントロピ符号化処理が行われている期間に集中し、ムラが生じる。従って、パケット化処理の負荷の変化量が増大し、負荷がピークのときにオーバーフローしないようにパケット化処理を高速に実行するようにしたり、符号化データをバッファしたりする必要が生じ、それによりコスト、負荷、および遅延時間の増大を招く恐れがある。

20

#### 【0196】

なお、図18の例は一例であり、エントロピ符号化処理は、リフティング処理の空き時間であれば任意に割り当てることができる。例えば、図18においては、ライン番号24（および23）の画像データが入力された後に実行されるリフティング演算DWT（Lev1）の後の空き時間に、5番目と6番目に合成フィルタ処理される係数データの符号化（VLC5およびVLC6）を割り当てるように説明したが、さらに7番目以降に合成フィルタ処理される係数データの符号化（VLC7乃至VLC12）を割り当てるようにしてもよい。また、ライン番号30（および29）の画像データが入力された後に実行されるリフティング演算DWT（Lev1）、DWT（Lev2）、およびDWT（Lev3）の後の空き時間に符号化を割り当てるようにしてもよい。

30

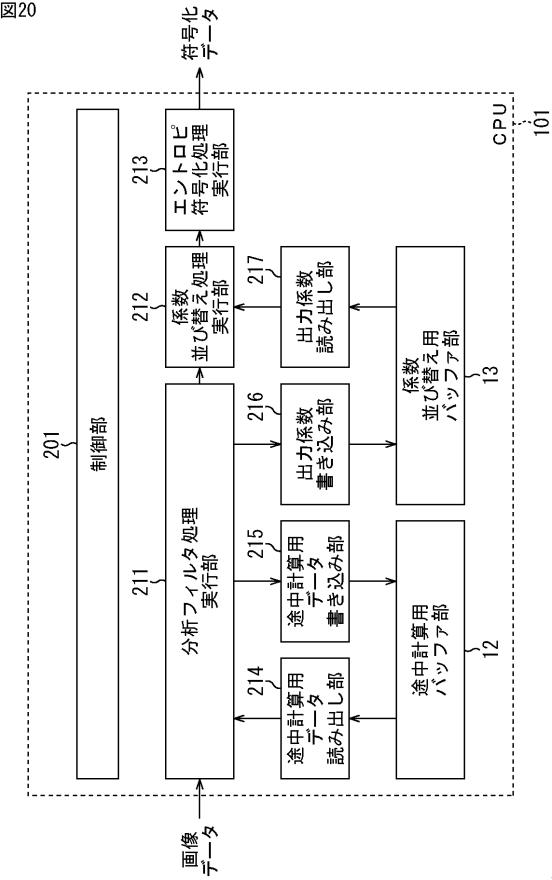

#### 【0197】

次に、このような流れで処理を実行する符号化部10の実現化について、より具体的に説明する。図20は、上述した流れで処理を実行する符号化部10を実現するソフトウェアプログラムを実行するCPU101が有する機能を示す機能ブロック図である。

#### 【0198】

図20は、図14に対応する図であり、図14に示されるブロックと対応するブロックには同一の番号を付してある。図20の場合、図14の場合より画像データバッファ部221が省略されるのみであり、CPU101が有する機能ブロックは基本的に図14の場合と同様であり、制御部201、分析フィルタ処理実行部211、係数並び替え処理実行部212、エントロピ符号化処理実行部213、途中計算用データ読み出し部214、途中計算用データ書き込み部215、出力係数書き込み部216、および出力係数読み出し部217を有する。ただし、図20の場合、制御部201は、画像データバッファ部221に関する制御は行わない。

40

#### 【0199】

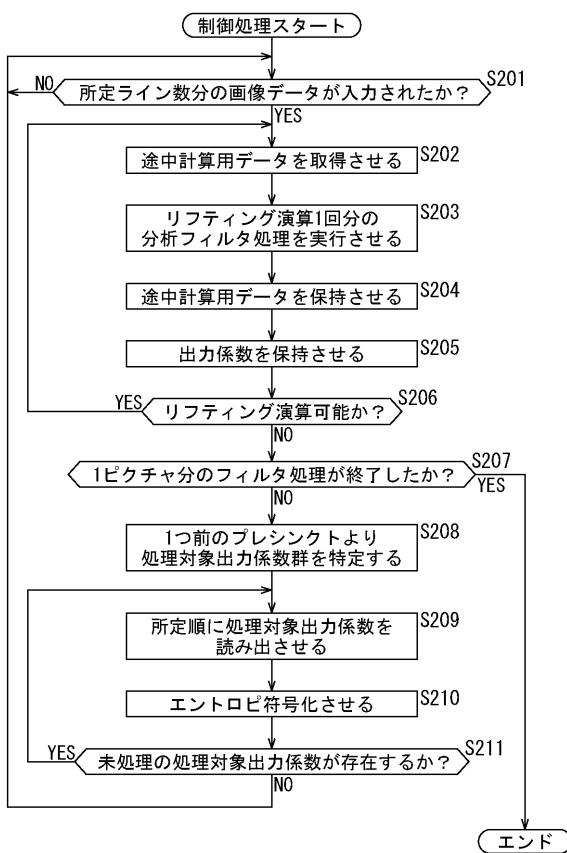

図20の制御部201は、図1の符号化部10を実現するために、各部を制御する制御処理を実行する。図21のフローチャートを参照して、その制御処理の流れの例を説明する。なお、この制御処理は、画像データのピクチャ毎に繰り返し実行される。

#### 【0200】

50

制御処理が開始されると、制御部201は、ステップS201において、所定ライン数（例えば2ラインまたは3ライン）分の画像データが入力されたか否かを判定し、入力されたと判定するまで待機する。そして、入力されたと判定した場合、制御部201は、処理をステップS202に進める。

【0201】

ステップS202において、制御部201は、分析フィルタ処理実行部211を制御し、途中計算用バッファ部12より、これから行うリフティング演算に必要な途中計算用データを取得させる。この制御により、分析フィルタ処理実行部211は、途中計算用データ読み出し部214を制御して、これから行うリフティング演算に必要な途中計算用データを、途中計算用バッファ部12より読み出させ、供給させる（つまり、途中計算用データを取得する）。この制御により、途中計算用データ読み出し部214は、要求された途中計算用データを途中計算用バッファ部12より読み出し、分析フィルタ処理実行部211に供給する。10

【0202】

ステップS203において、制御部201は、分析フィルタ処理実行部211を制御し、リフティング演算1回分の分析フィルタ処理を実行させる。この制御により、分析フィルタ処理実行部211は、図18を参照して説明したように、実行可能な分析フィルタ処理のリフティング演算を1回分実行する。

【0203】

リフティング演算が行われると、制御部201は、ステップS204において、分析フィルタ処理実行部211を制御し、リフティング演算に用いられた画像データや係数データ、およびリフティング演算により得られた係数データのうち、次回以降のリフティング演算に利用するデータを途中計算用データとして途中計算用バッファ部12に保持させる。この制御により、分析フィルタ処理実行部211は、途中計算用データ書き込み部215に途中計算用データを供給するとともに、その途中計算用データ書き込み部215を制御し、供給した途中計算用データを途中計算用バッファ部12に書き込ませる。この制御により、途中計算用データ書き込み部215は、分析フィルタ処理実行部211より供給された途中計算用データを、途中計算用バッファ部12に書き込み、保持させる。20

【0204】

ステップS205において、制御部201は、分析フィルタ処理実行部211を制御し、リフティング演算により得られた出力係数を、係数並び替え用バッファ部13に保持させる。この制御により、分析フィルタ処理実行部211は、出力係数書き込み部216に出力係数を供給するとともに、その出力係数書き込み部216を制御し、供給した出力係数を係数並び替え用バッファ部13に書き込ませる。この制御により、出力係数書き込み部216は、分析フィルタ処理実行部211より供給された出力係数を、係数並び替え用バッファ部13に書き込み、保持させる。30

【0205】

ステップS206において、制御部201は、新たな画像データの入力無しに、さらにリフティング演算が可能であるか否かを判定し、可能であると判定した場合、処理をステップS202に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS202乃至ステップS206の処理を繰り返すことにより、図18を参照して説明したように、入力された画像データに対応する、実行可能なリフティング演算を全て行わせる。40

【0206】

そして、ステップS206において、実行可能なリフティング演算が無くなったらと判定した場合、制御部201は、処理をステップS207に進める。

【0207】

ステップS207において、制御部201は、1ピクチャ分のフィルタ処理が終了したか否かを判定し、終了していないと判定した場合、処理をステップS208に進め、係数並び替え用バッファ部13に保持されている、1つ前のプレシンクトより処理対象出力係数群を特定する。つまり、制御部201は、次のリフティング演算開始タイミングまでの50

空き時間に符号化する出力係数を、リフティング演算により最後に生成された最低域の周波数成分より先に生成された周波数成分の中から特定する。なお、分析フィルタ処理されたのが第1プレシンクトである場合、制御部201は、1つ前のピクチャの最後のプレシンクトを1つ前のプレシンクトとし、処理対象出力係数群を特定する。また、分析フィルタ処理されたのが先頭のピクチャの第1プレシンクトである場合、制御部201は、ステップS208乃至ステップS211の処理を省略し、処理をステップS201に戻し、それ以降の処理を実行させる。

#### 【0208】

ステップS209において、制御部201は、係数並び替え処理実行部212を制御し、処理対象出力係数として指定された係数データを所定順に読み出させる。この制御により、係数並び替え処理実行部212は、出力係数読み出し部217を制御し、係数並び替え用バッファ部13に保持されている係数データ（処理対象出力係数）を、合成フィルタ処理を行う順に読み出させて供給させる。この制御により、出力係数読み出し部217は、係数並び替え用バッファ部13に保持されている係数データを、合成フィルタ処理を行う順に読み出し、読み出した係数データを係数並び替え処理実行部212に供給させる。係数並び替え処理実行部212は、供給された係数データを順次エントロピ符号化処理実行部213に供給する。

#### 【0209】

ステップS210において、制御部201は、エントロピ符号化処理実行部213を制御し、係数並び替え用バッファ部13より読み出された係数データをエントロピ符号化させる。この制御により、エントロピ符号化処理実行部213は、読み出された係数データを符号化し、得られた符号化データを出力する。

#### 【0210】

ステップS211において、制御部201は、係数並び替え用バッファ部13に、符号化処理していない処理対象出力係数が存在するか否かを判定し、存在すると判定した場合、処理をステップS209に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS209乃至ステップS211の処理を繰り返すことにより、係数並び替え用バッファ部13に保持されている全ての処理対象出力係数に対して符号化処理を実行させる。

#### 【0211】

ステップS211において、係数並び替え用バッファ部13に未処理の処理対象出力係数が存在しないと判定した場合、制御部201は、処理をステップS201に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS201乃至ステップS211の処理を繰り返すことにより、ピクチャ内の全プレシンクトについて、ウェーブレット変換処理を実行させ、さらにその空き時間にエントロピ符号化処理を実行することにより、ウェーブレット変換処理とエントロピ符号化処理を見かけ上、同時並行的に実行させる。

#### 【0212】

ステップS207において、1ピクチャ分のフィルタ処理が終了したと判定した場合、制御部201は、制御処理を終了する。なお、この制御処理が、画像データの最後のピクチャに対するものである場合、制御部201は、係数並び替え用バッファ部13に保持されている残りの出力係数全てを処理対象出力係数群として特定し、ステップS209およびステップS211と同様の処理を行い、全出力係数を符号化し、その符号化データを出力してから制御処理を終了する。

#### 【0213】

以上のように制御処理を行うことにより、制御部201は、容易に、ウェーブレット変換処理とエントロピ符号化処理を同時並列的に実行し、所定の速度で入力される画像データよりリアルタイムに符号化データを生成して出力することができる。また、これにより、入力画像データの保持が不要になる。このように、ウェーブレット変換処理および符号化処理の負荷を低減させることができる。

10

20

30

40

50

## 【0214】

なお、図21においては、制御処理の流れの例を説明したが、分析フィルタ処理実行部211乃至出力係数読み出し部217は、上述したように、この制御処理の各ステップに対応して制御部201の制御に対応する処理を実行する。従って、図21のフローチャートに示される制御処理の各ステップは、上述したとおりに、分析フィルタ処理実行部211乃至出力係数読み出し部217のそれぞれが実行する処理も表しているものとし、各部が実行する処理の図示は省略する。

## 【0215】

次に、他の処理進行方法について説明する。

## 【0216】

図11を参照して説明したように、復号部20における第2プレシンクトに対する符号化処理は、符号化部10における第2プレシンクトに対するウェーブレット変換処理が終了するまで開始することができない。そこで、図22に示されるように、符号化データを保持するコードバッファ部311を設け、符号化部10における第2プレシンクトに対するウェーブレット変換処理の最後のリフティング演算よりも前に、それ以前に生成される係数データを符号化するようにしてもよい。つまり、この場合、CPU101は、合成フィルタ処理の処理順と異なる順序でエントロピ符号化処理を先に行い、得られた符号化データを保持することにより、符号化データを合成フィルタ処理の処理順に出力させる。

10

## 【0217】

図22に、この場合の、CPU101において実行される処理の流れを模式的に示す。図22は、図12に対応する図であり、基本的には図12と同様の構成であるので、その詳細についての説明は省略する。

20

## 【0218】

図22においても、CPU101は、図12の場合と同様に、符号化部10における第2プレシンクトについて、画像データが2ライン入力される毎に実行可能なリフティング演算(分析フィルタ処理)を行う(DWT(Lev1)乃至DWT(Lev3))。ただし、図22の場合、CPU101は、図18の場合と同様に、リフティング演算終了後、次の2ラインが入力されるまでの間に(次のリフティング演算実行開始タイミングまでの間に)、復号部20における第2プレシンクトに対するエントロピ符号化処理を、係数データのライン単位で実行する。

30

## 【0219】

ただし、図22の場合、このエントロピ符号化処理を、ウェーブレット変換の処理対象プレシンクトと同じプレシンクトに対して行う。すなわち、この場合のウェーブレット変換とエントロピ符号化処理の関係は、図17ではなく図11に示される例のようになる。つまり、上述したように、第2プレシンクトに対する分析フィルタ処理が開始された時点では、5番目および6番目に合成フィルタ処理される係数データは生成されていない。図22の場合、CPU101は、これらの係数データの符号化よりも先に、既に生成され、係数並び替え用バッファ部13に保持されている、復号部20における第2プレシンクトの他の係数データ(すなわち、5番目および6番目に合成フィルタ処理される係数データに対応し、それよりも高域成分である、7番目乃至12番目に合成フィルタ処理される係数データ)の符号化を行う。

40

## 【0220】

図22の場合、これまでの例と異なり、符号化データを保持するコードバッファ部311が設けられている。処理対象プレシンクトの最後のリフティング演算により生成される係数データよりも先に符号化された、処理対象プレシンクトの他の係数データは、このコードバッファ部311に一旦保持される。そして、処理対象プレシンクトの最後のリフティング演算により生成される係数データが符号化されて出力されると、コードバッファ部311に保持されている符号化データが、合成フィルタ処理が行われる順に読み出されて出力される。

## 【0221】

50

より具体的に説明すると、図22の例の場合、ライン番号16（および15）の画像データが入力されると、CPU101は、図11の曲線161に囲まれた部分のリフティング演算DWT（Lev1）を行い、19番目に合成フィルタ処理される係数データを生成し、それを係数並び替え用バッファ部13に保持させる。この後、CPU101は、次のリフティング演算実行開始タイミングまでの時間を利用して、7番目乃至9番目に合成フィルタ処理される係数データを順次エントロピ符号化し（VLC7、VLC8、およびVLC9）、それぞれの処理において得られた符号化データをコードバッファ部311に保持させる。

#### 【0222】

そして、ライン番号18（および17）の画像データが入力されると、CPU101は、図11の曲線162に囲まれた部分のリフティング演算DWT（Lev1）およびDWT（Lev2）を行い、20番目および15番目に合成フィルタ処理される係数データを生成し、それらを順次係数並び替え用バッファ部13に保持させる。

10

#### 【0223】

さらに、ライン番号20（および19）の画像データが入力されると、CPU101は、図11の曲線163に囲まれた部分のリフティング演算DWT（Lev1）を行い、24番目に合成フィルタ処理される係数データを生成し、それを係数並び替え用バッファ部13に保持させる。この後、CPU101は、次のリフティング演算実行開始タイミングまでの時間を利用して、10番目乃至12番目に合成フィルタ処理される係数データを順次エントロピ符号化し（VLC10、VLC11、およびVLC12）、それぞれの処理において得られた符号化データをコードバッファ部311に保持させる。

20

#### 【0224】

また、ライン番号22（および21）の画像データが入力されると、CPU101は、図11の曲線164に囲まれた部分のリフティング演算DWT（Lev1）、DWT（Lev2）、およびDWT（Lev3）を行い、25番目、18番目、5番目、および6番目に合成フィルタ処理される係数データを生成し、25番目および18番目に合成フィルタ処理される係数データを順次係数並び替え用バッファ部13に保持させる。この後、CPU101は、次のリフティング演算実行開始タイミングまでの時間を利用して、5番目および6番目に合成フィルタ処理される係数データを順次エントロピ符号化し（VLC5およびVLC6）、それぞれの処理において得られた符号化データを出力する。そして、CPU101は、コードバッファ部311に保持させた7番目乃至12番目に合成フィルタ処理される係数データの符号化データを合成フィルタ処理順に読み出し、5番目および6番目に合成フィルタ処理される係数データの符号化データに続けて出力する。

30

#### 【0225】

つまり、図23に示されるように、所定の速度で入力される画像データに対して、ウェーブレット変換処理とエントロピ符号化処理を、プレシンクトをずらすことなく、リアルタイムに実行することができる。このようにすることにより、CPU101は、生成した符号化データを、次のプレシンクトに対する分析フィルタ処理が開始される前に出力することができ、各符号化データの出力タイミングを、図12の場合と同じままCPU101の使用効率を向上させることができる。さらに、図22の例の場合、画像データバッファ部221を省略することができる。

40

#### 【0226】

ただし、図22の例の場合、コードバッファ部311が必要になるので、その分、必要なメモリ容量が図18の例の場合よりも増大する。ただし、コードバッファ部311においては、符号化データを蓄積するため、画像データを蓄積する場合よりもそのデータ量が低減される。すなわち、図12の場合よりも、データのバッファに必要なメモリ容量を低減させることができる。

#### 【0227】

図18の場合と比較すると、最初のピクチャの先頭のプレシンクトよりエントロピ符号化処理を行うことができるので、CPU101の使用効率は図22の場合の方が高い。ただし、コードバッファ部311の分、必要なメモリ容量が増大する。また、符号化データの

50

出力タイミングにムラがあるので、符号化部 10 の後段の処理が図 22 の場合の方が困難になる（負荷が大きくなる恐れがある）。

【0228】

次に、このような流れで処理を実行する符号化部 10 の実現化について、より具体的に説明する。図 24 は、上述した流れで処理を実行する符号化部 10 を実現するソフトウェアプログラムを実行するCPU 101 が有する機能を示す機能ブロック図である。

【0229】

図 24 も、図 14 に対応する図であり、図 14 に示されるブロックと対応するブロックには同一の番号を付してある。図 24 の場合、CPU 101 は、図 20 の場合と基本的に同様の機能ブロックを有するが、さらに、コードバッファ部 311、符号化データ書き込み部 312、および符号化データ読み出し部 313 を有する。

【0230】

符号化データ書き込み部 312 および符号化データ読み出し部 313 は、制御部 201 に制御されて、キャッシュメモリ（図示せず）またはRAM 103 等に対して、エントロピ符号化処理において生成された符号化データの読み出しや書き込みを行うことにより、図 22 のコードバッファ部 311 を、キャッシュメモリ（図示せず）またはRAM 103 等の記憶領域に形成させる。符号化データ書き込み部 312 は、エントロピ符号化処理実行部 213 より供給される符号化データをコードバッファ部 311 に書き込む（保持させる）。および符号化データ読み出し部 313 は、コードバッファ部 311 に保持されている符号化データを、合成フィルタ処理の順に読み出してエントロピ符号化処理実行部 213 に供給する。

【0231】

図 24 の制御部 201 は、図 1 の符号化部 10 を実現するために、各部を制御する制御処理を実行する。図 25 および図 26 のフローチャートを参照して、その制御処理の流れの例を説明する。なお、この制御処理は、画像データのピクチャ毎に繰り返し実行される。

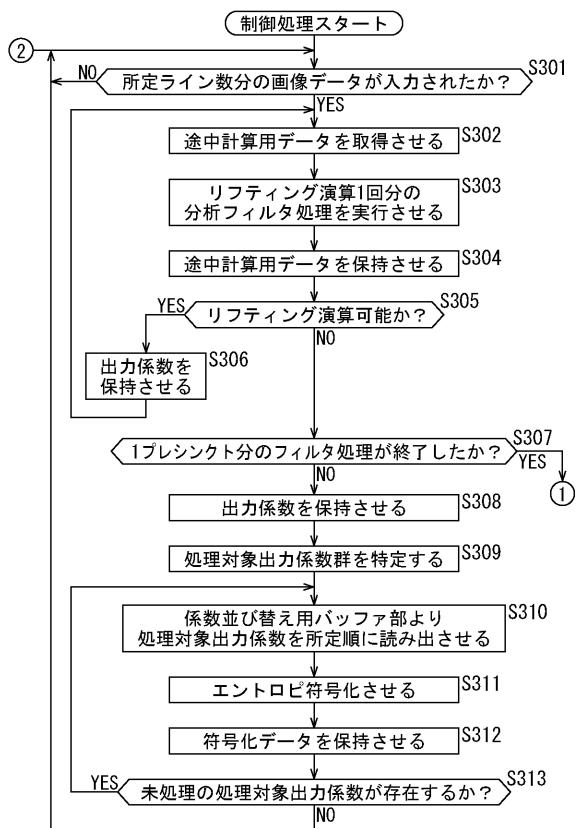

【0232】

制御処理が開始されると、制御部 201 は、ステップ S301において、所定ライン数（例えば 2 ラインまたは 3 ライン）分の画像データが入力されたか否かを判定し、入力されたと判定するまで待機する。そして、入力されたと判定した場合、制御部 201 は、処理をステップ S302 に進める。

【0233】

ステップ S302 において、制御部 201 は、分析フィルタ処理実行部 211 を制御し、途中計算用バッファ部 12 より、これから行うリフティング演算に必要な途中計算用データを取得させる。この制御により、分析フィルタ処理実行部 211 は、途中計算用データ読み出し部 214 を制御して、これから行うリフティング演算に必要な途中計算用データを、途中計算用バッファ部 12 より読み出させ、供給させる（つまり、途中計算用データを取得する）。この制御により、途中計算用データ読み出し部 214 は、要求された途中計算用データを途中計算用バッファ部 12 より読み出し、分析フィルタ処理実行部 211 に供給する。

【0234】

ステップ S303 において、制御部 201 は、分析フィルタ処理実行部 211 を制御し、リフティング演算 1 回分の分析フィルタ処理を実行させる。この制御により、分析フィルタ処理実行部 211 は、図 22 を参照して説明したように、実行可能な分析フィルタ処理のリフティング演算を 1 回分実行する。

【0235】

リフティング演算が行われると、制御部 201 は、ステップ S304 において、分析フィルタ処理実行部 211 を制御し、リフティング演算に用いられた画像データや係数データ、およびリフティング演算により得られた係数データのうち、次回以降のリフティング演算に利用するデータを途中計算用データとして途中計算用バッファ部 12 に保持させる

10

20

30

40

50

。この制御により、分析フィルタ処理実行部211は、途中計算用データ書き込み部215に途中計算用データを供給するとともに、その途中計算用データ書き込み部215を制御し、供給した途中計算用データを途中計算用バッファ部12に書き込ませる。この制御により、途中計算用データ書き込み部215は、分析フィルタ処理実行部211より供給された途中計算用データを、途中計算用バッファ部12に書き込み、保持させる。

【0236】

ステップS305において、制御部201は、新たな画像データの入力無しに、さらにリフティング演算が可能であるか否かを判定し、可能であると判定した場合、処理をステップS306に進める。

【0237】

ステップS306において、制御部201は、分析フィルタ処理実行部211を制御し、リフティング演算により得られた出力係数を、係数並び替え用バッファ部13に保持させる。この制御により、分析フィルタ処理実行部211は、出力係数書き込み部216に出力係数を供給するとともに、その出力係数書き込み部216を制御し、供給した出力係数を係数並び替え用バッファ部13に書き込ませる。この制御により、出力係数書き込み部216は、分析フィルタ処理実行部211より供給された出力係数を、係数並び替え用バッファ部13に書き込み、保持させる。

【0238】

ステップS306の処理が終了すると、制御部201は、処理をステップS302に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS302乃至ステップS306の処理を繰り返すことにより、図22を参照して説明したように、入力された画像データに対応する、実行可能リフティング演算を全て行わせる。

【0239】

そして、ステップS305において、実行可能リフティング演算が無くなつたと判定した場合、制御部201は、処理をステップS307に進める。ステップS307において、制御部201は、1フレシンクト分のフィルタ処理が終了したか否かを判定し、終了していないと判定した場合、処理をステップS308に進める。

【0240】

ステップS308において、制御部201は、分析フィルタ処理実行部211を制御し、リフティング演算により得られた出力係数を、係数並び替え用バッファ部13に保持させる。この制御により、分析フィルタ処理実行部211は、出力係数書き込み部216に出力係数を供給するとともに、その出力係数書き込み部216を制御し、供給した出力係数を係数並び替え用バッファ部13に書き込ませる。この制御により、出力係数書き込み部216は、分析フィルタ処理実行部211より供給された出力係数を、係数並び替え用バッファ部13に書き込み、保持させる。

【0241】

ステップS309において、制御部201は、係数並び替え用バッファ部13に保持されている現在の処理対象フレシンクトの係数データより、処理対象出力係数群を特定する。つまり、制御部201は、次のリフティング演算開始タイミングまでの空き時間に符号化する出力係数を特定する。

【0242】

ステップS310において、制御部201は、係数並び替え処理実行部212を制御し、処理対象出力係数として指定された係数データを所定順に読み出させる。この制御により、係数並び替え処理実行部212は、出力係数読み出し部217を制御し、係数並び替え用バッファ部13に保持されている係数データ（処理対象出力係数）を、合成フィルタ処理を行う順に読み出させて供給させる。この制御により、出力係数読み出し部217は、係数並び替え用バッファ部13に保持されている係数データを、合成フィルタ処理を行う順に読み出し、読み出した係数データを係数並び替え処理実行部212に供給させる。係数並び替え処理実行部212は、供給された係数データを順次エントロピ符号化処理実行部213に供給する。

10

20

30

40

50

**【0243】**

ステップS311において、制御部201は、エントロピ符号化処理実行部213を制御し、係数並び替え用バッファ部13より読み出された係数データをエントロピ符号化させる。この制御により、エントロピ符号化処理実行部213は、読み出された係数データを符号化する。

**【0244】**

ステップS312において、制御部201は、エントロピ符号化処理実行部213を制御し、ステップS311において生成された符号化データをコードバッファ部311に保持させる。この制御により、エントロピ符号化処理実行部213は、符号化データ書き込み部312に符号化データを供給するとともに、符号化データ書き込み部312を制御し、供給した符号化データをコードバッファ部311に書き込ませる。この制御により、符号化データ書き込み部312は、エントロピ符号化処理実行部213より供給された出力係数を、コードバッファ部311に書き込み、保持させる。

10

**【0245】**

ステップS313において、制御部201は、係数並び替え用バッファ部13に、符号化処理していない処理対象出力係数が存在するか否かを判定し、存在すると判定した場合、処理をステップS310に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS310乃至ステップS313の処理を繰り返すことにより、係数並び替え用バッファ部13に保持されている全ての処理対象出力係数に対して符号化処理を実行させる。

20

**【0246】**

ステップS313において、係数並び替え用バッファ部13に未処理の処理対象出力係数が存在しないと判定した場合、制御部201は、処理をステップS301に戻し、それ以降の処理を繰り返す。つまり、制御部201は、ステップS301乃至ステップS313の処理を繰り返すことにより、ピクチャ内の全プレシンクトについて、ウェーブレット変換処理を実行させ、さらにその空き時間にエントロピ符号化処理を実行することにより、ウェーブレット変換処理とエントロピ符号化処理を見かけ上同時並行的に実行させる。

**【0247】**

ステップS307において、1プレシンクト分のフィルタ処理が終了したと判定した場合、制御部201は、処理を図26のステップS321に進める。

30

**【0248】**

図26のステップS321において、制御部201は、エントロピ符号化処理実行部213を制御し、最後のリフティング演算の出力係数をエントロピ符号化させる。つまり、この最後のリフティング演算の出力係数は、係数並び替え用バッファ部13を介さずにエントロピ符号化させる。

**【0249】**

ステップS321の制御により、エントロピ符号化処理実行部213は、例えば5番目に合成フィルタ処理される係数データおよび6番目に合成フィルタ処理される係数データを順に符号化し、得られた符号化データを順次出力する。

40

**【0250】**

その符号化処理が終了すると、制御部201は、ステップS322において、符号化データ読み出し部313を制御し、コードバッファ部311より符号化データを所定順に読み出させる。この制御により、符号化データ読み出し部313は、コードバッファ部311に保持されている符号化データを、例えば合成フィルタ処理順に読み出し、それをエントロピ符号化処理実行部213に供給する。エントロピ符号化処理実行部213は、その供給された符号化データを、ステップS321において符号化して出力した符号化データに続けて出力する。

**【0251】**

ステップS323において、制御部201は、1ピクチャ分のフィルタ処理が終了した

50

か否かを判定し、1ピクチャ分のフィルタ処理が終了して無いと判定した場合、処理を図25のステップS301に戻し、それ以降の処理を繰り返す。

#### 【0252】

また、ステップS323において、1ピクチャ分のフィルタ処理が終了したと判定された場合、制御部201は、処理をステップS324に進め、係数並び替え用バッファ部13に保持されている残りの出力係数を処理対象出力係数群に設定する。

#### 【0253】

制御部201は、ステップS325において、係数並び替え処理実行部212を制御し、処理対象出力係数として指定された係数データを所定順に読み出させる。この制御により、係数並び替え処理実行部212は、出力係数読み出し部217を制御し、係数並び替え用バッファ部13に保持されている係数データ（処理対象出力係数）を、合成フィルタ処理を行う順に読み出させて供給させる。この制御により、出力係数読み出し部217は、係数並び替え用バッファ部13に保持されている係数データを、合成フィルタ処理を行う順に読み出し、読み出した係数データを係数並び替え処理実行部212に供給させる。係数並び替え処理実行部212は、供給された係数データを順次エントロピ符号化処理実行部213に供給する。

#### 【0254】

ステップS326において、制御部201は、エントロピ符号化処理実行部213を制御し、係数並び替え用バッファ部13より読み出された係数データをエントロピ符号化させる。この制御により、エントロピ符号化処理実行部213は、読み出された係数データを符号化し、得られた符号化データを出力する。

#### 【0255】

ステップS327において、制御部201は、係数並び替え用バッファ部13に、符号化処理していない処理対象出力係数が存在するか否かを判定し、存在すると判定した場合、処理をステップS325に戻し、それ以降の処理を繰り返す。

#### 【0256】

ステップS327において、係数並び替え用バッファ部13に未処理の処理対象出力係数が存在しないと判定した場合、制御部201は、制御処理を終了する。

#### 【0257】

以上のように制御処理を行うことにより、制御部201は、ウェーブレット変換処理とエントロピ符号化処理を同時並列的に実行し、より容易に、所定の速度で入力される画像データよりリアルタイムに符号化データを生成して出力することができる。また、これにより、保持するデータを符号化データにすることができるので、処理に必要なメモリ量を低減させ、ウェーブレット変換処理および符号化処理の負荷を低減させることができる。

#### 【0258】

なお、図25および図26においては、制御処理の流れの例を説明したが、分析フィルタ処理実行部211乃至出力係数読み出し部217は、上述したように、この制御処理の各ステップに対応して制御部201の制御に対応する処理を実行する。従って、図25および図26のフローチャートに示される制御処理の各ステップは、上述したとおりに、分析フィルタ処理実行部211乃至符号化データ読み出し部313のそれぞれが実行する処理も表しているものとし、各部が実行する処理の図示は省略する。

#### 【0259】

以上においては、図10を参照して説明したように、処理演算部としてのCPUが1つであるパーソナルコンピュータ100においてソフトウェアプログラムを実行する場合について説明したが、近年においては、CPUを複数有する情報処理装置も多く存在する。また、情報処理装置がCPUを1つしか有していないても、そのCPUが、互いに独立して動作することができるコアを複数有する場合もある。このように、互いに独立して動作する複数の演算処理部を有する情報処理装置は、複数の処理を互いに並行して実行することができる。以下においては、このような互いに独立して動作する複数の演算処理部を有する情報処理装置を用いて、上述したようなソフトウェアエンコーダを実現させる場合について説明

10

20

30

40

50

する。

【0260】

図27は、パーソナルコンピュータの他の構成例を示すブロック図である。図27に示されるパーソナルコンピュータ400は、基本的に図10に示されるパーソナルコンピュータ100と同様の構成を有する。すなわち、パーソナルコンピュータ400は、パーソナルコンピュータ100のROM102と同様のROM403、パーソナルコンピュータ100のRAM103と同様のRAM404、パーソナルコンピュータ100のバス104と同様のバス405、パーソナルコンピュータ100の入出力インターフェース110と同様の入出力インターフェース410、パーソナルコンピュータ100の入力部111と同様の入力部411、パーソナルコンピュータ100の出力部112と同様の出力部412、パーソナルコンピュータ100の記憶部113と同様の記憶部413、パーソナルコンピュータ100の通信部114と同様の通信部414、および、パーソナルコンピュータ100のドライブ115と同様のドライブ415を有する。ドライブ415には、パーソナルコンピュータ100のリムーバブルメディア121と同様のリムーバブルメディア421が適宜装着される。

【0261】

しかしながら、パーソナルコンピュータ400は、パーソナルコンピュータ100が1つのCPU101を有するのと異なり、CPU401およびCPU402を有する。CPU401およびCPU402のそれぞれは、基本的にCPU101と同様である。CPU401とCPU402は、互いに独立して処理を実行することができる。すなわち、パーソナルコンピュータ400は、互いに独立して動作する2つの演算処理部(CPU401およびCPU402)を有する。

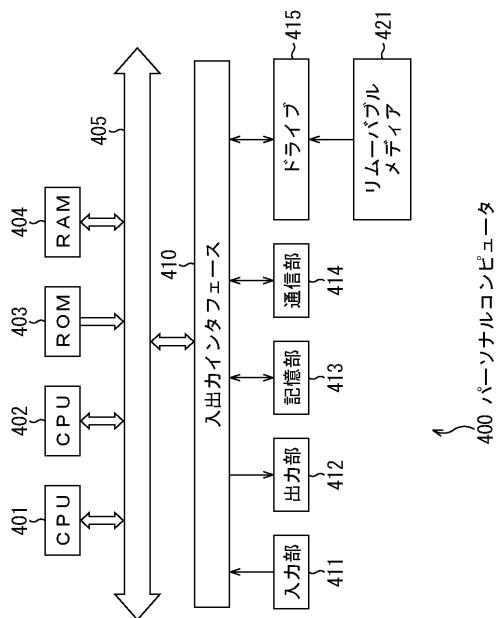

【0262】

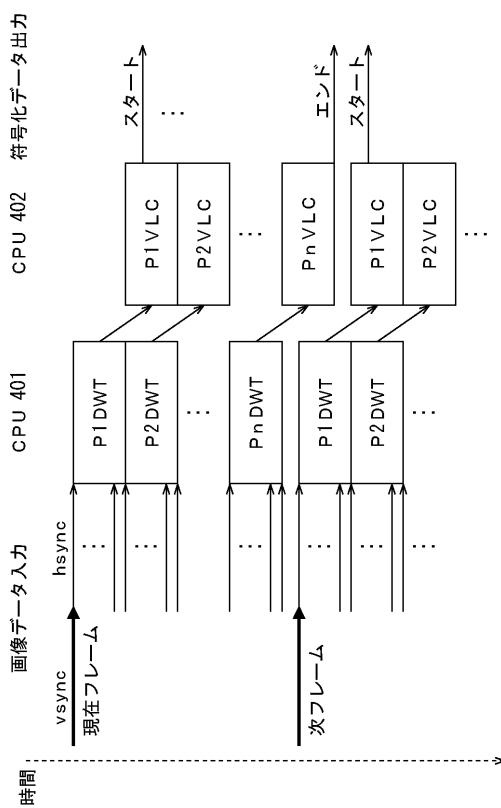

このようなパーソナルコンピュータ400において図1の符号化部10を実現させる場合、CPU401とCPU402とを使用して、図28のように処理が実行される。図28に、CPU401およびCPU402において実行される処理の流れを模式的に示す。図28は、図12に対応する図であり、基本的には図12と同様の構成であるので、その詳細についての説明は省略する。

【0263】

図28の例の場合、互いに独立して動作する2つの演算処理部(CPU401およびCPU402)が存在するので、一方の演算処理部であるCPU401において、ウェーブレット変換処理を実行させ、他方の演算処理部であるCPU402において、エントロピ符号化処理を実行させる。このようにすることにより、ウェーブレット変換処理とエントロピ符号化処理を互いに並行して実行することができる。図28の例の場合、上述した例と異なり、時分割による見かけ上の並列化ではなく、2つの演算処理部を用いて2つの処理を実際に並行して動作させる。

【0264】

上述した他の例と同様に、一方のCPU401は、画像データが2ライン入力される毎に実行可能なリフティング演算(DWT)を行い、出力係数を生成して係数並び替え用バッファ部13に保持させる。この分析フィルタ処理の実行中に、他方のCPU402は、この分析フィルタ処理と並行して、係数並び替え用バッファ部13に蓄積されている出力係数を、合成フィルタ処理を行う順に読み出してエントロピ符号化(VLC)し、得られた符号化データを順次出力する。

【0265】

このように2つの演算処理部を用いることにより、各CPUの負荷が低減される。従って、上述した他の例の場合よりも低速に動作するCPUであってもオーバーフローせずに、所定の速度で入力される画像データに対して、ウェーブレット変換処理とエントロピ符号化処理を容易にリアルタイムに実行することができる。

【0266】

また、図29に示されるように、この場合、CPU401が第2プレシンクトに対してウェーブレット変換(P2DWT)を行っているのと並行して、CPU402が第1プレシンクト

10

20

30

40

50

に対してエントロピ符号化を行う(P1 VLC)。従って、この場合の遅延時間は、上述した他の例と略同じである。また、CPU 4 0 2 は、符号化処理のみを行うので、符号化データの出力タイミングを適宜分散させることができる。従って、符号化部 1 0 の後段の処理が容易になる。

【0267】

また、図 2 8 に示されるように、CPU 4 0 1 が、出力係数を係数並び替え用バッファ部 1 3 に保持させるのと並行してCPU 4 0 2 が出力係数を読み出す。従って、係数並び替え用バッファ部 1 3 に同時に保持されるデータ量は、上述した他の例より少なくなる。つまり、この場合、係数並び替え用バッファ部 1 3 として必要なメモリ容量を低減させることができる。

10

【0268】

ただし、この場合、CPU 4 0 1 とCPU 4 0 2 とで動作を連携させる必要があり、CPU 4 0 1 において実行される処理と、CPU 4 0 2 において実行される処理の両方を制御する仕組みが必要になる。

【0269】

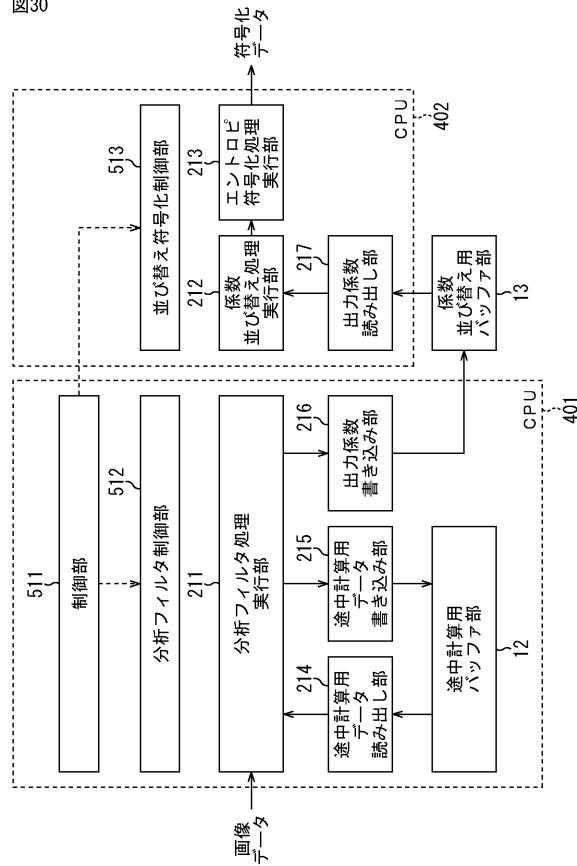

図 3 0 は、上述した流れで処理を実行する符号化部 1 0 を実現するソフトウェアプログラムを実行するCPU 4 0 1 およびCPU 4 0 2 が有する機能を示す機能ブロック図である。

【0270】

図 3 0 も、図 1 4 に対応する図であり、図 1 4 に示されるブロックと対応するブロックには同一の番号を付してある。図 3 0 の場合、図 1 4 や図 2 0 に示される分析フィルタ処理実行部 2 1 1 乃至出力係数読み出し部 2 1 7 の各処理部は、CPU 4 0 1 またはCPU 4 0 2 に割り当てられる。

20

【0271】

CPU 4 0 1 は、分析フィルタ処理に関する機能を有しており、分析フィルタ処理実行部 2 1 1 、途中計算用データ読み出し部 2 1 4 、途中計算用データ書き込み部 2 1 5 、および出力係数書き込み部 2 1 6 を有する。CPU 4 0 2 は、係数並び替えおよびエントロピ符号化に関する機能を有しており、係数並び替え処理実行部 2 1 2 、エントロピ符号化処理実行部 2 1 3 、および出力係数読み出し部 2 1 7 を有する。

【0272】

なお、図 3 0 の例においては、途中計算用バッファ部 1 2 がCPU 4 0 1 のキャッシュメモリ(図示せず)に形成され、係数並び替え用バッファ部 1 3 がRAM 4 0 4 に形成されるものとして説明を行うが、上述したように、途中計算用バッファ部 1 2 および係数並び替え用バッファ部 1 3 は、任意の記憶領域に形成することができる。ただし、アクセス頻度の高い途中計算用バッファ部 1 2 は、負荷や遅延時間を低減させるために、分析フィルタ処理が行われるCPU 4 0 1 のキャッシュメモリに形成させるのが望ましい。

30

【0273】

図 3 0 に示されるように、CPU 4 0 1 およびCPU 4 0 2 の両方の機能ブロックにより、上述した他の例のCPU 1 0 1 と同様に、図 1 の符号化部 1 0 を実現する。つまり、CPU 4 0 1 において、画像データに対して分析フィルタ処理が行われ、その出力係数が係数並び替え用バッファ部 1 3 に保持され、CPU 4 0 2 において、その出力係数を合成フィルタ処理を行う順に読み出し、各係数に対して符号化処理を行い、符号化データを生成して出力する。

40

【0274】

CPU 4 0 1 は、さらに、制御部 5 1 1 および分析フィルタ制御部 5 1 2 を有し、CPU 4 0 2 は、さらに、並び替え符号化制御部 5 1 3 を有する。

【0275】

制御部 5 1 1 は、CPU 4 0 1 の分析フィルタ制御部 5 1 2 およびCPU 4 0 2 の並び替え符号化制御部 5 1 3 の動作を制御する。分析フィルタ制御部 5 1 2 は、CPU 4 0 1 が有する各機能ブロックの動作を制御し、CPU 4 0 1 において実行される分析フィルタ処理に関する制御を行う。並び替え符号化制御部 5 1 3 は、CPU 4 0 2 が有する各機能ブロックの動

50

作を制御し、CPU 4 0 2において実行される係数の並び替えやエントロピ符号化に関する制御を行う。

#### 【0276】

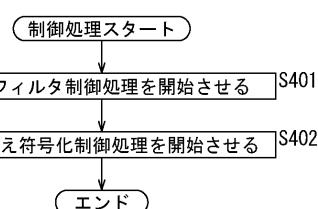

図31のフローチャートを参照して、制御部511が実行する制御処理の流れの例を説明する。なお、この制御処理は、入力される画像データのピクチャ毎に実行される。

#### 【0277】

制御処理が開始されると、制御部511は、ステップS401において、分析フィルタ制御部512を制御し、分析フィルタ制御処理を開始させる。この制御により、分析フィルタ制御部512は、分析フィルタ制御処理を開始する。分析フィルタ制御処理については後述する。ステップS402において、制御部511は、並び替え符号化制御部513を制御し、並び替え符号化制御処理を開始させる。この制御により、並び替え符号化制御部513は、並び替え符号化制御処理を開始する。並び替え符号化制御処理については後述する。

#### 【0278】

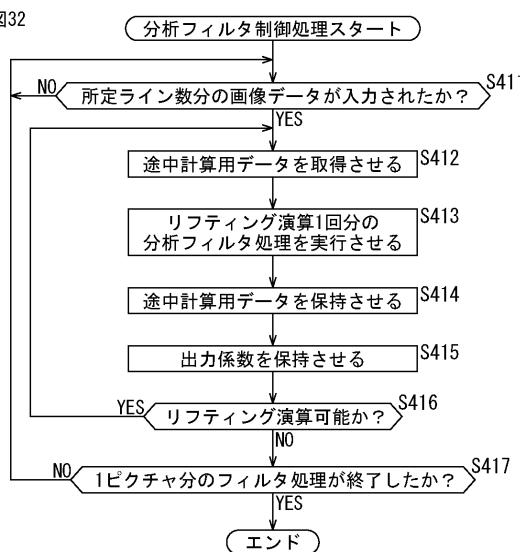

図32のフローチャートを参照して、分析フィルタ制御部512が実行する分析フィルタ制御処理の流れの例を説明する。

#### 【0279】

分析フィルタ制御処理が開始されると、分析フィルタ制御部512は、ステップS411において、所定ライン数（例えば2ラインまたは3ライン）分の画像データが入力されたか否かを判定し、入力されたと判定するまで待機する。そして、入力されたと判定した場合、分析フィルタ制御部512は、処理をステップS412に進める。

#### 【0280】

ステップS412において、分析フィルタ制御部512は、分析フィルタ処理実行部211を制御し、途中計算用バッファ部12より、これから行うリフティング演算に必要な途中計算用データを取得させる。この制御により、分析フィルタ処理実行部211は、途中計算用データ読み出し部214を制御して、これから行うリフティング演算に必要な途中計算用データを、途中計算用バッファ部12より読み出させ、供給させる（つまり、途中計算用データを取得する）。この制御により、途中計算用データ読み出し部214は、要求された途中計算用データを途中計算用バッファ部12より読み出し、分析フィルタ処理実行部211に供給する。

#### 【0281】

ステップS413において、分析フィルタ制御部512は、分析フィルタ処理実行部211を制御し、リフティング演算1回分の分析フィルタ処理を実行させる。この制御により、分析フィルタ処理実行部211は、図28を参照して説明したように、実行可能な分析フィルタ処理のリフティング演算を1回分実行する。

#### 【0282】

リフティング演算が行われると、分析フィルタ制御部512は、ステップS414において、分析フィルタ処理実行部211を制御し、リフティング演算に用いられた画像データや係数データ、およびリフティング演算により得られた係数データのうち、次回以降のリフティング演算に利用するデータを途中計算用データとして途中計算用バッファ部12に保持させる。この制御により、分析フィルタ処理実行部211は、途中計算用データ書き込み部215に途中計算用データを供給するとともに、その途中計算用データ書き込み部215を制御し、供給した途中計算用データを途中計算用バッファ部12に書き込ませる。この制御により、途中計算用データ書き込み部215は、分析フィルタ処理実行部211より供給された途中計算用データを、途中計算用バッファ部12に書き込み、保持させる。

#### 【0283】

ステップS415において、分析フィルタ制御部512は、分析フィルタ処理実行部211を制御し、リフティング演算により得られた出力係数を、係数並び替え用バッファ部13に保持させる。この制御により、分析フィルタ処理実行部211は、出力係数書き込

み部 216 に出力係数を供給するとともに、その出力係数書き込み部 216 を制御し、供給した出力係数を係数並び替え用バッファ部 13 に書き込ませる。この制御により、出力係数書き込み部 216 は、分析フィルタ処理実行部 211 より供給された出力係数を、係数並び替え用バッファ部 13 に書き込み、保持させる。

【0284】

ステップ S416において、分析フィルタ制御部 512 は、新たな画像データの入力無しに、さらにリフティング演算が可能であるか否かを判定し、可能であると判定した場合、処理をステップ S412 に戻し、それ以降の処理を繰り返す。つまり、分析フィルタ制御部 512 は、ステップ S412 乃至ステップ S416 の処理を繰り返すことにより、図 28 を参照して説明したように、入力された画像データに対応する、実行可能なリフティング演算を全て行わせる。

【0285】

そして、ステップ S416において、実行可能なリフティング演算が無くなつたと判定した場合、分析フィルタ制御部 512 は、処理をステップ S417 に進める。ステップ S417において、分析フィルタ制御部 512 は、1ピクチャ分のフィルタ処理が終了したか否かを判定し、1ピクチャ分のフィルタ処理が終了して無いと判定した場合、処理をステップ S411 に戻し、それ以降の処理を繰り返す。

【0286】

また、ステップ S417において、1ピクチャ分のフィルタ処理が終了したと判定された場合、分析フィルタ制御部 512 は、分析フィルタ制御処理を終了する。

【0287】

次に、図 33 のフローチャートを参照して、並び替え符号化制御部 513 が実行する並び替え符号化制御処理の流れの例を説明する。

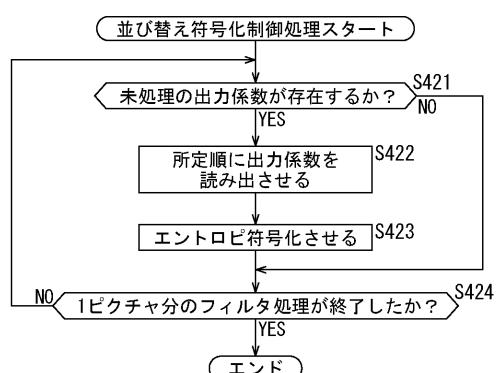

【0288】

並び替え符号化制御処理が開始されると、並び替え符号化制御部 513 は、ステップ S421において、係数並び替え用バッファ部 13 に、符号化処理していない出力係数が存在するか否かを判定し、存在すると判定した場合、処理をステップ S422 に進める。ステップ S422において、並び替え符号化制御部 513 は、係数並び替え処理実行部 212 を制御し、係数並び替え用バッファ部 13 に保持されている出力係数を所定順に読み出させる。この制御により、係数並び替え処理実行部 212 は、出力係数読み出し部 217 を制御し、係数並び替え用バッファ部 13 に保持されている係数データ（出力係数）を、合成フィルタ処理を行う順に読み出させて供給させる。この制御により、出力係数読み出し部 217 は、係数並び替え用バッファ部 13 に保持されている係数データを、合成フィルタ処理を行う順に読み出し、読み出した係数データを係数並び替え処理実行部 212 に供給させる。係数並び替え処理実行部 212 は、供給された係数データを順次エントロピ符号化処理実行部 213 に供給する。

【0289】

ステップ S423において、並び替え符号化制御部 513 は、エントロピ符号化処理実行部 213 を制御し、係数並び替え用バッファ部 13 より読み出された係数データをエントロピ符号化させる。この制御により、エントロピ符号化処理実行部 213 は、読み出された係数データを符号化し、得られた符号化データを出力する。

【0290】

ステップ S423 の処理を終了すると、並び替え符号化制御部 513 は、処理をステップ S424 に進める。また、ステップ S421において、未処理の出力係数が存在しないと判定した場合、並び替え符号化制御部 513 は、ステップ S422 およびステップ S423 の処理を省略し、処理をステップ S424 に進める。

【0291】

ステップ S424において、並び替え符号化制御部 513 は、1ピクチャ分のフィルタ処理が終了したか否かを判定し、1ピクチャ分のフィルタ処理が終了していないと判定した場合、処理をステップ S421 に戻し、それ以降の処理を繰り返す。

10

20

30

40

50

**【 0 2 9 2 】**

また、ステップ S 4 2 4 において、1ピクチャ分のフィルタ処理が終了したと判定された場合、並び替え符号化制御部 5 1 3 は、並び替え符号化制御処理を終了する。

**【 0 2 9 3 】**

以上のように各制御処理を行うことにより、制御部 5 1 1 、分析フィルタ制御部 5 1 2 、および並び替え符号化制御部 5 1 3 は、ウェーブレット変換処理とエントロピ符号化処理を、2つの演算処理部を利用して実際に並行して実行し、容易に、所定の速度で入力される画像データよりリアルタイムに符号化データを生成して出力することができる。

**【 0 2 9 4 】**

なお、図 2 7 においては、CPUの個数が2つであるように説明したが、上述した処理は 10 、3つ以上のCPUを有するパーソナルコンピュータにおいても実行可能である。また、図 2 6 より前の図面を参照して説明した他の制御方法を、図 2 7 に示されるパーソナルコンピュータ 4 0 0 のように複数の演算処理部を有する情報処理装置において実行することもできる。

**【 0 2 9 5 】**

また、以上に説明した各実施の形態においては、それぞれの制御部が、分析フィルタ処理実行部 2 1 1 乃至出力係数読み出し部 2 1 7 等の各処理部を制御するように説明したが、上述した制御処理は、分析フィルタ処理実行部 2 1 1 乃至出力係数読み出し部 2 1 7 等の各処理部において行われるようにしてよい。つまり、制御部を別途設けずに、実際に 20 データを処理する分析フィルタ処理実行部 2 1 1 乃至出力係数読み出し部 2 1 7 等の各処理部が適宜互いを制御しあうようにしてよい。

**【 0 2 9 6 】**

以上においては、ウェーブレット変換処理をリフティング演算処理1回分毎に制御し、また、符号化処理を各係数データに対する処理毎に制御するように説明したが、ウェーブレット変換処理および符号化処理のそれぞれを複数の工程に分割する処理単位であれば、どの様な処理単位で制御するようにしてよい。例えば、ウェーブレット変換処理をリフティング演算処理1回分よりもさらに細かい処理単位で制御するようにし、より細かな制御を行いCPUの使用効率をさらに向上させることができるようにしてよいし、複数のリフティング演算処理を処理単位とし、制御処理をより簡易化するようにしてよい。また、例えば、符号化処理を係数データ毎の処理よりさらに細かい処理単位で制御するようにし、より細かな制御を行いCPUの使用効率をさらに向上させることができるようにしてよいし、複数の係数データに対する処理を処理単位とし、制御処理をより簡易化するよう 30 にしてよい。

**【 0 2 9 7 】**

また、以上においては分析フィルタ処理に  $5 \times 3$  フィルタを用いるように説明したが、フィルタ処理に使用されるフィルタはどの様なフィルタを用いてもよく、例えば、 $9 \times 7$  フィルタを用いるようにしてよい。

**【 0 2 9 8 】**

上述した一連の処理は、ソフトウェアにより実行させることもできるが、ハードウェアにより実行させることもできる。一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または、各種のプログラムをインストールすることで、各種の機能を実行することができる、例えば汎用のパーソナルコンピュータ、または、複数の装置よりなる情報処理システムの情報処理装置などに、プログラム記録媒体からインストールされる。 40

**【 0 2 9 9 】**

この記録媒体は、例えば、図 1 0 や図 2 7 に示されるように、装置本体とは別に、ユーザにプログラムを配信するために配布される、プログラムが記録されている磁気ディスク（フレキシブルディスクを含む）、光ディスク（CD-ROM(Compact Disk-Read Only Memory), DVD(Digital Versatile Disk)を含む）、光磁気ディスク（MD (Mini-Disk)（登録商標）を含む）、もしくは半導体メモリなどよりなるリムーバブルメディア 1 2 1 またはリム 50

ーバブルメディア421により構成されるだけでなく、装置本体に予め組み込まれた状態でユーザに配信される、プログラムが記録されているROM102若しくはROM403、または、記憶部113若しくは記憶部413などで構成される。

【0300】

なお、本明細書において、記録媒体に記録されるプログラムを記述するステップは、記載された順序に沿って時系列的に行われる処理はもちろん、必ずしも時系列的に処理されなくとも、並列的あるいは個別に実行される処理をも含むものである。

【0301】

また、本明細書において、システムとは、複数のデバイス（装置）により構成される装置全体を表すものである。

10

【0302】

なお、以上において、1つの装置として説明した構成を分割し、複数の装置として構成するようにしてもよい。逆に、以上において複数の装置として説明した構成をまとめて1つの装置として構成されるようにしてもよい。また、各装置の構成に上述した以外の構成を付加するようにしてももちろんよい。さらに、システム全体としての構成や動作が実質的に同じであれば、ある装置の構成の一部を他の装置の構成に含めるようにしてもよい。つまり、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【産業上の利用可能性】

【0303】

20

以上説明した本発明は、複数の端末間で画像を圧縮して伝送、受信して伸長して画像を出力するシステム、特に低遅延で実現する必要性が高いプロダクツ・アプリケーションに好適である。具体的には、放送局で多用するデジタルトライアックシステム、ライブ映像配信システム、TV会議システム、監視カメラ・レコーダシステム、医用遠隔医療診断、生徒と教師間のインタラクティブ通信、ビデオゲーム等に応用が可能である。また、画像データを圧縮符号化して記録媒体に記録する装置（記録再生装置も含む）やシステム等にも適用可能である。

【図面の簡単な説明】

【0304】

30

【図1】符号化部の構成例を示す図である。

【図2】復号部の構成例を示す図である。

【図3】ウェーブレット変換について概略的に説明するための略線図である。

【図4】ウェーブレット変換について概略的に説明するための略線図である。

【図5】ウェーブレット変換について概略的に説明するための略線図である。

【図6】5×3分析フィルタのリフティング構成の例を説明する図である。

【図7】5×3合成フィルタのリフティング構成の例を説明する図である。

【図8】分析フィルタ処理および合成フィルタ処理の流れの例を説明する図である。

【図9】符号化側および復号側の各処理が並列的に実行される様子を説明するための略線図である。

【図10】パーソナルコンピュータの主な構成例を示すブロック図である。

40

【図11】ウェーブレット変換処理とエントロピ符号化処理の流れの関係の例を説明する図である。

【図12】CPUにおいて実行される処理の流れの例を説明する模式図である。

【図13】CPUにおいて実行される処理の流れの例を説明する模式図である。

【図14】CPUが有する機能の構成例を説明する機能ブロック図である。

【図15】制御処理の流れの例を説明するフローチャートである。

【図16】制御処理の流れの例を説明する、図15に続くフローチャートである。

【図17】ウェーブレット変換処理とエントロピ符号化処理の流れの関係の他の例を説明する図である。

【図18】CPUにおいて実行される処理の流れの、他の例を説明する模式図である。

50

- 【図19】CPUにおいて実行される処理の流れの、他の例を説明する模式図である。

- 【図20】CPUが有する機能の、他の構成例を説明する機能ブロック図である。

- 【図21】制御処理の流れの、他の例を説明するフローチャートである。

- 【図22】CPUにおいて実行される処理の流れの、さらに他の例を説明する模式図である

- 。

- 【図23】CPUにおいて実行される処理の流れの、さらに他の例を説明する模式図である

- 。

- 【図24】CPUが有する機能の、さらに他の構成例を説明する機能ブロック図である。

- 【図25】制御処理の流れの、さらに他の例を説明するフローチャートである。

- 【図26】制御処理の流れの、さらに他の例を説明する、図25に続くフローチャートである。

- 【図27】パーソナルコンピュータの、他の主な構成例を示すブロック図である。

- 【図28】CPUにおいて実行される処理の流れの、さらに他の例を説明する模式図である

- 。

- 【図29】CPUにおいて実行される処理の流れの、さらに他の例を説明する模式図である

- 。

- 【図30】CPUが有する機能の、さらに他の構成例を説明する機能ブロック図である。

- 【図31】制御処理の流れの、さらに他の例を説明するフローチャートである。

- 【図32】分析フィルタ制御処理の流れの例を説明するフローチャートである。

- 【図33】並び替え符号化制御処理の流れの例を説明するフローチャートである。

- 【符号の説明】

- 【0305】

- 10 符号化部, 11 ウエーブレット変換部, 12 途中計算用バッファ部,

13 係数並び替え用バッファ部, 14 係数並び替え部, 15 エントロピ符号化

部, 100 パーソナルコンピュータ, 101 CPU, 201 制御部, 211

分析フィルタ処理実行部, 212 係数並び替え処理実行部, 213 エントロピ

符号化処理実行部, 214 途中計算用データ読み出し部, 215 途中計算用データ

書き込み部, 216 出力係数書き込み部, 217 出力係数読み出し部, 22

1 画像データバッファ部, 311 コードバッファ部, 312 符号化データ書き

込み部, 313 符号化データ読み出し部, 401 および 402 CPU, 511

制御部, 512 分析フィルタ制御部, 513 並び替え符号化制御部

【図1】

## 【図2】

【図3】

## 【図4】

【図5】

【図6】

$$d_i^1 = d_i^0 - 1/2(s_{i-1}^0 + s_{i+1}^0); \text{ 高域成分出力}$$

$$s_i^1 = s_i^0 + 1/4(d_{i-1}^1 + d_i^1); \text{ 低域成分出力}$$

【図7】

$$s_i^0 = s_i^1 - 1/4(d_{i-1}^1 + d_i^1); \text{ 偶数番目出力}$$

$$d_i^0 = d_i^1 + 1/2(s_i^0 + s_{i+1}^0); \text{ 奇数番目出力}$$

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

ライン番号 分割レベル1 分割レベル2 分割レベル3

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

ライン番号 分割レベル1 分割レベル2 分割レベル3

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【 図 25 】

図25

【 図 26 】

図26

【図27】

図27

## 【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

図32

【図33】

図33

---

フロントページの続き

(56)参考文献 特開2001-326936(JP,A)

特開平10-063643(JP,A)

特開2005-217872(JP,A)

特開2007-049485(JP,A)

特開2003-274185(JP,A)

特開2000-115770(JP,A)

特開2000-299863(JP,A)

特開2001-218208(JP,A)

特開2003-319185(JP,A)

特開2004-242287(JP,A)

特開2004-040388(JP,A)

特開2004-194224(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N7/24-7/68

H04N1/41-1/419

H03M3/00-11/00