(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3853448号

(P3853448)

(45) 発行日 平成18年12月6日(2006.12.6)

(24) 登録日 平成18年9月15日(2006.9.15)

(51) Int.C1.

F 1

G 1 1 C 29/04

(2006.01)

G 1 1 C 29/00

603B

請求項の数 2 (全 17 頁)

(21) 出願番号 特願平8-339559

(22) 出願日 平成8年12月19日(1996.12.19)

(65) 公開番号 特開平10-188591

(43) 公開日 平成10年7月21日(1998.7.21)

審査請求日 平成15年11月28日(2003.11.28)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100089233

弁理士 吉田 茂明

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 森嶋 哉圭

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 小松 正

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項1】

行列方向に配列されたメモリセルと、前記メモリセルにデータ又は選択信号を伝送するビット線又はワード線であるメモリー線と、故障した前記メモリ線に代替できる冗長メモリセルを有する冗長メモリ線と、前記ビット線と外部回路とデータの入出力をするデータ線と、前記メモリセルの書き込み時データと記憶データとを比較して故障メモリセルの有無を示す比較データを出力する比較回路と、前記比較データを記憶する前記メモリ線ごとに設けられたメモリ線故障記憶回路と、前記メモリ線故障記憶回路の出力に基づき前記メモリ線又は前記冗長メモリ線のいずれかを選択する前記メモリ線ごとに設けられたメモリ線選択回路とを備える半導体記憶装置において、

比較回路が比較データを一時保持して比較保持データを出力する比較レジスタであって、データ線を介して前記比較保持データをメモリ線故障記憶回路に記憶することを特徴とする半導体記憶装置。

## 【請求項2】

複数個のメモリ線に並列的にデータの入出力が可能な複数個のデータ線と、前記複数個のメモリ線に対応して複数個の比較レジスタを設け、前記比較レジスタの比較保持データを対応するデータ線を介して対応するメモリ線故障記憶回路に記憶することを特徴とする請求項1記載の半導体記憶装置。

## 【発明の詳細な説明】

【0001】

**【発明の属する技術分野】**

本発明は冗長メモリセルを有する半導体記憶装置に関するものである。

**【0002】****【従来の技術】**

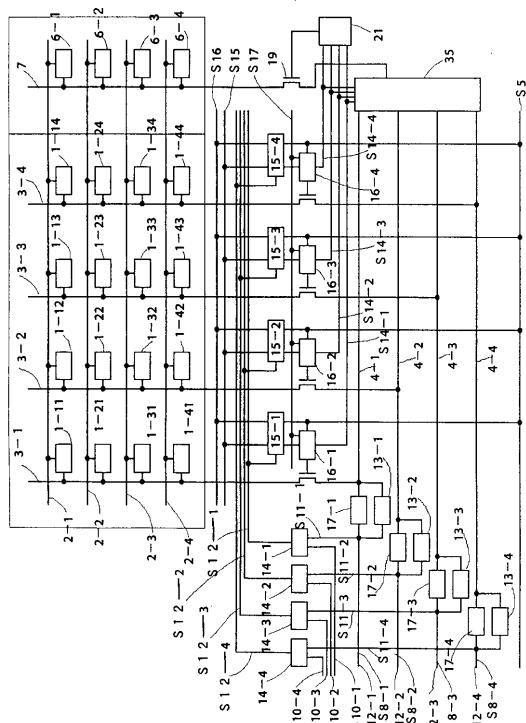

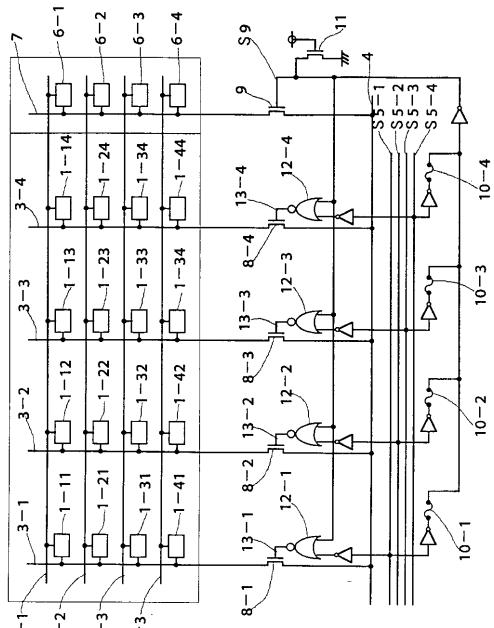

図17は従来の半導体記憶装置の回路図である。ここではカラム方向の冗長方式を示している。図17において1-11～1-44は行列方向に配列されたメモリセル(図では簡単のため4行4列のメモリセル構成を示す)である。2-1～2-4はメモリセルアレイの各行毎に設けられたワード線である。3-1～3-4はメモリセルアレイの各列毎に設けられたビット線である。4はビット線3-1～3-4を冗長ビット線7のそれぞれと共に接続された入力／出力信号線(以下、I/O線という)である。S5-1～S5-4はそれぞれビット線3-1～3-4を選択するカラム選択信号で、図示しないカラムデコード回路から供給される。

10

**【0003】**

6-1～6-4は冗長メモリセルである。7は冗長メモリセル6-1～6-4が接続されている冗長ビット線である。8-1～8-4はそれぞれカラムデコード信号S5-1～S5-4に基づき、それぞれビット線3-1～3-4とI/O線4を接続するトランスマニアゲートである。9は冗長ビット線7とI/O線4とを接続する冗長線トランスマニアゲートである。10-1～10-4はそれぞれビット線3-1～3-4の冗長ビット線7への切り替えを制御するヒューズである。11は冗長カラム選択信号S9に接続された駆動力の小さいトランジスタである。12-1～12-4はNOR回路である。

20

**【0004】**

次に動作について説明する。メモリセル1-11～1-44を図示しない比較回路によりテストし、故障が認められなかった場合はヒューズ10-1～10-4をレーザーにより全て切断する。この場合、冗長カラム選択信号S9はトランジスタ11により接地されているので、冗長線トランスマニアゲート9は導通せず冗長メモリセル6-1～6-4は選択されない。また、NOR回路12-1～12-4への入力の一方は常に“L”であるので、カラムデコード信号S5-1～S5-4はそれぞれ、そのままビット線選択信号S13-1～S13-4となり、正規のビット線トランスマニアゲート8-1～8-4が選択される。

**【0005】**

30

次に例えばメモリセル1-22に故障が認められた場合には、ヒューズ10-2以外の全てのヒューズをレーザーで切断する。この場合、故障したメモリセル1-22が接続されているビット線3-2を選択するカラムデコード信号が与えられると、即ちカラムデコード信号S5-2が“H”になると、その信号はヒューズ10-2を介して冗長カラム選択信号S9に伝えられる。

**【0006】**

このとき、トランジスタ11は駆動力が小さいために冗長カラム選択信号S9の振幅には影響を与えない。また、NOR回路12-1～12-4への入力の一方は“H”となるので、ビット線選択S13-1～S13-4は“L”的ままである。すなわち、故障したメモリセルが接続されたビット線3-2の代わりに冗長ビット線7がI/O線4と接続されこの半導体記憶装置はあたかも故障がないように動作する。

40

**【0007】****【発明が解決しようとする課題】**

従来の冗長回路制御回路は以上のように構成されているため、故障したメモリセルの冗長メモリセルへの置換はヒューズをレーザーで切断することにより制御していた。しかし、レーザー装置は高価であり、製造コストが増加するという欠点があった。

**【0008】**

本発明はかかる問題点に鑑みてなされたものであって、高価な装置を用いることなく、製造コストを増加することなく故障メモリセルを冗長メモリセルに置き替えることのできる半導体記憶装置を得ることを目的とする。

50

さらにチップ面積の小さな半導体記憶装置を得ることを目的とする。

さらに故障メモリセルの冗長メモリセルへの置換の高速化が可能な半導体記憶装置を得ることを目的とする。

#### 【0009】

##### 【課題を解決するための手段】

この発明の請求項1に記載の半導体記憶装置は、行列方向に配列されたメモリセルと、メモリセルにデータ又は選択信号を伝送するビット線又はワード線であるメモリー線と、故障した前記メモリ線に代替できる冗長メモリセルを有する冗長メモリ線と、ビット線と外部回路とデータの入出力をするデータ線と、メモリセルの書き時データと記憶データとを比較して故障メモリセルの有無を示す比較データを出力する比較回路と、比較データを記憶するメモリ線ごとに設けられたメモリ線故障記憶回路と、メモリ線故障記憶回路の出力に基づきメモリ線又は冗長メモリ線のいずれかを選択するメモリ線ごとに設けられたメモリ線選択回路とを備える半導体記憶装置において、比較回路が比較データを一時保持して比較保持データを出力する比較レジスタであって、データ線を介して比較保持データをメモリ線故障記憶回路に記憶するものである。

10

#### 【0010】

この発明の請求項2に記載の半導体記憶装置は、複数個のメモリ線に並列的にデータの入出力が可能な複数個のデータ線と、複数個のメモリ線に対応して複数個の比較レジスタを設け、比較レジスタの比較保持データを対応するデータ線を介して対応するメモリ線故障記憶回路に記憶するものである。

20

#### 【0013】

##### 【発明の実施の形態】

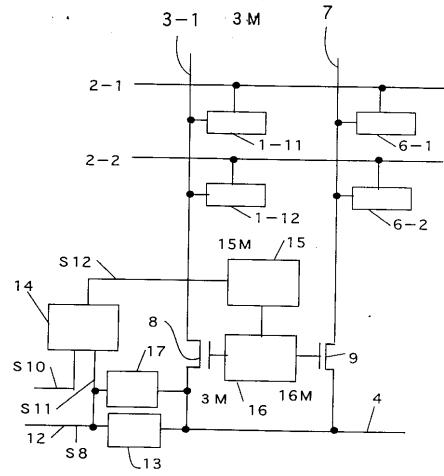

図1は第1の発明の構成を示すブロック図である。1-11、1-12はメモリセルであって、データを記憶するものである。6-1、6-2は冗長メモリセルであって、メモリセル1-11、1-12と代替可能なものである。

3Mはメモリ線であって、メモリセルにデータを入出力するビット線又はメモリセルの選択信号を入力するワード線である。

3-1はメモリ線3Mであるビット線であって、メモリセル1-11、1-12と接続されメモリセル1-11、1-12にデータを入出力する配線である。7はメモリ線3Mである冗長ビット線であって、冗長メモリセル6-1、6-2が接続されており、メモリ線3-1に代替可能なものである。

30

2-1、2-2はメモリ線3Mであるワード線であって、メモリセル1-11、1-12と接続されビットメモリセル1-11及び冗長メモリセル6-1、又はメモリセル1-12及び冗長メモリセル6-2の選択信号を送る配線である。

#### 【0014】

12はデータ線であって、外部回路とメモリ線間のデータを入出力する配線である。4はI/O線であって、ビット線3-1と冗長ビット線7に接続され、データ線12とメモリ線又は冗長線を接続する配線である。8、9はトランスファーゲートであって、ビット線3-1又は冗長ビット線7とI/O線4との接続をオンオフするものである。

#### 【0015】

40

14は比較回路であって、メモリセル1-11又は1-12への書き時データS10と記憶データS11を比較してメモリセルの故障の有無を示す比較データS12を出力するものである。15Mはメモリ線ごとに設けられたメモリ線故障記憶回路であって、比較データS12を記憶するものである。15はメモリ線故障記憶回路15Mであるビット線故障記憶回路である。16Mはメモリ線ごとに設けられたメモリ線選択回路であって、メモリ線故障記憶回路15Mの出力に基づきメモリ線3M又は冗長メモリ線のいずれかを選択するものである。16はメモリ線選択回路16Mであるビット線選択回路である。17はセンスアンプであって、I/O線4の信号を増幅するものである。13はライトアンプであって、データ線12の信号S8の駆動回路である。

#### 【0016】

50

次にこの半導体記憶装置の動作を説明する。まずメモリセルへのデータの書き込み動作は、メモリ線 3 M であるビット線 3 - 1、及びワード線 2 - 1、2 - 2 に接続されたメモリセル 1 - 1 1、1 - 1 2 を順次選択して、データ線 1 2 からデータ S 8 を入力して記憶させる。

次にメモリセルの故障の有無の検査は、メモリセル 1 - 1 1、1 - 1 2 の記憶データ S 1 1 と外部に保持していた書込時データ S 1 0 とを比較回路 1 4 で比較することにより行い、その結果は比較データ S 1 2 として出力される。記憶データ S 1 1 と書込時データ S 1 0 が異なる場合は故障メモリセル有りと判定される。比較データ S 1 2 はビット線故障記憶回路 1 5 に転送され記憶される。

#### 【 0 0 1 7 】

10

次にビット線故障記憶回路の出力に基づき、ビット線に故障のある場合はビット線選択回路 1 6 により故障ビット線に替えて冗長メモリ線 7 が接続される。例えばビット線 3 - 1 に故障メモリセルの無い場合はビット線 3 - 1 が選択され、ビット線 3 - 1 に故障の有る場合はビット線 3 - 1 の替わりに冗長メモリ線 7 が選択されて I / O 線 4 に切替えて接続される。

#### 【 0 0 1 8 】

以上のようにメモリ線ごとにメモリ線故障記憶回路 1 5 M を設けたので、故障の有無はメモリ線故障記憶回路 1 5 M に保持されるので、ヒューズを用いることなく又レーザー装置も用いることなく故障メモリ線を冗長メモリ線に切り替えることができるので、レーザー装置の購入、保守等に掛かるコストを削減することが出来る。

20

#### 【 0 0 1 9 】

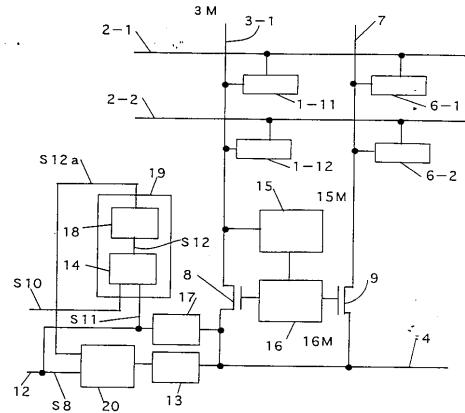

図 2 は第 2 の発明の構成を示すブロック図である。この発明の構成は、図 1 のブロック図において、比較回路 1 4 を比較データ S 1 2 を一時保持するラッチ回路 1 8 を有する比較レジスタ 1 9 としたものである。1 8 はラッチ回路であって、比較データ S 1 2 を一時保持するものである。1 9 は比較レジスタであって、比較回路 1 4 とラッチ回路 1 8 とで構成され、メモリセル 1 - 1 1 ~ 1 - 1 2 の記憶データ S 1 1 と書込時データ S 1 0 との比較データ S 1 2 を一時保持して比較保持データ S 1 2 a を出力するものである。2 0 は入力切替器であって、比較保持データ S 1 2 a 又はデータ線 1 2 のデータ S 8 を選択するものである。その他の符号は図 1 のものと同じものである。

#### 【 0 0 2 0 】

30

つぎにこの半導体記憶装置の動作を説明する。まずメモリセル 1 - 1 1 ~ 1 - 1 2 のデータの書き込み動作は第 1 の発明のものと同じである。メモリセルの故障の検査も第 1 の発明と同様にして行う。次に比較データ S 1 2 は比較レジスタ 1 9 のラッチ回路 1 8 で一時保持され、比較保持データ S 1 2 a は書込制御信号（図示なし、後述の S 1 5 ）に同期して、さらに書込制御信号に同期して切替器 2 0 では比較レジスタ 1 9 からの比較保持データ S 1 2 a が選択されてライトアンプ 1 3 からに入力されるので、比較保持データ S 1 2 a は I / O 線 4 を通ってビット線故障記憶回路 1 5 に記憶される。

以下の故障ビット線を冗長ビット線への切替え動作はブロック図 1 のものと同じである。

#### 【 0 0 2 1 】

以上のように比較レジスタ 1 9 を設けたので、比較レジスタ 1 9 からビット線故障記憶回路 1 5 への比較保持データ S 1 2 a の書き込み専用の配線を必要とせずチップの面積を小さくすることができる。

40

#### 【 0 0 2 2 】

実施の形態 1 .

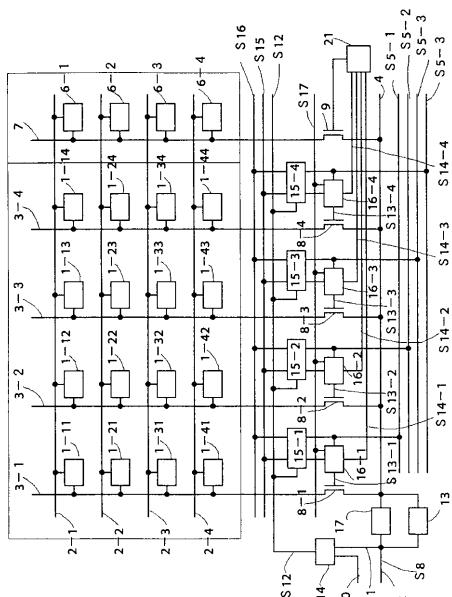

図 3 は実施の形態 1 の半導体記憶装置の回路図である。図 3 において、1 - 1 1 ~ 1 - 4 4 は行列方向に配列されたメモリセル（図では 4 行 4 列とする）である。2 - 1 ~ 2 - 4 はワード線であって、メモリセルの選択信号を入力する配線である。3 - 1 ~ 3 - 4 はビット線であって、メモリセルにデータを入出力する配線である。6 - 1 ~ 6 - 4 は冗長メモリセルであって、メモリセル 1 - 1 1 ~ 1 - 4 4 に置き換え得るものである。7 は冗長ビット線である。

50

**【0023】**

S 13-1 ~ S 13-4 はそれぞれカラム選択信号であって、ビット線 3-1 ~ 3-4 のトランスマルチплексорを駆動するものである。

**【0024】**

14 は比較回路である。15-1 ~ 15-4 はビット線ごとに設けられたビット線故障記憶回路であって、比較データ S 12 を記憶するものである。16-1 ~ 16-4 はビット線ごとに設けられたビット線選択回路である。

**【0025】**

21 は冗長ビット線選択回路であって、冗長ビット線の選択信号 S 14-1 ~ S 14-4 に基づき、冗長ビット線 7 を選択するものである。S 15 は書き制御信号であって、ビット線故障記憶回路 15-1 ~ 15-4 の記憶データの書き込みを制御するものである。S 16 はリセット信号であって、ビット線故障記憶回路 15-1 ~ 15-4 の初期値設定をするための信号である。S 17 はテスト信号であって、メモリセルの故障テスト期間中にビット線選択回路 16-1 ~ 16-4 の状態を固定する信号である。

その他の符号は図 1、図 2 及び図 17 のものと同じものである。

**【0026】**

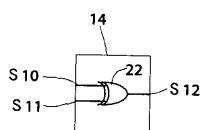

図 9 は比較回路 14 の一実施例を示す回路図である。22 はメモリセルの書き時データ S 10 と記憶データ S 11 とが一致していれば比較データ S 12 として “L” を出力し、不一致ならば “H” を出力する XOR 回路である。

**【0027】**

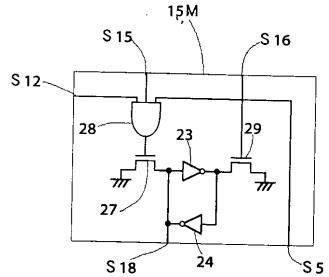

図 10 はメモリ線故障記憶回路 15M を示す回路図である。これは図 3 のビット線故障記憶回路 15、又は図 4 に示すワード線故障記憶回路 15a の回路例である。23 と 24 はインバータで、記憶素子であるラッチ回路を形成するものである。25 は “H” または “L” を記憶する記憶ノード、26 は記憶ノード 25 の反転信号を記憶するノードである。27 は AND 回路 28 の出力により記憶ノード 25 と GND を接続するトランジスタである。

28 はカラムデコード信号 S 5、書き制御信号 S 15 及び比較データ S 12 を入力とする AND 回路である。29 はリセット信号 S 16 によりノード 26 を “L” とするトランジスタである。

**【0028】**

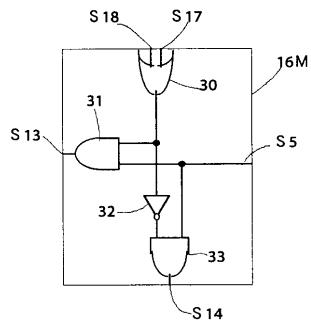

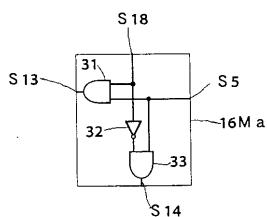

図 11 はメモリ線選択回路 16M の一実施例を示す回路図である。図 3 のビット線選択回路 16 又は図 4 のワード線選択回路 16a の回路例である。30 は記憶ノード 25 の信号 S 18 とテスト信号 S 17 を入力とする OR 回路である。31 はカラムデコード信号 S 5 と OR 回路 30 の出力を入力とし、ビット線を選択するカラム選択信号 S 13 を出力する AND 回路である。32 はインバータ、33 はカラムデコード信号 S 5 とインバータ 32 の出力を入力とし、冗長ビット線選択信号 S 14 を出力する AND 回路である。

**【0029】**

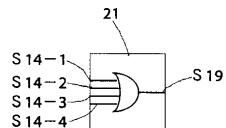

図 12 は図 3 の冗長ビット線選択回路 21 の回路図である。これはビット線選択回路 16-1 ~ 16-4 の出力信号 S 14-1 ~ S 14-4 を入力としその出力信号 S 19 を冗長ビット線トランスマルチплексор 9 に入力する OR 回路である。

**【0030】**

次に実施の形態 1 の半導体記憶装置の動作を説明する。

まずメモリセル 1-11 ~ 1-44 へのデータの書き込みの動作を説明する。

データ線 12 よりライトアンプ 13 を介して外部回路より I/O 線 4 に書き込みデータ S 8 を入力する。

次にカラムデコード信号 S 5-1 ~ S 5-4 に基づき所定のトランスマルチплексорを導通させてビット線を選択し、又図示しないローデコード信号に基づきワード線 2-1 ~ 2-4 の一つを選択して所定のメモリセルにデータ S 8 を書き込む。以下順次全てのメモリセル 1-11 ~ 1-44 について繰り返す。ここでそれぞれのメモリセルの書き時データは図示しない外部のテスト回路に保持しておく。

10

20

30

40

50

**【0031】**

次に各ビット線に接続されたメモリセル1-11～1-44の故障の有無を検査する動作について説明する。

書込時と同様にして、コラムデコード信号、ロウデコード信号に基づき所定のビット線を選択し、ワード線2-1～2-4を順次切り替え所定のビット線のメモリセル1-11～1-44の記憶データS11を順次読み出すことができる。次に記憶データS11と書込時データS10とを比較回路14に入力し比較する。ここでメモリセルの記憶データはビット線3-1～3-4、I/O線4、センスアンプ17を介して比較回路14に入力される。また書込時データS10は外部のテスト回路から入力される。

比較回路14において、記憶データS11が書込時データS10と異なるときはメモリセルに故障ありと判別される。比較回路14は図9に示すようにXOR回路であり、記憶データS11と書込時データS10とが一致するときは比較データS12として“L”を出力し、不一致ならば“H”を出力する。10

**【0032】**

比較データS12は、対応するビット線ごとに設けられたそれぞれのビット線故障記憶回路15-1～15-4に記憶される。

次に図10に示すビット線故障記憶回路の動作について説明する。メモリセルの故障テストを行う前に、まずリセット信号S16として“H”を入力して各ビット線故障記憶回路15-1～15-4の記憶データを初期化する。すなわち記憶ノード25の初期値を“H”とする。次に所定のビット線を選択するカラムデコード信号S5、ビット線故障記憶回路15-1～15-4を書き込み可能とする書込制御信号S15をそれぞれ“H”とする。20

**【0033】**

比較データS12を入力することにより記憶ノード25にビット線の故障の有無が記憶される。例えばメモリセル1-22を選択したとき、メモリセル1-22が正常であれば比較データS12は“L”が入力されるので、記憶ノード25の電位は変化せず、故障があれば記憶ノード25に“L”が記憶される。

メモリセルのテスト動作は冗長メモリセルを有する半導体記憶装置の電源投入後少なくとも1回行われる。

**【0034】**

次にビット線故障記憶回路15-1～15-4の出力に基づきビット線選択回路16はビット線に故障のない場合は正規のビット線を選択し、ビット線3-1～3-4に故障のある場合は故障ビット線に替えて冗長ビット線7を選択する。30

**【0035】**

図11に示すビット線選択回路16において、メモリセルの故障テスト中はテスト信号S17を“H”とする。このときOR回路30の出力は記憶ノード25のデータS18に関わらず“H”であるので、インバータ32の出力は“L”、AND回路33の出力S14は“L”である。AND回路31の入力の一方は“H”であるので、カラム選択信号S13はカラムデコード信号S5がそのまま出力される。

**【0036】**

図11において、カラムデコード信号S5が“L”であって、このビット線が選択されない場合は、ビット線選択回路16の出力のカラム選択信号S13及び冗長線選択信号S14は常時“L”となる。40

このビット線を選択し、カラムデコード信号S5を“H”としたとき、テスト信号S17は“H”、カラム選択信号S13は“H”、又冗長線選択信号S14は“L”であるので、正規のビット線が選択される。

**【0037】**

メモリセルの故障テスト終了後の通常使用状態において、テスト信号S17は“L”、カラムデコード信号は“H”であるので、ビット線故障記憶回路15-1～15-4の出力信号S18の入力があると、所定のビット線に故障がない場合S18は“H”で、カラム選択信号S13は“H”、冗長線選択信号S14は“L”が出力される。又所定のビット

10

20

30

40

50

線に故障がある場合 S 1 8 は “ L ” で、カラム選択信号 S 1 3 は “ H ” 、冗長線選択信号 S 1 4 は “ H ” が出力される。

#### 【 0 0 3 8 】

ビット線が正常な場合は、カラム選択信号 S 1 3 により所定のビット線トランスファゲート 8 - 1 ~ 8 - 4 が ON し、所定のビット線 3 - 1 ~ 3 - 4 と I / O 線 4 とが接続される。

所定のビット線に故障がある場合は、冗長線選択信号 S 1 4 - 1 ~ S 1 4 - 4 のうち故障があるビット線に対応するものが図 12 の OR 回路で選択され冗長線トランスファゲート 9 を導通して冗長ビット線 7 と I / O 線 4 を接続する。

#### 【 0 0 3 9 】

以上のようにビット線ごとにビット線故障記憶回路を設けたので、ヒューズを用いることなく、また、レーザー装置も用いることなく、故障しているメモリセルが接続された故障ビット線を冗長ビット線に置き替えることが出来、レーザー装置の購入、保守等に掛かるコストを削減することが出来る。

#### 【 0 0 4 0 】

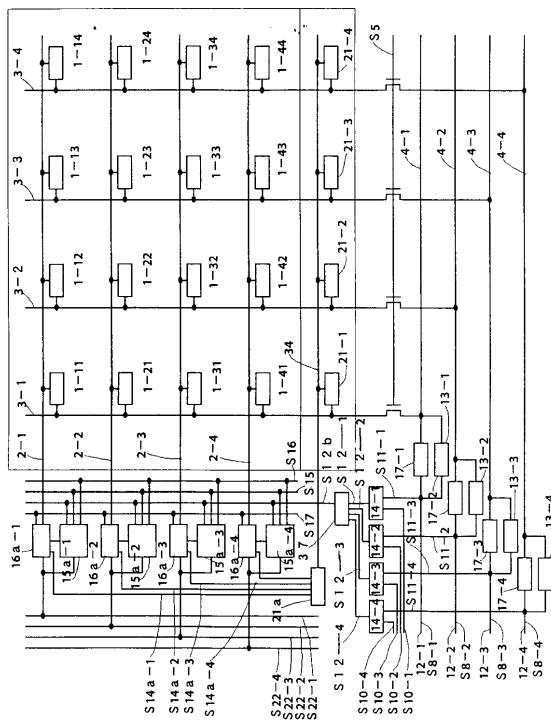

実施の形態 2 .

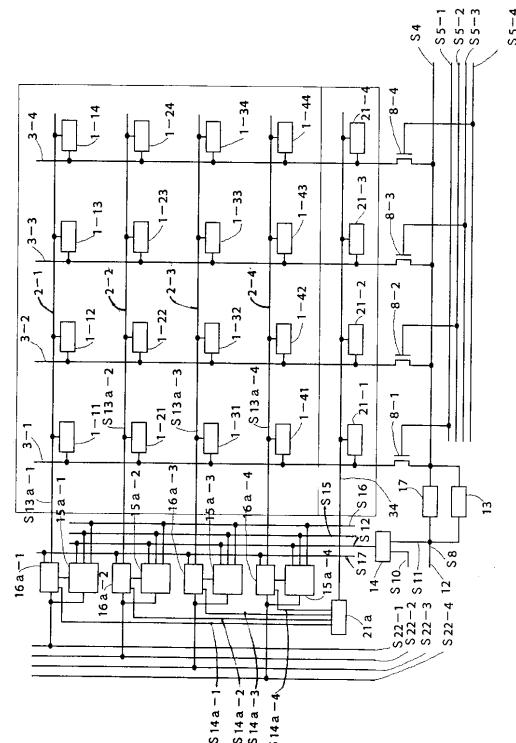

図 4 は実施の形態 2 の半導体記憶装置の回路図である。図 4 において、2 1 - 1 ~ 2 1 - 4 は冗長メモリセルであって、メモリセル 1 - 1 1 ~ 1 - 4 4 に置き換えるものである。3 4 は冗長メモリ線である冗長ワード線であって、冗長メモリセル 2 1 - 1 ~ 2 1 - 4 が接続された配線である。S 2 2 - 1 ~ S 2 2 - 4 はロウデコード信号であって、ワード線を選択する信号である。

#### 【 0 0 4 1 】

1 5 a - 1 ~ 1 5 a - 4 はワード線ごとに設けられたワード線故障記憶回路であって、比較データ S 1 2 を記憶するものである。1 6 a - 1 ~ 1 6 a - 4 はワード線ごとに設けられたワード線選択回路であって、ワード線故障記憶回路 1 5 a - 1 ~ 1 5 a - 4 の記憶データに基づき所定のワード線のメモリセルを選択する信号 S 1 3 a - 1 ~ S 1 3 a - 4 又は冗長ワード線を選択する信号 S 1 4 a - 1 ~ S 1 4 a - 4 を出力するものである。

2 1 a は冗長ワード線選択回路であって、冗長ワード線の選択信号 S 1 4 a - 1 ~ S 1 4 a - 4 に基づき、冗長ワード線 3 4 を選択するものである。

その他の符号は図 3 のものと同じものである。

#### 【 0 0 4 2 】

次に実施の形態 2 の半導体記憶装置の動作を説明する。まずメモリセル 1 - 1 1 ~ 1 - 4 4 へのデータの書き込みの動作は実施の形態 1 と同じである。

次に各ワード線 2 - 1 ~ 2 - 4 に接続されたメモリセル 1 - 1 1 ~ 1 - 4 4 の故障の有無の検査の動作について説明する。

書き込み時と同様にして、ロウデコード信号 S 2 2 - 1 ~ S 2 2 - 4 により所定のワード線を選択し、ビット線 3 - 1 ~ 3 - 4 を順次切り替えることにより所定のワード線に接続されているメモリセル 1 - 1 1 ~ 1 - 4 4 に記憶されていた記憶データ S 1 1 を順次読み出すことができる。

#### 【 0 0 4 3 】

比較回路 1 4 によるメモリセルの故障の検査は実施の形態 1 と同様のものである。比較回路 1 4 の比較データ S 1 2 は、対応するワード線ごとに設けられたワード線故障記憶回路 1 5 a - 1 ~ 1 5 a - 4 に記憶される。

次にワード線故障記憶回路 1 5 a - 1 ~ 1 5 a - 4 の出力に基づきワード線選択回路 1 6 a - 1 ~ 1 6 a - 4 によりワード線 2 - 1 ~ 2 - 4 に故障のない場合は正規のワード線が選択され、ワード 2 - 1 ~ 2 - 4 に故障のある場合は故障ワード線に替えて冗長ワード線 3 4 を選択する信号が出力される。

その他の回路の動作は実施の形態 1 のものと同じである。

#### 【 0 0 4 4 】

以上のようにワード線ごとにワード線故障記憶回路を設けたので、ヒューズを用いること

10

20

30

40

50

なく、また、レーザー装置も用いることなく、故障しているメモリセルが接続された故障ワード線を冗長ワード線に置き替えることが出来、レーザー装置の購入、保守等に掛かるコストを削減することが出来る。

#### 【0045】

実施の形態3.

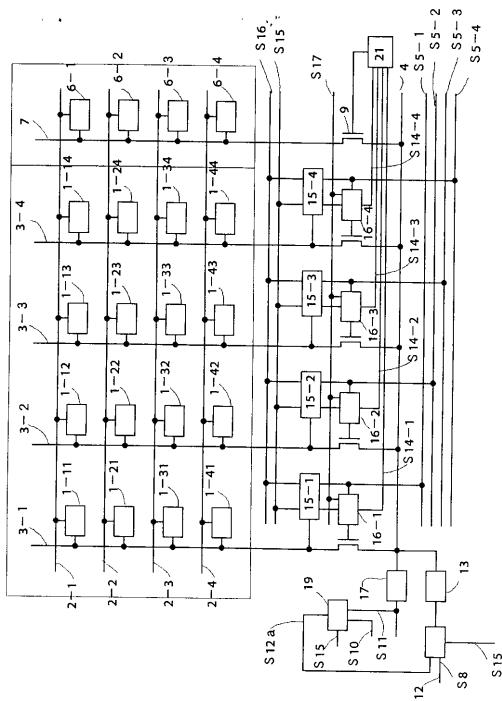

図5は実施の形態3の半導体記憶装置の回路図である。この回路は、実施の形態1において、複数のビット線に接続されたメモリセルへのデータの書き込みをワード線ごとに複数のビット線に同時にデータの書き込みを可能とし、又複数のビット線のメモリセルの故障の検査を複数のビット線同時に検査可能とするものである。又故障の検査結果は各ビット線ごとに設けられたビット線故障記憶回路15-1~15-4に格納させるものである。 10

#### 【0046】

12-1~12-4は複数個のデータ線であって、ビット線3-1~3-4のメモリセルに同時に書き込みを可能とする並列に設けられたものである。

17-1~17-4及び13-1~13-4はそれぞれのデータ線12-1から12-4に設けられたセンスアンプ及びライトアンプである。4-1~4-4は複数個のI/O線であって、データ線12-1~12-4に対応するものである。14-1~14-4は、複数個の比較回路であって、ビット線3-1~3-4の数に対応して並列に設けられたものである。

#### 【0047】

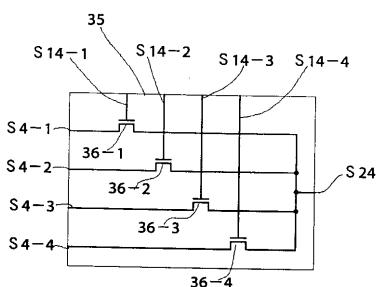

35はI/O線選択回路であって、ビット線選択回路16-1~16-4の出力に基づき、I/O線4-1~4-4のいずれかと冗長線7を接続するもので、図13に示す回路である。S10-1~S10-4は並列的に書き込んだメモリセルへの書き込み時データである。S5はカラムデコード信号である。 20

S11-1~S11-4はビット線3-1~3-3に接続されたメモリセルの記憶データである。S12-1~S12-4はそれぞれ比較回路14-1~14-4の出力信号である比較データである。

その他の符号は図3及び図4のものと同じものである。

#### 【0048】

図13は図5におけるI/O線選択回路35の回路例である。ビット線選択回路16-1~16-4の出力S14-1~S14-4の何れかが“H”的時、対応するI/O線4-1~4-4と冗長ビット線7を接続するものである。 30

例えば、信号S14-2が“H”でその他の信号S14-1、S14-3、S14-4が“L”的時、トランジスタ36-2のみがONし、I/O線4-2がトランスファゲート36-2を介して冗長ビット線7と接続される。

#### 【0049】

次に実施の形態3の半導体記憶装置の動作を説明する。

まずメモリセル1-11~1-44へのデータの書き込みの動作を説明する。

データ線12-1~12-4よりライトアンプ13-1~13-4を介して外部回路よりI/O線4-1~4-4に書き込みデータS8-1~S8-4を入力する。

次にカラムデコード信号S5に基づき複数個のビット線3-1~3-4を同時に選択し、又図示しないローデコード信号に基づきワード線2-1~2-4の一つを選択し、選択したワード線に接続されたメモリセルに同時にデータS8-1~S8-4を書き込む。以下順次ワード線を切り替えて繰り返す。 40

#### 【0050】

次に各ビット線3-1~3-4に接続されたメモリセル1-11~1-44の故障の有無を検査する動作について説明する。

書き込み動作の時と同様にして、カラムデコード信号S5及びロウデコード信号に基づきメモリセル1-11~1-44の記憶データS11-1~S11-4を読み出す。

次に比較回路14-1~14-4により複数個のビット線に対応するメモリセルの記憶データS11-1~S11-4とメモリセルの書き込み時データS10-1~S10-4を同時 50

に比較して比較データ S 12-1 ~ S 12-4 を同時に出力する。

比較データ S 12-1 ~ S 12-4 は、対応するビット線ごとにそれぞれビット線故障記憶回路 15-1 ~ 15-4 に同時に記憶される。

#### 【0051】

所定のビット線のメモリセルが正常な場合は、正規のビット線 3-1 ~ 3-4 と I/O 線 4-1 ~ 4-4 とが接続される。又所定のビット線に故障の有る場合は、冗長ビット線 7 と接続される。

#### 【0052】

以上のように複数のビット線への複数の入力回路と、複数のビット線に対応する複数の比較回路を設けたので、高速に故障ビット線を冗長ビット線に置き換えることができる。 10

#### 【0053】

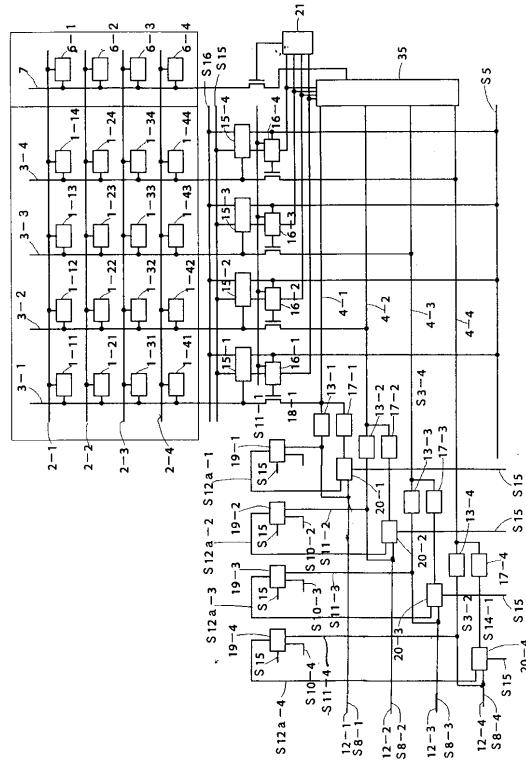

実施の形態 4.

図 6 は実施の形態 4 の半導体記憶装置の回路図である。この回路は、実施の形態 2 において、複数個のビット線に対応するメモリセルへのデータの書き込みをワード線ごとに同時に可能とし、又複数個のビット線のメモリセルの故障の検査をワード線単位で同時に可能とするものである。

37 は OR 回路であって、比較回路 14-1 ~ 14-4 の比較データ S 12-1 ~ S 12-4 に基づきワード線比較データ S 12 b を出力するものである。その他の符号は図 3 ~ 図 5 のものと同じものである。

#### 【0054】

次に実施の形態 4 の半導体記憶装置の動作を説明する。 20

まずメモリセル 1-11 ~ 1-4 4 へのデータの書き込みの動作は実施の形態 3 のものと同じである。

次に各ビット線 3-1 ~ 3-4 のメモリセル 1-11 ~ 1-4 4 の故障の検査の動作について説明する。書き込み動作と同様にして、カラムデコード信号 S 5 とロウデコード信号によりメモリセル 1-11 ~ 1-4 4 の記憶データ S 11-1 ~ S 11-4 を読み出す。

#### 【0055】

次に比較回路 14-1 ~ 14-4 によりメモリセルの記憶データ S 11-1 ~ S 11-4 とメモリセルへの書き込みデータ S 10-1 ~ S 10-4 を複数ビット線に対して同時に比較して比較データ S 12-1 ~ S 12-4 を複数ビット線に対して同時に出力する。比較データ S 12-1 ~ S 12-4 に基づき、OR 回路 37 からワード線比較データ S 12 b が出力され、対応するワード線ごとに設けられたワード線故障記憶回路 15a-1 ~ 15a-4 に順次記憶される。 30

以下、所定のワード線のメモリセルに故障の有る場合の冗長ワード線 34 への置き換えの動作は実施の形態 2 のものと同じである。

#### 【0056】

以上のように複数のビット線への複数の入力回路と、複数のビット線に対応する複数の比較回路を設けたので、高速に故障ワード線を冗長ワード線に置き換えることができる。

#### 【0057】

実施の形態 5.

図 7 は実施の形態 5 の半導体記憶装置の回路図である。この回路は、実施の形態 1 において、比較回路 14 とビット線故障記憶回路を結ぶ専用の配線に要する配線面積を削減するためのものである。 40

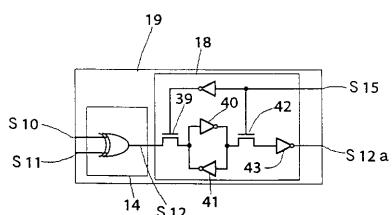

19 は比較レジスタであって、比較回路 14 にラッチ回路 18 を設けたもので、比較回路 14 の比較データ S 12 を書き込み制御信号 S 15 が入るまで一時保持するものである。 S 12 a は比較保持データで比較レジスタ 19 の出力信号である。

20 は入力切替器で、書き込み制御信号 S 15 により外部データ S 8 と 比較保持データ S 12 a とを選択的に切替えるものである。

#### 【0058】

図 14 は比較レジスタ 19 の一実施例を示す回路図である。 18 はラッチ回路であって、

40、41はラッチを形成するインバータ、39、42は書込制御信号S15により比較回路14の出力信号S12をラッチに入力し、或いはラッチから比較保持データS12aを出力するスイッチである。

その他の符号は図3のものと同じものである。

#### 【0059】

次に実施の形態5の動作を説明する。

図7において、メモリセル1-11~1-44へのデータ書き込みの動作は実施の形態1と同じである。

又メモリセル1-11~1-44の故障の検査の動作も比較レジスタ19の比較回路14で比較するところまで実施の形態1と同じである。比較データS12は図14に示すラッチ回路18に一時保持される。

10

#### 【0060】

次に一時保持されていた比較レジスタ19の比較保持データS12aは、書込制御信号S15により出力され又書込制御信号S15に同期して入力切替器20を切替えI/O線4に入力される。

比較保持データS12aは、I/O線4を介してビット線故障記憶回路15-1~15-4に記憶される。

それ以降の故障ビット線を冗長ビット線への置き換えの動作は実施の形態1と同じである。

。

#### 【0061】

以上のように比較レジスタを設けたので、比較レジスタ19の比較保持データS12aの出力はI/O線4を介してビット線故障記憶回路15-1~15-4に記憶されるので、比較回路レジスタ19からビット線故障記憶回路15-1~15-4への専用の配線を必要とせずチップ面積を削減することができる。

20

#### 【0062】

実施の形態6.

図8は実施の形態6の半導体記憶装置の回路図である。この半導体記憶装置は実施の形態5において複数のビット線から同時にデータの入出力を可能とするものである。

19-1~19-4は、複数個の比較レジスタであって、同時に出入力するビット線3-1~3-4の数に対応して複数個並列に設けられたものである。

30

20-1~20-4は複数個の入力切替器で、外部データS8-1~S8-4と比較保持データS12a-1~S12-4を切り替えるものである。

その他の符号は図3~図7のものと同じものである。

#### 【0063】

次に実施の形態6の動作を説明する。

図8において、メモリセル1-11~1-44へのデータ書き込みの動作は実施の形態1と同じである。又メモリセル1-11~1-44の故障の有無の検査の動作は実施の形態5と同じである。

#### 【0064】

次に複数のビット線に対応する比較保持データS12a-1~S12a-4は、書込制御信号S15に基づき同時に出力されこの書込制御信号S15に同期して複数のビット線に対応する入力切替器20-1~20-4を比較保持データS12a-1~S12a-4側に切替えてそれぞれI/O線4-1~4-4に入力される。

40

比較保持データS12a-1~S12a-4はI/O線4-1~4-4を介して同時にそれぞれ対応するビット線故障記憶回路15-1~15-4に記憶される。

それ以降の故障ビット線を冗長ビット線への切り替えの動作は実施の形態1と同じである。

。

#### 【0065】

以上のように複数のビット線に対応して複数個の比較レジスタを設けたので、比較保持データS12a-1~S12a-4はI/O線4を介して同時にビット線故障記憶回路15

50

-1～15-4に記憶されるので、高速に故障ビット線を冗長ビット線への置き換えが可能であると共に、比較レジスタ19-1～19-4からビット線故障記憶回路15-1～15-4への専用の配線を必要とせずチップ面積を削減することができる。

#### 【0066】

実施の形態7.

図15は実施の形態1～6におけるメモリ線選択回路16Mの他の実施例16Maであって、図11の回路からOR回路30とテスト信号S17を省略したものである。

#### 【0067】

次に図15のビット線選択回路16Maを用いた場合の故障ビット線を冗長ビット線への置き換えの動作を説明する。この回路によれば、メモリセルの故障テストの途中であっても、故障したメモリセルが見つかり次第ビット線故障記憶回路15-1～15-4の記憶ノード25に“L”が記憶されるので、即座に故障ビット線は冗長ビット線7に置換される。

しかし、ビット線に故障メモリセルが1つでもあれば故障ビット線は冗長ビット線に置換されてしまうのでそれ以降のテストは不要となる。よってテスト信号を省略することができる。

#### 【0068】

このようにビット線選択回路16からインバータとテスト信号入力のための配線を省略したので、さらにチップ面積を削減することができる。

#### 【0069】

実施の形態8.

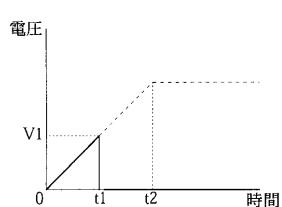

図16は実施の形態8のパワーオンリセットの動作を説明する図である。図2～8のリセット信号S16として図16に示す電源投入と共に所定の電圧レベルが得られるパワーオンリセット回路を設けて半導体記憶装置の簡単化をすることができる。

#### 【0070】

#### 【発明の効果】

この発明の請求項1に記載の半導体記憶装置は、メモリ線の故障の有無を記憶するメモリ線故障記憶回路をメモリ線ごとに備えたので、高価なレーザ装置を用いることなく、製造コストを増加することなく故障メモリセルを冗長メモリセルに置替えができる。さらに、比較回路を比較レジスタとしたので、比較データをメモリ線故障記憶回路に書込む専用配線が不要となり、チップ面積を小さくすることができる。

#### 【0071】

この発明の請求項2に記載の半導体記憶装置は、複数個のメモリ線に並列にデータの入力が可能な複数個のデータ線と、複数個のメモリ線に対応して複数個の比較レジスタを設けたので、チップ面積を小さくすると共に、故障メモリセルの冗長メモリセルへの置換を高速化することができる。

#### 【図面の簡単な説明】

【図1】 第1の発明の構成を示すブロック図である。

【図2】 第2の発明の構成を示すブロック図である。

【図3】 実施の形態1の半導体記憶装置の回路図である。

【図4】 実施の形態2の半導体記憶装置の回路図である。

【図5】 実施の形態3の半導体記憶装置の回路図である。

【図6】 実施の形態4の半導体記憶装置の回路図である。

【図7】 実施の形態5の半導体記憶装置の回路図である。

【図8】 実施の形態6の半導体記憶装置の回路図である。

【図9】 比較回路14の一実施例を示す回路図である。

【図10】 メモリ線故障記憶回路の一実施例を示す回路図である。

【図11】 メモリ線選択回路の一実施例を示す回路図である。

【図12】 冗長ビット線選択回路21の一実施例を示す回路図である。

【図13】 I/O線選択回路の一実施例を示す回路図である。

10

20

30

40

50

【図14】 比較レジスタ19の一実施例を示す回路図である。

【図15】 メモリ線選択回路の他の実施例を示す回路図である。

【図16】 実施の形態8のパワーオンリセットの動作を説明する図である。

【図17】 従来の半導体記憶装置の回路図である。

【符号の説明】

1-11~1-44 メモリセル、

2-1~2-4 ワード線

3M メモリ線、

3-1~3-4 ビット線、

4、4-1~4-4 I/O線、

6-1~6-4 冗長メモリセル、

7M 冗長メモリ線、

7 冗長ビット線、

12、12-1~12-4 データ線、

13、13-1~13-4 ライトアンプ、

14 比較回路、

15M メモリ線故障記憶回路、

15-1~15-4 ビット線故障記憶回路、

15a-1~15a-4 ワード線故障記憶回路、

16M メモリ線選択回路、

16-1~16-4 ビット線選択回路、

16a-1~16a-4 ワード線選択回路、

17、17-1~17-4 センスアンプ、

18 ラッチ回路、

19 比較レジスタ、

20 入力切替器、

21 冗長ビット線選択回路、

34 冗長ワード線、

35 I/O線選択回路

10

20

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特開昭52-055333(JP,A)

特開平08-335399(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 29/00