# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

#01L 23/525 (2006.01) #01L 23/00 (2006.01)

H01L 23/31 (2006.01) H01L 23/498 (2006.01)

(52) CPC특허분류 *H01L 23/525* (2013.01) *H01L 23/31* (2013.01)

(21) 출원번호 **10-2019-0084554**

(22) 출원일자 **2019년07월12일**

심사청구일자 **없음**

(11) 공개번호 10-2021-0007692

(43) 공개일자 2021년01월20일

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

김동호

경기도 화성시 삼성전자로 1 삼성전자(주)화성사 업장

(74) 대리인 **하영욱**

전체 청구항 수 : 총 20 항

#### (54) 발명의 명칭 재배선 충을 포함하는 반도체 패키지 및 이를 제조하기 위한 방법

## (57) 요 약

본 개시의 일 실시예는 반도체 패키지를 개시한다. 상기 반도체 패키지는, 재배선 충(redistributed layer; RDL); 상기 재배선 충과 전기적으로 연결되고, 상기 재배선 충의 상면에 배치되는 반도체 칩; 상기 재배선 충과 전기적으로 연결되고, 상기 재배선 충의 상면에서 상기 반도체 칩의 주변에 배치되는 복수의 솔더 볼(solder ball)들; 상기 복수의 솔더 볼들과 전기적으로 연결되고, 상기 복수의 솔더 볼들의 상면에 배치되는 인터포저 (interposer); 상기 인터포저의 하단에서 상기 반도체 칩, 상기 재배선 충의 상면 및 측면을 인캡슐레이션 (encapsulation)하는 인캡슐란트(encapsulant) 충; 및 상기 인터포저의 하면 및 상기 인캡슐란트 충의 상면 사이의 빈 공간을 메우는 언더필(underfill) 충;을 포함하고, 상기 인캡슐란트 충은 상기 재배선 충의 측면을 둘러 싸는 측면 인캡슐란트 영역을 포함한다.

# 대표도

# (52) CPC특허분류

**H01L 23/49816** (2013.01)

**H01L 23/49838** (2013.01)

**H01L 24/06** (2013.01)

**H01L 24/97** (2013.01)

## 명 세 서

## 청구범위

## 청구항 1

재배선 층(redistributed layer; RDL);

상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에 배치되는 반도체 칩;

상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에서 상기 반도체 칩의 주변에 배치되는 복수의 솔더 볼(solder ball)들;

상기 복수의 솔더 볼들과 전기적으로 연결되고, 상기 복수의 솔더 볼들의 상면에 배치되는 인터포저 (interposer);

상기 인터포저의 하단에서 상기 반도체 칩 및 상기 재배선 층의 측면을 인캡슐레이션(encapsulation)하는 인캡슐란트(encapsulant) 층; 및

상기 인터포저의 하면 및 상기 인캡슐란트 층의 상면 사이를 메우는 언더필(underfill) 층;을 포함하고,

상기 인캡슐란트 층은 상기 재배선 층의 측면을 둘러싸는 측면 인캡슐란트 영역을 포함하는, 반도체 패키지.

## 청구항 2

청구항 1에 있어서,

상기 측면 인캡슐란트 영역의 수직 단면의 일측의 폭의 길이는 140μm(micrometer)인, 반도체 패키지.

#### 청구항 3

청구항 1에 있어서,

상기 재배선 층의 수직 단면의 높이는 60 µm인, 반도체 패키지.

# 청구항 4

청구항 1에 있어서,

상기 재배선 층은 코어(core) 층을 제외한 복수의 유전(dielectric)층들을 포함하는, 반도체 패키지.

#### 청구항 5

청구항 4에 있어서,

상기 복수의 유전층들은 제1 내지 제4 재배선 층을 포함하고,

상기 제1 내지 제4 재배선 층의 각각의 수직 단면의 높이는 15 µm인, 반도체 패키지.

## 청구항 6

청구항 1에 있어서,

상기 반도체 칩은 상기 반도체 칩의 하면에 배치되는 연결부를 통해 상기 재배선 충과 전기적으로 연결되는, 반도체 패키지.

## 청구항 7

청구항 6에 있어서,

상기 연결부는, 상기 재배선 층과 전기적으로 연결되는 솔더 범프(b $\mu$ mp) 또는 금속 패드(metal pad)를 포함하는, 반도체 패키지.

#### 청구항 8

청구항 1에 있어서,

상기 재배선 층의 상면의 가로 길이는 10mm(millimeter) 내지 14mm이고, 세로 길이는 10mm 내지 14mm인, 반도체패키지.

## 청구항 9

청구항 1에 있어서,

상기 인캡슐란트 층의 수직 단면의 높이는 180 µm인, 반도체 패키지.

# 청구항 10

청구항 1에 있어서,

상기 인터포저의 상면부터 상기 반도체 칩의 상면까지의 높이는 140μm인, 반도체 패키지.

#### 청구항 11

청구항 1에 있어서,

상기 반도체 칩의 상면의 가로 길이는 7mm 내지 11mm이고, 세로 길이는 7mm 내지 11mm인, 반도체 패키지.

#### 청구항 12

재배선 층(redistributed layer; RDL);

상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에 배치되는 반도체 칩;

상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에 배치되는 복수의 내부 솔더 볼(solder ball)들;

상기 복수의 내부 솔더 볼들과 전기적으로 연결되고, 상기 복수의 내부 솔더 볼들의 상면에 배치되는 인터포저 (interposer);

상기 인터포저의 하단에서 상기 반도체 칩, 상기 재배선 층의 측면 및 하면을 인캡슐레이션(encapsulation)하는 인캡슐란트(encapsulant) 층; 및

상기 인터포저의 하면 및 상기 인캡슐란트 층의 상면 사이를 메우는 언더필(underfill) 층;을 포함하고,

상기 인캡슐란트 층은, 상기 재배선 층의 측면을 둘러싸는 측면 인캡슐란트 영역, 및 상기 재배선 층의 하면을 덮는 하면 인캡슐란트 영역을 포함하는, 반도체 패키지.

## 청구항 13

청구항 12에 있어서,

상기 하면 인캡슐란트 영역의 수직 단면의 높이는 50 µm인, 반도체 패키지.

## 청구항 14

청구항 12에 있어서,

상기 하면 인캡슐란트 영역은 복수의 외부 솔더 볼들을 배치하기 위한 외부 솔더 볼 영역을 포함하는, 반도체패키지.

# 청구항 15

청구항 14에 있어서,

상기 외부 솔더 볼 영역은 복수의 원형 구멍들을 포함하는, 반도체 패키지.

## 청구항 16

청구항 15에 있어서,

상기 복수의 원형 구멍들의 각각은 상기 하면 인캡슐란트 영역의 상면에 형성되는 상측 원, 및 상기 하면 인캡슐란트 영역의 하면에 형성되는 하측 원을 포함하는, 반도체 패키지.

#### 청구항 17

청구항 16에 있어서,

상기 하측 원의 지름의 길이는 상기 상측 원의 지름의 길이 보다 큰, 반도체 패키지.

#### 청구항 18

청구항 16에 있어서,

상기 상측 원의 지름의 길이는 300 µm인, 반도체 패키지.

#### 청구항 19

청구항 16에 있어서,

상기 하측 원의 지름의 길이는 360 µm인, 반도체 패키지.

#### 청구항 20

실리콘(silicon) 웨이퍼(wafer) 층(layer), 상기 실리콘 웨이퍼 층의 상면(upper side)에 형성되는 재배선 층, 및 복수의 내부(inner) 솔더 볼(solder ball)들을 포함하는 반도체(semiconductor) 다이(die)를 캐리어 (carrier) 스트립(strip) 기판(substrate)에 부착(attaching)하고;

상기 캐리어 스트립 기판의 상면, 상기 실리콘 웨이퍼 층의 측면(side), 상기 재배선 층의 측면 및 상면, 및 상기 반도체 다이의 측면을 인캡슐레이션하여 인캡슐란트 층을 형성하고;

상기 복수의 내부 솔더 볼들의 상면에 인터포저 충을 배치하고; 상기 인캡슐란트 충의 상부 및 상기 인터포저 충의 하부를 언더필 수지를 이용하여 메우고;

상기 캐리어 스트립 기판 및 상기 실리콘 웨이퍼 층을 그라인딩하고;

상기 캐리어 스트립 기판 및 상기 실리콘 웨이퍼 층을 그라인당하여 노출된 상기 재배선 층의 하면에 복수의 외부 솔더 볼들을 배치하고,

상기 인캡슐란트 층이 상기 재배선 층의 측면을 둘러싸도록 절단(sawing)하는, 반도체 패키지를 제조하는 방법.

## 발명의 설명

# 기 술 분 야

[0001] 본 개시는 재배선 층을 포함하는 반도체 패키지 및 이를 제조하기 위한 방법에 관한 것이다.

## 배경기술

[0002] 반도체 디바이스를 생성하기 위한 웨이퍼 레벨(wafer level)의 공정은 재배선 층을 형성하는 공정을 포함할 수 있다. 상기 재배선 층은 전도성의 금속 배전라인을 포함할 수 있다. 예를 들어, 재배선 층은 미리 정해진 배열을 갖는 금속 배전라인을 포함할 수 있다. 재배선 층은 도금을 패터닝(patterning)하는 방법을 통해 실리콘 웨이퍼 상에 형성될 수 있다. 재배선 층은 외부로부터의 기계적 충격, 수분, 각종 이물질에 의해 손상될 수 있다. 재배선 층은 강도를 강화하기 위한 코어(core) 층을 포함할 수 있다. 코어 층으로 인해 재배선 층의 두께 (thickness)는 증가될 수 있다.

#### 발명의 내용

# 해결하려는 과제

[0003] 본 개시는 코어 층을 제외한 복수의 유전층들을 포함하는 재배선 층을 포함하는 반도체 패키지 및 이를 제조하

기 위한 방법을 제공하고자 한다.

## 과제의 해결 수단

- [0004] 본 개시의 일 실시예는 반도체 패키지를 개시한다. 상기 반도체 패키지는, 재배선 층(redistributed layer; RDL); 상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에 배치되는 반도체 칩; 상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에서 상기 반도체 칩의 주변에 배치되는 복수의 솔더 볼(solder ball)들; 상기 복수의 솔더 볼들과 전기적으로 연결되고, 상기 복수의 솔더 볼들의 상면에 배치되는 인터포저 (interposer); 상기 인터포저의 하단에서 상기 반도체 칩, 상기 재배선 층의 상면 및 측면을 인캡슐레이션 (encapsulation)하는 인캡슐란트(encapsulant) 층; 및 상기 인터포저의 하면 및 상기 인캡슐란트의 상면 사이의 빈 공간을 메우는 언더필(underfill) 층;을 포함한다. 상기 인캡슐란트는 상기 재배선 층의 측면을 둘러싸는 측면 인캡슐란트 영역을 포함한다.

- [0005] 본 개시의 일 실시예는 반도체 패키지를 개시한다. 상기 반도체 패키지는, 재배선 층; 상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에 배치되는 반도체 칩; 상기 재배선 층과 전기적으로 연결되고, 상기 재배선 층의 상면에서 상기 반도체 칩의 주변에 배치되는 복수의 내부 솔더 볼들; 상기 복수의 내부 솔더 볼들과 전기적으로 연결되고, 상기 복수의 내부 솔더 볼들의 상면에 배치되는 인터포저; 상기 인터포저의 하단에서 상기 반도체 칩, 상기 재배선 층의 측면 및 하면을 인캡슐레이션하는 인캡슐란트 층; 및 상기 인터포저의 하면 및 상기 인캡슐란트의 상면 사이의 빈 공간을 메우는 언더필 층;을 포함한다. 상기 인캡슐란트 층은, 상기 재배선 층의 측면을 둘러싸는 측면 인캡슐란트 영역, 및 상기 재배선 층의 하면을 덮는 하면 인캡슐란트 영역을 포함한다.

- [0006] 본 개시의 일 실시예는 반도체 패키지를 제조하기 위한 방법을 개시한다. 상기 반도체 패키지의 제조 방법은, 실리콘(silicon) 웨이퍼(wafer) 충(layer), 상기 실리콘 웨이퍼 충의 상면(upper side)에 형성되는 재배선 충, 및 복수의 내부(inner) 솔더 볼(solder ball)들을 포함하는 반도체(semiconductor) 다이(die)를 캐리어 (carrier) 스트립(strip) 기판(substrate)에 부착(attaching)하고; 상기 캐리어 스트립 기판의 상면, 상기 실리콘 웨이퍼 층의 측면(side), 상기 재배선 충의 측면 및 상면, 및 상기 반도체 다이의 측면을 인캡슐레이션하여 인캡슐란트 충을 형성하고; 상기 복수의 내부 솔더 볼들의 상면에 인터포저 충을 배치하고; 상기 인캡슐란트 충의 상부 및 상기 인터포저 충의 하부를 언더필 수지를 이용하여 메우고; 상기 캐리어 스트립 기판 및 상기 실리콘 웨이퍼 충을 그라인딩하고; 상기 캐리어 스트립 기판 및 상기 실리콘 웨이퍼 충을 그라인딩하여 노출된 상기 재배선 충의 하면에 복수의 외부 솔더 볼들을 배치하고, 상기 인캡슐란트 층이 상기 재배선 층의 측면을 둘러싸도록 절단(sawing)한다.

# 발명의 효과

- [0007] 본 개시에 따르면, 반도체 패키지 및 이를 제조하기 위한 방법을 통해, 반도체 패키지의 전체 두께를 감소시킬 수 있다.

- [0008] 본 개시에 따르면, 반도체 패키지 및 이를 제조하기 위한 방법을 통해, 반도체 패키지의 재배선 충 중 외부로 노출되는 부분을 보호함으로써, 반도체 패키지의 안정성 및 신뢰도를 증가시킬 수 있다.

- [0009] 본 개시에 따르면, 반도체 패키지 및 이를 제조하기 위한 방법을 통해, 반도체 패키지의 강도 및 내구성을 증가 시킬 수 있다.

#### 도면의 간단한 설명

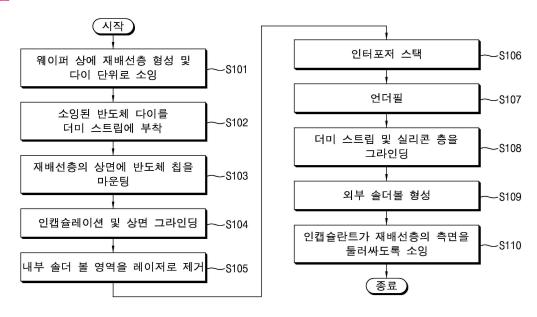

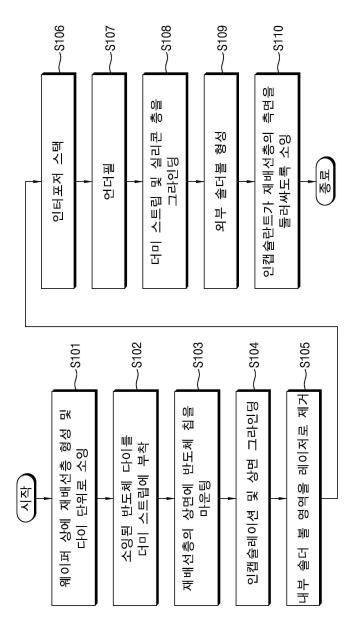

- [0010] 도 1은 본 개시의 일 실시예에 따른 반도체 패키지를 제조하기 위한 방법을 도시한 흐름도이다.

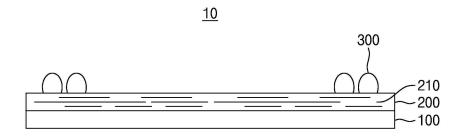

- 도 2는 본 개시의 일 실시예에 따른 실리콘 웨이퍼, 상기 실리콘 웨이퍼 상에 형성된 재배선 층, 및 상기 재배선 층 상에 형성된 솔더 볼의 단면도이다.

- 도 3은 본 개시의 일 실시예에 따른 더미(d  $\mu$  mmy) 스트립(strip), 및 상기 더미 스트립에 부착된 반도체 다이 (die)의 단면도이다.

- 도 4는 본 개시의 일 실시예에 따른 더미 스트립, 및 상기 더미 스트립에 부착된 반도체 다이의 개념도이다.

- 도 5는 본 개시의 일 실시예에 따른 더미 스트립, 상기 더미 스트립 상에 부착된 반도체 다이, 및 상기 다이 상에 실장(mounting)된 반도체 칩의 단면도이다.

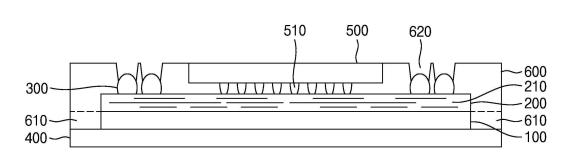

도 6은 본 개시의 일 실시에에 따른 더미 스트립 상에 부착된 반도체 다이, 및 상기 반도체 다이 상에 실장된 반도체 칩을 인캡슐레이션한 반도체 패키지의 단면도이다.

도 7은 본 개시의 일 실시예에 따른 내부 솔더 볼 영역이 제거된 인캡슐란트 층을 포함하는 반도체 패키지의 단면도이다.

도 8은 본 개시의 일 실시예에 따른 인터포저를 포함하는 반도체 패키지의 단면도이다.

도 9는 본 개시의 일 실시예에 따른 언더 필(under fill) 층을 포함하는 반도체 패키지의 단면도이다.

도 10은 본 개시의 일 실시예에 따른 실리콘 웨이퍼 및 더미 스트립이 제거된 반도체 패키지의 단면도이다.

도 11은 본 개시의 일 실시예에 따른 복수의 외부 솔더 볼들을 포함하는 반도체 패키지의 단면도이다.

도 12는 본 개시의 일 실시예에 따른 반도체 칩의 상면도이다.

도 13은 본 개시의 일 실시예에 따른 재배선 층의 단면도이다.

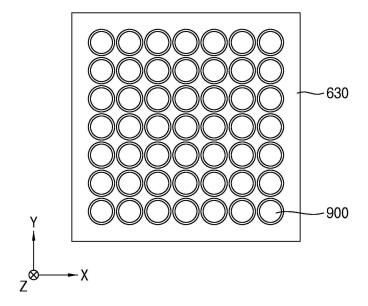

도 14는 본 개시의 일 실시예에 따른 반도체 패키지의 하면도이다.

도 15는 본 개시의 일 실시예에 따른 반도체 패키지를 제조하기 위한 방법을 도시한 흐름도이다.

도 16은 본 개시의 일 실시예에 따른 하면 인캡슐란트 층을 포함하는 반도체 패키지의 단면도이다.

도 17은 본 개시의 일 실시예에 따른 외부 솔더 볼 영역을 포함하는 하면 인캡슐란트 층을 포함하는 반도체 패키지의 단면도이다.

도 18는 본 개시의 일 실시예에 따른 하면 인캡슐란트 층 및 복수의 외부 솔더 볼들을 포함하는 반도체 패키지의 단면도이다.

도 19는 본 개시의 일 실시예에 따른 반도체 패키지의 하면도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0011] 도 1은 본 개시의 일 실시예에 따른 반도체 패키지를 제조하기 위한 방법을 도시한 흐름도이다.

- [0012] 도 1을 참고하면, 실리콘 웨이퍼 상에는 재배선 층이 형성될 수 있다. 재배선 층이 형성된 실리콘 웨이퍼는 다이(die) 단위로 소잉(sawing)될 수 있다(S101).

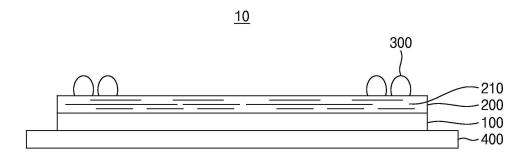

- [0013] 예를 들어, 도 2를 참고하면, 실리콘 웨이퍼(100) 상에는 재배선 층(200)이 형성될 수 있다.

- [0014] 재배선 층(200)은 유전(dielectric)층을 포함할 수 있다. 재배선 층(200)의 내부에는 전도성의 금속 배전 라인 (210)이 형성될 수 있다. 예를 들어, 금속 배전 라인(210)은 미리 정해진 패턴(pattern)을 가질 수 있다. 재배선 층(200)은 패터닝(patterning) 방식으로 형성된 금속 배전 라인(210)을 포함할 수 있다. 재배선 층(200)의 상면에는 인터포저(interposer)와 재배선 층(200)을 전기적으로 연결하기 위한 복수의 솔더 볼(solder ball)들 (300)이 배치될 수 있다. 복수의 솔더 볼들(300)은 복수의 내부 솔더 볼들이라 지칭될 수 있다. 복수의 내부 솔더 볼들(300)은 재배선 층(200)의 금속 배전 라인(210)과 전기적으로 연결될 수 있다. 재배선 층(200)이 형성된 실리콘 웨이퍼(100)는 다이(10) 단위로 소잉될 수 있다. 소잉된 실리콘 웨이퍼(100)는 실리콘 층이라 지칭될 수 있다.

- [0016] 다시 도 1을 참고하면, 소잉된 다이들은 더미 스트립 기판에 부착(attaching)될 수 있다(S102).

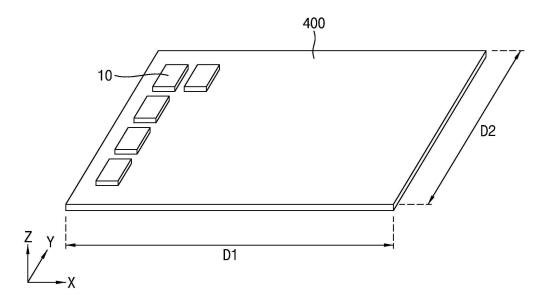

- [0017] 예를 들어, 도 3을 참고하면, 소잉된 반도체 다이(10)는 더미 스트립 기판(400) 상에 부착될 수 있다. 더미 스트립 기판(400)은 캐리어(carrier) 스트립 기판이라 지칭될 수 있다.

- [0018] 예를 들어, 도 4를 참고하면, 더미 스트립 기판(400)의 가로 길이(D1)는 210 밀리미터(millimeter; mm)일 수 있다. 더미 스트립(400)의 세로 길이(D2)는 77.5mm일 수 있다. 소잉된 복수의 반도체 다이들(10)은 미리 정해진 간격에 따라 더미 스트립 기판에 부착될 수 있다.

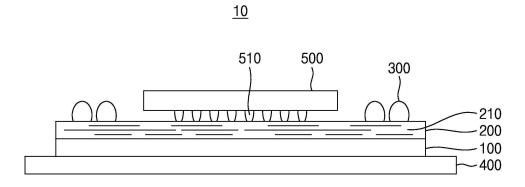

- [0020] 다시 도 1을 참고하면, 재배선 층의 상면에는 반도체 칩이 마운팅(mounting)될 수 있다(S103).

- [0021] 예를 들어, 도 5를 참고하면, 재배선 충(200)의 상면에는 반도체 칩(500)이 마운팅될 수 있다. 반도체 칩(500)의 하면에는 연결부(connection unit)(510)가 배치될 수 있다. 예를 들어, 연결부(510)는 복수의 솔더 범프(bμmp)들을 포함할 수 있다.

- [0022] 연결부(510)는 복수의 구리 필러(copper pillar)들과 복수의 솔더 범프들이 적충된 구조를 가질 수 있다. 예를 들어, 반도체 칩(500)의 하면에는 복수의 구리 필러들이 배치될 수 있다. 복수의 구리 필러들의 하면에는 복수의 솔더 범프들이 배치될 수 있다. 복수의 구리 필러들 및 복수의 솔더 범프들은 전기적으로 연결될 수 있다. 복수의 솔더 범프들은 재배선 충과 전기적으로 연결될 수 있다.

- [0023] 연결부(510)는 복수의 금속 패드들을 포함할 수 있다. 예를 들어, 복수의 금속 패드들은 재배선 충과 전기적으로 연결될 수 있다.

- [0024] 반도체 칩(500)은 메모리 칩 또는 로직(logic) 칩일 수 있다.

- [0026] 다시 도 1을 참고하면, 더미 스트립 기판에 부착된 다이들은 인캡슐레이션(encapsulation)될 수 있다(S104).

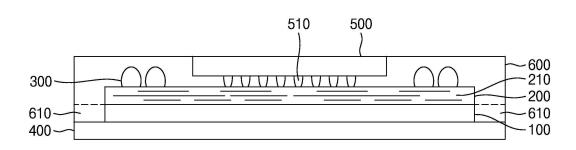

- [0027] 예를 들어, 도 6을 참고하면, 더미 스트립 기판(400) 상에 배치된 실리콘 층(100), 상기 실리콘 층(100) 상에 배치된 재배선 층(200), 상기 재배선 층(200)의 상면에 배치된 솔더 볼(300) 및 반도체 칩(500)의 노출된 부분은 인캡슐란트(encapsulant)(600)에 의해 인캡슐레이션될 수 있다. 인캡슐란트(600)는 에폭시 수지(epoxy resin) 및 그 등가물 중 하나일 수 있으나 이에 한정되지 않는다. 인캡슐란트(600)는 인캡슐레이션 층 또는 몰딩 층 또는 패시베이션(passivation) 층이라 지칭될 수 있다.

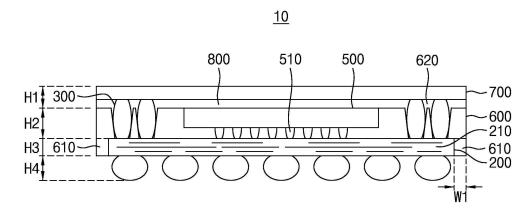

- [0028] 인캡슐란트 층(600)은 실리콘 층(100)의 측면, 재배선 층(200)의 측면 및 상면, 그리고 반도체 칩(500)의 측면 및 하면을 둘러쌀 수 있다. 설명의 편의를 위해, 인캡슐란트 층(600) 중 재배선 층(200)의 측면을 둘러싸는 영역은 측면 인캡슐란트 영역(610)이라 지칭될 수 있다.

- [0030] 다시 도 1을 참고하면, 인캡슐레이션된 반도체 다이의 상면 중 재배선 층의 상면에 배치된 복수의 내부 솔더 볼들의 위치에 대응하는 영역은 레이저 드릴링(drilling) 방식을 통해 제거될 수 있다(S105).

- [0031] 예를 들어, 도 7을 참고하면, 인캡슐레이션된 반도체 다이(10)의 상면 중 재배선 층(200)의 상면에 배치된 복수의 내부 솔더 볼들(300)의 위치에 대응하는 영역들(620)은 레이저에 의해 제거될 수 있다. 복수의 내부 솔더 볼들(300)은 레이저에 의해 제거된 영역들(620)을 통해 외부로 노출될 수 있다.

- [0033] 다시 도 1을 참고하면, 인캠슐레이션된 반도체 다이의 상면에는 인터포저가 스택(stack)될 수 있다(S106).

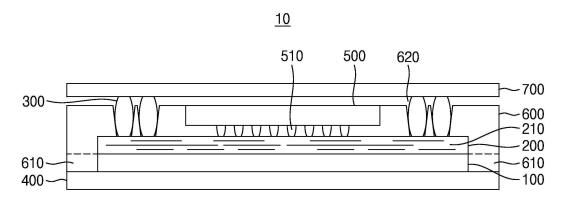

- [0034] 예를 들어, 도 8을 참고하면, 복수의 내부 솔더 볼들(300)은 인터포저(700)의 하면에 배치되는 솔더 볼들과 전기적으로 연결될 수 있다. 설명의 편의상, 인터포저(700)의 하면에 배치되는 솔더 볼들은 복수의 내부 솔더 볼들이라 지칭될 수 있다. 예를 들어, 인터포저(700)의 하면에 배치되는 솔더 볼들은 복수의 내부 솔더 볼들(300)에 포함될 수 있다.

- [0035] 인터포저(700)는 반도체 칩(500)의 상면 보다 더 높이 위치하도록 배치될 수 있다. 예를 들어, 복수의 내부 솔더 볼들(300)의 수직 단면의 높이는 연결부(510)를 포함하는 반도체 칩(500)의 수직 단면의 높이를 초과할 수 있다. 인터포저(700)는 복수의 내부 솔더 볼들(300)을 통해 재배선 층(200)과 전기적으로 연결될 수 있다.

- [0037] 다시 도 1을 참고하면, 인캡슐레이션된 반도체 다이의 상면과 인터포저의 하면 사이의 빈 공간은 언더필 (underfill)될 수 있다(S107).

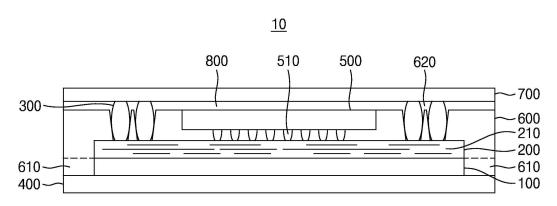

- [0038] 예를 들어, 도 9를 참고하면, 인캡슐레이션된 반도체 다이(10)의 상면과 인터포저(700)의 하면 사이의 빈 공간은 언더필 수지(800)에 의해 메워질 수 있다. 언더필 수지(800)에 의해 메워지는 영역은 언더필 층이라 지칭될수 있다. 반도체 다이(10)는 반도체 패키지라 지칭될수 있다.

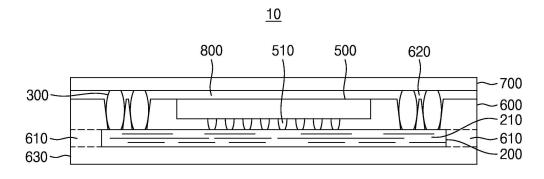

- [0040] 다시 도 1을 참고하면, 더미 스트립 및 실리콘 웨이퍼는 그라인딩(grinding)될 수 있다(S108).

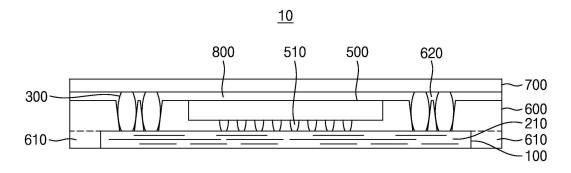

- [0041] 예를 들어, 도 10을 참고하면, 반도체 패키지(10)의 하부를 구성하는 더미 스트립(400) 및 실리콘 층(100)은 그라인딩될 수 있다. 더미 스트립(400) 및 실리콘 층(100)의 그라인딩으로 인해 재배선 층(200)의 하면은 노출될수 있다.

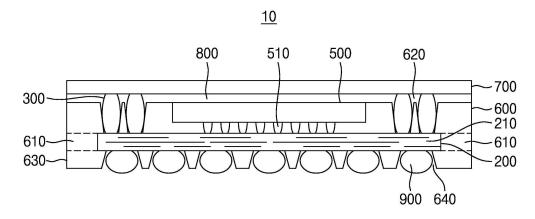

- [0043] 다시 도 1을 참고하면, 재배선 층의 하면에는 복수의 솔더 볼들이 형성될 수 있다(S109). 반도체 패키지는 인캡 슐란트 층이 재배선 층의 측면을 둘러싸도록 소잉될 수 있다(S110).

- [0044] 예를 들어, 도 11을 참고하면, 재배선 층(200)의 하면에는 복수의 솔더 볼들(900)이 형성될 수 있다. 복수의 솔더 볼들(900)은 복수의 외부 솔더 볼들이라 지칭될 수 있다. 복수의 외부 솔더 볼들(900)은 재배선 층(200)의 금속 배전 라인(210)과 전기적으로 연결될 수 있다. 복수의 외부 솔더 볼들(900)은 재배선 층(200)을 통해 반도체 칩(500)과 전기적으로 연결될 수 있다. 복수의 외부 솔더 볼들(900)은 재배선 층(200) 및 복수의 내부 솔더볼들(300)을 통해 인터포저(700)와 전기적으로 연결될 수 있다.

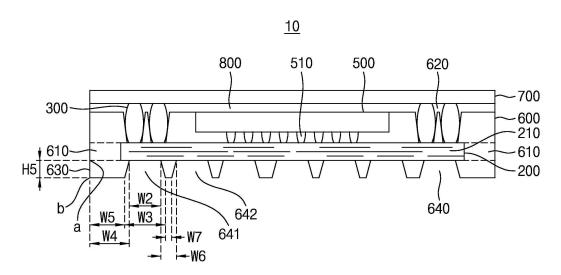

- [0045] 반도체 패키지(10)는 재배선 층(200)의 측면이 인캡슐란트 층(600)에 의해 둘러싸이도록 소잉될 수 있다. 예를 들어, 재배선 층(200)의 측면을 둘러싸는 측면 인캡슐란트 영역(610)의 수직 단면의 일측의 폭(width)의 길이 (W1)는 140 마이크로미터(micromiter; µm) 이하일 수 있다.

- [0046] 반도체 칩(500)의 상면으로부터 인터포저(700)의 상면까지의 수직 거리의 길이(H1)는 140 μm일 수 있다. 반도체 칩(500)의 상면으로부터 재배선 층(200)의 상면까지의 수직 거리의 길이(H2)는 120 μm일 수 있다. 재배선 층 (200)의 상면으로부터 하면까지의 수직 거리의 길이(H3)는 60 μm일 수 있다. 재배선 층(200)의 하면으로부터 솔 더 범프(510)의 하단까지의 수직 거리의 길이(H4)는 100 μm일 수 있다.

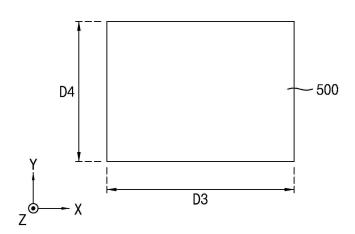

- [0047] 도 12를 참고하면, 재배선 충 (200)의 상면에 배치되는 반도체 칩(500)의 상면 또는 하면의 가로 길이(D1)는 7mm 내지 11mm일 수 있다. 반도체 칩(500)의 상면 또는 하면의 세로 길이(D2)는 7mm 내지 11mm일 수 있다.

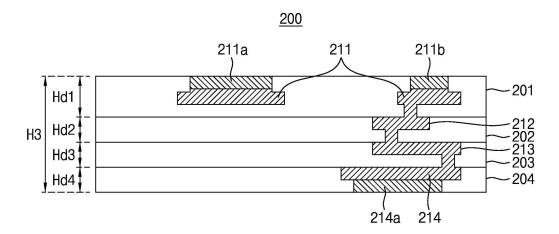

- [0049] 도 13을 참고하면, 재배선 층(200)은 제1 배선 층(201) 내지 제4 배선 층(204)을 포함할 수 있다.

- [0050] 제1 배선 층(201)은 제1 도전 라인(211), 복수의 내부 솔더 볼 패드들(211a), 및 복수의 반도체 칩 패드들 (211b)을 포함할 수 있다. 제1 도전 라인(211)은 복수의 내부 솔더 볼 패드들(211a) 및 복수의 반도체 칩 패드 들(211b)과 전기적으로 연결될 수 있다.

- [0051] 제1 도전 라인(211)은 제1 배선 층(201) 내에서 미리 정해진 패턴에 따라 배치될 수 있다.

- [0052] 복수의 내부 솔더 볼 패드들(211a)은 복수의 내부 솔더 볼들(900)을 제1 도전 라인(211)과 전기적으로 연결시키기 위한 도전 패드일 수 있다. 예를 들어, 복수의 내부 솔더 볼 패드들(211a)은 복수의 내부 솔더 볼들(900)과 전기적으로 연결될 수 있다.

- [0053] 복수의 반도체 칩 패드들(211b)은 반도체 칩(500)을 제1 배선 층(201)과 전기적으로 연결시키기 위한 도전 패드일 수 있다. 예를 들어, 반도체 칩(500)의 연결부(510)는 복수의 반도체 칩 패드들(211b)과 전기적으로 연결될수 있다. 예를 들어, 반도체 칩(500)의 연결부(510)가 복수의 솔더 범프들은 포함하는 경우, 상기 복수의 솔더 범프들은 복수의 반도체 칩 패드들(211b)과 전기적으로 연결될수 있다. 예를 들어, 반도체 칩(500)의 연결부(510)가 복수의 금속 패드들을 포함하는 경우, 상기 복수의 금속 패드들은 복수의 반도체 칩 패드들(211b)과 전기적으로 연결될수 있다.

- [0054] 제1 배선 층(201)의 수직 단면의 높이(Hd1)는 15 μ m일 수 있다.

- [0055] 제2 배선 충(202)은 제2 도전 라인(212)을 포함할 수 있다. 예를 들어, 제2 도전 라인(212)은 제2 배선 충(202) 내에서 미리 정해진 패턴에 따라 배치될 수 있다. 제2 도전 라인(212)은 제1 도전 라인(211)과 전기적으로 연결 될 수 있다.

- [0056] 제2 배선 층(202)의 수직 단면의 높이(Hd2)는 15 μ m일 수 있다.

- [0057] 제3 배선 충(203)은 제3 도전 라인(213)을 포함할 수 있다. 예를 들어, 제3 도전 라인(213)은 제3 배선 충(203) 내에서 미리 정해진 패턴에 따라 배치될 수 있다. 제3 도전 라인(213)은 제2 도전 라인(212)과 전기적으로 연결

될 수 있다.

- [0058] 제3 배선 충(203)의 수직 단면의 높이(Hd3)는 15 μm일 수 있다.

- [0059] 제4 배선 충(204)은 제4 도전 라인(214) 및 외부 솔더 볼 패드(214a)를 포함할 수 있다. 제4 도전 라인(214) 및 외부 솔더 볼 패드(214a)는 전기적으로 연결될 수 있다. 제4 도전 라인(214)은 제4 배선 충(204) 내에서 미리 정해진 패턴에 따라 배치될 수 있다. 제4 도전 라인(214)은 제3 도전 라인(213)과 전기적으로 연결될 수 있다.

- [0060] 복수의 외부 솔더 볼 패드들(213a)은 복수의 외부 솔더 볼들(900)을 제4 도전 라인(214)과 전기적으로 연결시키기 위한 도전 패드일 수 있다. 예를 들어, 복수의 외부 솔더 볼 패드들(213a)은 복수의 외부 솔더 볼들(900)과 전기적으로 연결될 수 있다.

- [0061] 제4 배선 층(204)의 수직 단면의 높이(Hd4)는 15 μ m일 수 있다.

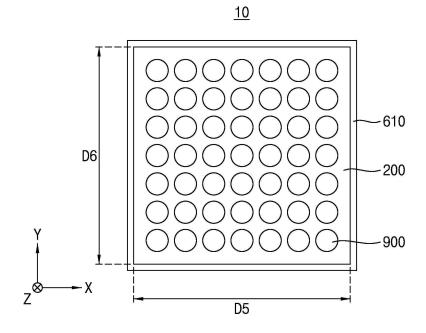

- [0063] 도 14를 참고하면, 일 실시예에 따른 반도체 패키지(10)는 재배선 층(200)의 측면을 둘러싸는 측면 인캡슐란트 영역(610)을 통해 재배선 층(200)의 측면을 외부로부터 보호할 수 있다. 예를 들어, 재배선 층(200)의 측면 중 일부분에는 도전 라인(210)이 노출될 수 있다. 도전 라인(210) 중 노출된 일부의 도전 라인에 의해 재배선 층(200)의 안정성 및 신뢰도는 낮아질 수 있다. 측면 인캡슐란트 영역(610)은 재배선 층(200)의 측면을 둘러쌈으로써, 도전 라인(210) 중 노출된 일부의 도전 라인을 보호할 수 있다. 측면 인캡슐란트 영역(610)을 통해 재배선 층(200)의 안정성 및 신뢰도는 향상될 수 있다.

- [0064] 재배선 충(200)의 하면의 가로 길이(D5)는 10mm 내지 14mm일 수 있다. 재배선 충(200)의 하면의 세로 길이(D6)는 10mm 내지 14mm일 수 있다.

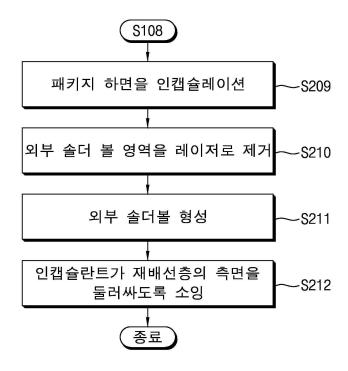

- [0066] 도 15는 본 개시의 일 실시예에 따른 반도체 패키지를 제조하기 위한 방법을 도시한 흐름도이다.

- [0067] 도 15를 참고하면, 일 실시예에 따른 패키징 순서는 도 1의 S108 단계에서 S209 단계로 진행될 수 있다.

- [0068] 예를 들어, 도 16을 참고하면, 더미 스트립 및 실리콘 층이 그라인딩(S108)된 이후, 반도체 패키지(10)의 하면은 추가적인 인캡슐란트(630)에 의해 인캡슐레이션될 수 있다(S209). 반도체 패키지(10)의 하면을 인캡슐레이션하는 인캡슐란트(630)는 하면 인캡슐란트 영역이라 지칭될 수 있다. 예를 들어, 인캡슐란트 층(600)은 측면 인캡슐란트 영역(610) 및 하면 인캡슐란트 영역(630)을 포함할 수 있다.

- [0070] 다시 도 15를 참고하면, 반도체 패키지(10)의 하면 인캡슐란트 영역(630) 중 복수의 외부 솔더 볼들이 배치되는 영역은 레이저를 통해 제거될 수 있다(S210).

- [0071] 예를 들어, 도 17을 참고하면, 하면 인캡슐란트 영역(630) 중 복수의 외부 솔더 볼들(900)이 배치되는 외부 솔더 볼 영역(640)은 레이저 드릴링 방식을 통해 제거될 수 있다. 외부 솔더 볼 영역(640)을 통해 재배선 층(200)의 하면 중 복수의 외부 솔더 볼들(900)이 배치되는 부분은 노출될 수 있다.

- [0072] 외부 솔더 볼 영역(640)은 복수의 원형 구멍(hole)들을 포함할 수 있다. 복수의 원형 구멍들은 하면 인캡슐란트 영역(630)의 하면으로부터 재배선 층(200)으로 갈수록 좁아질 수 있다.

- [0073] 예를 들어, 제1 원형 구멍(641)에서 재배선 충(200)에 인접한 상측 원의 지름의 길이(W2)는, 하면 인캡슐란트 영역(630)의 하면에 인접한 하측 원의 지름의 길이(W3) 보다 작을 수 있다.

- [0074] 예를 들어, 제1 원형 구멍(641)의 상측 원의 지름의 길이(W2)는 300 μm일 수 있다. 제1 원형 구멍(641)의 하측 원의 지름의 길이(W3)는 360 μm일 수 있다.

- [0075] 반도체 패키지(10)의 수직 단면에서, 하면 인캡슐란트 영역(630)의 측면 중 재배선 충(200)의 하면과 수평하는 일 지점(a)으로부터, 제1 원형 구멍(641)의 상측 원의 둘레의 일 지점과의 최단 거리의 길이(W4)는 220 μ m일 수 있다.

- [0076] 반도체 패키지(10)의 수직 단면에서, 하면 인캡슐란트 영역(630)의 측면의 모서리 지점(b)으로부터, 제1 원형 구멍(641)의 하측 원의 둘레와의 최단 거리의 길이(W5)는 190 μm일 수 있다.

- [0077] 반도체 패키지(10)의 수직 단면에서, 제1 원형 구멍(641)의 상측 원의 둘레와 제2 원형 구멍(642)의 상측 원의 둘레 간의 최단 거리의 길이(W6)는 150 µm일 수 있다.

- [0078] 반도체 패키지(10)의 수직 단면에서, 제1 원형 구멍(641)의 하측 원의 둘레와 제2 원형 구멍(642)의 하측 원의 둘레 간의 최단 거리의 길이(W7)는 90 u m일 수 있다.

- [0079] 하면 인캡슐란트 영역(630)의 수직 단면의 높이(H5)는 50 µm일 수 있다.

- [0081] 다시 도 15를 참고하면, 반도체 패키지(10)의 외부 솔더 볼 영역(640)에는 복수의 외부 솔더 볼들이 형성될 수 있다(S211).

- [0082] 예를 들어, 도 18을 참고하면, 반도체 패키지(10)의 외부 솔더 볼 영역(640)에는 복수의 외부 솔더 볼들(900)이 형성될 수 있다.

- [0083] 도 19는 본 개시의 일 실시예에 따른 반도체 패키지(10)의 하면도이다. 도 19를 참고하면, 하면 인캡슐란트 영역(630)은 외부 솔더 볼 영역(640)을 제외한 반도체 패키지(10)의 하면을 인캡슐레이션할 수 있다.

- [0084] 하면 인캡슐란트 영역(630)은 반도체 패키지(10)의 하면에 노출되는 재배선 층(200)의 하면을 외부로부터 보호할 수 있다. 하면 인캡슐란트 영역(630)은 재배선 층(200)의 하면을 보호함으로써, 재배선 층(200)의 안정성 및 신뢰도를 향상시킬 수 있다.

- [0085] 하면 인캡슐란트 영역(630)은 반도체 패키지(10)의 하면에 노출되는 재배선 층(200)의 하면을 격자형(lattice)으로 덮을 수 있다. 하면 인캡슐란트 영역(630)은 반도체 패키지(10)의 하면을 격자형(lattice)으로 고정시킬수 있다. 하면 인캡슐란트 영역(630)은 재배선 층(200)의 하면을 고정시킴으로써, 재배선 층(200)의 하면을 포함하는 반도체 패키지(10)의 하면의 강도를 증가시킬수 있다.

- [0087] 당업자에 의해 인지될 수 있는 바와 같이, 본 개시에서 설명된 혁신적인 개념들은 응용 분야의 넓은 범위에 걸쳐 수정 및 변경될 수 있다. 따라서, 청구된 주제의 범위는 위에서 논의된 특정한 예시적인 교시들의 어떤 것으로 제한되어서는 안되고, 아래의 청구항들에 의해 정의된다.

#### 부호의 설명

[0088] 10: 반도체 패키지 100: 실리콘 웨이퍼 층

200: 재배선 층 201: 제1 재배선 층

202: 제2 재배선 층 203: 제3 재배선 층

204: 제4 재배선 층 210: 도전 라인

211: 제1 도전 라인 212: 제2 도전 라인

213: 제3 도전 라인 214: 제4 도전 라인

300: 내부 솔더 볼 400: 더미 스트립 기판

500: 반도체 칩 510: 연결부

600: 인캡슐란트 610: 측면 인캡슐란트 영역

620: 내부 솔더 볼 영역 630: 하면 인캡슐란트 영역

640: 외부 솔더 볼 영역 641: 제1 원형 구멍

642: 제2 원형 구멍 700: 인터포저

800: 언더필 층 900: 외부 솔더 볼

# 도면

# 도면1

도면2

도면3

도면4

도면5

# 도면6

<u>10</u>

도면7

<u>10</u>

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

# 도면19

<u>10</u>