(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5215087号

(P5215087)

(45) 発行日 平成25年6月19日(2013.6.19)

(24) 登録日 平成25年3月8日(2013.3.8)

(51) Int.Cl.

F 1

H03F 3/45 (2006.01)

H03F 3/45

H03F 1/26 (2006.01)

H03F 1/26

H03F 3/08 (2006.01)

H03F 3/08

Z

請求項の数 9 (全 17 頁)

(21) 出願番号

特願2008-221221 (P2008-221221)

(22) 出願日

平成20年8月29日 (2008.8.29)

(65) 公開番号

特開2010-57014 (P2010-57014A)

(43) 公開日

平成22年3月11日 (2010.3.11)

審査請求日

平成23年8月17日 (2011.8.17)

(73) 特許権者 000154325

住友電工デバイス・イノベーション株式会

社

神奈川県横浜市栄区金井町1番地

(74) 代理人 100087480

弁理士 片山 修平

(74) 復代理人 100137615

弁理士 横山 照夫

(74) 復代理人 100134511

弁理士 八田 俊之

(72) 発明者 原 弘

山梨県中巨摩郡昭和町大字紙漉阿原100

O番地 ユーディナデバイス株式会社内

審査官 高橋 義昭

最終頁に続く

(54) 【発明の名称】電子回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号が入力される入力端子と参照信号端子とを有する差動增幅回路と、前記入力信号を平均化し平均化信号を生成する平均化回路と、

前記参照信号端子と前記平均化回路の出力との間に設けられ、前記平均化信号を保持し前記参照信号端子に出力する第1保持回路と、

前記第1保持回路と前記平均化回路との間に設けられた第1スイッチと、

前記第1保持回路の出力、および前記平均化回路の出力と前記第1スイッチとの間の出力ノードのいずれかを選択的に前記参照信号端子に接続する第2スイッチと、

前記出力ノードと前記第2スイッチとの間に接続され、前記平均化信号を保持し前記第2スイッチに出力する第2保持回路と、

を備えることを特徴とする電子回路。

## 【請求項 2】

前記第1スイッチは、前記入力信号を平均化するための通信準備期間において、前記第1保持回路と前記平均化回路とを接続し、前記通信準備期間の後は前記第1保持回路と前記平均化回路とを遮断することを特徴とする請求項1記載の電子回路。

## 【請求項 3】

前記第1スイッチは、前記入力信号を平均化するための通信準備期間において、前記第1保持回路と前記平均化回路とを接続し、前記通信準備期間の後は前記第1保持回路と前記平均化回路とを遮断し、

10

20

前記第2スイッチは、前記通信準備期間において前記出力ノードを選択し前記参照信号端子に接続し、前記通信準備期間の後は前記第1保持回路の出力を選択し前記参照信号端子に接続することを特徴とする請求項1記載の電子回路。

**【請求項4】**

入力信号が入力される入力端子と参照信号端子とを有する差動増幅回路と、

前記入力信号を平均化し平均化信号を生成する平均化回路と、

前記参照信号端子と前記平均化回路の出力との間に設けられ、前記平均化信号を保持し前記参照信号端子に出力する第1保持回路と、

前記第1保持回路と前記平均化回路との間に設けられた第1スイッチと、

を具備し、

前記第1保持回路の出力は前記平均化回路に入力され、前記平均化回路を介した前記第1保持回路の出力が前記参照信号端子に出力されることを特徴とする電子回路。

**【請求項5】**

前記平均化回路は、前記入力信号および前記第1保持回路の出力のいずれかを選択して平均化することにより前記平均化信号を生成することを特徴とする請求項4記載の電子回路。

**【請求項6】**

前記第1スイッチは、前記入力信号を平均化するための通信準備期間において、前記第1保持回路と前記平均化回路とを接続し、前記通信準備期間の後は前記第1保持回路と前記平均化回路とを遮断し、

前記平均化回路は、前記通信準備期間において前記入力信号を選択し平均化することにより前記平均化信号を生成し、前記通信準備期間の後は前記第1保持回路の出力を選択することにより前記平均化信号を生成することを特徴とする請求項5記載の電子回路。

**【請求項7】**

前記平均化回路の出力と前記第1スイッチとの間に前記平均化信号を保持し、前記通信準備期間の後はその出力が前記参照信号端子に接続され、前記通信準備期間においてはその出力が前記第1スイッチに接続される第2保持回路が設けられ、

前記第1保持回路は前記第2保持回路で保持された前記平均化信号を保持することを特徴とする請求項6記載の電子回路。

**【請求項8】**

前記第1保持回路は、前記入力信号のピークを保持するピークホールド回路またはローパスフィルタであることを特徴とする請求項1から7のいずれか一項記載の電子回路。

**【請求項9】**

前記第1保持回路は、出力を一定値に設定可能であることを特徴とする請求項1から8のいずれか一項記載の電子回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電子回路及に関し、特に、入力端子と参照信号端子とを有する差動増幅回路を備え、入力信号を平均化した信号を参照信号として生成する電子回路に関する。

**【背景技術】**

**【0002】**

近年、PON(Passive Optical Network)方式のFTTH(Fiber to the home)が普及している。このシステムでは、各家庭から送信されてくる様々な振幅の光信号を受信し電気信号として増幅することが求められる。

**【0003】**

例えば、特許文献1には、PON方式の光通信に用いられる受信回路が開示されている。このような受信回路においては、フォトダイオード(PD)等の受光素子が光信号を受信し電流を出力する。トランシスインピーダンスアンプ(TIA)がPDの出力した電流信号を電圧信号に変換する。差動増幅回路がTIAの出力信号と、TIAの出力信号の平均

10

20

30

40

50

値に関係した参照信号と、を差動増幅し、TIAの出力信号が参照信号より高ければハイレベル、低ければローレベルを出力する。ここで、例えばPON方式の光通信に用いられる受信回路では、通信相手との距離の違いにより、光信号の振幅が異なる。このため、通信相手ごとに入力信号の平均値に関係した信号を参照信号として生成し、これと入力信号とを比較しハイレベル、ローレベルを出力する。

【特許文献1】特開2005-223638号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来の受信回路においては、参照信号が入力信号の平均値に到達するまでの安定期間を要するため、入力信号が入力されてから一定時間通信準備期間（プリアンブル期間ともいう）とし、ダミーの信号を受信する。しかしながら、このように生成された参照信号は、その後の通信期間において、入力光信号のレベル変動があると、その影響を受けて、本来の値とは異なってしまう。

【0005】

本発明は、上記課題に鑑みなされたものであり、入力信号の影響で参照信号が変動することを抑制することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、入力信号が入力される入力端子と参照信号端子とを有する差動増幅回路と、前記入力信号を平均化し平均化信号を生成する平均化回路と、前記参照信号端子と前記平均化回路の出力との間に設けられ、前記平均化信号を保持し前記参照信号端子に出力する第1保持回路と、前記第1保持回路と前記平均化回路との間に設けられた第1スイッチと、前記第1保持回路の出力、および前記平均化回路の出力と前記第1スイッチとの間の出力ノードのいずれかを選択的に前記参照信号端子に接続する第2スイッチと、前記出力ノードと前記第2スイッチとの間に接続され、前記平均化信号を保持し前記第2スイッチに出力する第2保持回路と、を備えることを特徴とする電子回路である。本発明によれば、第1スイッチが第1保持回路と平均化回路とを遮断することにより、入力信号の影響で参照信号が変動することを抑制することができる。

【0007】

上記構成において、前記第1スイッチは、前記入力信号を平均化するための通信準備期間において、前記第1保持回路と前記平均化回路とを接続し、前記通信準備期間の後は前記第1保持回路と前記平均化回路とを遮断する構成とすることができます。この構成によれば、通信準備期間においては、入力信号の平均化信号を参照信号とすることができます、通信準備期間後は、入力信号の影響で参照信号が変動することを抑制することができる。

【0009】

上記構成において、前記第1スイッチは、前記入力信号を平均化するための通信準備期間において、前記第1保持回路と前記平均化回路とを接続し、前記通信準備期間の後は前記第1保持回路と前記平均化回路とを遮断し、前記第2スイッチは、前記通信準備期間において前記出力ノードを選択し前記参照信号端子に接続し、前記通信準備期間の後は前記第1保持回路の出力を選択し前記参照信号端子に接続する構成とすることができます。この構成によれば、通信準備期間においては、入力信号の平均化信号を参照信号とすることができます、通信準備期間後は、入力信号の影響で参照信号が変動することを抑制することができる。

【0011】

本発明は、入力信号が入力される入力端子と参照信号端子とを有する差動増幅回路と、前記入力信号を平均化し平均化信号を生成する平均化回路と、前記参照信号端子と前記平均化回路の出力との間に設けられ、前記平均化信号を保持し前記参照信号端子に出力する第1保持回路と、前記第1保持回路と前記平均化回路との間に設けられた第1スイッチと、を具備し、前記第1保持回路の出力は前記平均化回路に入力され、前記平均化回路を介

10

20

30

40

50

した前記第1保持回路の出力が前記参照信号端子に出力されることを特徴とする電子回路である。

**【0012】**

上記構成において、前記平均化回路は、前記入力信号および前記第1保持回路の出力のいずれかを選択して平均化することにより前記平均化信号を生成する構成とすることができる。この構成によれば、平均化回路が第1保持回路の出力を選択することにより、入力信号の影響で参照信号が変動することを抑制することができる。

**【0013】**

上記構成において、前記第1スイッチは、前記入力信号を平均化するための通信準備期間において、前記第1保持回路と前記平均化回路とを接続し、前記通信準備期間の後は前記第1保持回路と前記平均化回路とを遮断し、前記平均化回路は、前記通信準備期間において前記入力信号を選択し平均化することにより前記平均化信号を生成し、前記通信準備期間の後は前記第1保持回路の出力を選択することにより前記平均化信号を生成する構成とすることができます。この構成によれば、通信準備期間においては、平均化信号を参照信号とすることができる、通信準備期間後は、入力信号の影響で参照信号が変動することを抑制することができる。

10

**【0014】**

上記構成において、前記平均化回路の出力と前記第1スイッチとの間に前記平均化信号を保持し、前記通信準備期間の後はその出力が前記参照信号端子に接続され、前記通信準備期間においてはその出力が前記第1スイッチに接続される第2保持回路が設けられ、前記第1保持回路は前記第2保持回路で保持された前記平均化信号を保持する構成とすることができます。この構成によれば、第2保持回路により、参照信号を早期に安定化させることができます。

20

**【0015】**

上記構成において、前記第1保持回路は、前記入力信号のピークを保持するピークホールド回路またはローパスフィルタである構成とすることができます。

**【0016】**

上記構成において、前記第1保持回路は、出力を一定値に設定可能である構成とすることができます。

**【発明の効果】**

30

**【0017】**

本発明によれば、第1スイッチが第1保持回路と平均化回路とを遮断することにより、入力信号の影響で参照信号が変動することを抑制することができる。

**【発明を実施するための最良の形態】**

**【0018】**

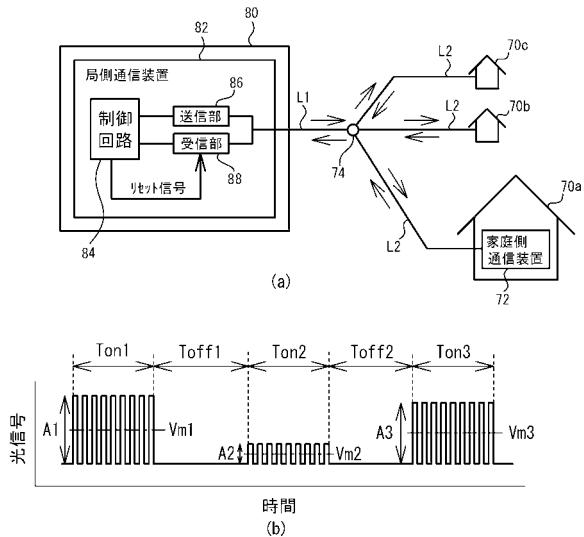

まず、PON方式の通信システムについて説明する。図1(a)は、PON方式のプロック図である。局舎80内の局側通信装置82は、複数の家庭70aから70c内の各家庭側通信装置72と光ファイバである通信経路L1およびL2を介し接続されている。局側通信装置82とオプティカルスプリッタ74とは1本の通信経路L1で接続されている。オプティカルスプリッタ74と各家庭側通信装置72との間は各通信経路L2を介し接続されている。オプティカルスプリッタ74は、各家庭側通信装置72から各通信経路L2を介し入出力された信号を通信経路L1に結合する。通信経路L1の信号は局側通信装置82に入出力される。局側通信装置82は制御回路84、送信部86および受信部88を有している。送信部86は、各家庭側通信装置72に光信号を送信する送信回路である。受信部88は、各家庭側通信装置72からの光信号を受信する受信回路である。制御回路84は送信部86および受信部88を制御する回路であり、例えば、受信部88にリセット信号を出力する。

40

**【0019】**

図1(b)は、受信部88の受光素子(図2のフォトダイオード42参照)に入力される光信号を時間に対し示す模式図である。期間Ton1の間は家庭70aの家庭側通信装

50

置 7 2 からの光信号が入力される。期間  $T_{off1}$  の間は光信号は入力されず、期間  $T_{on2}$  において家庭 7 0 b の家庭側通信装置（不図示）からの光信号が入力される。さらに、期間  $T_{off2}$  の間は光信号は入力されず、期間  $T_{on3}$  において家庭 7 0 c の家庭側通信装置（不図示）からの光信号が入力される。各家庭側通信装置 7 2 の出力信号の振幅および各通信経路 L 2 での光信号の損失はそれぞれ異なる。このため、期間  $T_{on1}$ 、 $T_{on2}$  および  $T_{on3}$  の光信号の振幅はそれぞれ振幅 A 1、A 2 および A 3 と異なる。このように、PON用の P D 1 2 には、異なる家庭から光信号が異なる振幅で不定期に入力される。なお、期間  $T_{off1}$  および  $T_{off2}$  は通信経路 L 2 を切り換える期間である。

## 【 0 0 2 0 】

10

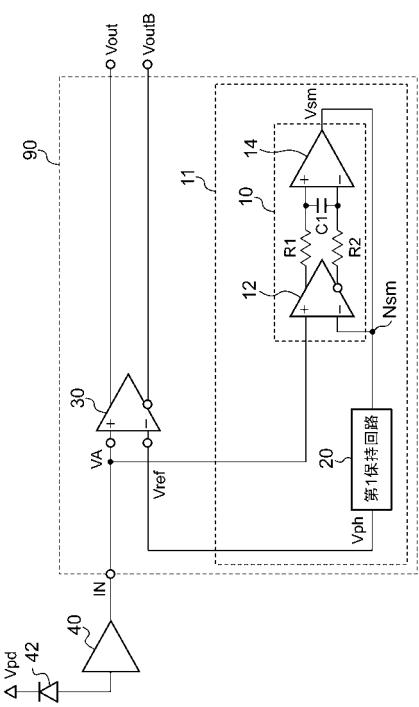

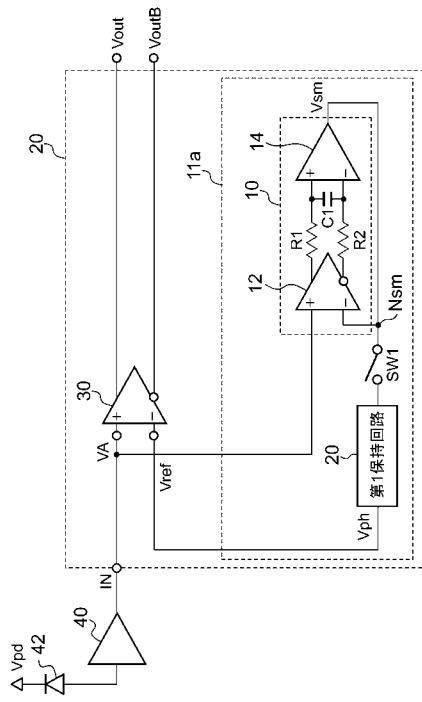

次に比較例について説明する。図 2 は、比較例に係る電子回路のブロック図である。図 2 を参照に、フォトダイオード (P D) 4 2 の出力電流を増幅した TIA 4 0 の出力電圧信号がデジタル入力信号 V A として電子回路 9 0 に入力される。電子回路 9 0 は差動増幅回路 3 0 および参照信号生成回路 1 1 を有している。差動増幅回路 3 0 は、入力信号 V A が入力する入力端子と参照信号 V ref が入力する参照信号端子を有している。差動増幅回路 3 0 は入力信号 V A と参照信号 V ref を差動増幅し、差動出力信号 V out および V out B を出力する。このように、差動増幅回路 3 0 は、デジタル情報を含んだ高周波信号であるデジタル入力信号 V A を参照信号 V ref と比較することで、パルス信号に変換するパルス変換回路である。

## 【 0 0 2 1 】

20

参照信号生成回路 1 1 は、平均化回路 1 0 と第 1 保持回路 2 0 とを有している。平均化回路 1 0 は、入力信号 V A を平均化し平均化信号 V sm を出力する。平均化回路 1 0 は、差動増幅回路 1 2、1 4、抵抗 R 1、R 2 およびキャパシタ C 1 を有する。差動増幅回路 1 2 には入力信号 V A と差動増幅回路 1 4 の出力ノード N sm の平均化信号 V sm とが入力する。差動増幅回路 1 2 は入力信号 V A と平均化信号 V sm とを差動増幅し、差動信号を抵抗 R 1 および R 2 を介し差動増幅回路 1 4 に出力する。差動増幅回路 1 4 の 2 つの入力はキャパシタ C 1 により互いに接続されている。平均化回路 1 0 は、入力信号 V A を、抵抗 R 1、R 2 およびキャパシタ C 1 で規定される時定数により平均化し、平均化信号 V sm を出力ノード N sm に出力する。

## 【 0 0 2 2 】

30

第 1 保持回路 2 0 は、差動増幅回路 3 0 の参照信号端子と平均化回路 1 0 との間に接続されている。第 1 保持回路 2 0 は、例えばピークホールド回路であり、平均化信号 V sm を保持し、保持信号 V ph を差動増幅回路 3 0 の参照信号端子に出力する。例えば、第 1 保持回路 2 0 は、平均化信号 V sm のピーク付近の信号を保持し保持信号 V ph として出力する。保持信号 V ph は参照信号 V ref として差動増幅回路 3 0 に入力される。

## 【 0 0 2 3 】

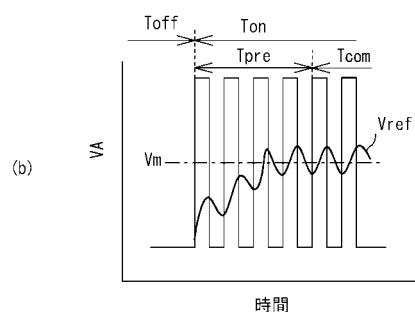

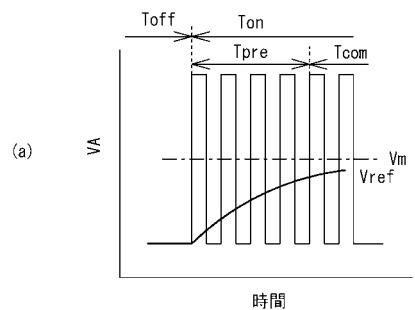

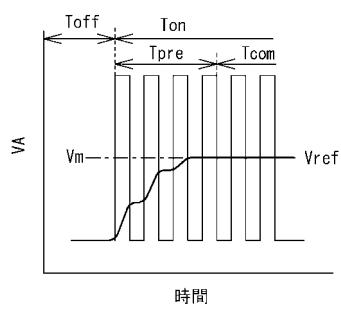

平均化回路 1 0 および第 1 保持回路 2 0 の機能について説明する。図 3 ( a ) 及び図 3 ( b ) は、時間に対する入力信号 V A と参照信号 V ref とを示した図である。図 3 ( a ) 及び図 3 ( b ) を参照に、期間  $T_{off}$  において、P D 4 2 に光信号は入力されない。よって、入力信号 V A は初期値である。期間  $T_{on}$  において、P D 4 2 に光信号が入力され、入力信号 V A が変動する。ある一定期間（通信準備期間  $T_{pre}$ ）においては、オン、オフ信号（0、1 信号）が交互に入力される。通信準備期間  $T_{pre}$  以降は実際にデータが送信される通信期間  $T_{com}$  である。通信期間  $T_{com}$  において、入力信号 V A は、オン、オフ信号が交互に入力されるとは限らないが、以降の図では、オン、オフ信号が交互に入力される場合を記載する。

40

## 【 0 0 2 4 】

差動増幅回路 3 0 は、参照信号 V ref に対し入力信号 V A が大きいか小さいかでハイレベルまたはローレベルを出力信号 V out および V out B として出力する。このため、参照信号 V ref は早期に、入力信号 V A の平均値 V m となることが好ましい。しかしな

50

がら、図3(a)のように、平均化回路10の時定数が長いと、参照信号Vrefは早期には平均値Vmとはならない。このように、通信準備期間Tpre内に参照信号Vrefが安定化しない。一方、図3(b)のように、平均化回路10の時定数が短いと、参照信号Vrefは通信準備期間Tpre内に早期に平均値Vmとなるが、その後、入力信号VAの変動に同期し参照信号Vrefも変動してしまう。

#### 【0025】

図4は比較例の入力信号VAと参照信号Vrefとを示した図である。図4を参照に、平均化回路10の時定数を図3(b)のように短くする。また、第1保持回路20の保持の時定数を平均化回路10の時定数より十分長くする。これにより、参照信号Vrefは入力信号VAに追従し早期に立ち上がる。入力信号VAがローレベルの場合も、第1保持回路20が平均化信号Vsmのピーク付近の保持信号Vphを出力するため、図3(b)のような参照信号Vrefの時間に対する変動は小さく、通信準備期間Tpre内に参照信号Vrefは早期に入力信号VAの平均値Vmに達し安定する。

10

#### 【0026】

しかしながら、比較例の参照信号生成回路11においては、参照信号Vrefが安定した後の通信期間Tcomにおいて、入力光信号のレベル変動があると、その影響を受けることにより、第1保持回路20に入力する平均化信号Vsmが変動すると、第1保持回路20は平均化信号Vsmのピークを保持してしまう。また、第1保持回路20から平均化回路10側への放電等によつても保持信号Vphが変動し参照信号Vrefが変動してしまう。例えば、通信期間Tcomにおいて、入力信号VAの出力レベルが大きくなつた場合には、それらにつられて平均化信号Vsmも大きくなり、保持信号Vphも大きくなつてしまつ。

20

#### 【0027】

表1は本発明の原理を示す表である。本発明によれば、参照信号生成回路11は、入力信号VAを平均化した平均化信号Vsmを参照信号Vrefとし、その後、入力信号VAによらず平均化信号Vsmを保持した保持信号Vphを参照信号Vrefとする。例えば、通信準備期間Tpreにおいて、平均化信号Vsmを参照信号Vrefとする。これにより、参照信号Vrefを入力信号VAの平均値とすることができます。一方、通信期間Tcom(通信準備期間の後)は入力信号VAによらず平均化信号Vsmを保持した保持信号Vphを参照信号Vrefとする。つまり、通信期間においては、保持信号Vphは入力信号VAに依存しない。これにより、参照信号Vrefを入力信号VAの平均値に保持したままとすることができ、入力信号VAの影響で参照信号Vrefが変動することを抑制することができる。

30

#### 【表1】

| 期間              | 通信準備期間          | 通信期間                    |

|-----------------|-----------------|-------------------------|

| 参照信号生成回路の出力Vref | 入力信号を平均化した平均化信号 | 入力信号によらず、平均化信号を保持した保持信号 |

40

#### 【0028】

通信準備期間Tpreにおいて、参照信号生成回路11が入力信号VAを平均化し平均化信号Vsmとする。よつて、参照信号生成回路11は、入力信号VAを平均化し平均化信号とした際の平均化信号Vsmのピークを保持し参照信号Vrefとすることが好ましい。

#### 【0029】

なお、表1では通信準備期間Tpreと通信期間Tcomとで参照信号Vrefを切り換えている。参照信号Vrefの切り換えのタイミングは、参照信号Vrefが入力信号VAの平均値に安定した後または入力信号VAの平均値に近づけばよく、通信期間Tcomの前であることで通信期間中のVrefは安定する。以下、表1に示した参照信号生成

50

回路 1 1 を実現する実施例について説明する。

**【実施例 1】**

**【0 0 3 0】**

図 5 は実施例 1 に係る電子回路のブロック図である。図 5 を参照に、実施例 1 の参照信号生成回路 1 1 a は、平均化回路 1 0 の出力ノード N s m と第 1 保持回路 2 0 との間に第 1 スイッチ S W 1 が設けられている。つまり、第 1 スイッチ S W 1 は、平均化信号 V s m を第 1 保持回路 2 0 a に接続または遮断する。その他の構成は比較例の図 2 と同じであり説明を省略する。

**【0 0 3 1】**

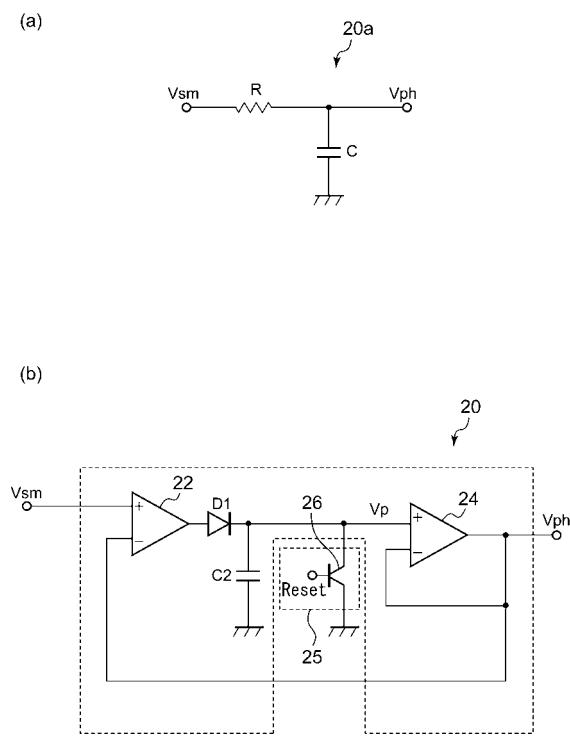

図 6 ( a ) は、第 1 保持回路 2 0 としてローパスフィルタを用いる例を示す図である。

図 6 ( a ) を参照に、第 1 保持回路 2 0 a は、入力と出力との間の抵抗 R と、出力とグラ

ンドとの間のキャパシタ C と、を有している。このように、第 1 保持回路 2 0 a として時

定数が平均化回路 1 0 の時定数より十分大きなローパスフィルタを用いることができる。

**【0 0 3 2】**

図 6 ( b ) は、第 1 保持回路 2 0 としてピークホールド回路を用いる例を示す図である。

図 6 ( b ) を参照に、第 1 保持回路 2 0 は差動増幅回路 2 2 、 2 4 、ダイオード D 1 、

キャパシタ C 2 及びリセット回路 2 5 を有している。差動増幅回路 2 2 は、平均化信号 V

s m と保持信号 V p h とを差動増幅する。差動増幅回路 2 2 の出力はダイオード D 1 のア

ノードに接続する。ダイオード D 1 のカソードは差動増幅回路 2 4 の入力に接続される。

差動増幅回路 2 4 は、信号 V p と保持信号 V p h とを差動増幅し保持信号 V p h を出力す

る。ダイオード D 1 のカソードとグラントとの間には、キャパシタ C 2 とリセット回路 2

5 とが並列に接続される。リセット回路 2 5 は N P N バイポーラトランジスタ 2 6 である

。トランジスタ 2 6 のコレクタがダイオード D 1 のカソードに、エミッタがグラントに接

続され、ベースにリセット信号 R e s e t が入力される。リセット信号 R e s e t がハイ

レベルになると、第 1 保持回路 2 0 は、保持信号 V p h を一定値（例えばグラント）に設

定する。これにより、第 1 保持回路 2 0 がリセットされる。

**【0 0 3 3】**

平均化信号 V s m が保持信号 V p h より大きいと、差動増幅回路 2 2 は正の信号を出力

し、ダイオード D 1 を介しキャパシタ C 2 を充電し、信号 V p の電位が定まる。差動増幅

回路 2 4 は信号 V s m と保持信号 V p h とを差動増幅する。よって、保持信号 V p h は信

号 V p となる。信号 V s m が保持信号 V p h より小さいと、差動増幅回路 2 2 は負の信号

を出力するが、ダイオード D 1 は逆方向のため、信号 V p は変化しない。以上により、ピ

ークホールド回路である第 1 保持回路 2 0 は、平均化信号 V s m の極大値（ピーク）に保

持信号 V p h を保持する。

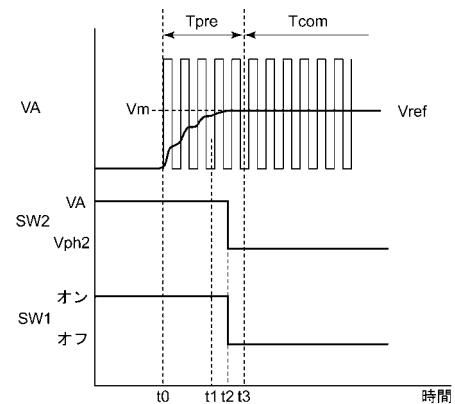

**【0 0 3 4】**

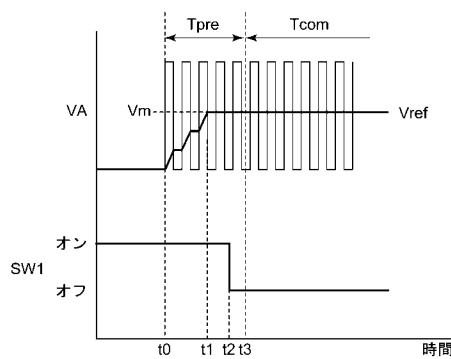

図 7 は、実施例 1 に係る電子回路の動作を示すタイムチャートである。時間に対する入

力信号 V A および参照信号 V r e f 並びに第 1 スイッチ S W 1 の動作を示している。図 7

を参照に、入力信号 V A が入力する時点 t 0 では第 1 スイッチ S W 1 はオン状態である。

よって、通信準備期間 T p r e の当初は、比較例の図 4 で説明した動作と同様に、参照信

号 V r e f は早期に入力信号 V A の平均値となり安定する。参照信号 V r e f が安定した

時点の時間 t 1 の後、時間 t 2 に第 1 スイッチ S W 1 がオフする。これにより、通信準備

期間 T p r e が終了した以降は、第 1 スイッチ S W 1 がオフする前に第 1 保持回路 2 0 が

保持した保持信号 V p h が参照信号 V r e f となるため、平均化信号 V s m が参照信号 V

r e f に影響することを抑制することができる。たとえ、時間 t 1 の前にスイッチ S W 1

がオフしたとしても、参照信号 V r e f が安定レベルに近づいていれば平均化信号 V s m

が参照信号 V r e f に影響することを抑制することができる。

**【0 0 3 5】**

実施例 1 によれば、図 7 のように、第 1 スイッチ S W 1 は、時間 t 2 までの期間において（つまり、通信準備期間 T p r e の少なくとも一部の期間において）平均化信号 T s m

を第 1 保持回路 2 0 に接続する。これにより、表 1 のように、参照信号生成回路 1 1 a は

10

20

30

40

50

、入力信号  $V_A$  を平均化した平均化信号  $V_{sm}$  を保持し参照信号  $V_{ref}$  とする。また、第1保持回路20が平均化信号  $V_{sm}$  を保持した保持信号  $V_{ph}$  を参照信号  $V_{ref}$  とするため、図4で説明したように、参照信号  $V_{ref}$  を早期に入力信号  $V_A$  の平均値近くに安定化させることができる。一方、図7のように、第1スイッチSW1は、時間  $t_2$  以降の期間（つまり、通信準備期間  $T_{pre}$  以降の通信期間  $T_{com}$ ）は、平均化信号  $V_{sm}$  と第1保持回路20とを遮断する。これにより、表1のように、入力信号  $V_A$  によらず平均化信号  $V_{sm}$  を保持した保持信号  $V_{ph}$  を参照信号  $V_{ref}$  とする。よって、入力信号  $V_A$  の影響で参照信号  $V_{ref}$  が変動することを抑制することができる。

#### 【0036】

さらに、第1保持回路20がリセット可能であることにより、図1(b)の期間  $T_{off_1}$  および  $T_{off_2}$  に第1保持回路20をリセットし、参照信号  $V_{ref}$  を最小値にセットすることができる。10

#### 【実施例2】

#### 【0037】

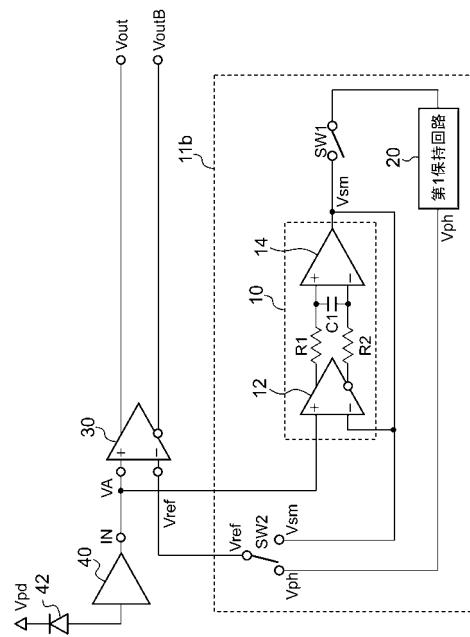

実施例2は第2スイッチSW2を有する例である。図8は実施例2のブロック図である。図8を参照に、実施例2の参照信号生成回路11bは、平均化信号  $V_{sm}$  と保持信号  $V_{ph}$ とのいずれかを選択し参照信号  $V_{ref}$  とする第2スイッチSW2を有している。つまり、第2スイッチSW2は、第1保持回路20の出力、および平均化回路10の出力と第1スイッチSW1との間の出力ノード  $N_{sm}$  のいずれかを選択的に差動增幅回路30の参照信号端子に接続する。その他の構成は、実施例1の図5と同じであり、説明を省略する。20

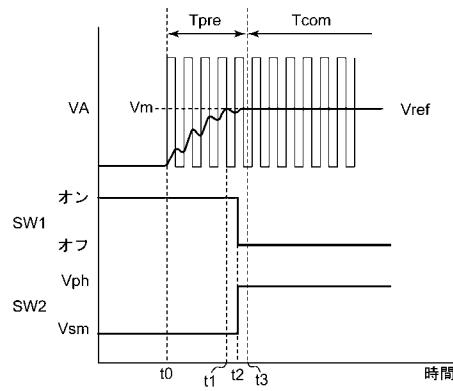

#### 【0038】

図9は、実施例2に係る電子回路の動作を示すタイムチャートである。時間に対する入力信号  $V_A$  および参照信号  $V_{ref}$  並びに第1スイッチSW1および第2スイッチSW2の動作を示している。図9を参照に、時間  $t_2$  以前では、第2スイッチSW2は平均化信号  $V_{sm}$  を選択し参照信号  $V_{ref}$  とする。時間  $t_2$  以降では、スイッチSW2は保持信号  $V_{ph}$  を選択し参照信号  $V_{ref}$  とする。

#### 【0039】

実施例2によれば、図9のように、第2スイッチSW2は、時間  $t_2$  以前（通信準備期間  $T_{pre}$  の初期）において、平均化信号  $V_{sm}$  を選択する。つまり、出力ノード  $N_{sm}$  を選択し差動增幅回路30の参照信号端子に接続する。これにより、表1のように、参照信号生成回路11bは、入力信号  $V_A$  を平均化した平均化信号  $V_{sm}$  を参照信号  $V_{ref}$  とすることができる。このとき、第1スイッチSW1は、オン状態になっており、第1保持回路20には、平均化信号  $V_{sm}$  が入力されている。一方、第2スイッチSW2は、時間  $t_2$  以降（通信準備期間  $T_{pre}$  の後）は、保持信号  $V_{ph}$  を選択する。つまり、第1保持回路20の出力を選択し差動增幅回路30の参照信号端子に接続する。時間  $t_2$  以降は、第1スイッチSW1がオフとなっており、第1保持回路20には、時間  $t_2$  までの平均化信号  $V_{sm}$  の例えればピーク値が保持されている。これにより、表1のように、入力信号  $V_A$  によらず平均化信号  $V_{sm}$  を保持した保持信号  $V_{ph}$  を参照信号  $V_{ref}$  とすることができます。よって、入力信号  $V_A$  の影響で参照信号  $V_{ref}$  が変動することを抑制することができる。

40

#### 【実施例3】

#### 【0040】

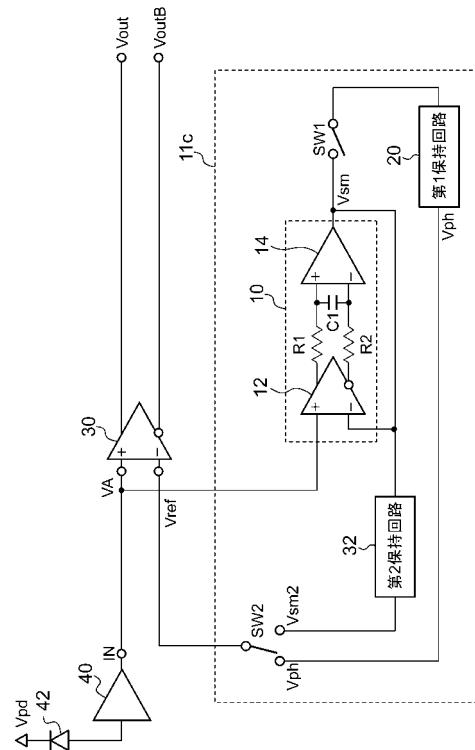

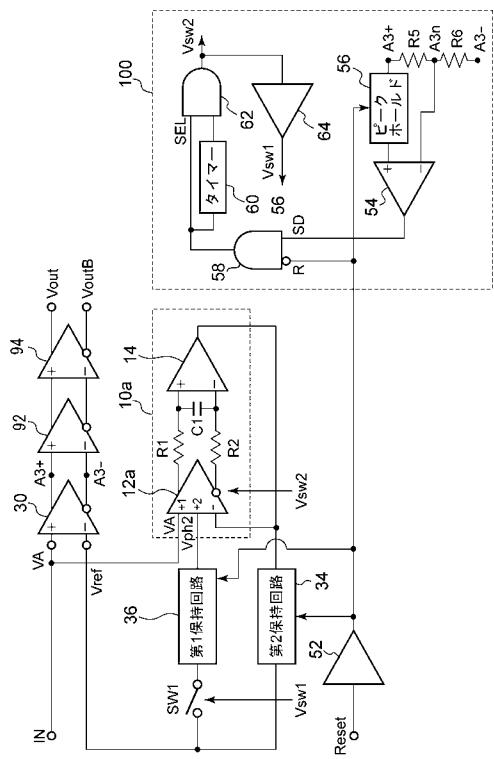

実施例3は、参照信号生成回路が第2保持回路を有する例である。図10は、実施例3のブロック図である。図10を参照に、実施例3の参照信号生成回路11cは、平均化信号  $V_{sm}$  を保持する第2保持回路32を有している。つまり、第2保持回路32は、出力ノード  $N_{sm}$  と第2スイッチSW2の間に接続されている。第2スイッチSW2は、第2保持回路32が保持した平均化信号  $V_{sm2}$  と保持信号  $V_{ph}$  とのいずれかを選択し、選択した信号を参照信号  $V_{ref}$  とする。その他の構成は、実施例2の図8と同じであり、説明を省略する。50

## 【0041】

実施例3の第1スイッチSW1および第2スイッチSW2の動作は、実施例2の図9と同じである。実施例3によれば、通信準備期間T<sub>pre</sub>において、第2スイッチSW2は、第2保持回路3\_2が保持した平均化信号V<sub>sm2</sub>を参照信号V<sub>ref</sub>とする。これにより、通信準備期間T<sub>pre</sub>において、参照信号V<sub>ref</sub>をより早く安定化させることができる。なお、第2保持回路3\_2の時定数は、通信準備期間T<sub>pre</sub>におけるオフの間には、平均化信号V<sub>sm</sub>を保持すればよいため、第1保持回路2\_0の時定数より小さいことがほしい。このように、通信準備期間T<sub>pre</sub>と通信期間T<sub>com</sub>との保持時間を独立に設定することができる。また、第2保持回路3\_2としては、図6(a)のようなローパスフィルタまたは図6(b)のようなピークホールド回路を用いることができる。

10

## 【実施例4】

## 【0042】

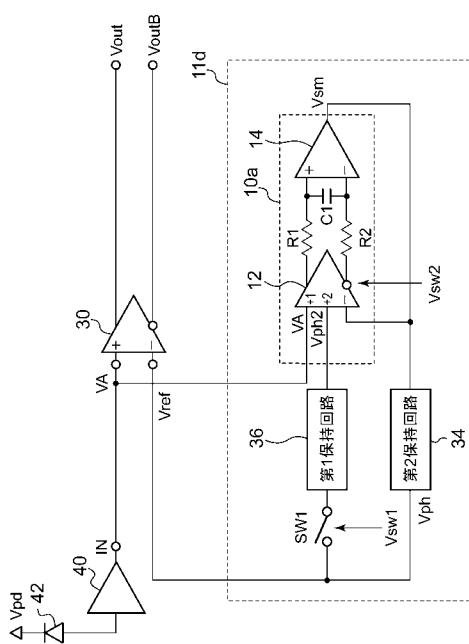

図11は実施例4に係る電子回路のブロック図である。図11を参照に、参照信号生成回路1\_1dは、平均化回路1\_0a、第1保持回路3\_6、第1スイッチSW1および第2保持回路3\_4を有している。平均化回路1\_0aは、差動増幅回路1\_2aおよび1\_4、抵抗R1、R2およびキャパシタC1を有している。差動増幅回路2\_3aの正側の入力が+1と+2との2つあり、第2スイッチ信号V<sub>sw2</sub>により、入力+1または+2を選択することができる。他の差動増幅回路1\_2aおよび1\_4、抵抗R1、R2およびキャパシタC1の構成は実施例1~3の平均化回路1\_0と同じであり説明を省略する。平均化回路1\_0aの出力V<sub>sm</sub>(平均化信号)は、第2保持回路3\_4に入力する。第2保持回路3\_4は平均化信号V<sub>sm</sub>を保持し(例えば、平均化信号V<sub>sm</sub>のピークを保持し)保持信号V<sub>ph</sub>を第1スイッチSW1を介し第1保持回路3\_6に出力する。また第2保持回路3\_4はV<sub>ph</sub>を差動増幅回路3\_0の参照信号端子に出力する。平均化回路1\_0aの入力+1には、入力信号VAが入力し、入力+2には、第1保持回路3\_6の出力V<sub>ph2</sub>が入力する。よって、平均化回路1\_0aは、入力信号VAおよび第1保持回路3\_6の出力V<sub>ph2</sub>のいずれかを選択して平均化することにより平均化信号V<sub>sm</sub>を生成することができる。

20

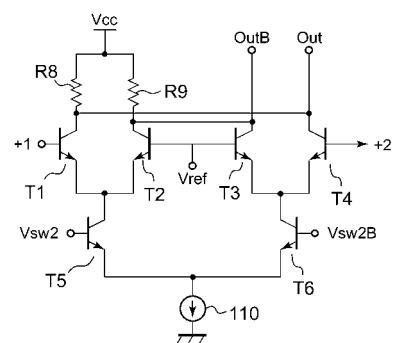

## 【0043】

図12は、差動増幅回路1\_2aの回路図である。図12を参照に、差動増幅回路1\_2aは、NPNトランジスタT1~T6、抵抗R8、R9および電流源1\_10を有している。第2スイッチ信号V<sub>sw2</sub>とV<sub>sw2B</sub>とは補信号である。第2スイッチ信号V<sub>sw2</sub>がハイの場合、トランジスタT1、T2、抵抗R8およびR9からなる差動回路が活性化し、参照信号V<sub>ref</sub>と入力+1の差動信号OutおよびOutBが出力される。第2スイッチ信号V<sub>sw2</sub>がローの場合、トランジスタT3、T4、抵抗R8およびR9からなる差動回路が活性化し、参照信号V<sub>ref</sub>と入力+2の差動信号OutおよびOutBが出力される。このように、トランジスタT5およびT6は入力+1と+2との選択する第2スイッチSW2として機能する。

30

## 【0044】

図13は、実施例4に係る電子回路の動作を示すタイムチャートである。時間に対する入力信号VAおよび参照信号V<sub>ref</sub>並びに第1スイッチSW1および第2スイッチSW2の動作を示している。図13を参照に、時間t0では、第2スイッチSW2は入力信号VAを選択し、第1スイッチSW1はオンしている。参照信号V<sub>ref</sub>は第2保持回路3\_4により、早期に安定することができる。また、第1スイッチSW1がオンしているため、第1保持回路3\_6に保持信号V<sub>ph</sub>が保持される。時間t1において、参照信号V<sub>ref</sub>が安定した後の時間t2に第1スイッチSW1がオフする。第2スイッチSW2が入力信号VAから第1保持回路3\_6の出力V<sub>ph2</sub>に切り換わる。言い換えれば、差動増幅回路1\_2aは入力を+1から+2に切り換える。これにより、平均化回路1\_0aは出力V<sub>ph2</sub>を平均化する。

40

## 【0045】

実施例4によれば、第2スイッチSW2が入力信号VAを選択すると、平均化回路1\_0aは、入力信号VAの平均化により平均化信号V<sub>sm</sub>を生成する。このとき第1スイッチ

50

S W 1 がオンしているため、第 1 保持回路 3 6 は、平均化信号 V s m を保持し V p h 2 を出力する。第 1 保持回路 3 6 の出力 V p h 2 は平均化回路 1 0 a に入力する。第 2 スイッチ S W 2 が第 1 保持回路 3 6 の出力 V p h 2 を選択すると、平均化回路 1 0 a を介した第 1 保持回路 3 6 の出力 V p h 2 が差動增幅回路 3 0 の参照信号端子に出力される。

#### 【 0 0 4 6 】

実施例 4 によれば、通信準備期間 T p r e において、第 1 スイッチ S W 1 はオンし第 1 保持回路 3 6 と平均化回路 1 0 a とを接続する。平均化回路 1 0 a は入力信号 V A を選択し平均化することにより平均化信号 V s m を生成する。これにより、表 1 のように、参照信号生成回路 1 1 d の出力である参照信号 V r e f は、入力信号 V A を平均化した信号となる。一方、通信準備期間 T p r e の後、第 1 スイッチ S W 1 はオフし第 1 保持回路 3 6 と平均化回路 1 0 a とを遮断する。平均化回路 1 0 a は第 1 保持回路 3 6 の出力 V p h 2 を選択し平均化することにより平均化信号 V s m を生成する。これにより、参照信号 V r e f は、第 1 保持回路 3 6 の出力 V p h 2 を平均化した信号となる。つまり、参照信号 V r e f は、表 1 のように、入力信号 V A によらず、第 1 保持回路 3 6 が平均化信号 V s m を保持した保持信号（出力 V p h 2 ）となる。よって、入力信号 V A の影響で参照信号 V r e f が変動することを抑制することができる。10

#### 【 0 0 4 7 】

さらに、平均化回路 1 0 a の出力と第 1 スイッチ S W 1 との間に第 2 保持回路 3 4 が接続されている。第 2 保持回路 3 4 は、平均化信号 V s m を保持し参照信号端子および第 1 スイッチ S W 1 に出力する。つまり、第 2 保持回路 3 4 と第 1 スイッチ S W 1 との間のノード（保持ノード）が差動增幅回路 3 0 の参照信号端子に接続されている。第 1 保持回路 3 6 は第 2 保持回路 3 4 に保持された平均化信号を保持する。これにより、通信準備期間 T p r e においても第 2 保持回路 3 4 が入力信号 V A の平均化信号を保持し参照信号とするため、参照信号 V r e f を早期に安定化させることができる。通信準備期間 T p r e における時定数は入力信号 V A のオンオフの期間に対し長い時間であればよく、通信期間 T c o m における時定数は期間 T o n に対し長い時間であることが好ましい。よって、第 1 保持回路 3 6 の時定数は第 2 保持回路 3 4 の時定数より長いことが好ましい。また、比較例と同様に、平均化回路 1 0 a の平均化の時定数は第 2 保持回路 3 4 の時定数より短いことが好ましい。このように、通信準備期間 T p r e において参照信号 V r e f を安定化させる時定数と通信期間 T c o m において参照信号を安定に保つ時定数を独立に設定することができる。2030

#### 【 0 0 4 8 】

第 1 保持回路 3 6 および第 2 保持回路 3 4 は、例えば図 6 ( a ) のローパスフィルタとすることができます。また、例えば、図 6 ( b ) のピークホールド回路とすることができます。。

#### 【 実施例 5 】

#### 【 0 0 4 9 】

図 1 4 は実施例 5 のブロック図である。図 1 4 を参照に、実施例 4 の図 1 1 に比較し、差動增幅回路 3 0 の後段に差動增幅回路 9 2 および 9 4 が設けられている。これにより、実施例 4 より大きな出力を行うことができる。また、差動增幅回路 9 2 または 9 4 をリミットアンプとすることにより、差動出力信号 V o u t および V o u t B を矩形波とすることができます。第 1 保持回路 3 6 および第 2 保持回路 3 4 は、図 6 ( b ) のピークホールド回路を用いている。40

#### 【 0 0 5 0 】

制御回路 1 0 2 は、抵抗 R 5 、 R 6 、ピークホールド回路 5 6 、ヒステリシス比較器 5 4 、 A N D 回路 5 8 、 6 2 、タイマー 6 0 および増幅回路 6 4 を有している。差動增幅回路 3 0 の出力信号 A 3 + 、 A 3 - の間に抵抗 R 5 、 R 6 が接続されている。ピークホールド回路 5 6 は、信号 A 3 + のピークを保持し、ヒステリシス比較器 5 4 に出力する。抵抗 R 5 と R 6 とで抵抗分割された信号がヒステリシス比較器 5 4 の他方の入力に入力する。ヒステリシス比較器 5 4 は、信号 A 3 + が信号 A 3 + の極大値の一定割合以下となると信50

号 S D としてローレベルを出力する。增幅回路 6 4 は信号 S D を増幅する。

#### 【 0 0 5 1 】

AND 回路 5 8 にはリセット信号 R e s e t の反転と信号 S D が入力する。よって、AND 回路 5 8 は、リセット信号 R e s e t がローレベル（リセットをしていない）でかつ信号 S D がハイレベルのとき信号 S E L としてハイレベルを出力する。AND 回路 6 2 には、信号 S E L と信号 S E L をタイマー 6 0 で遅延させた信号とが入力する。AND 回路 6 2 は、信号 S E L がローレベルとなって、一定時間後にローレベルを出力する。これにより、第 1 スイッチ信号 V s w 1 および第 2 スイッチ信号 V s w 2 としてローレベルが出力される。增幅回路 6 4 は第 1 スイッチ信号 V s w 1 を増幅する。第 2 スイッチ S W 2 は第 2 スイッチ信号 V s w 2 がハイレベルのとき V A を選択し、ローレベルのとき V p h 2 を選択する。第 1 スイッチ S W 1 は、第 1 スイッチ信号 V s w 1 がハイレベルのときオンし、ローレベルのときオフする。

10

#### 【 0 0 5 2 】

增幅回路 5 2 はリセット信号 R e s e t を増幅する。リセット信号 R e s e t はハイレベルとなると対応する回路をリセットする信号である。增幅回路 5 2 の出力は、ピークホールド回路 5 6 、第 1 保持回路 3 6 および第 2 保持回路 3 4 に入力する。リセット信号 R e s e t がハイレベルになると、ピークホールド回路 5 6 、第 1 保持回路 3 6 および第 2 保持回路 3 4 はリセットされ、ピークホールド回路 5 6 、第 1 保持回路 3 6 および第 2 保持回路 3 4 がそれぞれ保持していた保持信号はリセットされる。

20

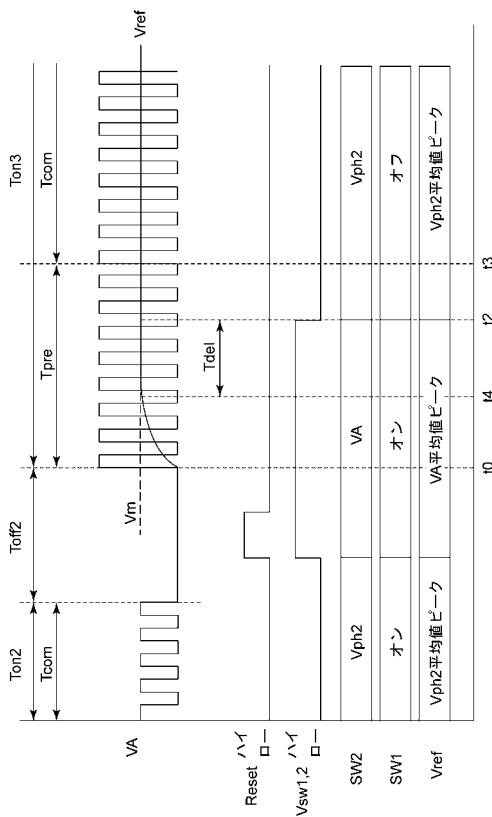

#### 【 0 0 5 3 】

図 15 は実施例 5 に係る電子回路の動作を示すタイムチャートである。時間に対する入力信号 V A 、 R e s e t 信号、スイッチ信号 V s w 1 、 V s w 2 、第 1 スイッチ S W 1 の動作、第 2 スイッチ S W 2 の動作および参照信号 V r e f を示している。前の入力信号 V A が入力される期間 T o n 2 では、 R e s e t 信号はロー、スイッチ信号 V s w 1 および V s w 2 はローである。第 2 スイッチ S W 2 は V p h 2 を選択しており、参照信号 V r e f は V p h 2 の平均値のピークとなっている。第 1 スイッチ S W 1 はオフである。入力信号 V A が入力されない期間 T o f f 2 において、リセット信号 R e s e t がハイレベルとなる。第 1 保持回路 3 6 、第 2 保持回路 3 4 およびピークホールド回路 5 6 がリセットされる。これにより、 A 3 + は A 3 + の極大値の一定割合以上となるため、信号 S D はハイレベルとなる。よって、信号 S E L もハイレベルとなり、スイッチ信号 V s w 1 および V s w 2 はハイレベルとなる。これにより、第 1 スイッチ S W 1 はオン、第 2 スイッチ S W 2 は V A を選択し、参照信号 V r e f は入力信号 V A の平均値のピークとなる。

30

#### 【 0 0 5 4 】

時間 t 0 において、期間 T o n 3 となり入力信号 V A が入力しはじめる。時間 t 0 において、参照信号 V r e f は 0 （最小値）のため、 A 3 + は極大値となる。参照信号 V r e f が大きくなるにつれ、 A 3 + は極大値に対する A 3 + の割合は小さくなる。時間 t 4 において、 A 3 + の極大値に対する A 3 + の割合が一定値以下になると、信号 S D はローレベルになる。ここで、ヒステリシス比較器 5 4 の時定数を入力信号 V A の周期より長くすることにより、信号 S A は入力信号 V A の周期の影響を受けない。時間 t 4 において、信号 S E L がローレベルとなる。タイマー 6 0 による遅延時間 T d e l 後の時間 t 2 において、スイッチ信号 V s w 1 および V s w 2 がローレベルとなる。これにより、第 1 スイッチ S W 1 はオフ、第 2 スイッチ S W 2 は V p h 2 を選択し、参照信号 V r e f は V p h 2 の平均値のピークとなる。

40

#### 【 0 0 5 5 】

以上のように、実例例 5 の回路により実施例 4 の図 13 で説明した動作が可能となる。抵抗 R 5 および R 6 は、参照信号 V r e f が平均値 V m となる直前に信号 S D がハイレベルとなるように設定することが好ましい。タイマー 6 0 の遅延時間は、参照信号 V r e f が安定してから、通信準備期間 T p r e が終了するまでの間にスイッチ信号 V s w 2 および V s w 1 がオフするように設定することが好ましい。

#### 【 0 0 5 6 】

10

20

30

40

50

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

【0057】

【図1】図1(a)はPON方式のブロック図、図1(b)はPON方式の光通信の時間に対する光信号の模式図である。

【図2】図2は比較例に係る電子回路の回路図である。

【図3】図3(a)および図3(b)は保持回路を有さず時定数が大きい場合、小さい場合のタイミングチャートである。 10

【図4】図4は比較例に係る電子回路のタイミングチャートである。

【図5】図5は実施例1に係る電子回路の回路図である。

【図6】図6(a)はローパスフィルタを用いた保持回路の例であり、図6(b)はピークホールド回路を保持回路に用いた例である。 15

【図7】図7は実施例1に係る電子回路のタイミングチャートである。

【図8】図8は実施例2に係る電子回路の回路図である。

【図9】図9は実施例2に係る電子回路のタイミングチャートである。

【図10】図10は実施例3に係る電子回路の回路図である。

【図11】図11は実施例4に係る電子回路の回路図である。 20

【図12】図12は差動増幅回路の回路図である。

【図13】図13は実施例4に係る電子回路のタイミングチャートである。

【図14】図14は実施例5に係る電子回路の回路図である。

【図15】図15は実施例5に係る電子回路のタイミングチャートである。

【符号の説明】

【0058】

|          |                |

|----------|----------------|

| 1 0      | 平均化回路          |

| 1 1      | 参照信号生成回路       |

| 2 0、 3 4 | 第1保持回路         |

| 3 0      | 差動増幅回路         |

| 3 2、 3 6 | 第2保持回路         |

| 4 0      | トランスインピーダンスアンプ |

| 4 2      | フォトダイオード       |

| S W 1    | 第1スイッチ         |

| S W 2    | 第2スイッチ         |

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開2000-278222(JP,A)

特公昭62-053967(JP,B1)

国際公開第2008/102819(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H03F 1/26 3/08 3/45