## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(45) 공고일자 2014년11월28일

(11) 등록번호 10-1466594

(24) 등록일자 2014년11월24일

(51) 국제특허분류(Int. Cl.)

H01L 21/20 (2006.01)

(21) 출원번호 10-2008-0027015

(22) 출원일자 2008년03월24일

심사청구일자 2013년03월06일

(65) 공개번호 10-2008-0087693

(43) 공개일자 2008년10월01일

(30) 우선권주장

JP-P-2007-00079264 2007년03월26일 일본(JP)

(56) 선행기술조사문헌

JP09116182 A\*

JP10092980 A\*

JP2003282610 A\*

JP1997275184 A

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

도겐 요시타카

일본, 가나가와Ken 243-0036, 아쓰기시, 하세 398

가부시키가이샤한도오따이 에네루기 켄큐쇼 내

수기야마 에이지

일본, 가나가와Ken 243-0036, 아쓰기시, 하세 398

가부시키가이샤한도오따이 에네루기 켄큐쇼 내

(뒷면에 계속)

(74) 대리인

장훈

전체 청구항 수 : 총 13 항

심사관 : 강병섭

## (54) 발명의 명칭 반도체 장치의 제작 방법

**(57) 요약**

본 발명은, 외부로부터의 국소적 가압(押壓)에 의하여 파괴되지 않는 신뢰성이 높은 반도체 장치를 수율 높게 제작하는 방법을 제공한다. 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성된 반도체 소자를 갖는 소자 기판을 형성하고, 소자 기판 위에 유기 화합물 또는 무기 화합물의 섬유체를 제공하고, 소자 기판 및 섬유체 위로부터 유기 수지를 포함하는 조성물을 도포하고 소자 기판을 가열함으로써, 소자 기판 위에 유기 화합물 또는 무기 화합물의 섬유체가 유기 수지로 함침(含浸)된 밀봉층을 형성하여, 반도체 장치를 제작한다.

**대 표 도**

(72) 발명자

오타니 히사시

일본, 가나가와켄 243-0036, 아쓰기시, 하세 398

가부시키가이샤한도오따이 에네루기 켄큐쇼 내

초록메 다큐야

일본, 가나가와켄 243-0036, 아쓰기시, 하세 398

가부시키가이샤한도오따이 에네루기 켄큐쇼 내

---

## 특허청구의 범위

### 청구항 1

삭제

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

반도체 장치의 제작 방법에 있어서:

복수의 능동 소자들을 갖는 소자 기판의 제 1 표면 위에 제 1 섬유체를 제공하는 단계;

상기 제 1 섬유체가 제 1 유기 수지로 함침되도록 상기 제 1 섬유체와 상기 소자 기판 위로부터 상기 제 1 유기 수지를 포함하는 제 1 조성물을 도포하는 단계;

상기 제 1 조성물을 도포한 후, 상기 소자 기판을 가열함으로써 상기 제 1 섬유체와 상기 제 1 유기 수지를 포함하는 제 1 밀봉층을 형성하는 단계;

상기 소자 기판의 상기 제 1 표면의 반대 쪽의 면인 상기 소자 기판의 제 2 표면 위에 제 2 섬유체를 제공하는 단계;

상기 제 2 섬유체가 제 2 유기 수지로 함침되도록 상기 제 2 섬유체와 상기 소자 기판에 상기 제 2 유기 수지를 포함하는 제 2 조성물을 도포하는 단계;

상기 제 2 조성물을 도포한 후, 상기 소자 기판을 가열함으로써 상기 제 2 섬유체와 상기 제 2 유기 수지를 포함하는 제 2 밀봉층을 형성하는 단계; 및

상기 소자 기판과, 상기 제 1 및 제 2 밀봉층들을 분단하여 복수의 반도체 장치들을 얻는 단계를 포함하는, 반도체 장치의 제작 방법.

### 청구항 6

제 5 항에 있어서,

상기 분단은 다이싱, 스크라이빙, 재단기(cutting machine)의 이용, 및 레이저 컷법 중 하나에 의해 수행되는, 반도체 장치의 제작 방법.

### 청구항 7

제 5 항에 있어서,

상기 제 2 섬유체는 유리 섬유를 포함하는, 반도체 장치의 제작 방법.

### 청구항 8

반도체 장치의 제작 방법에 있어서:

복수의 능동 소자들을 갖는 소자 기판의 제 1 표면 위에 제 1 유기 수지 층을 형성하는 단계;

제 1 섬유체가 상기 제 1 유기 수지 층의 제 1 유기 수지로 함침되도록 상기 제 1 유기 수지 층과 상기 소자 기

판 상에 상기 제 1 섬유체를 제공하는 단계;

상기 제 1 섬유체를 제공한 후, 상기 소자 기판을 가열함으로써 상기 제 1 섬유체와 상기 제 1 유기 수지를 포함하는 제 1 밀봉층을 형성하는 단계;

상기 소자 기판의 상기 제 1 표면의 반대 쪽의 면인 상기 소자 기판의 제 2 표면 위에 제 2 유기 수지 층을 형성하는 단계;

제 2 섬유체가 상기 제 2 유기 수지 층의 제 2 유기 수지로 합침되도록 상기 제 2 유기 수지 층 및 상기 소자 기판 상에 상기 제 2 섬유체를 제공하는 단계;

상기 제 2 섬유체를 제공한 후, 상기 소자 기판을 가열함으로써 상기 제 2 섬유체와 상기 제 2 유기 수지를 포함하는 제 2 밀봉층을 형성하는 단계; 및

상기 소자 기판과, 상기 제 1 및 제 2 밀봉층들을 분단하여 복수의 반도체 장치들을 얻는 단계를 포함하는, 반도체 장치의 제작 방법.

### **청구항 9**

제 8 항에 있어서,

상기 분단은 다이싱, 스크라이빙, 재단기의 이용, 및 레이저 컷법 중 하나에 의해 수행되는, 반도체 장치의 제작 방법.

### **청구항 10**

제 8 항에 있어서,

상기 제 2 섬유체는 유리 섬유를 포함하는, 반도체 장치의 제작 방법.

### **청구항 11**

제 5 항 또는 제 8 항에 있어서,

상기 복수의 능동 소자들을 덮는 절연층을 형성하는 단계를 더 포함하는, 반도체 장치의 제작 방법.

### **청구항 12**

제 5 항 또는 제 8 항에 있어서,

상기 소자 기판 위에 안테나를 형성하는 단계를 더 포함하는, 반도체 장치의 제작 방법.

### **청구항 13**

제 5 항 또는 제 8 항에 있어서,

상기 소자 기판은 SOI 기판을 이용하여 형성되는, 반도체 장치의 제작 방법.

### **청구항 14**

제 5 항 또는 제 8 항에 있어서,

상기 복수의 능동 소자들 중 하나는 MOS 트랜지스터, 비휘발성 기억 소자 및 다이오드로부터 선택되는, 반도체 장치의 제작 방법.

### **청구항 15**

제 5 항 또는 제 8 항에 있어서,

상기 제 1 섬유체는 유리 섬유를 포함하는, 반도체 장치의 제작 방법.

### **청구항 16**

제 5 항 또는 제 8 항에 있어서,

상기 제 1 밀봉층의 제 1 개구부내의 상기 소자 기판의 제 1 배선에 접속되는 제 1 접속 단자를 형성하는 단계; 및

상기 제 1 접속 단자와 제 1 안테나가 서로 전기적으로 접속되도록 상기 제 1 밀봉층에 상기 제 1 안테나를 갖는 제 1 기판을 접합하는 단계를 더 포함하는, 반도체 장치의 제작 방법.

#### 청구항 17

삭제

#### 청구항 18

제 16 항에 있어서,

상기 소자 기판의 제 2 배선의 일부가 제 2 개구부내에 노출되도록 상기 제 2 밀봉층내의 상기 제 2 개구부를 형성하는 단계;

상기 제 2 개구부내의 상기 제 2 배선에 접속되는 제 2 접속 단자를 형성하는 단계; 및

상기 제 2 접속 단자와 제 2 안테나가 서로 전기적으로 접속되도록 상기 제 2 밀봉층에 상기 제 2 안테나를 갖는 제 2 기판을 접합하는 단계를 더 포함하는, 반도체 장치의 제작 방법.

#### 청구항 19

삭제

#### 청구항 20

삭제

#### 청구항 21

삭제

#### 청구항 22

삭제

#### 청구항 23

삭제

#### 청구항 24

삭제

#### 청구항 25

삭제

#### 청구항 26

삭제

#### 청구항 27

삭제

#### 청구항 28

삭제

#### 청구항 29

삭제

청구항 30

삭제

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001] 본 발명은, 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성된 반도체 소자를 갖는 반도체 장치의 제작 방법에 관한 것이다.

#### 배경기술

[0002] 현재, 무선 칩, 센서 등, 각종 장치의 박형화가 제품 소형화에 있어서 중요한 요소가 되고 있고, 그 기술이나 사용 범위가 급속히 넓어지고 있다. 이를 박형화된 각종 장치는 어느 정도 가요성이 있기 때문에 만곡한 면에 설치하여 사용할 수 있다.

[0003] 또한, 특히 문헌 1에서는, 0.5mm이하의 사이즈의 반도체 칩을 종이 또는 필름 상태의 매체에 매립하여 구부림이나 접중 하중을 개선한 반도체 장치가 개시되어 있다.

[0004] [특히 문헌 1] 특개2004-78991호 공보

#### 발명의 내용

##### 해결 하고자하는 과제

[0005] 그러나, 안테나를 칩에 형성하여 내장(온 칩(On-chip)화)하는 반도체 장치인 경우, 칩의 면적이 작으면, 안테나 사이즈가 작아지며 통신 거리가 짧아지는 문제가 있다. 또한, 종이 또는 필름 매체에 형성된 안테나를 칩에 접속하여 반도체 장치를 제작하는 경우, 칩의 사이즈가 작으면 접속 불량이 생기고 수율이 저하된다.

[0006] 그래서, 본 발명은 외부로부터 국소적인 압력이 가해져도 쉽게 파괴되지 않고, 신뢰성이 높은 반도체 장치를 수율 높게 제작하는 방법을 제공한다.

##### 과제 해결수단

[0007] 본 발명은, 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성된 반도체 소자를 갖는 소자 기판을 형성하고, 소자 기판 위에 유기 화합물 또는 무기 화합물의 섬유체를 제공하고, 소자 기판 및 섬유체 위에 유기 수지를 포함하는 조성물을 도포하고, 유기 수지를 섬유체에 함침시키고 소자 기판을 가열함으로써, 소자 기판 위에 유기 화합물 또는 무기 화합물의 섬유체를 포함하는 밀봉층을 형성하여, 반도체 장치를 제작하는 것을 특징으로 한다.

[0008] 또한, 본 발명은, 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성된 반도체 소자를 갖는 소자 기판을 형성하고, 소자 기판 위로부터 유기 수지를 포함하는 조성물을 도포하여, 소자 기판 및 유기 수지 층 위에 유기 화합물 또는 무기 화합물의 섬유체를 제공하고, 유기 수지를 섬유체에 함침시키고 소자 기판을 가열함으로써, 소자 기판 위에 유기 화합물 또는 무기 화합물의 섬유체를 포함하는 밀봉층을 형성하여, 반도체 장치를 제작하는 것을 특징으로 한다.

[0009] 소자 기판의 두께는, 1μm이상 80μm이하, 또는 1μm이상 50μm이하, 또는 1μm이상 20μm이하, 1μm이상 10μm 이하, 또는 1μm이상 5μm이하이며, 밀봉층의 두께는 10μm이상 100μm이하인 것이 바람직하다. 이러한 두께로 함으로써 만곡이 가능한 반도체 장치를 제작할 수 있다.

[0010] 섬유체로서는, 유기 화합물 또는 무기 화합물의 고강도 섬유를 사용한 직포(織布) 또는 부직포(不織布)가 있다. 고강도 섬유로서는, 구체적으로는 인장탄성율이 높은 섬유이다. 또는, 영률(Young's modulus)이 높은 섬유이다.

[0011] 또한, 유기 수지로서는, 열 가소성 수지, 또는 열 경화성 수지를 사용할 수 있다.

[0012] 섬유체로서, 고강도 섬유를 사용함으로써, 반도체 장치에 국소적인 압력이 가해지더라도, 상기 압력이 섬유체 전체에 분산되어, 반도체 장치의 일부가 연신되는 것을 방지할 수 있다. 즉, 일부의 연신에 따른 배선, 반도체 소자 등의 파괴를 방지할 수 있다.

## 효과

[0013] 본 발명에 의하여, 외부로부터 국소적인 압력이 가해져도 쉽게 파괴되지 않고, 신뢰성이 높은 반도체 장치를 수율 높게 제작할 수 있다.

## 발명의 실시를 위한 구체적인 내용

[0014] 이하에 본 발명의 실시형태를 도면에 의거하여 설명한다. 그러나, 본 발명은 많은 다른 모양으로 실시하는 것이 가능하고, 본 발명의 형태 및 상세한 사항은 본 발명의 취지 및 범위에서 벗어남이 없이 다양하게 변경될 수 있다는 것은 당업자라면 용이하게 이해할 수 있다. 따라서, 본 발명이 하기 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다. 또한, 실시형태를 설명하기 위한 모든 도면에 있어서, 동일 부분 또는 동일 기능을 갖는 부분에는 동일한 부호를 붙이고, 그 반복 설명은 생략한다.

[0015] (실시형태 1)

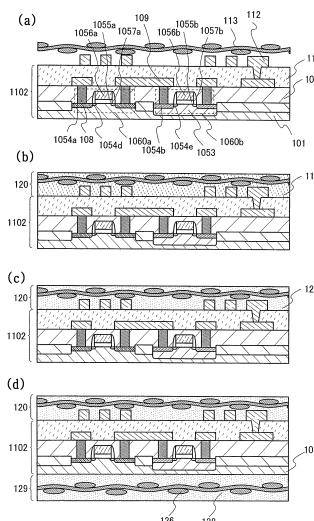

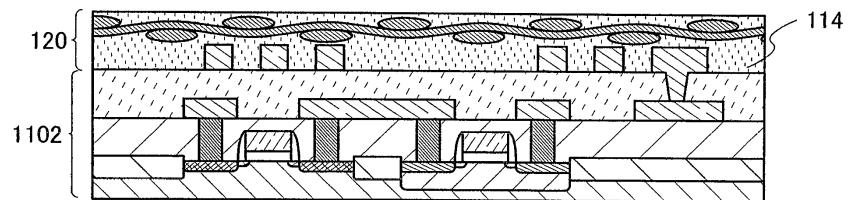

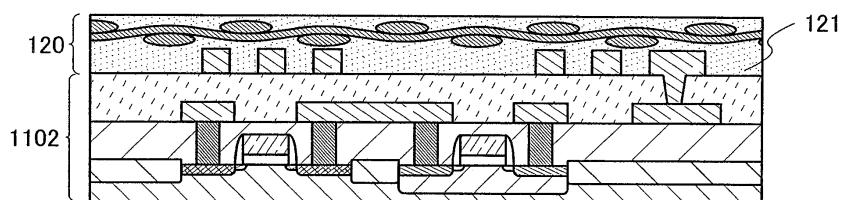

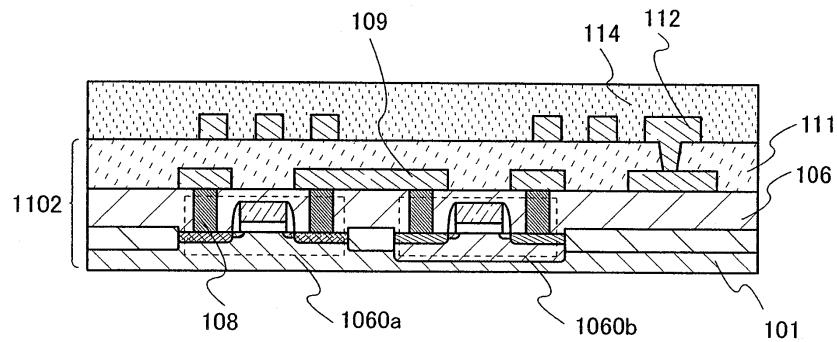

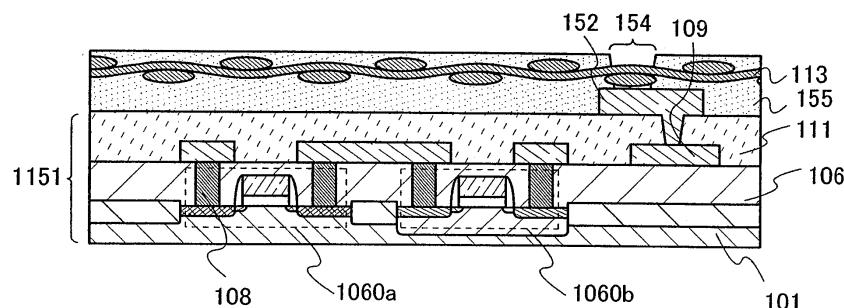

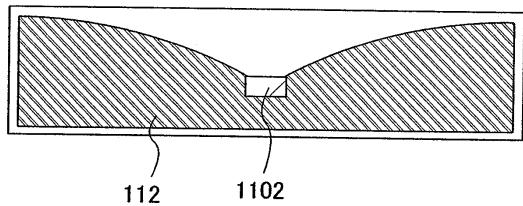

[0016] 본 실시형태에서는, 외부로부터의 국소적인 압력이 가해져도 쉽게 파괴되지 않는 반도체 장치를 수율 높게 제작하는 방법을 도 1a 내지 도 1d를 사용하여 나타낸다.

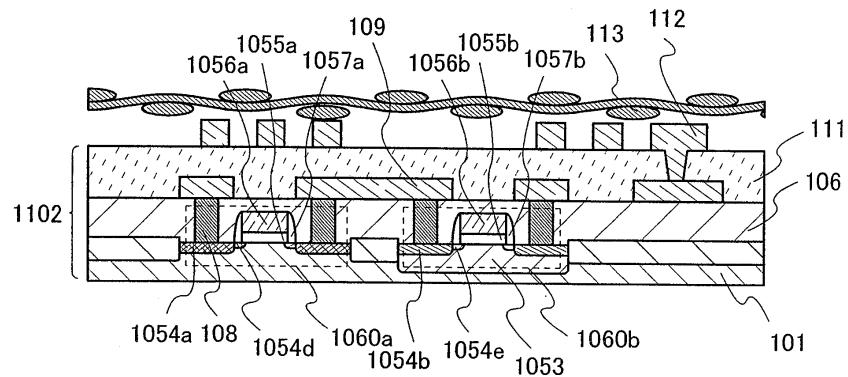

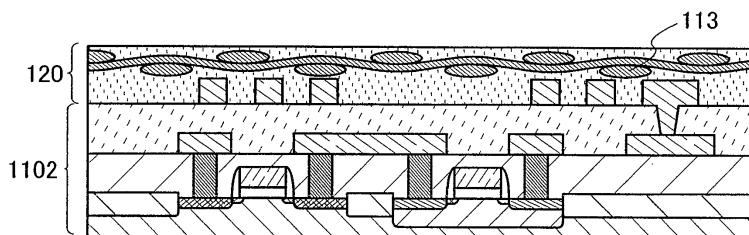

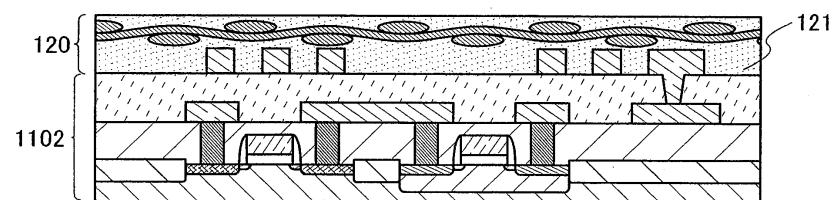

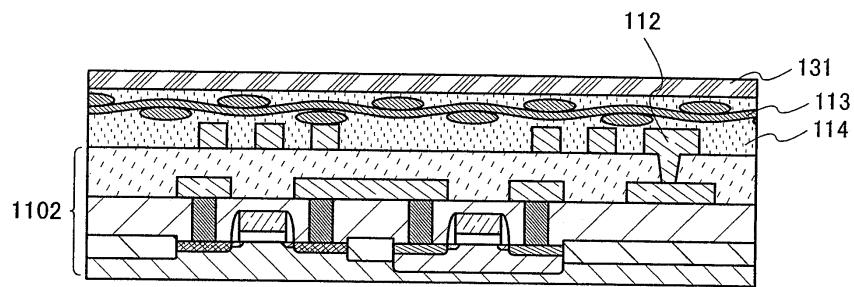

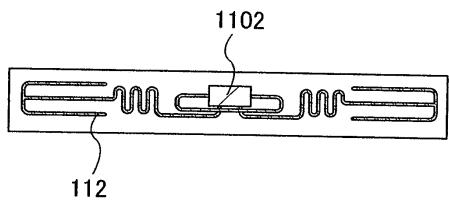

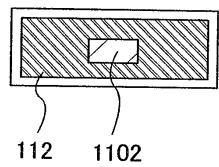

[0017] 도 1a에 도시하는 바와 같이, 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판(1102) 및 안테나(112)를 형성한다. 다음, 소자 기판(1102) 및 안테나(112) 위에 섬유체(113)를 제공한다.

[0018] 소자 기판(1102)에 포함되는 반도체 소자의 대표 예로서는, MOS 트랜ジ스터, 다이오드, 비휘발성 기억 소자 등의 능동 소자, 저항 소자, 용량 소자 등의 수동 소자가 있다. 또한, 단결정 반도체 기판으로서는, 대표적으로는, n형 또는 p형의 도전형을 갖는 단결정 규소 기판(실리콘 웨이퍼), 화합물 반도체 기판(GaAs 기판, InP 기판, GaN 기판, SiC 기판, 사파이어 기판, ZnSe 기판 등)을 사용하는 것이 바람직하다. 또한, SOI(Si-On-Insulator) 기판을 사용할 수도 있다. SOI 기판으로서, 경면(鏡面) 연마 웨이퍼에 산소 이온을 주입한 후, 고온 어닐함으로써, 표면으로부터 일정한 깊이에 산화층을 형성시키는 것과 동시에, 표면층에 생긴 결함을 소멸시켜 만들어진 소위 SIMOX(Separation by IMplanted OXygen) 기판이나, 수소 이온 주입에 의하여 형성된 미소 보이드(void)의 열 처리에 의한 성장을 이용하여 Si 기판을 벽개(劈開)하는 스마트 컷 기술이나 ELTRAN(Epitaxial Layer Transfer : 캐논사의 등록상표)법을 이용하여 형성한 SOI 기판을 이용하여도 좋다. 소자 기판(1102)의 두께로서는,  $1\mu\text{m}$  이상  $80\mu\text{m}$  이하, 또는  $1\mu\text{m}$  이상  $50\mu\text{m}$  이하, 또는  $1\mu\text{m}$  이상  $20\mu\text{m}$  이하,  $1\mu\text{m}$  이상  $10\mu\text{m}$  이하, 또는  $1\mu\text{m}$  이상  $5\mu\text{m}$  이하인 것이 바람직하다. 이러한 두께로 함으로써, 만곡이 가능한 반도체 장치를 제작할 수 있다. 또한, 반도체 장치의 상면의 면적은,  $4\text{mm}^2$  이상, 또는  $9\text{mm}^2$  이상인 것이 바람직하다.

[0019] 소자 기판(1102)에 적어도 MOS 트랜ジ스터, 저항 소자, 용량 소자, 배선 등이 형성되는 경우, 반도체 장치로서 다른 장치의 제어나 데이터의 계산이나 가공을 행하는 마이크로 프로세서(MPU)를 제작할 수 있다. MPU는, CPU, 메인 메모리, 컨트롤러, 인터페이스, I/O포트 등을 가진다.

[0020] 또한, 소자 기판(1102)에, 적어도 기억 소자 및 MOS 트랜ジ스터가 형성되는 경우, 반도체 장치로서 기억 장치를 제작할 수 있다. 기억 소자로서는, 플로팅 게이트 또는 전하축적 층을 갖는 비휘발성 기억소자, MOS 트랜ジ스터 및 그것에 접속되는 용량 소자, MOS 트랜ジ스터 및 그것에 접속되는 강유전 층을 갖는 용량 소자, 한 쌍의 전극 사이에 유기 화합물 층이 끼워진 유기 메모리 소자 등이 있다. 또한, 이러한 기억 소자를 갖는 반도체 장치로서는, DRAM(Dynamic Random Access Memory), SRAM(Static Random Access Memory), FeRAM(Ferroelectric Random Access Memory), 마스크 ROM(Read Only Memory), EEPROM(Electrically Programmable Read Only Memory), EEPROM(Electrically Erasable and Programmable Read Only Memory), 플래시 메모리 등의 기억 장치가 있다.

[0021] 소자 기판(1102)에, 적어도 다이오드가 형성되는 경우, 반도체 장치로서 광 센서, 이미지 센서, 형태 전지 등을 제작할 수 있다. 다이오드로서는, 아모페스 실리콘이나 폴리실리콘을 사용한 PN 다이오드, PIN 다이

오드, 애벌란시 다이오드, 쇼트키 다이오드 등의 다이오드가 있다.

[0022] 소자 기판(1102)에, 적어도 MOS 트랜지스터를 형성하고, MOS 트랜지스터에 전기적으로 접속하는 안테나를 소자 기판(1102) 위에 형성하는 경우, 반도체 장치로서는 무선으로 정보를 송수신하는 것이 가능한 ID태그, IC태그, RF(Radio Frequency)태그, 무선 태그, 전자 태그, RFID(Radio Frequency Identification)태그, IC카드, ID카드 등(이하, RFID라고 나타낸다)을 제작할 수 있다. 또한, 본 발명의 반도체 장치는, MOS 트랜지스터 등으로 구성되는 집적 회로부와 안테나를 밀봉한 인렛(inlet)이나, 상기 인렛을 씰(seal)형상이나 카드 형상으로 한 것도 포함한다. 또한, RFID의 상면의 면적을  $4\text{mm}^2$  이상, 또한  $9\text{mm}^2$  이상으로 함으로써, 안테나의 사이즈를 크게 형성할 수 있기 때문에, 통신기와의 통신 거리가 긴 RFID를 제작할 수 있다.

[0023] 또한, 여기서는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성된 반도체 소자를 포함하는 소자 기판(1102)으로서는, MOS 트랜지스터(1060a, 1060b), MOS 트랜지스터(1060a, 1060b)를 덮는 절연층(106), 절연층(106)을 통하여 MOS 트랜지스터(1060a)의 소스 영역과 드레인 영역, 및 MOS 트랜지스터(1060b) 웨爾 영역의 소스 영역과 드레인 영역에 접속하는 도전층(108, 109), 도전층(108, 109) 및 절연층(106)의 일부를 덮는 절연층(111)을 나타낸다. 또한, 소자 기판(1102) 위에는, 절연층(111)을 통하여 도전층(109)에 접속하는 안테나(112)를 나타낸다.

[0024] MOS 트랜지스터(1060a)는, 적어도 반도체 기판(101), 불순물 영역(1054a), 게이트 절연막(1055a), 게이트 전극(1056a)으로 구성된다. 또한, MOS 트랜지스터(1060b)는 적어도 웨爾 영역, 불순물 영역(1054b), 게이트 절연막(1055b), 게이트 전극(1056b)으로 구성된다. 반도체 기판(101)이 n형인 경우에는, 웨爾 영역으로서 p형 불순물이 주입된 p웨爾 영역(1053)이 형성되어 있다. p형 불순물로서, 예를 들면 붕소가 사용되어,  $5 \times 10^{15} \text{cm}^{-3}$  내지  $1 \times 10^{16} \text{cm}^{-3}$  정도의 농도로 첨가되어 있다. p웨爾 영역(1053)을 형성함으로써, 이 영역에 n채널형의 트랜지스터를 형성할 수 있다. 또한, p웨爾 영역(1053)에 첨가하는 p형 불순물은, MOS 트랜지스터의 임계 잠전압을 제어하는 작용도 있다. 반도체 기판(101) 및 p웨爾 영역(1053)에 형성되는 채널형성 영역은, 게이트 전극(1056a, 1056b)과 대략 일치하는 영역에 형성되는 것이고, 반도체 기판(101), p웨爾 영역(1053)에 형성되는 한 쌍의 불순물 영역(1054a, 1054b, 1054d, 1054e) 사이에 위치한다.

[0025] 한 쌍의 불순물 영역(1054a, 1054b)은, MOS 트랜지스터에 있어서 소스 영역 및 드레인 영역으로서 기능하는 영역이다. 한 쌍의 불순물 영역(1054a, 1054b)은 각각 n형 불순물인 인 혹은 비소, p형 불순물인 붕소를 피크 농도  $10^{21} \text{cm}^{-3}$ 로 첨가함으로써 형성된다.

[0026] 게이트 전극(1056a, 1056b)의 측벽에는, 스페이서(1057a, 1057b)가 형성되고, 그 단부(端部)에 있어서 누설 전류를 방지하는 효과가 있다. 또한, 이 스페이서(1057a, 1057b)를 이용하여, 게이트 전극(1056a, 1056b)의 채널 길이 방향의 양쪽 단부의 아래 쪽에 저농도 불순물 영역(1054d, 1054e)을 형성할 수 있다. 이 저농도 불순물 영역(1054d, 1054e)은, 저농도 드레인(LDD)으로서 기능한다. 저농도 불순물 영역(1054d, 1054e)은 필수적인 구성이 아니지만, 이 영역을 형성함으로써 드레인단의 전계를 완화하고 MOS 트랜지스터의 열화를 억제 할 수 있다.

[0027] 게이트 절연막(1055a, 1055b)은, 열처리를 행하여, 반도체 기판(101)의 표면을 산화시킴으로써 산화규소막으로 형성할 수 있다. 또한, 열 산화법에 의하여 산화규소막을 형성한 후에, 질화 처리를 행함으로써 산화규소막의 표면을 질화시켜, 산화규소막과 산소와 질소를 갖는 막(산질화규소막)의 적층 구조로 형성할 수 있다. 게이트 절연막(1055a, 1055b)은, 두께 5nm 내지 50nm의 산화규소 및 산화질화규소 등의 무기 절연물로 형성한다.

[0028] 게이트 전극(1056a, 1056b)은 탄탈(Ta), 텅스텐(W), 티탄(Ti), 몰리브덴(Mo), 크롬(Cr), 니오브(Nb) 등으로부터 선택된 금속, 또는 이를 금속을 주성분으로 하는 합금 재료 또는 화합물 재료로 형성하는 것이 바람직하다. 또한, 인 등의 불순물 원소를 첨가한 다결정 실리콘을 사용할 수 있다. 또한, 1층 또는 복수 층의 금속 질화물층과 상기 금속의 금속층의 적층 구조로 제어 게이트 전극을 형성하여도 좋다. 금속 질화물로서는, 질화 텅스텐, 질화 몰리브덴, 질화 티탄을 사용할 수 있다. 금속 질화물층을 형성함으로써, 금속 질화물층 위에 형성되는 금속층의 밀착성을 향상시킬 수 있고, 박리를 방지할 수 있다.

[0029] 절연층(106)은 MOS 트랜지스터 및 배선으로서 기능하는 도전층을 절연하기 위한 충간 절연층으로서 기능한다. 절연층(106)은 CVD법이나 스퍼터링법 등에 의하여, 산화규소, 질화규소, 산화질화규소, 질화산화규소 등의 산소 또는 질소를 갖는 절연층이나, DLC(Diamond Like Carbon) 등의 탄소를 함유하는 층, 에폭시, 폴리이

미드, 폴리아미드, 폴리비닐페놀, 벤조시클로부텐, 아크릴 등의 유기 재료 또는 실록산 수지 등의 실록산 재료로 이루어지는 단층 또는 적층 구조로 형성할 수 있다.

[0030] 도전층(108, 109)은, 배선, 플래그(flag) 등으로서 기능한다. 도전층(108, 109)은 CVD법이나 스퍼터링 법 등에 의하여, 알루미늄(Al), 텅스텐(W), 티탄(Ti), 탄탈(Ta), 몰리브덴(Mo), 니켈(Ni), 백금(Pt), 구리(Cu), 금(Au), 은(Ag), 망간(Mn), 네오디뮴(Nd), 탄소(C), 규소(Si)로부터 선택된 원소, 또는 이들 원소를 주성분으로 하는 합금 재료 또는 화합물 재료로 단층 또는 적층으로 형성한다. 알루미늄을 주성분으로 하는 합금 재료란, 예를 들면, 알루미늄을 주성분으로 하고 니켈을 함유하는 재료, 또는 알루미늄을 주성분으로 하고, 니켈과, 탄소와 규소 중의 한쪽 또는 양쪽 모두를 함유하는 합금 재료에 상당한다. 도전층(108, 109)은, 예를 들면, 배리어막과 알루미늄 규소(Al-Si)막과 배리어막의 적층 구조, 배리어막과 알루미늄 규소(Al-Si)막과 질화티탄(TiN)막과 배리어막의 적층 구조를 채용하면 좋다. 또한, 배리어 막이란, 티탄, 티탄의 질화물, 몰리브덴, 또는 몰리브덴의 질화물로 이루어지는 박막에 상당한다. 알루미늄이나 알루미늄 규소는 저항값이 낮고 저렴하기 때문에, 도전층(108, 109)을 형성하는 재료로서 최적이다. 또한, 상층과 하층에 배리어막을 형성하면, 알루미늄이나 알루미늄-규소의 힐록(hilllock)의 발생을 방지할 수 있다. 또한, 환원성이 높은 원소인 티탄으로 된 배리어 막을 형성하면, 반도체 기판 위에 얹은 자연 산화막이 생성되어 있어도, 이 자연 산화막을 환원하여, 반도체 기판과 양호한 콘택트를 취할 수 있다.

[0031] 또한, 도전층(109) 및 절연층(106) 위에 보호막으로서 기능하는 절연층이 형성되어도 좋다. 절연층은, 질화규소, 질화산화규소, 산화질화규소, 산화규소, 질화탄소, DLC(Diamond-Like Carbon) 등으로 형성된다. 보호막을 이온 보조 증착(IAD)으로 형성하면, 치밀한 보호막을 형성할 수 있다. 보호막으로서 기능하는 절연층을 형성함으로써, 외부로부터 MOS 트랜지스터에 수분이 침입을 하는 것을 방지할 수 있고, 특히 치밀한 보호막을 형성함으로써 그 효과는 보다 높아진다. 즉, MOS 트랜지스터 및 반도체 장치의 전기적인 특성의 신뢰성을 높일 수 있다.

[0032] 또한, 절연층(106) 위에 도전층 및 상기 도전층을 절연하는 절연층을 한 쌍 또는 복수 쌍 형성하여, 다층 구조로 하여도 좋다. 다층 구조로 함으로써, 고집적화할 수 있다.

[0033] 안테나(112)는, 은(Ag), 금(Au), 구리(Cu), 니켈(Ni), 백금(Pt), 팔라듐(Pd), 탄탈(Ta), 몰리브덴(Mo), 및 티탄(Ti) 등의 어느 1개 이상의 금속 입자를 갖는 액적이나 페이스트를 액적 토출법(잉크젯 법, 디스펜서 법 등)에 의하여 토출하고, 건조 소성하여 형성한다. 액적 토출법에 의하여 안테나를 형성함으로써, 공정 수를 저감할 수 있고, 이에 따라 비용을 삭감할 수 있다.

[0034] 또한, 스크린 인쇄법을 사용하여 안테나(112)를 형성하여도 좋다. 스크린 인쇄법을 사용하는 경우, 안테나(112)의 재료로서는, 입경이 수nm 내지 수십μm의 도전성 입자를 유기 수지에 용해, 또는 분산시킨 도전성 페이스트를 선택적으로 인쇄한다. 도전성 입자로서는, 은(Ag), 금(Au), 구리(Cu), 니켈(Ni), 백금(Pt), 팔라듐(Pd), 탄탈(Ta), 몰리브덴(Mo), 및 티탄(Ti) 등의 어느 1개 이상의 금속 입자나 할로겐화 은의 미립자, 또는 분산성 나노 입자를 사용할 수 있다. 또한, 도전성 페이스트에 포함되는 유기 수지는, 금속 입자의 바인더, 용매, 분산제 및 괴복제로서 기능하는 유기 수지로부터 선택된 1개 또는 복수를 사용할 수 있다. 대표적으로는, 에폭시 수지, 실리콘(silicone) 수지 등의 유기 수지를 들 수 있다. 또한, 도전층을 형성할 때, 도전성의 페이스트를 압출(押出)한 후에 소성하는 것이 바람직하다.

[0035] 또한, 안테나(112)는 스크린 인쇄법 이외에도 그라비아 인쇄법 등을 사용하여도 좋고, 도금법, 스퍼터링법 등을 사용하여, 도전성 재료에 의하여 형성할 수 있다.

[0036] 여기서는, 스퍼터링법 등에 의하여 알루미늄 층을 형성한 후, 포토리소그래피 공정에 의하여 형성한 레지스트 마스크를 사용하여 선택적으로 에칭하고, 안테나(112)를 형성한다.

[0037] 또한, RFID의 신호의 전송 방식으로서, 전자 결합방식(electromagnetic coupling) 또는 전자 유도방식(electromagnetic induction)(예를 들면, 13.56MHz 대역)을 적용한다. 자속(磁束) 밀도의 변화에 의한 전자 유도를 이용하는 경우, 안테나의 상면 형상을 링(ring) 형상(예를 들면, 루프 안테나), 나선 형상(예를 들면, 스파이럴 안테나)으로 형성할 수 있다.

[0038] 또한, RFID에 있어서의 신호의 전송 방식으로서, 마이크로파 방식(예를 들면, UHF 대역(860MHz 내지 960MHz 대역), 2.45GHz 대역 등)을 적용할 수도 있다. 그 경우에는, 신호의 전송에 사용하는 전자파의 파장을 고려하여, 안테나의 길이 등의 형상을 적절히 설정하면 좋다.

[0039] 마이크로파 방식을 적용할 수 있는 RFID 안테나(112)의 예를 도 9a 내지 도 9d에 도시한다. 예를

들면, 안테나의 상면 형상을 선 형상(예를 들면, 디아폴(dipole) 안테나(도 9a 참조)), 평탄한 형상(예를 들면, 패치(patch) 안테나(도 9b 참조)), 또는 리본형의 형상(도 9c, 도 9d 참조) 등으로 형성할 수 있다. 또한, 안테나로서 기능하는 도전층의 형상은 선 형상에 한정되지 않고, 전자파의 파장을 고려하여 곡선 형상이나 지그재그 형상, 또는 이들을 조합한 형상이라도 좋다.

[0040] 또한, 소자 기판(1102)은, 이면부(裏面部)가 일부 제거되어 박막화되어 있는 것이 바람직하다. 이면부를 일부 제거하는 방법으로서는, 물리적 연마 및 화학적 제거가 있다. 물리적 연마는, 반도체 기판의 표면(반도체 소자가 형성되는 측)에 보호 테이프를 붙인 후, 반도체 기판의 이면을 기계 연마하고, 화학적 기계 연마에 의하여 이면을 연마한다. 또한, 화학적 제거는, SF<sub>6</sub>, CF<sub>4</sub> 등의 가스를 사용한 건식 에칭, 그리고 플루오르화수소, 질산, 초산 혼합액, 또는 수산화 칼륨 수용액을 사용한 웨트 에칭 등이 있다. 대표적으로는, 소자 기판(1102)의 두께가 1μm 이상 80μm 이하, 또는 1μm 이상 50μm 이하, 또는 1μm 이상 20μm 이하, 또는 1μm 이상 10μm 이하, 또는 1μm 이상 5μm 이하인 것이 바람직하다. 또한, 반도체 기판의 일부를 박리하여, 소자 기판(1102)을 박막화하여도 좋다.

[0041] 소자 기판(1102)의 일 표면, 또는 양쪽 면에 제공되는 섬유체(113)는, 유기 화합물 또는 무기 화합물의 고강도 섬유를 사용한 직포 또는 부직포이며, 소자 기판(1102)의 전면을 덮는다. 고강도 섬유로서는, 구체적으로는, 인장탄성율이 높은 섬유이다. 또한, 영률이 높은 섬유이다. 고강도 섬유의 대표 예로서는, 폴리비닐알콜 섬유, 폴리에스테르 섬유, 폴리아미드 섬유, 폴리에틸렌 섬유, 아라미드 섬유, 폴리파라페닐렌 벤조비스옥사졸 섬유, 유리 섬유, 또는 탄소 섬유이다. 유리 섬유로서는, E유리, S유리, D유리, Q유리 등을 사용한 유리 섬유를 사용할 수 있다. 또한, 섬유체(113)는, 일 종류의 상기 고강도 섬유로 형성되어도 좋다. 또한, 복수 종류의 상기 고강도 섬유로 형성되어도 좋다.

[0042] 또한, 섬유체(113)는, 섬유(단사(單絲))의 다발(이하, 사속(絲束)이라고 한다)을 날실(經絲) 및 씨실(緯絲)에 사용하여 제작한 직포, 또는 복수종의 섬유의 사속을 웬덤 또는 일 방향에 퇴적시킨 부직포로 구성되어도 좋다. 직포의 경우, 평직(平織), 능직(綾織), 수자직(satin-woven fabric) 등, 적절히 사용할 수 있다.

[0043] 사속의 단면은, 원형이라도 타원형이라도 좋다. 사속으로서 고압수류, 액체를 매체로 한 고주파 진동, 연속 초음파 진동, 룰에 의한 가압 등에 의하여, 개섬(開纖) 가공을 한 사속을 사용하여도 좋다. 개섬 가공을 한 사속은, 사속 폭이 넓어지고, 두께 방향의 단사(單絲)수를 삭감할 수 있고, 사속의 단면이 타원형, 또는 평판 형상이 된다. 또한, 사속으로서 저연사(低撲絲)를 사용함으로써, 사속이 편평화하기 쉽고, 사속의 단면 형상이 타원 형상, 또는 평판 형상이 된다. 이와 같이, 단면이 타원형, 또는 평판 형상의 사속을 사용함으로써, 섬유체(113)의 두께를 얇게 할 수 있다. 그래서, 박형의 반도체 장치를 제작할 수 있다. 사속 폭은, 4μm 이상 400μm 이하, 또는 4μm 이상 200μm 이하에 있어서, 본 발명의 효과가 확인되어, 원리상으로는, 보다 가늘어도 좋다. 또한, 사속의 두께는 4μm 이상 20μm 이하에 있어서, 본 발명의 효과가 확인되어, 원리상으로는 보다 얇아도 좋고, 그들은 섬유의 재료에 의존한다.

[0044] 또한, 본 명세서의 도면에 있어서는, 섬유체(113)는 단면이 타원형의 사속으로 평직한 직포로 표시된다. 또한, MOS 트랜지스터(1060a, 1060b)가 섬유체(113)의 사속보다 크지만, MOS 트랜지스터(1060a, 1060b)가 섬유체(113)의 사속보다 작은 경우도 있다.

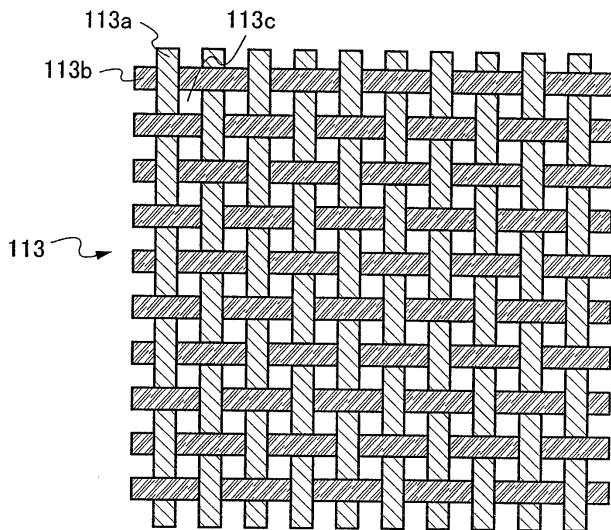

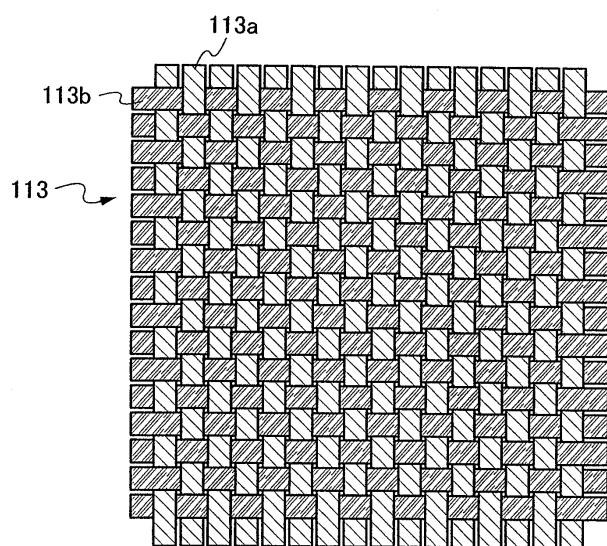

[0045] 섬유체(113)가 사속을 날실, 및 씨실을 사용하여 제작한 직포의 상면도를 도 8a 내지 도 8b에 나타낸다.

[0046] 도 8a에 도시하는 바와 같이, 섬유체(113)는 일정 간격을 둔 날실(113a) 및 일정 간격을 둔 씨실(113b)로 짜인다. 이러한 섬유체에는, 날실(113a) 및 씨실(113b)이 존재하지 않는 영역(바스켓 홀(113c)이라고 한다)을 가진다. 이러한 섬유체(113)는, 유기 수지가 섬유체에 함침되는 비율이 높아지고, 섬유체(113) 및 소자 기판의 밀착성을 높일 수 있다.

[0047] 도 8b에 도시하는 바와 같이, 섬유체(113)는 날실(113a) 및 씨실(113b)의 밀도가 높고, 바스켓 홀(113c)의 비율이 낮은 것이라도 좋다. 대표적으로는, 바스켓 홀(113c)의 사이즈가 국소적으로 가압되는 면적보다 작은 것이 바람직하다. 대표적으로는, 1변이 0.01mm 이상 0.2mm 이하의 직사각형인 것이 바람직하다. 섬유체(113)의 바스켓 홀(113c)의 면적이 이와 같이 작으면, 선단이 가는 부재(대표적으로는, 펜이나 연필 등의 필기구)에 의하여 가압되어도 상기 압력을 섬유체(113) 전체로 흡수할 수 있다.

[0048] 또한, 사속 내부로의 유기 수지의 함침율을 높이기 위하여, 섬유에 표면 처리를 행하여도 좋다. 예를 들면, 섬유 표면을 활성화시키기 위한 코로나 방전 처리, 플라즈마 방전 처리 등이 있다. 또한, 실란

커플링제, 티타네이트 커플링제를 사용한 표면 처리가 있다.

[0049] 다음, 도 1b에 도시하는 바와 같이, 섬유체(113) 및 소자 기판(1102) 위로부터 유기 수지를 포함하는 조성물을 도포하여, 유기 수지층(114)을 형성한다. 유기 수지층(114)은, 애폴시 수지, 불포화 폴리에스테르 수지, 폴리이미드 수지, 비스말레이이미드 트리아진 수지, 또는 시아네이트 수지 등의 열 경화성 수지를 사용할 수 있다. 또한, 폴리페닐렌 옥사이드 수지, 폴리에테르이미드 수지, 또는 불소 수지 등의 열 가소성 수지를 사용할 수 있다. 또한, 복수의 상기 열 가소성 수지 및 상기 열 경화성 수지를 사용하여도 좋다. 상기 유기 수지를 사용함으로써, 열 처리에 의하여 섬유체를 소자 기판에 고착할 수 있다. 또한, 유기 수지층(114)은, 유리 전이 온도가 높을수록 국소적인 가압에 대하여 쉽게 파괴되지 않기 때문에 바람직하다.

[0050] 유기 수지층(114)의 형성 방법으로서는, 인쇄법, 캐스팅 법, 액적 토출법, 딥 코팅법 등을 사용할 수 있다.

[0051] 이 때, 유기 수지층(114) 중의 일부, 또는 전부를 섬유체(113)에 함침시킨다. 즉, 섬유체(113)는 유기 수지층(114) 중에 포함된다. 이렇게 함으로써, 섬유체(113) 및 유기 수지층(114)의 밀착력이 높아진다.

[0052] 유기 수지층(114), 또는 섬유체의 사속 내에 고열 전도성 필러를 분산시켜도 좋다. 고열 도전성 필러로서는, 질화알루미늄, 질화붕소, 질화규소, 알루미나 등이 있다. 또한, 고열 도전성 필러로서는, 은, 구리 등의 금속입자가 있다. 고열 도전성 필러가 유기 수지, 또는 사속내에 포함됨으로써 소자 기판에서의 발열을 외부로 방출하기 쉽게 되기 때문에, 반도체 장치의 축열을 억제하는 것이 가능하고, 반도체 장치의 불량을 저감할 수 있다.

[0053] 다음, 유기 수지층(114)을 가열하여, 유기 수지층(114)의 유기 수지를 가소화 또는 경화한다. 또한, 유기 수지가 가소성 유기 수지의 경우, 그 후, 실온으로 냉각함으로써 가소화한 유기 수지를 경화한다.

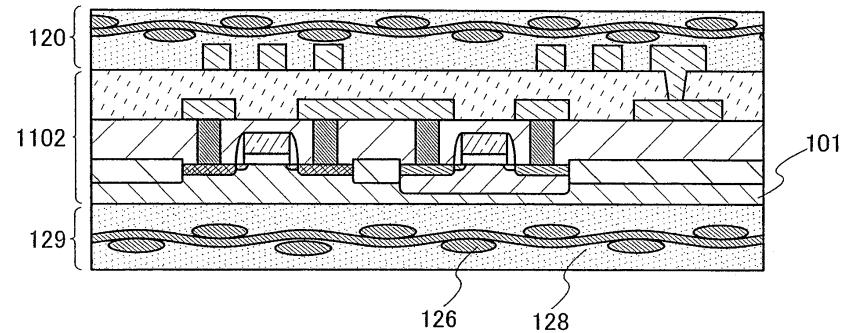

[0054] 이 결과, 도 1c에 도시하는 바와 같이, 섬유체(113)에 함침하고, 또 소자 기판(1102) 및 안테나(112)의 한쪽의 면에 고착된 유기 수지층(121)이 된다. 또한, 소자층(102) 및 안테나(112)의 한쪽의 면에 고착된 유기 수지층(121) 및 섬유체(113)를 밀봉층(120)으로서 나타낸다.

[0055] 또한, 소자 기판(1102)에 복수의 반도체 장치가 포함되는 경우, 소자 기판(1102) 및 밀봉층을 분단하여 복수의 반도체 장치를 잘라내어도 좋다. 이러한 공정에 의하여, 복수의 반도체 장치를 제작할 수 있다.

[0056] 이상과 같이, 반도체 장치를 제작할 수 있다.

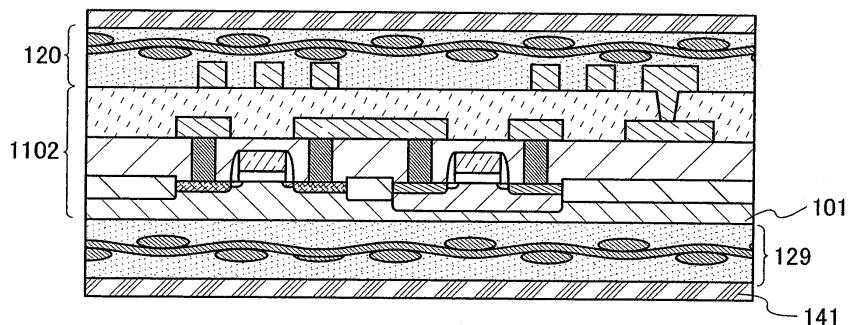

[0057] 또한, 반도체 기판(101) 측에도 밀봉층을 형성하여도 좋다. 반도체 기판(101) 위에 섬유체(126)를 제공한다. 섬유체(126)는, 도 1a에 도시하는 섬유체(113)를 적절히 사용할 수 있다. 섬유체(126) 및 소자 기판(1102) 위로부터 유기 수지를 포함하는 조성물을 도포하고, 소성하여 유기 수지층을 형성한다. 유기 수지층은, 도 1b에 도시하는 유기 수지층(114)을 적절히 사용할 수 있다. 다음, 유기 수지층을 가열하고, 유기 수지층의 유기 수지를 가소화 또는 경화한다. 유기 수지가 가소성인 경우, 이 후, 실온으로 냉각함으로써 가소화한 유기 수지를 경화한다. 이 결과, 도 1d에 도시하는 바와 같이, 섬유체(126)에 함침하여, 또 반도체 기판(101)에 형성되는 유기 수지층(128)으로 이루어지는 밀봉층(129)을 형성할 수 있다. 즉, 소자 기판(1102)의 양쪽의 면에 밀봉층(120, 129)이 형성되는 반도체 장치를 제작할 수 있다.

[0058] 이 때의 밀봉층(120, 129)이, 동일한 재질인 섬유체 및 유기 수지로 형성되어 있는 것이 훨 현상을 저감하기 위해서는 바람직하지만, 표리(表裏)를 판별하여 사용하는 용도의 경우에는, 반드시 동일한 재질일 필요는 없다. 이와 같이, 소자 기판의 양쪽의 면을 섬유체에 함침되는 유기 수지가 고착됨으로써, 섬유체에 의하여 지지되기 때문에 반도체 장치의 훨 현상을 감소시킬 수 있고, 후의 라미네이트 필름이나 씰 등에 상기 반도체 장치를 탑재하는 것이 용이해진다.

[0059] 또한, 소자 기판(1102)에 형성되는 밀봉층(120)의 섬유체의 날실 또는 씨실의 방향과 밀봉층(129)의 섬유체의 날실 또는 씨실의 방향이  $30^{\circ}$  이상  $60^{\circ}$  이하, 바람직하게는  $40^{\circ}$  이상  $50^{\circ}$  이하 어긋나게 되어도 좋다. 이 경우, 소자 기판의 표리에 제공되는 섬유체의 인장방향이 표리에 따라 다르기 때문에, 국소적으로 가압할 때의 연신이 등방적으로 된다. 그래서, 국소적인 가압에 의한 파괴를 보다 저감할 수 있다.

[0060] 또한, 도 1a 내지 도 1d에 있어서는, 소자 기판(1102) 위에 섬유체(113)를 제공한 후, 유기 수지층(114)을 형성하였지만, 이 대신 소자 기판(1102)에 유기 수지층(114)을 형성한 후, 섬유체를 소자 기판(1102) 및 유기 수지층(114) 위에 제공하여도 좋다. 이 공정에 대하여 이하에 나타낸다.

- [0061] 도 2a에 도시하는 바와 같이, 반도체 기판(101) 위에 단결정 반도체 기판 또는 SOI 기판을 이용하여 소자 기판(1102)을 형성하고, 소자 기판(1102) 위에 안테나(112)를 형성한다. 다음, 소자 기판(1102) 및 안테나(112) 위에 유기 수지층(114)을 형성한다.

- [0062] 다음, 도 2b에 도시하는 바와 같이, 소자 기판(1102) 및 안테나(112) 위에 섬유체(113)를 제공한다. 이 때, 유기 수지층(114)에 섬유체(113)를 누름으로 유기 수지층(114) 중에 섬유체(113)를 포함시킬 수 있다. 또한, 섬유체(113) 내에 유기 수지를 함침시킬 수 있다.

- [0063] 다음, 유기 수지층(114)을 가열하여 유기 수지층(114)의 유기 수지를 가소화 또는 경화한다. 또한, 유기 수지가 가소성 유기 수지인 경우, 그 후 실온으로 냉각함으로써 가소화한 유기 수지를 경화한다.

- [0064] 이 결과, 도 2c에 도시하는 바와 같이, 섬유체(113)에 함침하고, 또 소자 기판(1102) 및 안테나(112)의 편면에 고착되는 유기 수지층(121)이 된다. 또한, 소자 기판(1102) 및 안테나(112)의 편면에 고착된 유기 수지층(121) 및 섬유체(113)를 밀봉층(120)으로 도시한다.

- [0065] 이 후, 도 1d와 마찬가지로 반도체 기판(101) 위에 밀봉층(129)을 형성하여도 좋다.

- [0066] 이상과 같이, 반도체 장치를 제작할 수 있다.

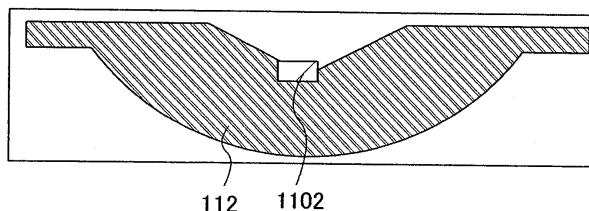

- [0067] 여기서, 본 실시 형태에서 나타내는 반도체 장치가 갖는 효과에 대하여, 도 3a 내지 도 3d를 사용하여 나타낸다.

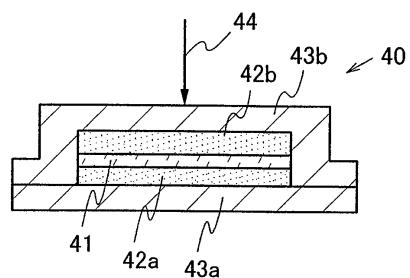

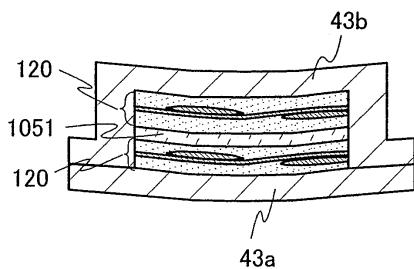

- [0068] 도 3a에 도시하는 바와 같이, 종래의 반도체 장치(40)는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판(41)이 접착재(42a, 42b)를 사용하여 필름(43a, 43b)으로 밀봉된다. 이러한 반도체 장치에 국소적인 가압(44)을 가한다.

- [0069] 그 결과, 도 3b에 도시하는 바와 같이, 소자 기판(41)을 구성하는 층, 접착재(42a, 42b), 필름(43a, 43b)이 각각 연신되어 버리고, 가압부에 있어서 곡률 반경이 작은 만곡이 생겨 버린다. 이 결과, 소자 기판(41)을 구성하는 반도체 소자, 배선 등에 균열이 생겨 반도체 장치가 파괴되어 버린다.

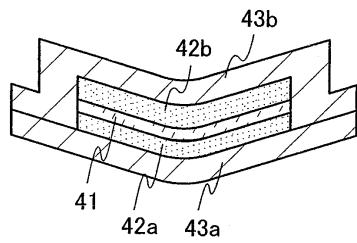

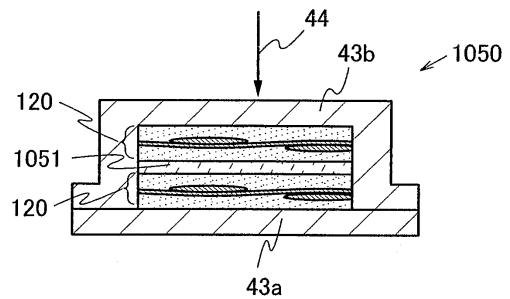

- [0070] 그렇지만, 본 실시형태에서 나타내는 반도체 장치(1050)는, 도 3c에 도시하는 바와 같이, 소자 기판(1051)의 편면, 또는 양쪽의 면에는 유기 수지를 함유하는 섬유체로 이루어지는 밀봉층이 형성된다. 섬유체는 고강도 섬유로 형성되어 있고, 고강도 섬유는 인장탄성율, 또는 영률이 높다. 그래서, 점압(点壓)이나 선압(線壓) 등의 국소적인 가압(44)이 가해져도 고강도 섬유는 연신되지 않고, 가압된 힘이 섬유체 전체에 분산되어, 반도체 장치 전체로 만곡하게 된다. 이 결과, 도 3d에 도시하는 바와 같이, 국소적인 가압이 가해져도 반도체 장치에서 생긴 만곡은, 곡률 반경이 큰 것이 되어, 소자 기판(1051)을 구성하는 반도체 소자, 배선 등에 균열이 생기지 않고, 반도체 장치의 파괴를 저감시킬 수 있다.

- [0071] 또한, 소자 기판(1051)의 두께를 얇게 함으로써, 반도체 장치를 만곡시킬 수 있게 된다. 그래서, 소자 기판(1051)의 면적을 보다 크게 할 수 있고, 반도체 장치를 제작하는 공정이 용이해진다. 또한, 상기 반도체 장치가 안테나를 내장하는 RFID의 경우, 안테나의 크기를 증대시킬 수 있다. 그래서, 통신 거리가 긴 RFID를 제작할 수 있다.

- [0072] 또한, 소자 기판(1102)에 복수의 반도체 장치가 포함되는 경우, 소자 기판(1102) 및 밀봉층을 분단하여, 복수의 반도체 장치를 잘라내어도 좋다. 이러한 공정에 의하여, 복수의 반도체 장치를 제작할 수 있다. 분단할 때는, 다이싱, 스크라이빙, 가위나 나이프 등의 날붙이를 갖는 재단기, 또는 레이저 컷법 등에 의하여 선택적으로 분단할 수 있다.

- [0073] 또한, 반도체 장치를 종이에 내장시킴으로써, 반도체 장치를 포함하는 종이를 형성할 수 있다. 구체적으로는, 제 1 습지(濕紙) 위에 반도체 장치를 형성한다. 그 위에 제 2 습지를 배치하여, 압착 및 건조한다. 이 결과, 반도체 장치를 포함하는 종이를 형성할 수 있다. 그 후, 상기 종이를 적절한 크기로 절단하여도 좋다.

- [0074] 본 실시형태에서 나타내는 반도체 장치는, 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 갖는 소자 기판과, 섬유체가 유기 수지로 고착되어 있다. 섬유체는, 국소적인 가압에 의한 압력을 섬유 전체에 분산하기 때문에 국소적으로 압력이 쉽게 가해지지 않는다. 그래서, 반도체 장치를 구성하는 배선이나 반도체 소자가 연신되지 않고, 반도체 장치가 쉽게 파괴되지 않는다. 즉, 소자 기판에 형성되는 반도체 소자, 배선 등이 연신되는 것을 저감할 수 있다. 그래서, 수율을 향상시킬 수 있다.

- [0075] 또한, 소자 기판의 두께를 얇게 함으로써, 반도체 장치를 만곡시킬 수 있게 된다. 그래서, 소자 기판의 면적을 보다 크게 할 수 있고, 반도체 장치를 제작하는 공정이 용이해진다. 또한, 상기 반도체 장치가 안테나를 내장하는 RFID의 경우, 안테나의 크기를 증대시킬 수 있다. 그래서, 통신 거리가 긴 RFID를 제작할 수 있다.

- [0076] (실시형태 2)

- [0077] 본 실시형태에서는, 실시 형태 1과 비교하여, 보다 쉽게 파괴되지 않는 반도체 장치의 제작 방법을 도 4a 내지 도 4c를 사용하여 설명한다.

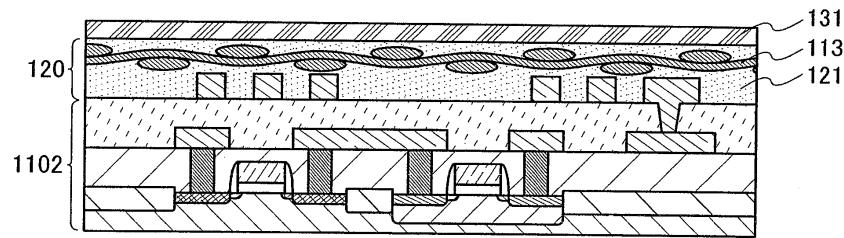

- [0078] 실시형태 1과 마찬가지로, 도 4a에 도시하는 바와 같이, 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판(1102) 및 안테나(112)를 형성한다. 다음, 소자 기판(1102) 및 안테나(112) 위에 섬유체(113)를 제공하고, 유기 수지층(114)을 형성하고, 유기 수지층(114) 위에 보호 필름(131)을 형성한다.

- [0079] 보호 필름(131)으로서는, 고강도 재료로 형성되어 있는 것이 바람직하다. 고강도 재료의 대표적인 예로서는, 폴리비닐알콜 수지, 폴리에스테르 수지, 폴리아미드 수지, 폴리에틸렌 수지, 아라미드 수지, 폴리파라페닐렌벤조비스옥사졸 수지, 유리 수지 등이 있다.

- [0080] 보호 필름(131)이 고강도 재료로 형성되어 있는 것으로, 실시형태 1과 비교하여 국소적인 가압에 의한 파괴를 억제할 수 있다. 구체적으로는, 섬유체(113)에 있어서, 날실속 및 씨실속이 분포되지 않는 바스켓 홀의 면적이 국소적으로 압력이 가해지는 면적보다 큰 경우, 바스켓 홀이 국소적으로 하중되면, 상기 압력이 섬유체(113)에서 흡수되지 않고, 직접 소자 기판(1102) 및 안테나(112)에 가해져 벼린다. 이 결과, 소자층(102) 및 안테나(112)가 연신되어, 반도체 소자 또는 배선이 파괴되어 벼린다.

- [0081] 그렇지만, 고강도 재료로 형성되는 보호 필름(131)을 유기 수지층(114) 위에 형성함으로써, 국소적인 하중을 보호 필름(131) 전체로 흡수하기 때문에 국소적인 가압에 의한 파괴가 적은 반도체 장치가 된다.

- [0082] 다음, 도 4b에 도시하는 바와 같이, 실시형태 1과 마찬가지로, 유기 수지층(114)을 가열하고 밀봉층(120)을 형성한다. 또한, 밀봉층(120)의 유기 수지는 보호 필름(131)을 소자 기판(1102) 및 안테나(112)에 고착한다. 즉, 밀봉층(120)은, 섬유체(113) 및 보호 필름(131)을 소자 기판(1102) 및 안테나(112)에 고착한다. 또한, 밀봉층(120)에 포함되는 유기 수지층(121)은, 섬유체(113) 중에 함침된다.

- [0083] 다음, 도 4c에 도시하는 바와 같이, 소자 기판(1102)의 반도체 기판(101)에 섬유체를 제공하고, 유기 수지층을 형성하고, 유기 수지층 위에 보호 필름(141)을 형성하고, 가열하여 압착하고, 밀봉층(129)에 의하여 보호 필름(141)을 소자 기판(1102)에 고착하여도 좋다.

- [0084] 또한, 도 4a에 있어서, 보호 필름(131)이 열 가소성 재료인 경우, 소자 기판(1102) 및 안테나(112)와 섬유체(113)의 사이에 보호 필름(131)을 형성하여 가열 압착하여도 좋다. 또한, 소자 기판(1102), 안테나(112) 및 섬유체(113)와 유기 수지층(114)의 사이에 보호 필름(131)을 형성하여 가열 압착하여도 좋다. 또한, 도 4c에 있어서, 보호 필름(141)이 열 가소성 재료인 경우, 소자 기판(1102)과 섬유체의 사이에 보호 필름(141)을 형성하여 가열 압착하여도 좋다. 또한, 소자 기판(1102) 및 섬유체와 유기 수지층과의 사이에 보호 필름(141)을 형성하여 가열 압착하여도 좋다. 상기 구조에 있어서도, 국소적인 가압에 의한 하중을 보호 필름 및 섬유체로 분산시킬 수 있고, 파괴를 저감할 수 있다.

- [0085] 또한, 소자 기판(1102)에 복수의 반도체 장치가 포함되는 경우, 소자 기판(1102) 및 밀봉층을 분단하여, 복수의 반도체 장치를 잘라내어도 좋다. 이러한 공정에 의하여, 복수의 반도체 장치를 제작할 수 있다.

- [0086] 또한, 실시형태 1과 마찬가지로 반도체 장치를 종이에 내장시킴으로써, 반도체 장치를 포함하는 종이를 형성할 수 있다.

- [0087] 이상과 같이, 국소적인 가압에 의한 파괴가 적은 반도체 장치를 제작할 수 있다. 또한, 소자 기판의 두께를 얇게 함으로써, 반도체 장치를 만곡시킬 수 있게 된다. 그래서, 소자 기판의 면적을 보다 크게 할 수 있고, 반도체 장치를 제작하는 공정이 용이해진다. 또한, 상기 반도체 장치가 안테나를 내장하는 RFID의 경우, 안테나의 크기를 증대시킬 수 있다. 그래서, 통신 거리가 긴 RFID를 제작할 수 있다.

- [0088] (실시형태 3)

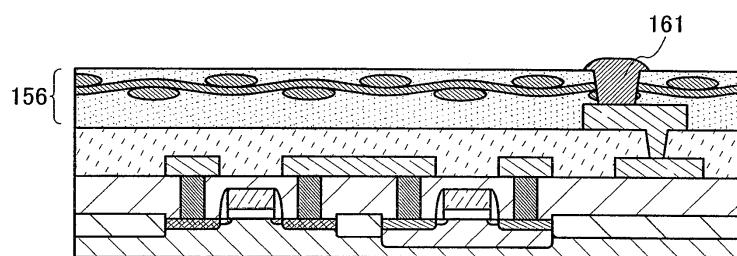

- [0089] 본 실시형태에서는, 소자층에 안테나가 형성되지 않고, 다른 기판에 형성된 안테나를 소자층에 접속한 반도체 장치의 제작 방법에 대하여, 도 5a 내지 도 7c를 사용하여 설명한다.

- [0090] 도 5a에 도시하는 바와 같이, 소자 기판(1151) 위에 섬유체(113) 및 개구부(154)를 갖는 유기 수지층(155)을 형성한다.

- [0091] 여기서는, 소자 기판(1151)으로서는 실시형태 1에 나타내는 바와 같이, 반도체 기판(101)에 MOS 트랜지스터(1060a, 1060b)를 형성한다. MOS 트랜지스터(1060a, 1060b) 위에 절연층(106)을 형성하고, 절연층(106)을 통하여 MOS 트랜지스터의 소스 영역 및 드레인 영역에 접속하는 도전층(108, 109)을 형성한다. 도전층(108, 109), 절연층(106) 위에 절연층(111)을 형성하고, 절연층(111)을 통하여 도전층(109)과 접속하는 전극 패드(152)를 형성한다.

- [0092] 유기 수지층(155)은, 전극 패드(152)의 일부를 노출하는 바와 같은 개구부(154)를 가지고 유기 수지를 유기 용재로 희석한 조성물을 인쇄법, 또는 액적토출법에 의하여 소자 기판(1151) 위에 형성하여 건조 소성하여 형성한다.

- [0093] 다음, 도 5b에 도시하는 바와 같이, 유기 수지층(155)의 개구부에 접속 단자(161)를 형성한다. 접속 단자(161)는, 인쇄법, 액적토출법 등에 의하여 형성할 수 있다. 접속 단자(161)의 재료로서는, 은(Ag), 금(Au), 구리(Cu), 니켈(Ni), 백금(Pt), 팔라듐(Pd), 탄탈(Ta), 몰리브덴(Mo) 및 티탄(Ti) 등의 어느 하나 이상의 금속 입자나, 할로겐화은의 미립자, 또는 분산성 나노 입자를 사용할 수 있다. 다음, 유기 수지층(153) 및 접속 단자(161)의 재료를 소성하여, 소자 기판(1151)의 편면에 유기 수지층(155) 및 섬유체(113)로 이루어지는 밀봉층(156)을 형성한다. 또한, 밀봉층(156)에는, 전극 패드(152)에 접속하는 접속 단자(161)가 형성된다.

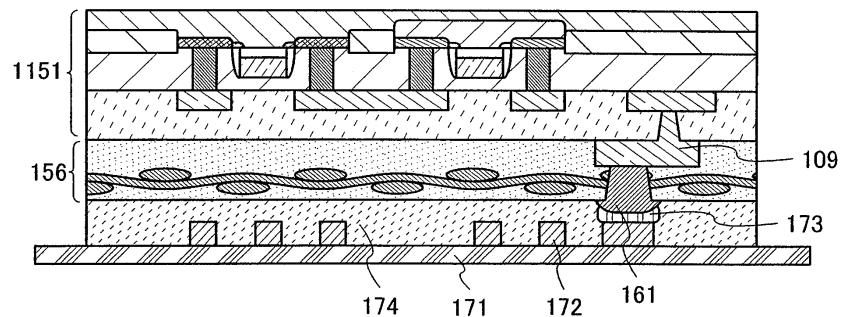

- [0094] 그 후, 도 5c에 도시하는 바와 같이, 소자 기판(1151)에 고착된 밀봉층(156)과, 안테나(172)가 형성된 기판(171)을 접착재(174)로 접착한다. 이 때, 소자 기판(1151)에 형성된 접속 단자(161)와 안테나(172)를 이방성 도전 접착재(173)를 사용하여 전기적으로 접속한다.

- [0095] 이방성 도전 접착재(173)로서는, 분산된 도전성 입자(입경이 수nm 내지 수십 $\mu$ m)를 함유하는 접착성 수지이며, 예폭시 수지, 폐놀 수지 등을 들 수 있다. 또한, 도전성 입자는 금, 은, 구리, 팔라듐, 니켈, 탄소, 또는 백금으로부터 선택된 일 원소, 혹은, 복수의 원소로 형성된다. 또한, 이들의 원소의 다층 구조를 갖는 입자라도 좋다. 또한, 수지로 형성된 입자의 표면에 금, 은, 구리, 팔라듐, 니켈, 또는 백금으로부터 선택된 일 원소, 혹은, 복수의 원소로 형성되는 박막이 형성된 도전성 입자를 사용하여도 좋다. 또한, 도전성 입자로서 CNT(카본 나노튜브)를 사용하여도 좋다.

- [0096] 안테나(172)로서는, 실시형태 1에 나타내는 안테나(112)와 동일한 재료 및 형성 방법을 적절히 사용할 수 있다.

- [0097] 안테나(172)가 형성된 기판(171)으로서는, 필름 형상의 플라스틱 기판, 예를 들면, 폴리에틸렌 테레프탈레이트(PET), 폴리에테르설휘(PES), 폴리에틸렌 나프탈레이트(PEN), 폴리카보네이트(PC), 나일론, 폴리에테르케톤(PEEK), 폴리설휘(PSF), 폴리에테르 이미드(PEI), 폴리아릴레이트(PAR), 폴리부틸렌 테레프탈레이트(PBT) 등을 사용할 수 있다.

- [0098] 다음, 도 6a에 도시하는 바와 같이, 실시형태 1과 마찬가지로, 반도체 기판

- [0099] (101) 표면에 밀봉층(129)을 형성하여도 좋다.

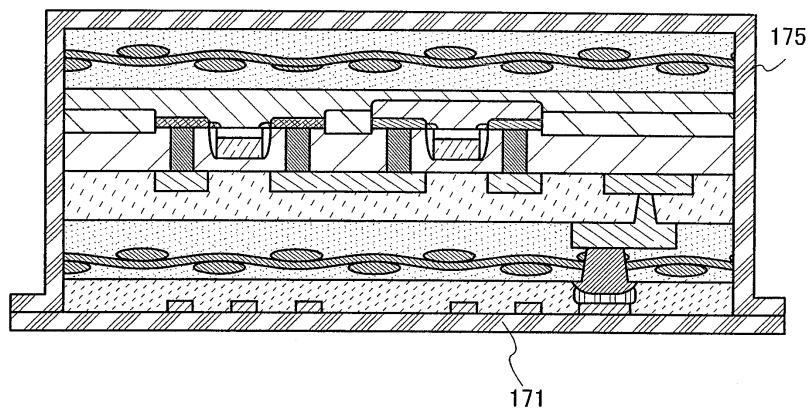

- [0100] 다음, 도 6b에 도시하는 바와 같이, 안테나(172)가 형성되는 기판(171)과 밀봉층(156), 소자 기판(1151) 및 밀봉층(129)을 밀봉하도록 필름(175)을 형성하여도 좋다. 필름으로서는, 안테나(172)가 형성된 기판(171)과 마찬가지의 필름을 사용할 수 있다.

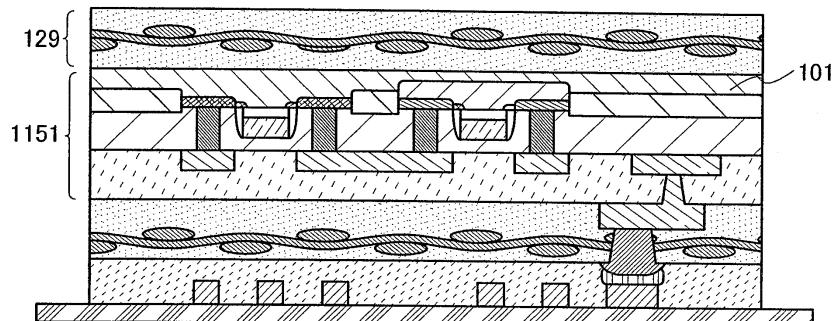

- [0101] 상기 형태에서는, 안테나(172)를 갖는 기판(171)이 소자 기판(1151)의 한쪽의 면에만 접착된 반도체 장치를 나타냈지만, 소자 기판(1151)의 양쪽의 면에 각각 안테나가 형성된 기판을 접착하여도 좋다. 그 형태를 도 7a 내지 도 7c를 사용하여 이하에 나타낸다.

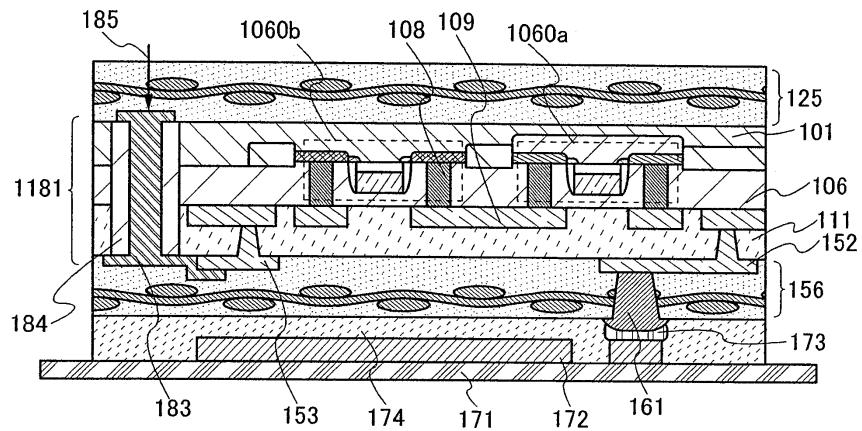

- [0102] 소자 기판(1181)으로서는, 실시형태 1에 나타내는 바와 같이, 반도체 기판(101)에 MOS 트랜지스터(1060a, 1060b)를 형성한다. MOS 트랜지스터(1060a, 1060b) 위에 절연층(106)을 형성하고, 절연층(106)을 통하여 MOS 트랜지스터 소스 영역 및 드레인 영역에 접속하는 도전층(108, 109)을 형성한다. 도전층(108, 109), 절연층(106) 위에 절연층(111)을 형성하고, 절연층(111)을 통하여 도전층(109)과 접속하는 전극 패드(152) 및 도

전층(153)을 형성한다.

[0103] 다음, 반도체 기판(101), 절연층(106), 절연층(111)에 관통 구멍을 형성하고, 관통 구멍의 표면에 관통 전극(183)을 형성한다. 또한, 관통 전극(183)은, 도전층(153)에 접한다. 또한, 관통 전극(183)은, 절연층(184)에 의하여 반도체 기판(101)과 절연되어 있다.

[0104] 이 후, 상기 소자 기판(1181)의 일 표면에 도 5a 및 도 5b와 유사한 공정에 의하여, 접속 단자(161)를 형성한다. 다음, 도 5c와 유사한 공정에 의하여, 안테나(172)가 형성된 기판(171)과 소자 기판(1181)의 한쪽의 면에 형성된 밀봉층(156)이 접착재(174)로 접착된다.

[0105] 또한, 소자 기판(1181)의 다른 쪽의 면(즉, 절연층(103) 표면)에는, 밀봉층(129)이 형성된다.

[0106] 다음, 소자 기판(1181)의 반도체 기판(101) 위에 섬유체를 제공하여, 유기 수지층을 형성한 후, 가열 압착하여 밀봉층(125)을 형성한다. 다음, 관통 전극(183)에 접속하는 접속 단자를 형성하기 위하여, 밀봉층(125)에 개구부를 형성한다. 여기서는, 밀봉층(125)으로부터 관통 전극(183)에 이르는 개구부를 레이저 범위 조사에 의하여 형성하고, 관통 전극(183)을 일부 노출시킨다.

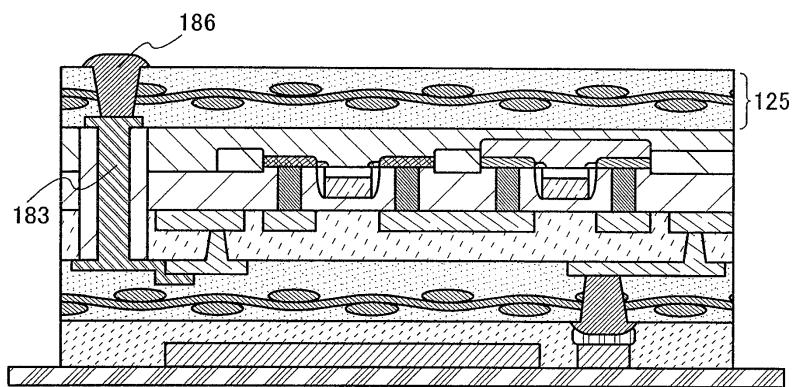

[0107] 다음, 도 7b에 도시하는 바와 같이, 개구부를 충전하도록 접속 단자(186)를 형성한다. 접속 단자(186)는 접속 단자(161)와 마찬가지로 형성할 수 있다.

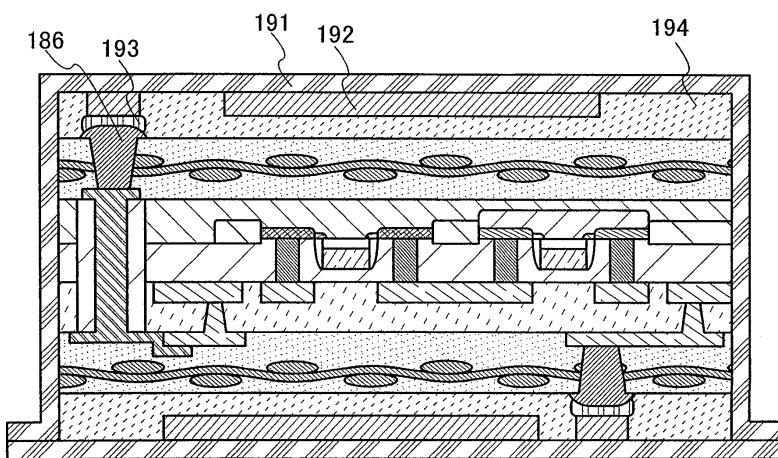

[0108] 다음, 도 7c에 도시하는 바와 같이, 밀봉층(129)과 안테나(192)가 형성된 기판(191)을 접착하는 것과 함께, 접속 단자(186) 및 안테나(192)를 이방성 도전 접착재(193)로 전기적으로 접속한다.

[0109] 이상과 같이, 소자 기판의 양쪽의 면에 안테나가 형성된 반도체 장치를 제작할 수 있다. 이러한 반도체 장치는, UHF대역의 전파가 수신 가능한 RFID와 같이, 대칭 구조인 안테나를 갖는 반도체 장치일 때 사용하면, 반도체 장치의 크기를 작게 할 수 있으므로 바람직하다.

[0110] 또한, 소자 기판(1151, 1181)에 복수의 반도체 장치가 포함되는 경우, 소자 기판(1151, 1181) 및 밀봉층을 분단하여, 복수의 반도체 장치를 잘라내어도 좋다. 이러한 공정에 의하여, 복수의 반도체 장치를 제작할 수 있다.

[0111] 또한, 실시형태 1과 마찬가지로 반도체 장치를 종이에 내장시킴으로써 반도체 장치를 포함하는 종이를 형성할 수 있다.

[0112] 본 실시형태에서 나타내는 반도체 장치는, 단결정 반도체 기판, 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 갖는 소자 기판과 섬유체가 유기 수지로 고착되어 있다. 섬유체는, 국소적인 가압에 의한 압력을 섬유 전체에 분산하기 때문에, 국소적으로 압력이 쉽게 가해지지 않는다. 그래서, 반도체 장치를 구성하는 배선이나 반도체 소자가 연신되지 않고, 반도체 장치가 쉽게 파괴되지 않는다. 즉, 소자 기판에 형성되는 반도체 소자, 배선 등이 연신되는 것을 저감할 수 있고, 수율을 향상시킬 수 있다.

[0113] 또한, 소자 기판의 두께를 얇게 함으로써, 반도체 장치를 만곡시킬 수 있게 된다. 그래서, 소자 기판의 면적을 보다 크게 할 수 있다. 그래서, 외부 안테나를 소자 기판에 접속할 때, 접속 면적을 크게 할 수 있고, 반도체 장치를 제작하는 공정이 용이해진다. 또한, 상기 반도체 장치가 안테나를 내장하는 RFID의 경우, 안테나의 크기를 증대시킬 수 있다. 그래서, 통신 거리가 긴 RFID를 제작할 수 있다.

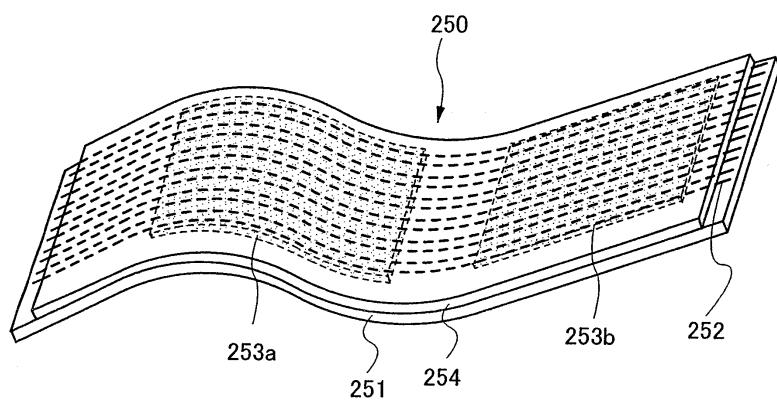

[0114] (실시형태 4)

[0115] 본 실시형태에서는, 실시형태 1 내지 실시형태 3에서 나타내는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판이 프린트 기판에 접속된 반도체 장치에 대하여 도 10a 및 도 10b를 사용하여 설명한다.

[0116] 도 10a는, 본 실시형태의 반도체 장치(250)의 사시도를 나타낸다. 반도체 장치(250)는, 플렉시블 프린트 기판에 실시형태 1 내지 실시형태 3에 나타내는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판이 형성된다. 예를 들면, 폴리에스테르, 폴리이미드 등으로 형성되는 베이스 필름(251) 위에 구리, 금, 은, 알루미늄 등으로 형성되는 배선(252)이 형성된다. 또한, 배선(252) 위에 절연층을 통하여 실시형태 1 내지 실시형태 3에 나타내는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판 및 밀봉층의 적층체(253a, 253b)가 형성되어 있다. 또한, 배선(252) 및 적층체(253a, 253b)는, 밀봉층의 콘택트 홀에 형성된 접속 단자를 통하여 접속되어 있다. 베이스 필름(251), 배선(252) 및 적층체(253a, 253b)는, 보호 필름(254)으로 덮여 있다. 또한, 반도체 장치(250)의 단부에 있어서는,

보호 필름(254)의 일부가 절제(切除)되어, 커넥터 등의 외부 회로와 배선(252)이 노출되어 있다.

[0117] 소자 기판은, 밀봉층을 끼워 베이스 기판에 형성되고, 가열 압착함으로써 배선 및 베이스 기판에 소자 기판을 고착시킬 수 있다.

[0118] 또한, 여기서는 1층의 배선(252)을 갖는 반도체 장치를 나타냈지만, 이 대신 다층 배선구조이어도 좋다. 또한, 복수의 배선으로 적층체(253a, 253b)가 끼워져 있어도 좋다. 이와 같이, 배선을 다층으로 함으로써, 실장 밀도를 높일 수 있다.

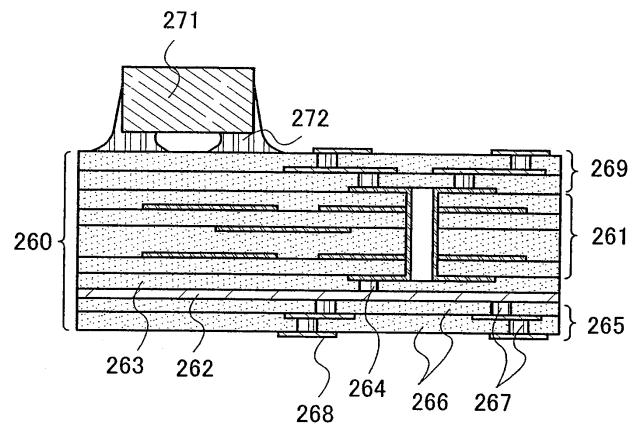

[0119] 도 10b는, 본 실시형태의 반도체 장치(260)의 단면도를 나타낸다. 반도체 장치(260)는, 프린트 기판에 실시형태 1 내지 실시형태 3에 나타내는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판이 형성된다. 예를 들면, 코어층(261)의 한쪽의 면에 실시형태 1 내지 실시형태 3에 나타내는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판(262)이 형성되어 있다. 또한, 코어층(261)과 실시형태 1 내지 실시형태 3에 나타내는 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 소자 기판(262)에 포함되는 반도체 소자, 또는 배선이 밀봉층(263)을 관통하는 비아(264)로 접속된다.

[0120] 또한, 소자 기판(262)에는 다층 배선(265)이 형성된다. 다층 배선(265)의 유기 수지층(266)에 형성되는 비아(267)에 의하여, 코어층(261), 소자 기판(262)에 형성되는 반도체 소자 및 배선 등이, 반도체 장치(260) 표면에 형성되는 도체 패턴(268)과 전기적으로 접속된다.

[0121] 또한, 코어층(261)의 다른 쪽 면에는, 다층 배선(269)이 형성되어 있다.

[0122] 또한, 반도체 장치(260)에 콘덴서, 코일, 저항, 다이오드 등의 첩(271)을 도전성 페이스트나 와이어 등의 실장 부재(272)로 실장하여도 좋다.

[0123] 본 실시형태의 반도체 장치는, 프린트 기판에 단결정 반도체 기판 또는 SOI 기판을 이용하여 형성되는 반도체 소자를 포함하는 층을 가진다. 또한, 섬유체를 사용한 프리프레그(prepreg)를 사용하여 소자 기판을 프린트 기판 내에 형성한다. 그래서, 국소적 하중(점압, 선압 등)이 가해져도 섬유체로 압력이 분산되기 때문에, 실장 공정이나 만곡에 의한 파괴를 저감할 수 있다. 또한, 고집적화가 가능하다.

[0124] (실시형태 5)

[0125] 본 실시형태에서는, 본 발명의 반도체 장치의 구성 및 응용예를 나타낸다. 여기서는, 반도체 장치의 대표 예로서 RFID 및 기억 장치에 대하여 설명한다.

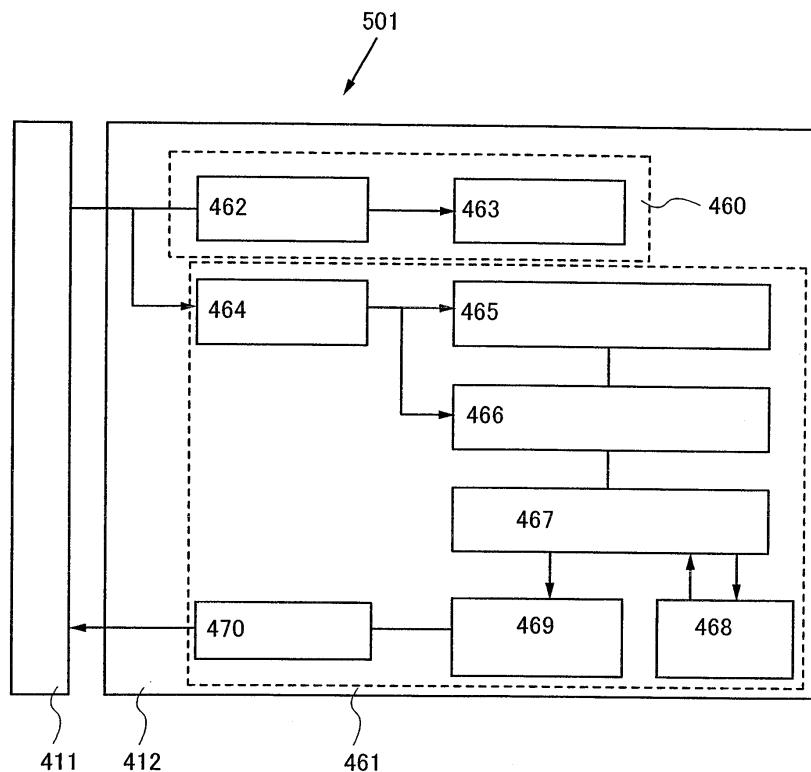

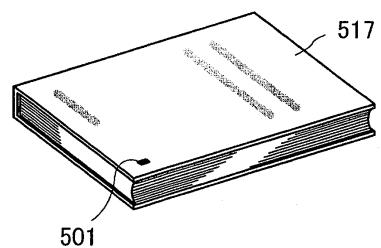

[0126] 처음, 본 발명의 반도체 장치의 하나인 RFID(501)의 회로 구성 예에 대하여 설명한다. 도 11에 RFID(501)의 회로 블록도를 나타낸다.

[0127] 도 11의 RFID(501)의 사양은, 국제표준 규격의 ISO 15693에 준거하여, 근방형이고, 교신신호 주파수는 13.56MHz이다. 또한, 수신은 데이터 판독 명령에만 대응하고, 송신의 데이터 전송 레이트는, 약 13kHz이고, 데이터 부호화 형식은, 맨체스터 코드를 사용한다.

[0128] RFID(501)의 회로부(412)는, 크게 나누어 전원부(460), 신호 처리부(461)로 구성된다. 전원부(460)는, 정류 회로(462)와 보유 용량(463)을 가진다. 또한, 전원부(460)에 안테나(411)로부터 수신 전력이 과잉인 경우, 내부 회로를 보호하기 위한 보호 회로부(리미터 회로부라고도 한다)와 보호 회로부를 동작 시킬지 말지를 제어하기 위한 보호회로 제어회로부를 형성하여도 좋다. 상기 회로부를 형성함으로써, RFID와 통신기와의 통신 거리가 극단적으로 짧은 상황 등에 있어서, RFID가 대전력을 수신함으로써 생기는 문제를 방지 할 수 있고, RFID의 신뢰성의 향상을 도모할 수 있다. 즉, RFID 내부의 소자의 열화나, RFID 자체를 파괴하지 않고, RFID를 정상으로 동작시킬 수 있다.

[0129] 또한, 여기서 통신기관, RFID와 무선 통신에 의하여 정보의 송수신을 행하는 수단을 가지고 있으면 좋고, 예를 들면, 정보를 판독하는 리더나 판독 기능 및 기록 기능을 구비한 리더/라이터 등을 들 수 있다. 또한, 판독 기능과 기록 기능의 한쪽, 또는 양쪽 모두를 구비하는 휴대 전화기나 컴퓨터 등도 포함된다.

[0130] 정류 회로(462)는, 안테나(411)에서 수신된 반송파를 정류하여, 직류 전압을 생성한다. 보유 용량(463)은, 정류 회로(462)에서 생성된 직류 전압을 평활화한다. 전원부(460)에 있어서 생성된 직류 전압은, 전원 전압으로서 신호 처리부(461)의 각 회로에 공급된다.

- [0131] 신호 처리부(461)는, 복조 회로(464), 클록 생성/보정 회로(465), 인식/판정 회로부(466)와 메모리 컨트롤러(467), 마스크 ROM(468), 부호화 회로(469) 및 변조 회로(470)를 가진다.

- [0132] 복조 회로(464)는, 안테나에서 수신한 신호를 복조하는 회로이다. 복조 회로(464)에서 복조된 수신 신호는 클록 생성/보정 회로(465)와 인식/판정 회로부(466)에 입력된다.

- [0133] 클록 생성/보정 회로(465)는, 신호 처리부(461)의 동작에 필요한 클록 신호를 생성하고, 또 그것을 보정하는 기능을 가진다. 예를 들면, 클록 생성/보정 회로(465)는 전압 제어 발진회로(이하 VCO(Voltage Controlled Oscillator)회로)를 가지고, VCO회로의 출력력을 귀환 신호로 하여, 공급되는 신호와의 위상을 비교한다. 그리고, 입력되는 신호와 귀환 신호가 일정한 위상이 되도록, 부귀환(負歸還)에 의하여 출력신호를 조정한다.

- [0134] 인식/판정 회로(466)는, 명령 코드를 인식하여 판정한다. 인식/판정 회로부(466)가 인식하여, 판정하는 명령 코드는, 프레임 종료신호(EOF, end of frame), 프레임 개시 신호(SOF, start of frame), 플래그, 커맨드 코드, 마스크 길이(mask length), 마스크값(mask value) 등이다. 또한, 인식/판정 회로부(466)는, 송신 어려를 식별하는 순회 용장 검사(CRC, cyclic redundancy check) 기능도 포함한다.

- [0135] 메모리 컨트롤러(467)는, 인식/판정 회로부(466)에서 처리된 신호를 기초로, 마스크 ROM으로부터 데이터를 판독한다. 또한, 마스크 ROM(468)에, ID 등이 기억되어 있다. 마스크 ROM(468)을 탑재함으로써, 복제나 개찬(改撰)이 불가능한 판독 전용의 RFID(501)로서 구성된다. 이러한 판독 전용의 RFID를 종이에 내장시킴으로써, 위조 방지된 종이를 제공할 수 있다.

- [0136] 부호화 회로(469)는, 메모리 컨트롤러(467)가 마스크 ROM(468)으로부터 판독한 데이터를 부호화한다. 부호화된 데이터는, 변조 회로(470)에서 변조된다. 변조 회로(470)에서 변조된 데이터는, 안테나(411)로부터 반송파에 중첩되어 송신된다.

- [0137] 다음, RFID의 사용 예에 대하여 나타낸다. 본 발명의 RFID는 모든 종이 매체, 및 필름 매체에 사용할 수 있다. 특히, 본 발명의 RFID는, 위조 방지가 요구되는 모든 종이 매체에 사용할 수 있다. 예를 들면, 지폐, 호적 등본, 주민등록증, 여권, 운전 면허증, 신분증, 회원증, 감정서, 진찰권, 정기권, 어음, 수표, 화물 상환증, 선하증권, 창고증권, 주권(株券), 채권, 상품권, 티켓, 저당증권 등이다.

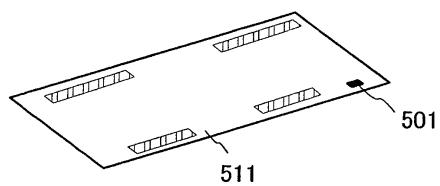

- [0138] 또한, 본 발명의 실시예에 의하여, 종이 매체 상에서 시각적으로 표시되는 많은 정보를 종이 매체, 및 필름 매체가 갖도록 할 수 있기 때문에, 본 발명의 RFID를 상품 라벨 등에 적용함으로써, 상품 관리의 전자 시스템화나 상품 도난의 방지에 이용할 수 있다. 이하, 도 12a 도 12e를 사용하여, 본 발명에 따른 종이의 사용 예를 설명한다.

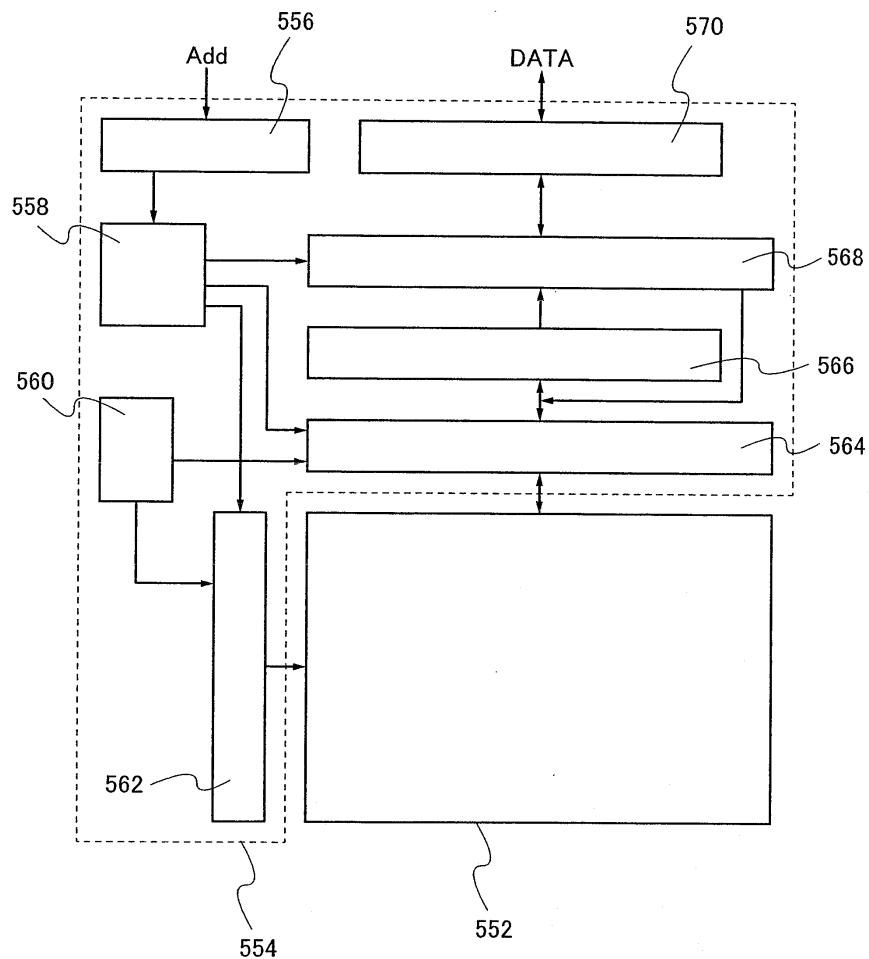

- [0139] 도 12a는 본 발명의 RFID(501)를 내장시킨 종이를 사용한 무기명 채권류(511)의 일례이다. 무기명 채권류(511)에는, 우표, 기차표, 티켓, 입장권, 상품권, 도서 상품권, 문구 상품권, 맥주 상품권, 쌀 상품권, 각종 기프트 상품권, 각종 서비스권 등이 포함되지만, 물론 이들에 한정되는 것이 아니다. 또한, 도 12b는 본 발명에 따른 RFID(501)를 내장시킨 종이를 사용한 증서류(512)(예를 들면, 주민등록증, 호적 등본)의 일례이다.

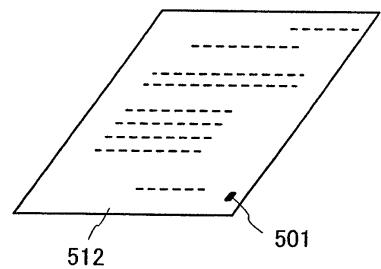

- [0140] 도 12c는 본 발명에 따른 RFID를 라벨에 적용한 일례이다. 라벨 대지(세퍼레이트지)(513) 위에, RFID(501)가 내장된 라벨(ID 씬)(514)이 형성되어 있다. 라벨(514)은 박스(515) 내에 수납되어 있다. 또한, 라벨(514) 위에는 그 상품이나 역무에 관한 정보(상품명, 브랜드, 상표, 상표권자, 판매자, 제조자 등)가 인쇄되어 있다. 한편, RFID(501)에는 그 상품(또는 상품의 종류) 고유의 ID 넘버가 기억되어 있어, 위조나, 상표권, 특허권 등의 지적 재산권 침해, 부정 경쟁 등의 불법 행위를 용이하게 피약할 수 있다. 또한, RFID(501) 내에는, 상품의 용기나 라벨에 다 명기할 수 없는 많은 정보, 예를 들면, 상품의 산지, 판매지, 품질, 원재료, 효능, 용도, 수량, 형상, 가격, 생산 방법, 사용 방법, 생산 시기, 사용시기, 유통기한, 취급 설명, 상품에 관한 지적 재산 정보 등을 입력해 둘 수 있다. 그래서, 거래자나 소비자는 간이한 통신기(리더)에 의하여 그들 정보에 액세스할 수 있다. 또한, 생산자 측으로부터는 용이하게 재기입, 소거 등도 가능하지만, 거래자나 소비자 측으로부터는 재기입, 소거 등을 할 수 없는 구조로 되어 있다.

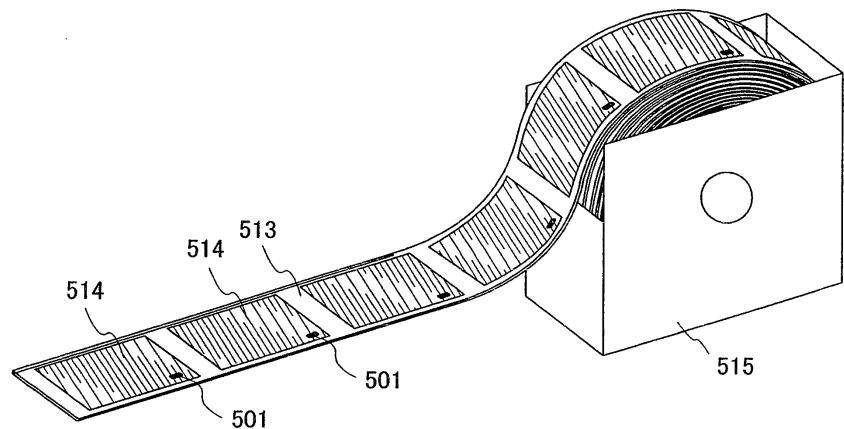

- [0141] 도 12d는, RFID(501)를 내장시킨 종이, 또는 필름으로 이루어지는 태그(516)를 나타낸다. RFID(501)를 내장시킨 종이, 또는 필름으로 태그(516)를 제작함으로써, 플라스틱의 케이스를 사용한 종래의 ID 태그보다 얄 값으로 제조할 수 있다. 도 12e는, 본 발명의 RFID를 표지에 사용한 서적(517)이고, 표지에 RFID(501)가 내장되어 있다.

- [0142] 본 발명의 반도체 장치의 일례인 RFID를 사용한 라벨(514)이나 태그(516)를 상품에 설치함으로써, 상품 관리가 용이해진다. 예를 들면, 상품이 도난 당한 경우에, 상품의 경로를 찾음으로써, 그 범인을 신속히 파악 할 수 있다. 이와 같이, 본 발명의 RFID를 ID 태그로서 사용함으로써, 상품의 원재료나 산지, 제조나 가공, 유통, 판매 등에 이르기까지의 이력 관리나 추적 조회를 할 수 있게 된다. 즉, 상품의 트레이서빌리티(traceability)를 가능하게 한다. 또한, 본 발명에 의하여, 상품의 트레이서빌리티 관리 시스템을 종래보다 저비용으로 도입할 수 있게 한다.

- [0143] 또한, 본 발명의 반도체 장치의 일례인 RFID는, 국소적인 가압에 의하여, 쉽게 파괴되지 않는다. 그래서, 본 발명의 반도체 장치의 일례인 RFID를 갖는 종이 매체, 및 필름 매체는, 붙이기, 또 설치하기 등의 처리에 있어서, 만곡시킬 수 있고, 처리 효율이 높아진다. 또한, 본 발명의 반도체 장치의 일례인 RFID를 갖는 종이 매체, 및 필름 매체에 필기구를 사용하여 정보를 기입할 수 있기 때문에, 사용 범위가 넓어진다.

- [0144] 다음, 본 발명의 반도체 장치의 일 형태인 기억 장치의 구성에 대하여, 이하에 나타낸다. 여기서는, 기억 장치의 대표적인 예로서 비휘발성 기억장치를 사용하여 나타낸다.

- [0145] 도 13은, 비휘발성 반도체 기억장치의 회로 블록도의 일례를 나타낸다. 비휘발성 반도체 기억장치는 메모리 셀 어레이(552)와 주변 회로(554)가 동일한 소자 기판 위에 형성되어 있다. 메모리 셀 어레이(552)는 실시형태 1에서 나타내는 바와 같은 비휘발성 기억소자를 가지고 있다. 주변 회로(554)의 구성은 이하와 같다.

- [0146] 워드 선을 선택하기 위하여, 행(行) 디코더(562)와, 비트 선을 선택하기 위하여, 열(列) 디코더(564)가 메모리 셀 어레이(552)의 주위에 형성되어 있다. 어드레스는 어드레스 버퍼(556)를 통하여 컨트롤 회로(558)로 보내지고, 내부 행 어드레스 신호 및 내부 열 어드레스 신호가 각각 행 디코더(562) 및 열 디코더(564)로 전송된다.

- [0147] 데이터 기입 및 소거에는 전원 전위를 승압한 전위가 사용된다. 그래서, 컨트롤 회로(558)에 의하여 동작 모드에 따라 제어되는 승압 회로(560)가 형성되어 있다. 승압 회로(560)의 출력은 행 디코더(562)나 열 디코더(564)를 통하여 워드 선이나 비트 선에 공급된다. 센스 앰프(566)는 열 디코더(564)로부터 출력된 데이터가 입력된다. 센스 앰프(566)에 의하여 판독된 데이터는 데이터 버퍼(568)에 보유되고, 컨트롤 회로(558)로부터의 제어에 의하여, 데이터가 웨덤 액세스되고, 데이터 입출력 버퍼(570)를 통하여 출력되도록 되어 있다. 기록 데이터는 데이터 입출력 버퍼(570)를 통하여 데이터 버퍼(568)에 일단 보유되고, 컨트롤 회로(558)의 제어에 의하여 열 디코더(564)로 전송된다.

- [0148] 이와 같이, 비휘발성 반도체 기억장치에서는, 메모리 셀 어레이(552)에 있어서, 전원 전위와는 다른 전위를 사용할 필요가 있다. 그래서, 적어도 메모리 셀 어레이(552)와 주변 회로(554) 사이는 전기적으로 절연 분리되어 있는 것이 바람직하다. 이 경우, 비휘발성 기억 소자 및 주변 회로의 트랜지스터를 절연 표면에 형성한 단결정 반도체 층으로 형성함으로써, 용이하게 절연 분리를 할 수 있다. 그것에 의하여, 오동작을 없애고, 소비전력이 낮은 비휘발성 반도체 기억장치를 얻을 수 있다.

- [0149] (실시형태 6)

- [0150] 본 실시형태에서는, 본 발명의 반도체 장치를 사용한 전자기기에 대하여 이하에 나타낸다.

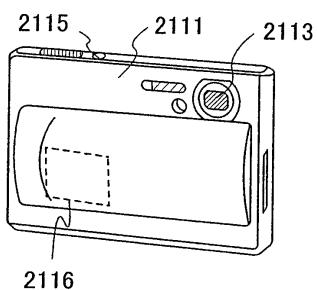

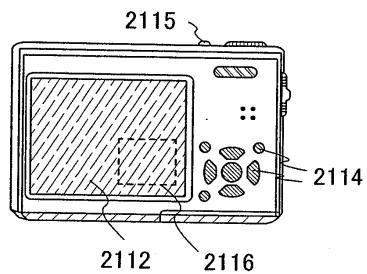

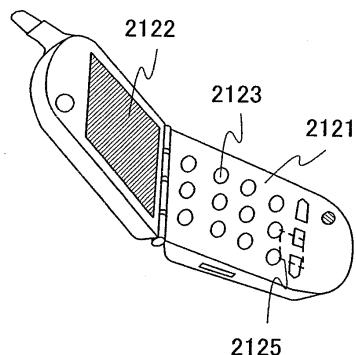

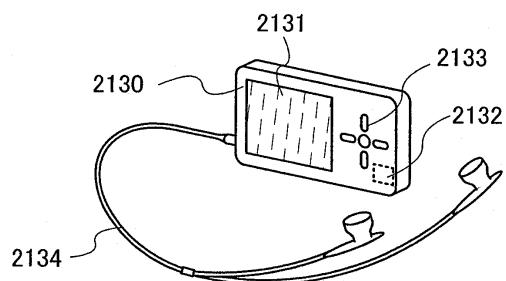

- [0151] 본 발명의 반도체 장치를 적용한 전자기기로서, 비디오 카메라, 디지털 카메라 등의 카메라, 고글형 디스플레이(헤드 장착형 디스플레이), 내비게이션 시스템, 음향 재생장치(카 오디오, 오디오 컴포넌트 등), 컴퓨터, 게임기기, 휴대형 정보 단말기(모바일 컴퓨터, 휴대 전화기, 휴대형 게임기 또는 전자 책 등), 기록 매체를 구비한 화상 재생장치(구체적으로는, DVD(Digital Versatile Disk) 등의 기록 매체를 재생하고, 그 화상을 표시 할 수 있는 디스플레이를 구비한 장치) 등을 들 수 있다. 그들 전자기기의 구체적인 예를 도 14a 내지 도 14e에 도시한다.

- [0152] 도 14a 내지 도 14b는 디지털 카메라를 나타내고 있다. 도 14b는 도 14a의 후측을 나타내는 도면이다. 이 디지털 카메라는 케이스(2111), 표시부(2112), 렌즈(2113), 조작 키(2114), 셔터 버튼(2115) 등을 가진다. 케이스(2111) 내부에는, 기억 장치, MPU, 이미지 센서 등의 기능을 갖는 본 발명의 반도체 장치(2116)를 구비한다.

- [0153] 또한, 도 14c는 휴대 전화기를 나타내고 있고, 휴대 단말기의 하나의 대표 예이다. 이 휴대 전화기는 케이스(2121), 표시부(2122), 조작 키(2123) 등을 포함한다. 또한, 휴대 전화기의 내부에는, 기억 장치, MPU, 이미지 센서 등의 기능을 갖는 본 발명의 반도체 장치(2125)를 구비한다.

[0154] 또한, 도 14d는 디지털 플레이어를 나타내고 있고, 오디오 장치의 하나의 대표 예이다. 도 14d에 도시하는 디지털 플레이어는 본체(2130), 표시부(2131), 기억 장치, MPU, 이미지 센서 등의 기능을 갖는 본 발명의 반도체 장치(2132), 조작부(2133), 이어폰(2134) 등을 포함하고 있다.

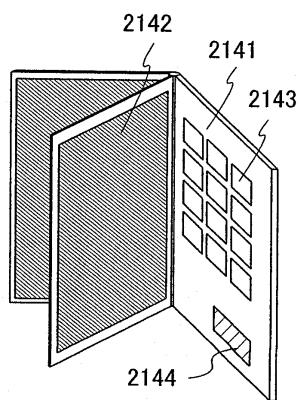

[0155] 또한, 도 14e는 전자 책(전자 페이퍼라고도 한다)을 나타내고 있다. 이 전자 책은 본체(2141), 표시부(2142), 조작 키(2143), 기억 장치, MPU, 이미지 센서 등의 기능을 갖는 본 발명의 반도체 장치(2144)를 포함하고 있다. 또, 모뎀이 본체(2141)에 내장되어 있어도 좋고, 무선으로 정보를 송수신할 수 있는 구성으로 하여도 좋다.

[0156] 이상과 같이, 본 발명의 반도체 장치의 적용 범위는 극히 넓고, 또 다른 전자기기에 사용할 수 있다.

### 도면의 간단한 설명

[0157] 도 1a 내지 도 1d는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0158] 도 2a 내지 도 2c는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0159] 도 3a 내지 도 3d는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0160] 도 4a 내지 도 4c는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0161] 도 5a 내지 도 5c는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0162] 도 6a 내지 도 6b는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0163] 도 7a 내지 도 7c는 본 발명의 반도체 장치의 제작 방법을 설명하는 단면도.

[0164] 도 8a 내지 도 8b는 본 발명에 적용 가능한 섬유체를 설명하는 상면도.

[0165] 도 9a 내지 도 9d는 본 발명에 적용 가능한 안테나를 설명하는 상면도.

[0166] 도 10a 내지 도 10b는 본 발명의 반도체 장치를 설명하는 사시도 및 단면도.

[0167] 도 11은 본 발명의 반도체 장치를 설명하는 상면도.

[0168] 도 12a 내지 도 12e는 본 발명의 반도체 장치의 응용 예를 설명하는 사시도.

[0169] 도 13은 본 발명의 반도체 장치를 설명하는 도면.

[0170] 도 14a 내지 도 14e는 본 발명의 반도체 장치를 적용할 수 있는 전자기기를 설명하는 도면.

[0171] <도면의 주요 부분에 대한 부호의 설명>

[0172] 101: 반도체 기판                          106: 절연층

[0173] 108: 도전층                                  109: 배선

[0174] 111: 절연층                                  112: 안테나

[0175] 113: 섬유체                                  114: 유기 수지층

[0176] 120: 밀봉층                                  121: 유기 수지층

[0177] 129: 밀봉층                                  1053: 웰 영역

[0178] 1102: 소자 기판                            1054a: 불순물 영역

[0179] 1054b: 저농도 불순물 영역            1054e: 저농도 불순물 영역

[0180] 1055a: 게이트 절연층                    1055b: 게이트 절연층

[0181] 1056a: 게이트 전극                        1056b: 게이트 전극

[0182] 1057a: 스페이서                            1057b: 스페이서

[0183] 1060a: MOS 트랜지스터                1060b: MOS 트랜지스터

## 도면

## 도면1a

## 도면1b

## 도면1c

## 도면1d

도면2a

도면2b

도면2c

도면3a

도면3b

도면3c

도면3d

도면4a

도면4b

도면4c

도면5a

도면5b

도면5c

도면6a

도면6b

도면7a

도면7b

도면7c

도면8a

도면8b

도면9a

도면9b

도면9c

도면9d

도면10a

도면10b

도면11

도면12a

도면12b

도면12c

도면12d

도면12e

도면13

도면14a

도면14b

도면14c

도면14d

도면14e