(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-142783

(P2010-142783A)

(43) 公開日 平成22年7月1日(2010.7.1)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>B06B 1/04</b> (2006.01)  | B06B 1/04  | A 3H075     |

| <b>H02N 2/00</b> (2006.01)  | H02N 2/00  | B 3H077     |

| <b>F04B 43/04</b> (2006.01) | F04B 43/04 | B 5D107     |

| <b>F04B 9/00</b> (2006.01)  | F04B 9/00  | B           |

審査請求 未請求 請求項の数 2 O L (全 13 頁)

|           |                              |                                                       |

|-----------|------------------------------|-------------------------------------------------------|

| (21) 出願番号 | 特願2008-325833 (P2008-325833) | (71) 出願人 000001889<br>三洋電機株式会社<br>大阪府守口市京阪本通2丁目5番5号   |

| (22) 出願日  | 平成20年12月22日 (2008.12.22)     | (71) 出願人 506227884<br>三洋半導体株式会社<br>群馬県邑楽郡大泉町坂田一丁目1番1号 |

|           |                              | (71) 出願人 000010098<br>アルプラス電気株式会社<br>東京都大田区雪谷大塚町1番7号  |

|           |                              | (74) 代理人 100075258<br>弁理士 吉田 研二                       |

|           |                              | (74) 代理人 100096976<br>弁理士 石田 純                        |

最終頁に続く

(54) 【発明の名称】電圧出力ドライバー

## (57) 【要約】

【課題】駆動信号を半波波形とすることで効率的に圧電素子を駆動する。

【解決手段】昇圧回路  $L_{VS}$ ,  $Q_3$ ,  $D_1$  は、低電圧の信号電源を昇圧して、圧電素子の駆動制御信号に応じて決定された高電圧の駆動電源を発生する。駆動波発生手段が前記信号電源を電源として、前記駆動制御信号に応じた振幅を有する圧電素子の駆動波形を発生し、アンプ  $AP_1$ ,  $AP_2$  が駆動波形を增幅し、前記駆動制御信号に応じた振幅であって、圧電素子を駆動する駆動信号を得る。駆動波発生手段において、駆動波形として、サイン波形の一方側に膨らむ部分をカットして他方側に膨らむ部分のみを残した波形（半波波形）を発生し、これをアンプ  $AP_1$ ,  $AP_2$  に入力することで、圧電素子  $PZ$  を半波駆動する。

【選択図】図 15

**【特許請求の範囲】****【請求項 1】**

容量性負荷を駆動する電圧出力ドライバーであって、

信号電源に基づいて、容量性負荷の駆動制御信号に応じて決定された電圧の駆動電源を発生する電源回路と、

前記信号電源を電源として、前記駆動制御信号に応じた振幅を有する容量性負荷の駆動波形であって、位相が互いに 180 度ずれた一対の駆動波形を発生する駆動波形発生手段と、

前記駆動電源を電源として、前記駆動波形を増幅し、前記駆動制御信号に応じた振幅であって、容量性負荷を駆動する駆動信号を得る増幅回路と、

を有し、

前記駆動波形発生手段は、駆動波形として、サイン波形の一方側に膨らむ部分をカットして他方側に膨らむ部分のみを残した波形として発生することを特徴とする電圧出力ドライバー。

**【請求項 2】**

請求項 1 に記載の電圧出力ドライバーにおいて、

駆動電源制御信号を一対の駆動波形に対し所定値だけ高い波形として、前記駆動電源電圧を駆動信号に対し所定値高いものに制御することを特徴とする電圧出力ドライバー。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、容量性負荷へ駆動信号を出力する電圧出力ドライバーに関する。

**【背景技術】****【0002】**

従来、圧電素子を利用したダイヤフラムポンプが提案されている。このポンプは、圧電ポンプと呼ばれ、圧電素子への電圧印加の方向を順次変更することで、圧電素子を往復動作させてダイヤフラムを往復動作させて駆動される。

**【0003】**

このような圧電ポンプでは、圧電素子に対する駆動信号を出力する駆動回路が必要であり、ポンプ流量を制御するためには、印加電圧や周期を制御する必要がある。モータの駆動制御には、インバータを用いた駆動電流制御などがあるが、小型のモータの簡易な駆動制御では、印加電圧を制御する駆動電流の振幅制御も広く行われている。

**【0004】****【特許文献 1】特開平 6 - 109068 号公報****【特許文献 2】特開平 8 - 205563 号公報****【特許文献 3】特開 2000 - 60847 号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

ここで、パーソナルコンピュータでは、CPUなどの部材の冷却のために冷却ファンを有しており、このファンの強度調節のために通常はファンモータへの印加電圧を変更している。圧電ポンプは小型であり、これを用いると、パーソナルコンピュータの内部部材の水冷システムを構成することが現実的に可能と考えられる。この場合、圧電ポンプの吐出量を効果的に制御する圧電ポンプを駆動する高電圧出力を効率的に得る回路が望まれる。特に、電力効率のよい駆動が望まれる。

**【課題を解決するための手段】****【0006】**

本発明は、容量性負荷を駆動する電圧出力ドライバーであって、信号電源に基づいて、容量性負荷の駆動制御信号に応じて決定された電圧の駆動電源を発生する電源回路と、前記信号電源を電源として、前記駆動制御信号に応じた振幅を有する容量性負荷の駆動波形

10

20

30

40

50

であって、位相が互いに 180 度ずれた一対の駆動波形を発生する駆動波形発生手段と、前記駆動電源を電源として、前記駆動波形を増幅し、前記駆動制御信号に応じた振幅であって、容量性負荷を駆動する駆動信号を得る増幅回路と、を有し、前記駆動波形発生手段は、駆動波形として、サイン波形の一方側に膨らむ部分をカットして他方側に膨らむ部分のみを残した波形として発生することを特徴とする。

#### 【0007】

また、駆動電源制御信号を一対の駆動波形に対し所定値だけ高い波形として、前記駆動電源電圧を駆動信号に対し所定値高いものに制御することが好適である。

#### 【発明の効果】

#### 【0008】

10

駆動信号を半波形状にすることで、効率的に容量性負荷の駆動が可能となる。

#### 【発明を実施するための最良の形態】

#### 【0009】

以下、本発明の実施形態について、図面に基づいて説明する。

#### 【0010】

20

#### 「圧電ポンプの構成」

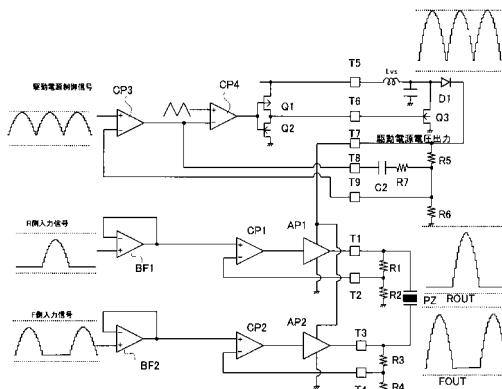

圧電素子を利用したダイヤフラムポンプ（圧電ポンプ）の構成について、図1を用いて説明する。ポンプケーシング10内には、周囲がポンプケーシング10内壁に固定され、中央側が上下動するダイヤフラム12が配置され、このダイヤフラム12の一方側にポンプ室14が形成される。ポンプ室14には、流入通路16に接続される流入口18と、流出通路20に接続される流出口22が設けられ、流入通路16と流入口18の間には流入側の逆止弁24、流出通路20と流出口22の間には流出側の逆止弁26が設けられている。

#### 【0011】

30

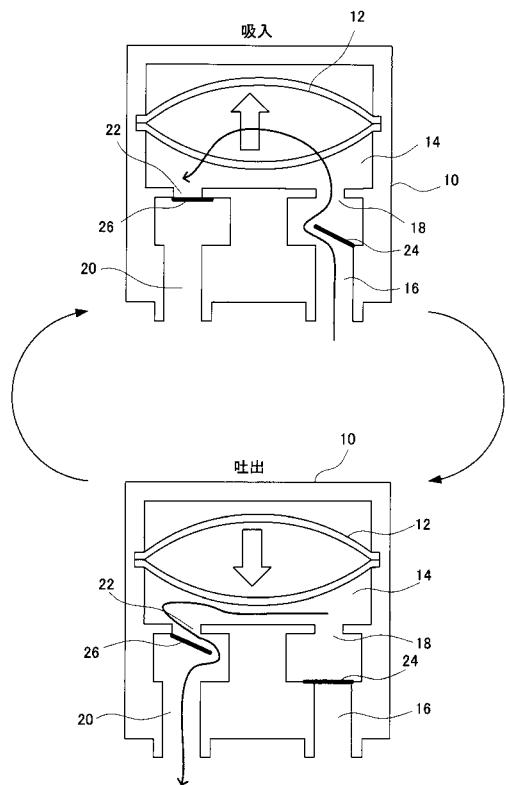

ここで、ダイヤフラム12は、図2に示すように薄い金属板Mの表裏両面に、両面に電極を有する圧電素子PZ1、PZ2を貼り合わせた構造になっている。そして、圧電素子PZ1の上側の電極と、圧電素子PZ2の下側の電極の間に1つの位相の交流電圧（サイン波状の駆動信号）が印加され、圧電素子PZ1、PZ2に挟まれた真ん中の金属板Mに位相が反対の（180度異なる）交流電圧（位相が反対のサイン波状の駆動信号）が印加される。これによって、2つの圧電素子PZ1、PZ2とも印加電圧が大きいときに大きく反ることになり、図1、2に示すように、ダイヤフラム12が周辺部を支点とし真ん中を最大振幅として上下に振動することになる。

#### 【0012】

30

流入側の逆止弁24は、ポンプ室14へ流入する方向の流体の流れを許可し、反対の流れを阻止する。一方、流出側の逆止弁26は、ポンプ室14から流出する方向の流体の流れを許可し、反対の流れを阻止する。従って、図1に示すように、ダイヤフラム12の振動に伴うポンプ室14の容積変化に伴い、流入通路16の流体がポンプ室14を介し流出通路20に押し出される。

#### 【0013】

40

#### 「駆動信号出力回路」

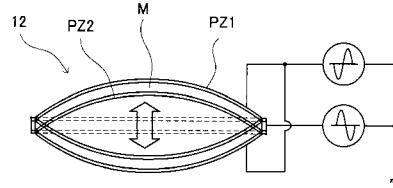

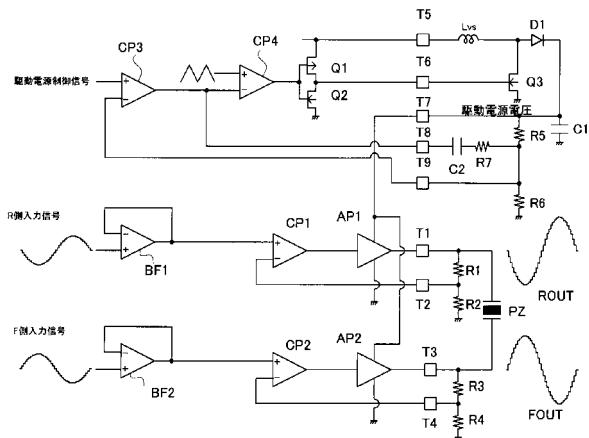

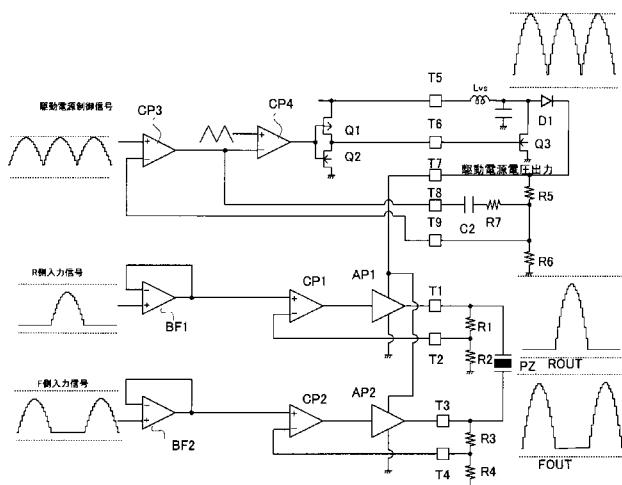

図3には、圧電素子PZへの駆動信号を出力する駆動信号出力回路の構成が示されている。1つの駆動波形（サイン波状の交流波形）であるR側入力信号は、バッファアンプBF1の正入力端に入力される。このバッファアンプBF1は、その出力が負入力端に接続されており、R側入力信号がそのままの波形で出力される。バッファアンプBF1の出力はコンパレータ（エラーアンプ）CP1の正入力端に入力される。このコンパレータCP1の負入力端には、帰還信号が入力されており、両信号の誤差信号がコンパレータCP1の出力に得られる。得られた誤差信号は、高電源電圧で駆動される出力アンプAP1に供給され、この出力アンプAP1の出力が出力端T1に供給される。出力端T1には、圧電素子PZの一方側の電極が接続されているとともに、分圧抵抗R1、R2を介しグランドに接続されている。分圧抵抗R1、R2の中点は、端子T2を介し、コンパレータCP1

50

の負入力端に接続され、出力電圧が分圧された電圧がコンパレータ C P 1 に負帰還される。

#### 【 0 0 1 4 】

従って、コンパレータ C P 1 は、その出力が、帰還信号である分圧抵抗 R 1 , R 2 の中点電圧が R 側入力信号に一致するように動作し、従って出力端 T 1 からの駆動信号 R O U T が R 側入力信号に応じたものになる。

#### 【 0 0 1 5 】

また、F 側入力信号は、R 側入力信号と位相が 180 度異なる信号（相補的な信号）であり、F 側入力信号は、バッファアンプ B F 2 、コンパレータ C P 2 、出力アンプ A P 2 を介し、F 側入力信号に対応した高電圧の駆動信号となり、出力端 T 3 に供給される。出力端 T 3 は、圧電素子 P Z の他方側の電極が接続されているとともに、分圧抵抗 R 3 , R 4 を介しグランドに接続されており、分圧抵抗 R 3 , R 4 の中点電圧がコンパレータ C P 2 に負帰還されている。従って、出力端 T 3 からの出力である駆動信号 F O U T が出力端 T 1 からの駆動信号 R O U T と反対の極性の信号となり、圧電素子 P Z の両面の電極に位相が 180 度異なる一対の駆動信号 R O U T , F O U T が印加されることになる。この圧電素子 P Z が上述の圧電ポンプのダイヤフラム 1 2 を構成しており、ダイヤフラム 1 2 が往復移動することになる。なお、上述の圧電ポンプは、2 つの圧電素子 P Z 1 , P Z 2 を有しているが、圧電素子 P Z がそのうちの 1 つに該当していても良いし、ダイヤフラム 1 2 を 1 つの圧電素子 P Z で構成してもよい。

10

#### 【 0 0 1 6 】

次に、駆動電源制御信号は、コンパレータ C P 3 の正入力端に入力される。コンパレータ C P 3 の負入力端には帰還信号が入力されている。コンパレータ C P 3 の出力は、コンパレータ C P 4 の負入力端に入力される。このコンパレータ C P 4 の正入力端には、予め設定された三角波が供給されている。従って、このコンパレータ C P 4 の出力には、コンパレータ C P 3 の出力の電圧に応じたデューティー比の P W M 信号が得られる。すなわち、駆動電源制御信号がフィードバック信号に比べて高ければ、コンパレータ C P 3 の出力電圧が高くなり、デューティー比（H レベルの期間）が少ない P W M 信号がコンパレータ C P 4 から出力される。なお、駆動電源制御信号は、後述するように、圧電素子 P Z の駆動を制御するための制御電源電圧 V C C に基づいて発生される。

20

#### 【 0 0 1 7 】

コンパレータ C P 4 の出力は、p チャネルトランジスタ Q 1 と、n チャネルトランジスタ Q 2 のゲートに供給される。このトランジスタ Q 1 は、ソースが端子 T 5 に接続され、ドレインがトランジスタ Q 2 のドレインに接続されており、トランジスタ Q 2 のソースはグランドに接続されている。そして、トランジスタ Q 1 , Q 2 のドレイン同士の接続点は、端子 T 6 に接続されている。

30

#### 【 0 0 1 8 】

端子 T 5 には、外付けのコイル L v s を介し、外付けのダイオード D 1 のアノードに接続され、このダイオード D 1 のカソードは外付けコンデンサ C 1 を介しグランドに接続されている。また、端子 T 6 には、n チャネルトランジスタ Q 3 のゲートが接続され、このトランジスタ Q 3 のドレインがコイル L v s とダイオード D 1 の接続点に接続され、ソースがグランドに接続されている。

40

#### 【 0 0 1 9 】

従って、コンパレータ C P 4 からの出力である P W M 信号が H レベルであると、トランジスタ Q 2 がオンし端子 T 6 が L レベルとなりトランジスタ Q 3 はオフ、P W M 信号が L レベルであると、トランジスタ Q 2 がオフし端子 T 6 が H レベルとなりトランジスタ Q 3 はオンする。このトランジスタ Q 3 がオンすることで、コイル L v s にエネルギーが蓄積され、トランジスタ Q 3 がオフすることで、コイル L v s に蓄積されたエネルギーに応じてコンデンサ C 1 に充電される。従って、コンパレータ C P 4 からの出力における L レベルの期間が長いほど、コンデンサ C 1 への充電量が大きくなり、コンデンサ C 1 からの出力である駆動電源電圧が高くなる。なお、ダイオード D 1 に並列してトランジスタを設け

50

ると、そのスイッチングにより駆動電源電圧を下げることが容易になる。

#### 【0020】

コンデンサC1の上側（ダイオードD1のカソードに接続される電極）は、端子T7に接続され、この端子T7が出力アンプAP1, AP2へ駆動電源電圧として供給される。また、コンデンサC1の上側は、外付けの分圧抵抗R5, R6を介しグランドに接続されている。分圧抵抗R5, R6の中点は、外付けの抵抗R7、コンデンサC2を介し、端子T8に接続されている。そして、端子T8は、コンパレータCP4の負入力端に接続されている。抵抗R7、コンデンサC2は、ハイパスフィルタを構成しており、これによって駆動電源電圧出力の高周波成分が除去される。さらに、分圧抵抗R5, R6の中点は端子T9に接続されており、この端子T9がコンパレータCP3の負入力端に接続されている。従って、駆動電源電圧を分圧抵抗R5, R6で分圧した電圧が駆動電源制御信号と比較されるフィードバック信号（帰還信号）となり、帰還信号の電圧が駆動電源制御信号の電圧に一致するように、駆動電源電圧が制御される。

10

#### 【0021】

このようにして、駆動電源制御信号によって、駆動電源電圧を任意に制御することが可能になる。これによって、端子T1, T3からの出力である、駆動信号ROUT, FOUTの振幅が制御される。なお、後述するように、駆動電源制御信号は、電源電圧VCCとして本ドライバーに外部から供給される。

#### 【0022】

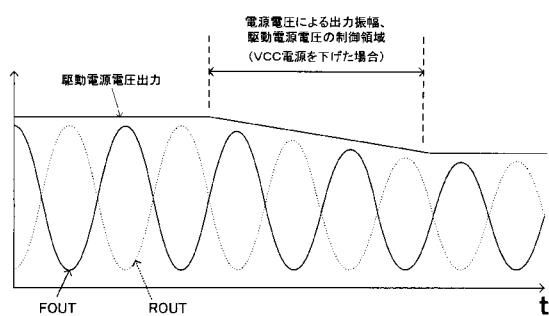

図4には、駆動信号ROUT, FOUTの状態が示してある。駆動電源電圧出力を下すことによって、ROUT, FOUTの振幅が小さくなる。これによって、圧電素子PZの動きが制御され、圧電ポンプのダイヤフラムの振幅が制御されてポンプの吐出量を制御することができる。

20

#### 【0023】

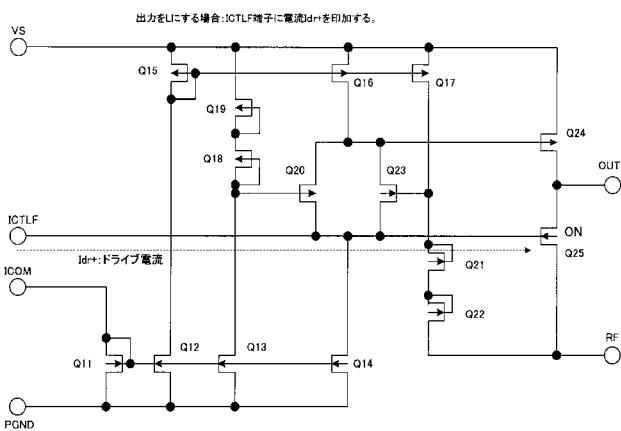

##### 「出力アンプAPの構成」

図5、図6には、出力アンプAPの構成例が示されている。ICOMからは定電流が供給され、これがnチャネルトランジスタQ11のドレインおよびゲートに供給される。トランジスタQ11のソースはグランド（PGND）に接続されている。トランジスタQ11のゲートには、ソースがグランド（PGND）に接続されたnチャネルトランジスタQ12, Q13, Q14のゲートが共通接続されている。従って、トランジスタQ11に対し、トランジスタQ12, Q13, Q14がカレントミラーを構成し、これらトランジスタQ11～Q14に同一の定電流が流れる。

30

#### 【0024】

トランジスタQ12のドレインには、pチャネルトランジスタQ15のドレインが接続されており、このトランジスタQ15のソースは駆動電源VSに接続されている。トランジスタQ15はドレイン・ゲートが短絡されており、このゲートには、ソースがVSに接続されたpチャネルトランジスタQ16, Q17のゲートが接続されている。従って、これらトランジスタQ16, Q17にも、トランジスタQ11に流れるのと同じ定電流が流れれる。

40

#### 【0025】

トランジスタQ13のドレインは、2つのドレイン・ゲート間が短絡されたpチャネルトランジスタQ18, Q19を介し、駆動電源VSに接続されており、トランジスタQ13とトランジスタQ18のドレインがpチャネルトランジスタQ20のゲートに接続されている。また、トランジスタQ17のドレインは、2つのドレイン・ゲート間が短絡されたnチャネルトランジスタQ21, Q22を介し、外部のグランドに接続されている端子RFに接続されている。トランジスタQ17とトランジスタQ21の接続点は、nチャネルトランジスタQ23のゲートに接続されている。

#### 【0026】

そして、トランジスタQ20のソースと、トランジスタQ23のドレインは、トランジスタQ16のドレインに共通接続されるとともに、pチャネルトランジスタQ24のゲー

50

トに接続されている。また、トランジスタ Q 2 0 のドレインと、トランジスタ Q 2 3 のソースは、トランジスタ Q 1 4 のドレインに共通接続されるとともに、n チャネルトランジスタ Q 2 5 のゲートに接続されている。また、トランジスタ Q 2 0 のドレイン、トランジスタ Q 2 3 のソース、トランジスタ Q 1 4 のドレイン、n チャネルトランジスタ Q 2 5 のゲートには、I C T L F 端からドライブ電流  $I_{d\ r}$  が供給される。すなわち、この I C T L F 端がコンパレータ C P 1 ( またはコンパレータ C P 2 ) の出力に接続されている。

#### 【 0 0 2 7 】

また、トランジスタ Q 2 4 のソースは駆動電源 V S に接続され、ドレインはトランジスタ Q 2 5 のドレインに接続されるとともに出力端子 O U T ( T 1 または T 2 ) に接続されており、トランジスタ Q 2 5 のソースは端子 R F に接続されている。

10

#### 【 0 0 2 8 】

このような回路において、トランジスタ Q 2 0 とトランジスタ Q 2 3 には、トランジスタ Q 1 6 に流れる定電流を分割した電流が流れ。また、トランジスタ Q 1 9 , Q 1 8 には、トランジスタ Q 1 3 に流れる定電流が流れ、トランジスタ Q 2 1 , Q 2 2 には、トランジスタ Q 1 7 に流れる電流が流れ。従って、通常は、トランジスタ Q 2 0 , Q 2 3 に流れる電流は等しい。

#### 【 0 0 2 9 】

ドライブ電流  $I_{d\ r}$  がトランジスタ Q 2 5 のゲートに向けて流れる電流  $I_{d\ r^+}$  であるとこれによって、図 5 に示すように、トランジスタ Q 2 5 がオンし、出力端 O U T から電流を引き抜く方向の電流が流れ、出力端 O U T は L レベル側に動く。このとき、トランジスタ Q 2 0 およびトランジスタ Q 2 3 に流れる電流の和はトランジスタ Q 1 4 に流れる定電流に等しいため、トランジスタ Q 2 4 はオフしている。

20

#### 【 0 0 3 0 】

一方、ドライブ電流  $I_{d\ r}$  がトランジスタ Q 2 5 のゲートから引き抜く方向に流れる電流  $I_{d\ r^-}$  であると、これによって、図 6 に示すように、トランジスタ Q 2 3 のドレイン電流が大きくなり、トランジスタ Q 2 4 がオンし、出力端 O U T から電流を吐き出す方向の電流が流れ、出力端 O U T は H レベル側に動く。

20

#### 【 0 0 3 1 】

このようにして、I C T L F に流れる電流に応じて、出力トランジスタ Q 2 4 , Q 2 5 が制御されて、出力端 O U T からの出力が制御される。この出力アンプ A P は、駆動電源 V S からの電力によって出力を得る高耐圧出力部として機能する。従って、図 3 における出力アンプ A P 1 , A P 2 として、図 5 , 6 に示されるアンプをそれぞれ用意し、コンパレータ C P 1 , C P 2 の出力をそれぞれのアンプの I C T L F に入力することによって、出力端 O U T において、駆動信号 R O U T , F O U T をそれぞれ得ることができる。

30

#### 【 0 0 3 2 】

なお、信号系の電源電圧は、例えば、5 V 程度であり、駆動電源 V S は例えば 2 0 0 V 程度である。

#### 【 0 0 3 3 】

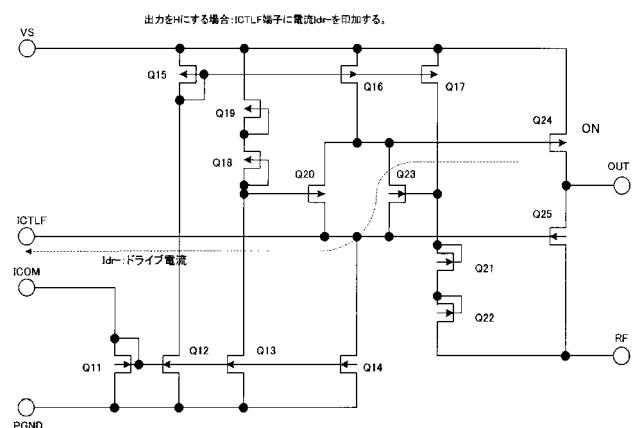

##### 「 V C C 連動 D A C の構成 」

従来の装置において、ファン駆動制御用にファンの駆動を制御する制御電源電圧である電源電圧 V C C を出力できる回路がすでに用意されている場合がある。この場合には、この電源電圧 V C C に応じて、圧電素子 P Z を制御する信号を発生することが好適である。

40

#### 【 0 0 3 4 】

図 7 には、このような場合に好適な構成が示されている。外部から入力されてくる電圧がポンプの駆動要求に従って適宜変更される電源 V C C が入力される端子 T 1 1 は、抵抗 R 1 1 , R 1 2 の直列接続からなる分圧抵抗を介しグランドに接続されている。分圧抵抗 R 1 1 と R 1 2 の中点は、出力が負入力端に短絡されたバッファアンプ B F 1 1 の正入力端に入力され、この出力が D / A コンバータ 3 0 の電源 V D A C となっている。

#### 【 0 0 3 5 】

なお、この例では、リファレンス V 1 が正入力端に入力され、負入力端に分圧抵抗 R 1

50

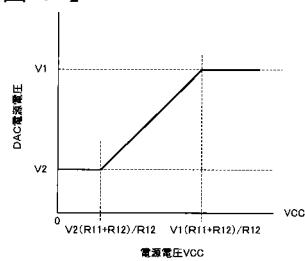

1とR12の中点が接続されるとともに、分圧抵抗R11とR12の中点がダイオードD11を介し出力に接続されるコンパレータCP11と、リファレンスV2が正入力端に入力され、負入力端に分圧抵抗R11とR12の中点が接続されるとともに、出力がダイオードD12を介し分圧抵抗R11とR12の中点に接続されるコンパレータCP12と、が設けられている。ダイオードD11は、分圧抵抗R11とR12の中点からコンパレータCP11の出力に向けて流れる電流のみを流し、ダイオードD12は、コンパレータCP11の出力から分圧抵抗R11とR12の中点に向けて流れる電流のみを流す。従って、分圧抵抗R11とR12の中点電圧は、リファレンス電圧V1, V2でクリップされることになる。従って、電源VDACは、電源電圧VCCの変化に伴い、図8に示すように変化することになる。すなわち、電源VDACは、電源電圧VCCが $0 \sim V_2 (R_{11} + R_{12}) / R_{12}$ の間は $V_2$ 、 $V_2 (R_{11} + R_{12}) / R_{12} \sim V_1 (R_{11} + R_{12}) / R_{12}$ の間は $V_2 - V_1$ に直線的に変化し、 $V_1 (R_{11} + R_{12}) / R_{12}$ 以上では $V_1$ に固定される。

#### 【0036】

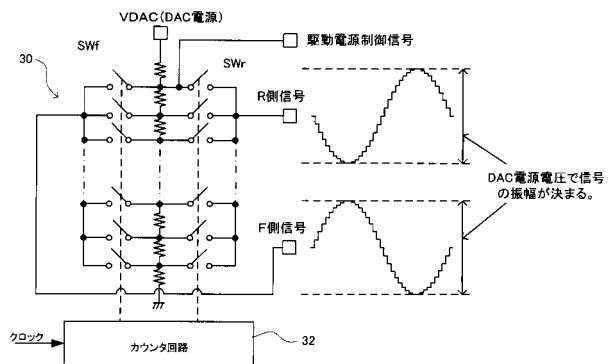

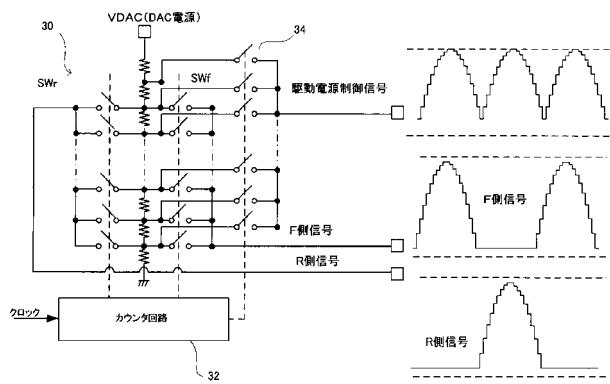

図9には、D/Aコンバータ30の構成が示されている。電源Vdacとグランドの間には、入力デジタル信号のビット数に応じた抵抗が直列接続されている。そして、各抵抗間の接続点には2つのスイッチがそれぞれ対応して設けられており、一方側のR側スイッチ群SWrの抵抗側でない端部が共通接続してR側信号の出力、他側のF側スイッチ群SWfの抵抗側でない端部が共通接続してF側信号の出力になっている。

#### 【0037】

また、R側、F側スイッチ群を制御するためにカウンタ回路32が設けられている。このカウンタ32は、所定のクロックをアップカウント、ダウンカウントを繰り返す。例えば、512段階のカウント値を0 511 0 511というように順次繰り返し出力する。そして、これらカウンタの出力がR側スイッチ群SWrとF側スイッチ群SWfとで、ちょうど反対の出力が出るように対応付けられている。すなわち、カウンタ32の出力が0のときにR側スイッチ群SWrの出力が0であれば、F側スイッチ群SWfの出力が511となるように設定されている。

#### 【0038】

従って、R側信号、F側信号が図示のように、1クロックに対し順次変化する相補的なサインカーブになる。そして、電源Vdacが変化することで、R側信号、F側信号の振幅が連動して変化する。従って、電源VCCに応じて振幅が変化するR側信号、F側信号がD/Aコンバータ30の出力に得られる。また、D/Aコンバータ30の最大出力が駆動電源制御信号として出力される。

#### 【0039】

このような図9の出力信号が図3のバッファアンプBF1, BF2、コンパレータCP3に入力される。そして、分圧抵抗R1, R2, R3, R4, R5, R6の比を適切に設定することで、入力されてくるVCCに応じて、圧電ポンプの吐出量を目標値に制御することが可能になる。

#### 【0040】

なお、図9では、D/Aコンバータ30からR側信号、F側信号をそのまま出力することにした。しかし、R側信号、F側信号は上下対称である。従って、半分(180度分)の出力のみをD/Aコンバータ30から出力し、他の半分については、出力を反転することができる。これによって、D/Aコンバータ30における抵抗列を半分の規模にすることが可能になる。

#### 【0041】

##### 「半波駆動について」

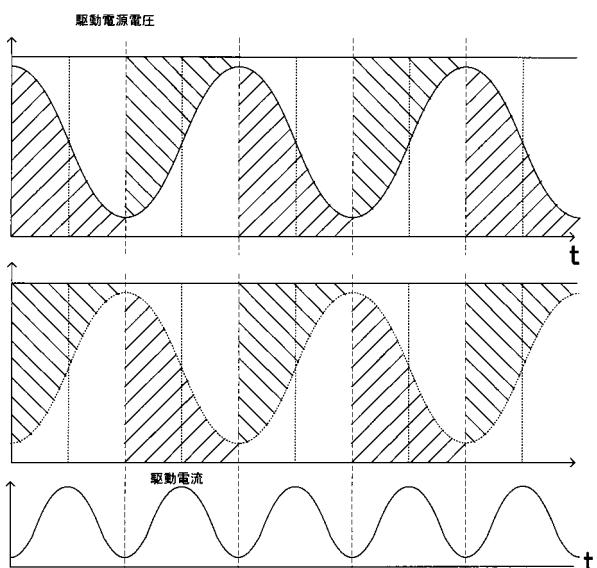

このように、本実施形態では、電源電圧VCCに応じて駆動電源制御信号を発生し、昇圧を制御している。ここで、駆動電源電圧は、駆動信号ROUT、FOUTより大きい必要があるが、一定である必要はない。特に、駆動電源電圧が一定であると、図10に示すように、駆動信号との差が大きいときには、その差分をアンプAP1, AP2の上側トランジ

10

20

30

40

50

ンジスタが受け持つことになり、ここにおける電力消費が大きくなる等問題がある。図10における右下がり斜線領域が、上側トランジスタが消費する領域である。なお、図における右上がりの斜線で示す領域は、下側トランジスタが受け持つ領域である。

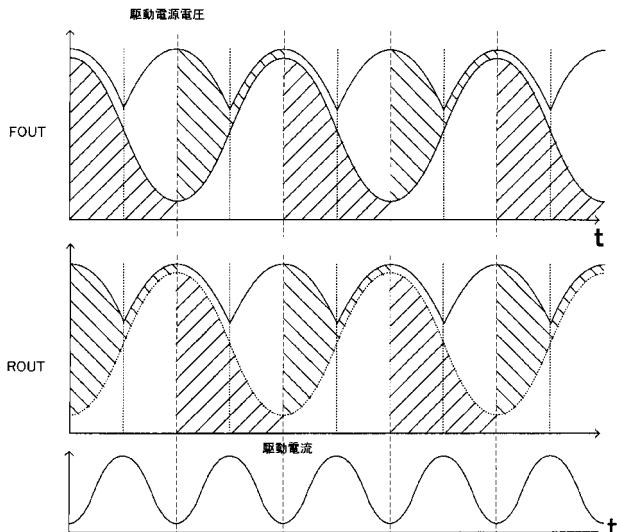

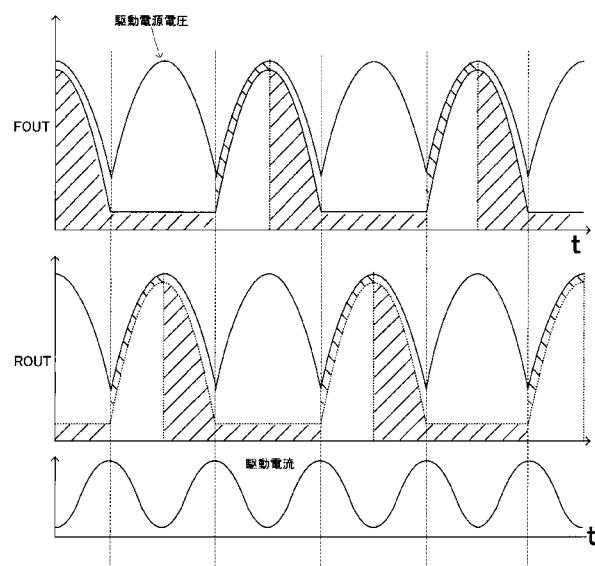

#### 【0042】

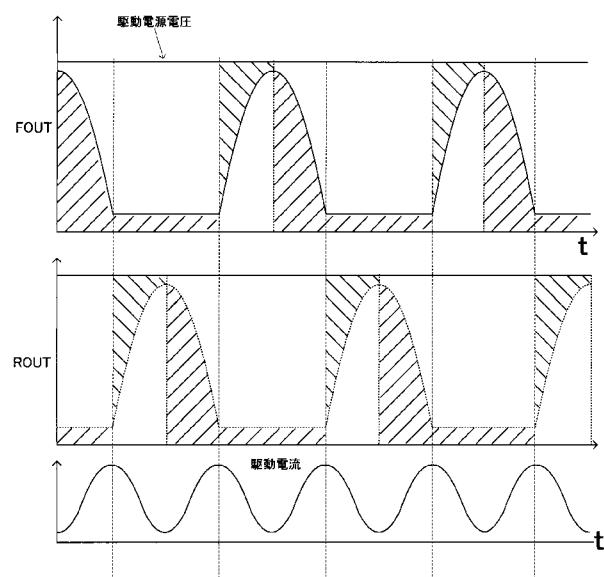

そこで、本実施形態では、図11に示すように、駆動信号の波形をサイン波ではなく、上側の山を残し、下側の谷をフラットにした半波波形にする。これによって、上側トランジスタが受け持つ領域は各段に小さくなり、効率的な圧電素子PZの駆動が行える。

#### 【0043】

また、図3の構成において、駆動電源制御信号を駆動信号の波形に応じて変更することも好適である。例えば、図12に示すように、サイン波状の駆動信号ROUT、FOUTの両方の包絡線より若干高い値の設定されている。これによって、上側トランジスタが受け持つ領域が小さくなるが、駆動信号の谷に当たる部分では、大きな領域が残ることになる。

#### 【0044】

図13には、駆動信号を図11の場合と同じように半波波形とした例が示されている。これによって、上側トランジスタがかなり小さな領域に限定され、効率的な圧電素子PZの駆動が達成される。

#### 【0045】

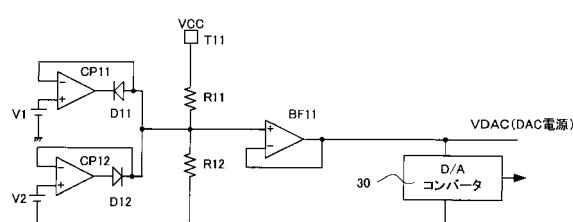

##### 「VCC連動DACによる駆動電源制御信号生成の構成」

図14には、VCCに連動するA/Dコンバータ30を利用して半波波形のR側信号およびF側信号、およびそれに対応した駆動電源制御信号を形成する構成を示してある。この例では、カウンタ回路32のカウント値に応じて、スイッチSWr, SWfが制御され、カウント値の上昇、下降に応じて、R側信号およびF側信号の山が交互に作成され、一方側信号の山が形成されている場合には、他側信号は最低レベルを維持している。このようなスイッチSWr, SWfの制御によって、図示のような半波のR側信号、F側信号を得られる。

#### 【0046】

また、スイッチSW34は、スイッチSWr, SWfの山を出力するスイッチに対し所定だけ、高い出力を得るスイッチをオンするように制御される。これによってR側信号、F側信号の包絡線に対し、所定値高い駆動電源制御信号を得ることができる。

#### 【0047】

なお、D/Aコンバータ30の直列抵抗の値をR側信号、F側信号の波形に応じて設定することで、上昇、下降を直線ではなく、目的の波形にしている。本実施形態の場合、半波形状であり、カウント値の低い方に応する抵抗値が大きくカウント値が高い方に応する抵抗値が小さい。そこで、カウント値に応じて対応するスイッチを変更していくことで、図示のようなR側信号およびF側信号が得られる。

#### 【0048】

ここで、図3における抵抗R1(R3) : R2(R4)の分圧比と、抵抗R5 : R6の分圧比を変更することで、駆動電源電圧を駆動信号より所定値高く設定することができる。すなわち、 $R1 / (R1 + R2)$ に比べ、 $R5 / (R5 + R6)$ を小さくすることで、駆動電源電圧を駆動信号より高く設定することができる。しかし、このように分圧比によって、駆動電源電圧と、駆動信号の電圧の関係を設定すると、駆動電源電圧は、駆動信号のピーク時において差分がより大きなものになる。

#### 【0049】

そこで、本実施形態においては、駆動電源制御信号をR側信号、F側信号の高い方より所定値だけ高い値として出力する。このようにして得たオフセットされた駆動電圧制御信号により、駆動電源電圧の昇圧を制御することで、抵抗R1(R3) : R2(R4)の分圧比と、抵抗R5 : R6の分圧比を同一としておき、駆動電源電圧を駆動信号に比べ所定値高いものに制御することができ、かつその差を常に同一の値に設定することが可能になる。

10

20

30

40

50

## 【0050】

図15には、図3と同様の回路において、半波の駆動電源制御信号、R側信号、F側信号を入力し、半波の駆動信号ROUT、FOUTを得る構成を示してある。このように、出力自体の構成は、図3として半波駆動を行うことができる。

## 【図面の簡単な説明】

## 【0051】

【図1】圧電ポンプの構成を示す図である。

【図2】圧電ポンプのダイヤフラムの構成を示す図である。

【図3】高電圧出力ドライバーの出力部の構成を示す図である。

【図4】駆動信号の波形を示す図である。

10

【図5】出力アンプの構成を示す図である。

【図6】出力アンプの構成を示す図である。

【図7】電源V DACの出力のための構成を示す図である。

【図8】電源V DACの電源V CCに対する特性を示す図である。

【図9】電源V DACに応じた出力振幅の出力を得るD/Aコンバータの構成を示す図である。

【図10】通常駆動の場合の駆動電源電圧、駆動信号、出力電流の波形を示す図である。

【図11】半波駆動の場合の駆動電源電圧、駆動信号、出力電流の波形を示す図である。

20

【図12】通常駆動で、駆動電源電圧を駆動信号に応じて変化させた場合の駆動電源電圧、駆動信号、出力電流の波形を示す図である。

【図13】半波駆動で、駆動電源電圧を駆動信号に応じて変化させた場合の駆動電源電圧、駆動信号、出力電流の波形を示す図である。

【図14】半波の駆動電源制御信号、R側信号、F側信号を作成する回路を示す図である。

【図15】半波駆動の高電圧出力ドライバーの出力部の構成を示す図である。

## 【符号の説明】

## 【0052】

10 ポンプケーシング、12 ダイヤフラム、14 ポンプ室、16 流入部、18

流入口、20 流出部、22 流出口、24, 26 逆止弁、30 コンバータ、32

カウンタ回路、AP1, AP2 出力アンプ、BF1, BF2, BF11 バッファア

ンプ、C1, C2 コンデンサ、CP1, CP2, CP3, CP4, CP8, CP11,

CP12 コンパレータ、CS11~CS13 定電流源、D1, D11, D12 ダ

イオード、Q1~Q2, Q11~Q25, Q41~Q54 トランジスタ、R1~R7,

R11, R12, R41~43 抵抗。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 10】

【図 9】

【図 11】

【図 12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 前戸 秀巨

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 田邊 雅史

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 島崎 努

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 佐藤 昭

東京都大田区雪谷大塚町1番7号 アルプス電気株式会社内

(72)発明者 徳弘 宏道

東京都大田区雪谷大塚町1番7号 アルプス電気株式会社内

(72)発明者 服部 靖之

東京都大田区雪谷大塚町1番7号 アルプス電気株式会社内

(72)発明者 石川 潤

東京都大田区雪谷大塚町1番7号 アルプス電気株式会社内

F ターム(参考) 3H075 AA06 BB04 BB13 BB30 CC25 DB02 EE06 EE12

3H077 AA02 BB03 CC02 CC09 DD06 EE02 FF36

5D107 AA03 CC02 CC13 CD03 CD06