(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

H04N 5/44 (2006.01)

G06F 3/12 (2006.01)

(45) 공고일자

2007년06월29일

(11) 등록번호

10-0733936

(24) 등록일자

2007년06월25일

(21) 출원번호 10-2005-0049143

(22) 출원일자 2005년06월09일

심사청구일자 2005년06월09일

(65) 공개번호 10-2006-0048291

(43) 공개일자 2006년05월18일

(30) 우선권주장 JP-P-2004-00172786 2004년06월10일 일본(JP)

(73) 특허권자 캐논 가부시끼가이샤

일본 도쿄도 오오따꾸 시모마루꼬 3조메 30방 2고(72) 발명자 미우라 히로야

일본 도쿄도 오오따꾸 시모마루꼬 3조메 30방 2고 캐논가부시끼가이샤

내(74) 대리인 구영창

이중희

장수길(56) 선행기술조사문헌

일본2004-172786

심사관 : 정윤석

전체 청구항 수 : 총 11 항

(54) 신호 처리 장치

(57) 요약

아날로그 영상 신호를 입력하는 입력 수단과, 상기 아날로그 영상 신호를 디지털 영상 신호로 변환하는 A/D 변환기와, 상기 A/D 변환기로부터 출력된 미리 정해진 기간의 디지털 영상 신호의 레벨을 검출하는 검출 수단과, 상기 검출 수단에 의해 검출된 레벨과 목표값과의 차분값을 검출하는 차분 출력 수단과, 상기 차분 출력 수단으로부터의 출력에 대하여 시그마-델타 변조를 수행하는 변조 수단과, 상기 변조 수단으로부터의 출력에 기초하여 상기 입력 수단에 의해 입력된 아날로그 영상 신호에 대해 클램프 처리를 수행하고, 상기 클램프 처리된 아날로그 영상 신호를 상기 A/D 변환기에 출력하는 클램프 수단을 포함하는 신호 처리 장치가 개시된다.

대표도

도 1

특허청구의 범위

## 청구항 1.

신호 처리 장치에 있어서,

아날로그 영상 신호를 입력하는 입력 수단과,

상기 아날로그 영상 신호를 디지털 영상 신호로 변환하는 A/D 변환기와,

상기 A/D 변환기로부터 출력된 디지털 영상 신호의 소정 기간에 있어서의 레벨을 검출하는 검출 수단과,

상기 검출 수단에 의해 검출된 레벨과 목표값과의 차분값을 검출하는 차분 출력 수단과,

상기 차분 출력 수단의 출력에 대하여 시그마-델타 변조 처리를 실시하는 변조 수단과,

상기 변조 수단의 출력을 상기 입력 수단으로부터 입력된 아날로그 영상 신호에 공급함으로써, 상기 아날로그 영상 신호의 신호 전위를 조정하는 클램프 처리를 실행하고, 상기 클램프 처리한 아날로그 영상 신호를 상기 A/D 변환기에 출력하는 클램프 수단

을 포함하는 신호 처리 장치.

## 청구항 2.

제1항에 있어서,

상기 클램프 수단은 상기 변조 수단의 출력을 필터 처리하여 상기 아날로그 영상 신호에 공급하는 저역 통과 필터를 포함하는 것을 특징으로 하는 신호 처리 장치.

## 청구항 3.

제1항에 있어서,

상기 변조 수단은 상기 아날로그 영상 신호에 있어서의 1수평 라인의 모든 기간에 걸쳐 변조 결과를 출력하며,

상기 클램프 수단은 상기 아날로그 영상 신호에 있어서의 1수평 라인의 모든 기간에 걸쳐 상기 변조 수단의 출력을 상기 아날로그 영상 신호에 공급함으로써, 상기 클램프 처리를 실행하는 것을 특징으로 하는 신호 처리 장치.

## 청구항 4.

제1항에 있어서,

상기 검출 수단은 상기 디지털 영상 신호의 페데스탈 레벨(peDESTAL level)을 검출하며,

상기 변조 수단은 상기 아날로그 영상 신호의 페데스탈 기간에서만의 변조 결과를 출력하며,

상기 클램프 수단은 상기 페데스탈 기간에서만 상기 클램프 처리를 수행하는 신호 처리 장치.

## 청구항 5.

제1항에 있어서,

상기 변조 수단의 동작 주파수는 상기 아날로그 영상 신호의 주파수 대역보다도 높은 신호 처리 장치.

### 청구항 6.

제5항에 있어서,

상기 변조 수단의 동작 주파수는 상기 아날로그 영상 신호의 컬러 서브캐리어 신호(color subcarrier signal) 주파수의  $n$  배( $n$ 은 2 이상의 정수)인 신호 처리 장치.

### 청구항 7.

제1항에 있어서,

상기 변조 수단이 변조 결과를 출력하는 기간을 임의로 설정하는 설정 수단을 더 포함하고,

상기 클램프 수단은 상기 설정 수단에 의해 설정된 기간에만 상기 클램프 처리를 수행하는 신호 처리 장치.

### 청구항 8.

제1항에 있어서,

상기 차분 출력 수단의 출력 게인을 임의로 변경하고, 상기 출력 게인을 상기 변조 수단에 출력하는 게인 변경 수단을 더 구비하는 신호 처리 장치.

### 청구항 9.

제1항에 있어서,

상기 변조 수단은 샘플당 1비트의 신호를 출력하는 신호 처리 장치.

### 청구항 10.

제1항에 있어서,

상기 목표값을 임의로 설정하는 설정 수단을 더 구비하는 신호 처리 장치.

### 청구항 11.

제1항에 있어서,

상기 A/D 변환기, 상기 검출 수단, 상기 차분 출력 수단 및 상기 변조 수단은 동일한 집적 회로 상에 구성되고, 상기 입력 수단과 상기 클램프 수단은 상기 집적 회로와는 별개의 회로로 구성되어 있는 것을 특징으로 하는 신호 처리 장치.

**명세서**

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 신호 처리 장치에 관한 것으로, 특히 영상 신호를 클램프하는 장치에 관한 것이다.

텔레비전 수상기, 비디오 테이프 레코더 또는 디지털 비디오 카메라에 있어서의 공지의 아날로그 영상 신호 입력부에서는, 입력 신호에 직렬로 제공된 컨덴서와 A/D 변환기(ADC)의 입력 단자 사이의 신호 전위가 저항과 전류원을 포함하는 회로나 전류원을 포함하는 회로에 의해 증가/감소된다. 또한, 신호 경로에 제공되어 레벨 시프트용의 비디오 앰프부를 이용하여 신호의 페데스탈 레벨(peDESTAL level)이 클램프된다(예를 들어, 일본 특허공개 평7-135579호 공보 참조).

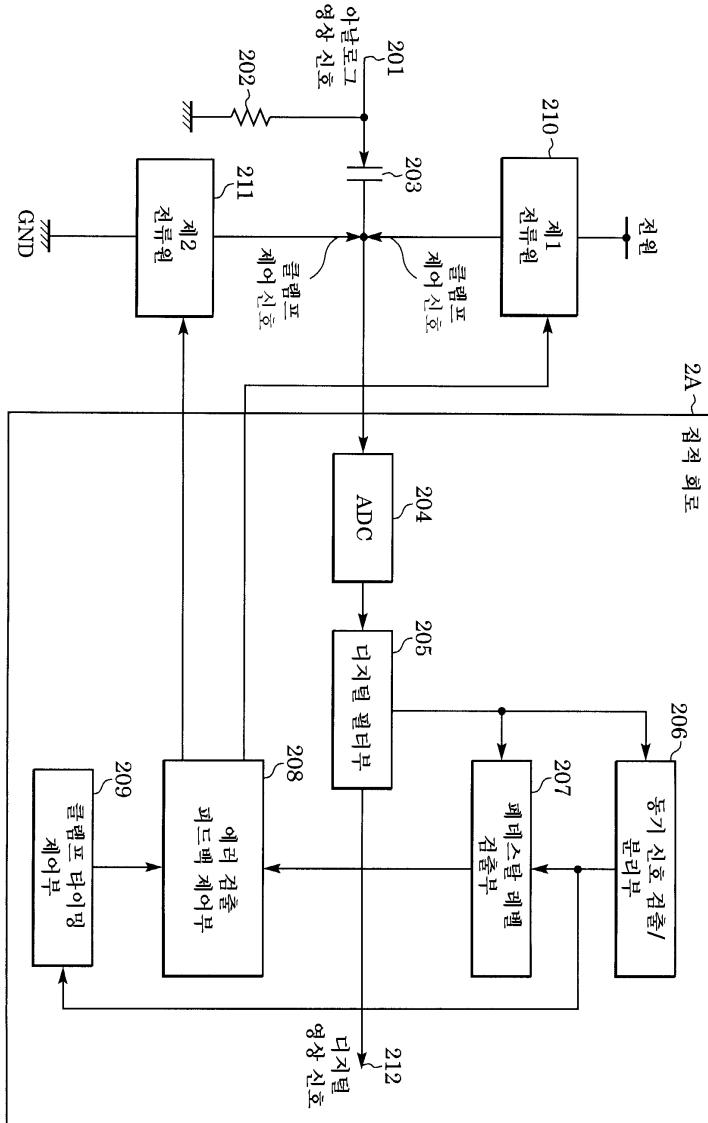

도 5는 공지의 디지털 영상 신호 처리 시스템에 있어서의 클램프 회로의 일례를 도시한 도면이다. 도 5에 도시된 바와 같이, 디지털 영상 신호 처리 시스템에서는, 입력 아날로그 영상 신호는 A/D 변환기(ADC)(204)에 의해 디지털 신호로 변환된 후 그 입력 영상 신호의 페데스탈 레벨이 검출된다. 그런 다음, 검출한 페데스탈 레벨과 목표값의 차분이 제로(0)가 되도록 전류원 등에 대해 피드백 제어를 수행함으로써 클램프 제어가 행해진다.

도 5에서, 입력 신호(201)는 아날로그 영상 신호이다. 예를 들어, 이 신호는 NTSC(National Television System Committee) 방식 또는 PAL(phase-alternation line) 방식 등의 텔레비전 신호 방식에 따른 콤포지트 신호(composite signal)이다. 종단 저항(202)은 입력 신호(201)를 전송하는 전송 선로와의 임피던스 매칭을 실현한다. 여기서는 소비자용(consumer-oriented) 영상 기기에 있어서 일반적인  $75\Omega$ 의 전송 선로에 정합한  $75\Omega$ 의 종단 저항이 사용된다.

커플링 컨덴서(203)는 DC 성분을 제거하며 접속되는 외부 기기(미도시)와 본 회로의 ADC(204)의 입력 단자 사이에서 AC 커플링을 실현한다. ADC(204)는 입력 신호(201)를 디지털 신호로 변환한다. 디지털 필터(205)는 저역 통과 필터나 노치 필터이고, 콤포지트 신호인 입력 신호(201)로부터 서브캐리어 신호를 제거하고 SYNC(동기 신호)가 부가된 휘도 신호 성분을 분리한다.

동기 신호(SYNC) 검출/분리부(206)는 디지털 필터부(205)로부터 획득한 SYNC가 부가된 휘도 신호 성분으로부터 콤포지트 SYNC 신호 성분을 분리한다. 페데스탈 레벨 검출부(207)는 동기 신호 검출/분리부(206)로부터 획득한 콤포지트 SYNC 신호 성분을 기준으로서 페데스탈 부분의 디지털 레벨(신호 레벨)을 검출한다.

에러 검출 피드백 제어부(208)는 임의로 설정된 페데스탈 레벨의 목표값과 페데스탈 레벨 검출부(207)에 의해 검출된 입력 신호(201)의 신호 레벨을 AD 변환하여 획득한 디지털값을 비교하여 그 차분값(에러)을 구한다. 에러 검출 피드백 제어부(208)는 차분값에 따라서 제1 전류원(210)과 제2 전류원(211)에 대하여 에러를 정정하기 위하여 제어 신호를 출력하여 피드백 제어를 행한다.

클램프 타이밍 제어부(209)는 동기 신호 검출/분리부(206)로부터 획득한 콤포지트 SYNC 신호에 기초하여 에러 검출 피드백 제어부(208)로부터의 제어 신호의 출력 타이밍을 제어한다. 예를 들어, 영상 신호에 있어서의 백포치(back porch) 부분에서만 클램프 제어를 행함으로써, 영상 신호에의 영향을 회피할 수 있다.

제1 전류원(210)은 컨덴서(203)와 ADC(204)를 접속하는 접속선과 전원 전압 사이에 설치된다. 이 제1 전류원(210)은 에러 검출 피드백 제어부(208)의 출력값이 1인 경우에 ON 되어, 컨덴서(203)를 충전시켜 페데스탈 레벨을 상승시킨다. 제2 전류원(211)은 컨덴서(203)와 ADC(204)를 접속하는 접속선과 접지 사이에 설치된다. 이 제2 전류원(211)은 에러 검출 피드백 제어부(208)의 출력값이 0인 경우에 ON 되어, 컨덴서(203)를 방전시켜 페데스탈 레벨을 하강시킨다.

또한, 제1 전류원(210)을 저항으로 대체하고, 제2 전류원(211)만으로 제어할 수도 있다. 마찬가지로, 제2 전류원(211)을 저항으로 대체하고, 제1 전류원(210)만으로 제어할 수도 있다.

입력 신호(201)는 제1 전류원(210) 또는 제2 전류원(211)에 의해 클램프된 후, ADC(204)에 의해 디지털 신호로 변환되고, 디지털 필터(205)에 의해 필터링된다. 이에 의해 디지털 영상 신호(212)가 획득된다. 도 5에서, ADC(204), 디지털 필터(205), 동기 신호 검출/분리부(206), 페데스탈 레벨 검출부(207), 에러 검출 피드백 제어부(208) 및 클램프 타이밍 제어부(209)는 집적 회로(2A)를 형성하도록 집적된다.

제1 및 제2 전류원(210, 211)을 이용하는 대신에, 컨덴서(203) 다음의 신호 경로에 비디오 앰프를 설치하여 신호 레벨을 시프트할 수도 있다. 비디오 앰프를 이용하는 경우, 비디오 앰프의 포지티브 입력측에 아날로그 입력 신호를 입력하고 네거티브 입력측에 에러 검출 피드백 제어부(208)로부터의 제어 신호를 입력함으로써 클램프 제어를 실현한다.

### 발명이 이루고자 하는 기술적 과제

그러나, 전류원이나 비디오 앰프를 이용하지 않고, 아날로그 영상 신호의 페데스탈 레벨을 클램프할 수 있는 보다 간소한 구성의 클램프 회로가 요구된다.

### 발명의 구성

본 발명은 전술한 문제를 해결하여, 보다 간소한 구성으로 클램프 처리를 수행할 수 있는 장치를 제공하는 것을 목적으로 한다.

본 발명의 일면에 따르면, 아날로그 영상 신호를 입력하는 입력 수단과, 상기 아날로그 영상 신호를 디지털 영상 신호로 변환하는 A/D 변환기와, 상기 A/D 변환기로부터 출력된 미리 정해진 기간의 디지털 영상 신호의 레벨을 검출하는 검출 수단과, 상기 검출 수단에 의해 검출된 레벨과 목표값과의 차분값을 검출하는 차분 출력 수단과, 상기 차분 출력 수단으로부터의 출력에 대하여 시그마-델타 변조를 수행하는 변조 수단과, 상기 변조 수단으로부터의 출력에 기초하여 상기 입력 수단에 의해 입력된 아날로그 영상 신호에 대해 클램프 처리를 수행하고, 상기 클램프 처리된 아날로그 영상 신호를 상기 A/D 변환기에 출력하는 클램프 수단을 포함하는 신호 처리 장치가 개시된다.

본 발명의 다른 특징 및 장점은 첨부 도면을 참조한 하기의 실시예에 대한 상세한 설명으로부터 분명해질 것이다.

#### <실시예>

이하, 도면을 참조하여 본 발명의 실시예에 대하여 설명한다.

#### [제1 실시예]

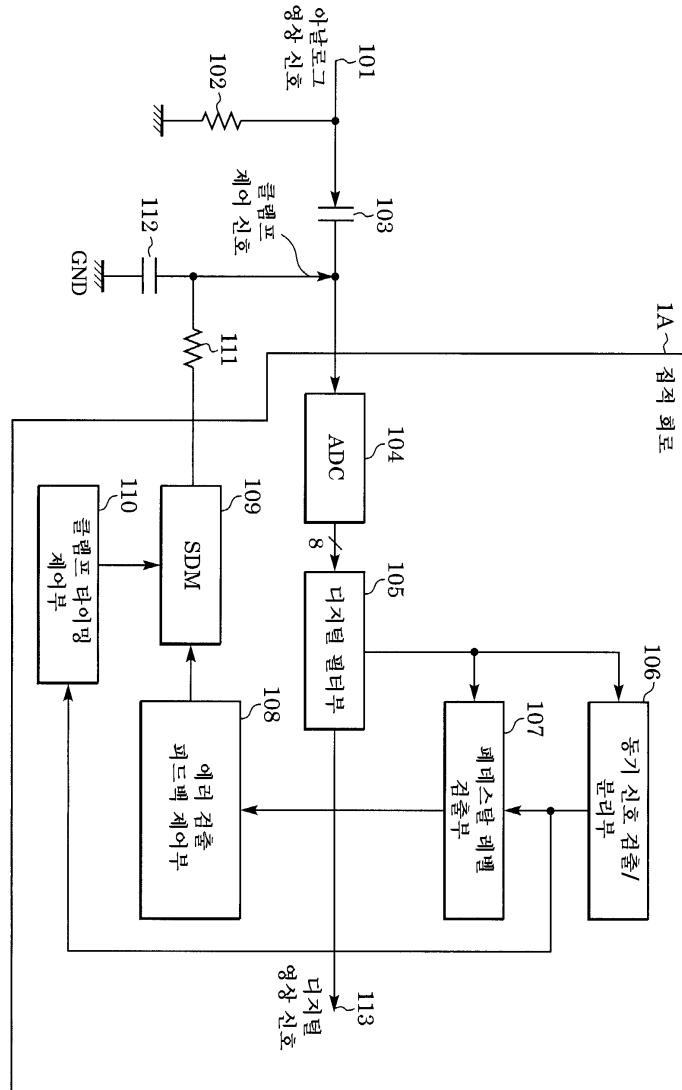

우선, 본 발명의 제1 실시예에 따른 영상 신호의 클램프 회로에 대하여 설명한다. 도 1은 본 발명의 제1 실시예에 따른 영상 신호의 클램프 회로를 포함하는 영상 신호 처리 시스템(또는 영상 처리 장치)의 개략 구성을 도시한 블록도이다.

도 1에 도시된 바와 같이, AD 변환 및 디지털 처리를 행하는 회로는 ASIC(application-specific integrated circuit)으로서 구성된다. 도 1에서, 입력 신호(101)는 아날로그의 영상 신호이다. 구체적으로, 입력 신호(101)는 NTSC 방식의 콤포지트 영상 신호이다. 입력 신호(101)는 NTSC 방식의 콤포지트 영상 신호에 국한되지 않으며, 휴도 신호(Y) 또는 PAL 방식의 영상 신호 등이어도 된다.

종단 저항(102)은 입력 신호(101)를 전송하는 전송 선로와 접지 사이에 접속되며, 전송 선로와의 임피던스 매칭을 실현한다. 여기서는 소비자용 영상 기기에 있어서 일반적인 75Ω의 전송 선로에 정합한 75Ω의 종단 저항이 사용된다.

커플링 컨덴서(103)는 영상 신호(입력 신호(101))의 전송 선로와 후술하는 A/D 변환기(ADC)(104)의 입력 단자 사이에 접속되어 있다. 커플링 컨덴서(103)는 외부 기기(미도시)로부터 전송 선로를 통해 공급되는 입력 영상 신호(101)의 DC 성분을 제거하여 그 영상 신호를 ADC(104)의 입력 단자에 입력한다. 즉, 커플링 컨덴서(103)는 입력 신호(101)를 AC 커플링하는데 이용된다.

ADC(104)는 AC 커플링된 아날로그 입력 신호(101)를 디지털 신호로 변환한다. 여기서, ADC(104)는 샘플링 레이트 27MSPS(mega samples per second)에서 동작하며 1샘플당 8비트의 디지털 데이터를 출력한다.

디지털 필터부(105)는 ADC(104)로부터 출력된 디지털 영상 신호(콤파지트 신호)로부터 서브캐리어 신호를 제거하고, SYNC가 부가된 휘도 신호 성분을 분리하여, 디지털 영상 신호(113)를 출력한다. 구체적으로, 디지털 필터부(105)는 저역 통과 필터 또는 노치 필터이다.

동기 신호(SYNC) 검출/분리부(동기 신호 분리 수단)(106)는 디지털 필터부(105)로부터 획득한 SYNC가 부가된 휘도 신호 성분으로부터 콤파지트 SYNC 신호를 분리한다. 페데스탈 레벨 검출부(레벨 검출 수단)(107)는 동기 신호 검출/분리부(106)로부터 획득한 콤파지트 SYNC 신호를 기준으로서 페데스탈 부분의 디지털 레벨(신호 레벨)을 검출한다.

에러 검출 피드백 제어부(차분 출력 수단)(108)는 임의로 설정된 페데스탈 레벨의 목표값과 페데스탈 레벨 검출부(107)에 의해 검출된 신호 레벨을 비교하여, 그 차분값(에러)을 후술하는 시그마-델타 변조부(SDM: sigma-delta modulator)(변조 수단)(109)에 출력한다.

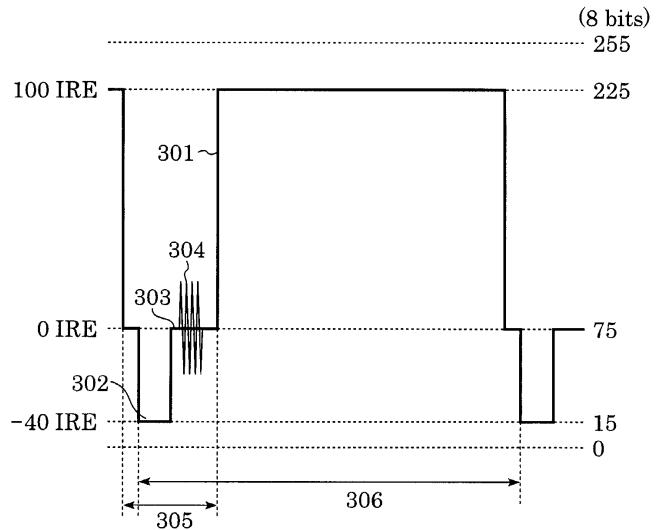

여기서, 본 실시예에서 처리되는 영상 신호에 대하여 설명한다. 도 2는 본 실시예에서 처리되는 입력 영상 신호의 상태를 도시한 도면이다. 도 2에 도시된 영상 신호는 NTSC 방식의 텔레비전 신호에 있어서의 1수평 라인(1H)에 해당한다. 수직 축에서, 좌측은 아날로그 영상 신호의 아날로그 신호 레벨(-40~100 IRE)을 나타내며, 우측은 AD 변환 후의 영상 신호의 디지털 신호 레벨(0~255)을 나타낸다. 도 2의 좌측의 값 -40~100 IRE는 NTSC 포맷에 따른 입력 신호(101)의 아날로그 입력 범위를 나타낸다.

도 2에 도시된 바와 같이, 본 실시예에서는 페데스탈 레벨(백포치(303)의 신호 레벨)이 0 IRE이고, 콤파지트 SYNC 칩(302)의 신호 레벨은 -40 IRE이고, 영상 신호 파형(301)의 영상 신호 부분은 백색의 휘도 100% 레벨이다. 즉, 설명을 간략화하기 위해, 도 2의 영상 신호 파형(301)은 백색의 휘도 100%의 신호이기 때문에, 콤파지트 신호이기는 하지만, 영상 신호 부분(기간 305을 제외한 기간 306)에는 크로마(chroma) 신호가 중첩되지 않는다.

한편, 아날로그 입력 범위와 대조하여, 도 2의 우측의 0~255까지의 값은 ADC(104)의 출력 범위(8비트)에 대응한다. 여기서는 이상적인 페데스탈 클램프가 행해졌을 때 획득될 수 있는 디지털값을 나타내고 있다.

도면으로부터 알 수 있는 바와 같이, 페데스탈 레벨의 목표 디지털값은 0 IRE에 대응한 75이다. 영상 신호 파형(301)은 입력 신호(101)의 파형이다. 콤파지트 SYNC 칩(302)은 수평 동기 신호를 나타낸다. 파형(304)은 컬러 버스트(color burst) 신호를 나타내며 NTSC 방식인 경우 3.579545MHz의 주파수를 갖는다. 또한, 기간 305는 수평 블랭킹 기간(horizontal blanking period)(수평 귀선(retrace) 기간)을 나타내며 NTSC 방식인 경우  $10.9 \pm 0.2\mu\text{s}$ 이다. 기간 306은 1수평 라인의 기간이며 NTSC 방식인 경우  $63.555\mu\text{s}$ 이다.

도 1을 다시 참조하면, 시그마-델타 변조(SDM)부(109)는 에러 검출 피드백 제어부(108)로부터 페데스탈 레벨에러를 수신하여, 입력 영상 신호의 대역보다 충분히 높은 동작 주파수인 54MHz에서 시그마-델타 변조("델타-시그마 변조"라고도 함)를 실시한 다음, 1샘플당 1비트의 변조된 신호를 출력한다.

또한, "시그마"와 "델타"는 반대로 될 수 있으므로, 시그마-델타 변조부(109)는 "델타-시그마 변조부"(DSM)라고도 부를 수 있다.

클램프 처리의 정밀도를 높이기 위해, SDM(109)의 출력을 1샘플당 2비트의 디지털 데이터로 하고, SDM(109)의 후단에 설치된 저역 통과 필터(LPF)부를 D/A 변환기로 치환할 수도 있다.

클램프 타이밍 제어부(110)는 SYNC 검출/분리부(106)로부터 획득한 콤파지트 SYNC 신호 성분에 기초하여 SDM(109)의 출력 타이밍을 제어한다.

일반적인 페데스탈 클램프에서는, 클램프 처리가 영상으로서 표시되지 않는 수평 블랭킹 기간 305에 포함되는 백포치(303)에서 수행되는 것이 보통이다. 본 실시예에 이 방법을 적용할 수도 있다.

SDM(109)는 클램프 타이밍 제어부(110)로부터의 타이밍 신호에 따라서 클램프 처리를 행한다.

저항(111)은 SDM(109)의 출력 단자와 커플링 컨덴서(103)와 ADC(104)의 노드 사이에 접속된다. 컨덴서(112)의 한쪽 단자는 접지에 접속되며 다른 쪽의 단자는 저항(111)을 통하여 SDM(109)에 접속된다. 컨덴서(112) 및 저항(111)의 결합은

저역 통과 필터로서 기능한다. 이 저역 통과 필터는 페데스탈 레벨의 에러가 적어지도록 피드백 제어된 신호, 즉 SDM(109)에 의해 시그마-델타 변조된 신호를 평활화(영상에 영향을 주는 고주파 성분을 제거)하여 클램프 제어 신호를 생성한다. 이 클램프 제어 신호를 이용함으로써, 커플링 컨덴서(103)에 의해 DC 성분이 삭제된 입력 신호(101)가 클램프된다.

전술한 바와 같이, 커플링 컨덴서(103)에 의해 입력 신호(101)로부터 DC 성분이 제거되고, 이 신호에 대해 페데스탈 클램프가 수행된다. 그런 다음, 이 신호는 ADC(104)에 의해 디지털 신호로 변환되고 디지털 필터(105)를 통해 필터링되어, 디지털 영상 신호(113)가 획득된다.

집적 회로(IC)(1A)는 전술한 ADC(104), 디지털 필터(105), SYNC 검출/분리부(106), 페데스탈 레벨 검출부(107), 에러 검출 피드백 제어부(108), SDM(109) 및 클램프 타이밍 제어부(110)가 집적되어 있는 ASIC이다. 또한, 집적 회로(1A)는 CMOS(Complementary Metal Oxide Semiconductor) 프로세스만으로 제작된 반도체 회로이다.

또한, 집적 회로(1A)에 사용되는 동작 클럭은 다음과 같은 방식으로 생성된다. 발진기(미도시)에 의해 13.5MHz의 클럭이 생성되며 이 클럭은 PLL 회로(미도시)에 의해 2 및 4 체배된다. 이에 의해, 27MHz( $=13.5\text{MHz} \times 2$ ) 및 54MHz( $=13.5\text{MHz} \times 4$ )의 동작 클럭이 생성된다.

또한, 다른 주파수의 동작 클럭이 사용될 수도 있다. 예를 들어, 발진기의 주파수를 입력 영상 신호의 영상 포맷(NTSC 또는 PAL)의 서브캐리어 주파수로 하고, 그 서브캐리어 주파수를 PLL에 의해 체배할 수도 있다. 이들의 주파수를 이용함으로써 시스템 구성이 간소화될 수 있다.

이상, 도 1에 도시된 제1 실시예에 따른 전술한 페데스탈 클램프 방법과 도 5에 도시된 공지예의 주된 차이점은, 커플링 컨덴서(103)로부터 출력된 영상 신호 레벨을 제어하는 클램프 제어 신호의 생성 방법이다.

아래에서는, 도 5에 도시된 공지예와 제1 실시예의 클램프 회로를 비교하기로 한다. 도 5의 공지예에서는 집적 회로(2A)에 외부 부착한 전류원(또는 비디오 앰프)에 의해 페데스탈 레벨이 제어된다.

한편, 본 실시예에서는, SDM(109)와 저역 통과 필터의 조합에 의해 페데스탈 레벨을 제어하기 위한 신호가 생성된다. 여기서, SDM(109)와 저역 통과 필터의 조합은 시그마-델타 변조 D/A 변환기라고 간주할 수도 있다.

이와 같이, 공지의 클램프 회로는 집적 회로(2A)의 외부 컴포넌트로서 트랜지스터 등의 전류원이나 비디오 앰프를 필요로 하지만, 본 실시예에서는 크기가 작기 때문에 집적 회로(1A)에 용이하게 탑재할 수 있는 SDM(109)을 제공함으로써, 외부 컴포넌트로서 R(저항(111))과 C(컨덴서(112))로 구성되는 저역 통과 필터만을 필요로 한다.

이러한 구성에 의해, 공지예와 비교하여 시스템 내의 부품 수를 삭감할 수 있으며 실장 면적 및 비용을 줄일 수 있다.

또한, R과 C로 구성된 저역 통과 필터의 특성을 변경함으로써, SDM(109)의 고주파 성분을 입력 영상 신호에 의도적으로 중첩시켜, 일부 시스템에서 발생할 수 있는 특정 입력 영상에 대한 출력 영상의 비트(beat) 문제를 해결할 수 있다. 이 문제는 SDM(109)의 랜덤 노이즈 특성을 이용하여, 의사 디더링 처리(pseudo dithering)를 수행함으로써 해결할 수 있다.

## [제2 실시예]

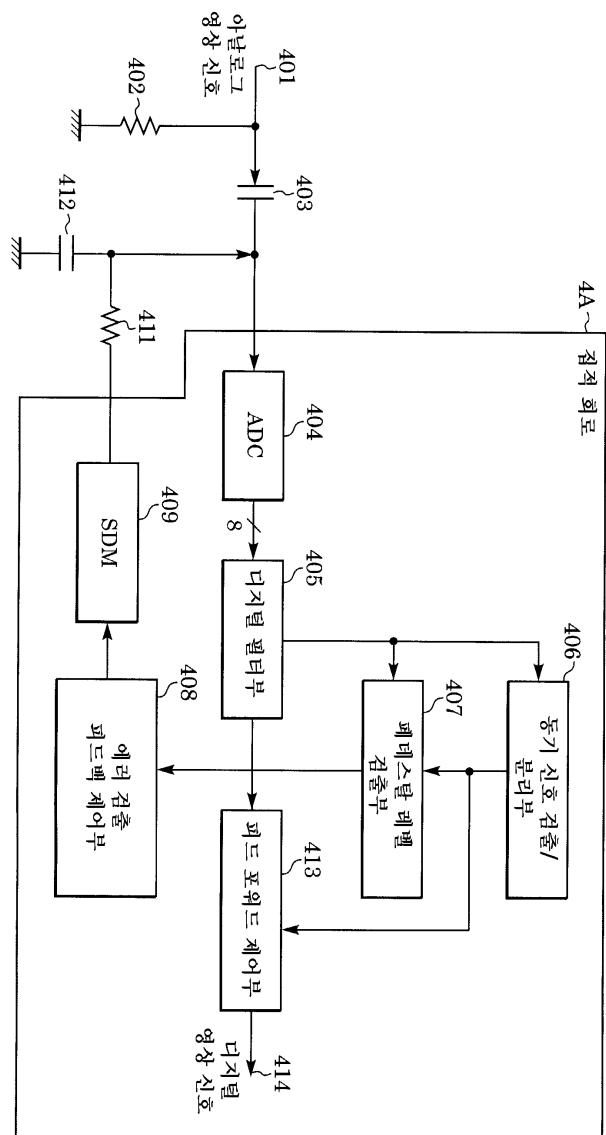

다음으로, 본 발명의 제2 실시예에 따른 영상 신호의 클램프 회로에 대하여 설명한다. 도 3은 본 발명의 제2 실시예에 따른 영상 신호의 클램프 회로를 포함하는 영상 신호 처리 시스템(또는 영상 처리 장치)의 개략 구성을 도시한 블록도이다.

도 3에 도시된 제2 실시예에서, 부호 401~409, 411 및 412로 표기된 부재는 도 1에 도시된 제1 실시예의 부호 101~109, 111 및 112로 표기된 것과 동등한 것이므로 이에 대한 설명을 생략한다. 또한, 제2 실시예의 회로 구성은, 도 1에 도시된 클램프 타이밍 제어부(110)가 설치되어 있지 않다는 점과 피드포워드 제어부(413)가 디지털 필터(405)의 후단에 설치되어 있다는 점에서, 제1 실시예의 회로 구성과 크게 다르다.

이러한 구성에 의해, 제2 실시예에 따른 클램프 회로는, 1수평 라인의 일부의 기간에만 클램프 처리가 수행되는 것이 아니라, 1수평 라인의 전체 기간 동안 클램프 제어가 수행된다. 또한, 피드백 루프에 의한 클램프 제어로 억제되지 않은 페데스탈 레벨의 변동이 피드포워드 제어부(413)에 의해 보상된다.

보다 구체적으로, 피드포워드 제어부(413)는, 여러 검출 피드백 제어부(408)에서 검출된 페데스탈 레벨 목표값과 실제 입력 디지털값의 차분(예러)이 페데스탈 클램프 처리의 피드백 제어 후에 잔존하는 경우, 페데스탈 레벨을 목표값에 근접하도록 하기 위한 피드포워드 제어를 행하여 디지털 영상 신호(414)를 출력한다.

즉, 디지털 영상 신호(414)는 입력 신호(401)를 페데스탈 클램프하고, 그 입력 신호(401)를 ADC(404)에 의해 디지털 신호로 변환한 다음, 디지털 필터(405)와 피드포워드 제어부(413)를 통해 필터링하여 생성된다. 집적 회로(4A)는 ADC(404), 디지털 필터(405), SYNC 검출/분리부(406), 페데스탈 레벨 검출부(407), 여러 검출 피드백 제어부(408), SDM(409), 및 피드포워드 제어부(413)가 집적되어 있는 ASIC이다. 예를 들어 집적 회로(4A)는 CMOS 프로세스에 의해 제작된 반도체 회로이다.

전술한 바와 같이, 제2 실시예에 따른 클램프 회로는 페데스탈 레벨이 SDM(409) 및 저역 통과 필터의 조합을 이용하여 제어된다. 이러한 구성에 의해, 도 5에 도시된 공지의 집적 회로(2A)와 달리 집적 회로(4A)에 트랜지스터 등의 전류원이나 비디오 앰프를 외부에 부착할 필요가 없다.

즉, 도 3에 도시된 바와 같이, 크기가 작기 때문에 집적 회로(4A)에 용이하게 탑재할 수 있는 SDM(409)을 제공하고 R(저항(411))과 C(컨덴서(412))로 구성되는 저역 통과 필터를 외부 부착함으로써 클램프 처리를 실현할 수 있다.

또한, 제2 실시예에 따른 클램프 회로는, 입력 영상 신호의 주파수 대역보다도 높은 동작 주파수로 시그마-델타 변조를 행하여, 클램프의 제어 신호를 생성한다. 따라서, 한정된 기간의 영상 신호가 아니라, 영상 신호의 전역에서 클램프 제어를 행하는 경우에도, 영상 신호의 주파수 대역에 영향을 주는 노이즈나 비트가 발생되지 않는다.

그 때문에, ADC(404)에 많은 양의 전류가 누설되는 경우에도, 영상 신호에 영향을 주지 않고, 충분한 응답 성능을 갖는 페데스탈 클램프 제어가 실현될 수 있다.

또한, 제2 실시예에서는, 피드백 제어에 의한 페데스탈 클램프에 부가하여, 피드백 제어에 의해서는 억제되지 않은 페데스탈 레벨의 변동을 보상하는 피드포워드 제어를 실시한다.

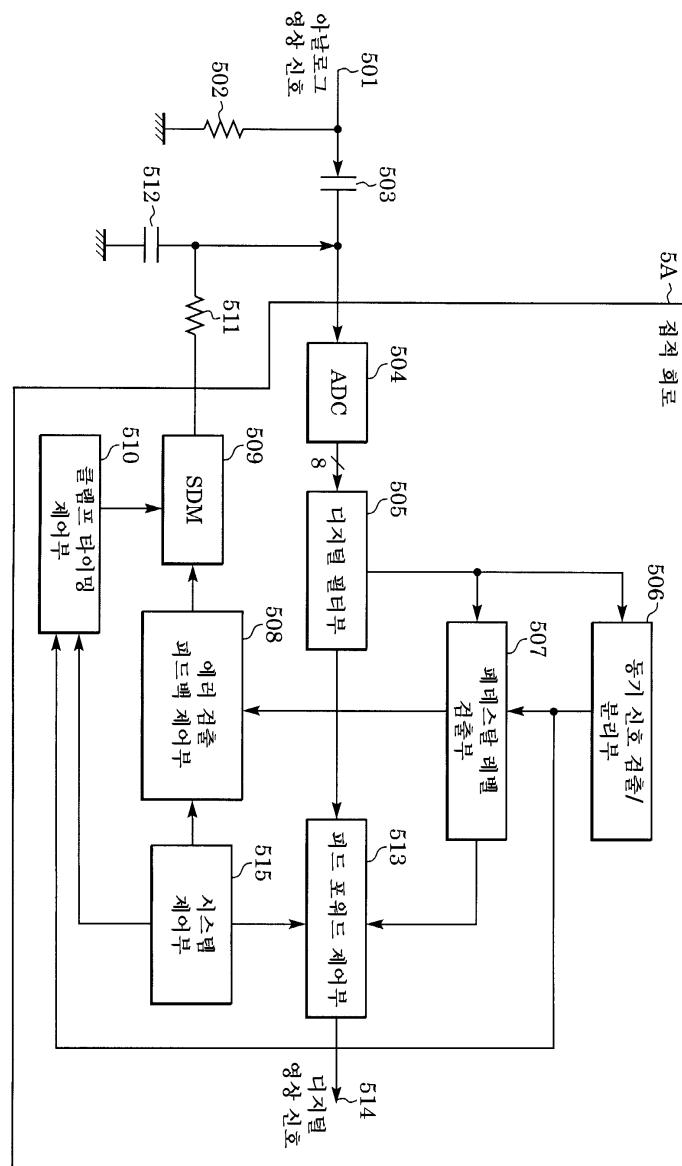

### [제3 실시예]

다음으로, 본 발명의 제3 실시예에 따른 영상 신호의 클램프 회로에 대하여 설명한다. 도 4는 본 발명의 제3 실시예에 따른 영상 신호의 클램프 회로를 포함하는 영상 신호 처리 시스템(또는 영상 처리 장치)의 개략 구성을 도시한 블록도이다.

도 4에 도시된 제3 실시예에서, 부호 501~512로 표기된 부재는 도 1에 도시된 제1 실시예에서 부호 101~112로 표기된 것과 동등한 것이므로 이에 대한 설명은 생략한다. 도 4에 도시된 피드포워드 제어부(513)는 도 3에 도시된 피드포워드 제어부(413)와 동등하다.

도 4의 회로 구성에서는 시스템 제어부(설정 제어 수단)(515)를 구비한다는 점에서 제1 및 제2 실시예와 상이하다. 시스템 제어부(515)는 여러 검출 피드백 제어부(508), 클램프 타이밍 제어부(510) 및 피드포워드 제어부(513)를 제어함으로써, 클램프 처리의 실행 타이밍, 여러 검출 피드백 제어량 및 피드포워드 제어량을 가변 제어한다.

보다 구체적으로, 시스템 제어부(515)는 클램프 타이밍 제어부(510)에서의 클램프 제어 신호의 출력 타이밍, 여러 검출 피드백 제어부(508)에서의 여러 검출 피드백 제어량 및 피드포워드 제어부(513)에서의 피드포워드 제어량을 가변 제어한다. 집적 회로(5A)는 도 4에 도시된 ADC(504), 디지털 필터(505), SYNC 검출/분리부(506), 페데스탈 레벨 검출부(507), 여러 검출 피드백 제어부(508), SDM(509), 피드포워드 제어부(513) 및 시스템 제어부(515)가 집적되어 있는 ASIC이다. 예를 들어, 집적 회로(5A)는 CMOS 프로세스로 제작된 반도체 회로이다.

제3 실시예에 따른 전술한 구성을 갖는 클램프 회로에서는, 페데스탈 레벨이 SDM(509) 및 저역 통과 필터의 조합에 의해 제어된다. 따라서, 도 5에 도시된 공지의 집적 회로(2A)와 달리 트랜지스터 등의 전류원이나 비디오 앰프를 집적 회로(5A)에 외부 부착할 필요가 없다.

즉, 크기가 작기 때문에 집적 회로(5A)에 용이하게 탑재할 수 있는 SDM(509)을 제공하고 R(저항(511))과 C(컨덴서(512))로 구성되는 저역 통과 필터를 외부 부착함으로써 클램프 처리를 실현할 수 있다. 이러한 구성에 의해, 공지에와 비교하여 부품 수를 삭감할 수 있으며 실장 면적 및 비용을 줄일 수 있다.

또한, 제3 실시예에서는, 시스템 제어부(515)에 의해 블랭킹 기간 동안만 클램프 제어하고 영상 부분을 포함하는 전체 기간 동안 클램프 제어할 수 있게 된다. 또한, 각종의 페데스탈 클램프 방법이 실현될 수 있다. 예를 들어, 입력 영상 신호의 휘도 레벨에 따라서 클램프 제어량을 변화시킬 수 있다.

또한, 시스템 제어부(515)가 SDM(509) 및 저역 통과 필터에 의해 피드백 제어량(피드백 개인)을 제어하고 디지털 피드포워드 제어량(피드포워드 개인)을 제어할 수 있도록 함으로써, 페데스탈 클램프가 보다 적절하게 제어될 수 있다.

전술한 바와 같이, 공지의 페데스탈 클램프 제어에서는, 도 5에 도시된 바와 같이, 집적 회로(2A)에 트랜지스터 등의 전류원이나 비디오 앰프가 외부에서 부착되어야만 한다.

한편, 전술한 제1 내지 제3 실시예에 따른 클램프 회로에서는, 비디오 대역의 신호를 주로 처리하는 집적 회로에 소규모의 SDM이 내장된다. 이러한 구성에 의해, 외부 컴포넌트로서 R(저항)과 C(컨덴서)로 구성되는 저역 통과 필터(시그마-델타 변조 DAC)만 필요로 된다. 이것에 의해, 부품 수를 삭감할 수 있으며 실장 면적 및 비용을 줄일 수 있다.

또한, 전술한 실시예에 따른 클램프 회로에 따르면, 시스템 구성에 따라서 이하에 기재하는 잇점을 얻을 수 있다.

클램프 처리 후의 출력 영상에 대한 비트 문제를 SDM의 랜덤 노이즈 특성을 이용하여 의사 디더링 처리를 수행함으로써 해결할 수 있다. 구체적으로, 저역 통과 필터의 특성을 변화시킴으로써, 의도적으로 시그마-델타 변조의 고주파 성분을 입력 영상 신호에 중첩시킨다.

피드백 제어에 의한 페데스탈 클램프에 추가하여, 피드백 제어로는 억제하지 못한 페데스탈 레벨의 변동을 피드포워드 제어에 의해 보상한다. 이에 의해, 보다 적절한 페데스탈 클램프 제어가 실현된다.

한정된 기간의 영상 신호가 아니라, 영상 신호의 전역에서 클램프 제어를 행하는 경우에도, 영상 신호의 주파수 대역에 영향을 주는 노이즈나 비트가 발생되지 않는다. 따라서, 많은 양의 전류가 ADC에 누설되는 경우에도, 영상 신호에 영향을 주지 않고, 충분한 응답 성능을 갖는 페데스탈 클램프가 실현될 수 있다.

대조적으로, 시스템 제어부를 가변 제어 수단으로서 제공함으로써 각종의 페데스탈 클램프 방법을 실현할 수 있다. 예를 들어, 클램프 제어를 영상 신호의 블랭킹 기간에만 수행하거나 영상 신호의 전역에 걸쳐 수행할 수 있다. 또한, 입력 영상 신호의 휘도 레벨에 따라서 클램프 제어량을 동적으로 변화시킬 수도 있다. 또한, 시스템 제어부는 SDM 및 저역 통과 필터에 의해 피드백 제어량(피드백 개인)을 가변 제어하고 디지털 피드포워드 제어량(피드포워드 개인)을 가변 제어할 수 있기 때문에, 페데스탈 클램프 제어가 보다 적절하게 수행될 수 있다.

전술한 실시예에 따른 클램프 회로의 시스템 컨트롤러 내의 각 블록의 처리 기능은 대응하는 프로그램을 메모리로부터 판독하여 중앙 처리 장치(CPU)가 해당 프로그램을 실행하도록 함으로써 실현될 수도 있다. 대안적으로, 각 기능의 전부 또는 일부를 전용 하드웨어에 의해 실현할 수도 있다.

전술한 메모리의 예로는 광자기 디스크 장치, 플래시 메모리 등의 불휘발성 메모리, CD-ROM 등의 데이터 판독만 가능한 기록 매체, RAM 이외의 휘발성 메모리, 및 이들 매체의 조합에 의한 컴퓨터 판독가능/기입가능 기록 매체를 포함한다.

전술한 클램프 회로의 시스템 컨트롤러 내의 각 처리를 행하는 기능을 실현하기 위한 프로그램을 컴퓨터 판독가능 기록 매체에 기록하고, 기록된 프로그램을 컴퓨터 시스템에 의해 판독 및 실행함으로써 각 처리를 수행할 수도 있다. 여기서, "컴퓨터 시스템"에는 OS(운영 체제) 및 주변 기기 등의 하드웨어가 포함된다.

상기 프로그램은 컴퓨터 시스템의 저장 장치 등으로부터 전송 매체를 통하여 또는 전송 매체 중의 전송파에 의해 다른 컴퓨터 시스템에 전송될 수도 있다. 여기서, 프로그램을 전송하는 "전송 매체"는 예를 들어 인터넷 등의 네트워크 및 전화 회선 등의 통신 회선과 같이, 정보를 전송하는 기능을 갖는 매체이다.

상기 프로그램은 전술한 기능의 일부만을 실현하도록 사용될 수도 있다. 또한, 상기 프로그램은 컴퓨터 시스템에 이미 기록되어 있는 프로그램과 협력하여 전술한 기능을 실현할 수 있는, 소위 차분 파일(differential file)(차분 프로그램)일 수도 있다.

또한, 전술한 프로그램을 기록한 컴퓨터 판독가능 기록 매체 등의 프로그램 제품도 본 발명의 실시예에 적용될 수 있다.

이상, 본 발명을 예시적 실시예에 대하여 설명하였지만, 본 발명은 개시된 실시예에 국한되지는 않는다. 반대로, 본 발명은 첨부된 청구항의 사상 및 범주에 포함된 각종의 변형물 및 등가물을 포함하는 것이다. 전술한 실시예 각각의 설명에 대응하는 청구항의 수가 반드시 하나인 것은 아니다. 또한, 전술한 실시예에 의해 각 클레임의 엘리먼트가 제한되지는 않는다.

### 발명의 효과

전술한 바와 같이, 본 발명의 신호 처리 장치에 따르면, 보다 간소한 구성으로 클램프 처리를 수행할 수 있는 장치가 제공된다.

### 도면의 간단한 설명

도 1은 본 발명의 제1 실시예에 따른 영상 신호의 클램프 회로를 포함하는 영상 신호 처리 시스템(또는 영상 처리 장치)의 개략 구성을 도시한 블록도.

도 2는 제1 실시예에 따른 영상 신호의 일례(NTSC)를 도시한 도면.

도 3은 본 발명의 제2 실시예에 따른 영상 신호의 클램프 회로를 포함하는 영상 신호 처리 시스템의 개략 구성을 도시한 블록도.

도 4는 본 발명의 제3 실시예에 따른 영상 신호의 클램프 회로를 포함하는 영상 신호 처리 시스템의 개략 구성을 도시한 블록도.

도 5는 공지의 디지털 영상 신호 처리 시스템에 있어서의 클램프 회로의 일례를 도시한 도면.

<도면의 주요 부분에 대한 부호의 설명>

101, 401, 501: 입력 신호

102, 402, 502: 종단 저항

103, 403, 503: 커플링 컨덴서

104, 404, 504: ADC

105, 405, 505: 디지털 필터부

106, 406, 506: 동기 신호 검출/분리부

107, 407, 507: 페데스탈 레벨 검출부

108, 408, 508: 에러 검출 피드백 제어부

109, 409, 509: SDM(시그마-델타 변환) 부

110, 510: 클램프 타이밍 제어부

111, 411, 511: 저항

112, 412, 512: 컨덴서

413, 513: 피드포워드 제어부

113, 414, 514: 디지털 영상 신호

515: 시스템 제어부

도면

도면1

## 도면2

## 도면3

도면4

## 도면5