(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4674474号

(P4674474)

(45) 発行日 平成23年4月20日(2011.4.20)

(24) 登録日 平成23年2月4日(2011.2.4)

(51) Int.Cl.

F 1

H04S 5/02 (2006.01)

H03F 3/68 (2006.01)H04S 5/02

H03F 3/68Q

B

請求項の数 4 (全 10 頁)

(21) 出願番号 特願2005-48351 (P2005-48351)

(22) 出願日 平成17年2月24日 (2005.2.24)

(65) 公開番号 特開2006-237928 (P2006-237928A)

(43) 公開日 平成18年9月7日 (2006.9.7)

審査請求日 平成19年12月20日 (2007.12.20)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(74) 代理人 100120156

弁理士 藤井 兼太郎

(72) 発明者 渡部 敦夫

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

審査官 大野 弘

最終頁に続く

(54) 【発明の名称】パラレル駆動バイアンプ切換回路

## (57) 【特許請求の範囲】

## 【請求項 1】

多チャンネル再生モードと2チャンネルステレオ再生モードとを選択的に切換可能なA V

アンプに用いるパラレル駆動バイアンプ切換回路であって、

P W M 方式の第1の増幅器と、

P W M 方式の第2の増幅器と、

前記第1の増幅器に接続する第1のスピーカと、

前記第2の増幅器に接続する第2のスピーカと、

遅延回路とを備え、

多チャンネル再生の時は第1の信号源の信号を前記第1の増幅器で増幅して前記第1のスピーカの端子に出力し前記第2の信号源の信号を前記第2の増幅器で増幅して前記第2のスピーカの端子に出力し、

2チャンネルステレオ再生の時は第1の信号源の信号を前記遅延回路を介して前記第1の増幅器で増幅して前記第1のスピーカの端子に出力すると共に前記第1の信号源の信号を前記第2の増幅器で増幅して前記第1のスピーカの同一端子に同一入力信号のタイミングを一致させることなく出力するように構成した事を特徴とするパラレル駆動バイアンプ切換回路。

## 【請求項 2】

多チャンネル再生モードと2チャンネルステレオ再生モードとを選択的に切換可能なA V

アンプに用いるパラレル駆動バイアンプ切換回路であって、

10

20

入力端子を第 1 の信号源にスイッチを介して接続し出力端子を第 1 のスピーカの端子に接続する PWM 方式の第 1 の増幅器と、

入力端子を第 2 の信号源にスイッチを介して接続し出力をスイッチを介して前記第 1 のスピーカの端子に接続するかまたはスイッチを介して第 2 のスピーカの端子に接続する PWM 方式の第 2 の増幅器と、

前記第 1 の信号源と前記第 1 の増幅器の入力との間にスイッチを介して接続された遅延回路と、

前記第 1 の信号源と前記第 2 の増幅器の入力との間にスイッチを介して接続された信号経路とを備え、

前記各部に配置された複数のスイッチの切換によって、

10

多チャンネル再生の時は第 1 の信号源の信号を前記第 1 の増幅器で増幅して前記第 1 のスピーカの端子に出力し前記第 2 の信号源の信号を前記第 2 の増幅器で増幅して前記第 2 のスピーカの端子に出力し、

2 チャンネルステレオ再生の時は第 1 の信号源の信号を前記遅延回路を介して前記第 1 の増幅器で増幅して前記第 1 のスピーカの端子に出力すると共に前記第 1 の信号源の信号を前記第 2 の増幅器で増幅して前記第 1 のスピーカの同一出力端子に同一入力信号のタイミングを一致させることなく出力するように構成した事を特徴とするパラレル駆動バイアンプ切換回路。

#### 【請求項 3】

増幅器は 3 個以上であり、遅延回路の数は増幅器の数より 1 個少ないものである請求項 1 記載のパラレル駆動バイアンプ切換回路。

20

#### 【請求項 4】

前記信号源となるデコーダと、

前記複数のスイッチのオン、オフを制御するコンピュータ装置と、

前記コンピュータ装置に指示を与えるモード選択部とをさらに備えた請求項 1 から 3 のいずれかに記載のパラレル駆動バイアンプ切換回路。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、多チャンネル再生及び 2 チャンネルステレオ再生が出来る AV アンプやレシーバなどの音響装置に関するものである。

30

#### 【背景技術】

#### 【0002】

従来、多チャンネル AV アンプとしてのサラウンド方式としては、ドルビーサラウンド方式が知られている（例えば、特許文献 1 の従来の例である第 2 図参照。）。

#### 【0003】

このドルビーサラウンド方式は、フロント 3 チャンネル、リア 1 チャンネルの構成であり、サラウンドプロセッサ回路 21 は、入力する左右 2 チャンネルのステレオ再生信号 L, R を基に、内部ロジックによりフロント用の左右出力 F<sub>L</sub>、F<sub>R</sub>（ステレオ）、リア用の左右出力 R<sub>L</sub>、R<sub>R</sub>（モノラル）、センター出力 C の計 5 つの出力を生成して出力する。上記 5 つの出力信号は、それぞれの出力回路毎に設けたパワーアンプ 22<sub>1</sub>～22<sub>5</sub>により増幅された後、スピーカーターミナル 23 を通じて各スピーカ 24<sub>L</sub>、24<sub>R</sub>、25<sub>L</sub>、25<sub>R</sub>、26<sub>C</sub> に送られ、それぞれのスピーカーをならす事により所定のドルビーサラウンド再生を行うものである。

40

#### 【特許文献 1】実公平 6-23119 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0004】

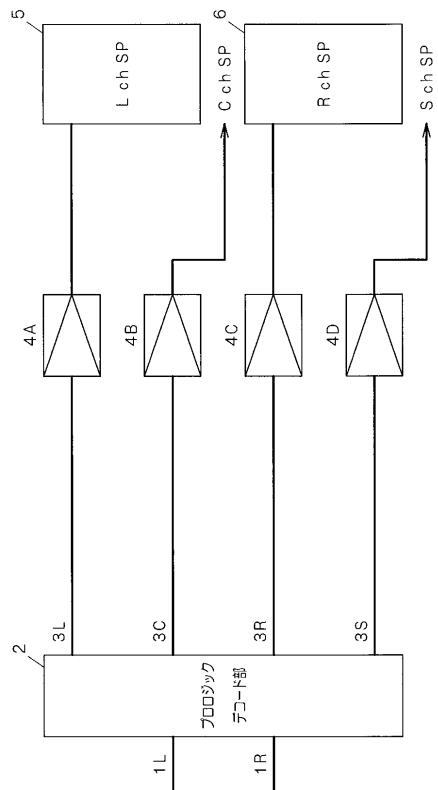

しかしながら上記の様な従来の AV アンプの場合、2 チャンネルステレオを再生する時を考えると図 4 のようになり、増幅回路が L チャンネル用の増幅器 4A、R チャンネル用

50

の増幅器 4 C の各 1 つしかない為、2 チャンネル時に使用しないマルチチャネル再生用アンプ 4 B、4 D が余っていても何ら 2 チャンネル再生時の音質向上に寄与出来ないという問題点を有していた。

【 0 0 0 5 】

本発明は、上記従来の問題点を改善しようとするものであり、多チャンネル A V アンプに簡単な切換回路と遅延回路を追加する事により、2 チャンネルステレオ再生時には並列駆動バイアンプ再生による高音質駆動を低価格で実現する事を目的としてなされたものである。

【課題を解決するための手段】

【 0 0 0 6 】

上記課題を解決する為に本発明のパラレル駆動バイアンプ切換回路は、多チャンネル再生モードと 2 チャンネルステレオ再生モードとを選択的に切換可能な A V アンプに用いるパラレル駆動バイアンプ切換回路であって、入力端子を第 1 の信号源にスイッチを介して接続し出力端子を第 1 のスピーカの端子に接続する PWM 方式の第 1 の増幅器と、出力端子を第 2 の信号源にスイッチを介して接続し出力をスイッチを介して前記第 1 のスピーカの端子に接続するかまたはスイッチを介して第 2 のスピーカの端子に接続する PWM 方式の第 2 の増幅器と、前記第 1 の信号源と前記第 1 の増幅器の間に挿入されスイッチを介して接続される遅延回路と、前記第 1 の信号源と前記第 2 の増幅器の入力との間にスイッチを介して接続された信号経路とを備え、前記各部に配置された複数のスイッチの切換によって、多チャンネル再生の時は第 1 の信号源の信号を前記第 1 の増幅器で増幅して前記第 1 のスピーカの端子に出力し前記第 2 の信号源の信号を前記第 2 の増幅器で増幅して前記第 2 のスピーカの端子に出力し、2 チャンネルステレオ再生の時は第 1 の信号源の信号を前記遅延回路を介して前記第 1 の増幅器で増幅して前記第 1 のスピーカの端子に出力すると共に前記第 1 の信号源の信号を前記第 2 の増幅器で増幅して前記第 1 のスピーカの同一端子に同一入力信号のタイミングを一致させることなく出力するように構成した事を特徴とするものである。

【 0 0 0 7 】

上記の各構成において、多チャンネル再生の時は第 1 の信号源の信号を第 1 の増幅器で増幅して第 1 のスピーカの端子に出力し、第 2 の信号源の信号を第 2 の増幅器で増幅して第 2 のスピーカ端子に出力し、2 チャンネルステレオ再生の時は第 1 の信号源の信号を前記第 1 の遅延回路を介して前記第 1 の増幅器で増幅して前記第 1 のスピーカの端子に出力すると共に前記第 1 の信号源の信号を前記第 2 の増幅器で増幅して前記第 1 のスピーカの端子に同時出力するよう各スイッチを切り替えるものである。

【 0 0 0 8 】

この時、遅延回路によって並列駆動する相互の増幅器の入力信号のタイミングを一致させずに入力する事により、無帰還フルデジタルアンプの場合に発生するノイズの重畠を抑え、かつ他方の増幅器の帰還回路による影響を受けずに直結出来る事を特徴とする。

【 0 0 0 9 】

また本発明のパラレル駆動バイアンプ切換回路は、増幅器は 3 個以上であり、遅延回路の数は増幅器の数より 1 個少ないものであることを特徴とする。

【 0 0 1 0 】

また本発明のパラレル駆動バイアンプ切換回路成は、前記信号源となるデコーダと、前記複数のスイッチのオン、オフを制御するコンピュータ装置と、前記コンピュータ装置に指示を与えるモード選択部とを備えることを特徴とする。

【 0 0 1 1 】

このように本発明は多チャンネル再生かステレオ再生かによって、スピーカの結線を変える事なく、ステレオ再生時にはパラレル駆動バイアンプ再生の高音質再生を可能とする。

【発明の効果】

【 0 0 1 2 】

10

20

30

40

50

本発明のパラレル駆動バイアンプ切換回路は、請求項 1 ないし 2 の構成により、ステレオ時のパラレル駆動バイアンプ切換を簡単な構成で普及価格帯の多チャンネル再生用の A V アンプで実現させる事が出来る様にしたため、従来の A V アンプでは困難とされていた大幅な音質改善をステレオ再生時に低コストで実現できるさせるという利点がある。

【発明を実施するための最良の形態】

【0013】

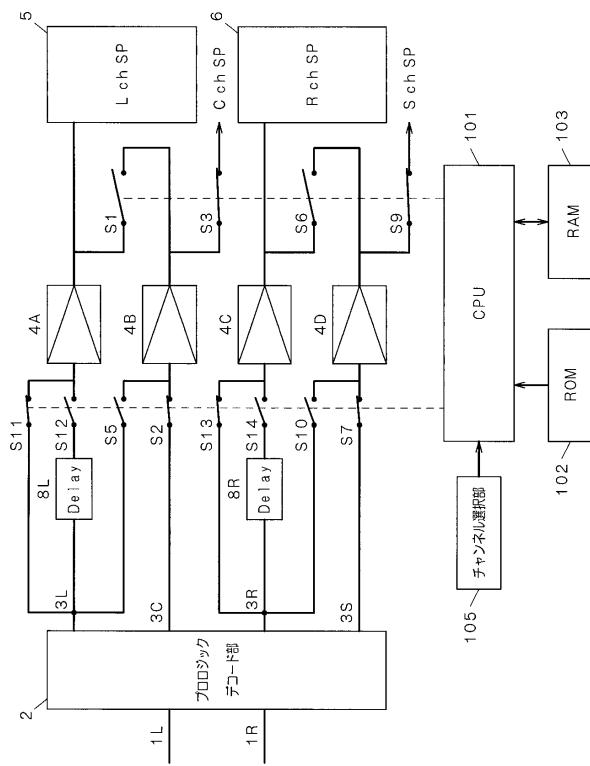

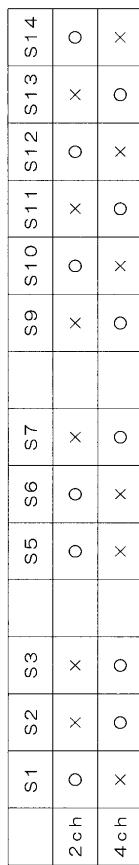

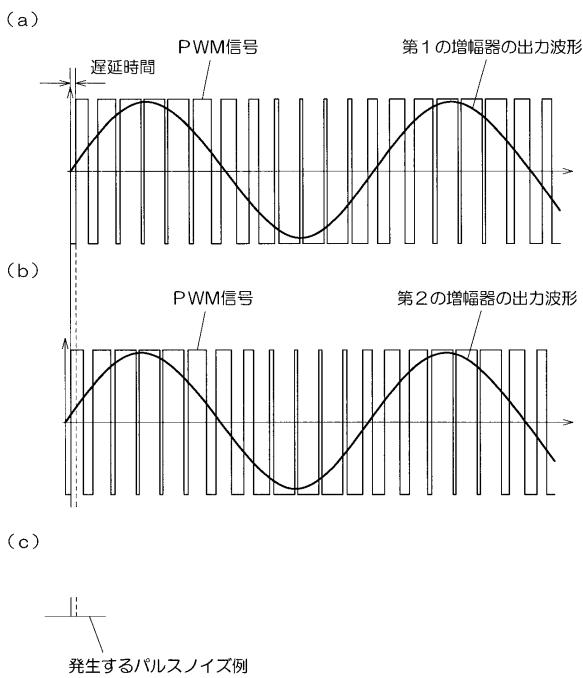

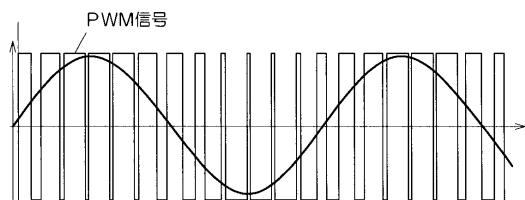

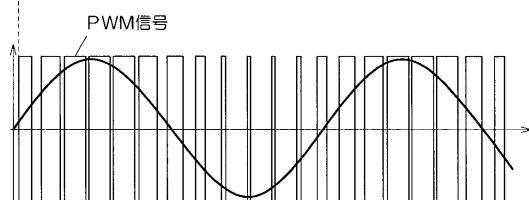

以下本発明のパラレル駆動バイアンプ切換回路の一実施形態例について、図面図 1 を参考しながら詳細に説明する。図 1 は本発明の一実施形態におけるパラレル駆動バイアンプ切換回路のブロック図、図 2 は本発明の一実施形態において、C P U により制御される各スイッチのオンオフ状態の組み合わせを示す説明図、図 3 は本発明の一実施形態における P W M 信号と出力波形に対する発生ノイズ例を示す説明図である。

10

【0014】

図 1 において、第 1 ないし第 14 のスイッチである S 1 ないし S 14 は連動スイッチで同時にオンまたはオフになる様に構成されている。

【0015】

4 チャンネルの音声情報でエンコードされた 2 チャンネル入力信号が入力端子 1 L、1 R に入力されるデコーダであるプロロジックデコード部デコーダ 2 は、第 1 ないし第 4 の信号源であるデコード出力端子 3 L、3 C、3 R、3 S を有し、それぞれ L チャンネル、C チャンネル、R チャンネルおよび S チャンネルの信号を出力する。デコードの方法は周知であるからここでは説明しない。

20

【0016】

本実施形態では図示の第 1 ~ 第 4 の増幅器 4 A ~ 4 D はパルスワイドモジュレーション ( P W M ) 方式を用いるものとし、第 1 の増幅器である L チャンネル用増幅器 4 A は、入力がスイッチ S 1 1 を介してデコード出力端子 3 L に接続され、出力は第 1 のスピーカである L チャンネル用のスピーカ 5 の端子に接続されると共にスイッチ S 1 を介して第 2 の増幅器である C チャンネル用増幅器 4 B の出力に接続される。

【0017】

第 2 の増幅器である増幅器 4 B は、入力をスイッチ S 2 を介してデコード出力端子 3 C に接続され、出力はスイッチ S 1 を介してスピーカ 5 の端子に接続されると共にスイッチ S 3 を介して第 2 のスピーカである図示しない C チャンネルスピーカの端子に接続されている。

30

【0018】

また増幅器 4 A の入力にはデコード出力端子 3 L からスイッチ S 1 2 を介してデコード出力端子 3 L との間に第 1 の遅延回路 8 L が接続されている。

【0019】

更に増幅器 4 B の入力にはスイッチ S 5 を介してデコード出力端子 3 L にがスイッチ S 5 を介して接続されている。

【0020】

第 3 の増幅器である R チャンネル用増幅器 4 C は、入力がスイッチ S 1 3 を介してデコード出力端子 3 R に接続され、出力は第 2 のスピーカである R チャンネル用のスピーカ 6 の端子に接続されると共にスイッチ S 6 を介して第 4 の増幅器である P W M 方式の S チャンネル用増幅器 4 D の出力に接続される。

40

【0021】

第 4 の増幅器である増幅器 4 D は、入力をスイッチ S 7 を介してデコード出力端子 3 S に接続され、出力はスイッチ S 6 を介してスピーカ 6 の端子に接続されると共にスイッチ S 9 を介して第 4 のスピーカである図示しない S チャンネルスピーカの端子に接続されている。

【0022】

また増幅器 4 C の入力にはスイッチ S 1 4 を介してデコード出力端子 3 R との間に第 2 の遅延回路 8 R が接続されている。

50

## 【0023】

更に増幅器4Dの入力にはスイッチS10を介してデコード出力端子3Rに接続されている。以下RチャンネルとSチャンネルについても上記と同様である。

## 【0024】

以上の様に構成されたパラレル駆動バイアンプ切換回路について、以下その動作を説明する。まずホーム・シアター再生機器として一般的である多チャンネル対応AVアンプとして用いる場合を説明する。チャンネル選択部105でが多チャンネル再生を選択した場合、映画等の多チャンネルエンコードされたソースは入力端子1L, 1Rから入力され、プロロジックデコード部デコーダ2で4つの信号に分離され、出力端子3L, 3C, 3R, 3Sに出力される。この時CPU101は、図2の4chに示すようにスイッチS2, S3, S7, S9, S11, S13をオンにし、スイッチS1, S5, S6, S10およびS12, S14をオフにする。プロロジックデコード部デコーダ2の出力端子3Lの出力はスイッチS5, S12が開いて、かつスイッチS11が閉じているので、増幅器4Aで増幅され、スイッチS1が開いている為Lチャンネル用スピーカ5の端子に印加されてノーマルモードで再生される。プロロジックデコード部デコーダ2の出力端子3Rの出力はスイッチS10, S14が開いて、かつスイッチS13が閉じているので、増幅器4Cで増幅され、スイッチS6が開いている為Rチャンネル用スピーカ6の端子に印加されてノーマルモードで再生される。

10

## 【0025】

プロロジックデコード部デコーダ2の出力端子3Cの出力はスイッチS2が閉じられているので増幅器4Bで増幅され、スイッチS1は開いてかつスイッチS3が閉じているのでCチャンネルスピーカで再生され、同じく出力端子3Sの出力はスイッチS7が閉じられているので増幅器4Dで増幅され、スイッチS6が開いてかつスイッチS9が閉じているのでSチャンネルスピーカで再生される。スイッチS5, S10, S12, S14が開いている為に遅延回路8L, 8Rは動作していない。

20

## 【0026】

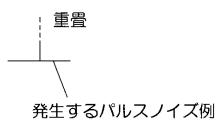

つぎに通常のステレオ再生の場合を説明する。プロロジックデコード部デコーダ2から出力される信号はLチャンネルとRチャンネルのみである。Lチャンネルについて説明すると、チャンネル選択部105が2チャンネルステレオ再生を選択した場合、CPU101は、図2の2chに示すようにスイッチS1, S5, S12を閉じ、スイッチS2, S3, S11を開く。出力端子3Lの信号は、スイッチS12から遅延回路8Lを通ってスイッチS12から増幅器4Aで増幅されてLチャンネル用スピーカ5の端子にの出力へ接続される経路とスイッチS5から第2のLチャンネル用増幅器4Bで増幅されてスイッチS1を通ってLチャンネル用スピーカ5の端子にの出力端子へ接続される経路とに二分され、Lチャンネル用再生スピーカ5をパラレル駆動バイアンプ方式で駆動再生することとなる。この時、遅延回路8Lがないと、従来のAVアンプにおけるPWM信号と出力波形に対する発生ノイズ例を示す説明図の図5(c)のノイズ波形の実線と破線の和に示すように2つのアンプの発生するノイズのタイミングが一致してノイズレベルが高くなる。遅延回路8Lにより並列駆動する相互の増幅器の入力信号のタイミングを一致させずに入力する事により、図3に示すように無帰還フルデジタルアンプの場合に発生するノイズが図3(c)の実線と遅延された破線のように一方が遅延することにより重畠を抑え、かつ他方の増幅器の帰還回路による影響を受けずに直結出来る事を特徴とする。図3、図5とも、簡単に示すためノイズは一波形ずつについて示している。

30

## 【0027】

ここで、遅延回路8Lの遅延時間の設定は、サンプリング周波数Fsをたとえば48kHzとすれば、ここで使用しているPWMモジュレータは1/4波長に対して256分割設定できる仕様のものを使った場合、少なくとも1/4波長に対して±(1/256)だけずらせばよい。したがって時間としては少なくとも、

$$(1/48000) \div 4 \times (2/256) = 0.041 \mu s$$

程度となる。この遅延時間は、上記の値を最低値として、パラレル駆動した場合の回路で

40

50

の歪等の最適値を勘案して決定する。

この場合、多チャンネル再生時には L チャンネル用増幅器となる増幅器 4 A と C チャンネル用増幅器となる増幅器 4 B は、パラレルに接続され L チャンネルスピーカ 5 を低インピーダンスで駆動し、低域成分の音質向上に効果があるダンピングファクターを増加する効果が期待できる。

【 0 0 2 8 】

R チャンネルに対しても同様に、スイッチ S 6 , S 1 0 , S 1 4 を閉じ、スイッチ S 7 , S 9 , S 1 3 を開いておく。出力端子 3 R の信号は、スイッチ S 1 4 から遅延回路 8 R を通ってスイッチ S 1 4 から増幅器 4 C で増幅されて R チャンネル用スピーカ 6 の端子に 10 の出力端子へ接続される経路と、スイッチ S 1 0 から第 4 の R チャンネル用増幅器 4 D で増幅されてスイッチ S 6 を通って R チャンネル用スピーカ 6 の端子にの出力用端子へ接続される経路とに二分され、R チャンネル用パラレル駆動バイワイヤリング再生スピーカ 6 をパラレル駆動バイアンプ方式で駆動再生することとなる。この時も L チャンネルと同様に、遅延回路 8 R により並列駆動する相互の増幅器の入力信号のタイミングを一致させずに入力する事により、図 3 に示すように無帰還フルデジタルアンプの場合に発生するノイズが図 3 ( c ) の実線と破線のように一方が遅延することにより重畠を抑え、かつ他方の増幅器の帰還回路による影響を受けずに直結出来る。

【 0 0 2 9 】

この場合も、多チャンネル再生時には R チャンネル用増幅器となる増幅器 4 C と S チャンネル用増幅器となる増幅器 4 D は、パラレルに接続され L チャンネルスピーカ 5 を低インピーダンスで駆動し、低域成分音質向上に効果があるダンピングファクターを増加する効果が期待できる。

【 0 0 3 0 】

なお、上記の説明ではオンまたはオフするスイッチを用いたが、スイッチ S 1 と S 3 、スイッチ S 6 と S 9 とをそれぞれ切換スイッチにし、スイッチ S 2 , S 5 , S 7 , S 1 0 , S 1 1 , S 1 2 , S 1 3 , S 1 4 を廃止し、代わりに増幅器 4 A , 4 B , 4 C , 4 D に入力切換スイッチを設ければスイッチの数を減らす事が出来る。

【 0 0 3 1 】

また、スイッチの位置は図示の位置に限定されず、信号の経路が、各増幅器、遅延回路およびスピーカの間で請求の範囲に示された接続状態に切り換わり得るものであればよいものである。

【 0 0 3 2 】

また、C P U 1 0 1 は、チャネル選択部 1 0 5 から与えられる選択情報に従って、スイッチ S 1 ~ S 1 4 のオンオフを制御する。このチャネル選択部 1 0 5 は、A V アンプの操作パネルに設けられ、ユーザーによって操作される。チャネル選択部 1 0 5 は、2 チャネルステレオ再生モードか 4 チャネル再生モードかを選択する。R O M 1 0 2 は、C P U 1 0 1 のための動作プログラムを格納している。C P U 1 0 1 は、この動作プログラムに従って動作する。R A M 1 0 3 は、C P U 1 0 1 がプログラム動作を行うときに発生する種々の作業データを記憶するワーキングメモリとして機能する。

【 0 0 3 3 】

さらに、ここでは 2 個のアンプのパラレル駆動を説明したが、3 個以上のアンプのパラレル駆動としてもよい。その場合遅延回路はパラレル数 - 1 個必要であり、スイッチも上記に準じて増設すればよい。

【 0 0 3 4 】

以上の様に本実施形態によれば、簡単なスイッチの切換回路と遅延回路を A V アンプ本体に追加する事により、多チャンネル再生用の増幅器をステレオ再生時に有効に用いてステレオ再生時の音質改善を図る事が出来る。

【 産業上の利用可能性 】

【 0 0 3 5 】

本発明のパラレル駆動バイアンプ切換回路は、多チャンネル再生及び 2 チャンネルステ

10

20

30

40

50

レオ再生が出来る A V アンプやレシーバなどの音響装置での音質向上用途にも適用できる産業上の利用可能性高いものである。

【図面の簡単な説明】

【0036】

【図1】本発明の一実施形態におけるパラレル駆動バイ A V アンプ切換回路のブロック図

【図2】本発明の一実施形態にお於いて、C P U により制御される各スイッチのオンオフ状態の組み合わせを示す説明図

【図3】本発明の一実施形態における例のP W M 信号と出力波形に対する発生ノイズ例を示す説明図

10

【図4】従来の A V アンプのブロック図

【図5】従来例の A V アンプにおけるP W M 信号と出力波形に対する発生ノイズ例を示す説明図

【符号の説明】

【0037】

1 L , 1 R 入力端子

2 プロロジックデコード部デコーダ

3 L , 3 C , 3 R , 3 S 出力端子

4 A 第1の増幅器

20

4 B 第2の増幅器

4 C 第3の増幅器

4 D 第4の増幅器

5 L チャンネル用スピーカ

6 R チャンネル用スピーカ

8 L , 8 R 遅延回路

S 1 ~ S 1 4 スイッチ

101 C P U

102 R O M

103 R A M

105 チャンネル選択部

30

【図1】

【図2】

【図3】

【図4】

【図5】

(a)

(b)

(c)

発生するパルスノイズ例

---

フロントページの続き

(56)参考文献 特開平09-271100(JP, A)

特開2004-048333(JP, A)

実開昭60-047316(JP, U)

特開昭60-192512(JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| H 04 R | 3 / 0 0 |

| H 03 F | 3 / 6 8 |

| H 04 S | 5 / 0 2 |

| H 04 S | 7 / 0 0 |