(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2011-527827

(P2011-527827A)

(43) 公表日 平成23年11月4日(2011.11.4)

(51) Int.Cl.

**H01L 27/146 (2006.01)**

**H04N 5/361 (2011.01)**

**H04N 5/374 (2011.01)**

F 1

H01L 27/14 A

H04N 5/335 610

H04N 5/335 740

テーマコード(参考)

4M118

5C024

審査請求 未請求 予備審査請求 未請求 (全 18 頁)

(21) 出願番号 特願2011-517402 (P2011-517402)

(86) (22) 出願日 平成21年6月25日 (2009.6.25)

(85) 翻訳文提出日 平成23年1月7日 (2011.1.7)

(86) 国際出願番号 PCT/US2009/003794

(87) 国際公開番号 WO2010/005490

(87) 国際公開日 平成22年1月14日 (2010.1.14)

(31) 優先権主張番号 12/169,723

(32) 優先日 平成20年7月9日 (2008.7.9)

(33) 優先権主張国 米国(US)

(71) 出願人 510215606

オムニヴィジョン テクノロジーズ イン

コーポレイテッド

アメリカ合衆国 カリフォルニア州 95

054 サンタ クララ バートン ドラ

イヴ 4275

(74) 代理人 110001210

特許業務法人 YK I 国際特許事務所

(72) 発明者 プラディ フレデリック ティー

アメリカ合衆国 ニューヨーク ロチェス

ター ステイト ストリート 343

(72) 発明者 マッカートン ジョン ピー

アメリカ合衆国 ニューヨーク ロチェス

ター ステイト ストリート 343

最終頁に続く

(54) 【発明の名称】暗電流を低減させた裏面照射イメージセンサ

## (57) 【要約】

裏面照明イメージセンサは、画素アレイの複数の感光素子を実装したセンサ層と、センサ層の裏面に隣接する酸化膜層を備える。センサ層は、シード層と、シード層の上に形成されたエピタキシャル層を含み、シード層は、指定されたドーパントがセンサ層の画素アレイ領域に略限定される断面ドーピングプロファイルを有する。このドーピングプロファイルにより、有利な点として、センサ層と酸化膜層との界面において発生する暗電流が低減される。イメージセンサは、デジタルカメラまたはその他の種類のデジタルイメージングデバイスに実装できる。

FIG. 3

**【特許請求の範囲】****【請求項 1】**

各々が裏面照明用に構成された画素アレイを有する複数のイメージセンサを形成するためのウェハレベル加工方法であって、前記イメージセンサはイメージセンサウェハを使って形成され、前記イメージセンサウェハは基板と、前記基板上に形成された埋め込み酸化膜層と、前記埋め込み酸化膜層上に形成されたシード層を含み、前記方法は、

前記シード層の上に犠牲酸化膜層を形成するステップと、

前記イメージセンサウェハの画素アレイ領域を露出させるステップと、

前記露出された画素アレイ領域内の前記シード層の中にドーパントを注入するステップと、

10

前記犠牲酸化膜層を除去するステップと、

前記ドープシード層の上にエピタキシャル層を形成するステップと、

前記イメージセンサウェハをさらに加工して、複数のイメージセンサを形成するステップと、

を含むことを特徴とする方法。

**【請求項 2】**

請求項 1 に記載の方法であって、

前記イメージセンサウェハの画素アレイ領域を露出させる前記ステップは、

前記犠牲酸化膜層の上にフォトレジストを堆積させるステップと、

前記フォトレジストをパターニングして、前記イメージセンサウェハの前記画素アレイ領域を露出させるステップと、

20

をさらに含み、

前記ドーパントを前記シード層の中に注入した後に、前記フォトレジストの残りの部分が除去されることを特徴とする方法。

**【請求項 3】**

請求項 1 に記載の方法であって、

前記犠牲酸化膜層と前記シード層を通じて前記埋め込み酸化膜層の表面に延びるアライメントマークを形成するステップをさらに含むことを特徴とする方法。

**【請求項 4】**

請求項 1 に記載の方法であって、

前記ドーパントは、ヒ素とリンの一方からなる n 型ドーパントであることを特徴とする方法。

30

**【請求項 5】**

請求項 1 に記載の方法であって、

前記ドーパントは、ボロンとインジウムの一方からなる p 型ドーパントであることを特徴とする方法。

**【請求項 6】**

請求項 1 に記載の方法であって、

前記露出された画素アレイ領域内の前記シード層の中にドーパントを注入する前記ステップは、前記ドーパントを、前記犠牲酸化膜層を通じて前記露出された画素アレイ領域内の前記シード層の中に注入するステップをさらに含むことを特徴とする方法。

40

**【請求項 7】**

請求項 1 に記載の方法であって、

前記露出された画素アレイ領域内の前記シード層の中にドーパントを注入する前記ステップは、前記露出された画素アレイ領域の各々の前記犠牲酸化膜層に開口部をエッチングするステップと、前記エッチングされた開口部を通じて前記シード層に前記ドーパントを注入するステップをさらに含むことを特徴とする方法。

**【請求項 8】**

請求項 1 に記載の方法であって、

前記犠牲酸化膜層を除去する前に前記イメージセンサウェハをアニーリングするステッ

50

プをさらに含むことを特徴とする方法。

【請求項 9】

請求項 1 に記載の方法であって、

前記エピタキシャル層の中に前記画素アレイの感光素子を形成するステップをさらに含むことを特徴とする方法。

【請求項 10】

請求項 1 に記載の方法であって、

前記基板を除去して、前記埋め込み酸化膜層の裏面を露出させるステップをさらに含むことを特徴とする方法。

【請求項 11】

請求項 1 に記載の方法であって、

前記イメージセンサウェハを前記複数のイメージセンサに分離するステップをさらに含むことを特徴とする方法。

【請求項 12】

請求項 1 に記載の方法であって、

前記イメージセンサウェハは、SOI (silicon-on-insulator) ウェハを含むことを特徴とする方法。

【請求項 13】

裏面照明用に構成された画素アレイを有するイメージセンサであって、

前記画素アレイの複数の感光素子を含むセンサ層と、

前記センサ層の裏面に隣接する酸化膜層と、

を備え、

前記センサ層はシード層と、前記シード層の上に形成されたエピタキシャル層を含み、前記シード層は、指定されたドーパントが前記センサ層の画素アレイ領域に略限定される断面ドーピングプロファイルを有することを特徴とするイメージセンサ。

【請求項 14】

請求項 13 に記載のイメージセンサであって、

前記ドーパントは、ヒ素とリンの一方からなるn型ドーパントであることを特徴とするイメージセンサ。

【請求項 15】

請求項 13 に記載のイメージセンサであって、

前記ドーパントは、ボロンとインジウムの一方からなるp型ドーパントであることを特徴とするイメージセンサ。

【請求項 16】

請求項 13 に記載のイメージセンサであって、

前記ドーパントは、前記シード層の上に形成され、前記シード層の上に前記エピタキシャル層が形成される前に除去される前記犠牲酸化膜層を通じて前記シード層の中に注入されることを特徴とするイメージセンサ。

【請求項 17】

請求項 13 に記載のイメージセンサであって、

前記ドーパントは、前記画素アレイ領域内の犠牲酸化膜層の中にエッチングされた開口部を通じて前記シード層の中に注入され、前記犠牲酸化膜層は前記シード層の上に前記エピタキシャル層を形成する前に除去されることを特徴とするイメージセンサ。

【請求項 18】

請求項 13 に記載のイメージセンサであって、

前記イメージセンサはCMOSイメージセンサであることを特徴とするイメージセンサ。

【請求項 19】

デジタルイメージングデバイスであって、

裏面照明用に構成された画素アレイを有するイメージセンサと、

10

20

30

40

50

前記イメージセンサの出力を処理してデジタル画像を生成するように構成された1つまたは複数の処理要素と、

を備え、

前記イメージセンサは、

前記画素アレイの複数の感光素子を有するセンサ層と、

前記センサ層の裏面に隣接する酸化膜層と、

を備え、

前記センサ層は、シード層と、前記シード層の上に形成されたエピタキシャル層を備え、前記シード層は、指定されたドーパントが前記センサ層の画素アレイ領域に略限定される断面ドーピングプロファイルを有することを特徴とするデジタルイメージングデバイス。

10

#### 【請求項 20】

請求項19に記載のデジタルイメージングデバイスであって、

前記イメージングデバイスはデジタルカメラを備えることを特徴とするデジタルイメージングデバイス。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、一般に、デジタルカメラおよびその他の種類のイメージングデバイスに使用される電子イメージセンサと、より詳しくは、裏面照明イメージセンサの形成に用いられる加工技術に関する。

20

##### 【背景技術】

##### 【0002】

一般的な電子イメージセンサは、二次元アレイとして配置された多数の感光性画像素子（「画素」）を有する。このようなイメージセンサは、画素の上に適当なカラーフィルタアレイ（CFA）を形成することによって、カラー画像を生成するように構成してもよい。この種のイメージセンサの例は、“Image Sensor with Improved Light Sensitivity”と題する米国特許出願公開第2007/0024931号明細書において開示されており、同出願を引用によって本願に援用する。

30

##### 【0003】

周知のように、イメージセンサは、CMOS（相補型金属酸化膜半導体）回路を使って実装されてもよい。このような構成では、各画素は一般に、シリコン基板上のシリコンセンサ層の中に形成されたフォトダイオードおよびその他の回路素子を有する。一般に1つまたは複数の誘電層がシリコンセンサ層の上に形成され、他の回路素子のほか、相互接続を実現するための多層の配線層が組み込まれる。イメージセンサの、誘電層およびこれに関連する配線層が形成される面が一般に表面と呼ばれ、シリコン基板を持つ面が裏面と呼ばれる。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

【特許文献1】米国特許出願公開第2007/235829号明細書

40

【特許文献2】欧州特許出願公開第1,612,863号明細書

【特許文献3】米国特許出願公開第2006/186560号明細書

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

表面照明イメージセンサは、被写体であるシーンからの光がイメージセンサの表面に入射するもので、シリコン基板は比較的厚い。しかしながら、イメージセンサの表面に誘電層に関連する配線層およびその他の特徴部が存在することによって、イメージセンサの開

50

口率と量子効率が不利な影響を受けることがある。

#### 【0006】

裏面照明イメージセンサとは、表面の誘電層に伴う開口率と量子効率の問題に対処するために、厚いシリコン基板を薄くするか、除去して、被写体であるシーンからの光がイメージセンサの裏面に入射するように構成されたイメージセンサである。したがって、入射光は、誘電層の配線層およびその他の特徴部の影響を受けなくなり、開口率と量子効率が改善される。

#### 【0007】

裏面照明イメージセンサは、シリコン基板の厚さを薄くし、または除去するために、加工が困難な場合がある。たとえば“Photo-Sensor and Pixel Array with Backside Illumination and Method of Forming the Photo-Sensor”と題する米国特許出願公開第2007/0194397号明細書等に開示されているような従来の加工技術では、ダイが大型化し、コスト高となりうる。

10

#### 【0008】

裏面照明イメージセンサに伴うまた別の問題は、いわゆる「暗」電流、すなわち、入射光が全くなくても、センサ内で生成される電流に関する。暗電流は、入射光を検出しにくくするため、センサの性能に不利な影響を与える。このような電流は、特に、SOI (silicon-on-insulator) イメージセンサウェハを利用して形成される裏面照明イメージセンサの場合に特に大きな問題となるが、これは暗電流がセンサ層と埋め込み酸化膜層との界面において発生する傾向にあるからである。たとえば、T.ジョイ他の“Development of a Production-Ready, Back-Illuminated CMOS Image Sensor with Small Pixels” 2007 IEDM Technical Digest, pp. 1007-1009 を参照されたい。

20

#### 【0009】

そこで、特にSOIイメージセンサウェハを使用した場合に、暗電流が低減される裏面照明イメージセンサを形成するための加工技術が必要とされている。

#### 【課題を解決するための手段】

30

#### 【0010】

本発明の説明のための実施形態では、暗電流が低減された裏面照明イメージセンサが提供される。

#### 【0011】

本発明の1つの態様によれば、裏面照明イメージセンサを形成する工程が提供される。この工程は、それぞれ、裏面照明用に構成された画素アレイを有する複数のイメージセンサを形成するウェハレベルの工程であり、イメージセンサはイメージセンサウェハを利用して形成される。イメージセンサウェハは、基板と、基板上に形成された埋め込み酸化膜層と、埋め込み酸化膜層の上に形成されたシード層を含む。この工程は、シード層の上に犠牲酸化膜層を形成するステップと、イメージセンサウェハの画素アレイ領域を露出させるステップと、露出された画素アレイ領域内のシード層の中にドーパントを注入するステップと、犠牲酸化膜層を除去するステップと、ドープシード層の上にエピタキシャル層を形成するステップと、イメージセンサウェハをさらに加工して複数のイメージセンサを形成するステップと、を含む。

40

#### 【0012】

イメージセンサウェハの画素アレイ領域を露出させるには、たとえば、犠牲酸化膜層の上にフォトレジストを堆積させ、フォトレジストをパターニングすることによって、イメージセンサウェハの画素アレイ領域を露出させてもよい。フォトレジストの残りの部分は、シード層にドーパントを注入した後に除去される。

#### 【0013】

ドーパントを露出された画素アレイ領域内のシード層に注入するには、たとえば、犠牲

50

酸化膜層を通じて、露出された画素アレイ領域内のシード層にドーパントを注入してもよい。別の例として、ドーパントを露出された画素アレイ領域内のシード層に注入するためには、露出された画素アレイ領域の各々の犠牲酸化膜層にエッチングで開口部を形成し、エッチングされた開口部からドーパントをシード層に注入してもよい。

#### 【0014】

本発明の別の態様によれば、裏面照明イメージセンサは、画素アレイの複数の感光素子を実装したセンサ層と、センサ層の裏面に隣接する酸化膜層を有する。センサ層は、シード層と、シード層の上に形成されたエピタキシャル層を含み、シード層は、指定されたドーパントがセンサ層の画素アレイ領域に略限定されるような断面ドーピングプロファイルを有する。

10

#### 【発明の効果】

#### 【0015】

本発明による裏面照射イメージセンサは、有利な態様として、デジタルカメラまたはその他の種類のイメージングデバイスに実装され、これによって、イメージセンサダイの大きさやコストが大幅に増大することなく、このようなデバイスの性能が改善される。

#### 【0016】

本発明の上記およびその他の目的、特徴、利点は、以下の説明と図面を見れば明らかであり、図中、できるかぎり、複数の図面に共通する同じ特徴には同じ参照番号を用いた。

#### 【図面の簡単な説明】

#### 【0017】

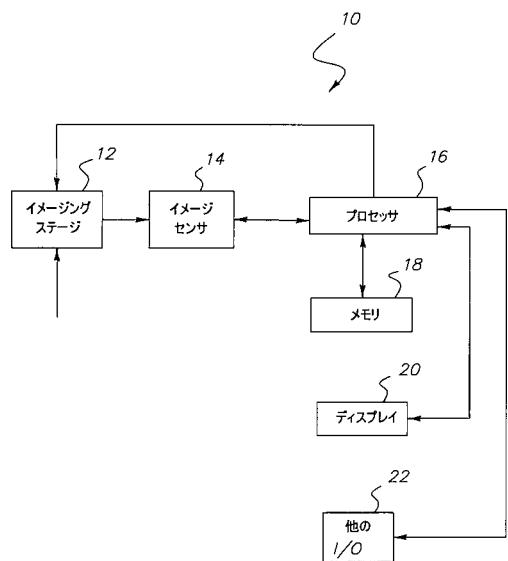

【図1】本発明の実施形態により構成された裏面照明イメージセンサを備えるデジタルカメラのブロック図である。

20

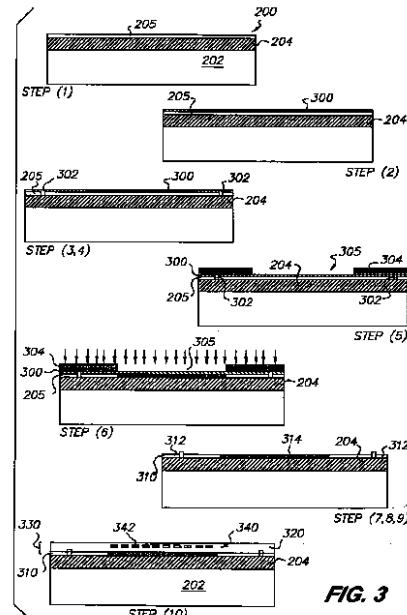

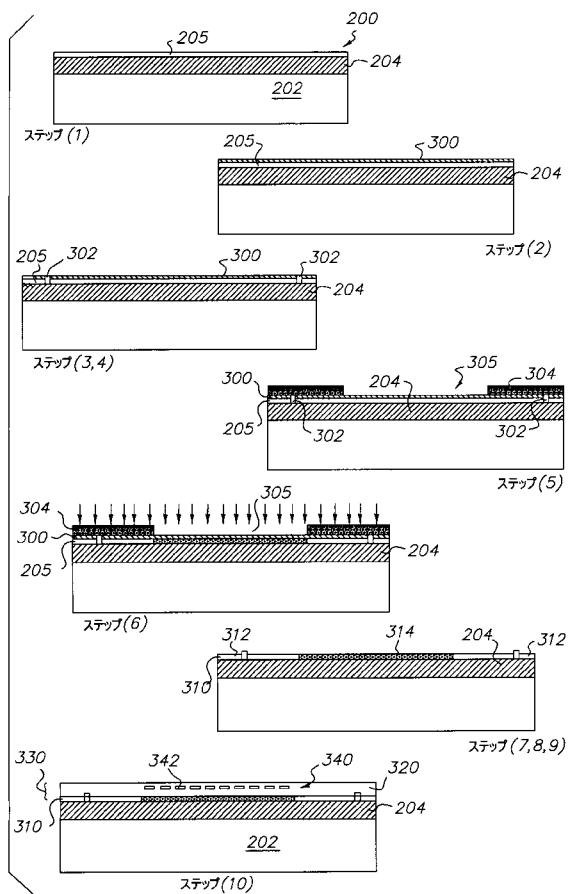

【図2】裏面照明イメージセンサの一部の、そのイメージセンサを形成する工程の一例における各段階の断面図であり、ドープされたシリコンシード層を形成する技術を説明する図である。

【図3】本発明の実施形態による、裏面照明イメージセンサの一部の、そのイメージセンサを形成する工程の一例における各段階の断面図である。

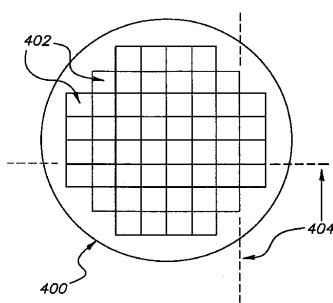

【図4】図3の工程例を用いて形成された複数のイメージセンサを含むイメージセンサウェハの平面図である。

#### 【発明を実施するための形態】

#### 【0018】

本明細書では、本発明をデジタルカメラ、裏面照明イメージセンサおよび、このようなイメージセンサを形成するための加工技術の具体的な実施形態に関連して説明する。しかしながら、理解すべき点として、説明のためのこれらの構成は例として示したにすぎず、本発明の範囲をいかようにも限定するものともみなすべきではない。当業者は、開示された構成が、他の各種のイメージングデバイスおよびイメージセンサにも容易に応用できることがわかるであろう。

30

#### 【0019】

図1は、本発明の実施形態におけるデジタルカメラ10を示す。このデジタルカメラにおいて、被写体であるシーンからの光は、イメージングステージ12に入力される。イメージングステージは、レンズ、減光フィルタ、アイリスおよびシャッタ等、従来の要素を有していてもよい。光は、イメージングステージ12によって合焦されて、イメージセンサ14の上に結像され、イメージセンサは入射光を電気信号に変換する。デジタルカメラ10はさらに、プロセッサ16と、メモリ18と、ディスプレイ20と、1つまたは複数のその他の入力/出力(I/O)要素22を有する。

40

#### 【0020】

図1の実施形態では別の要素として示されているが、イメージングステージ12はイメージセンサ14と、おそらくはデジタルカメラ10の1つまたは複数のその他の要素と一緒に化させて、小型カメラモジュールを形成してもよい。

#### 【0021】

50

イメージセンサ14は、この実施形態では、C M O Sイメージセンサであると仮定されるが、他のタイプのイメージセンサを使って本発明を実施してもよい。より詳しくは、イメージセンサ14は、図3に関して以下に説明する方法で形成される裏面照明イメージセンサであってもよい。イメージセンサは一般に、行と列に配置された複数の画素を含む画素アレイを有し、画素アレイのサンプリングと読み出しに関連するその他の回路、たとえば、信号発生回路、信号処理回路、行列選択回路等を備えていてもよい。このサンプリングおよび読み出し回路は、たとえば、画素アレイから読み出されるアナログ信号を処理するためのアナログ信号プロセッサと、この信号をデジタル形式に変換するためのアナログ-デジタル変換器を含んでいてもよい。デジタルカメラ10での使用に適した、これらおよびその他の種類の回路は当業者の間で周知であるため、本明細書では説明しない。サンプリングおよび読み出し回路は部分的にイメージセンサの外に配置しても、あるいは、たとえばフォトダイオードおよび画素アレイのその他の要素と共に集積回路で画素アレイと一緒に形成してもよい。

10

## 【0022】

イメージセンサ14は一般に、関連するC F Aパターンを有するカラーイメージセンサとして実装される。イメージセンサ14に使用できるC F Aパターンとしては、先に引用した米国特許出願公開第2007/0024931号明細書において開示されているものがあるが、本発明の他の実施形態では、それ以外のC F Aパターンを用いてもよい。別の例としては、従来のベイヤパターンも使用でき、これは“Color Imaging Array”と題する米国特許第3,971,065号明細書に開示されており、同特許を引用によって本願に援用する。

20

## 【0023】

プロセッサ16は、たとえばマイクロプロセッサ、C P U(中央処理ユニット)、A S I C(特定用途集積回路)、D S P(デジタル信号プロセッサ)またはその他の処理デバイスまたは、これらの複数のデバイスの組み合わせを備えていてもよい。イメージングステージ12の各種の要素とイメージセンサ14は、プロセッサ16から供給されるタイミング信号またはその他の信号によって制御されてもよい。

20

## 【0024】

メモリ18は、たとえば、R A M(ランダムアクセスメモリ)、R O M(リードオンリーメモリ)、フラッシュメモリ、ディスクベースメモリ、リムーバブルメモリまたはその他の種類の記憶素子等のあらゆる方式のメモリのあらゆる組み合わせで構成されてもよい。

30

## 【0025】

画素アレイのサンプリングと読み出しおよび対応する画像データの処理にかかる機能はメモリ18に記憶され、少なくとも部分的にソフトウェアの形で実装され、プロセッサ16によって実行されてもよい。

## 【0026】

イメージセンサ14によって捕捉された画像は、プロセッサ16によってメモリ18の中に保存され、ディスプレイ20に表示されてもよい。ディスプレイ20は一般に、アクティブマトリクスカラーL C D(液晶ディスプレイ)であるが、その他の種類のディスプレイを利用してよい。その他のI/O要素22は、たとえば各種のオンスクリーンコントロール、ボタン、その他のユーザインターフェース、ネットワークインターフェース、メモリカードインターフェース等を含んでいてもよい。

40

## 【0027】

図1に示されるタイプのデジタルカメラの動作に関するその他の詳細は、たとえば、先に引用した米国特許出願公開第2007/0024931号明細書に記載されている。

## 【0028】

図1に示されるデジタルカメラは、当業者の間で周知の種類の追加の、または代替の要素を備えていてもよいことがわかるであろう。特に図示されず、本明細書にも記されていない要素は、当業者の間で周知のものの中から選択してもよい。前述のように、本発明は、さまざまな他のデジタルカメラまたはイメージングデバイスに実装してもよい。また、

50

前述のように、本明細書に記載される実施形態の特定の要素は、少なくとも部分的に、イメージングデバイスの1つまたは複数の処理要素によって実行されるソフトウェアの形で実装されてもよい。このようなソフトウェアは、本明細書の教示から容易に実装でき、これは、当業者にとって明らかであろう。

#### 【0029】

イメージセンサ14は、シリコン基板またはその他の種類の基板上に作製されてもよい。一般的なCMOSイメージセンサにおいて、画素アレイの各画素は、その画素における光源レベルを測定するためのフォトダイオードおよびこれに関連する回路を備える。このような回路は、たとえばトランジスタ、リセットトランジスタ、選択トランジスタ、出力トランジスタ、その他の要素が周知の従来の方法で構成されたものを備えていてもよい。

10

#### 【0030】

前述のように、SOIイメージセンサから形成された裏面照明イメージセンサにおいて発生する問題は、センサ層と埋め込み酸化物層との界面において発生しがちな暗電流に関する。この問題に対処する方法を、図2,3に関して説明する。留意すべき点として、これらの図に示される断面は本発明の各種の態様を明瞭に示すために簡略化されており、必ずしも正確な縮尺ではない。ある実施形態は、明確に示されていないが、説明した一般的な種類のイメージセンサに一般的に関連していると当業者の間で周知の各種の他の要素を含んでいてもよい。

20

#### 【0031】

図2,3に示される技術には一般に、イメージセンサウェハを加工して、それぞれが裏面照明のために構成された画素アレイを有する複数のイメージセンサを形成することがかかる。図2,3に示されるイメージセンサウェハ200の一部は概して、イメージセンサの中の特定の1つに対応し、周辺領域により取り囲まれる画素アレイ領域を含むように描かれている。周辺領域は、ボンドパッド領域、またはイメージセンサの他の部分を含むか、あるいはこれと関連付けられてもよい。別の画素アレイ領域は一般に、イメージセンサウェハを使用して形成される個々のイメージセンサに関連付けられる。

20

#### 【0032】

イメージセンサウェハ200はまた、表面と裏面を有する。前述のように、表面は一般に、イメージセンサの、誘電層とこれに関連付けられる配線層が形成される面を指し、シリコン基板を有する面は裏面と呼ばれる。「表面」と「裏面」という用語は、本明細書において、イメージセンサウェハまたはこのようなウェハから形成されるイメージセンサの特定の面、およびイメージセンサウェハまたは対応するイメージセンサの特定の層の面を指す。

30

#### 【0033】

前述のように、図の実施形態は、裏面照明イメージセンサ、すなわち、被写体のシーンからの光がセンサの裏面から画素アレイのフォトダイオードまたは他の感光素子に入射するイメージセンサに関する。

#### 【0034】

注意すべき点として、「上(on)」、「上(over)」等の用語は、イメージセンサウェハの層または対応するイメージセンサに関連して使用された場合、広く解釈されるものとし、したがって、1つまたは複数の中間の層またはその他の中間のイメージセンサ特徴部または素子の存在を排除するものとは解釈されない。したがって、本明細書において、ある層が他の層の上に、または他の層の上に形成されているとの記載があった場合、その層は、1つまたは複数の別の層によって後者の層から分離されているかもしれない。

40

#### 【0035】

図2,3に示されるイメージセンサウェハ200は、SOI(silicon-on-insulator)ウェハの例である。本発明の別の実施形態では、他の種類のウェハを利用して裏面照明イメージセンサを形成してもよく、たとえば、埋め込み酸化膜層を持

50

たないエピタキシャルウェハまたはバルク半導体ウェハでもよいが、SOIウェハを用いれば一般に、裏面加工のための、より平滑な表面が提供される。

#### 【0036】

図2は、イメージセンサウェハ200の埋め込み酸化膜層の表面の上にドープシリコンシード層を形成するための1つの考えられるウェハレベル工程を示す。この工程は、ステップ(1)、(2)、(3)を含む。

#### 【0037】

ステップ(1)は、シリコン基板202と、基板上に形成された埋め込み酸化膜(BOX)層204と、埋め込み酸化膜層の上に形成されたシリコンシード層205を含む、出発材料としてのSOIイメージセンサウェハ200を示す。前述のように、本明細書では、イメージセンサウェハの各種の層は表面と裏面を有するように描かれててもよい。たとえば、埋め込み酸化膜層204は、表面204Fと裏面204Bを有する。

10

#### 【0038】

ステップ(2)において、シリコンシード層205のin-situドーピングを行い、図のように、N+シリコンシード層205'を形成する。N+シリコンシード層は、画素アレイがPMOS(p型金属酸化膜半導体)回路である場合に使用され、画素アレイがNMOS(n型金属酸化膜半導体)回路であれば、P+シリコンシード層が用いられる。この例では、PMOS回路であると想定されるため、前述のようにドープシリコンシード層はN+シリコンシード層である。

20

#### 【0039】

ステップ(3)において、N+シリコンシード層205'の上にシリコンエピタキシャル層210を成長させ、シリコンエピタキシャル層の中に多数のウェル212を形成する。ウェル212は一般に、イメージセンサウェハの、あるイメージセンサの画素アレイ領域ではなく、その周辺領域に対応する部分に形成する。

#### 【0040】

図2に示される工程は、裏面照明イメージセンサの中のセンサ層と埋め込み酸化膜層との界面における暗電流を低減させることができる。しかしながら、出願人は、図のステップ(3)に示されるように、この特定の技術によって、周辺ウェル212がN+シリコンシード層205'に、または相互に短絡することを発見した。このような周辺ウェルの短絡は、シリコンエピタキシャル層210の厚さを増加させることによって防止できるが、これは、望ましくない面として、エピタキシャル層210の中で形成される画素アレイの隣接するフォトダイオード間のクロストークの増大の原因となりうる。

30

#### 【0041】

図3は、暗電流が低減されるだけでなく、エピタキシャル層の厚さを大幅に増大させることなく、周辺ウェルの短絡を回避する、裏面照明イメージセンサを形成するためのウェハレベル工程を示す。工程は、ステップ(1)から(10)を含む。

#### 【0042】

注意すべき点として、以下に説明するイメージセンサ形成工程は、イメージセンサウェハ上のドープシリコンシード層の形成を中心として説明する。イメージセンサ形成の他の態様、たとえばイメージセンサウェハのセンサ層中の画素アレイのフォトダイオードおよび関連回路の形成および、回路、導体、ボンドパッド等の他の特徴部の形成は、当業者の間で周知の従来の技術によって実行してもよい。

40

#### 【0043】

ステップ(1)はここでも、シリコン基板202と、基板上に形成された埋め込み酸化膜層204と、埋め込み酸化膜層の上に形成されたシリコンシード層205を含む、出発材料としてのSOIイメージセンサウェハ200を示す。この実施形態におけるシリコンシード層は、厚さが約50オングストロームから約0.2マイクロメートル(μm)である。

#### 【0044】

ステップ(2)において、犠牲酸化膜層300をシリコンシード層205の上に形成す

50

る。本実施形態における犠牲酸化膜層は、厚さが約 50 オングストロームから約 200 オングストロームである。

#### 【0045】

ステップ(3)において、アラインメントマーク 302 をパターニングし、形成するが、これには一般に、フォトレジストの堆積と、これに続く露出、現像、エッチング等のリソグラフィ工程がかわる。アラインメントマークは、所望のアラインメントマークパターンにしたがってパターニングされ、所望のパターンは一般に、イメージングセンサウェハの加工に使用されているリソグラフィ装置の具体的な種類によって異なる。この例では、アラインメントマーク 302 は犠牲酸化膜層 300 とシード層 205 を通り、その下の埋め込み酸化膜層 204 の表面まで延びる。

10

#### 【0046】

アラインメントマークは、ポリシリコンであってもよい。このタイプのポリシリコンアラインメントマークを裏面照明イメージセンサの中に形成するための有利な方法は、先に引用した米国特許出願のコダック社ドケット番号第 94870 号に開示されている。同特許出願中に開示されている 1 つの実施形態では、アラインメントマークの開口部をエッチングして、その下にある埋め込み酸化膜層の表面を露出させ、開口部から、埋め込み酸化膜層の露出面上へのエピタキシャル成長によってポリシリコンアラインメントマークを形成する。

#### 【0047】

ステップ(4)において、アラインメントマーク 302 のパターニングの残りのフォトレジストを犠牲酸化膜層 300 から削り取る。

20

#### 【0048】

ステップ(5)において、フォトレジスト 304 を犠牲酸化膜層 300 の上に堆積させ、アラインメントマーク 302 と整合させてパターニングし、画素アレイ領域 305 を露出させる。画素アレイ領域 305 は、このイメージセンサウェハから形成される予定の、あるイメージセンサに関連付けられ、そのイメージセンサの周辺領域は露出させず、フォトレジストによって被覆したままとする。別の実施形態では、フォトレジストの堆積とパターニング以外の方法を使って、イメージセンサウェハの画素アレイ領域を露出させてもよい。

30

#### 【0049】

ステップ(6)において、ドーパントを、露出された画素アレイ領域 305 内のシード層 205 の中に注入する。この例のドーパントは n 型ドーパント、すなわちヒ素であるが、他の実施形態では、リン等の他の n 型ドーパントも使用できる。前述のように、n 型ドーパントは PMOS 回路に基づく画素アレイに使用され、p 型ドーパントは NMOS 回路に基づく画素アレイに使用される。p 型ドーパントとしては、ボロンとインジウムがある。ここでも、この例は PMOS 回路と想定されているため、ドーパントは n 型ドーパントである。シード層に注入するためのドーパントの濃度は、約  $5 \times 10^{14}$  原子 /  $\text{cm}^3$  より大きいか、またはこれと等しいが、他の実施形態では他のドーパント濃度も使用できる。

#### 【0050】

図に示す構成において、ステップ(6)は、ドーパントを、犠牲酸化膜層 300 を通つて、露出された画素アレイ領域 305 内のシード層 205 の中に注入するステップを含む。他の実施形態では、たとえば、露出された画素アレイ領域内の犠牲酸化膜層に開口部をエッチングし、エッチングによる開口部からシード層の中にドーパントを注入するステップを含んでもよい。後者のエッチング開口部方式は、犠牲酸化膜層の中に注入する方法で実現できるものより深く注入するために使用してもよい。ドーピング作業完了後のシリコンシード層 205 を、本明細書において、ドープシリコンシード層 310 と呼ぶ。

40

#### 【0051】

ステップ(7)において、フォトレジスト 304 の残りの部分を犠牲酸化膜層 300 から削り取る。

#### 【0052】

50

ステップ(8)において、ウェハの上面を洗浄し、その後、アニーリングによってすべての損傷を修復する。

【0053】

ステップ(9)において、犠牲酸化膜層300を除去する。

【0054】

図からわかるように、これらのステップが完了した時のドープシリコンシード層310は、n型ドーパント、この例ではヒ素が、画素アレイ領域305に略限定されている断面ドーピングプロファイルを有する。したがって、ドープシリコンシード層310は、あるイメージセンサの周辺領域にあたるドープされていない部分312と、そのイメージセンサの画素アレイ領域にあたるN+ドープ領域314を含む。この裏面ドーピングプロファイルにより、埋め込み酸化膜層204との界面における暗電流を軽減させ、その一方で、図2に関連して前述したような周辺ウェルの短絡を回避できる。10

【0055】

ステップ(10)において、シリコンエピタキシャル層320を、ドープされていない部分310とN+ドープ部314を含むドープシリコンシード層310の上に成長させる。その結果得られたイメージセンサウェハは、ドープシリコンシード層310とシリコンエピタキシャル層320を含むセンサ層330を有する。エピタキシャル層は、厚さ約1μmから20μmまで成長させてもよい。

【0056】

その後の加工作業には、たとえば、画素アレイ340の、フォトダイオードまたは他のフォトレジスト素子342を含む部分をエピタキシャル層320の中に形成するステップが含まれていてもよい。このような素子は、アライメントマーク302と直接または間接的に位置合わせした状態で形成する。20

【0057】

図には示されていないが、さらに別の加工作業をイメージセンサウェハに施して、デジタルカメラ10のイメージセンサ14を含む、複数の裏面照明イメージセンサを生産する。説明のための例として、このような別の作業は、エピタキシャル層320の表面上に少なくとも1つの誘電層を形成するステップであってもよい。この実施形態における誘電層は多層の誘電材料を含んでいてもよく、たとえば、層間誘電層(ILD)や、多層の配線層を分離する金属間誘電層(ILD)がある。相互接続、ゲートまたはその他の回路素子をはじめとする各種のイメージセンサ特徴部を、従来の方法によって誘電層の中に形成してもよい。その他の実施形態は、複数の誘電層を備えていてもよく、これらは1つまたは複数の中間層によって分離されてもよい。さらに別の加工作業で形成される誘電層および他の層はまた、アライメントマーク302と直接または間接的に位置合わせされる。30

【0058】

誘電層を形成した後に、誘電層の表面にハンドルウェハを取り付ける。ハンドルウェハは、たとえば、低温酸化膜接合(oxide-to-oxide bonding)によって取り付けてもよい。

【0059】

次に、基板202を除去し、埋め込み酸化膜層204の裏面を露出させる。基板は、たとえば、研削、研磨またはエッティング法をあらゆる組み合わせで利用して除去してもよい。通常は、基板の全体を除去し、ウェハ裏面に埋め込み酸化膜層204を露出させる。別の実施形態、たとえばエピタキシャルまたはバルク半導体ウェハを用いるものにおいて、基板は、完全に除去するのではなく、薄くしてもよい。40

【0060】

基板を除去した後、構造をCFAの上にめくり返し、関係するマイクロレンズをCFA層の中の埋め込み酸化膜層204裏面に形成する。ハンドルウェハが基板としての役割を果たし、当初の基板202を除去した後に構造を支持する。一般に、イメージセンサウェハの画素アレイの各々は対応するCFAを有し、このCFAは、センサ層330の各感光素子342の上に配置されたカラーフィルタ素子を有する。50

## 【0061】

結果として得られた加工後のイメージセンサウェハは、裏面照明用に構成された複数のイメージセンサへとダイシングされ、その1つがデジタルカメラ10のイメージセンサ14である。ウェハダイシング作業について、図4に関連して以下に詳しく説明する。本実施形態においては、ハンドルウェハをダイシングの前に除去せず、永久的なハンドルウェアとし、その一部は、ダイシングによって相互に分離された個々のイメージセンサの一部として残る。

## 【0062】

他の実施形態において、一時的なキャリアウェハをハンドルウェハの代わりに使用してもよい。一時的なキャリアウェハは、エポキシ系またはその他の適当な接着剤で付着させてもよい。一時的なキャリアウェハを取り付けた後に、基板202を前述のように除去する。CFAの各々の上を覆う透明カバーを含む透明カバーシートをイメージセンサウェハの裏面に取り付けてから、一時的なキャリアウェハを除去してもよい。このようなガラスカバーの各々は、その対応するCFAの上に配置される中央穴を有していてもよく、さらに、エポキシによって酸化膜層204の裏面に固定された周辺支持手段を有していてもよい。一時的なカバーシートは、ガラスその他の透明材料で形成してもよい。このようなカバーシートは、ウェハに1枚のシートとして取り付け、イメージセンサをウェハからダイシングする際に個別のカバーに分割してもよい。一時的なキャリアウェハと透明カバーシートの使用に関する詳細は、先に引用した米国特許出願コダック社ドケット番号第94872号に記載されている。しかしながら、理解すべき点として、このような要素とそれに関連する加工作業の使用は本発明の要求事項ではない。

10

20

30

## 【0063】

本発明の特定の実施形態で実行できるその他の作業としては、たとえば、再配線層(RDL)導体の形成、パシベーション層の形成、コンタクト配線層の形成がある。

前述のように、図3に示される加工作業は、イメージセンサウェハに適用されるウェハレベルの加工作業である。図4は、複数のイメージセンサ402を含むイメージセンサウェハ400の平面図である。イメージセンサ402は、図3に関連して説明したイメージセンサウェハ400のウェハレベルの加工を通じて形成する。このイメージセンサは、ウェハをダイシングライン404に沿ってダイシングすることにより、相互に分離する。イメージセンサ402のうちの1つが、図1のデジタルカメラ10のイメージセンサ14に対応する。

30

## 【0064】

上記の実施形態は、有利な点として、裏面照明イメージセンサを形成するための改善された加工装置を提供する。たとえば、図3の工程により生産される装置では、ドープシード層310が、周辺ウェルの短絡を発生させずに、またはエピタキシャル層320を不適切に厚くすることなく、センサ層330と埋め込み酸化膜層204との界面における暗電流を低減させるように構成される。その結果、入射光検出能力の向上という点で改善された性能を示す裏面照明イメージセンサが提供される。

## 【0065】

本発明について、特定の説明のための実施形態に関連して詳細に説明したが、当然のことながら、付属の特許請求範囲に記されている本発明の範囲内で、変更や改変を加えることができる。たとえば、本発明は、別の材料、ウェハ、層、工程ステップ等を用いて、他の種類のイメージセンサやデジタルイメージングデバイスに実装することができる。したがって、実施形態に関連して説明した層の厚さやドーパント濃度等の各種の加工パラメータは、別の実施形態では変えてよい。これらおよびその他の実施形態は、当業者にとって容易に明らかになるであろう。

40

## 【符号の説明】

## 【0066】

10 デジタルカメラ、12 イメージングステージ、14 裏面照明イメージセンサ、16 プロセッサ、18 メモリ、20 ディスプレイ、22 入力/出力(I/O)

50

要素、200 イメージセンサウェハ、202 基板、204 埋め込み酸化膜(BOX)層、204B 埋め込み酸化膜層裏面、204F 埋め込み酸化膜層表面、205 シード層、205' ドープシード層、210 エピタキシャル層、212 ウェル、300 犠牲酸化膜層、302 アライメントマーク、304 フォトレジスト、305 画素アレイ領域、310 ドープシード層、312 シード層のドープされていない部分、314 シード層のドープ部分、320 エピタキシャル層、330 センサ層、340 画素アレイ、342 感光素子、400 イメージセンサウェハ、402 イメージセンサ、404 ダイシングライン。

【図1】

【図2】

【図3】

【図4】

FIG. 4

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2009/003794 |

|---------------------------------------------------|

|                                                        |

|--------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. H01L27/146 |

|--------------------------------------------------------|

According to International Patent Classification (IPC) or to both national classification and IPC

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, INSPEC

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                     | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2007/235829 A1 (LEVINE PETER A [US] ET AL) 11 October 2007 (2007-10-11)<br>paragraphs [0020] – [0036]; figures 1A-1E, 5             | 1-20                  |

| X         | EP 1 612 863 A (SONY CORP [JP])<br>4 January 2006 (2006-01-04)<br>paragraph [0016] – paragraph [0043];<br>figures 1, 3A-3G             | 1-20                  |

| X         | US 2006/186560 A1 (SWAIN PRADYUMNA [US] ET AL) 24 August 2006 (2006-08-24)<br>paragraph [0016] – paragraph [0031];<br>figures 1A-1D, 5 | 1-20                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents:

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- \*&\* document member of the same patent family

Date of the actual completion of the international search

18 September 2009

Date of mailing of the international search report

30/09/2009

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL – 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Franchise, Vincent

**INTERNATIONAL SEARCH REPORT**

International application No

PCT/US2009/003794

**C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                      | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| P,X       | WO 2008/118525 A (SARNOFF CORP [US]; SWAIN PRADYUMNA KUMAR [US]; BHASKARAN MAHALINGAM [U] 2 October 2008 (2008-10-02)<br>page 7, line 7 - page 10, line 22; figures 1-9 | 1-20                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2009/003794

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|--|------------------|

| US 2007235829                          | A1 | 11-10-2007       | WO | 2008147421 A1           |  | 04-12-2008       |

| EP 1612863                             | A  | 04-01-2006       | CN | 1716628 A               |  | 04-01-2006       |

|                                        |    |                  | JP | 4211696 B2              |  | 21-01-2009       |

|                                        |    |                  | JP | 2006019360 A            |  | 19-01-2006       |

|                                        |    |                  | KR | 20060048661 A           |  | 18-05-2006       |

|                                        |    |                  | TW | 281252 B                |  | 11-05-2007       |

|                                        |    |                  | US | 2006006488 A1           |  | 12-01-2006       |

|                                        |    |                  | US | 2009057803 A1           |  | 05-03-2009       |

| US 2006186560                          | A1 | 24-08-2006       | JP | 2008530801 T            |  | 07-08-2008       |

|                                        |    |                  | WO | 2006086644 A2           |  | 17-08-2006       |

| WO 2008118525                          | A  | 02-10-2008       | US | 2008237668 A1           |  | 02-10-2008       |

---

**フロントページの続き**

(81) 指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,SE,SI,S,K,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,J,P,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PE,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

F ターム(参考) 4M118 AA05 AA10 AB01 BA14 CA02 EA01 EA14 EA15 FA06 GA02

GC07 GD04

5C024 AX01 CX32 CY47 GX03 GX24 GY31 HX01