(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6480248号

(P6480248)

(45) 発行日 平成31年3月6日(2019.3.6)

(24) 登録日 平成31年2月15日(2019.2.15)

|              |             |

|--------------|-------------|

| (51) Int.Cl. | F 1         |

| H03K 19/173  | (2006.01)   |

| H01L 27/10   | (2006.01)   |

| H01L 21/8242 | (2006.01)   |

| H01L 27/108  | (2006.01)   |

| H01L 29/786  | (2006.01)   |

| HO3K 19/173  | HO3K 19/173 |

| H01L 27/10   | H01L 27/10  |

| H01L 21/8242 | H01L 27/108 |

| H01L 27/108  | H01L 29/78  |

| H01L 29/786  | (2006.01)   |

請求項の数 6 (全 28 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2015-88946 (P2015-88946)   |

| (22) 出願日     | 平成27年4月24日 (2015.4.24)       |

| (65) 公開番号    | 特開2016-54475 (P2016-54475A)  |

| (43) 公開日     | 平成28年4月14日 (2016.4.14)       |

| 審査請求日        | 平成30年4月11日 (2018.4.11)       |

| (31) 優先権主張番号 | 特願2014-91701 (P2014-91701)   |

| (32) 優先日     | 平成26年4月25日 (2014.4.25)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

| (31) 優先権主張番号 | 特願2014-180766 (P2014-180766) |

| (32) 優先日     | 平成26年9月5日 (2014.9.5)         |

| (33) 優先権主張国  | 日本国 (JP)                     |

|                     |           |

|---------------------|-----------|

| (73) 特許権者           | 000153878 |

| 株式会社半導体エネルギー研究所     |           |

| 神奈川県厚木市長谷398番地      |           |

| (72) 発明者            | ビヨクルン ノラ  |

| 神奈川県厚木市長谷398番地 株式会社 |           |

| 半導体エネルギー研究所内        |           |

| (72) 発明者            | 青木 健      |

| 神奈川県厚木市長谷398番地 株式会社 |           |

| 半導体エネルギー研究所内        |           |

| (72) 発明者            | 黒川 義元     |

| 神奈川県厚木市長谷398番地 株式会社 |           |

| 半導体エネルギー研究所内        |           |

審査官 白井 亮

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のロジックブロックと、第2のロジックブロックと、プログラマブルスイッチと、を有し、

前記第1のロジックブロックは、前記第2のロジックブロックと、前記プログラマブルスイッチによって接続可能であり、

前記プログラマブルスイッチは、パストランジスタと、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、を有し、

前記第1のトランジスタ、前記パストランジスタ、及び前記第2のトランジスタは、この順に直列に接続され、

前記第1のトランジスタと前記第2のトランジスタの双方のソースとドレインとは、回路図において、前記第1のロジックブロックと前記第2のロジックブロックとの間に設けられ、

前記第1のトランジスタと前記第2のトランジスタとの双方がオフ状態であるときに、前記第3のトランジスタを介して前記パストランジスタのソースとドレインの一方にローレベル電位が供給されることを特徴とする半導体装置。

## 【請求項 2】

さらに、書き込みトランジスタと、ピット線と、を有し、

前記書き込みトランジスタのソースとドレインとは、回路図において、前記ピット線と前記パストランジスタのゲートの間に設けられることを特徴とする請求項1記載の半導体

装置。

【請求項 3】

前記書き込みトランジスタが、活性層として酸化物半導体膜を有することを特徴とする請求項 2 記載の半導体装置。

【請求項 4】

さらに、ワード線を有し、

前記書き込みトランジスタは、前記ワード線の信号により制御されることを特徴とする請求項 2 または 3 記載の半導体装置。

【請求項 5】

前記書き込みトランジスタがオフ状態であるとき、前記パストランジスタのゲートが実質的に電気的に分離されることを特徴とする請求項 2 乃至 4 のいずれか一項に記載の半導体装置。 10

【請求項 6】

前記書き込みトランジスタがオフ状態であるとき、前記パストランジスタのゲートが浮遊状態となることを特徴とする請求項 2 乃至 4 のいずれか一項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

この開示物は半導体装置に関する。

【背景技術】

【0002】

フィールドプログラマブルゲートアレイ (FPGA) のルーティングスイッチは 2 つのロジックブロック (LB) 間、あるいは、LB と出入力回路間の接続を決定するスイッチとして作用する。ルーティングスイッチはバスゲート (パストランジスタ) に接続するコンフィギュレーションメモリに接続の情報を保持する。

【0003】

最近、酸化物半導体をトランジスタのチャネルに使用する FPGA が提案されている（特許文献 1 および 2）。酸化物半導体ベースの FPGA は消費電力を低減し、微細化で有利である。さらに、1 より多い設定を有するマルチコンテキスト FPGA も提案されている（非特許文献 1）。 30

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】米国特許第 8,547,753 号明細書

【特許文献 2】米国特許第 8,675,382 号明細書

【非特許文献】

【0005】

【非特許文献 1】Y. Okamoto et al. "Novel application of crystalline indium-gallium-zinc-oxide technology to LSI: Dynamically reconfigurable programmable logic device based on multi-context architecture.", In 2013 International Conference on Semiconductor Technology for Ultra Large Scale Integrated Circuits and Thin Film Transistors (ULSIC vs. TFT 4). 40

【発明の概要】

【発明が解決しようとする課題】

【0006】

この開示物では、半導体装置に関する新規な回路、アーキテクチャー、駆動方法、装置の 50

いずれかが提供される。

**【課題を解決するための手段】**

**【0007】**

例えば、第1のロジックブロック、第2のロジックブロックとプログラム可能なスイッチ（プログラマブルスイッチ）とを有する半導体装置が提供される。第1のロジックブロックと第2のロジックブロックはプログラマブルスイッチにより接続可能であり、プログラマブルスイッチは、パストランジスタ、第1のトランジスタ、第2のトランジスタ、第3のトランジスタを有し、第1のトランジスタ、パストランジスタ、第2のトランジスタはこの順に直列に接続され、回路図において、第1のトランジスタと第2のトランジスタのソースとドレインは第1のロジックブロックと第2のロジックブロックの間に位置し、半導体装置は、第1のトランジスタと第2のトランジスタがともにオフ状態のときに、パストランジスタのソースとドレインの一方に、第3のトランジスタを介して、ある電位が供給されるように設計されている。10

**【0008】**

例えば、2つのロジックブロックと、パストランジスタと2つの選択トランジスタとプリチャージトランジスタを有する半導体装置が提供される。2つの選択トランジスタはパストランジスタを挟むように配置され、パストランジスタは2つの選択トランジスタのソースの間に位置する。2つの選択トランジスタのソースとドレインは2つのロジックブロック間に位置する。2つの選択トランジスタがオフ状態であるとき、パストランジスタのソースあるいはドレインに、オン状態であるプリチャージトランジスタを経由してある電位が与えられ、さらに、電気的導通によって、あるコンテキストのための他の電位が、パストランジスタのゲートに与えられる。コンテキストを実行するとき、パストランジスタのゲートは実質的に電気的に分離されていて（浮遊状態で）、2つの選択トランジスタはオン状態で、プリチャージトランジスタはオフ状態である。20

**【発明の効果】**

**【0009】**

上記半導体装置は新規であり、消費電力を低減すること、処理速度を向上すること、安定性、信頼性あるいは以下に記載されることのいずれかを得ることの一つ以上に対して優位性を有する。

**【図面の簡単な説明】**

**【0010】**

【図1】マルチコンテキストFPGAを説明する例を示す。

【図2】パストランジスタの動作を説明する例を示す。

【図3】パストランジスタの動作を説明する例を示す。

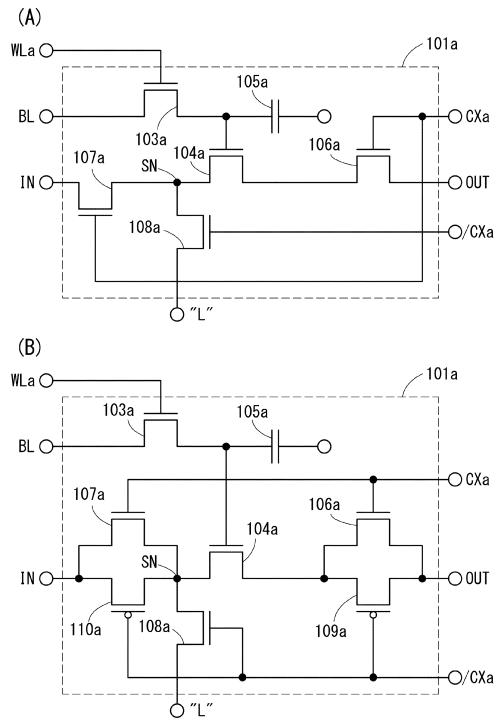

【図4】プログラマブルスイッチの例を示す。

【図5】プログラマブルスイッチの例を示す。

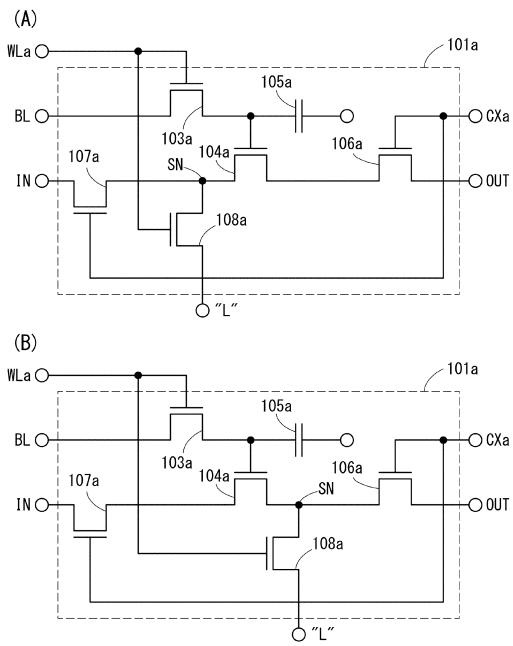

【図6】プログラマブルスイッチの例を示す。

【図7】プログラマブルスイッチの例を示す。

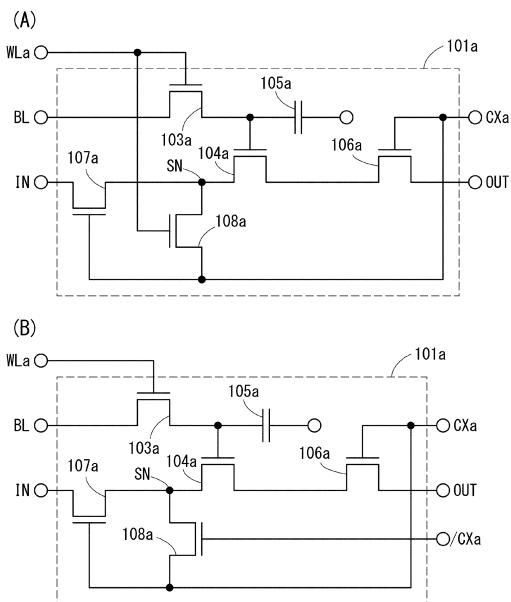

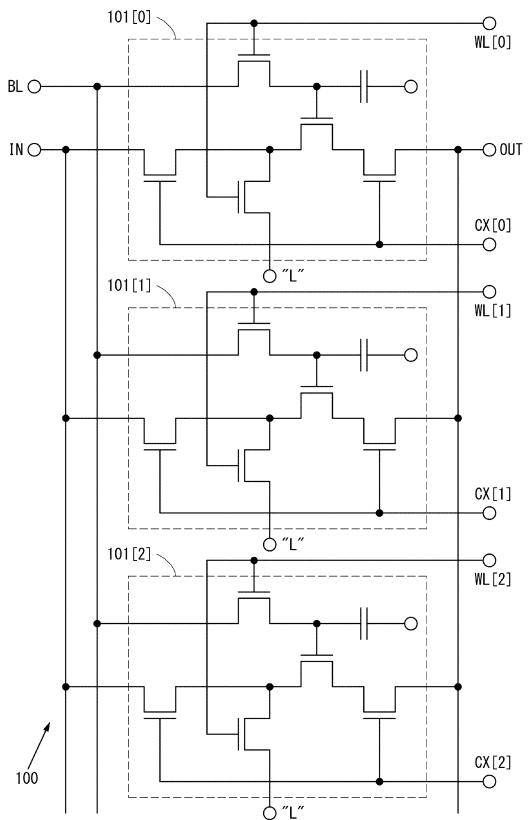

【図8】ルーティングスイッチの例を示す。

【図9】ルーティングスイッチの例を示す。

【図10】ルーティングスイッチの例を示す。

【図11】プログラマブルスイッチの動作を説明する例を示す。

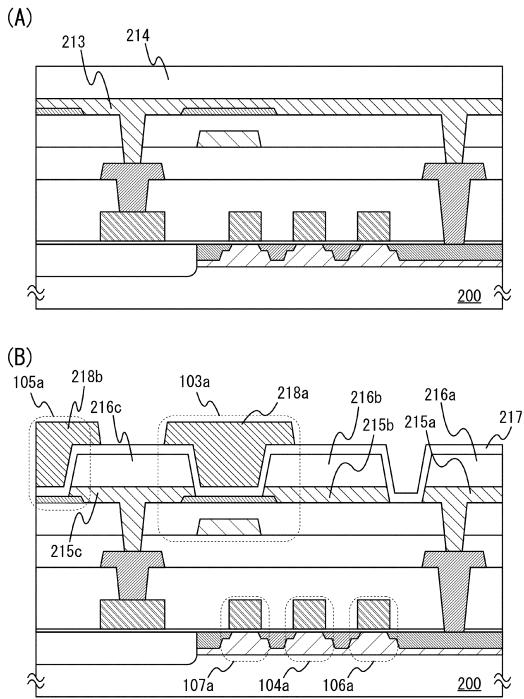

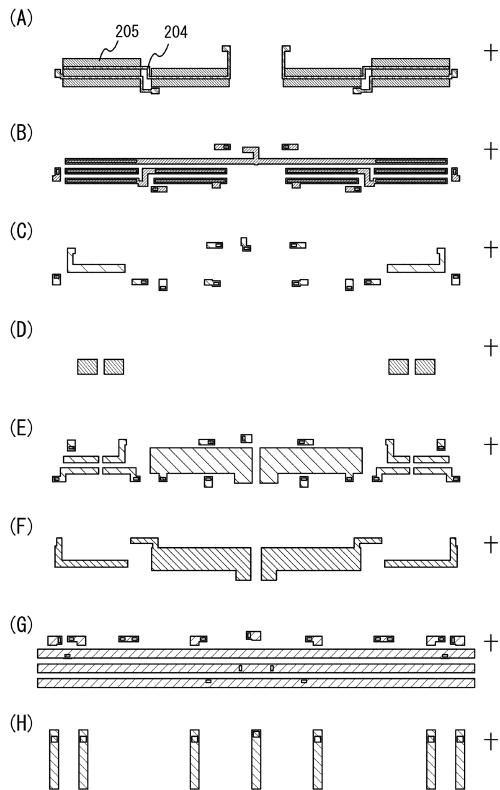

【図12】半導体装置の作製工程の断面図の例を示す。

【図13】半導体装置の作製工程の断面図の例を示す。

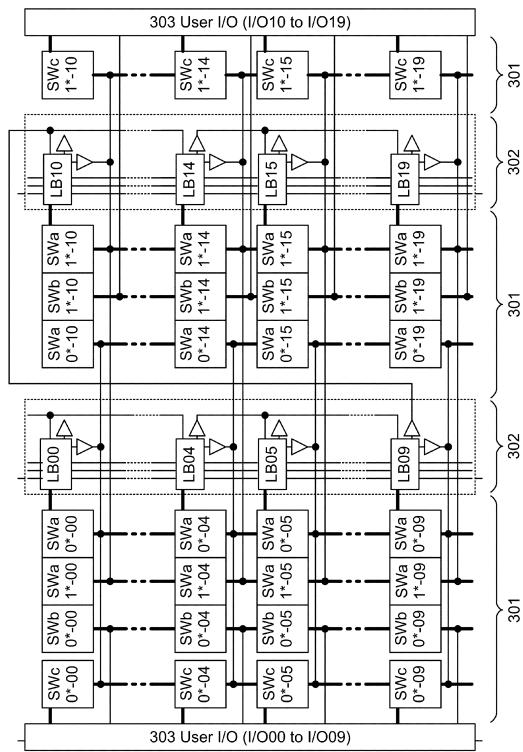

【図14】FPGAの例を示す。

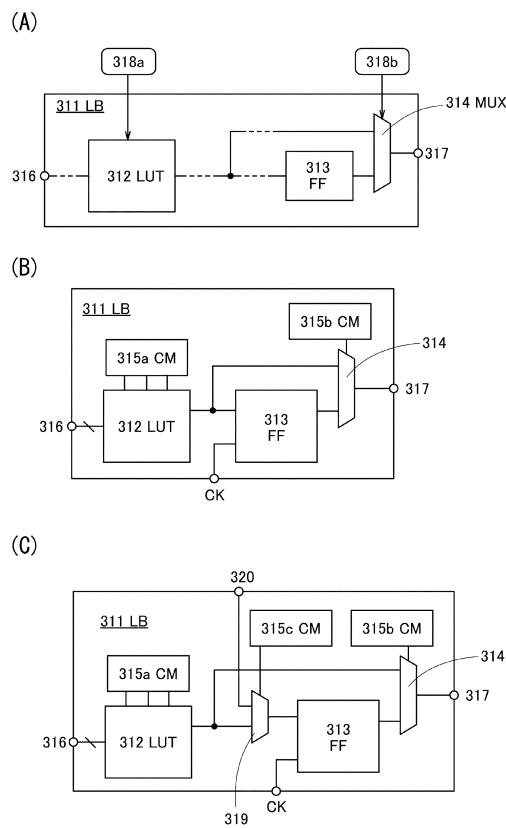

【図15】ロジックブロックの例を示す。

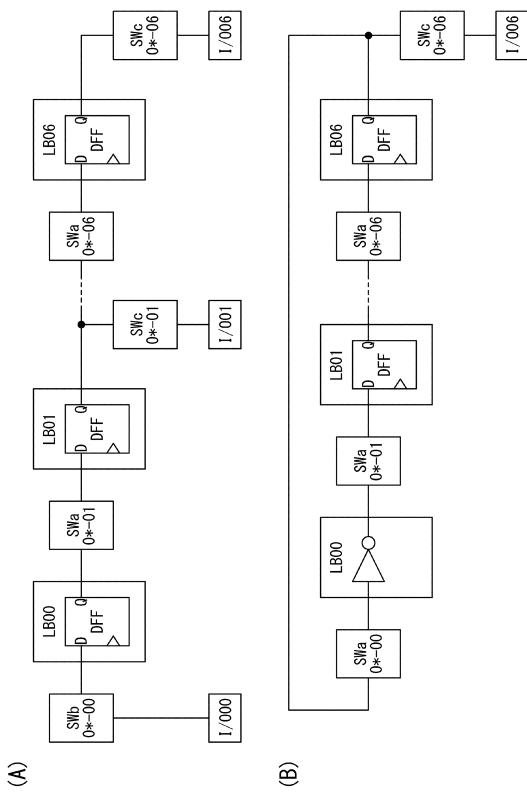

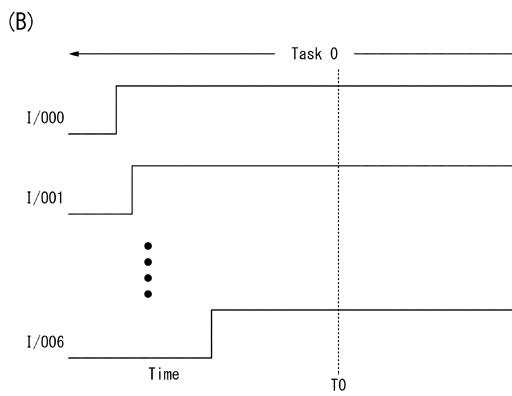

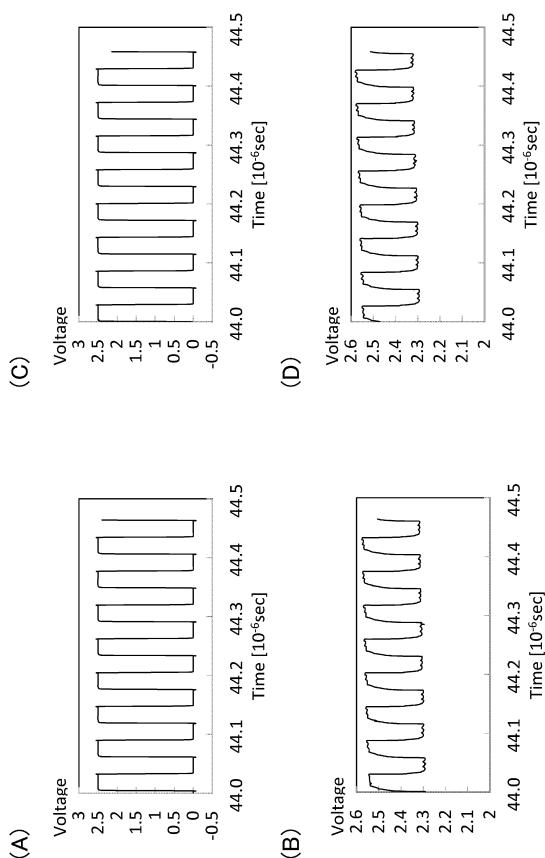

【図16】実施例で設定された回路、(A)シフタ回路、と(B)リングオシレータを示す。

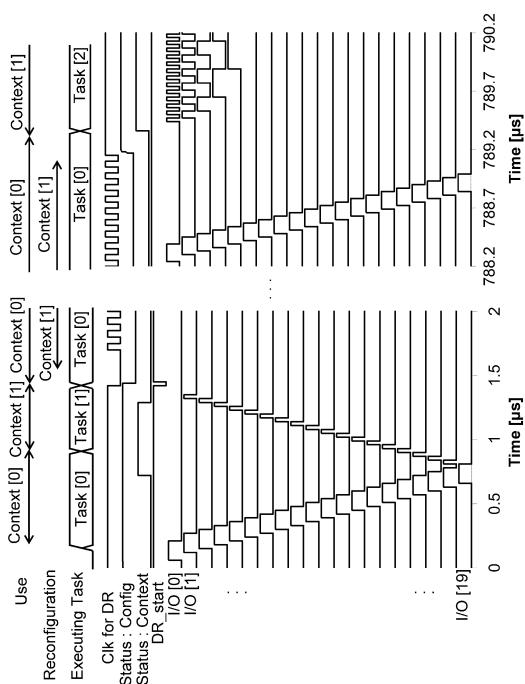

【図17】実施例の入出力回路の電位の概略を示す。

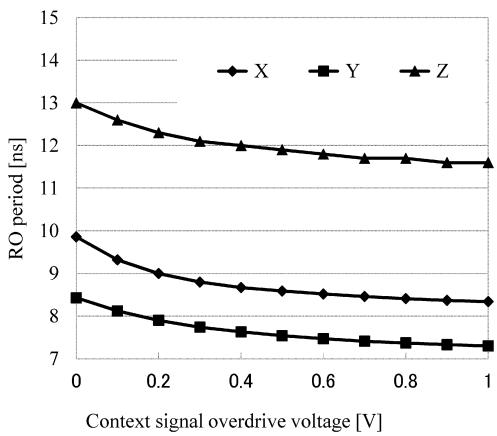

【図18】実施例のリングオシレータのシミュレーションされた特性を示す。50

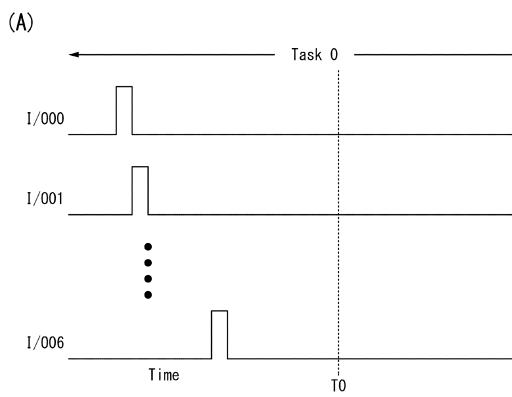

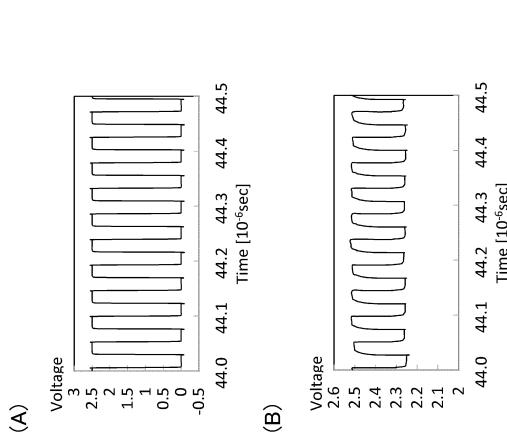

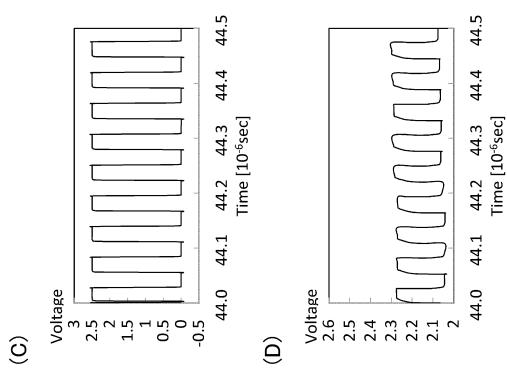

【図19】実施例のリングオシレータのシミュレーションされた特性を示す。

【図20】実施例のリングオシレータのシミュレーションされた特性を示す。

【図21】実施例の半導体装置の配線、半導体膜、コンタクトホールのレイアウトを示す。

【図22】実施例の半導体装置のシミュレーションされた特性を示す。

【図23】実施例の半導体装置のシミュレーションされた特性を示す。

**【発明を実施するための形態】**

**【0011】**

以下、図面を参照して実施の形態が記述される。しかしながら、実施の形態は多くの異なる様様で実施することができる。精神および範囲から逸脱することなく形態と詳細を様々に変更することは当業者には容易に理解されよう。

10

**【0012】**

(実施の形態1)

図1(A)はマルチコンテキストFPGAの一部のブロック図を示す。マルチコンテキストFPGAは、ルーティングスイッチ100、ロジックブロック102a、ロジックブロック102bを有する。ロジックブロック102a、ロジックブロック102bは、ルーティングスイッチ100を介して接続可能である。

20

**【0013】**

例えば、ルーティングスイッチ100がオン状態のとき、ロジックブロック102aの出力信号は、ロジックブロック102bに入力され、また、ルーティングスイッチ100がオフ状態のとき、ロジックブロック102aとロジックブロック102bは電気的に分離される。ここで、ルーティングスイッチ100とロジックブロック102aの間のノードを「IN」、ルーティングスイッチ100とロジックブロック102bの間のノードを「OUT」と呼ぶ。

20

**【0014】**

ルーティングスイッチ100は2以上のプログラマブルスイッチを有する。例えば、ルーティングスイッチ100は、プログラマブルスイッチ101a、プログラマブルスイッチ101b、プログラマブルスイッチ101cを有し、それぞれ、独立にコンフィギュレーションデータを有する。コンフィギュレーションデータは、ビット線BLより、それぞれのプログラマブルスイッチに供給される。なお、コンフィギュレーションデータを書き込むことやプログラマブルスイッチを選択すること等のために他の配線が追加されてもよい。

30

**【0015】**

図1(B)はプログラマブルスイッチを有するルーティングスイッチ100の例を示す。例えば、プログラマブルスイッチ101aは、書き込みトランジスタ103a、パストランジスタ104a、容量素子105a、選択トランジスタ106aを有する。

**【0016】**

本実施の形態では、書き込みトランジスタ103a、パストランジスタ104a、選択トランジスタ106aはn型である。しかし、それらのいくつか、あるいは全てがp型であつてもよい。

40

**【0017】**

容量素子105aの一方の電極は、パストランジスタ104aのゲートに接続していてよい。あるいは、書き込みトランジスタ103aのソースとドレインは、容量素子105aの一方の電極とビット線BLの間に設けられてもよい。

**【0018】**

さらに、書き込みトランジスタ103a、パストランジスタ104a、選択トランジスタ106aは、トランスマッショングートのような他のスイッチングエレメントでもよい。トランスマッショングートを用いれば、信号電位の低下がないので、速度、消費電力を低減する点、駆動電圧を下げる点で有利である。

**【0019】**

50

同様に、プログラマブルスイッチ 101b、プログラマブルスイッチ 101c は、それぞれ、書き込みトランジスタ 103b、パストランジスタ 104b、容量素子 105b、選択トランジスタ 106b と、書き込みトランジスタ 103c、パストランジスタ 104c、容量素子 105c、選択トランジスタ 106c を有する。

#### 【0020】

書き込みトランジスタ 103a、書き込みトランジスタ 103b、書き込みトランジスタ 103c は、それぞれ、ワード線 WL a、ワード線 WL b、ワード線 WL c によって制御される。プログラマブルスイッチ 101a へのコンフィギュレーションデータの書き込みは、書き込みトランジスタ 103a がオン状態のときにおこなわれる。パストランジスタ 104a のゲート（メモリノード MN）の電位は、書き込みトランジスタ 103a がオン状態のとき、コンフィギュレーションデータ（あるいはビット線 BL の電位）に応じたものとなる。10

#### 【0021】

メモリノード MN は、実質的に、かつ、電気的に、書き込みトランジスタ 103a を介してのみ、他の配線と接続可能であることに注意が必要である。したがって、書き込みトランジスタ 103a がオフ状態のときには、メモリノード MN は電気的に分離される。もちろん、2 以上のトランジスタのソース電極やドレイン電極がメモリノード MN に接続されてもよい。その場合には、全てのトランジスタがオフ状態のときに、メモリノード MN は電気的に分離される。

#### 【0022】

一例では、十分な期間、メモリノード MN に電荷を保持するためには、書き込みトランジスタ 103a がオフ状態のときのソースドレイン電流は、 $1 \text{ zA}$  ( $1 \times 10^{-21} \text{ A}$ ) 未満である。メモリノード MN が十分な電荷を保持できる期間はオフ状態のソースドレイン電流（オフ状態電流）と、メモリノード MN の容量に依存する。他の経路（例えば、ゲートとメモリノード MN 間（いわゆるゲートリーク））を介するメモリノードからのリークも  $1 \text{ zA}$  未満とするとよい。20

#### 【0023】

特許文献 1、2 および非特許文献 1 に記載されているように、酸化物半導体系トランジスタはこの目的には理想的であり、メモリノード MN は実質的に不揮発メモリの一部として機能する。30

#### 【0024】

酸化物半導体系トランジスタは、酸化物半導体薄膜を活性層として有するので、2 つのゲートが間に酸化物半導体膜を挟んで互いに向かいあうように設けられてもよい。

#### 【0025】

一例では、酸化物半導体系トランジスタは酸化物半導体膜の一表面に向かう一つのゲート電極を有する。他の例では、酸化物半導体系トランジスタは、そのようなゲート電極に加えて、酸化物半導体膜の他の表面に向かう他のゲート電極を有する。

#### 【0026】

パストランジスタ 104a の状態（オンあるいはオフ）は、主として、メモリノード MN の電位に依存する。例えば、メモリノード MN とパストランジスタ 104a 間の電位差が、パストランジスタ 104a のしきい値より大きければ、パストランジスタ 104a はオン状態である。40

#### 【0027】

選択トランジスタ 106a は、コンテキストを選択するための信号（コンテキスト信号）が伝送するコンテキスト線 CXa によって制御される。ノード IN とノード OUT が接続されるには（あるいは、選択トランジスタ 106a とパストランジスタ 104a を通って、ノード IN からノード OUT に信号が通るには）、選択トランジスタ 106a とパストランジスタ 104a の双方がオン状態であることが必要である。同様に、選択トランジスタ 106b、選択トランジスタ 106c は、それぞれ、コンテキスト線 CXb、コンテキスト線 CXc によって制御される。50

**【0028】**

図1(B)に示されるように、選択トランジスタ106a、選択トランジスタ106b、選択トランジスタ106cは、独立して制御できるので、それらのいずれかを選択することにより、選択されたプログラマブルスイッチに格納されていたコンテキストが実行できる。例えば、選択トランジスタ106bを選択することにより、プログラマブルスイッチ101bに格納されていたコンテキストが実行可能となる。

**【0029】**

上記の例では、ルーティングスイッチ100には3つのプログラマブルスイッチがあるので、最大3つのコンテキストが実行可能である。しかし、さらにプログラマブルスイッチを追加することで、より多くのコンテキストが実行可能である。あるいは、ルーティングスイッチ100にはプログラマブルスイッチが2以下しかなくてもよい。

10

**【0030】**

書き込みトランジスタ103a、書き込みトランジスタ103b、書き込みトランジスタ103cは独立して制御できるので、コンフィギュレーションデータは、プログラマブルスイッチ101a、プログラマブルスイッチ101b、プログラマブルスイッチ101cに独立して書き込む。

**【0031】**

さらに、プログラマブルスイッチ101bが使用中であっても、(使用中でない)プログラマブルスイッチ101aにコンフィギュレーションデータを書き込むこともできる。この操作はダイナミック・リコンフィギュレーション(動的再構成)と呼ばれる。例えば、プログラマブルスイッチ101bに格納されている第1のコンテキストに基づいて第1のタスクが実行されているときに、プログラマブルスイッチ101aに新しいコンフィギュレーションデータが書き込む。

20

**【0032】**

パストランジスタ104aのソース電極(あるいはドレイン電極)の電位は、コンフィギュレーションデータを書き込むときに重要な役割を果たす。図2と図3でその理由を説明する。

**【0033】**

図2(A)は、コンフィギュレーションデータ「H」(ハイレベル電位、例えば、0.8V)がプログラマブルスイッチに書き込まれるのを示す。ここで、ビット線BLの電位は「H」であり、したがって、メモリノードMNの電位は(実質的に)「H」となる。一方で、ノードINの電位は、パストランジスタ104aのしきい値以上だけ、ビット線BLの電位より低い「L」(ローレベル電位、例えば、0V)となるように設定されている。したがって、パストランジスタ104aはオン状態であり、メモリノードMNは、パストランジスタ104aのチャネルを介して、ノードIN(そしてソースノードSN)と容量的に結合する。

30

**【0034】**

書き込みトランジスタ103aがオフになった後、ノードINの電位が、「L」から「H」に上がると、メモリノードMNの電位は、容量結合により「H + V」に上昇する(図2(B))。これはブースティング効果と呼ばれる。VがVth(パストランジスタ104aのしきい値)より大きければ、ノードOUTの電位は「L」から「H」となる。VがVth(パストランジスタ104aのしきい値)より小さければ、ノードOUTの電位は「H」に届かないかもしれない。しかしながら、パストランジスタ104aのオン抵抗が低下するので、パストランジスタ104aによる信号遅延は減少する。

40

**【0035】**

ノードINの電位が「L」に低下すると、メモリノードMNの電位は容量結合により、「H」に戻る(図2(C))。

**【0036】**

図3(A)も、コンフィギュレーションデータ「H」がプログラマブルスイッチに書き込まれるのを示すが、ノードINの電位が「H」に設定された条件でのものである。ここで

50

、ノードOUTの電位は、「H - V<sub>t h</sub>」であるが、パストランジスタ104aはオン状態のままであると仮定する。したがって、メモリノードMNは、パストランジスタ104aのチャネルを介して、ノードIN(そしてソースノードSN)と容量的に結合する。

#### 【0037】

書き込みトランジスタ103aがオフになった後、ノードINの電位が、「H」から「L」に下がると、メモリノードMNのポテンシャルは、容量結合により「H - V」あるいは「H - V<sub>t h</sub>」のいずれか高いほうに低下する(図3(B))。これは逆ブースティング効果と呼ばれる。上述のように、ノードOUTの電位が「H - V<sub>t h</sub>」であったとすると、その電位が「L」に低下するには、ゲート電位が低いために、パストランジスタ104aのオン抵抗が高くなり、より多くの時間がかかる。

10

#### 【0038】

ノードINの電位が「H」に上昇すると、メモリノードMNの電位は容量結合により、「H」に戻る、しかし、ノードOUTの電位は「H - V<sub>t h</sub>」を超えることはない(図3(C))。

#### 【0039】

図3(B)および図3(C)に示されるように、コンフィギュレーションデータを書き込む際に、ソースノードSNの電位を「H」にすることは問題となることがある。結論として、コンフィギュレーションデータを書き込む際に、ソースノードSNの電位は、メモリノードMNで可能な最高電位より、V<sub>t h</sub>を超えるだけ低いことが望ましい。例えば、コンフィギュレーションデータを書き込む際に、ノードINの電位は、「L」に設定される。

20

#### 【0040】

図1(B)に示される回路では、ロジックブロック102aの出力に応じて、ソースノードSNは「H」あるいは「L」となる。したがって、プログラマブルスイッチ101aのパフォーマンスはロジックブロック102aの出力とコンフィギュレーションのタイミングに依存する。すなわち、コンフィギュレーションデータの書き込みのときロジックブロック102aの出力が「L」であれば、図2に示すようにブースティング効果により優れたパフォーマンスを示すが、そうでなければ、図3に示すように逆ブースティング効果により不十分なパフォーマンスとなる。このように、プログラマブルスイッチ(およびFGA)は、不安定であり、うまく動作しない。

30

#### 【0041】

また、回路の動作は、もっとも遅い信号を元におこなうため、条件によって信号が早くなったり遅くなったりする場合には、遅くなった場合を基準にクロック等が設定される。つまり、図2のように動作が速い場合と、図3のように動作が遅い場合があれば、クロックは図3の場合を想定して設定される。結果、回路動作は遅くなる。

#### 【0042】

図1(B)に示されるプログラマブルスイッチでは、ソースノードSNは無防備であり、その電位は、実質的にノードINの電位と同じである。したがって、逆ブースティング効果は不可避である。図4(A)に示される回路はそのような困難を克服する。

40

#### 【0043】

図4(A)に示されるプログラマブルスイッチ101aは、図1(B)に示されるプログラマブルスイッチと同様、書き込みトランジスタ103a、パストランジスタ104a、容量素子105a、選択トランジスタ106aを有する。加えて、図4(A)に示されるプログラマブルスイッチ101aは、選択トランジスタ107aとプリチャージトランジスタ108aを有する。

#### 【0044】

選択トランジスタ107a、パストランジスタ104a、選択トランジスタ106aは、この順に、ノードINとノードOUTの間に直列に接続される。選択トランジスタ106aと選択トランジスタ107aは、それぞれ、コンテキスト線CXa、コンテキスト線CYaによって制御される。選択トランジスタ106aと選択トランジスタ107aをオフ

50

とすることで、パストランジスタ 104a のソースとドレインはノード IN とノード OUT から電気的に分離される。

#### 【0045】

プリチャージトランジスタ 108a のソースとドレインの一方はパストランジスタ 104a のソースとドレインの一方に接続される。この例では、プリチャージトランジスタ 108a のソースとドレインの他方にある電位が供給される。その電位は、例えば、「L」であるが、メモリノード MN で可能なもっとも高い電位より少なくとも Vth だけ低いもの（例えば、「H - Vth」より低いもの）であれば利用できる。一例では、電位は、「L - Vth」より高くてよい。

#### 【0046】

なお、プリチャージトランジスタ 108a がオフ状態のときは、プリチャージトランジスタ 108a のソースとドレインの他方の電位は「H」でも、その他の電位でもよい。したがって、プリチャージトランジスタ 108a のソースとドレインの他方の電位は一定であっても、変動していてもよい。なお、例えば、容量素子 105a の他方の電極の電位を用いてもよい。

#### 【0047】

プリチャージトランジスタ 108a はプリチャージ線 PCa によって制御され、選択トランジスタ 106a と選択トランジスタ 107a をオフとし、プリチャージトランジスタ 108a をオンとすることで、例えば、ソースノード SN の電位は「L」とできる。

#### 【0048】

上記のとおり、ダイナミックリコンフィギュレーションでは、プログラマブルスイッチへのコンフィギュレーションデータの書き込みは、そのプログラマブルスイッチに格納されているコンテキストが実行されていないときにおこなわれる。したがって、プログラマブルスイッチへコンフィギュレーションデータを書き込むとき、選択トランジスタ 106a と選択トランジスタ 107a はオフ状態にできる。

#### 【0049】

一例では、プリチャージトランジスタ 108a は、選択トランジスタ 106a と選択トランジスタ 107a 双方がオフ状態である全てあるいは一部の期間において、オン状態とできる。一例では、プリチャージトランジスタ 108a は、書き込みトランジスタ 103a がオフとされたとき、あるいは、その前においてオン状態である。

#### 【0050】

選択トランジスタ 106a と選択トランジスタ 107a を互いに同期してオンあるいはオフにしてもよい。図 4 (B) に示されるプログラマブルスイッチ 101a では、選択トランジスタ 106a と選択トランジスタ 107a 双方は、単一のコンテキスト線 CXa によって制御される。

#### 【0051】

上記のように、プリチャージトランジスタ 108a は、選択トランジスタ 106a と選択トランジスタ 107a 双方がオフ状態であるときにオン状態となる。したがって、プリチャージトランジスタ 108a を、選択トランジスタ 106a と選択トランジスタ 107a と逆にオンあるいはオフとすることもできる。図 5 (A) に示されるプログラマブルスイッチ 101a では、プリチャージトランジスタ 108a は、反コンテキスト信号（コンテキスト信号の反転信号）を伝送する反コンテキスト線 / CXa によって制御される。

#### 【0052】

プログラマブルスイッチ 101a が、図 5 (B) に示されるようなトランスミッショングートを有していれば、反コンテキスト線と反コンテキスト信号は、p 型トランジスタ（選択トランジスタ 109a と選択トランジスタ 110a）を制御することに使用できる。

#### 【0053】

図 6 (A) はプログラマブルスイッチ 101a の別の例を示す。この例では、プリチャージトランジスタ 108a は、書き込みトランジスタ 103a と同様にワード線 WLa によって制御される。すなわち、プリチャージトランジスタ 108a を、書き込みトランジス

10

20

30

40

50

タ 1 0 3 a と同期させて、オンあるいはオフとする。

**【 0 0 5 4 】**

図 6 ( B ) はプログラマブルスイッチ 1 0 1 a の別の例を示す。この例では、図 6 ( A ) に示されたプログラマブルスイッチ 1 0 1 a を改変して、ソースノード S N がパストランジスタ 1 0 4 a と選択トランジスタ 1 0 6 a の間に設けられる。このような改変は、図 4 および図 5 に示されるプログラマブルスイッチにおいても適用できる。

**【 0 0 5 5 】**

図 7 ( A ) はプログラマブルスイッチ 1 0 1 a の別の例を示す。この例では、図 6 ( A ) に示されたプログラマブルスイッチ 1 0 1 a が改変されて、プリチャージトランジスタ 1 0 8 a がソースノード S N とコンテキスト線 C X a の間に設けられる。

10

**【 0 0 5 6 】**

選択トランジスタ 1 0 6 a と選択トランジスタ 1 0 7 a をオンとするために、コンテキスト線 C X a の電位が上昇するとき、プリチャージトランジスタ 1 0 8 a は、書き込みトランジスタ 1 0 3 a と同様に、オフ状態である。選択トランジスタ 1 0 6 a と選択トランジスタ 1 0 7 a をオフとするために、コンテキスト線 C X a の電位が低下している間に、プリチャージトランジスタ 1 0 8 a と書き込みトランジスタ 1 0 3 a がオンになると、ソースノード S N は、その低下した電位（例えば、「L」）でプリチャージされる。

**【 0 0 5 7 】**

このような改変は、図 4 および図 5 に示されるプログラマブルスイッチにおいても適用できる。図 7 ( B ) は図 5 ( A ) のプログラマブルスイッチ 1 0 1 a をもとにしたものである。

20

**【 0 0 5 8 】**

図 8 は、複数のプログラマブルスイッチ 1 0 1 ( プログラマブルスイッチ 1 0 1 [ 0 ] 、プログラマブルスイッチ 1 0 1 [ 1 ] 、プログラマブルスイッチ 1 0 1 [ 2 ] 、 · · ) を有するルーティングスイッチ 1 0 0 の例である。個々のプログラマブルスイッチ 1 0 1 は図 6 ( A ) に示される回路構成を有する。この例では、ルーティングスイッチ 1 0 0 は、ビット線 B L 、ワード線 W L [ 0 ] 、ワード線 W L [ 1 ] 、ワード線 W L [ 2 ] 、 · · 、コンテキスト線 C X [ 0 ] 、コンテキスト線 C X [ 1 ] 、コンテキスト線 C X [ 2 ] 、 · · によって制御される。ノード IN とノード OUT の接続は、選択されたコンテキストによって決定される。

30

**【 0 0 5 9 】**

図 9 はルーティングスイッチ 1 0 0 の例である。図 9 のルーティングスイッチ 1 0 0 は、図 8 のものに似ているが、プログラマブルスイッチ 1 0 1 [ 0 ] のソースノードにプリチャージトランジスタを介してワード線 W L [ 1 ] の電位が供給される点で異なる。

**【 0 0 6 0 】**

プログラマブルスイッチ 1 0 1 [ 0 ] の書き込みトランジスタとプリチャージトランジスタがオン状態のとき、ワード線 W L [ 1 ] の電位は「L」である（あるいはそれより低い）。したがって、プログラマブルスイッチ 1 0 1 [ 0 ] のソースノードの電位は「L」となる（あるいはそれより低くなる）。

**【 0 0 6 1 】**

40

この構造は、書き込みトランジスタとプリチャージトランジスタが同じ構造である場合、特に、書き込みトランジスタとプリチャージトランジスタが同じ層の配線や膜を使用する場合に有利である。

**【 0 0 6 2 】**

図 1 0 はルーティングスイッチ 1 0 0 の例である。図 1 0 のルーティングスイッチ 1 0 0 は、図 8 のものに似ているが、プログラマブルスイッチ 1 0 1 [ 0 ] のプリチャージトランジスタがコンテキスト線 C X [ 1 ] によって制御される点で異なる。したがって、プログラマブルスイッチ 1 0 1 [ 0 ] のプリチャージトランジスタは、プログラマブルスイッチ 1 0 1 [ 1 ] のコンテキストが実行されている間のみオン状態となる。

**【 0 0 6 3 】**

50

プログラマブルスイッチ 101[1] のコンテキストが実行されるとき、プログラマブルスイッチ 101[0] の選択トランジスタはオフ状態であり、プログラマブルスイッチ 101[0] のプリチャージトランジスタはオン状態である。したがって、この期間がプログラマブルスイッチ 101[0] にコンフィギュレーションデータを書き込むのに利用できる。ルーティングスイッチ 100 がプログラマブルスイッチ 101 を多く有するほどこの構造は有利となる。

#### 【0064】

図 11(A) は図 4(B) に示されたプログラマブルスイッチ 101a の駆動方法を説明する例である。この例では、メモリノード MN の電位は、当初、「L」に設定されていると仮定する。さらに、この例では、ノード IN の電位は、周期的に上昇下降する。

10

#### 【0065】

T1において、選択トランジスタ 106a と選択トランジスタ 107a がオフとなる。T8において、選択トランジスタ 106a と選択トランジスタ 107a がオンとなる。したがって、バストランジスタ 104a のソースとドレインは、T1からT8の間は、ノード IN とノード OUT から電気的に分離される。したがって、この期間はコンフィギュレーションデータを書き込むのに使用できる。

#### 【0066】

なお、T1からT8の期間は、他のプログラマブルスイッチが使用されていて、他のコンテキスト(タスク)が実行されている。

20

#### 【0067】

T3において、書き込みトランジスタ 103a がオンとなる。T5において、書き込みトランジスタ 103a がオフとなる。T3からT5の操作によって、コンフィギュレーションデータの書き込みが完了する。この例では、ビット線 BL の電位は T4 から T6 の間、「H」である。したがって、メモリノード MN の電位は T4 において「H」となる。

#### 【0068】

T5においてワード線 WL a の電位が低下する際、メモリノード MN の電位は、書き込みトランジスタ 103a (およびワード線 WL a) とメモリノード MN との間に有る容量(主として寄生容量)によって生じる容量結合により、若干低下することがある。

#### 【0069】

T5の後、メモリノード MN は、全ての配線から電気的に分離される。この状態を(電気的に)浮遊であるという。しかしながら、メモリノード MN は、配線や導体によって容量的に影響を受ける。

30

#### 【0070】

一方、プリチャージ線 PC a の電位は、T2 に上昇し、T7 に下降する。したがって、プリチャージトランジスタ 108a は、T2 にオンとなり、T7 にオフとなる。結果、ソースノード SN の電位は、書き込みトランジスタ 103a がオフとなる前に「L」に設定される。

#### 【0071】

T8の後、ソースノード SN のポテンシャルは、選択トランジスタ 107a がオン状態なので、周期的に上昇下降する。さらに、メモリノード MN の電位も、ブースティング効果により、ソースノード SN の電位に同期して変化する。

40

#### 【0072】

図 11(A) には示されていないが、もし、メモリノード MN の最高電位が「H + Vth」より高ければ、ノード OUT の電位は、ノード IN の電位と同じ高さとなる。

#### 【0073】

図 11(B) は別の例を示す。この例でも、T11 から T18 の期間が、コンフィギュレーションデータの書き込みに使用できる。この例では、ビット線 BL とプリチャージ線 PC a の信号は、それぞれ、図 11(A) の例におけるプリチャージ線 PC a とビット線 BL の信号と同じである。したがって、メモリノード MN とソースノード SN の電位のタイミングチャートは図 11(A) のものとは異なる。

50

**【 0 0 7 4 】**

これらの例では、書き込みトランジスタ 103a がオンとなる前にプリチャージトランジスタ 108a がオンとなる場合(図 11(A))あるいは、書き込みトランジスタ 103a がオンとなっている間にプリチャージトランジスタ 108a がオンとなる場合(図 11(B))で、書き込みトランジスタ 103a がオフとなった後にプリチャージトランジスタ 108a がオフとなる。

**【 0 0 7 5 】**

しかしながら、他の駆動方法も利用できる。例えば、図 11(A) の T1 から T5 あるいは図 11(B) の T11 から T15 の間の任意の期間が、プリチャージトランジスタ 108a をオン状態とする期間に使用できる。

10

**【 0 0 7 6 】****( 実施の形態 2 )**

本実施の形態では、断面図を用いて、実施の形態 1 の半導体装置を製造するステップを説明する。図 12 および図 13 は断面図を示す。なお、図 12 および図 13 は半導体装置の層構造を理解するためだけのものであり、図 12 および図 13 は特定の実在する断面ではない。

**【 0 0 7 7 】****( 図 12 ( A ) )**

素子分離領域 201 が半導体基板 200 に形成される。半導体基板 200 は、例えば、単結晶シリコン基板あるいはシリコン・オン・インシュレータ(SOI)基板でもよい。半導体基板 200 は n 型ドーパントで軽くドーピングされていてもよいし、真性でもよい。素子分離領域 201 は、例えば、シャロー・トレインチ・アイソレーション(STI)技術によって形成されてもよい。

20

**【 0 0 7 8 】**

次に、素子分離領域 201 が設けられていない領域に p 型領域 202 が形成される。

**【 0 0 7 9 】****( 図 12 ( B ) )**

素子分離領域 201 と p 型領域 202 の上にゲート絶縁物 203 が形成される。ゲート絶縁物 203 は p 型領域 202 の上のみに形成されてもよい。ゲート絶縁物 203 は、例えば、酸化シリコン、酸化ハフニウム、その他の酸化物でできてもよい。

30

**【 0 0 8 0 】**

配線 204a、配線 204b がゲート絶縁物 203 の上に形成される。この図では、配線 204a(および配線 204b)の 2 つの断面が示されている。これは、この面では、配線 204a が 2 つの断面を有し、それぞれの断面は单一の物体のものを示していることを意味している。

**【 0 0 8 1 】**

配線 204a と配線 204b は金属やドーピングされたシリコンでできてもよい。一例では、配線 204a と配線 204b は、単層あるいは多層の導電膜の選択的なエッチングにより形成されてもよい。この例では、配線 204a と配線 204b は互いに分離されている(互いに接触しない)。

40

**【 0 0 8 2 】**

配線 204a と配線 204b は、図 4(B)、図 5、図 6 あるいは図 7 の、それぞれ、コンテキスト線 CXa(の一部)とメモリノード MN(の一部)に相当することがある。

**【 0 0 8 3 】**

n 型領域 205a、n 型領域 205b、n 型領域 205c、n 型領域 205d を、配線 204a と配線 204b をドーピングマスクとして用いて形成する。n 型領域 205c は図 4(B)、図 5、図 6 あるいは図 7 のソースノード SN(の一部)に相当することがある。このステップの前後にゲート絶縁物 203 の一部の領域がエッチングされてもよい。

**【 0 0 8 4 】****( 図 12 ( C ) )**

50

層間絶縁物 206 が、ゲート絶縁物 203、配線 204a、配線 204b の上に形成される。層間絶縁物 206 は、例えば、酸化シリコン、酸化炭化シリコンあるいはその他の金属酸化物からできてもよい。層間絶縁物 206 は誘電率を減らすためにボイドを有してもよい。

【0085】

層間絶縁物 206 の表面は研磨平坦化される。層間絶縁物 206 にコンタクトホールを形成した後、配線 207a、配線 207b が形成される。配線 207a と配線 207b は、図 4 (B)、図 5、図 6 あるいは図 7 の、それぞれ、ノード OUT (の一部) とメモリノード MN (の一部) に相当することがある。

【0086】

(図 12 (D))

層間絶縁物 206、配線 207a、配線 207b の上に層間絶縁物 208 が形成される。層間絶縁物 208 の表面は研磨平坦化される。配線 209 が、層間絶縁物 208 の上に形成される。さらに、層間絶縁物 210 が、層間絶縁物 208 と配線 209 の上に形成される。層間絶縁物 210 の表面は研磨平坦化される。

【0087】

酸化物半導体膜 211a と酸化物半導体膜 211b が層間絶縁物 210 の上に形成される。酸化物半導体膜 211a は配線 209 と重なる。酸化物半導体膜 211a と酸化物半導体膜 211b は In - Ga - Zn 酸化物でできてもよい。層間絶縁物 208 と層間絶縁物 210 をエッチングして、配線 207a へのコンタクトホール 212a と、配線 207b へのコンタクトホール 212b が形成される。

【0088】

(図 13 (A))

単層あるいは多層の導電層 213 を、層間絶縁物 210、酸化物半導体膜 211a、酸化物半導体膜 211b の上に、それらを覆い、コンタクトホール 212a とコンタクトホール 212b を埋めるように形成する。導電層 213 の表面は研磨平坦化される。さらに、単層あるいは多層の絶縁体 214 を導電層 213 の上に形成する。絶縁体 214 の表面は研磨平坦化される。

【0089】

(図 13 (B))

一回のリソグラフィーにより、導電層 213 と絶縁体 214 を選択的にエッチングし、配線 215a、配線 215b、配線 215c、配線 215a 上のパターン化された絶縁体 216a、配線 215b 上のパターン化された絶縁体 216b、配線 215c 上のパターン化された絶縁体 216c を形成する。配線 215a、配線 215b、配線 215c は、図 4 (B)、図 5、図 6 あるいは図 7 の、それぞれ、ノード OUT (の一部)、ビット線 BL (の一部)、メモリノード MN (の一部) に相当することがある。

【0090】

配線 215a、配線 215b、配線 215c の形状は、それぞれ、パターン化された絶縁体 216a、パターン化された絶縁体 216b、パターン化された絶縁体 216c と実質的に同一である。このエッチングにより、酸化物半導体膜 211a と酸化物半導体膜 211b が露出する。

【0091】

層間絶縁物 210、酸化物半導体膜 211a、酸化物半導体膜 211b、配線 215a、配線 215b、配線 215c、パターン化された絶縁体 216a、パターン化された絶縁体 216b、パターン化された絶縁体 216c の上にゲート絶縁体 217 を形成する。

【0092】

そして、配線 218a と配線 218b を、それぞれ、酸化物半導体膜 211a と酸化物半導体膜 211b を覆って形成する。配線 218a は、図 4 (B)、図 5、図 6 あるいは図 7 のワード線 WL a (の一部) に相当することがある。

【0093】

10

20

30

40

50

かくして、図4( B )、図5、図6あるいは図7の書き込みトランジスタ103a、パストランジスタ104a、容量素子105a、選択トランジスタ106a、選択トランジスタ107aを形成できる。これらの断面には示されていないが、プリチャージトランジスタ108aも同じ方法で形成できる。プリチャージトランジスタ108aは、書き込みトランジスタ103aのような構造あるいはパストランジスタ104aのような構造を有してもよい。

#### 【0094】

この例では、容量素子105aは金属-絶縁体-半導体(MIS)構造を有するが、金属-絶縁体-金属(MIM)構造を用いて形成してもよい。メモリノードMNの電位に関わらず十分な容量を得るために、配線218bの電位は、「H」に容量素子105aのしきい値を足したものより高くするとよい。しきい値が0V未満であれば、配線218bに与えられる電位は「H」とでき、しきい値が「L-H」未満であれば、配線218bに与えられる電位は「L」でよい。10

#### 【0095】

配線218bに高い電位が不要であるので、そのような低いしきい値は、酸化物半導体からゲート絶縁体217への電子注入を防止する上で有利である。電子注入は、しきい値上昇が生じ、容量減少をもたらす。

#### 【0096】

低い電位を印加することによるホール注入に関しては、酸化物半導体、特に、インジウム(In)、ガリウム(Ga)あるいは亜鉛(Zn)を有する酸化物半導体は、ホールの有効質量が重いのでホールを放出しない。したがって、ホール注入による劣化は無視できる。20

#### 【0097】

上記の特性は容量素子には好ましいものであるが、トランジスタにはそうではない。容量素子105aのしきい値が低いということは、構造が似ていることから、書き込みトランジスタ103aのしきい値の低いことを意味する。したがって、(後述する)バックゲートあるいはワード線WLaに低い電位を印加することが必要となる。

#### 【0098】

書き込みトランジスタ103aにおいては、パターン化された絶縁体216b/パターン化された絶縁体216cが配線218aと配線215b/配線215cの間に設けられている。したがって、配線218aと配線215b/配線215cの間の寄生容量が低減できる。30

#### 【0099】

書き込みトランジスタ103aは2つのゲート電極、すなわち、配線209と配線218aを有する。配線209は書き込みトランジスタ103aのしきい値を制御するためのバックゲートとして使用されてもよい。

#### 【0100】

配線209に、「L」より低い(固定された)電位を印加することで、書き込みトランジスタ103aのしきい値を高めることができる。したがって、ワード線WLa(配線218a)に「L」が印加されているときのソースドレン電流を1zA未満に低減できる。同様な効果は、バックゲート無しでも、ワード線WLaに「L」より低い電位を印加することで得られる。40

#### 【0101】

他の配線や層間絶縁物が形成されてもよい。

#### 【0102】

##### (実施の形態3)

本実施の形態ではプログラマブルスイッチを有する半導体装置(FPGA)の例を説明する。

#### 【0103】

図14はスイッチアレイ301、ロジックアレイ302、I/Oアレイ303を有するF50

P G A の例を示すブロック図である。

**【 0 1 0 4 】**

それぞれのスイッチアレイ 3 0 1 はマトリクス状に配置された複数のルーティングスイッチ ( S W a 、 S W b 、 S W c ) を含む回路ブロックである。それぞれのルーティングスイッチは、複数のコンテキストを格納するため、図 8 に示すように複数のプログラマブルスイッチを含む。

**【 0 1 0 5 】**

それぞれのロジックアレイ 3 0 2 は、列状に配置された複数のロジックブロックを有する。図 1 4 の例では、それぞれのロジックアレイ 3 0 2 は、一列に配置された 1 0 個のロジックブロック ( L B 0 0 乃至 L B 0 9 ) を有する。それぞれのロジックブロックはコンフィギュレーションデータを保持するメモリを有する。

10

**【 0 1 0 6 】**

I / O アレイ 3 0 3 は、F P G A の両端に設けられ、それぞれ、列状に配置された 1 0 個の入出力回路 ( I / O 0 0 0 乃至 I / O 0 9 および I / O 1 0 乃至 I / O 1 9 ) を有する。

**【 0 1 0 7 】**

ルーティングスイッチ S W a はロジックブロック間の接続を制御する。例えば、「 S W a 0 \* - 0 0 」は、ロジックブロック L B 0 0 乃至 L B 0 9 のいずれかの出力とロジックブロック L B 0 0 の入力が、このルーティングスイッチにより接続あるいは切断されることを意味する。

20

**【 0 1 0 8 】**

ルーティングスイッチ S W b はロジックブロックの入力端子と入出力回路の間の接続を制御する。例えば、「 S W b 0 \* - 0 0 」は、入出力回路 I / O 0 0 0 乃至 I / O 0 9 のいずれかとロジックブロック L B 0 0 の入力が、このルーティングスイッチにより接続あるいは切断されることを意味する。

**【 0 1 0 9 】**

ルーティングスイッチ S W c はロジックブロックの出力端子と入出力回路の間の接続を制御する。例えば、「 S W c 0 \* - 0 0 」は、入出力回路 I / O 0 0 0 乃至 I / O 0 9 のいずれかとロジックブロック L B 0 0 の出力が、このルーティングスイッチにより接続あるいは切断されることを意味する。

30

**【 0 1 1 0 】**

一般的に、ロジックブロックは 1 以上のルックアップテーブル ( L U T ) 、 1 以上のフリップフロップ ( F F ) 、 1 以上のマルチプレクサ ( M U X ) を有する。図 1 5 ( A ) はロジックブロック 3 1 1 の構成例を描写するブロック図である。ロジックブロック 3 1 1 は、ルックアップテーブル 3 1 2 、フリップフロップ 3 1 3 、マルチプレクサ 3 1 4 を有する。

**【 0 1 1 1 】**

ルックアップテーブル 3 1 2 をロジックゲートとして機能を特定させるための情報を含むコンフィギュレーションデータ 3 1 8 a は、ルックアップテーブル 3 1 2 に入力される。換言すれば、ルックアップテーブル 3 1 2 から出力される信号のロジックレベル ( 例えば「 1 / 0 」あるいは「 H / L 」 ) は、コンフィギュレーションデータ 3 1 8 a と入力端子 3 1 6 からルックアップテーブル 3 1 2 へ入力される信号のロジックレベルに応じて決定される。

40

**【 0 1 1 2 】**

ルックアップテーブル 3 1 2 から出力される信号はフリップフロップ 3 1 3 に入力される。ロジックブロック 3 1 1 に含まれているフリップフロップ 3 1 3 から出力される信号は、他のロジックブロック 3 1 1 に含まれているフリップフロップ 3 1 3 に入力されることがある。フリップフロップ 3 1 3 はこれらの入力信号を保持する機能を有する。

**【 0 1 1 3 】**

マルチプレクサ 3 1 4 の駆動を制御する情報を有するコンフィギュレーションデータ 3 1 8 b はマルチプレクサ 3 1 4 に入力される。マルチプレクサ 3 1 4 は、コンフィギュレー

50

ションデータ318bに応じて、ルックアップテーブル312あるいはフリップフロップ313から出力される信号のいずれかを選択する機能を有する。マルチプレクサ314によって選択された信号はロジックブロック311の出力端子317から出力される。

#### 【0114】

図15(B)は図15(A)のロジックブロック311の具体的な構成例を示す。図15(B)のロジックブロック311は、ルックアップテーブル312、フリップフロップ313、マルチプレクサ314、ルックアップテーブル312のためのコンフィギュレーションデータ318aを格納するコンフィギュレーションメモリ315a、マルチプレクサ314のためのコンフィギュレーションデータ318bを格納するコンフィギュレーションメモリ315bを有する。10

#### 【0115】

ルックアップテーブル312で実行される論理動作は、コンフィギュレーションメモリ315aに格納されているコンフィギュレーションデータ318aに応じて変わる。ルックアップテーブル312で実行される論理動作がコンフィギュレーションデータ318aによって決定されるとき、ルックアップテーブル312は、入力端子316に供給される複数の入力信号に対応した出力信号を生成する。フリップフロップ313は、ルックアップテーブル312で生成された出力信号を保持し、クロック信号CKに同期してルックアップテーブル312の出力信号に対応する出力信号を出力する。

#### 【0116】

ルックアップテーブル312およびフリップフロップ313から出力される信号はマルチプレクサ314に入力される。マルチプレクサ314は、コンフィギュレーションメモリ315bに格納されているコンフィギュレーションデータ318bに応じてこれら2つの出力信号のうちの一つを選択し、出力する機能を有する。マルチプレクサ314から出力される信号は出力端子317に供給される。20

#### 【0117】

図15(C)は、図15(A)のロジックブロック311の別の具体的な構成例を示す。図15(C)のロジックブロック311は、図15(B)のロジックブロック311とマルチプレクサ319とマルチプレクサ319のためのコンフィギュレーションデータを格納するコンフィギュレーションメモリ315cを有する点で異なる。

#### 【0118】

ルックアップテーブル312から出力される信号と他のロジックブロック311にあるフリップフロップ313から出力される信号がマルチプレクサ319に入力される。他のロジックブロック311にあるフリップフロップ313から出力される信号は入力端子320から入力される。マルチプレクサ319は、コンフィギュレーションメモリ315cに格納されているコンフィギュレーションデータに応じてこれら2つの出力信号のうちの一つを選択し、出力する機能を有する。30

#### 【0119】

図15(C)のロジックブロック311では、フリップフロップ313は、マルチプレクサ319から出力された信号を保持し、クロック信号CKに同期してマルチプレクサ319から出力された信号に対応する出力信号を出力する。40

#### 【0120】

なお、図15(B)あるいは図15(C)で示されるロジックブロック311では、コンフィギュレーションデータによって使用可能なフリップフロップ313の型が決定される。特に、フリップフロップ313は、コンフィギュレーションデータにもよるが、D - フリップフロップ、T - フリップフロップ、JK - フリップフロップ、RS - フリップフロップのいずれかである。

#### 【実施例】

#### 【0121】

実施の形態3で示されたFPGAのパフォーマンスを、S P I C EシミュレータとしてシノプシスX A(登録商標)を使用して、シミュレーションした。このシミュレーションで50

は、2種類のプログラマブルスイッチを検証した。1つは図1(B)で示されるもので、他の1つは図6(A)で示されるものである。

#### 【0122】

FPGAは、20個のロジックブロックと20個の入出力端子(I/O[0]乃至I/O[19])、2つのコンテキスト(Context[1]とContext[2]を有するものとした。また、さまざまなタスク(Task[0]、Task[1]等)を実行できるものとした。シミュレーションでは、グローバルクロック周波数が2.5Vで33MHzとした。

#### 【0123】

シミュレーションでは、初期化の後、FPGAの一部をシフタ回路に対応した構成に設定した。すなわち、シフタ回路を実行するためのContext[0]に対応したコンフィギュレーションデータをFPGAに書き込み、Task[0]として動作させた。シフタ回路は図16(A)に示される。Task[0]の間に、FPGAの一部をリングオシレータの構成に設定した。すなわち、リングオシレータを実行するContext[1]に対応したコンフィギュレーションデータをFPGAに書き込み、Task[0]の後で、Task[1]として動作させた。(7段) リングオシレータは図16(B)に示される。リングオシレータの構成への設定をTask[0]を中断することなく実行した。

#### 【0124】

図15(B)に示されるロジックブロックを想定すれば、シフタ回路に対応した構成に設定するために、ルックアップテーブル312は特定の入力信号のみに応じて信号をフリップフロップ313に出力するように設定し、マルチプレクサ314はフリップフロップの出力のみを通過させるように設定した。

#### 【0125】

同様に、リングオシレータに対応した構成に設定するために、ルックアップテーブル312は特定の入力信号のみに応じて反転信号をマルチプレクサ314に出力するように設定し、マルチプレクサ314はルックアップテーブル312の出力のみを通過させるように設定した。

#### 【0126】

Context[1]に対応したコンフィギュレーションデータは、Task[0]の間にそれぞれのルーティングスイッチの対応するプログラマブルスイッチに書き込んだ。

#### 【0127】

Task[0]の間、シフタ回路は、I/O00からの入力信号に応じて、図17(A)で示されるパルス信号、あるいは図17(B)で示されるステップ信号を出力した。したがって、リングオシレータへの再設定において、プログラマブルスイッチのソースノードの電位は、シフタ回路の出力に応じて変わった。

#### 【0128】

図17(A)および図17(B)に示されるように、再設定はT0に開始された。T0では、個々のロジックブロックの出力電位は、シフタ回路がパルス信号を出力したときは、「L」であり、シフタ回路がステップ信号を出力したときは、「H」であった。

#### 【0129】

図18(A)と図18(C)は、図1(B)に示されるプログラマブルスイッチを使用した場合の、I/O06のシミュレーションされた出力、すなわち、Task[1]の間のリングオシレータの発振波形である。図18(A)は、図17(A)のT0、すなわち、ソースノードの電位が「L」であるときに設定されたものであり、図18(C)は、図17(B)のT0、すなわち、ソースノードの電位が「H」でのものである。

#### 【0130】

図18(A)と図18(C)より、発振周波数は、それぞれ21MHzと13MHzであった。これはオン抵抗の差によって生じた。このように何らかの要因によって信号の応答速度が変動する場合、回路の動作は遅い信号に基づいて設定される。この場合は、13MHzを前提に回路の動作が設定される。

10

20

30

40

50

**【0131】**

図18(B)と図18(D)は、図1(B)に示されるルーティングスイッチ100を使用した場合の、Task[1]の間の対応するプログラマブルスイッチのメモリノードのシミュレーションされた出力である。図18(B)と図18(D)は、それぞれ、図18(A)と図18(C)に対応する。見てわかるように、ブースティング効果と逆ブースティング効果によって両者に差が生じ、ソースノードの電位がLという条件で設定されたものの電位(図18(B))は他方より高い。

**【0132】**

図19は、図6(A)で示されるプログラマブルスイッチを有するFPGAのパフォーマンスを示す。図19(A)と図19(C)は、Task[1]の間のI/O06のシミュレーションされた出力である。図19(A)は、パルス信号で設定されたものであり、図19(C)は、ステップ信号でのものである。いずれの場合も発振周波数は18MHzであった。

10

**【0133】**

これは、図18(A)のものよりは低いものの、図18(C)のものよりは高い。図1(B)の回路では、図18(C)に示されるリングオシレータの発振周波数(13MHz)より定まる応答速度を前提として、回路の動作が設定されるのに対し、図6(A)の回路では、図19(A)と図19(C)に示されるリングオシレータの発振周波数(18MHz)より定まる応答速度を前提として、回路の動作が設定される。したがって、より高速な動作が実現できる。

20

**【0134】**

図19(B)と図19(D)は、Task[1]の間の、対応するプログラマブルスイッチのメモリノードのシミュレーションされた出力である。図19(B)と図19(D)は、それぞれ、図19(A)と図19(C)に対応し、実質的な差異はなかった。

**【0135】**

図1(B)と図6(A)を比較すれば、後者は、追加のトランジスタ、選択トランジスタ107aを必要とするので、動作速度や信号の強度で不利である。出力信号の強度と伝送遅延を改善するためのコンテキスト信号のオーバードライブをシミュレーションした。

**【0136】**

図20は、Task[1]の間の7段リングオシレータで、コンテキスト信号がオーバードライブされたときに、図1(B)のプログラマブルスイッチと図6(A)のプログラマブルスイッチに関して周期がどのように変わるかシミュレーションした結果を示す。見てわかるように、図6(A)のプログラマブルスイッチ(曲線X)は、コンフィギュレーションが「L」でおこなわれた図1(B)のプログラマブルスイッチ(曲線Y)より長い周期となるが、コンフィギュレーションが「H」でおこなわれた図1(B)のプログラマブルスイッチ(曲線Z)よりはるかに短い周期となる。

30

**【0137】**

次に、3つの異なるプログラムをFPGAからロードする場合についてシミュレーションをおこなった。すなわち、I/O[0]からI/O[19]に、信号をシフトさせる増加シフタ(Task[0])と、I/O[19]からI/O[0]に、信号をシフトさせる減少シフタ(Task[1])と、I/O[i]の周波数をI/O[i-1]の半分に変換する分周回路(Task[2])である。

40

**【0138】**

最初に、第1の構成に対応したタスクが、実行される。このとき、Context[0]にはTask[0]が、Context[1]にはTask[1]が保存されていた。Context[0]が実行された後、Context[1]が続いた。その後、Context[1]がTask[2]を保持するように再構成されている間に、Context[0]をもう一度実行した。再構成が終わると、最後にContext[1]を実行した。シミュレーションの結果を図22に示す。図から、コンテキストの切り替えが明瞭におこなえること、および、Context[0]がFPGAで実行されている間に、Con

50

`t e x t [ 1 ]` が、最初のシフタの構成から分周回路の構成にどのように変化することがわかる。

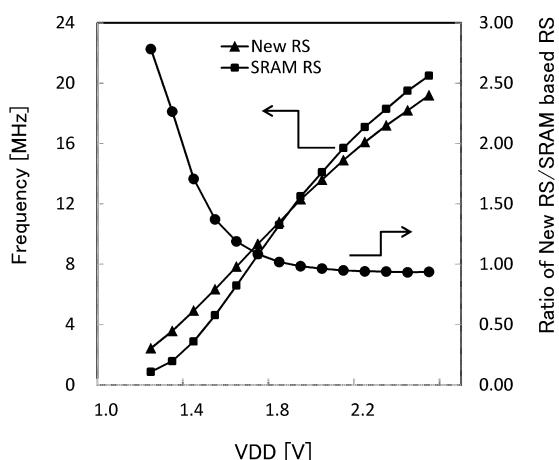

#### 【 0 1 3 9 】

次に、図 4 ( B ) に示されるプログラマブルスイッチ 101a を含む F P G A と、 S R A M ベースの F P G A との特性の比較をおこなった。市販されているリコンフィギュラブルな F P G A のほとんどは S R A M ベースである。評価はそれぞれのタイプのルーティングスイッチで 53 段リングオシレータを構成することでおこなった。ここで、容量素子 105a の容量は 4 fF とした。

#### 【 0 1 4 0 】

図 23 は、オーバードライブ信号がコンテキスト線 C X a に印加されている場合の、それぞれのルーティングスイッチでの発振周波数の電圧依存性である。図から明らかなように、図 4 ( B ) に示されるプログラマブルスイッチ 101a を含むルーティングスイッチ ( N e w R S ) は、高い電圧域では、 S R A M ベースのルーティングスイッチ ( S R A M R S ) に劣るもの、 1.8 V 未満では、優れていることがわかった。例えば、電圧 1.5 V では、 S R A M ベースのルーティングスイッチより 37 % 高速となった。

#### 【 0 1 4 1 】

次に消費電力について検討した。 S R A M ベースの F P G A のコンフィギュレーションメモリのスタティック消費電力は、微細化とともに増加し、全消費電力の 38 % を占めていると推定されている。 S P I C E を用いたシミュレーションでは、図 4 ( B ) に示されるプログラマブルスイッチ 101a を含むルーティングスイッチを再構成する際の全エネルギーは 334 fJ であると計算された。うち、 187 fJ はデータを書き換えるために用いられ、 147 fJ が、ソースノード S N の電位を電位 " L " ( 接地電位 ) とするために用いられる。

#### 【 0 1 4 2 】

上記でシミュレーションに用いたものと同等な半導体装置の構造を以下に説明する。図 21 は半導体装置の配線、半導体膜、コンタクトホールのレイアウトを示す。なお、各図の右端の十字 ( + ) はマーカーとして機能する。したがって、 2 以上の図を、それらの全ての十字が完全に重なるように重ねると、異なる層の間の正確な関係が理解できよう。

#### 【 0 1 4 3 】

半導体装置は、単結晶シリコンウェハー上の酸化シリコン上の単結晶シリコン膜 ( 厚さ 50 nm ) 、単結晶シリコン膜を酸化して形成された第 1 のゲート絶縁物 ( 厚さ 15 nm ) 、第 1 のゲート絶縁物上の第 1 の配線 ( 厚さ 30 nm の窒化タンタルとその上の厚さ 170 nm の W の多層構造 ) 、第 1 の層間絶縁物 ( 厚さ 50 nm の S i O N と厚さ 280 nm の S i N O と厚さ 300 nm の S i O x の多層構造 ) 、第 2 の配線 ( 厚さ 150 nm の W ) 、第 2 の層間絶縁物 ( 厚さ 400 nm 乃至 500 nm の T E O S - S i O x ) 、第 3 の配線 ( 厚さ 150 nm の W ) 、第 3 の層間絶縁物 ( 厚さ 50 nm の A l O x と厚さ 300 nm の S i O x の多層構造 ) 、厚さ 15 nm の I n - G a - Z n 酸化物膜、第 4 の配線 ( 厚さ 100 nm の W ) 、第 2 のゲート絶縁物 ( 厚さ 15 nm の S i O N ) 、第 5 の配線 ( 厚さ 30 nm の窒化タンタルとその上の厚さ 135 nm の W の多層構造 ) 、第 4 の層間絶縁物 ( 厚さ 70 nm の A l O x と厚さ 300 nm の S i O N の多層構造 ) 、第 6 の配線 ( 厚さ 50 nm の T i と厚さ 200 nm の A l と厚さ 50 nm の T i の多層構造 ) 、第 5 の層間絶縁物 ( 厚さ 1500 nm のポリイミド ) 、第 7 の配線 ( 厚さ 50 nm の T i と厚さ 300 nm の A l と厚さ 50 nm の T i の多層構造 ) 、第 6 の層間絶縁物 ( 厚さ 1500 nm のポリイミド ) を有した。

#### 【 0 1 4 4 】

第 1 の配線のいくつかはシリコンベースのトランジスタのゲート電極として機能した。第 2 の配線のいくつかはシリコンベースのトランジスタのソースあるいはドレイン電極として機能した。第 3 の配線のいくつかは酸化物半導体ベースのトランジスタのバックゲート電極として機能した。第 4 の配線のいくつかは酸化物半導体ベースのトランジスタのソースあるいはドレイン電極として機能した。第 5 の配線のいくつかは酸化物半導体ベースの

10

20

30

40

50

トランジスタのゲート電極として機能した。

**【0145】**

第1の層間絶縁物、第2の層間絶縁物、第3の層間絶縁物、第2のゲート絶縁物、第4の層間絶縁物、第5の層間絶縁物には、異なる層の間の接続のためのコンタクトホールが形成された。

**【0146】**

図21(A)は単結晶シリコン膜と第1の配線204のレイアウトを示す。単結晶シリコン膜は、n型領域205を有した。なお、第1の配線204と重なった単結晶シリコン膜の部分は、弱くp型にドープされた。

**【0147】**

図21(B)は第2の配線(ハッチングされた部分)と、第1の層間絶縁物に設けられた、n型領域205へのコンタクトホールのレイアウトを示す。コンタクトホールは、ハッチングされた部分中の長方形として示されている。

**【0148】**

図21(C)は第3の配線(ハッチングされた部分)と、第2の層間絶縁物に設けられた、第2の配線へのコンタクトホールのレイアウトを示す。コンタクトホールは、ハッチングされた部分中の長方形として示されている。

**【0149】**

図21(D)はIn-Ga-Zn酸化物膜のレイアウトを示す。

**【0150】**

図21(E)は第4の配線(ハッチングされた部分)と、第3の層間絶縁物に設けられた、第3の配線へのコンタクトホールのレイアウトを示す。コンタクトホールは、ハッチングされた部分中の長方形として示されている。

**【0151】**

図21(F)は第5の配線(ハッチングされた部分)のレイアウトを示す。

**【0152】**

図21(G)は第6の配線(ハッチングされた部分)と、第2のゲート絶縁物および第4の層間絶縁物に設けられた、第4の配線および第5の配線へのコンタクトホールのレイアウトを示す。コンタクトホールは、ハッチングされた部分中の長方形として示されている。

**【0153】**

図21(H)は第7の配線(ハッチングされた部分)と、第5の層間絶縁物に設けられた、第6の配線へのコンタクトホールのレイアウトを示す。コンタクトホールは、ハッチングされた部分中の長方形として示されている。

**【0154】**

なお、酸化物半導体トランジスタは、1.0 μmの、単結晶シリコントランジスタは0.5 μmの設計ルールを用いた。上記のレイアウトでは、同様な設計ルールを用いたSRAMベースのルーティングスイッチより、面積が38%減少する。

**【符号の説明】**

**【0155】**

100 ルーティングスイッチ

101 プログラマブルスイッチ

101a プログラマブルスイッチ

101b プログラマブルスイッチ

101c プログラマブルスイッチ

102a ロジックブロック

102b ロジックブロック

103a 書き込みトランジスタ

103b 書き込みトランジスタ

103c 書き込みトランジスタ

10

20

30

40

50

|         |              |    |

|---------|--------------|----|

| 1 0 4 a | パストランジスタ     |    |

| 1 0 4 b | パストランジスタ     |    |

| 1 0 4 c | パストランジスタ     |    |

| 1 0 5 a | 容量素子         |    |

| 1 0 5 b | 容量素子         |    |

| 1 0 5 c | 容量素子         |    |

| 1 0 6 a | 選択トランジスタ     | 10 |

| 1 0 6 b | 選択トランジスタ     |    |

| 1 0 6 c | 選択トランジスタ     |    |

| 1 0 7 a | 選択トランジスタ     |    |

| 1 0 8 a | プリチャージトランジスタ |    |

| 1 0 9 a | 選択トランジスタ     |    |

| 1 1 0 a | 選択トランジスタ     |    |

| 2 0 0   | 半導体基板        |    |

| 2 0 1   | 素子分離領域       |    |

| 2 0 2   | p型領域         |    |

| 2 0 3   | ゲート絶縁物       |    |

| 2 0 4   | 配線           |    |

| 2 0 4 a | 配線           |    |

| 2 0 4 b | 配線           | 20 |

| 2 0 5   | n型領域         |    |

| 2 0 5 a | n型領域         |    |

| 2 0 5 b | n型領域         |    |

| 2 0 5 c | n型領域         |    |

| 2 0 5 d | n型領域         |    |

| 2 0 6   | 層間絶縁物        |    |

| 2 0 7 a | 配線           |    |

| 2 0 7 b | 配線           |    |

| 2 0 8   | 層間絶縁物        |    |

| 2 0 9   | 配線           | 30 |

| 2 1 0   | 層間絶縁物        |    |

| 2 1 1 a | 酸化物半導体膜      |    |

| 2 1 1 b | 酸化物半導体膜      |    |

| 2 1 2 a | コンタクトホール     |    |

| 2 1 2 b | コンタクトホール     |    |

| 2 1 3   | 導電層          |    |

| 2 1 4   | 絶縁体          |    |

| 2 1 5 a | 配線           |    |

| 2 1 5 b | 配線           |    |

| 2 1 5 c | 配線           | 40 |

| 2 1 6 a | パターン化された絶縁体  |    |

| 2 1 6 b | パターン化された絶縁体  |    |

| 2 1 6 c | パターン化された絶縁体  |    |

| 2 1 7   | ゲート絶縁体       |    |

| 2 1 8 a | 配線           |    |

| 2 1 8 b | 配線           |    |

| 3 0 1   | スイッチアレイ      |    |

| 3 0 2   | ロジックアレイ      |    |

| 3 0 3   | I/Oアレイ       |    |

| 3 1 1   | ロジックブロック     | 50 |

|         |                |    |

|---------|----------------|----|

| 3 1 2   | ルックアップテーブル     |    |

| 3 1 3   | フリップフロップ       |    |

| 3 1 4   | マルチプレクサ        |    |

| 3 1 5 a | コンフィギュレーションメモリ |    |

| 3 1 5 b | コンフィギュレーションメモリ |    |

| 3 1 5 c | コンフィギュレーションメモリ |    |

| 3 1 6   | 入力端子           |    |

| 3 1 7   | 出力端子           |    |

| 3 1 8 a | コンフィギュレーションデータ | 10 |

| 3 1 8 b | コンフィギュレーションデータ |    |

| 3 1 9   | マルチプレクサ        |    |

| 3 2 0   | 入力端子           |    |

| B L     | ビット線           |    |

| C X     | コンテキスト線        |    |

| C X a   | コンテキスト線        |    |

| C X b   | コンテキスト線        |    |

| C X c   | コンテキスト線        |    |

| C Y a   | コンテキスト線        |    |

| I N     | ノード            |    |

| I / O   | 入出力回路          | 20 |

| L B     | ロジックブロック       |    |

| M N     | メモリノード         |    |

| O U T   | ノード            |    |

| S N     | ソースノード         |    |

| S W a   | ルーティングスイッチ     |    |

| S W b   | ルーティングスイッチ     |    |

| S W c   | ルーティングスイッチ     |    |

| W L     | ワード線           |    |

| W L a   | ワード線           |    |

| W L b   | ワード線           | 30 |

| W L c   | ワード線           |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2-1】

【図2-2】

【図2-3】

---

フロントページの続き

(56)参考文献 特開2004-119970(JP,A)

特開2013-251894(JP,A)

特開平07-321641(JP,A)

特開平10-214482(JP,A)

特開2001-024162(JP,A)

米国特許第08072237(US,B1)

(58)調査した分野(Int.Cl., DB名)

H03K 19/173

H01L 21/8242

H01L 27/10

H01L 27/108

H01L 29/786