(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-60079

(P2006-60079A)

(43) 公開日 平成18年3月2日(2006.3.2)

| (51) Int.CI.                 | F 1             | テーマコード (参考) |

|------------------------------|-----------------|-------------|

| <b>H01L 29/786 (2006.01)</b> | H01L 29/78 618B | 5 F 11 O    |

| <b>H01L 21/336 (2006.01)</b> | H01L 29/78 618A |             |

| <b>H01L 51/05 (2006.01)</b>  | H01L 29/78 617T |             |

|                              | H01L 29/28      |             |

審査請求 未請求 請求項の数 18 O L (全 23 頁)

|           |                              |          |                                          |

|-----------|------------------------------|----------|------------------------------------------|

| (21) 出願番号 | 特願2004-241336 (P2004-241336) | (71) 出願人 | 000006747<br>株式会社リコー<br>東京都大田区中馬込1丁目3番6号 |

| (22) 出願日  | 平成16年8月20日 (2004.8.20)       | (74) 代理人 | 100090527<br>弁理士 舘野 千恵子                  |

|           |                              | (72) 発明者 | 田野 隆徳<br>東京都大田区中馬込1丁目3番6号 株式会社リコー内       |

|           |                              | (72) 発明者 | 藤村 浩<br>東京都大田区中馬込1丁目3番6号 株式会社リコー内        |

|           |                              | (72) 発明者 | 近藤 浩<br>東京都大田区中馬込1丁目3番6号 株式会社リコー内        |

最終頁に続く

(54) 【発明の名称】半導体層のパターン形成方法及び電子素子、電子素子アレイ、表示装置

## (57) 【要約】

【課題】FET構造を有する素子の半導体層を、製造工程が簡便で、高速、かつメンテナンス性よく、しかも有機半導体材料にダメージを与えることなく任意のパターン形状で形成できるパターン形成方法と、電子素子、電子素子アレイ、表示装置を提供する。

【解決手段】基板1上に直接またはゲート絶縁層4を介してソース電極5およびドレイン電極6を対向形成すると共に、該ソース電極およびドレイン電極形成領域以外のゲート絶縁層または基板の各臨界表面張力を各電極の形成領域における各臨界表面張力よりも小さい低表面エネルギーとし、ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層3を形成する。この製造方法によって得られた電子素子をアレイ化し、これを用いて表示装置を構成する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

基板上に直接またはゲート絶縁層を介してソース電極およびドレイン電極を適宜の間隔で対向形成し、該ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層を形成する工程を有する、FET構造からなる半導体層のパターン形成方法であって、

前記ソース電極およびドレイン電極形成領域以外のゲート絶縁層または基板の各臨界表面張力は、該ソース電極およびドレイン電極の形成領域における各臨界表面張力よりも小さい低表面エネルギーであることを特徴とする半導体層のパターン形成方法。

**【請求項 2】**

基板上に、少なくとも臨界表面張力の小さい低表面エネルギーのゲート絶縁層を設け、所定のゲート絶縁層上に臨界表面張力の大きな高表面エネルギーのソース電極およびドレイン電極を適宜の間隔で対向形成し、該ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層を形成する工程を有する、FET構造からなる半導体層のパターン形成方法。

**【請求項 3】**

前記ソース電極およびドレイン電極の形成領域以外のゲート絶縁層または基板の臨界表面張力に比べて、10 mN/m以上臨界表面張力が大きいソース電極およびドレイン電極を形成する工程を含むことを特徴とする請求項 1 または 2 に記載の半導体層のパターン形成方法。

10

20

20

30

40

50

**【請求項 4】**

前記ソース電極およびドレイン電極に挟持された低表面エネルギーのゲート絶縁層または基板の間隔が、該ソース電極およびドレイン電極の各幅よりも小さくなるように各電極を形成する工程を含むことを特徴とする請求項 1 ~ 3 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 5】**

前記ソース電極およびドレイン電極に挟持されたゲート絶縁層または基板の臨界表面張力が、該各電極に挟持されていないゲート絶縁層または基板の臨界表面張力の値よりも大きくなるように作製する工程を含むことを特徴とする請求項 1 ~ 4 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 6】**

前記ゲート絶縁層は、エネルギーの付加によって臨界表面張力が変化する材料からなることを特徴とする請求項 1 ~ 5 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 7】**

前記ゲート絶縁層は、少なくとも第一の材料と第二の材料とからなり、該第一の材料は第二の材料と比較してエネルギーの付加によって臨界表面張力が大きく変化する材料であり、該第二の材料は第一の材料とは別の性能を補完する機能を有する材料であり、

かつ、前記第一の材料と第二の材料はゲート絶縁層厚方向に濃度分布を有し、最表層部における第一の材料の濃度が第二の材料の濃度よりも高いことを特徴とする請求項 1 ~ 6 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 8】**

前記第二の材料は、第一の材料と比較して電気絶縁性の高い材料であることを特徴とする請求項 7 に記載の半導体層のパターン形成方法。

**【請求項 9】**

前記第二の材料は、第一の材料と比較して高比誘電率の材料であることを特徴とする請求項 7 に記載の半導体層のパターン形成方法。

**【請求項 10】**

前記エネルギー付加が紫外線照射により行われ、ゲート絶縁層の臨界表面張力を変化させて低表面エネルギー領域を形成することを特徴とする請求項 6 ~ 9 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 1 1】**

前記ゲート絶縁層は、側鎖に疎水性基を有する高分子材料からなることを特徴とする請求項 1 ~ 1 0 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 1 2】**

前記側鎖に疎水性基を有する高分子材料は、ポリイミド構造を有する材料からなることを特徴とする請求項 1 1 に記載の半導体層のパターン形成方法。

**【請求項 1 3】**

前記半導体層は、有機半導体からなることを特徴とする請求項 1 ~ 1 2 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 1 4】**

前記ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与する方法が、インクジェット法であることを特徴とする請求項 1 ~ 1 3 のいずれかに記載の半導体層のパターン形成方法。

**【請求項 1 5】**

請求項 1 ~ 1 4 のいずれかに記載の半導体層のパターン形成方法により半導体層がパターニングされたことを特徴とする電子素子。

**【請求項 1 6】**

請求項 1 5 に記載の電子素子が絶縁性基板上に複数形成されたことを特徴とする電子素子アレイ。

**【請求項 1 7】**

前記絶縁性基板が、臨界表面張力の小さい低表面エネルギー領域を有するゲート絶縁層を兼ねることを特徴とする請求項 1 6 に記載の電子素子アレイ。

**【請求項 1 8】**

請求項 1 6 または 1 7 に記載の電子素子アレイを備えたことを特徴とする表示装置。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、半導体装置の製造方法とその関連技術に関し、特にフラットパネルディスプレイの駆動用などに用いられる素子の半導体層のパターン形成方法と、それにより得られる電子素子、それをアレイ化した電子素子アレイ、および電子素子アレイを備えた表示装置に関するものである。

**【背景技術】****【0 0 0 2】**

トランジスタアレイを形成する場合、隣り合ったトランジスタ素子の半導体層を電気的に分離しておかないと、動作時に隣りのトランジスタからのリーク電流によって相互干渉し、正確な動作ができなくなる。そのため、良好な性能の半導体素子を作製する上で、半導体層のパターニングを行うことが必須となる。例えば、現在広く利用されている無機半導体材料の場合には、フォトリソグラフィを用いて微細なパターンを形成する方法が一般的に用いられている。

**【0 0 0 3】**

すなわち、フォトリソグラフィでは、一般的に次のような工程によってパターニングが行われる。まず、パターニングしたい材料（以下、材料 A とよぶ）を基板全面に形成する。次に、形成した材料 A の上にフォトレジストをコーティングして乾燥した後、フォトマスクを使用して形成したいパターンを露光する。次いで、レジストを現像し、 rinsing することによってレジストパターンを形成する。その後、材料 A が溶解するエッチング剤を用いて材料 A をエッチングする。エッチング後、レジストを除去する。以上のプロセスを踏むことで材料 A を所望の形にパターニングすることができる。しかし、製造工程が複雑で

時間を要するなどの問題がある。

#### 【0004】

一方、近年有機半導体材料を使ったデバイスが注目を集めようになってきた。すなわち、有機半導体材料を用いた場合、無機半導体材料のデバイスと比較して、(1)成膜などの製造工程が簡単であり、(2)ファンデルワールス力によるゆるやかな結合で結びついているため材料自体に可撓性があり、フレキシブル基板への適用が容易であるなどの特徴がある。そのため、絶縁膜、誘電体膜、導電膜、半導体素子、発光素子、およびそれらを用いたフレキシブルで軽量な表示デバイスなどさまざま応用展開が期待されており、研究開発が活発化している。例えば、光や熱などの物理的外部刺激によりキャリア移動度が変化する材料を用いた電界効果型トランジスタ(FET)が提案されている(例えば、特許文献1参照。)。

#### 【0005】

しかしながら、材料や構成の研究開発が進む一方で、有機半導体材料に適した加工方法は未だ確立されていないのが現状である。なお、有機半導体材料のパターニングに無機半導体材料のパターニング方法をそのまま使うことは以下の理由から難しい。

(a) 有機材料は無機材料に比べて物理的、化学的にダメージを受けやすい。そのため、エッキングや、エッキング後のレジスト除去時にダメージを受けやすく、材料の劣化を抑えることが困難である。

(b) 無機材料のパターニングに使われるレジスト剤は有機系材料であり、パターニングしたい有機材料によっては、レジスト剤塗布時にレジスト剤の溶媒によってダメージを受けるおそれがある。

#### 【0006】

また、有機EL素子を製造する例として、有機エレクトロルミネッセンス(EL)材料のパターニング方法が提案されている(例えば、特許文献2参照。)。

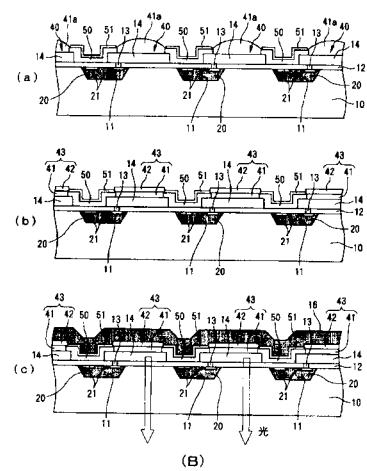

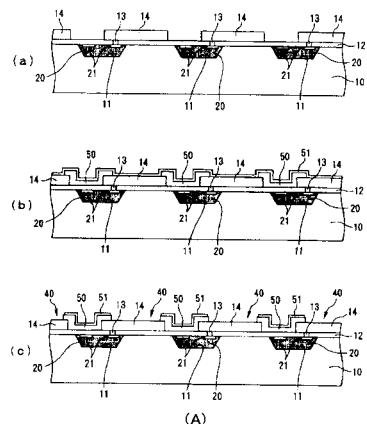

この提案における有機EL材料のパターニング方法、すなわち図1(A)、(B)[(A)：特許文献2の図1に該当、(B)：特許文献2の図2に該当]の模式図に示される工程によれば、まず、透明基板10に駆動回路を含む微細構造物20を埋め込み、保護薄膜12を形成した後、親液性の透明電極14を形成する[(A)-(a)]。次いで、透明基板10の表面全体をシリコン酸化膜などの親液性の材料からなる絶縁膜で覆った後にそれをパターニングすることにより、透明電極14が形成されていない領域、すなわち保護薄膜12が露出している領域を絶縁膜50で覆う。これを、ヘプタデカフルオロテトラヒドロデシルトリエトキシシランとともに密閉容器に入れて96時間室温で放置することで、透明基板10の表面全体を撥液性の膜51を形成する[(A)-(b)]。次に、透明基板10の表面に、マスクを介して紫外線を選択的に照射することにより、撥液性膜51のうち、画素形成領域40の部分の撥液性膜を分解除去する[(A)-(c)]。次いで、インクジェット方式によって正孔注入材料41aを画素形成領域40に塗布し、乾燥させることで正孔注入層41を形成する[(B)-(a)]。同様にして有機EL層42を形成して発光層43を形成する[(B)-(b)]。最後に陰極層16を形成して有機EL素子が完成する[(B)-(c)]。

#### 【0007】

上記方法によれば、ダメージを与えることなく有機材料をパターニングすることが可能となるが、撥液性膜の形成に長時間を要するため実用的とは言えない。また、パターニング時に含フッ素有機膜を分解して除去しているが、含フッ素有機膜は分解によって有害な分解ガスを発生するので、安全性、環境の面で好ましくないという難点がある。

#### 【0008】

また、有機半導体材料を用いてパターニングを行う別の例が提案されている(例えば、特許文献3参照。)。

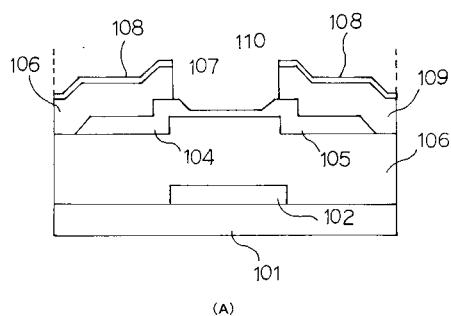

この提案における有機半導体材料のパターニング方法、すなわち図2(A)、(B)[(A)：参考文献の図5に該当、(B)：参考文献の図6に該当]の模式図に示される工程によれば、下記のようにして半導体のパターニングを行っている。

10

20

30

40

50

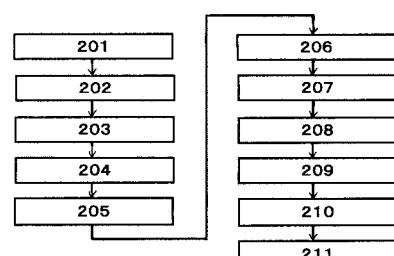

(1) ガラス基板 101 上に CrMo 膜をスパッタリング法により形成する(工程 201)。

(2) ホトリソ工程により CrMo 膜をパターン化してゲート電極 102 を形成する(工程 202)。

(3) ゲート電極 102 を形成したガラス基板 101 上に CVD 法により、酸化シリコン(SiO<sub>2</sub>)膜のゲート絶縁膜 103 を形成する(工程 203)。

(4) ホトリソ工程により、SiO<sub>2</sub>膜にゲート電極取り出し用穴 109 を形成する(工程 204)。

(5) その上にスパッタ法を用いて、CrMo 膜を形成し、ホトリソ工程によりパターン化して、ソース電極 104、ドレイン電極 105 を形成する(工程 205、206)。 10

(6) その上に蒸着法を用いて形成した Au 膜をホトリソ工程によりパターン化して、ソース電極 104、ドレイン電極 105 を形成する。ここで CrMo 膜は Au 膜と SiO<sub>2</sub>膜の密着性を向上させるために用いている(工程 207、208)。

(7) その上に、CVD 法を用いて、厚さ 500 nm の窒化シリコン(SiNx)膜 106 を形成する(工程 209)。

(8) ホトリソ工程により SiNx 膜の一部 110 を除去する(工程 210)。

(9) その上に有機半導体膜 107 および 108 を真空蒸着法により形成する(工程 211)。

#### 【0009】

しかし、上記方法によれば、ダメージを与えることなく有機材料をパターンングすることが可能となるが、CVD 法による窒化シリコン(SiNx)膜の形成に時間がかかり、実用的でないという問題がある。 20

#### 【0010】

【特許文献 1】特開平 7 - 86600 号公報

【特許文献 2】特開 2002 - 15866 号公報

【特許文献 3】特開 2000 - 269504 号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

本発明は、上記従来技術に鑑みてなされたものであり、FET 構造を有する素子の半導体層を、製造工程が簡便で、高速、かつメンテナンス性よく、しかも有機半導体材料にダメージを与えることなく任意のパターン形状で形成できるパターン形成方法と、それにより得られる電子素子、それをアレイ化した電子素子アレイ、および電子素子アレイを備えた表示装置を提供することを目的とする。 30

#### 【課題を解決するための手段】

#### 【0012】

本発明者らは銳意検討した結果、基板上に対向形成されたソース電極およびドレイン電極の形成領域における臨界表面張力よりも該領域以外の臨界表面張力を小さく低表面エネルギーとなるように制御し、各電極間に半導体材料を含有する溶液を付与して半導体層を形成すると所望のパターンが得られ、上記課題が解決されることを見出し本発明に至った。以下、本発明について具体的に説明する。 40

#### 【0013】

すなわち、本発明は、基板上に直接またはゲート絶縁層を介してソース電極およびドレイン電極を適宜の間隔で対向形成し、該ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層を形成する工程を有する、FET 構造からなる半導体層のパターン形成方法であって、

前記ソース電極およびドレイン電極形成領域以外のゲート絶縁層または基板の各臨界表面張力は、該ソース電極およびドレイン電極の形成領域における各臨界表面張力よりも小さい低表面エネルギーであることを特徴とする半導体層のパターン形成方法である。

#### 【0014】

また、本発明は、基板上に、少なくとも臨界表面張力の小さい低表面エネルギーのゲート絶縁層を設け、所定のゲート絶縁層上に臨界表面張力の大きな高表面エネルギーのソース電極およびドレイン電極を適宜の間隔で対向形成し、該ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層を形成する工程を有する、FET構造からなる半導体層のパターン形成方法である。

【0015】

ここで、上記いずれかのパターン形成方法において、前記ソース電極およびドレイン電極の形成領域以外のゲート絶縁層または基板の臨界表面張力に比べて、10 mN/m以上臨界表面張力が大きいソース電極およびドレイン電極を形成する工程を含むことが好適である。

10

【0016】

また、上記いずれかのパターン形成方法において、前記ソース電極およびドレイン電極に挟持された低表面エネルギーのゲート絶縁層または基板の間隔が、該ソース電極およびドレイン電極の各幅よりも小さくなるように各電極を形成する工程を含むことが好ましい。

【0017】

さらに、上記いずれかのパターン形成方法において、前記ソース電極およびドレイン電極に挟持されたゲート絶縁層または基板の臨界表面張力が、該各電極に挟持されていないゲート絶縁層または基板の臨界表面張力の値よりも大きくなるように作製する工程を含むことが望ましい。

20

【0018】

そして、上記いずれかのパターン形成方法において、前記ゲート絶縁層は、エネルギーの付加によって臨界表面張力が変化する材料からなることが好ましい。

【0019】

また、上記いずれかのパターン形成方法において、前記ゲート絶縁層は、少なくとも第一の材料と第二の材料とからなり、該第一の材料は第二の材料と比較してエネルギーの付加によって臨界表面張力が大きく変化する材料であり、該第二の材料は第一の材料とは別の性能を補完する機能を有する材料であり、

かつ、前記第一の材料と第二の材料はゲート絶縁層厚方向に濃度分布を有し、最表層部における第一の材料の濃度が第二の材料の濃度よりも高いことが望ましい。

30

【0020】

上記パターン形成方法において、前記第二の材料は、第一の材料と比較して電気絶縁性の高い材料であることが好ましい。

【0021】

上記パターン形成方法において、前記第二の材料は、第一の材料と比較して高比誘電率の材料であることが好ましい。

【0022】

また、上記いずれかのパターン形成方法において、前記エネルギー付加が紫外線照射により行われ、ゲート絶縁層の臨界表面張力を変化させて低表面エネルギー領域を形成することが望ましい。

40

【0023】

さらに、前記いずれかのパターン形成方法において、前記ゲート絶縁層は、側鎖に疎水性基を有する高分子材料からなることが好ましい。

【0024】

上記パターン形成方法において、前記側鎖に疎水性基を有する高分子材料は、ポリイミド構造を有する材料からなることが好適である。

【0025】

また、前記いずれかのパターン形成方法において、前記半導体層は、有機半導体からなることが好ましい。

【0026】

50

さらに、前記いずれかのパターン形成方法において、前記ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与する方法が、インクジェット法であることが好適である。

#### 【0027】

そして、本発明は、前記いずれかの半導体層のパターン形成方法により半導体層がパターニングされたことを特徴とする電子素子に係るものである。

#### 【0028】

さらに、本発明は、上記の電子素子が絶縁性基板上に複数形成されたことを特徴とする電子素子アレイに係るものである。

ここで、上記絶縁性基板が、臨界表面張力の小さい低表面エネルギー領域を有するゲート絶縁層を兼ねることが好ましい。 10

#### 【0029】

また、本発明は、上記いずれかに記載の電子素子アレイを備えたことを特徴とする表示装置係るものである。

#### 【発明の効果】

#### 【0030】

本発明によれば、FET構造を有する素子の半導体層を、製造工程が簡便で、高速、かつメンテナンス性よく、有機半導体材料にダメージを与えることなく任意のパターン形状で容易に、しかも確実に形成できるパターン形成方法が提供できる。そして、この製造方法によって容易に、電気特性、誘電特性など性能の良好な電子素子が得られる。また、この電子素子を用いれば、簡便で容易に低コストで電子素子アレイが提供でき、さらにこの電子素子アレイを使用することによって容易に安価な表示装置を提供することが可能になる。 20

#### 【発明を実施するための最良の形態】

#### 【0031】

前述のように本発明は、電界効果型トランジスタ(FET)構造を有する素子における半導体層のパターン形成方法に関するものであり、基板上に適宜の間隔で対向形成されたソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層を形成する工程を有する。その際、ソース電極およびドレイン電極は、ゲート絶縁層を介して形成されるか、または基板上に直接形成され、さらに、該ソース電極およびドレイン電極形成領域以外のゲート絶縁層または基板の各臨界表面張力は、該ソース電極およびドレイン電極の形成領域における各臨界表面張力よりも小さい低表面エネルギーに制御されることを特徴とするものである。 30

なお、本発明における臨界表面張力の大小、すなわち表面エネルギーの高低は相対的なものであり、後述のようにその差が10mN/m以上であることが好適である。

#### 【0032】

また本発明は、半導体層のパターン形成方法における特定の形態に関するものであり、基板上に、少なくとも臨界表面張力の小さい低表面エネルギーのゲート絶縁層を設け、所定のゲート絶縁層上に臨界表面張力の大きな高表面エネルギーのソース電極およびドレイン電極を適宜の間隔で対向形成し、各電極間に半導体材料を含有する溶液を付与してパターン化された半導体層を形成する工程を有することを特徴とするものである。 40

以下、本発明の好適な形態について図を参照して説明する。

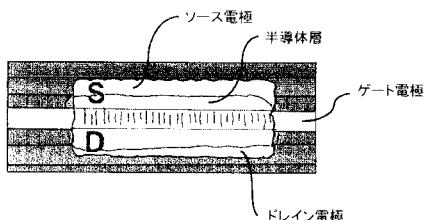

#### 【0033】

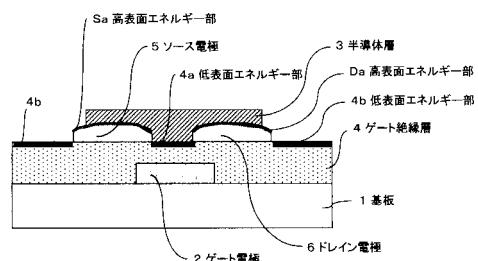

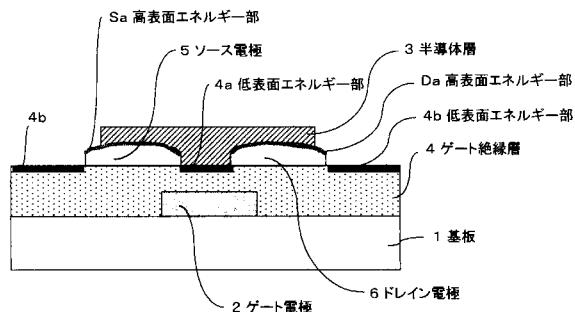

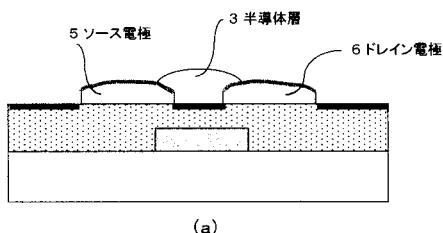

図3は、本発明を実施するのに好適なトランジスタ素子の構成例を示す概略断面図である。図3において、基板1上にゲート電極2が設けられ、その上にゲート絶縁層4が形成されている。ゲート絶縁層4上にソース電極5およびドレイン電極6が間隔を設けて対向形成されている。

この構成において、ソース電極5およびドレイン電極6の表面は、それぞれ臨界表面張力の大きい高表面エネルギー部Sa、Daとされ、一方、該各電極間のゲート絶縁層4の表面、および各電極が形成されている領域以外のゲート絶縁層4の表面は、それぞれ臨界 50

表面張力の小さい低表面エネルギー部 4 a、4 b となるように制御されて形成されている。

**【 0 0 3 4 】**

上記構成とされたソース電極 5 およびドレイン電極 6 間に、半導体材料を含有する溶液を付与した場合、ソース電極 5 およびドレイン電極 6 がバンク、いわゆる堤防となり、ゲート絶縁層 4 の低表面エネルギー部 4 b に半導体層が形成されることはなく、図 3 に示したようなパターン化された半導体層 3 が形成された素子を得ることができる。

**【 0 0 3 5 】**

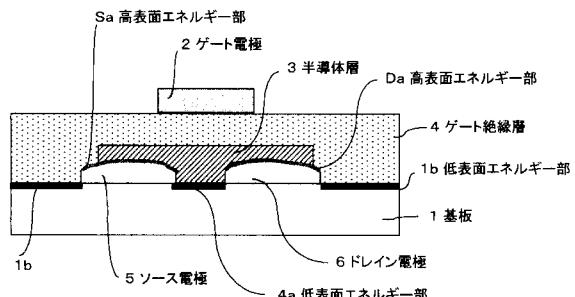

さらに、本発明を実施するのに好適なトランジスタ素子の別の構成例を図 4 の概略断面図に示す。

図 4において、基板 1 上にソース電極 5 およびドレイン電極 6 が間隔を設けて対向形成されている。ソース電極 5 およびドレイン電極 6 の表面はそれぞれ臨界表面張力の大きい高表面エネルギー部 S a、D a とされ、一方、該各電極間の基板 1 の表面、および各電極が形成されている領域以外の基板 1 の表面は、それぞれ臨界表面張力の小さい低表面エネルギー部 1 a、1 b となるように制御されて形成されている。

**【 0 0 3 6 】**

上記構成とされたソース電極 5 およびドレイン電極 6 間に、半導体材料を含有する溶液を付与した場合、ソース電極 5 およびドレイン電極 6 がバンク、いわゆる堤防となり、基板 1 の低表面エネルギー部 1 b に半導体層が形成されることはなく、図 4 に示したようなパターン化された半導体層 3 が形成される。半導体層 3 が形成された後、ゲート絶縁層 4 およびゲート電極 2 を形成して素子を得ることができる。

**【 0 0 3 7 】**

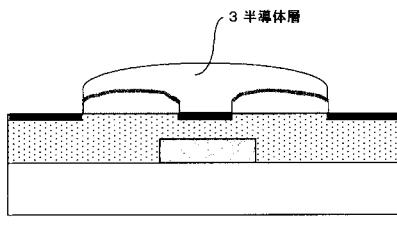

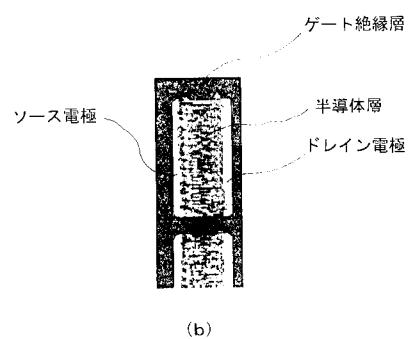

なお、半導体層 3 の形状は、前記図 3 や図 4 に示されるような断面形状である必要はなく、半導体層 3 の各パターンが分離独立し、チャネルが形成される部位に半導体層が形成された形状であればよい。半導体層の他の形状例を図 5 ( a )、( b ) に示す。

**【 0 0 3 8 】**

上記発明によれば、FET 構造を有する素子の半導体層を、有機半導体材料にダメージを与えることなく任意のパターン形状で容易に形成することができる。このような製造方法は、工程が簡便で、かつ高速に製造できメンテナンス性もよい。

**【 0 0 3 9 】**

また本発明は、前記図 3 または 4 に示したソース電極 5 およびドレイン電極 6 の形成領域以外のゲート絶縁層 4 または基板 1 の臨界表面張力に比べて、10 mN / m 以上臨界表面張力が大きいソース電極 5 およびドレイン電極 6 を形成する工程を含むことを特徴とするものである。

半導体材料を含有する液体をチャネル部にのみ確実に付着させるためには、前述のように、ソース電極 5 およびドレイン電極 6 の高表面エネルギー部とゲート絶縁層 4 または基板 1 の低表面エネルギー部の、いわゆるの臨界表面張力差の大きいことが必要であるが、この差を 10 mN / m 以上とすることにより、所定の場所に確実に半導体材料を含有する溶液を付着させ半導体層のパターン形成を行うことができる。

**【 0 0 4 0 】**

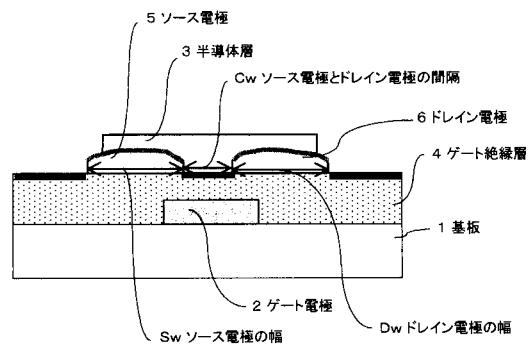

さらに本発明は、図 6 の概略断面図に示す構成を一例とすると、ソース電極 5 およびドレイン電極 6 に挟持された低表面エネルギーのゲート絶縁層 4 の間隔 C w が、ソース電極の幅 S w およびドレイン電極の幅 D w よりも小さくなるように各電極を形成する工程を含むことを特徴とするものである。

なお、図 6 ではゲート絶縁層 4 上にソース電極 5 およびドレイン電極 6 を設ける場合を示しているが、前述の図 4 のようにソース電極 5 およびドレイン電極 6 が直接基板 1 上に形成される場合も同様である。

**【 0 0 4 1 】**

上記のように構成すると、ソース電極の幅 S w およびドレイン電極の幅 D w に比較して、ゲート絶縁層 4 の間隔 C w、すなわちチャネル長が小さく、ゲート絶縁層 4 の低表面工

10

20

30

40

50

エネルギーとソース電極 5 およびドレイン電極 6 の高表面エネルギーとの差に基づきプロッキングが有効に働くため、半導体層のパターニングが良好に行われる。

#### 【 0 0 4 2 】

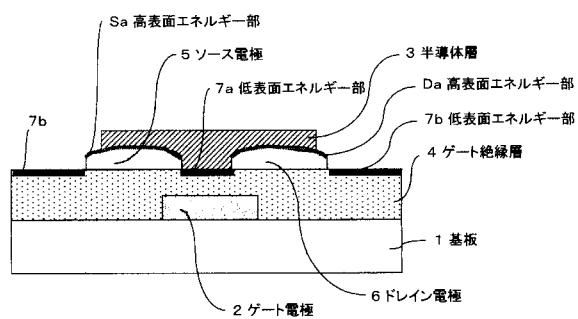

そして本発明は、図 7 の概略断面図に示す構成を一例とすると、ソース電極 5 およびドレイン電極 6 に挟持されたゲート絶縁層 4 の低表面エネルギー部 7 a の臨界表面張力が、ソース電極 5 およびドレイン電極 6 に挟持されていないゲート絶縁層 4 の低表面エネルギー部 7 b における臨界表面張力の値よりも大きくなるように作製する工程を含むことを特徴とするものである。

このような構成とすることにより、各電極に挟持されたゲート絶縁層 4 の表面エネルギーとソース電極 5 およびドレイン電極 6 の表面エネルギーとの差が少なくなり、各電極の臨界表面張力に近い値となり、密着性が良い半導体層を形成することができる。したがって、各パターン形成箇所における連続的な半導体層が形成され、その結果性能の良好な電子素子が提供される。

#### 【 0 0 4 3 】

図 8 ( a ) および ( b ) は、前記図 7 において、ゲート絶縁層 4 の低表面エネルギー部 7 a の臨界表面張力と、ソース電極 5 およびドレイン電極 6 の高表面エネルギー部 S a 、 D a の臨界表面張力との差を変化させ、半導体層を形成した場合の外観状態を示す俯瞰図である。

図 8 ( a ) は、低表面エネルギー部 7 a と高表面エネルギー部 S a 、 D a との差が大きい場合について、各電極間に半導体材料を含有する液体を付与して半導体層を形成した素子の俯瞰図である。半導体層の付着していないところが見受けられ、パターニングができていないことが分かる。

#### 【 0 0 4 4 】

一方、図 8 ( b ) は、低表面エネルギー部 7 a と高表面エネルギー部 S a 、 D a との差がより少ない場合について、各電極間に半導体材料を含有する液体を付与して半導体層を形成した素子の俯瞰図である。半導体層の良好なパターニングができていることが分かる。

#### 【 0 0 4 5 】

また本発明は、前記ゲート絶縁層が、エネルギーの付加によって臨界表面張力が変化する材料からなることを特徴とするものである。

臨界表面張力が変化する材料を用いることによって、エネルギーの付加によりゲート絶縁層表面に前述のような低表面エネルギー部を容易に形成することが可能となり、確実に半導体層のパターンが形成できる。

本発明に用いることのできるこのようなゲート絶縁層用材料としては、限定するものではないが、例えば、パラキシリレン、ブルランおよびその誘導体、ポリビニルフェノールなどが挙げられる。

#### 【 0 0 4 6 】

そして本発明は、前記ゲート絶縁層が、少なくとも第一の材料と第二の材料とからなるものである。そして、第一の材料は第二の材料と比較してエネルギーの付加によって臨界表面張力が大きく変化する材料であり、第二の材料は第一の材料とは別の性能を補完する機能を有する材料であると共に、第一の材料と第二の材料はゲート絶縁層厚方向に濃度分布を有し、最表層部における第一の材料の濃度が第二の材料の濃度よりも高いことを特徴とするものである。

#### 【 0 0 4 7 】

上記においてさらに望ましくは、最表層部における第一の材料濃度は 100 % に近いことが好ましい。このようにすると、臨界表面張力の制御、すなわち濡れ性変化機能を確実に発現することが可能となる。

上記のような構成とすることによって、確実に低表面エネルギー部を作製することができる、容易に半導体層のパターン形成を行うことができる。

#### 【 0 0 4 8 】

10

20

30

40

50

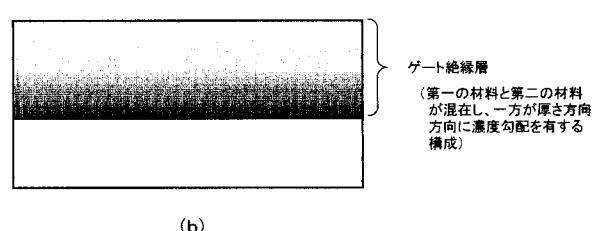

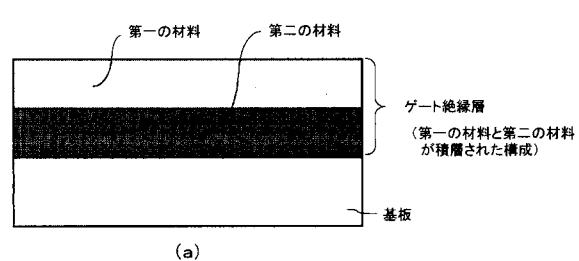

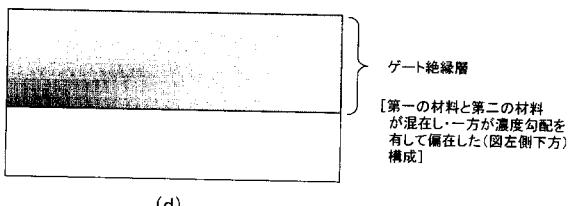

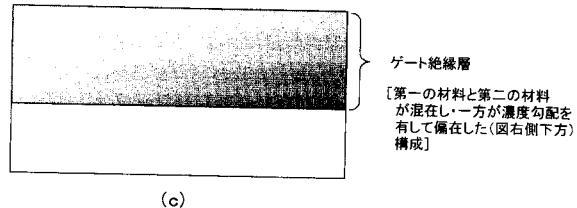

上記第一の材料と第二の材料の構成例を図9( a )、( b )の断面模式図に示す。

図9( a )に示す構造は、第一の材料からなる層を作製した後に第二の材料からなる層を順次積層して作製することが可能である。各層の作製方法としては、真空蒸着などの真空プロセスを用いることも可能であるし、溶液を用いた塗布プロセスを使用することも可能である。

#### 【 0 0 4 9 】

一方、図9( b )は、第一と第二の材料が混在し、厚さ方向に偏り無く濃度勾配を有する構成を示す。このような構造を得るためにプロセスとしては、第一の材料と第二の材料を混合した溶液を基板に塗布、乾燥する方法が挙げられる。

この方法は、第一の材料の極性が第二の材料と比較して小さい場合、または第一の材料の分子量が小さい場合などに適用される。すなわち、乾燥時に溶媒が蒸発するまでの間に第一の材料が表面側に移行し、表面側に濃度の高い分布を有する状態で層を形成することができる場合である。

#### 【 0 0 5 0 】

なお、塗布プロセスを用いた場合は、図9( b )に示したように、第一の材料からなる層と第二の材料からなる層は、界面によって明確に分離できない場合が多いが、本発明においては、最表層部における第一の材料濃度が第二の材料濃度よりも高ければ適用できる。

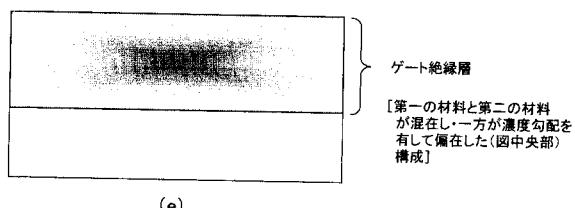

また、図10( c )～( e )の断面模式図に示したように、膜厚方向に対して所定の濃度分布で前記第一および第二の材料が混在・偏在していてもよい。なお、臨界表面張力が変化する構成とされたゲート絶縁層(濡れ変化材料層)が3種類以上の材料から構成されている場合は、3層以上の積層構造からなっていても構わないし、層構造を持たずには膜厚方向に対して所定の濃度分布で材料が混在していてもよい。

#### 【 0 0 5 1 】

また本発明は、前記第二の材料が、第一の材料と比較して電気絶縁性の高い材料であることを特徴とするものである。

このような材料構成とすることによって、電気絶縁性が高く確実に低表面エネルギー部を作製可能なゲート絶縁層が提供できるとともに、微細な導電層パターンを容易に形成することができる。

#### 【 0 0 5 2 】

上記において、電気絶縁性に優れた第二の材料とエネルギーの付加によって臨界表面張力が大きく変化する第一の材料の組成割合(第二の材料/第一の材料)は、重量比で50/50～99/1である。

上記組成割合における第一の材料の重量比が増加するにつれて、ゲート絶縁層(濡れ変化材料層)の電気絶縁性が低くなり、50を超えると電子素子の絶縁層としては不向きとなる。一方、第一の材料の重量比が減少し、1未満になると濡れ性変化が小さくなるため、導電層のパターニングが良好でなくなる。そのため、両者の混合比は、望ましくは60/40～95/5、さらに望ましくは70/30～90/10である。また、本発明におけるゲート絶縁層(濡れ変化材料層)の体積固有抵抗値は、 $1 \times 10^{12}$  cm前後からそれ以上であることが好ましい。

#### 【 0 0 5 3 】

さらに本発明は、前記第二の材料が、第一の材料と比較して高比誘電率の材料であることを特徴とするものである。

このような材料構成とすることによって、確実に低表面エネルギー部を作製可能なゲート絶縁層が提供できるとともに、容易に半導体層のパターン形成を行うことが可能となり、また絶縁層全体の比誘電率が大きくなることから、低電圧で駆動可能な素子を提供することができる。本発明における高誘電率とは、無機半導体で用いられている酸化シリコンの比誘電率4.0以上を指す。

#### 【 0 0 5 4 】

そして本発明は、前記ゲート絶縁層が、側鎖に疎水性基を有する高分子材料からなるこ

10

20

30

40

50

とを特徴とするものである。

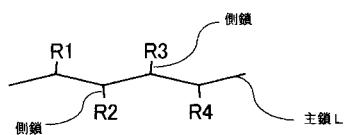

このような側鎖に疎水性基を有する高分子材料を用いることによって、エネルギーを付加して形成される撥水部と親水部の差が大きくなるため、ゲート絶縁層（濡れ変化材料層）上に微細な電極パターンングが施された積層構造体を作製することができ、繊細な半導体層のパターン形成を行うことが可能となる。図11に側鎖に疎水性基を有する高分子材料を説明するための概念図を示す。

#### 【0055】

図11において、Lは、例えば、ポリイミドや（メタ）アクリレート等の骨格を有する高分子材料の主鎖を示し、R1～R4は、主鎖Lに直接あるいは図示しない結合基を介して結合した疎水性基を有する側鎖を示す。なお、R1～R4は、それぞれ同じであっても異なっていてもよい。

#### 【0056】

上記疎水性基としては、末端構造が- $\text{CF}_2\text{CH}_3$ 、- $\text{CF}_2\text{CF}_3$ 、- $\text{CF}(\text{CF}_3)_2$ 、- $\text{C}(\text{CF}_3)_3$ 、- $\text{CF}_2\text{H}$ 、- $\text{CFH}_2$ 等の基が挙げられる。

ここで、分子鎖同士を配向しやすくするためにには、炭素鎖長の長い基が好ましく、炭素数4以上のものがより好ましい。さらには、アルキル基の水素原子の2個以上がフッ素原子に置換されたポリフルオロアルキル基（以下、「Rf基」と記す。）が好ましく、特に炭素数4～20のRf基が好ましく、とりわけ、炭素数6～12のRf基が好ましい。Rf基は直鎖構造であっても分岐構造であってもよいが、直鎖構造の方が好ましい。さらに、疎水性基は、アルキル基の水素原子の実質的に全てがフッ素原子に置換されたパーフルオロアルキル基が好ましい。パーフルオロアルキル基は $\text{C}_n\text{F}_{2n+1}-$ （ただし、nは4～16の整数）で表わされる基が好ましく、特に、nが6～12の整数である場合の該基が好ましい。パーフルオロアルキル基は直鎖構造であっても分岐構造であっても構わないが、直鎖構造が好ましい。

#### 【0057】

上記材料については特開平3-178478号公報等に詳しく記載されて周知であり、加熱状態で液体または固体と接触させたときに親液性となり、空气中で加熱すると疎液性となる性質を有する。すなわち、熱エネルギーの付加によって臨界表面張力を変化させることができる。なお、臨界表面張力は接触媒体の選択によって変化する。

#### 【0058】

さらに、疎水性基としては、フッ素原子を含まない- $\text{CH}_2\text{CH}_3$ 、- $\text{CH}(\text{CH}_3)_2$ 、- $\text{C}(\text{CH}_3)_3$ 等の末端構造を有する基を挙げることができる。

この場合にも、分子鎖同士を配向しやすくするためにには炭素鎖長の長い基が好ましく、炭素数4以上のものがより好ましい。疎水性基は、直鎖構造であっても分岐構造であってもよいが、直鎖構造の方が好ましい。上記アルキル基は、ハロゲン原子、シアノ基、フェニル基、ヒドロキシル基、カルボキシル基または炭素数1～12の直鎖、分岐鎖もしくは環状のアルキル基やアルコキシ基で置換されたフェニル基を含有していてもよい。Rの結合部位が多いほど表面エネルギーが低く（臨界表面張力が小さく）、疎液性になると考えられる。なお、紫外線照射等のエネルギー付加によって結合の一部が切断されるか、あるいは、配向状態が変化するために臨界表面張力が増加し、親液性になるものと推察される。

#### 【0059】

また、ポリイミドや（メタ）アクリレート等の骨格を有する前記図11の主鎖Lに図示しない結合基を介して疎水性基を有する側鎖については、下記文献Aや文献Bに記載されている二種類のポリイミドからなるブロック共重合体やポリメチルメタクリレートを、側鎖に用いることも可能である。

文献A：“Preparation of porous polyimides from selfassembled graft copolymers” E.Y.Lebedeva, B.S.Kesler, K.R.Carter, Polymer Preprint, vol.40(1), pp494-495 (1999).

文献B：“Nanoporous low-k polyimide films prepared from poly(amic acid)s with

10

20

30

40

50

grafted poly(methylmethacrylate)/poly(acrylamide) side chains" G.D.Fu, W.C.Wang, S.Li, E.T.Kang, K.G.Neoh, W.T.Tseng, D.J.Liaw, Journal of Materials Chemistry, vol.13, pp2150-2156 (2003).

### 【0060】

さらに本発明は、前記側鎖に疎水性基を有する高分子材料が、ポリイミド構造を有する材料からなることを特徴とするものである。

ポリイミド構造からなる高分子材料は、電気絶縁性、耐薬品性、耐熱性に優れているため、ゲート絶縁層上に電極層等を形成する際に、溶媒や焼成による温度変化によって、膨潤したりクラックが入るといったことがない。このため、各種性能に優れた低表面エネルギー部が作製可能なゲート絶縁層を提供できるとともに、確実に半導体層のパターン形成を行うことが可能となる。また、絶縁層を2種類以上の材料から構成する場合においては、耐熱性、耐溶剤性、親和性を考慮すると、側鎖に疎水性基を有する高分子材料以外の材料もポリイミドからなることが望ましい。

### 【0061】

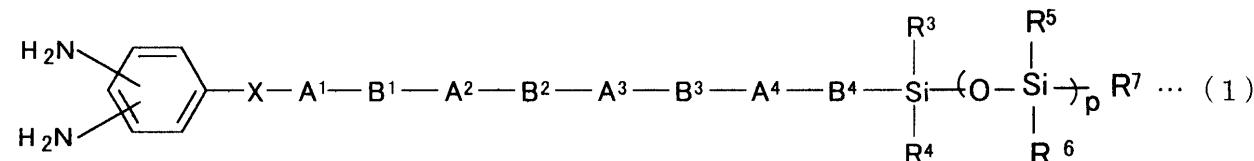

本発明で用いられる側鎖に疎水性基を有するポリイミド構造を有する高分子材料の疎水性基としては、限定するものではないが、例えば、ポリイミドを構成するアミン化合物として下記構造式(1)～(6)で示されるジアミン化合物のいずれかを含むことができる。

### 【0062】

### 【化1】

### 【0063】

上記構造式(1)中、Xは-C H<sub>2</sub>-または-C H<sub>2</sub>C H<sub>2</sub>-であり、A<sup>1</sup>は1,4-シクロヘキシレン、1,4-フェニレンまたは1～4個のフッ素で置換された1,4-フェニレンであり、A<sup>2</sup>、A<sup>3</sup>およびA<sup>4</sup>はそれぞれ独立して単結合、1,4-シクロヘキシレン、1,4-フェニレンまたは1～4個のフッ素で置換された1,4-フェニレンであり、B<sup>1</sup>、B<sup>2</sup>、B<sup>3</sup>はそれぞれ独立して単結合または-C H<sub>2</sub>C H<sub>2</sub>-であり、B<sup>4</sup>は炭素数1～10までのアルキレンであり、R<sup>3</sup>、R<sup>4</sup>、R<sup>5</sup>、R<sup>6</sup>、およびR<sup>7</sup>はそれぞれ独立して炭素数が1～10までのアルキルであり、pは1以上の整数である。

### 【0064】

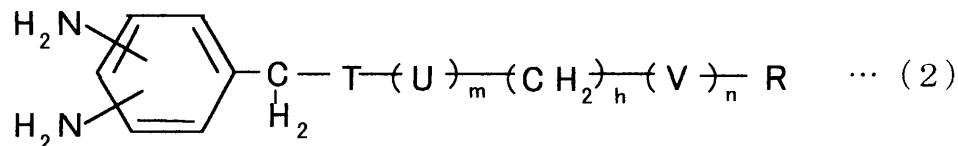

### 【化2】

### 【0065】

上記構造式(2)中、T、UおよびVはそれぞれ独立してベンゼン環またはシクロヘキサン環であり、これら環上の任意のHは炭素数1～3のアルキル、炭素数1～3のフッ素置換アルキル、F、ClまたはCNで置換されていてもよく、mおよびnはそれぞれ独立して0～2の整数であり、hは0～5の整数であり、RはH、F、Cl、CNまたは1価の有機基であり、mが2の場合の2個のUまたはnが2の場合の2個のVはそれぞれ同じ

10

20

30

40

50

でも異なっていてもよい。

【0066】

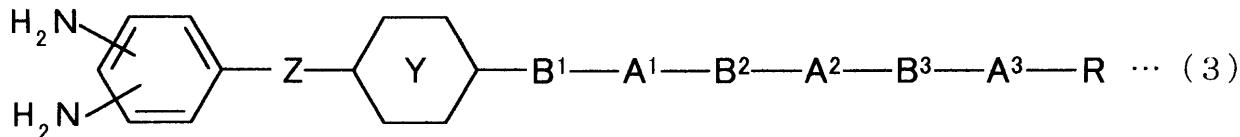

【化3】

10

【0067】

上記構造式(3)中、連結基Zは、 $\text{CH}_2$ 、 $\text{CFH}$ 、 $\text{CF}_2$ 、 $\text{CH}_2\text{CH}_2$ または $\text{CF}_2\text{O}$ であり、環Yは1,4-シクロヘキシレンまたは1~4個のHがFまたは $\text{CH}_3$ で置き換えられてもよい1,4-フェニレンであり、A<sup>1</sup>~A<sup>3</sup>はそれぞれ独立して単結合、1,4-シクロヘキシレンまたは1~4個のHがFまたは $\text{CH}_3$ で置き換えられてもよい1,4-フェニレンであり、B<sup>1</sup>~B<sup>3</sup>はそれぞれ独立して単結合、炭素数1~4のアルキレン、酸素原子、炭素数1~3のオキシアルキレンまたは炭素数1~3のアルキレンオキシであり、RはH、任意の $\text{CH}_2$ が $\text{CF}_2$ で置き換えられてもよい炭素数1~10のアルキル、または1個の $\text{CH}_2$ が $\text{CF}_2$ で置き換えられてもよい炭素数1~9のアルコキシもしくはアルコキシアルキルであり、ベンゼン環に対するアミノ基の結合位置は任意の位置である。ただし、Zが $\text{CH}_2$ である場合には、B<sup>1</sup>~B<sup>3</sup>のすべてが同時に炭素数1~4のアルキレンであることはなく、Zが $\text{CH}_2\text{CH}_2$ であって、環Yが1,4-フェニレンである場合には、A<sup>1</sup>およびA<sup>2</sup>がともに単結合であることはなく、またZが $\text{CF}_2\text{O}$ である場合には、環Yが1,4-シクロヘキシレンであることはない。

20

【0068】

【化4】

30

40

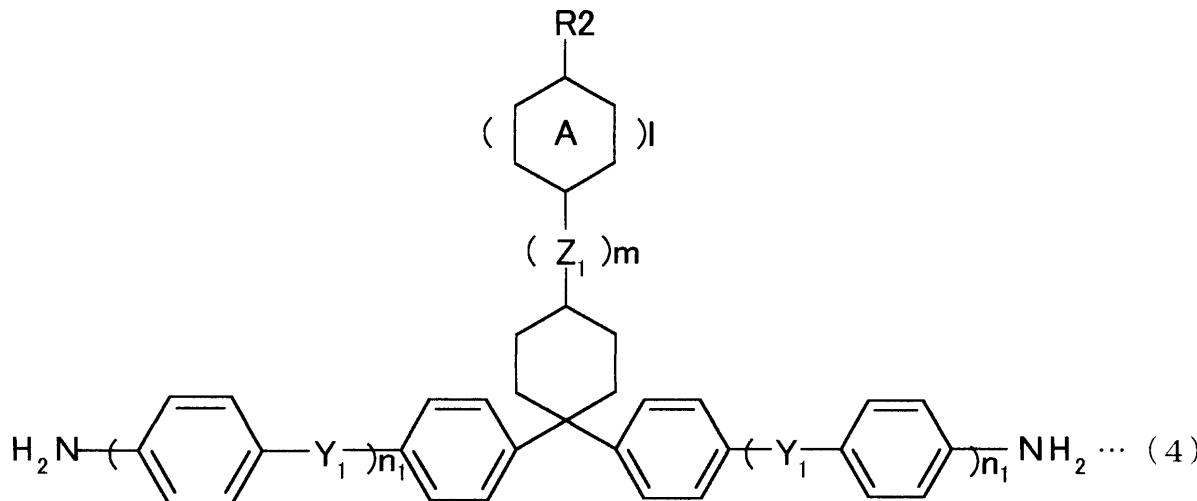

【0069】

上記構造式(4)中、 $R^2$ は水素原子または炭素数1~12のアルキル基であり、 $Z_1$ は $\text{CH}_2$ 基であり、mは0~2であり、環Aはベンゼン環またはシクロヘキサン環であり、1は0または1であり、各 $Y_1$ は独立に酸素原子または $\text{CH}_2$ 基であり、各 $n_1$ は独立に0または1である。

【0070】

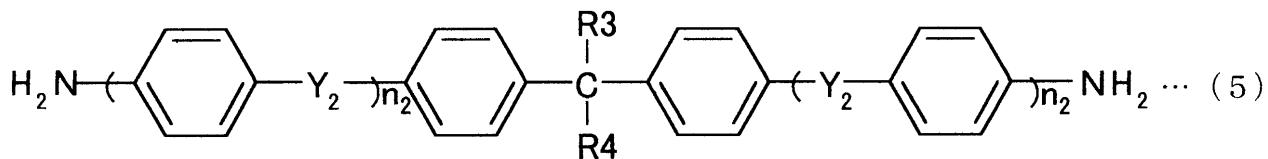

## 【化5】

## 【0071】

10

上記構造式(5)中、各 $\text{Y}_2$ は独立に酸素原子または $\text{CH}_2$ 基であり、 $\text{R}^3$ 、 $\text{R}^4$ は独立に水素原子、炭素数1～12のアルキル基またはパーフルオロアルキル基であり、少なくとも一方は炭素数3以上のアルキル基、またはパーフルオロアルキル基であり、各 $n_2$ は独立に0または1である。

## 【0072】

前記ジアミン化合物については、限定されるものではないが、例えば、特開2002-162630号公報、特開2003-96034号公報、特開2003-267982号公報等に詳しく記載されている。

## 【0073】

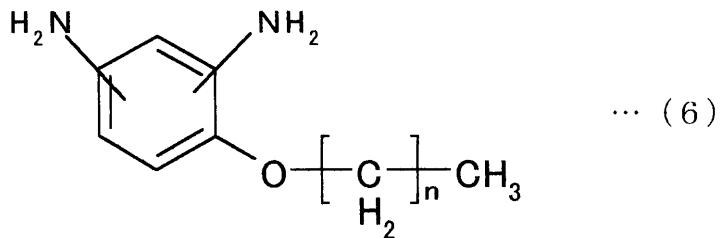

## 【化6】

20

## 【0074】

30

上記構造式(6)中、 $n$ は3～21の整数を示す。なお、溶媒への溶解性を考慮すると5から15が好ましい。

この化合物については、例えば、特開平5-43687号に詳しく記載されている。

## 【0075】

一方、これらのジアミン化合物とともにポリイミドの主鎖骨格を構成するために用いられるテトラカルボン酸二無水物については、脂肪族系、脂環式、芳香族系など種々の材料を用いることが可能である。

## 【0076】

具体的には、限定されるものではないが、ピロメリット酸二無水物、シクロブantanテトラカルボン酸二無水物、ブタンテトラカルボン酸二無水物などである。この他特開平11-193345号公報、特開平11-193346号公報、特開平11-193347号公報等に詳しく記載されている材料についても用いることが可能である。

40

## 【0077】

上記構造式(1)～(6)のジアミンと各種酸二無水物を用いて合成した疎水性基を含むポリイミドは単独で用いてもよいし、他の材料と混合して用いてもよい。ただし、混合して用いる場合は、耐熱性、耐溶剤性、親和性を考慮すると、混合する材料もポリイミド構造を有するものであることが望ましい。

## 【0078】

なお、本実施の形態におけるゲート絶縁層の厚さは30nm～3μmが好ましく、50nm～1μmがさらに好ましい。30nmより薄い場合にはバルク体としての特性(絶縁

50

性、ガスバリア性、防湿性等)が損なわれ、 $3 \mu m$ より厚い場合には表面形状が悪化するため好ましくない。

#### 【0079】

さらに本発明は、前記エネルギー付加が紫外線照射により行われ、ゲート絶縁層の臨界表面張力を変化させて低表面エネルギー領域を形成することを特徴とするものである。

このようにすれば、微細なパターンが容易に形成可能となる。紫外線としては $100 nm$ から $300 nm$ の比較的短い波長の光が含まれるのが望ましい。

#### 【0080】

また本発明は、前記半導体層が、有機半導体からなることを特徴とするものである。

有機半導体とすることにより、ゲート絶縁層と半導体層との界面特性を極めて良好なものとすることができると共に、印刷法等の簡易なプロセスにより容易に半導体層のパターン形成を行うことが可能となる。

#### 【0081】

上記有機半導体材料としては、限定するものではないが、例えば、ペンタセン、アントラセン、テトラセン、フタロシアニンなどの有機低分子、ポリアセチレン系導電性高分子、ポリパラフェニレンおよびその誘導体、ポリフェニレンビニレンおよびその誘導体などのポリフェニレン系導電性高分子、ポリピロールおよびその誘導体、ポリチオフェンおよびその誘導体、ポリフランおよびその誘導体等の複素環系導電性高分子、ポリアニリンおよびその誘導体等の各種イオン性導電性高分子等の有機半導体を用いることができる。

#### 【0082】

そして本発明は、前記ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与する方法が、インクジェット法であることを特徴とするものである。

すなわち、より小さな液滴を供給できるインクジェット法を利用することにより、表面エネルギーの影響を受けやすくすることができ、半導体層の微細なパターンが容易に形成可能となる。また、小さな液滴を必要量供給する方法を適用するので、半導体材料を無駄に使用せずに半導体層のパターン形成を行うことが可能となる。

#### 【0083】

さらに本発明は、前記いずれかに記載の半導体層のパターン形成方法により半導体層がパターニングされた電子素子を提供するものである。

前述のパターン形成方法によれば、製造プロセスが簡便であってかつ高精細なパターニングができるため、良好な特性の電子素子を提供することが可能となる。

#### 【0084】

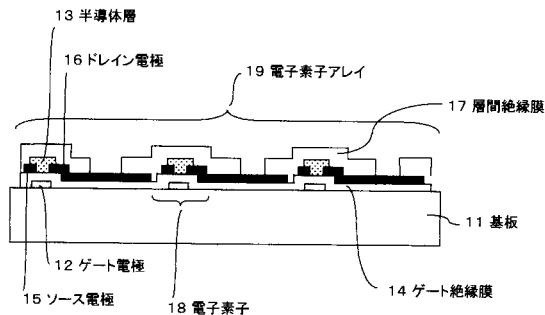

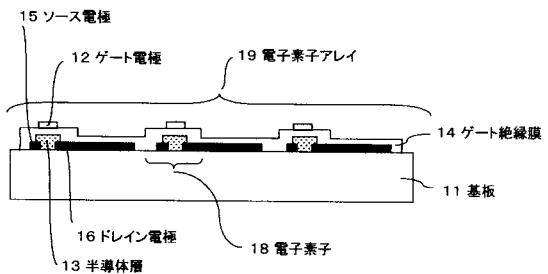

また本発明は、上記電子素子が絶縁性基板上に複数形成された電子素子アレイを提供するものである。

図12は、本発明における電子素子がゲート絶縁膜を介して絶縁性基板上に複数設置される電子素子アレイ(TFTアレイ)の構成例示す概略断面図である。

図12に示すように、電子素子アレイ19は、基板11上にゲート電極12、ゲート絶縁膜14、ソース電極15およびドレイン電極16、半導体層13、層間絶縁膜17が順次設けられてなる電子素子18がそれぞれ2次元的に複数個形成されている。

このような構成の電子素子アレイは簡便、かつ容易に低コストで製作可能であると共に、チャネル領域を含む半導体層13が島状に形成されているので隣接する素子への電流リークが発生せず良好な素子特性を発揮することができる。

#### 【0085】

さらにまた本発明は、前記電子素子アレイの絶縁性基板が、臨界表面張力の小さい低表面エネルギー領域を有するゲート絶縁層を兼ねることを特徴とするものである。

図13は、本発明における電子素子が直接絶縁性基板上に複数設置される電子素子アレイの(TFTアレイ)の構成例を示す概略断面図である。

図13に示すように、電子素子アレイ19は、基板11上に、ソース電極15およびドレイン電極16、半導体層13、ゲート絶縁膜14、ゲート電極12が順次設けられてなる電子素子18がそれぞれ2次元的に複数個形成されている。

10

20

30

40

50

## 【0086】

前記ゲート絶縁膜を介して電子素子を絶縁性基板上に複数設置した場合と同様に、簡便かつ容易に低コストで製作可能であり、チャネル領域を含む半導体層13が島状に形成されているので隣接する素子への電流リークが発生せず良好な素子特性を得ることができる。

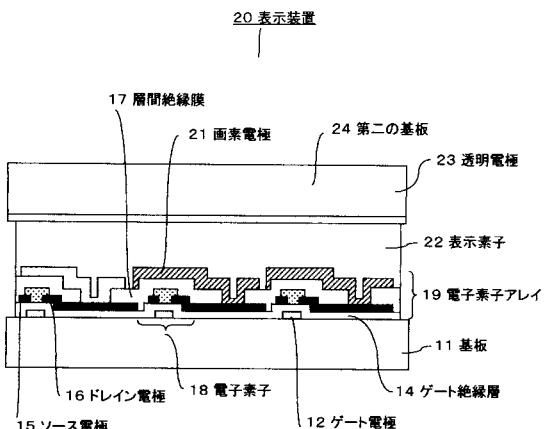

## 【0087】

そして本発明は、前記記載の電子素子アレイを備えた表示装置を提供するものである。上記電子素子アレイを用いれば、容易にしかも安価で表示装置を提供することが可能となる。

図14は、本発明における表示装置の構成例を示す概略断面図である。

10

図14において、前記図12のように構成された電子素子(TFT)アレイ基板11と透明導電膜23を有する第二の基板24との間に表示素子22が設けられ、TFTによって画素電極を兼ねるドレイン電極16上の表示素子がスイッチングされる。

第二の基板24としては、ガラスやポリエステル、ポリカーボネート、ポリアリレート、ポリエーテルスルファン等のプラスチックを用いることができる。表示素子22としては液晶、電気泳動、有機EL等の方式を用いることができる。

## 【0088】

液晶表示素子は、電界駆動であるため消費電力が小さく、また駆動電圧が低いことからTFTの駆動周波数を高くすることができ、大容量表示に適している。液晶表示素子の表示方式として、TN、STN、ゲスト・ホスト型、高分子分散液晶(Polymer-dispersed Liquid Crystal=PDL C)等が挙げられるが、反射型で明るい白色表示が得られる点ではPDL Cが好ましい。

20

## 【0089】

電気泳動表示素子は第一の色(例えば白色)を呈する粒子を第二の色を呈する着色分散媒中に分散した分散液からなるもので、第一の色を呈する粒子は着色分散媒中で帯電することにより、電界の作用で分散媒中における存在位置を変えることができ、それによって呈する色が変化する。この表示方式によれば明るく、視野角の広い表示ができ、また表示メモリー性があるため、特に消費電力の観点から好ましく使用される。

## 【0090】

上記分散液を高分子膜で包んだマイクロカプセルとすることにより、表示動作が安定化するとともに、表示装置の製造が容易になる。

30

マイクロカプセルはコアセルベーション法、In-Situ重合法、界面重合法等公知の方法で製作することができる。白色粒子としては、酸化チタンが特に好適に用いられ、必要に応じて表面処理あるいは他の材料との複合化等が施される。

## 【0091】

分散媒としては、ベンゼン、トルエン、キシレン、ナフテン系炭化水素等の芳香族炭化水素類、ヘキサン、シクロヘキサン、ケロシン、パラフィン系炭化水素等の脂肪族炭化水素類、トリクロロエチレン、テトラクロロエチレン、トリクロロフルオロエチレン、臭化エチル等のハロゲン化炭化水素類、含フッ素エーテル化合物、含フッ素エステル化合物、シリコーンオイル等の抵抗率の高い有機溶媒を使用するのが好ましい。分散媒を着色するためにには、所望の吸収特性を有するアントラキノン類やアゾ化合物類等の油溶性染が用いられる。分散液中には分散安定化のために界面活性剤等を添加してもよい。

40

## 【0092】

有機EL素子は自発光型であるため、鮮やかなフルカラー表示を行うことができる。またEL層は非常に薄い有機薄膜であるので、柔軟性に富み、特にフレキシブルな基板上に形成するのに適している。

## 【実施例】

## 【0093】

以下、実施例を挙げて本発明をさらに具体的に説明するが、本発明はその趣旨を逸脱しない限り下記実施例に限定されるものではない。

50

## 【0094】

## (実施例1)

以下の手順で前記図3に示したのと同様の構成のTFT素子を作製した。

(1) : ガラス基板上に膜厚60nmのAlを真空蒸着し、フォトリソエッティングにより40μmの幅に加工し、ゲート電極を形成した。

(2) : 化学蒸着法(CVD)を用いてポリパラキシリレンのゲート絶縁層を形成した。

(3) : メタルマスクを介してAuを蒸着することで電極幅40μm、電極間隔5μmのソース電極層およびドレイン電極層を形成した。

(4) : パターン形成装置としてインクジェット装置を用意し、このインクジェット装置にポリ3ヘキシルチオフェンのキシレン混合溶液を充填した。 10

(5) : 上記各電極が形成された基板をパターン形成装置にセットした。

(6) : パターン形成装置にパソコンから信号を送信し、ソース電極およびドレイン電極の電極間(チャネル部)が被覆される位置にポリ3ヘキシルチオフェンのキシレン混合溶液を吐出し、面積が約64μm角の半導体パターンを形成した。

(7) : 最後に180°のオーブンで60分加熱して半導体層を形成し、TFT素子を作製した。

なお、上記工程において形成されるソース電極およびドレイン電極形成領域以外のゲート絶縁層の各臨界表面張力は、図3で示したのと同様に各電極の臨界表面張力よりも小さい低表面エネルギーに制御されている。 20

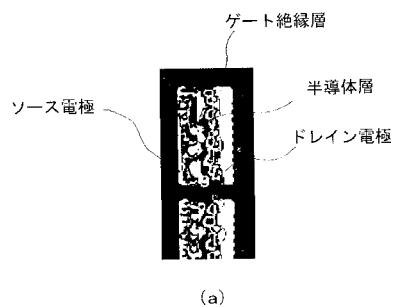

## 【0095】

上記手順によって得られたTFT素子の俯瞰図を図15に示す。図15に示されているように有機半導体材料にダメージを与えることなく所定のパターン形状からなる半導体層が形成されている。

このTFTの移動度は $9.8 \times 10^{-3} \text{ cm}^2/\text{Vs}$ 、On/Off比は650であり、半導体層をスピノコート法で形成する場合に較べて遜色なかった。

## 【0096】

## (実施例2)

以下の手順で前記図12に示したのと同様のTFT素子構造を有するアレイを作製した。

(1) : ガラス基板上に膜厚60nmのAlを真空蒸着し、フォトリソエッティングにより40μmの幅に加工し、ゲート電極を形成した。

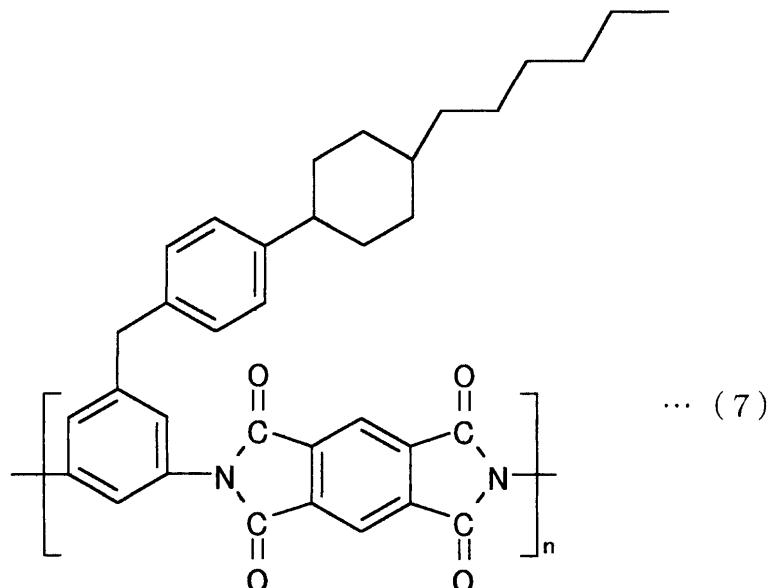

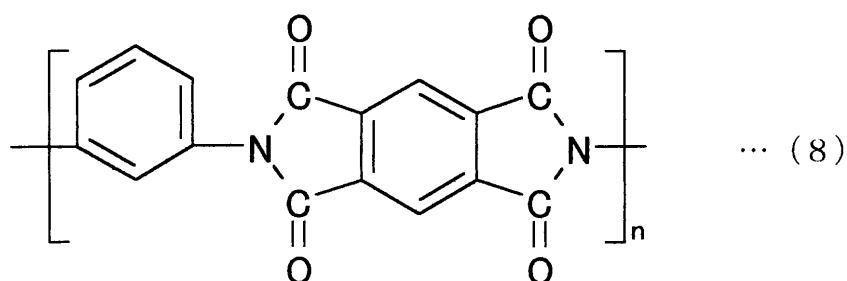

(2) : 加熱処理後に下記構造式(7)および構造式(8)で表されるポリイミド構造体となるポリイミド前駆体を溶解した混合溶液を、スピノコート法にて塗布し250°で加熱処理してゲート絶縁層を作製した。

(3) : 開口幅が40μm、開口部間のスペースが5μmのパターンを施したマスクをゲート絶縁層に圧着し、紫外線を9J/cm<sup>2</sup>の条件で照射した。

## 【0097】

【化7】

20

【0098】

【化8】

【0099】

(4) : インクジェット装置を用いて導電性高分子である P E D O T / P S S (ポリエチレンジオキシチオフェン / ポリエチレンスルfonyl 酸) の水溶液を、ゲート絶縁層の紫外線照射により形成された高表面エネルギー部に付与した。

(5) : 付与された導電性高分子溶液を 200 °C で焼成し、ソースならびにドレイン電極層を形成した。

(6) : 上記各電極が形成された基板をパターン形成装置にセットした。

(7) : パターン形成装置にパソコンから信号を送信し、ソース電極およびドレイン電極の電極間 (チャネル部) が被覆される位置にポリ 3-ヘキシルチオフェンのキシレン混合溶液を吐出し、64 μm 角の半導体パターンを形成した。

(8) : 最後に 180 °C のオーブンで 60 分加熱して半導体層を形成し、TFT 素子構造を有するアレイを作製した。

なお、上記工程において形成されるソース電極およびドレイン電極形成領域以外のゲート絶縁層の各臨界表面張力は、前記図 3 で示したのと同様に各電極の臨界表面張力よりも小さい低表面エネルギーに制御されている。

【0100】

以上の工程により、基板上に 32 × 32 個 (素子間ピッチ 500 μm) の TFT 素子を

40

50

有する電子素子アレイを作製した。TFTの平均的な特性は移動度が $3.5 \times 10^{-3} \text{ cm}^2/\text{V s}$ 、On/Off比が2500であった。

【図面の簡単な説明】

【0101】

【図1】従来技術(特許文献2)におけるEL材料パターニング工程を説明するための模式図[(A):文献図1に該当、(B):文献図2に該当]である。

【図2】従来技術(特許文献3)における有機半導体材料のパターニング工程を説明するための模式図[(A):文献図5に該当、(B):文献図6に該当]である。

【図3】本発明における実施の形態を説明するためのトランジスタ素子の構成例を示す概略断面図である。

10

【図4】本発明における実施の形態を説明するためのトランジスタ素子の別の構成例を示す概略断面図である。

【図5】本発明における実施の形態を説明するための半導体層の他の形状例を示す概略断面図である。

【図6】実施の形態において本発明のトランジスタ素子のソース電極とドレイン電極の間隔と該各電極の幅との関係を説明するための概略断面図である。

【図7】実施の形態において本発明のトランジスタ素子の低表面エネルギー部と高表面エネルギー部との関係を説明するための概略断面図である。

【図8】実施の形態でゲート絶縁層の低表面エネルギー部と各電極の高表面エネルギー部との臨界表面張力の差を変化させて形成した半導体層の外観を示す俯瞰図である。

20

【図9】実施の形態において本発明のゲート絶縁層が第一と第二の材料から構成(a:積層構成、b:混在した構成)される例を説明するための断面模式図である。

【図10】実施の形態において本発明のゲート絶縁層が第一と第二の材料から構成(c~e:混在・偏在した構成)される他の例を説明するための断面模式図である。

【図11】実施の形態において本発明のゲート絶縁層として用いる側鎖に疎水性基を有する高分子材料を説明するための概念図を示す。

【図12】本発明における電子素子がゲート絶縁膜を介して絶縁性基板上に複数設置される電子素子アレイ(TFTアレイ)の構成例を示す概略断面図である。

【図13】本発明における電子素子が直接絶縁性基板上に複数設置される電子素子アレイ(TFTアレイ)の構成例を示す概略断面図である。

30

【図14】本発明における表示装置の構成例を示す概略断面図である。

【図15】実施例1において作製したTFT素子の俯瞰図である。

【符号の説明】

【0102】

- 1 基板

- 2 ゲート電極

- 3 半導体層

- 4 ゲート絶縁層

- 4a 低表面エネルギー部

- 4b 低表面エネルギー部

- 5 ソース電極

- 6 ドレイン電極

- Sa 高表面エネルギー部

- Da 高表面エネルギー部

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(a)

(b)

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 友野 英紀

東京都大田区中馬込1丁目3番6号 株式会社リコー内

(72)発明者 近藤 均

東京都大田区中馬込1丁目3番6号 株式会社リコー内

F ターム(参考) 5F110 AA16 BB01 CC05 CC07 DD02 EE03 EE43 FF01 FF05 FF27

FF29 GG05 GG28 GG29 GG42 HK01 HK02 HK17 HK32 NN02