(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6903469号

(P6903469)

(45) 発行日 令和3年7月14日(2021.7.14)

(24) 登録日 令和3年6月25日(2021.6.25)

(51) Int.Cl.

F 1

|             |               |                  |      |      |      |

|-------------|---------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/20</b>   | <b>(2006.01)</b> | G09G | 3/20 | 622A |

| <b>G09G</b> | <b>3/36</b>   | <b>(2006.01)</b> | G09G | 3/36 |      |

| <b>G09G</b> | <b>3/3233</b> | <b>(2016.01)</b> | G09G | 3/20 | 622E |

| <b>H01L</b> | <b>51/50</b>  | <b>(2006.01)</b> | G09G | 3/20 | 622G |

| <b>H05B</b> | <b>33/14</b>  | <b>(2006.01)</b> | G09G | 3/20 | 622C |

請求項の数 7 (全 84 頁) 最終頁に続く

(21) 出願番号 特願2017-73565 (P2017-73565)

(22) 出願日 平成29年4月3日 (2017.4.3)

(65) 公開番号 特開2017-198978 (P2017-198978A)

(43) 公開日 平成29年11月2日 (2017.11.2)

審査請求日 令和2年4月1日 (2020.4.1)

(31) 優先権主張番号 特願2016-74956 (P2016-74956)

(32) 優先日 平成28年4月4日 (2016.4.4)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(31) 優先権主張番号 特願2016-87359 (P2016-87359)

(32) 優先日 平成28年4月25日 (2016.4.25)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 森 英典

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 福留 貴浩

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 塚本 丈二

最終頁に続く

(54) 【発明の名称】表示装置、表示モジュール、及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲートドライバと、表示部と、選択信号出力回路と、を有する表示装置であつて、

前記表示部は、第1の領域と第2の領域と、を有し、

前記第1の領域は、全面の表示が更新される機能を有し、

前記第2の領域は、部分的に表示が更新される機能を有し、

前記第1の領域および前記第2の領域は、それぞれ画素回路と、走査線と、を有し、

前記画素回路は、表示素子を有し、

前記ゲートドライバは、前記走査線と電気的に接続され、

前記走査線は、前記画素回路と電気的に接続され、

前記第1の領域に含まれる走査線は、第1の走査信号が与えられる機能を有し、

前記第2の領域に含まれる走査線は、第2の走査信号が与えられる機能を有し、

前記選択信号出力回路は、走査線を選択する第1の選択信号および第2の選択信号を出力する機能を有し、

前記第1の選択信号は、選択された前記第1の領域に含まれる走査線に前記第1の走査信号を与える機能を有し、

前記第1の領域に含まれる表示素子は、前記第1の走査信号によって表示が更新される機能を有し、

前記第2の選択信号は、選択された前記第2の領域に含まれる走査線に前記第2の走査信号を与える機能を有し、

10

20

前記第2の領域に含まれる表示素子は、前記第2の走査信号によって表示が更新される機能を有し、

前記第1の領域に含まれる表示素子の表示が更新される頻度は、前記第2の領域に含まれる表示素子の表示が更新される頻度と異なる表示装置。

**【請求項2】**

請求項1において、

前記第1の走査信号は、前記第2の走査信号とは異なる電圧振幅を有する表示装置。

**【請求項3】**

請求項1または請求項2において、

前記選択信号出力回路は、前記第1の選択信号と、前記第2の選択信号を切り替えて出力する機能を有する表示装置。 10

**【請求項4】**

請求項2において、

前記第1の領域は、第1の信号線を有し、

前記第2の領域は、第2の信号線を有し、

前記第1の信号線は、前記第1の領域に含まれる画素回路に、第1の階調信号を与える機能を有し、

前記第2の信号線は、前記第2の領域に含まれる画素回路に、第2の階調信号を与える機能を有し、

前記第1の領域に含まれる表示素子は、第1の階調を表示する機能を有し、 20

前記第2の領域に含まれる表示素子は、第2の階調を表示する機能を有し、

前記第1の領域に含まれる走査線は、第1の電圧および前記第1の電圧より小さい第2の電圧を出力する機能を有し、

前記第2の領域に含まれる走査線は、第3の電圧および前記第3の電圧より小さい第4の電圧を出力する機能を有し、

前記第1の階調信号により生成された最大電圧は、前記第1の電圧よりも小さい電圧であり、

前記第1の階調信号により生成された最小電圧は、前記第2の電圧よりも大きい電圧であり、

前記第2の階調信号により生成された最大電圧は、前記第3の電圧よりも小さい電圧であり、 30

前記第2の階調信号により生成された最小電圧は、前記第4の電圧よりも大きい電圧であり、

前記第1の階調信号により生成された最大電圧は、前記第2の階調信号により生成された最大電圧よりも大きい電圧であり、

前記第1の階調信号により生成された最小電圧は、前記第2の階調信号により生成された最小電圧よりも小さい電圧である表示装置。

**【請求項5】**

請求項1乃至4のいずれか一において、

前記第1の領域に含まれる表示素子は、液晶素子を有し、 40

前記第2の領域に含まれる表示素子は、自発光素子を有する表示装置。

**【請求項6】**

請求項1乃至5のいずれか一の表示装置と、

タッチセンサと、

を有する表示モジュール。

**【請求項7】**

請求項1乃至5のいずれか一の表示装置、または請求項6の表示モジュールと、操作キーまたはバッテリと、

を有する電子機器。

**【発明の詳細な説明】**

**【技術分野】****【0001】**

本発明の一態様は、表示装置、表示モジュール、及び電子機器に関する。

**【0002】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、またはそれらの製造方法に関する。

**【背景技術】**

10

**【0003】**

スマートフォン、タブレット等のモバイル機器が普及している。モバイル機器は、屋外環境や室内環境など利用する環境の明るさに適した表示をすることが求められている。

**【0004】**

自然光や室内照明光など、十分な明るさの光がある環境では反射光を利用した表示を行い、十分な明るさを得られない環境では発光素子を利用した表示を行う表示装置が開示されている。

**【0005】**

例えば特許文献1乃至3では、1つの画素に、液晶素子を制御する画素回路と、発光素子を制御する画素回路とが設けられている、ハイブリッド（複合型）表示装置が開示されている。

20

**【先行技術文献】****【特許文献】****【0006】****【特許文献1】**米国特許出願公開第2003/0107688号明細書**【特許文献2】**国際公開第2007/041150号公報**【特許文献3】**特開2008-225381号公報**【発明の概要】****【発明が解決しようとする課題】****【0007】**

30

外光を利用して表示を行う方法として、反射型液晶表示装置がある。反射型液晶表示装置ではバックライトを必要としないため低消費電力であるが、明るい外光が得られる場所でないと良好な表示を行えない。EL（Electroluminescence）素子は自発光素子であるため、発光表示装置は暗い場所で良好な表示ができる一方、明るい場所では、視認性が低下してしまう。特許文献1乃至3で開示されるハイブリッド表示装置は、反射型液晶表示装置と発光表示装置の特長が生かされており、使用場所の明るさによらず使用することができる。

**【0008】**

液晶素子と発光素子とでは光学的な応答速度が異なる。そのため表示内容に応じた所望の表示品質を得ることが難しかった。さらに階調信号が逐次更新されるため、消費電力の低減を図ることが難しかった。

40

**【0009】**

上記問題に鑑み、本発明の一態様は、表示装置を駆動するための新規な回路により、表示内容に応じた画素回路を選択する方法が最適化された、新規な表示装置等を提供することを課題の一とする。または、本発明の一態様は、表示内容に応じた表示素子の階調信号が更新されることで、表示品質が向上する表示装置等を提供することを課題の一とする。または、本発明の一態様は、表示内容に応じた表示素子の階調信号が更新されることにより消費電力が低減された、新規な構成の表示装置等を提供することを課題の一とする。

**【0010】**

なお本発明の一態様の課題は、上記列挙した課題に限定されない。上記列挙した課題は

50

、他の課題の存在を妨げるものではない。なお他の課題は、以下の記載で述べる、本項目で言及していない課題である。本項目で言及していない課題は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した課題、及び／又は他の課題のうち、少なくとも一つの課題を解決するものである。

**【課題を解決するための手段】**

**【0011】**

本発明の一態様は、ゲートドライバと、表示部と、選択信号出力回路と、を有する表示装置であって、表示部は、第1の領域と第2の領域と、を有し、第1の領域および第2の領域は、それぞれ画素回路と、走査線と、を有し、画素回路は、表示素子を有し、ゲートドライバは、走査線と電気的に接続され、走査線は、画素回路と電気的に接続され、走査線は、第1の走査信号が与えられる機能を有し、選択信号出力回路は、第1の走査信号が与えられる走査線を選択する第1の選択信号を出力する機能を有し、第1の選択信号は、選択された走査線に第1の走査信号を与える機能を有し、表示素子は、第1の走査信号によって表示が更新される機能を有し、第1の領域に含まれる表示素子の表示が更新される頻度は、第2の領域に含まれる表示素子と異なることを特徴とする表示装置である。

**【0012】**

本発明の一態様において、表示素子は、液晶素子を有することを特徴とする表示装置が好ましい。

**【0013】**

本発明の一態様において、表示素子は、自発光素子を有することを特徴とする表示装置が好ましい。

**【0014】**

本発明の一態様は、ゲートドライバと、表示部と、選択信号出力回路と、を有する表示装置であって、表示部は、画素回路と、第1の走査線と、第2の走査線と、を有し、画素回路は、第1の表示素子および第2の表示素子を有し、第1の走査線は、第1の走査信号が与えられる機能を有し、第2の走査線は、第2の走査信号が与えられる機能を有し、ゲートドライバは、シフトレジスタ回路と、選択回路とを有し、シフトレジスタ回路は、出力信号を出力する機能を有し、選択信号出力回路は、第1の選択信号および第2の選択信号を出力する機能を有し、選択回路は、出力信号、第1の選択信号および第2の選択信号により、第1の走査信号および第2の走査信号を生成する機能を有する表示装置である。

**【0015】**

本発明の一態様において、表示部は、第1の信号線と、第2の信号線を有し、第1の信号線は、第1の階調信号が与えられる機能を有し、第2の信号線は、第2の階調信号が与えられる機能を有し、第1の走査信号の電圧振幅は、第1の階調信号の電圧振幅より大きく、選択回路は、出力信号および第2の選択信号により、第2の走査信号を生成し、第2の走査信号の電圧振幅は、第2の階調信号の電圧振幅より大きく、第1の走査信号は、第2の走査信号とは異なる電圧振幅を有する表示装置が好ましい。

**【0016】**

本発明の一態様において、選択信号出力回路は、第1の選択信号と、第2の選択信号を切り替えて出力する機能を有する表示装置が好ましい。

**【0017】**

本発明の一態様は、信号線と、第1の走査線と、第2の走査線と、画素回路とを有する表示装置であって、画素回路は、第1の回路と、第2の回路とを有し、第1の回路は、第1の表示素子を有し、第2の回路は、第2の表示素子を有し、信号線は、第1の回路に第1の階調信号を与える機能を有し、信号線は、第2の回路に第2の階調信号を与える機能を有し、第1の表示素子は、第1の階調を表示する機能を有し、第2の表示素子は、第2の階調を表示する機能を有し、第1の走査線は、第1の電圧および、第1の電圧より小さい第2の電圧を出力する機能を有し、第2の走査線は、第3の電圧および、第3の電圧より小さい第4の電圧を出力する機能を有し、第1の階調信号により生成された最大電圧は

10

20

30

40

50

、第1の電圧よりも小さい電圧であり、第1の階調信号により生成された最小電圧は、第2の電圧よりも大きい電圧であり、第2の階調信号により生成された最大電圧は、第3の電圧よりも小さい電圧であり、第2の階調信号により生成された最小電圧は、第4の電圧よりも大きい電圧であり、第1の階調信号により生成された最大電圧は、第2の階調信号により生成された最大電圧よりも大きい電圧であり、第1の階調信号により生成された最小電圧は、第2の階調信号により生成された最小電圧よりも小さい電圧である。

#### 【0018】

本発明の一態様において、信号線と、第1の電源線と、画素回路とを有する表示装置であって、第1の回路は、第1の表示素子と、第1のトランジスタと、第1の容量素子とを有し、第2の回路は、第2の表示素子と、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、を有し、第1の表示素子は、第1の画素電極と、第1の対向電極とを有し、第2の表示素子は、第2の画素電極と、第2の対向電極とを有し、信号線は、第1のトランジスタのソースまたはドレインの一方に電気的に接続され、第1のトランジスタのソースまたはドレインの他方は、第1の画素電極に電気的に接続され、第1のトランジスタのソースまたはドレインの他方は、第1の容量素子の電極の一方に電気的に接続され、第1の容量素子の電極の他方は、第1の電源線が電気的に接続され、第1の走査線は、第1のトランジスタのゲートに電気的に接続され、信号線は、第2のトランジスタのソースまたはドレインの一方に電気的に接続され、第2のトランジスタのソースまたはドレインの他方は、第3のトランジスタのゲートに電気的に接続され、第3のトランジスタのソースまたはドレインの一方は、第2の画素電極と電気的に接続され、第3のトランジスタのソースまたはドレインの一方は、第4のトランジスタのソースまたはドレインの一方に電気的に接続され、第2の走査線は、第2のトランジスタのゲートに電気的に接続され、第1の電源線と、第4のトランジスタのソースまたはドレインの他方が電気的に接続され、第1の階調信号を、第1のトランジスタを介して、第1の容量素子の電極の一方に与えている期間に、第1の電源線に与えられる電圧を、第4のトランジスタを介して、第2の画素電極に与える機能を有する表示装置が好ましい。

#### 【0019】

上記態様において、第1の表示素子は、液晶素子を有し、第2の表示素子は、自発光素子を有すると好ましい。

#### 【0020】

本発明の一態様において、画素回路は、トランジスタを有し、トランジスタは、チャネル形成領域に酸化物半導体を有する表示装置が好ましい。

#### 【発明の効果】

#### 【0021】

本発明の一態様は、表示装置を駆動するための新規な回路により、表示内容に応じた画素回路を選択する方法が最適化された、新規な表示装置等を提供することができる。または、本発明の一態様は、表示内容に応じた表示素子の階調信号が更新されることにより、表示品質が向上する表示装置等を提供することができる。または、本発明の一態様は、表示内容に応じた表示素子の階調信号が更新されることにより消費電力が低減された、新規な構成の表示装置等を提供することができる。

#### 【0022】

なお本発明の一態様の効果は、上記列挙した効果に限定されない。上記列挙した効果は、他の効果の存在を妨げるものではない。なお他の効果は、以下の記載で述べる、本項目で言及していない効果である。本項目で言及していない効果は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した効果、及びノ又は他の効果のうち、少なくとも一つの効果を有するものである。従って本発明の一態様は、場合によっては、上記列挙した効果を有さない場合もある。

#### 【図面の簡単な説明】

#### 【0023】

10

20

30

40

50

- 【図 1】表示装置の構成を説明するための図。

- 【図 2】画素の構成を説明するための図。

- 【図 3】画素の構成を説明するための図。

- 【図 4】(A)：選択回路のブロック図。(B)：(A)の選択回路のタイミングチャート。

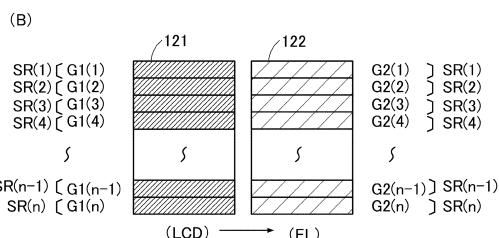

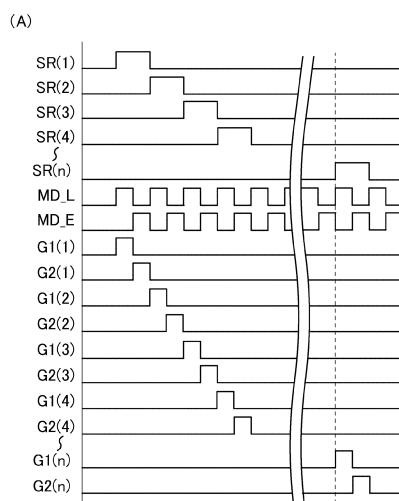

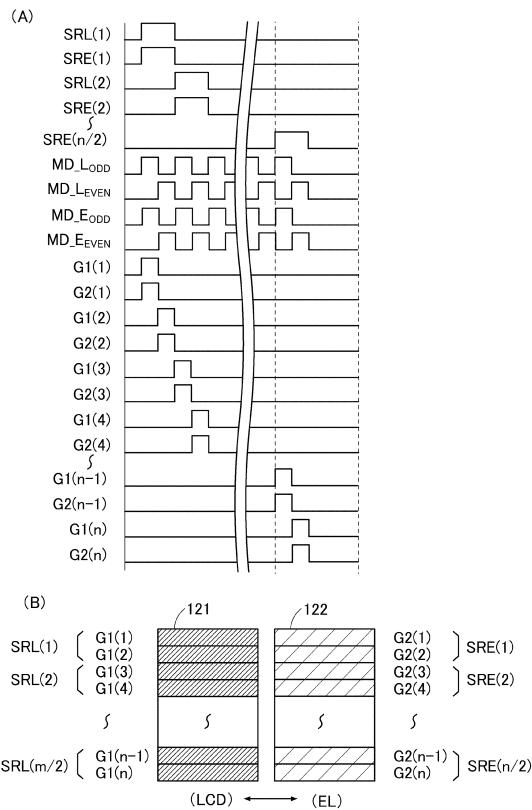

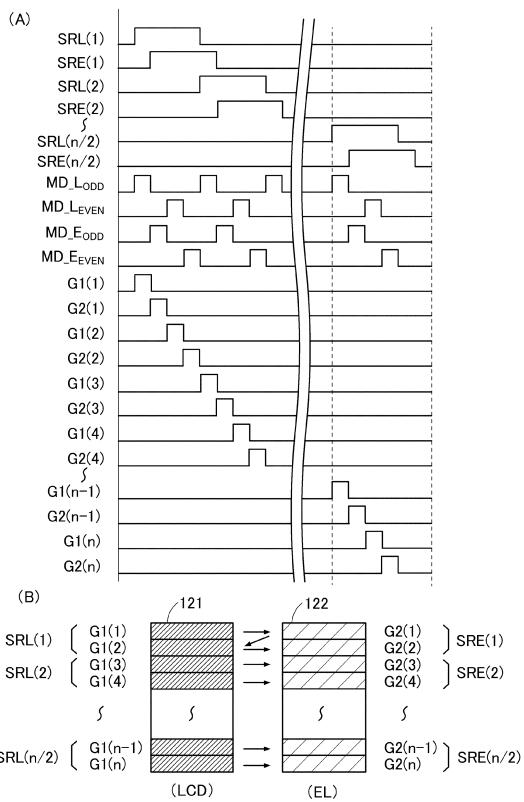

- 【図 5】(A)：図 1 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 6】(A)：図 1 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 7】表示装置の構成を説明するための図。 10

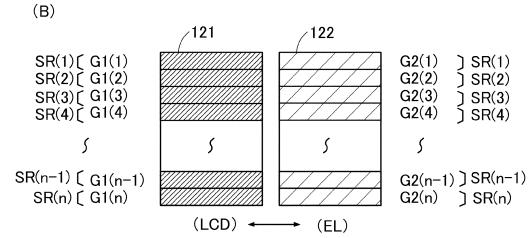

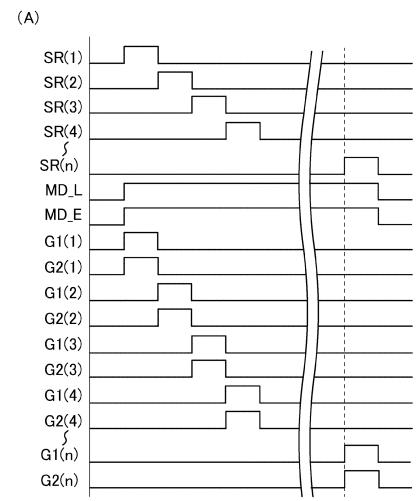

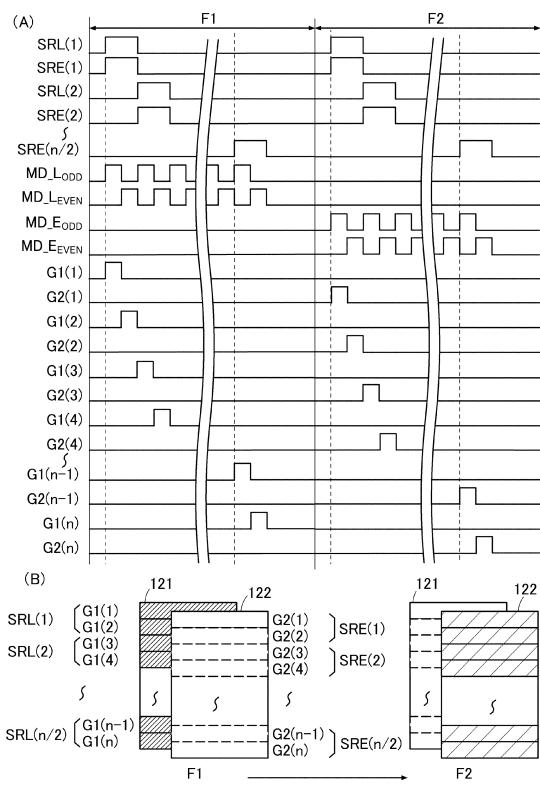

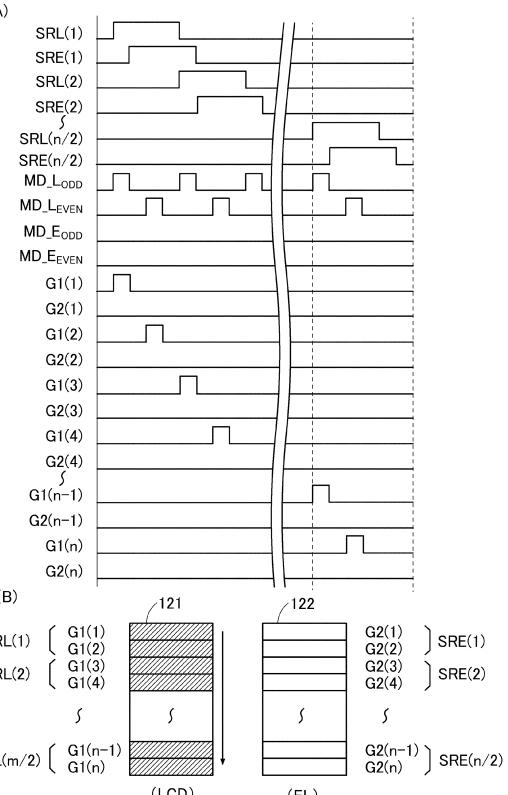

- 【図 8】(A)：図 7 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 9】(A)：図 7 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 10】表示装置の構成を説明するための図。

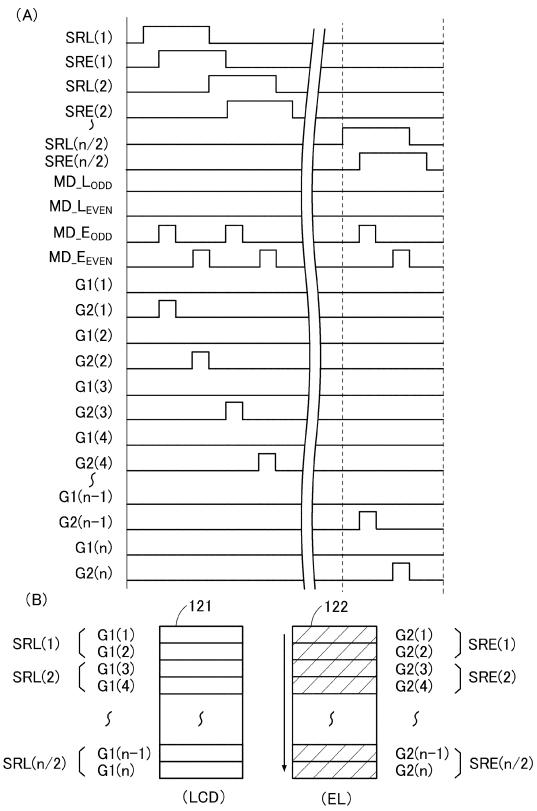

- 【図 11】(A)：図 10 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 12】(A)：図 10 の表示装置のタイミングチャート。(B)：動作を説明するための図。

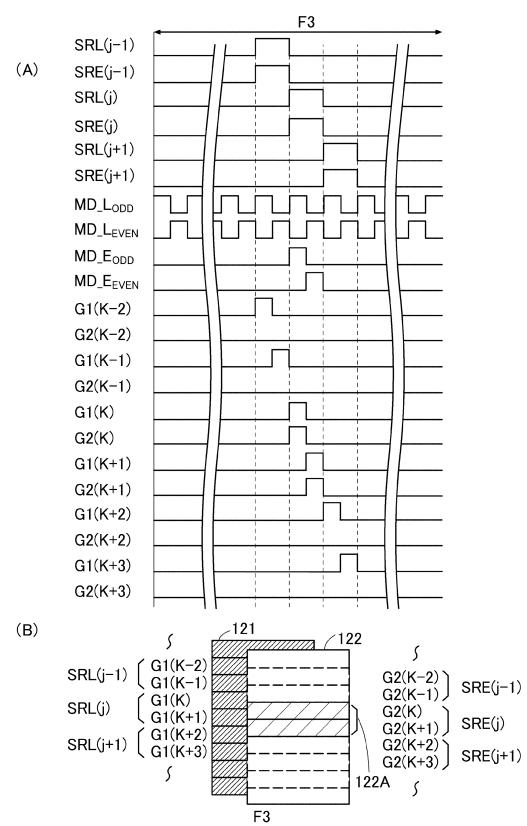

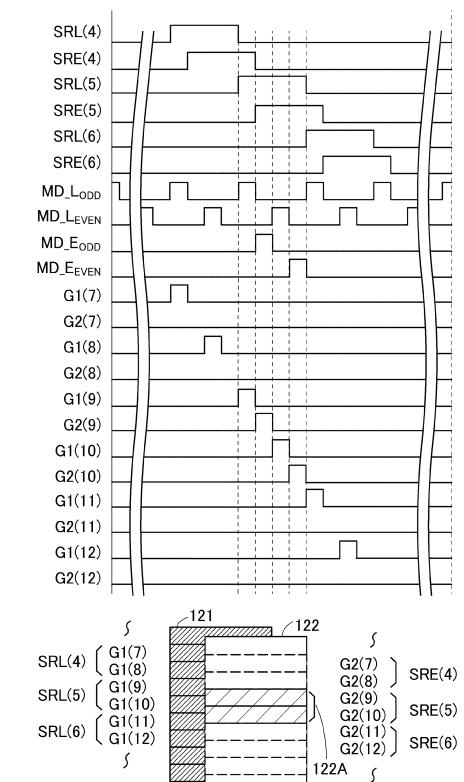

- 【図 13】(A)：図 10 の表示装置のタイミングチャート。(B)：動作を説明するための図。 20

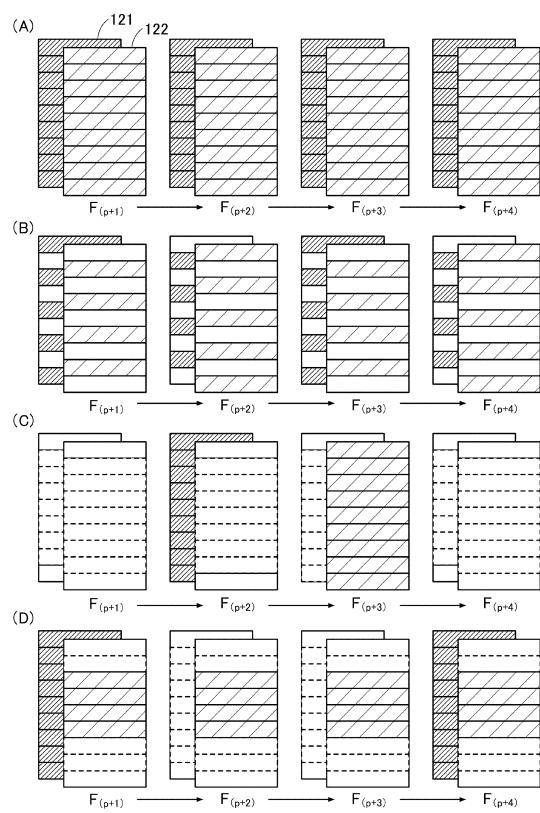

- 【図 14】(A)乃至(D)：表示例を説明するための図。

- 【図 15】画素の構成を説明するための図。

- 【図 16】表示装置の構成を説明するための図。

- 【図 17】(A)：図 16 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 18】(A)：画素の構成を説明するための図。(B)：(A)の画素のタイミングチャート。(C)：信号の電圧関係を説明する図。

- 【図 19】画素の構成を説明するための図。

- 【図 20】表示装置の構成を説明するための図。 30

- 【図 21】(A)：図 20 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 22】表示装置の構成を説明するための図。

- 【図 23】(A)：図 22 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 24】(A)：図 22 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 25】(A)：図 22 の表示装置のタイミングチャート。(B)：動作を説明するための図。

- 【図 26】(A)：図 22 の表示装置のタイミングチャート。(B)：動作を説明するための図。 40

- 【図 27】実施の形態に係る表示パネルの構成を説明する図。

- 【図 28】実施の形態に係る画素の構成を説明する図。

- 【図 29】実施の形態に係る表示パネルの構成を説明する図。

- 【図 30】実施の形態に係る画素回路の開口部を説明する図。

- 【図 31】実施の形態に係る表示パネルの構成を説明する図。

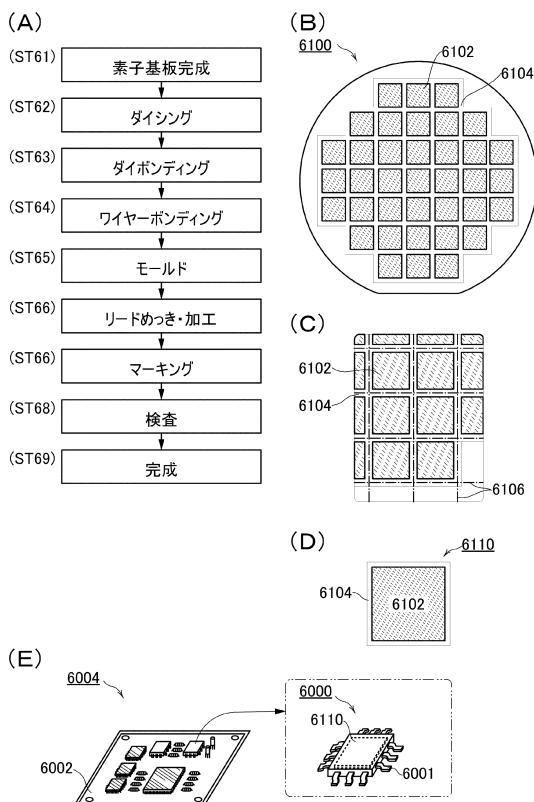

- 【図 32】(A)：電子部品の作製方法例を示すフローチャート。(B)：半導体ウエハの上面図。(C)：(B)の部分拡大図。(D)：チップの構成例を示す模式図。(E)：電子部品の構成例を示す斜視模式図。

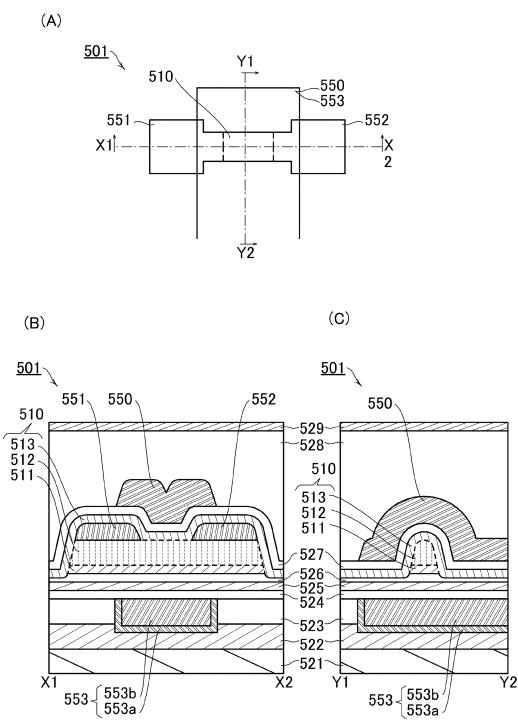

- 【図 33】OSトランジスタの構成例を示す上面図および断面図。 50

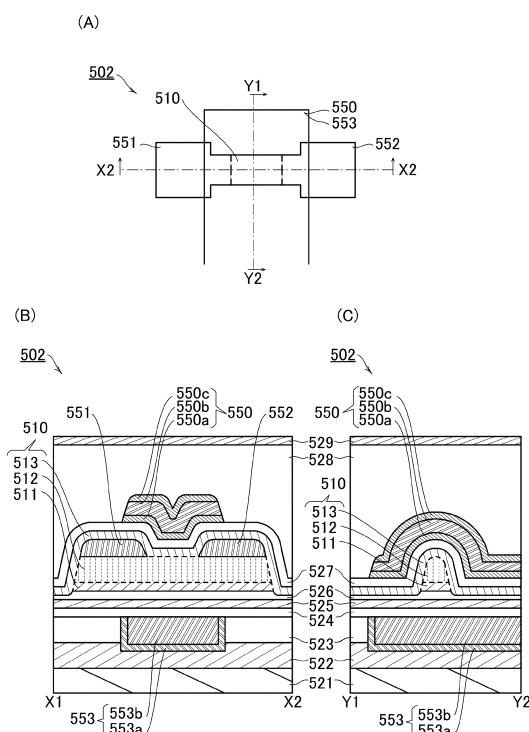

【図34】OSトランジスタの構成例を示す上面図および断面図。

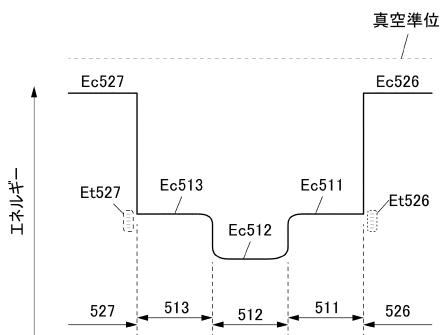

【図35】エネルギー・バンド構造の模式図。

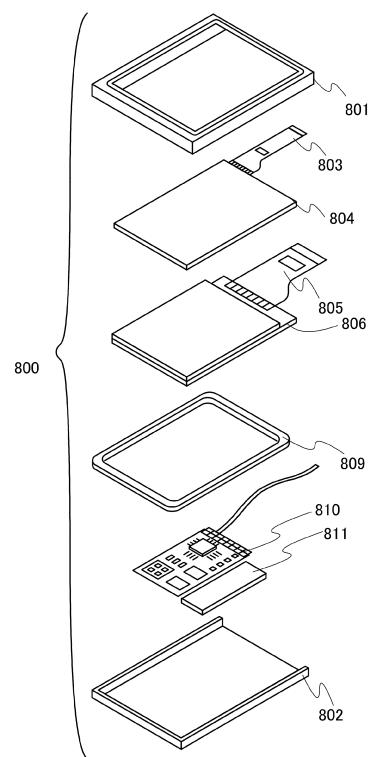

【図36】表示モジュールの例を示す図。

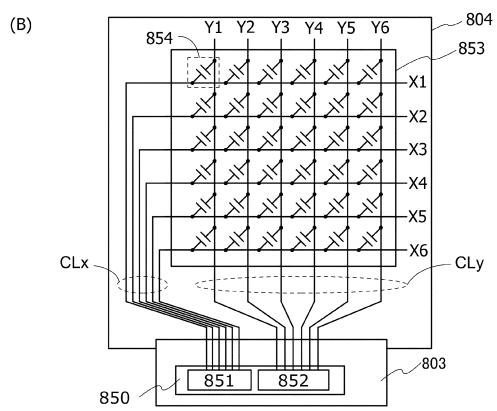

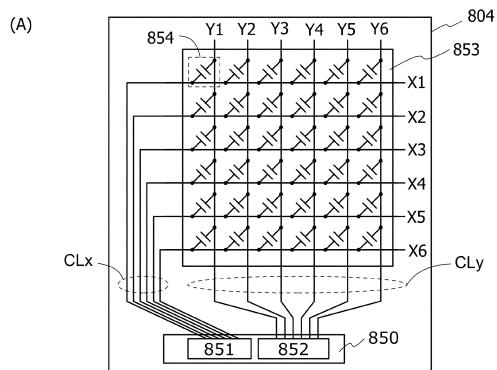

【図37】タッチパネルの構成例を示す模式図。

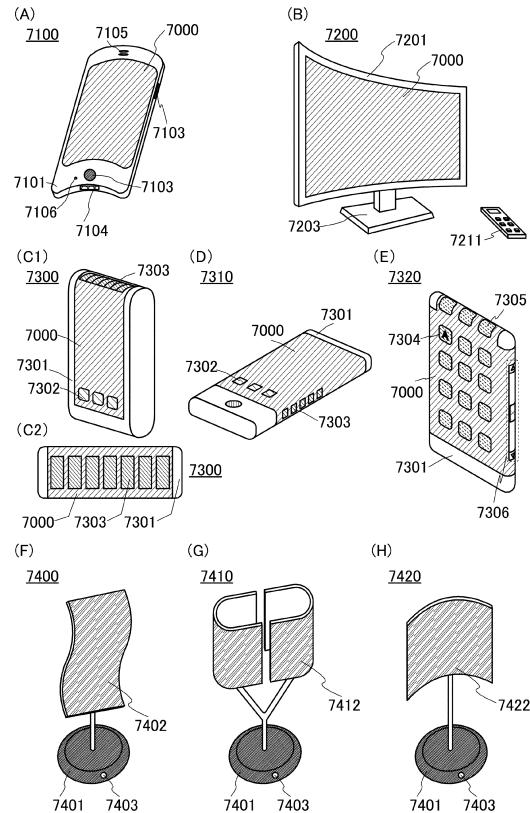

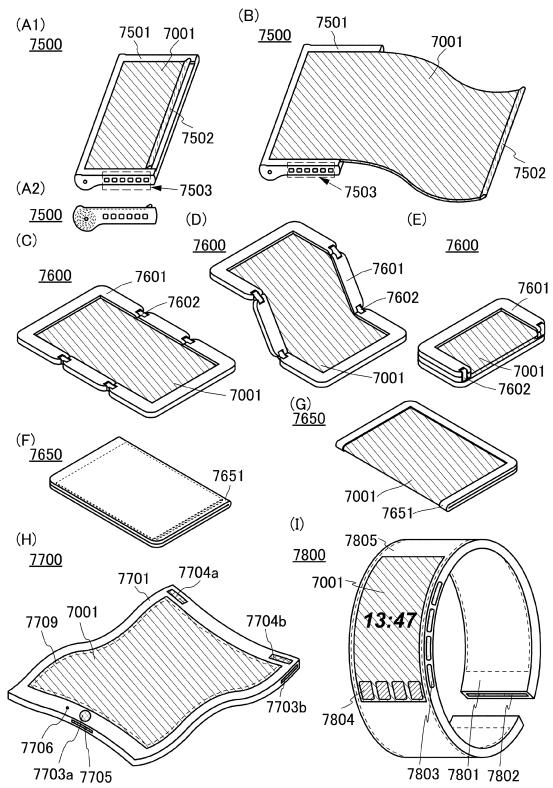

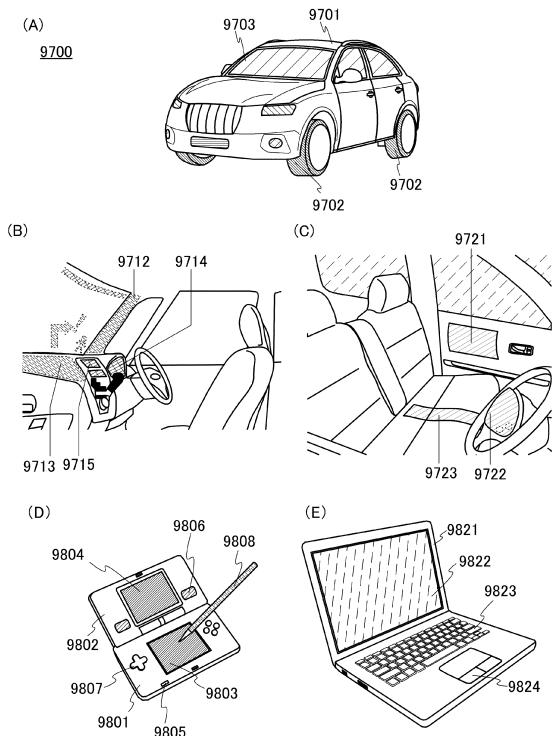

【図38】電子機器および照明装置の一例を示す図。

【図39】電子機器の一例を示す図。

【図40】電子機器の一例を示す図。

【発明を実施するための形態】

【0024】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

10

【0025】

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。

【0026】

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

20

【0027】

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

【0028】

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン（ドレイン端子、ドレイン領域またはドレイン電極）とソース（ソース端子、ソース領域またはソース電極）の間にチャネル領域を有しており、チャネル形成領域を介して、ソースとドレインとの間に電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。

30

【0029】

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。

【0030】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

40

【0031】

また、本明細書等において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

【0032】

50

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

【0033】

また、本明細書等において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態（非導通状態、遮断状態、ともいう）にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧 $V_{g s}$ がしきい値電圧 $V_{t h}$ よりも低い状態、pチャネル型トランジスタでは、ゲートとソースの間の電圧 $V_{g s}$ がしきい値電圧 $V_{t h}$ よりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、ゲートとソースの間の電圧 $V_{g s}$ がしきい値電圧 $V_{t h}$ よりも低いときのドレイン電流を言う場合がある。10

【0034】

トランジスタのオフ電流は、 $V_{g s}$ に依存する場合がある。従って、トランジスタのオフ電流が $I$ 以下である、とは、トランジスタのオフ電流が $I$ 以下となる $V_{g s}$ の値が存在することを言う場合がある。トランジスタのオフ電流は、所定の $V_{g s}$ におけるオフ状態、所定の範囲内の $V_{g s}$ におけるオフ状態、または、十分に低減されたオフ電流が得られる $V_{g s}$ におけるオフ状態、等におけるオフ電流を指す場合がある。

【0035】

一例として、しきい値電圧 $V_{t h}$ が0.5Vであり、 $V_{g s}$ が0.5Vにおけるドレイン電流が $1 \times 10^{-9} A$ であり、 $V_{g s}$ が0.1Vにおけるドレイン電流が $1 \times 10^{-1} A$ であり、 $V_{g s}$ が-0.5Vにおけるドレイン電流が $1 \times 10^{-19} A$ であり、 $V_{g s}$ が-0.8Vにおけるドレイン電流が $1 \times 10^{-22} A$ であるようなnチャネル型トランジスタを想定する。当該トランジスタのドレイン電流は、 $V_{g s}$ が-0.5Vにおいて、または、 $V_{g s}$ が-0.5V乃至-0.8Vの範囲において、 $1 \times 10^{-19} A$ 以下であるから、当該トランジスタのオフ電流は $1 \times 10^{-19} A$ 以下である、と言う場合がある。当該トランジスタのドレイン電流が $1 \times 10^{-22} A$ 以下となる $V_{g s}$ が存在するため、当該トランジスタのオフ電流は $1 \times 10^{-22} A$ 以下である、と言う場合がある。20

【0036】

また、本明細書等では、チャネル幅 $W$ を有するトランジスタのオフ電流を、チャネル幅 $W$ あたりを流れる電流値で表す場合がある。また、所定のチャネル幅（例えば $1 \mu m$ ）あたりを流れる電流値で表す場合がある。後者の場合、オフ電流の単位は、電流／長さの次元を持つ単位（例えば、 $A / \mu m$ ）で表される場合がある。30

【0037】

トランジスタのオフ電流は、温度に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、室温、60、85、95、または125におけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度（例えば、5乃至35のいずれか一の温度）におけるオフ電流、を表す場合がある。トランジスタのオフ電流が $I$ 以下である、とは、室温、60、85、95、125、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度（例えば、5乃至35のいずれか一の温度）、におけるトランジスタのオフ電流が $I$ 以下となる $V_{g s}$ の値が存在することを指す場合がある。40

【0038】

トランジスタのオフ電流は、ドレインとソースの間の電圧 $V_{d s}$ に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、 $V_{d s}$ が0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、または20Vにおけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証される $V_{d s}$ 、または、当該トランジスタが含まれる半導体装置50

等において使用される  $V_{ds}$  におけるオフ電流、を表す場合がある。トランジスタのオフ電流が  $I$  以下である、とは、 $V_{ds}$  が  $0.1V$ 、 $0.8V$ 、 $1V$ 、 $1.2V$ 、 $1.8V$ 、 $2.5V$ 、 $3V$ 、 $3.3V$ 、 $10V$ 、 $12V$ 、 $16V$ 、 $20V$ 、当該トランジスタが含まれる半導体装置等の信頼性が保証される  $V_{ds}$ 、または、当該トランジスタが含まれる半導体装置等において使用される  $V_{ds}$ 、におけるトランジスタのオフ電流が  $I$  以下となる  $V_{gs}$  の値が存在することを指す場合がある。

【0039】

上記オフ電流の説明において、ドレインをソースと読み替えてよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソースを流れる電流を言う場合もある。

【0040】

また、本明細書等では、オフ電流と同じ意味で、リーク電流と記載する場合がある。また、本明細書等において、オフ電流とは、例えば、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。

【0041】

(実施の形態1)

本実施の形態では、ゲートドライバの有する選択回路が、第1の表示素子を有する画素回路、または第2の表示素子を有する画素回路を選択する走査信号を生成する機能を有する表示装置について、図1乃至図6を用いて説明する。

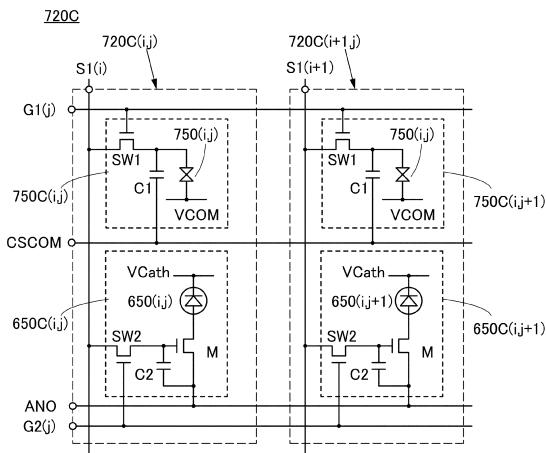

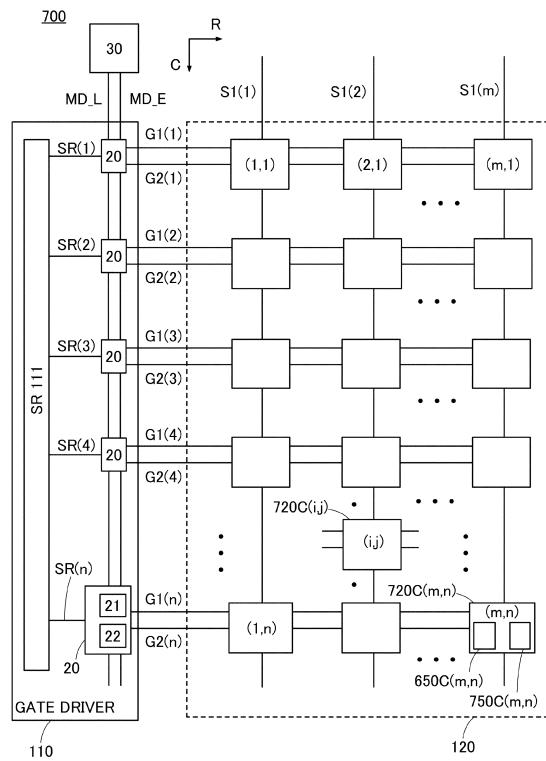

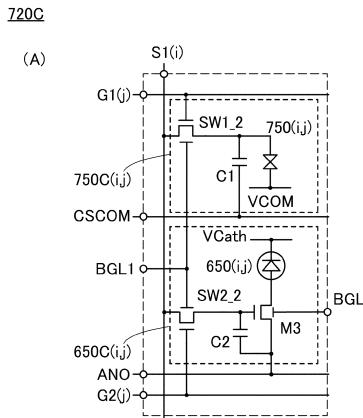

【0042】

図1は、表示装置700の構成を示すブロック図である。表示装置700はゲートドライバ110、選択信号出力回路30、および表示部120を有する。ゲートドライバ110は、シフトレジスタ回路111および選択回路20を有する。選択回路20は、判定回路21および22を有する。表示部120は、画素回路710C(1,1)乃至画素回路710C(m,n)を有する。画素回路710C(m,n)は、第1の表示素子を有する画素回路750C(m,n)、および第2の表示素子を有する画素回路650C(m,n)を有する。mおよびnは1以上の整数である。

【0043】

本実施の形態で説明する表示部120は、画素回路710C(1,1)乃至画素回路710C(m,n)と、第1の走査線G1と、第2の走査線G2と、第1の信号線S1と、第2の信号線S2とを有する。

【0044】

図2に、画素回路710Cの構成を示す。図1の表示装置700の表示部120の、画素の一つを、画素回路710C(i,j)として説明する。なお、iは1以上m以下の整数であり、jは1以上n以下の整数である。

【0045】

画素回路710C(i,j)は、画素回路750C(i,j)を有し、画素回路750C(i,j)は、第1の表示素子750(i,j)を有する。第1の表示素子750(i,j)は、一例として焼き付きを防止するために交流駆動される液晶素子が好ましい。

【0046】

画素回路710C(i,j)は、画素回路650C(i,j)を有し、画素回路650C(i,j)は、第2の表示素子650(i,j)を有する。第2の表示素子650(i,j)は、一例として直流駆動される発光素子が好ましい。

【0047】

画素回路750C(i,j)および画素回路650C(i,j)は、階調を表示できる最少の単位であり、階調は、電圧または電流による階調信号で制御される。

【0048】

画素回路750C(i,j)は、トランジスタSW1、容量素子C1、および第1の表示素子750(i,j)を有する。

【0049】

画素回路750C(i,j)のトランジスタSW1のゲートは、第1の走査線G1(j)

10

20

30

40

50

) と電気的に接続される。トランジスタ SW1 のソースまたはドレインの一方は、第 1 の信号線 S1 ( i ) と電気的に接続される。

【 0 0 5 0 】

トランジスタ SW1 のソースまたはドレインの他方は、容量素子 C1 の一方の電極および第 1 の表示素子 750 ( i , j ) の一方の電極と電気的に接続される。容量素子 C1 の他方の電極には、容量素子 C1 の基準電圧が CSCOM 端子を介して与えられる。第 1 の表示素子 750 ( i , j ) の他方の電極には、コモン電圧が VCOM 端子を介して与えられる。

【 0 0 5 1 】

画素回路 650C ( i , j ) は、トランジスタ SW2 、トランジスタ M 、容量素子 C2 、および第 2 の表示素子 650 ( i , j ) を有する。 10

【 0 0 5 2 】

画素回路 650C ( i , j ) のトランジスタ SW2 のゲートは、第 2 の走査線 G2 ( j ) と電気的に接続される。トランジスタ SW2 のソースまたはドレインの一方が第 2 の信号線 S2 ( i ) と電気的に接続される。

【 0 0 5 3 】

トランジスタ SW2 のソースまたはドレインの他方は、容量素子 C2 の一方の電極およびトランジスタ M のゲートと電気的に接続される。トランジスタ M のドレインには ANO 端子を介してアノード電圧が与えられる。トランジスタ M のドレインには、容量素子 C2 の他方の電極が接続される。トランジスタ M のソースには第 2 の表示素子 650 ( i , j ) の一方の電極が接続される。第 2 の表示素子 650 ( i , j ) の他方の電極は、カソード電圧が V Cath 端子を介して与えられる。容量素子 C2 の電極の他方がトランジスタ M のドレインと電気的に接続された例を示したが、ソースと電気的に接続してもよいし、他の電圧が与えられる端子と電気的に接続してもよい。 20

【 0 0 5 4 】

なお本発明の一様態は図 2 の画素回路 710C ( i , j ) の回路構成に限らない。図 2 とは異なる画素回路 710C ( i , j ) の回路構成の一例について図 3 ( A ) 乃至 ( C ) に図示する。

【 0 0 5 5 】

図 3 ( A ) 乃至 ( C ) は、トランジスタがバックゲートを有する画素を図示している。トランジスタ以外の構成については図 2 に示す回路と同様である。 30

【 0 0 5 6 】

図 2 と異なる点を示す。図 3 ( A ) では画素回路 710C ( i , j ) が有するトランジスタは、バックゲートを有するトランジスタを図示している。トランジスタ SW1\_1 のゲートはトランジスタ SW1\_1 のバックゲートと接続されている。トランジスタ SW2\_1 およびトランジスタ M\_1 のゲートも同様にバックゲートと電気的に接続されている。トランジスタ SW1\_1 のゲート電圧と同じ電圧が、トランジスタ SW1\_1 のバックゲートに与えられている。トランジスタ SW2\_1 およびトランジスタ M\_1 も同様である。

【 0 0 5 7 】

図 3 ( A ) と異なる点を示す。図 3 ( B ) のトランジスタ M\_2 は、バックゲートがトランジスタ M\_2 のソースと接続されている。トランジスタ M\_2 のソース電圧と同じ電圧が、トランジスタ M\_2 のバックゲートに与えられる。 40

【 0 0 5 8 】

図 3 ( A ) と異なる点を示す。図 3 ( C ) のトランジスタ M\_3 のバックゲートは、 BGL 端子と接続されている。バックゲートの電圧を BGL 端子から与えることができる。

【 0 0 5 9 】

なお本発明の一様態は図 3 の画素回路 710C ( i , j ) の回路構成に限らない。他の端子をバックゲートと電気的に接続もできるし、接続の方法を組み合わせることもできる。 50

## 【0060】

トランジスタは、ゲート電極（第1のゲート電極）およびバックゲート電極（第2のゲート電極）の電界により、チャネル領域が形成される酸化物半導体膜を電気的に取り囲むトランジスタのデバイス構造とすることができます。このようなデバイス構造を、*surr*

*ounded channel (s-channel)*構造と呼ぶ。

## 【0061】

図4(A)に選択回路20の構成を示す。選択回路20は、判定回路21および判定回路22を有する。判定回路21および判定回路22は、入力信号の条件を判定する回路25と、バッファ回路26を有する。

## 【0062】

回路25の入力端子の一方には、選択回路20を選択するためのシフトレジスタ回路11の出力信号SRが入力される。判定回路21の回路25の入力端子の他方には、選択信号出力回路30の選択信号MD\_Lが入力される。判定回路22の回路25の入力端子の他方には、選択信号出力回路30の選択信号MD\_Eが入力される。

## 【0063】

図4(B)に選択回路20が有する判定回路21の動作をタイミングチャートF21で示す。シフトレジスタ回路111の出力信号SRおよび選択信号MD\_LがHighのとき、第1の走査線G1にHighの信号を出力する。それ以外の入力条件の時は、第1の走査線G1にLowの信号が出力される。

## 【0064】

図4(B)に選択回路20が有する判定回路22の動作をタイミングチャートF22で示す。シフトレジスタ回路111の出力信号SRおよび選択信号MD\_EがHighのとき、第2の走査線G2にHighの信号を出力する。それ以外の入力条件の時は、第2の走査線G2にLowの信号が出力される。

## 【0065】

判定回路21のバッファ回路26は、第1の表示素子750の階調信号の電圧振幅より大きな電圧振幅の信号を第1の走査線G1に出力する。

## 【0066】

判定回路22のバッファ回路26は、第2の表示素子650の階調信号の電圧振幅より大きな電圧振幅の信号を第2の走査線G2に出力する。

## 【0067】

第1の表示素子750の階調信号の電圧振幅と、第2の表示素子650の階調信号の電圧振幅は異なるため、第1の走査線G1と、第2の走査線G2とは出力電圧の振幅が異なる。

## 【0068】

なお本発明の一様態は図4(B)の動作条件を満足すればよく、図4(A)の選択回路20の回路構成に限らない。

## 【0069】

図5(A)は、図1の表示装置700の動作についてタイミングチャートを示す。図1のゲートドライバ110は、シフトレジスタ回路111から出力信号SR(1)乃至SR(n)が順次出力される。

## 【0070】

第1の走査線G1(j)に出力する走査信号は、シフトレジスタ回路111の出力信号SR(j)および選択信号出力回路30の選択信号MD\_Lを用いて、選択回路20の判定回路21により生成される。

## 【0071】

第2の走査線G2(j)に出力する走査信号は、シフトレジスタ回路111の出力信号SR(j)および選択信号出力回路30の選択信号MD\_Eを用いて、選択回路20の判定回路22により生成される。

## 【0072】

10

20

30

40

50

図5(A)に示すタイミングチャートを用いて、出力信号SR(1)がHighの期間における、シフトレジスタ回路111の動作について説明する。

【0073】

出力信号SR(1)がHighの期間において、選択信号MD\_LがHighの期間に、第1の走査線G1(1)の走査信号がHighになり、画素回路750C(i, 1)と電気的に接続された第1の信号線S1(1)乃至S1(m)により、画素回路750C(i, 1)へ階調信号を書き込むことができる。

【0074】

出力信号SR(1)がHighの期間において、選択信号MD\_EがHighの期間に、第2の走査線G2(1)の走査信号がHighになり、画素回路650C(i, 1)と電気的に接続された第2の信号線S2(1)乃至S2(m)により、画素回路650C(i, 1)へ階調信号を書き込みができる。

10

【0075】

図5(B)は、表示部120の駆動状態を模式的に示す。画素回路750C(i, j)により表示された領域を液晶表示領域121とし、画素回路650C(i, j)により表示された領域を発光表示領域122とする。

【0076】

図5(B)は、出力信号SR(j)、選択信号MD\_L、選択信号MD\_E、および選択回路20によって、第1の走査線G1(j)に走査信号が出力されたことで液晶表示領域121の表示内容が更新される。さらに第2の走査線G2(j)に走査信号が出力されたことで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図5(A)のタイミングチャートと対応している。

20

【0077】

一例として、図1のシフトレジスタ回路111の出力信号SR(1)がHighのときについて説明する。選択信号MD\_LがHighのときに、選択回路20によって第1の走査線G1(1)に与えられる走査信号がHighになる。表示内容は、画素回路750C(1, 1)乃至画素回路750C(m, 1)に与えられた階調信号により更新される。

【0078】

出力信号SR(1)がHighのとき、選択信号MD\_EがHighになる。選択信号MD\_EがHighのときに、選択回路20によって第2の走査線G2(1)に与えられる走査信号がHighになる。表示内容は、画素回路650C(1, 1)乃至画素回路650C(m, 1)に与えられた階調信号により更新される。

30

【0079】

図5(A)では、出力信号SR(1)がHighの期間に、先に選択信号MD\_LがHighになり、続いて選択信号MD\_EがHighになる。図5(B)では、選択信号MD\_LがHighの期間に、液晶表示領域121の表示が先に更新される。続いて、選択信号MD\_EがHighの期間に発光表示領域122の表示が更新される。

【0080】

第1の走査線G1(1)、および第2の走査線G2(1)は、シフトレジスタ回路111、および選択回路20を有するゲートドライバで、走査線の選択を制御することができる。

40

【0081】

図1の例では、選択信号MD\_Lおよび選択信号MD\_Eの信号を用いるので、判定回路21および判定回路22はnチャンネル型トランジスタを有している。判定回路21および判定回路22は、相補型MOSスイッチ(CMOSスイッチ、アナログスイッチ)で構成することも可能である。相補型MOSスイッチで構成することで、選択条件を正論理および負論理で判定できるようになり、選択信号の数を減らすことができる。

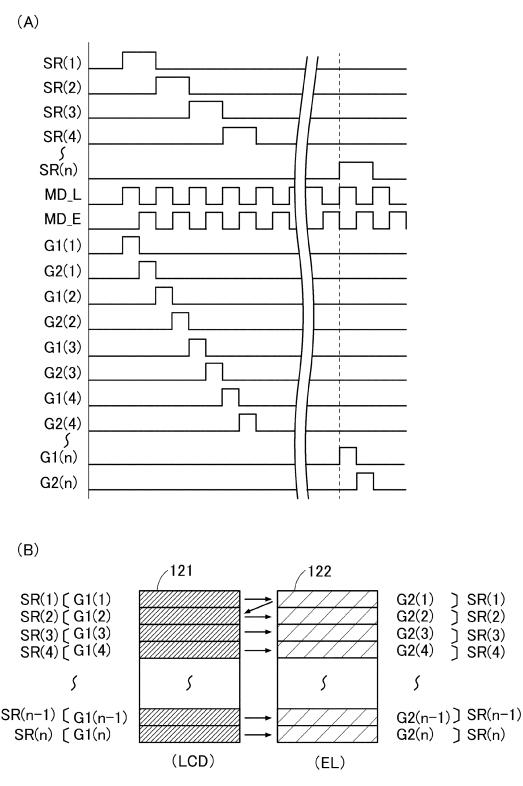

【0082】

図6(A)に示すタイミングチャートを用いて、図1の表示装置700を、図5(A)とは異なるタイミングで動作させる。出力信号SR(1)がHighの期間における、シ

50

フトレジスタ回路 111 の動作について説明する。

【0083】

出力信号 SR(1) が High の期間において、選択信号 MD\_L が High の期間に、第 1 の走査線 G1(1) の走査信号が High になり、第 1 の信号線 S1(1) 乃至 S1(m) により、画素回路 750C(i, 1) へ階調信号を書き込むことができる。

【0084】

出力信号 SR(1) が High の期間において、選択信号 MD\_E が High の期間に、第 2 の走査線 G2(1) の走査信号が High になり、第 2 の信号線 S2(1) 乃至 S2(m) により、画素回路 650C(i, 1) へ階調信号を書き込みができる。

【0085】

図 6(B) は、表示部 120 の駆動状態を模式的に示す。出力信号 SR(j)、選択信号 MD\_L、および選択信号 MD\_E によって、第 1 の走査線 G1(j) の走査信号が High になることで液晶表示領域 121 の表示内容が更新される。さらに第 2 の走査線 G2(j) の走査信号が High になることで発光表示領域 122 の表示内容が更新される。したがって表示が更新される順番は、図 6(A) のタイミングチャートと対応している。

【0086】

一例として、図 1 のシフトレジスタ回路 111 の出力信号 SR(1) が High のときについて説明する。選択信号 MD\_L が High のときに、選択回路 20 によって第 1 の走査線 G1(1) に与えられる走査信号が High になる。表示内容は、画素回路 750C(1, 1) 乃至画素回路 750C(m, 1) に与えられた階調信号により更新される。

【0087】

出力信号 SR(1) が High のとき、選択信号 MD\_E が High になる。選択信号 MD\_E が High のときに、選択回路 20 によって第 2 の走査線 G2(1) に与えられる走査信号が High になる。表示内容は、画素回路 650C(1, 1) 乃至画素回路 650C(m, 1) に与えられた階調信号により更新される。

【0088】

図 6(A) は図 5(A) とは異なり、出力信号 SR(1) が High の期間に、選択信号 MD\_L および MD\_E が同時に High になる。図 6(B) では、選択信号 MD\_L および MD\_E が同時に High のため、液晶表示領域 121 の表示と、発光表示領域 122 の表示が同時に更新される。

【0089】

図 5(A) では、画素回路 710C(i, j) の画素回路 750C(i, j) および画素回路 650C(i, j) は異なるタイミングで階調信号が更新されるのに対し、図 6(A) では、画素回路 750C(i, j) および画素回路 650C(i, j) は、シフトレジスタ回路 111 の出力信号 SR(j) と同じ期間に、第 1 の走査線 G1(j) の走査信号および第 2 の走査線 G2(j) の走査信号が High になり、階調信号が更新される。図 6(A) は、図 5(A) に比べて長い書き込み時間を確保できる。

【0090】

画素回路 750C(i, j) のトランジスタ SW1 のゲートと電気的に接続する第 1 の走査線 G1(j)、および画素回路 650C(i, j) のトランジスタ SW2 のゲートと電気的に接続する第 2 の走査線 G2(j) は、シフトレジスタ回路 111、および選択回路 20 を有するゲートドライバで、走査線の選択を制御することができる。

【0091】

以上、本実施の形態で示す構成、方法、駆動タイミングは、他の実施の形態で示す構成、方法、駆動タイミングと適宜組み合わせて用いることができる。

【0092】

(実施の形態 2)

本実施の形態では、画素回路 710C を有する高精細な表示を行う表示装置において、ゲートドライバを、奇数行と偶数行とに構成を分けて制御する方法について、図 7 乃至図

10

20

30

40

50

9を用いて説明する。

【0093】

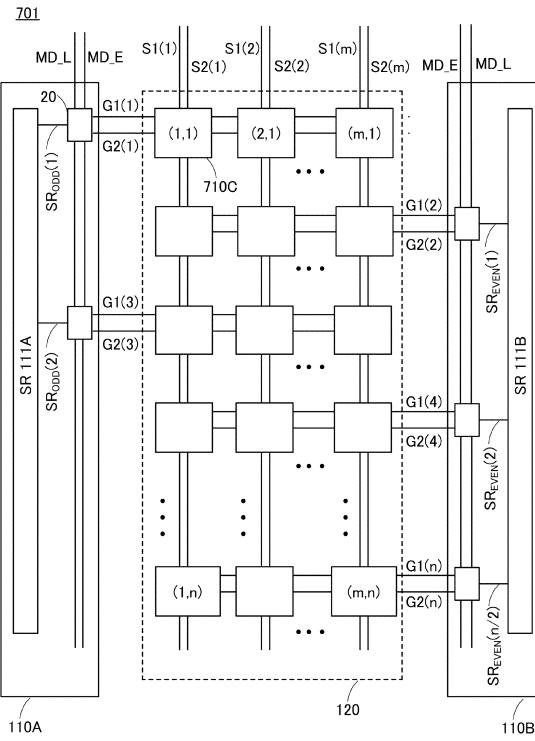

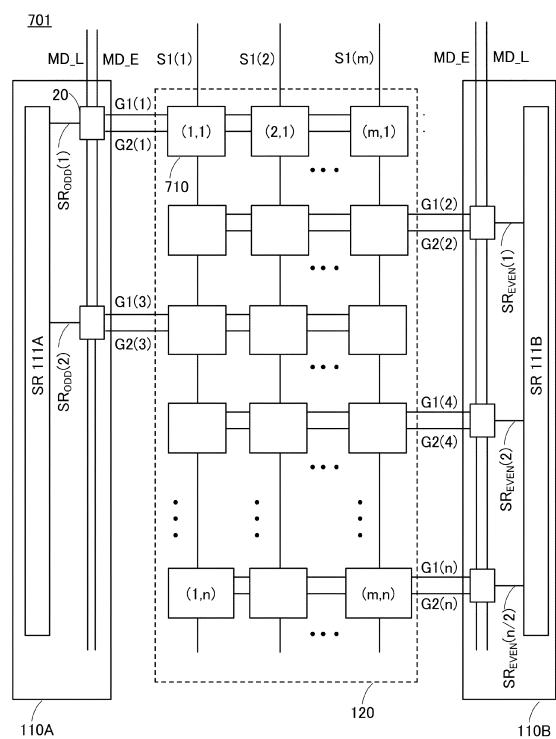

図7は、表示装置701の構成を示すブロック図である。図1と異なるのは、ゲートドライバ110が、図7では奇数行の走査線を制御するゲートドライバ110Aと、偶数行の走査線を制御するゲートドライバ110Bとに構成が分かれている点である。

【0094】

図7の表示装置701が有するゲートドライバ110Aおよびゲートドライバ110Bが有するシフトレジスタ回路111Aおよびシフトレジスタ回路111Bは、図1のゲートドライバ110が有するシフトレジスタ回路111の出力信号SRとは異なるタイミングの出力信号SR<sub>ODD</sub>およびSR<sub>EVEN</sub>を生成する。

10

【0095】

図7の表示装置701は、ゲートドライバを奇数行制御および偶数行制御に構成を分けることで、ゲートドライバの段数が半分になり、回路の面積も半分になる。第1の走査線G1の走査信号および第2の走査線G2の走査信号を駆動する選択回路20のバッファ回路26を大きくすることができ、電流供給能力を上げることができる。

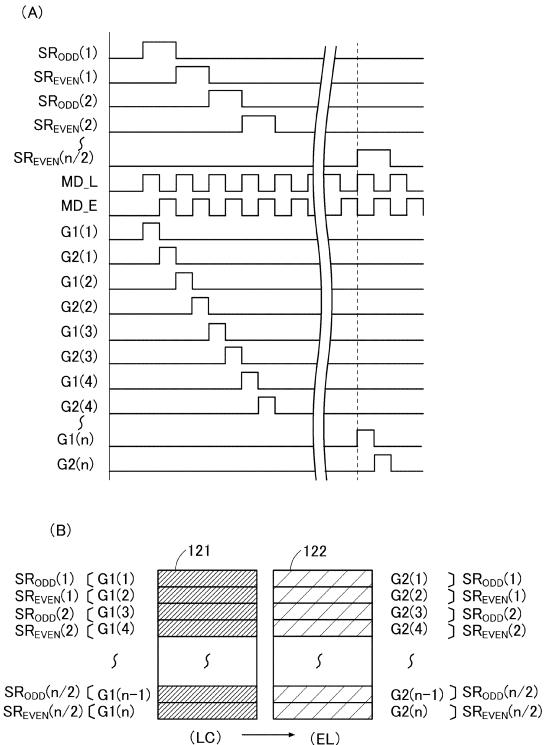

【0096】

図8(A)では、図7の表示装置701の動作についてタイミングチャートを示す。図8(A)に示すタイミングチャートでは、図5(A)に示すタイミングチャートと同じように選択信号MD\_L及び選択信号MD\_Eを入力している。これにより、図5(A)に示すタイミングチャートと同じタイミングで第1の走査線G1(1)乃至G1(n)、第2の走査線G2(1)乃至G2(n)に電圧が与えられる。

20

【0097】

図8(B)は、表示部120の駆動状態を模式的に示す。図5(B)とは異なり、図7のシフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)乃至SR<sub>ODD</sub>(n/2)、シフトレジスタ回路111Bの出力信号SR<sub>EVEN</sub>(1)乃至SR<sub>EVEN</sub>(n/2)、選択信号MD\_L、および選択信号MD\_Eによって、第1の走査線G1(1)乃至G1(n)の走査信号がHighになることで液晶表示領域121の表示内容が更新され、さらに第2の走査線G2(1)乃至G2(n)の走査信号がHighになることで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図8(A)のタイミングチャートと対応している。

30

【0098】

一例として、図7のシフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)がHighのときについて説明する。選択信号MD\_LがHighのときに、選択回路20によって第1の走査線G1(1)の走査信号がHighになる。画素回路750C(1,1)乃至画素回路750C(m,1)に与えられた階調信号により表示内容が更新される。

【0099】

シフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)がHigh、かつ、選択信号MD\_EがHighのときに、選択回路20によって第2の走査線G2(1)の走査信号がHighになる。画素回路650C(1,1)乃至画素回路650C(m,1)に与えられた階調信号により表示内容が更新される。

40

【0100】

図8(A)では、シフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)がHighの期間に、先に選択信号MD\_LがHighになり、続いて選択信号MD\_EがHighになる。図8(B)では、選択信号MD\_LがHighの期間に、液晶表示領域121の表示が先に更新される。続いて、選択信号MD\_EがHighの期間に発光表示領域122の表示が更新される。

【0101】

図9(A)では、図7の表示装置701の動作についてタイミングチャートを示す。図9(A)に示すタイミングチャートでは、図6(A)に示すタイミングチャートと同じように選択信号MD\_L及び選択信号MD\_Eを入力している。これにより、図6(A)に

50

示すタイミングチャートと同じタイミングで第1の走査線G1(1)乃至G1(n)、第2の走査線G2(1)乃至G2(n)に電圧が与えられる。

【0102】

図9(B)は、表示部120の駆動状態を模式的に示す。図7のシフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)乃至SR<sub>ODD</sub>(n/2)、シフトレジスタ回路111Bの出力信号SR<sub>EVEN</sub>(1)乃至SR<sub>EVEN</sub>(n/2)、選択信号MD\_L、および選択信号MD\_Eによって、第1の走査線G1(1)乃至G1(n)の走査信号がHighになることで液晶表示領域121の表示内容が更新される。さらに第2の走査線G2(1)乃至G2(n)の走査信号がHighになることで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図9(A)のタイミングチャートと対応している。10

【0103】

一例として、図7のゲートドライバ110Aが有するシフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)がHighのときについて説明する。選択信号MD\_LがHighのときに、選択回路20によって第1の走査線G1(1)に与えられる走査信号がHighになる。表示内容は、画素回路750C(1,1)乃至画素回路750C(m,1)に与えられた階調信号により更新される。

【0104】

シフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)がHighのとき、選択信号MD\_EがHighになる。選択信号MD\_EがHighのときに、選択回路20によって第2の走査線G2(1)に与えられる走査信号がHighになる。表示内容は、画素回路650C(1,1)乃至画素回路650C(m,1)に与えられた階調信号により更新される。20

【0105】

図9(A)は図8(A)とは異なり、シフトレジスタ回路111Aの出力信号SR<sub>ODD</sub>(1)がHighの期間に、選択信号MD\_LおよびMD\_Eが同時にHighになる。図9(B)では、選択信号MD\_LおよびMD\_Eが同時にHighのため、液晶表示領域121の表示と、発光表示領域122の表示が同時に更新される。

【0106】

画素回路750C(i,j)のトランジスタSW1のゲートと電気的に接続する第1の走査線G1(j)または画素回路650C(i,j)のトランジスタSW2のゲートと電気的に接続する第2の走査線G2(j)は、シフトレジスタ回路111A又はシフトレジスタ回路111B、および選択回路20を有するゲートドライバで、走査線の選択を制御することができる。30

【0107】

図7の表示装置701は、奇数行を制御するゲートドライバ110Aおよび偶数行を制御するゲートドライバ110Bに分けた構成においても、選択信号MD\_Lおよび選択信号MD\_Eを制御することで、図1の表示装置700と同じタイミングで動作させることができる。電流供給能力が向上することで、画素回路710Cを有する高精細な表示を行う表示装置を駆動することができる。40

【0108】

以上、本実施の形態で示す構成、方法、駆動タイミングは、他の実施の形態で示す構成、方法、駆動タイミングと適宜組み合わせて用いることができる。

【0109】

(実施の形態3)

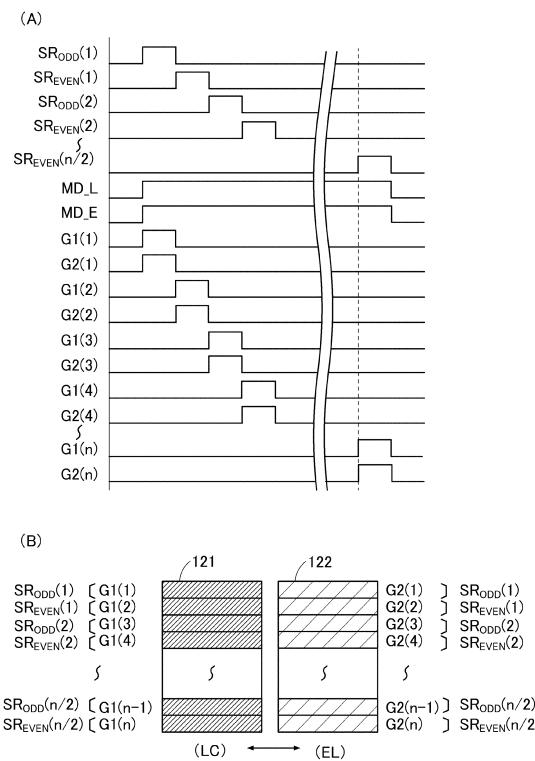

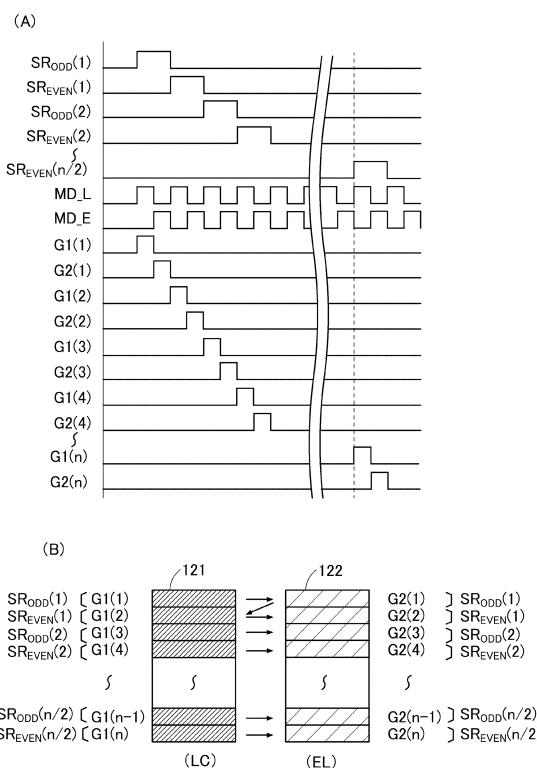

本実施の形態では、高精細な表示を行う表示装置において、液晶表示領域121および発光表示領域122を、異なる更新頻度で制御するゲートドライバの駆動方法について、図10乃至図14を用いて説明する。

【0110】

図10は、表示装置702の構成を示すブロック図である。図1と異なるのは、ゲート

50

ドライバ110が、図10では液晶表示領域121の走査線を制御するゲートドライバ110Cと、発光表示領域122の走査線を制御するゲートドライバ110Dとに構成が分かれている点である。さらに、選択回路20の出力信号は、奇数行の走査線と偶数行の走査線に出力される。

【0111】

図10の有する表示装置702のゲートドライバ110Cは液晶表示領域121の走査線を、ゲートドライバ110Dは発光表示領域122の走査線を、独立して選択制御することができる。

【0112】

図11(A)は、図10の表示装置702の動作についてタイミングチャートを示す。一例として、ゲートドライバ110Cの有するシフトレジスタ回路111Cの出力信号SRL(1)、およびゲートドライバ110Dの有するシフトレジスタ回路111Dの出力信号SRE(1)がHighの期間について、タイミングチャートの動作を説明する。

【0113】

シフトレジスタ回路111Cの出力信号SRL(1)がHighの期間において、選択信号MD\_L<sub>ODD</sub>がHighの期間に第1の走査線G1(1)の走査信号がHighになり、第1の信号線S1(1)乃至S1(m)により、画素回路750C(i, 1)へ階調信号を書き込むことができる。

【0114】

シフトレジスタ回路111Cの出力信号SRL(1)がHighの期間において、選択信号MD\_L<sub>EVEN</sub>がHighの期間に第1の走査線G1(2)の走査信号がHighになり、第1の信号線S1(1)乃至S1(m)により、画素回路750C(i, 2)へ階調信号を書き込むことができる。

【0115】

シフトレジスタ回路111Dの出力信号SRE(1)がHighの期間において、選択信号MD\_E<sub>ODD</sub>がHighの期間に第2の走査線G2(1)の走査信号がHighになり、第2の信号線S2(1)乃至S2(m)により、画素回路650C(i, 1)へ階調信号を書き込みができる。

【0116】

シフトレジスタ回路111Dの出力信号SRE(1)がHighの期間において、選択信号MD\_E<sub>EVEN</sub>がHighの期間に第2の走査線G2(2)の走査信号がHighになり、第2の信号線S2(1)乃至S2(m)により、画素回路650C(i, 2)へ階調信号の書き込みができる。

【0117】

図11(B)は、液晶表示領域121と発光表示領域122の駆動状態を模式的に示す。シフトレジスタ回路111Cの出力信号SRL(1)乃至SRL(n/2)と、選択信号MD\_L<sub>ODD</sub>とMD\_L<sub>EVEN</sub>と、シフトレジスタ回路111Dの出力信号SRE(1)乃至SRE(n/2)と、選択信号MD\_E<sub>ODD</sub>とMD\_E<sub>EVEN</sub>とにより、液晶表示領域121および発光表示領域122の表示内容が更新される順番を示す。

【0118】

図11(B)は、表示部120の駆動状態を模式的に示す。シフトレジスタ回路111Cの出力信号SRL(1)乃至SRL(n/2)と、選択信号MD\_L<sub>ODD</sub>と、MD\_L<sub>EVEN</sub>とによって第1の走査線G1(1)乃至G1(n)の走査信号にHighが outputされたことで液晶表示領域121の表示内容が更新され、シフトレジスタ回路111Dの出力信号SRE(1)乃至SRE(n/2)と、選択信号MD\_E<sub>ODD</sub>と、MD\_E<sub>EVEN</sub>とにより、第2の走査線G2(1)乃至G2(n)の走査信号にHighが outputされたことで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図11(A)のタイミングチャートと対応している。

【0119】

一例として、図10のシフトレジスタ回路111Cの出力信号SRL(1)がHigh

10

20

30

40

50

のときについて説明する。選択信号  $MD\_L_{odd}$  が  $High$  のときに、選択回路 20 によって第 1 の走査線  $G1(1)$  の走査信号が  $High$  になり、画素回路  $750C(1, 1)$  乃至画素回路  $750C(m, 1)$  が階調信号により表示内容が更新されることを示す。さらに選択信号  $MD\_L_{even}$  が  $High$  のときに、選択回路 20 によって第 1 の走査線  $G1(2)$  の走査信号が  $High$  になる。画素回路  $750C(1, 2)$  乃至画素回路  $750C(m, 2)$  が階調信号により表示内容が更新されることを示す。

#### 【0120】

同様に、シフトレジスタ回路 111D の出力信号  $SRE(1)$  が  $High$  のときについて説明する。選択信号  $MD\_E_{odd}$  が  $High$  のときに、選択回路 20 によって第 2 の走査線  $G2(1)$  の走査信号が  $High$  になり、画素回路  $650C(1, 1)$  乃至画素回路  $650C(m, 1)$  が階調信号により表示内容が更新されることを示す。さらに選択信号  $MD\_E_{even}$  が  $High$  のときに、選択回路 20 によって第 2 の走査線  $G2(2)$  の走査信号が  $High$  になる。画素回路  $650C(1, 2)$  乃至画素回路  $650C(m, 2)$  が階調信号により表示内容が更新されることを示す。

#### 【0121】

図 11(A) は、図 10 のシフトレジスタ回路 111C の出力信号  $SRL(1)$  およびシフトレジスタ回路 111D の出力信号  $SRE(1)$  が  $High$  の期間に、選択信号  $MD\_L_{odd}$  および  $MD\_E_{odd}$  が同時に  $High$  になる。図 11(B) では、選択信号  $MD\_L_{odd}$  および  $MD\_E_{odd}$  が同時に  $High$  のため、液晶表示領域 121 の表示と、発光表示領域 122 の表示が同時に更新されることを示す。

#### 【0122】

表示装置 702 のゲートドライバは、液晶表示領域 121 または発光表示領域 122 を独立して制御するために構成をわけた。さらに奇数行と、偶数行とを選択回路 20 で制御する構成とした。さらに選択信号  $MD\_L_{odd}$ 、 $MD\_L_{even}$ 、選択信号  $MD\_E_{odd}$ 、および  $MD\_E_{even}$  の駆動タイミングによって、画素回路  $750C(i, j)$  と、画素回路  $650C(i, j)$  に接続される走査線の選択制御ができる。

#### 【0123】

図 12(A) では図 10 の表示装置 702 の動作について図 11(A) とは異なるタイミングチャートを示す。ここでは、液晶表示領域 121 の表示と、発光表示領域 122 の表示が異なるタイミングで更新される例を示す。即ち、液晶表示領域 121 の表示と、発光表示領域 122 の表示の更新頻度が異なる例を示す。第 1 のフレーム F1、第 2 のフレーム F2 を用いて説明する。シフトレジスタ回路 111C の出力信号  $SRL(1)$  と、シフトレジスタ回路 111D の出力信号  $SRE(1)$  が  $High$  の期間について、タイミングチャートの動作を説明する。

#### 【0124】

一例として、第 1 のフレーム F1 では、ゲートドライバ  $110C$  とゲートドライバ  $110D$  は同じタイミングで動作しているため、シフトレジスタ回路 111C の出力信号  $SRL(1)$  と、シフトレジスタ回路 111D の出力信号  $SRE(1)$  は同じタイミングで出力されている。

#### 【0125】

シフトレジスタ回路 111C の出力信号  $SRL(1)$  と、選択信号  $MD\_L_{odd}$  とが  $High$  の期間は、判定回路 21 により第 1 の走査線  $G1(1)$  の走査信号に  $High$  が出力される。第 1 の走査線  $G1(1)$  の走査信号が  $High$  のとき、第 1 の表示素子  $750(i, 1)$  を有する画素回路  $750C(i, 1)$  の階調信号が更新される。

#### 【0126】

シフトレジスタ回路 111C の出力信号  $SRL(1)$  および選択信号  $MD\_L_{even}$  が  $High$  の期間は、判定回路 22 によって第 1 の走査線  $G1(2)$  の走査信号に  $High$  が出力される。第 1 の走査線  $G1(2)$  の走査信号が  $High$  のとき、画素回路  $750C(i, 2)$  の階調信号が更新される。

#### 【0127】

10

20

30

40

50

選択信号MD\_E<sub>ODD</sub>がLowの期間は、判定回路21により、出力信号SRE(1)の状態によらず、第2の走査線G2(1)の走査信号の出力はLowになる。選択信号MD\_E<sub>EVEN</sub>がLowの期間は、判定回路21により、出力信号SRE(1)の状態によらず、第2の走査線G2(1)の走査信号の出力はLowになる。

【0128】

一例として、第2のフレームF2では、ゲートドライバ110Cとゲートドライバ110Dは同じタイミングで動作しているため、シフトレジスタ回路111Cの出力信号SRL(1)と、シフトレジスタ回路111Dの出力信号SRE(1)は同じタイミングで出力されている。

【0129】

シフトレジスタ回路111Dの出力信号SRE(1)と、選択信号MD\_E<sub>ODD</sub>とがHighの期間は、判定回路21によって第2の走査線G2(1)の走査信号にHighが出力される。第2の走査線G2(1)の走査信号がHighのとき、画素回路650C(i, 1)の階調信号が更新される。

【0130】

シフトレジスタ回路111Dの出力信号SRE(1)および選択信号MD\_E<sub>EVEN</sub>がHighの期間は、判定回路22によって第2の走査線G2(2)の走査信号にHighが出力される。第2の走査線G2(2)の走査信号がHighのとき、第2の表示素子650(i, 2)を有する画素回路650C(i, 2)の階調信号だけ更新される。

【0131】

選択信号MD\_L<sub>ODD</sub>がLowの期間は、判定回路21により、出力信号SRL(1)の状態によらず、第1の走査線G1(1)の走査信号の出力はLowになる。選択信号MD\_L<sub>EVEN</sub>がLowの期間は、判定回路21によって、出力信号SRL(1)の状態によらず、第1の走査線G1(1)の走査信号の出力はLowになる。

【0132】

図12(B)では、第1のフレームF1と第2のフレームF2のタイミングで駆動したときの、液晶表示領域121と発光表示領域122の駆動状態を模式的に示す。

【0133】

第1のフレームF1では、液晶表示領域121は表示内容が更新され、発光表示領域122は表示内容が更新されない。第2のフレームF2では、液晶表示領域121は表示内容が更新されないが、発光表示領域122は表示内容が更新される。

【0134】

図12(B)は、表示部120の駆動状態を模式的に示す。シフトレジスタ回路111Cの出力信号SRL(1)乃至SRL(n/2)と、選択信号MD\_L<sub>ODD</sub>と、MD\_L<sub>EVEN</sub>とによって第1の走査線G1(1)乃至G1(n)の走査信号がHighになることで液晶表示領域121の表示内容が更新され、シフトレジスタ回路111Dの出力信号SRE(1)乃至SRE(n/2)と、選択信号MD\_E<sub>ODD</sub>と、MD\_E<sub>EVEN</sub>とにより、第2の走査線G2(1)乃至G2(n)の走査信号がHighになることで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図12(A)のタイミングチャートと対応している。

【0135】

第1のフレームF1では、液晶表示領域121は表示内容が更新され、発光表示領域122は表示内容が更新されない。

【0136】

一例として、シフトレジスタ回路111Cの出力信号SRL(1)がHighのときについて説明する。選択信号MD\_L<sub>ODD</sub>がHighのときに、選択回路20によって第1の走査線G1(1)の走査信号がHighになり、画素回路750C(1, 1)乃至画素回路750C(m, 1)が階調信号により表示内容が更新されることを示す。さらに選択信号MD\_L<sub>EVEN</sub>がHighのときに、選択回路20によって第1の走査線G1(2)の走査信号がHighになる。画素回路750C(1, 2)乃至画素回路750C(

10

20

30

40

50

m, 2) が階調信号により表示内容が更新されることを示す。

【0137】

同様に、シフトレジスタ回路111Dの出力信号SRE(1)がHighのときについて説明する。選択信号MD\_E<sub>ODD</sub>がLowのときに、選択回路20によって第2の走査線G2(1)の走査信号がLowになり、画素回路650C(1, 1)乃至画素回路650C(m, 1)の表示内容は更新されなかったことを示す。さらに選択信号MD\_E<sub>EVEN</sub>がLowのときに、選択回路20によって第2の走査線G2(2)の走査信号がLowになる。画素回路650C(1, 2)乃至画素回路650C(m, 2)の表示内容は更新されなかったことを示す。

【0138】

第2のフレームF2では、液晶表示領域121は表示内容が更新されないが、発光表示領域122は表示内容が更新される。

【0139】

一例として、シフトレジスタ回路111Cの出力信号SRL(1)がHighのときについて説明する。選択信号MD\_L<sub>ODD</sub>がLowのときに、選択回路20によって第1の走査線G1(1)の走査信号がLowになり、画素回路750C(1, 1)乃至画素回路750C(m, 1)の表示内容は更新されなかったことを示す。さらに選択信号MD\_L<sub>EVEN</sub>がLowのときに、選択回路20によって第1の走査線G1(2)の走査信号がLowになる。画素回路750C(1, 2)乃至画素回路750C(m, 2)の表示内容は更新されなかったことを示す。

10

20

【0140】

同様に、図10のシフトレジスタ回路111Dの出力信号SRE(1)がHighのときについて説明する。選択信号MD\_E<sub>ODD</sub>がHighのときに、選択回路20によって第2の走査線G2(1)の走査信号がHighになり、画素回路650C(1, 1)乃至画素回路650C(m, 1)が階調信号により表示内容が更新されることを示す。さらに選択信号MD\_E<sub>EVEN</sub>がHighのときに、選択回路20によって第2の走査線G2(2)の走査信号がHighになる。画素回路650C(1, 2)乃至画素回路650C(m, 2)が階調信号により表示内容が更新されることを示す。

【0141】

図12(A)の第1のフレームF1では、シフトレジスタ回路111Cの出力信号SRL(1)またはSRL(2)がHighの期間に、選択信号MD\_L<sub>ODD</sub>またはMD\_L<sub>EVEN</sub>がHighのときに液晶表示領域121の表示が更新される。第2のフレームF2では、シフトレジスタ回路111Dの出力信号SRE(1)またはSRE(2)がHighの期間に、選択信号MD\_E<sub>ODD</sub>またはMD\_E<sub>EVEN</sub>がHighのときに発光表示領域122の表示が更新される。

30

【0142】

図12(A)では、選択信号による走査線の選択制御によって、液晶表示領域121または発光表示領域122をフレーム単位で停止させる例を示したが、同様にフレーム単位でシフトレジスタ回路を停止させても同じ効果を得ることができる。

【0143】

40

さらに、画素回路750C(i, j)では静止画を、画素回路650C(i, j)では動画を再生するときに、静止画の場合は動画の場合に比べて表示内容の更新頻度を下げて駆動を行うなど、表示の内容に応じた最適な駆動を選択することができる。

【0144】

さらに、画素回路750C(i, j)および画素回路650C(i, j)をもつ高精細な表示部120を、最適な駆動を行うことにより消費電力の低減ができる。

【0145】

なお本発明の一様態は、選択回路20にて、偶数行と奇数行とを選択制御できるように示したが、選択回路にて選択できる行の数は2以上の整数でもよい。

【0146】

50

図13(A)では図10の表示装置702の動作について、図12(A)とは異なるタイミングチャートを示す。ここでは、表示装置において、第1の表示領域と第2の表示領域とを有し、第1の表示領域に含まれる表示素子の表示の更新頻度は、第2の表示領域に含まれる表示素子と異なる例を示す。具体的には、液晶表示領域121または発光表示領域122の一方は、全面において表示が順次更新されるが、他方は、部分的に表示が更新される例を示す。一例として第3のフレームF3を用いて説明する。シフトレジスタ回路111Cおよびシフトレジスタ回路111Dのj行目を中心に前後1行の動作をタイミングチャートで示す。

【0147】

一例として、シフトレジスタ回路111Cの出力信号SRL(j-1)、SRL(j)、およびSRL(j+1)と、シフトレジスタ回路111Dの出力信号SRE(j-1)、SRE(j)、およびSRE(j+1)が、Highの期間について、タイミングチャートの動作を説明する。

【0148】

第3のフレームF3では、ゲートドライバ110Cとゲートドライバ110Dは同じタイミングで動作している。シフトレジスタ回路111Cの出力信号SRL(j)と、シフトレジスタ回路111Dの出力信号SRE(j)とは同じタイミングで出力されている。

【0149】

図10のシフトレジスタ回路111Cが出力信号SRL(j-1)を選択回路20に与えたときの動作を説明する。選択信号MD\_L<sub>ODD</sub>がHighのときに、選択回路20によって第1の走査線G1(K-2)の走査信号がHighになり、画素回路750C(1, K-2)乃至画素回路750C(m, K-2)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_L<sub>EVEN</sub>がHighのときに、選択回路20によって第1の走査線G1(K-1)の走査信号がHighになり、画素回路750C(1, K-1)乃至画素回路750C(m, K-1)が階調信号により表示内容が更新されることを示す。

【0150】

図10のシフトレジスタ回路111Dが出力信号SRE(j-1)を選択回路20に与えたときの動作を説明する。選択信号MD\_E<sub>ODD</sub>がLowのときは、選択回路20によって第2の走査線G2(K-2)とG2(K-1)の走査信号がLowになり、画素回路650C(1, K-2)乃至画素回路650C(m, K-2)の表示内容が更新されなかったことを示す。さらに画素回路650C(1, K-1)乃至画素回路650C(m, K-1)の表示内容が更新されなかったことを示す。

【0151】

図10のシフトレジスタ回路111Cが出力信号SRL(j)を選択回路20に与えたときの動作を説明する。選択信号MD\_L<sub>ODD</sub>がHighのときに、選択回路20によって第1の走査線G1(K)の走査信号がHighになり、画素回路750C(1, K)乃至画素回路750C(m, K)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_L<sub>EVEN</sub>がHighのときに、選択回路20によって第1の走査線G1(K+1)の走査信号がHighになり、画素回路750C(1, K+1)乃至画素回路750C(m, K+1)が階調信号により表示内容が更新されることを示す。

【0152】

図10のシフトレジスタ回路111Dが出力信号SRE(j)を選択回路20に与えたときの動作を説明する。選択信号MD\_E<sub>ODD</sub>がHighのときに、選択回路20によって第2の走査線G2(K)の走査信号がHighになり、画素回路650C(1, K)乃至画素回路650C(m, K)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_E<sub>ODD</sub>がHighのときに、選択回路20によって第2の走査線G2(K+1)の走査信号がHighになり、画素回路650C(1, K+1)乃至画素回路650C(m, K+1)が階調信号により表示内容が更新されることを示す。

【0153】

10

20

30

40

50

図10のシフトレジスタ回路111Cが出力信号SRL(j+1)を選択回路20に与えたときの動作を説明する。選択信号MD\_L<sub>ODD</sub>がHighのときに、選択回路20によって第1の走査線G1(K+2)の走査信号がHighになり、画素回路750C(1, K+2)乃至画素回路750C(m, K+2)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_L<sub>EVEN</sub>がHighのときに、選択回路20によって第1の走査線G1(K+3)の走査信号がHighになり、画素回路750C(1, K+3)乃至画素回路750C(m, K+3)が階調信号により表示内容が更新されることを示す。

#### 【0154】

図10のシフトレジスタ回路111Dが出力信号SRE(j+1)を選択回路20に与えたときの動作を説明する。選択信号MD\_E<sub>ODD</sub>がLowのときは、選択回路20によって第2の走査線G2(K+2)とG2(K+1)の走査信号がLowになり、画素回路650C(1, K+2)乃至画素回路650C(m, K+2)の表示内容が更新されなかったことを示す。さらに画素回路650C(1, K+3)乃至画素回路650C(m, K+3)の表示内容が更新されなかったことを示す。

#### 【0155】

第3のフレームF3では、液晶表示領域121は表示内容が順次更新されるが、発光表示領域122は、出力信号SRE(j)の表示内容だけが更新される。

#### 【0156】

図13(B)は、表示部120の駆動状態を模式的に示す。シフトレジスタ回路111Cの出力信号SRL(1)乃至SRL(n/2)と、選択信号MD\_L<sub>ODD</sub>と、MD\_L<sub>EVEN</sub>とによって第1の走査線G1(1)乃至G1(n)の走査信号がHighになることで液晶表示領域121の表示内容が更新され、シフトレジスタ回路111Dの出力信号SRE(1)乃至SRE(n/2)と、選択信号MD\_E<sub>ODD</sub>と、MD\_E<sub>EVEN</sub>とにより、第2の走査線G2(1)乃至G2(n)の走査信号がHighになることで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図13(A)のタイミングチャートと対応している。

#### 【0157】

図13(B)では、選択信号により、特定の表示領域だけ表示内容を更新することができる。

#### 【0158】

一例として、画素回路750C(i, j)では液晶表示領域121のすべてに静止画を表示し、画素回路650C(i, j)では特定の発光表示領域122Aのみ動画を再生することができる。静止画を表示するときは、動画を表示するときに比べて表示内容の更新頻度を下げて駆動を行うなど、表示の内容に合わせた最適な駆動を選択することができる。

#### 【0159】

画素回路750C(i, j)および画素回路650C(i, j)を有する高精細な表示部120を、最適な駆動を行うことにより、表示内容の更新頻度を最適化することで消費電力の低減ができる。

#### 【0160】

なお本発明の一様態は、選択回路20にて、偶数行と奇数行とを選択制御できるように示したが、選択回路にて選択できる行の数は2以上の整数でもよい。

#### 【0161】

図14(A)乃至(D)には、図1、図7、図10に示す回路で可能な動作パターンの一例を示す。

#### 【0162】

図14(B)は、液晶表示領域121と発光表示領域122とを交互に1行ずつ間隔をあけて表示を更新することができる。液晶表示領域121または発光表示領域122のどちらかだけの表示を更新してもよい。高い階調を有し、画素サイズの精細度が高い表示装

10

20

30

40

50

置の場合、より長い書き込み時間を確保することで表示の品位を高めることができる。

【0163】

図14(C)は、液晶表示領域121と発光表示領域122とを4フレームに1回だけ表示内容を更新することができる。表示内容の更新頻度を下げて消費電力をより小さくすることができる。

【0164】

図14(D)は、図14(C)の動作に、さらに発光表示領域122の特定の領域の表示内容を更新する動作を組み合わせることができる。停止画を表示する液晶表示領域121では、表示内容の更新頻度を下げて消費電力を小さくし、特定の領域では動画表示に適した表示内容の更新をすることができる。動画再生を行う特定の領域は、図14(B)の駆動パターンを組み合わせることで、さらに消費電力を抑えることができる。

10

【0165】

画素回路750C(i, j)および画素回路650C(i, j)を有する高精細な表示部を、選択信号MD\_L<sub>ODD</sub>、選択信号MD\_L<sub>EVEN</sub>、選択信号MD\_E<sub>ODD</sub>、選択信号MD\_E<sub>EVEN</sub>、および選択回路20により、走査線の駆動するタイミングを制御することができる。さらに表示内容に応じた最適な更新頻度を制御することができる。さらに、図14(A)乃至(D)に示すように、液晶表示領域121および発光表示領域122の特定の領域における表示内容の更新を、走査線の選択制御により自由に制御することができる。

【0166】

20

以上、本実施の形態で示す構成、方法、駆動タイミングは、他の実施の形態で示す構成、方法、駆動タイミングと適宜組み合わせて用いることができる。

【0167】

(実施の形態4)

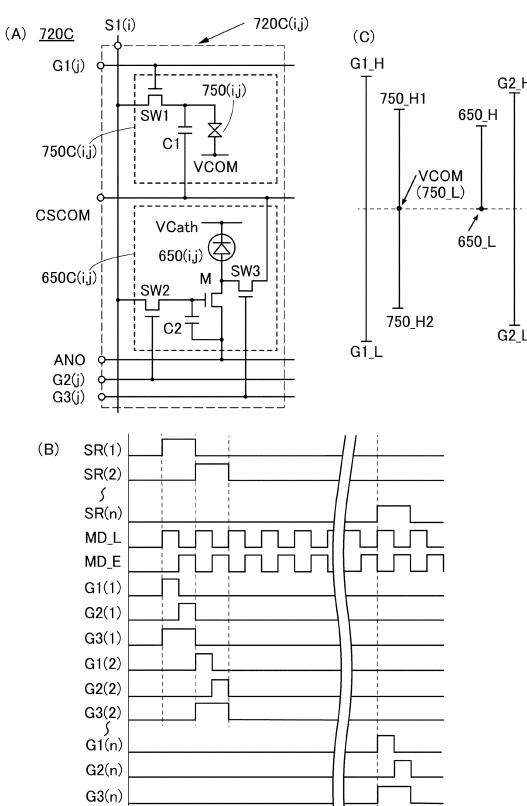

本実施の形態では、第1の表示素子を有する画素回路および第2の表示素子を有する画素回路に、電気的に接続される信号線から階調信号を与える機能を有する表示装置について、図15乃至図19を用いて説明する。

【0168】

図15に、画素回路720Cの構成例を示す。図16の表示装置700の表示部120の、画素の一つを、画素回路720C(i, j)として説明する。表示部120は、列方向にn個(nは1以上の整数)、行方向にm個(mは1以上の整数)、合計m×n個の画素がマトリクス状に配置されている。なおiは1以上m以下の整数であり、jは1以上n以下の整数である。

30

【0169】

画素回路720C(i, j)は、画素回路750C(i, j)を有し、画素回路750C(i, j)は、第1の表示素子750(i, j)を有する。第1の表示素子750(i, j)は、一例として焼き付きを防止するために交流駆動される液晶素子が好ましい。

【0170】

画素回路720C(i, j)は、画素回路650C(i, j)を有し、画素回路650C(i, j)は、第2の表示素子650(i, j)を有する。第2の表示素子650(i, j)は、一例として直流駆動される発光素子が好ましい。

40

【0171】

画素回路750C(i, j)のトランジスタSW1のゲートは、第1の走査線G1(j)と電気的に接続される。トランジスタSW1のソースまたはドレインの一方は、信号線S1(i)と電気的に接続される。

【0172】

信号線S1(i)から与えられる第1の階調信号により、第1の画素電極と、第1の対向電極との間に生成された電圧により、第1の表示素子750(i, j)の階調が制御される機能を有している。

【0173】

50

画素回路 650C (i, j) のトランジスタ SW2 のゲートは、第 2 の走査線 G2 (j) と電気的に接続される。トランジスタ SW2 のソースまたはドレインの一方が信号線 S1 (i) と電気的に接続される。

【0174】

信号線 S1 (i) から与えられる第 2 の階調信号によって制御されるトランジスタ M により、駆動電流は制御される。第 2 の表示素子 650 (i, j) に流れる駆動電流により、第 2 の表示素子 650 (i, j) の階調が制御される機能を有している。

【0175】

図 16 は、表示装置 700 の構成を示すブロック図である。表示装置 700 はゲートドライバ 110、選択信号出力回路 30、および表示部 120 を有する。ゲートドライバ 110 は、シフトレジスタ回路 111 および選択回路 20 を有する。選択回路 20 は、判定回路 21 および 22 を有する。表示部 120 は、画素回路 720C (1, 1) 乃至画素回路 720C (m, n) を有する。画素回路 720C (m, n) は、画素回路 750C (m, n) および画素回路 650C (m, n) を有する。

【0176】

本実施の形態で説明する表示部 120 は、画素回路 720C (1, 1) 乃至画素回路 720C (m, n) と、第 1 の走査線 G1 (1) 乃至 G1 (n) と、第 2 の走査線 G2 (1) 乃至 G2 (n) と、信号線 S1 (1) 乃至 S1 (m) とを有する。

【0177】

選択回路 20 は、図 4 と同じため説明を省略する。

【0178】

図 17 (A) は、図 16 の表示装置 700 の動作についてタイミングチャートを示す。図 16 のゲートドライバ 110 は、シフトレジスタ回路 111 から出力信号 SR (1) 乃至 SR (n) が順次出力される。

【0179】

画素回路 750C (i, j) と電気的に接続される第 1 の走査線 G1 (j) に出力する走査信号は、シフトレジスタ回路 111 の出力信号 SR (j) および選択信号出力回路 30 の選択信号 MD\_L から、選択回路 20 の判定回路 21 により生成される。

【0180】

画素回路 650C (i, j) と電気的に接続される第 2 の走査線 G2 (j) に出力する走査信号は、シフトレジスタ回路 111 の出力信号 SR (j) および選択信号出力回路 30 の選択信号 MD\_E から、選択回路 20 の判定回路 22 により生成される。

【0181】

一例として、図 17 (A) に示すタイミングチャートを用いて、出力信号 SR (1) が High の期間における、ゲートドライバ 110 の動作について説明する。

【0182】

シフトレジスタ回路 111 の出力信号 SR (1) が High の期間において、選択信号 MD\_L が High の期間に、第 1 の走査線 G1 (1) の走査信号が High になり、画素回路 750C (i, 1) と電気的に接続された信号線 S1 (1) 乃至 S1 (m) により、画素回路 750C (i, 1) へ階調信号を書き込むことができる。

【0183】

シフトレジスタ回路 111 の出力信号 SR (1) が High の期間において、選択信号 MD\_E が High の期間に、第 2 の走査線 G2 (1) の走査信号が High になり、画素回路 650C (i, 1) と電気的に接続された信号線 S1 (1) 乃至 S1 (m) により、画素回路 650C (i, 1) へ階調信号を書き込みができる。

【0184】

図 17 (B) は、表示部 120 の駆動状態を模式的に示す。画素回路 750C (i, j) により表示された領域を液晶表示領域 121 とし、画素回路 650C (i, j) により表示された領域を発光表示領域 122 とする。

【0185】

10

20

30

40

50

図16のシフトレジスタ回路111の出力信号SR(j)、選択信号MD\_L、選択信号MD\_E、および選択回路20によって、第1の走査線G1(j)に走査信号を出力することで、液晶表示領域121の表示内容が更新され、さらに第2の走査線G2(j)に走査信号を出力することで発光表示領域122の表示内容が更新される。したがって表示が更新される順番は、図17(A)のタイミングチャートと対応している。

#### 【0186】

図17(B)は、出力信号SR(1)がHighの期間について説明する。選択信号MD\_LがHighの期間に、選択回路20によって第1の走査線G1(1)の走査信号がHighになる。したがって、画素回路750C(1,1)乃至画素回路750C(m,1)の表示内容は、階調信号によって更新される。

10

#### 【0187】

出力信号SR(1)がHighの期間、かつ選択信号MD\_EがHighの期間に、選択回路20によって第2の走査線G2(1)の走査信号がHighになる。したがって、画素回路650C(1,1)乃至画素回路650C(m,1)の表示内容は、階調信号によって更新される。

#### 【0188】

図17(A)では、出力信号SR(1)がHighの期間に、先に選択信号MD\_LがHighになり、続いて選択信号MD\_EがHighになる。図17(B)では、選択信号MD\_LがHighの期間に、液晶表示領域121の表示が先に更新されることを示す。続いて、選択信号MD\_EがHighの期間に発光表示領域122の表示が更新されることを示す。

20

#### 【0189】

図16に示す回路では、第1の走査線G1と、第2の走査線G2とは異なるタイミングで走査信号がHighになることで、信号線に与えられる第1の階調信号と、第2の階調信号とは、お互いに影響を及ぼさない。

#### 【0190】

画素回路750C(i,1)のトランジスタSW1のゲートと電気的に接続する第1の走査線G1(1)、および画素回路650C(i,1)のトランジスタSW2のゲートと電気的に接続する第2の走査線G2(1)は、シフトレジスタ回路111、および選択回路20を有するゲートドライバ110で、走査線の選択を制御することができる。

30

#### 【0191】

信号線S1(i)には、画素回路750C(i,1)の階調信号と、画素回路650C(i,1)の階調信号を与えることができる。

#### 【0192】

図15に示す画素回路720C(i,j)では、画素回路650C(i,j)の有する第2の表示素子650(i,j)の抵抗成分がばらつくと、トランジスタMのドレインとソース間の電圧が追従してばらつく。トランジスタMのドレインはアノード電圧で固定され、第2の表示素子650(i,j)の対向電極はカソード電圧で固定されているため、トランジスタMのソース電圧にはばらつきが生じる。トランジスタMのソース電圧にはばらつきが生じると、トランジスタMのソースとゲート間にかかる電圧がばらつくため、駆動電流がばらつき、階調は正しく制御されない。

40

#### 【0193】

表示素子650(i,j)を正しい階調で制御するためには、トランジスタMのソース電圧を基準として、トランジスタMのゲートに第2の階調信号によって生成された電圧を与える必要がある。

#### 【0194】

図18(A)乃至図18(C)を用いて、画素回路650C(i,j)の有する第2の表示素子650(i,j)の抵抗成分のばらつきに影響を受けずに、駆動電流を制御する動作について説明する。図18(A)が図15と異なる点を示す。図18(A)では画素回路650C(i,j)が、トランジスタSW3を有している。

50

## 【0195】

トランジスタ SW3 のソースまたはドレインの一方は、トランジスタ M のソースと電気的に接続されている。トランジスタ SW3 のソースまたはドレインの他方は C S C O M 端子に電気的に接続されている。トランジスタ SW3 のゲートには、第 3 の走査線 G3 ( j ) が電気的に接続されている。

## 【0196】

第 3 の走査線は、シフトレジスタ回路 111 の出力信号 SR が第 3 の走査信号として与えられている。

## 【0197】

図 18 ( B ) を用いて、画素回路 650C ( i , j ) が有する第 2 の表示素子 650 ( i , j ) の抵抗成分のばらつきに影響を受けずに、駆動電流を制御する動作についてタイミングチャートを用いて説明する。第 1 の走査信号が High の期間、第 3 の走査線 G3 にはシフトレジスタ回路 111 の出力信号 SR ( j ) が第 3 の走査信号として与えられる。トランジスタ SW3 のゲートが High となり、トランジスタ M のソースは C S C O M 端子を介してコモン電圧が与えられる。

## 【0198】

トランジスタ M のソースと、第 2 の画素電極とは電気的に接続されているため、第 2 の画素電極と、第 2 の対向電極との間には第 2 の表示素子 650 ( i , j ) を介して電流が流れる。第 2 の表示素子 650 ( i , j ) の発光に寄与しない大きさの電流になるよう、第 2 の表示素子 650 ( i , j ) の電気的特性からコモン電圧を決めることが望ましい。

## 【0199】

出力信号 SR ( j ) が High の期間、トランジスタ M のソースにコモン電圧が与えられる。画素回路 750C ( i , j ) の有する第 1 の表示素子 750 ( i , j ) が、第 1 の階調信号により階調が変化する期間、画素回路 650C ( i , j ) の第 2 の表示素子 650 ( i , j ) は発光に必要な電流が与えられないため、消灯している。

## 【0200】

第 2 の走査信号が High になり、画素回路 650C ( i , j ) に階調信号を書き込む期間も、トランジスタ M のソースはコモン電圧で固定されている。そのため画素回路 650C ( i , j ) にはコモン電圧を基準とした階調信号が正しく与えられる。

## 【0201】

図 18 ( C ) に、図 18 ( A ) の信号の電圧関係を示す。まず、走査信号について説明をする。第 1 の走査信号の High の期間に与えられる高い電圧を G1\_H とし、 Low の期間に与えられる低い電圧を G1\_L とする。第 2 の走査信号の High の期間に与えられる高い電圧を G2\_H とし、 Low の期間に与えられる低い電圧を G2\_L とする。一例として G1\_H と G2\_H 、および G1\_L と G2\_L が異なる電圧の例を示したが、それぞれを同じ電圧にすると電源の数を減らすことができるので回路規模を小さくできる。

## 【0202】

階調信号について説明をする。一例として第 1 の表示素子 750 ( i , j ) が反転駆動を行う液晶素子について示す。第 1 の画素電極と、第 1 の対向電極が、ともにコモン電圧の時に表示が黒の階調を示すとき、第 1 の階調信号から生成されるもっとも大きな電圧を 750\_H1 とし、反転駆動時の第 1 の階調信号から生成されるもっとも小さな電圧を 750\_H2 とする。750\_L は、コモン電圧とする。第 2 の階調信号から生成されるもっとも大きな電圧を 650\_H とし、第 2 の階調信号から生成されるもっとも小さな電圧を 650\_L とする。

## 【0203】

図 18 ( C ) では、650\_L には、750\_L と同じコモン電圧を与えたが、650\_L としては、カソード端子に流れる電流が第 2 の表示素子 650 ( i , j ) の発光に寄与しない大きさとなるような電圧が与えられることが好ましい。第 2 の表示素子 650 (

i, j) の電気的特性から 650\_L に与えるコモン電圧が求められることが好ましい。

【0204】

図18(C)に示していない信号の電圧について示す。A N O 端子に与えられるアノード電圧は、650\_Hよりも大きな電圧が与えられ、V C a t h 端子に与えられるカソード電圧は、650\_Lよりも小さな電圧が与えられる。

【0205】

図18(A)で示した回路では、画素回路 650\_C (i, j) の有する第2の表示素子 650 (i, j) の抵抗成分のばらつきに影響を受けないよう駆動電流を制御する回路を追加しなくても、画素回路 750\_C (i, j) が有する容量素子 C1 の基準電圧であるコモン電圧を利用することで、新規な配線を追加せずに、表示品質を改善することができる

10

。

【0206】

図18(A)で示した回路では、画素回路 650\_C (i, j) が有する第2の表示素子 650 (i, j) の抵抗成分のばらつきに影響を受けないよう駆動電流を制御する回路を追加しなくても、第1の走査線 G1 と、第2の走査線 G2 とは異なるタイミングで走査信号が H i g h になることで、信号線に与えられる第1の階調信号と、第2の階調信号とは、お互いに影響を及ぼさない。

【0207】

なお本発明の一様態は図15の画素回路 720\_C (i, j) の回路構成に限らない。図 15 とは異なる画素回路 720\_C (i, j) が有する、画素回路 750\_C (i, j) 及び画素回路 650\_C (i, j) の回路構成の一例について図19に図示する。

20

【0208】

図19は、図3(C)が有する画素回路 750\_C (i, j) 及び画素回路 650\_C (i, j) と異なる点を示す。図19のトランジスタ SW1\_2 のバックゲートと、トランジスタ SW2\_2 のバックゲートは、B G L 1 端子と接続されている。バックゲートの電圧を B G L 1 端子から与えることができる。B G L 1 端子に与える電圧は、B G L 端子に与える電圧と同じでもよいし、異なる電圧でもよい。

【0209】

なお本発明の一様態は図19の画素回路 720\_C (i, j) の回路構成に限らない。他の端子をバックゲートと電気的に接続もできるし、接続の方法を組み合わせることもできる。

30

【0210】

以上、本実施の形態で示す構成、方法、駆動タイミングは、他の実施の形態で示す構成、方法、駆動タイミングと適宜組み合わせて用いることができる。

【0211】

(実施の形態 5)

本実施の形態では、画素回路 720\_C を有する高精細な表示を行う表示装置において、ゲートドライバを、奇数行と偶数行とに構成を分けて制御する方法について、図20および図21を用いて説明する。

40

【0212】

図20は、表示装置 701 の構成を示すブロック図である。図16と異なるのは、ゲートドライバ 110 が、図20では奇数行の走査線を制御するゲートドライバ 110\_A と、偶数行の走査線を制御するゲートドライバ 110\_B とに構成が分かれている点である。

【0213】

図20の表示装置 701 が有するシフトレジスタ回路 111\_A、およびシフトレジスタ回路 111\_B は、図16のシフトレジスタ回路 111 の出力信号 S R とは異なるタイミングの出力信号 S R \_ O D D および S R \_ E V E N を生成する。

【0214】

図20の表示装置 701 は、ゲートドライバを奇数行制御および偶数行制御に構成を分けることで、ゲートドライバの段数が半分になり、回路の面積も半分になる。第1の走査

50

線 G 1 の走査信号および第 2 の走査線 G 2 の走査信号を駆動する選択回路 2 0 のバッファ回路 2 6 を大きくすることができ、電流供給能力を上げることができる。図 2 0 で示す  $n$  は整数で、かつ 2 以上の偶数とする。

#### 【 0 2 1 5 】

図 2 1 ( A ) では、図 2 0 の表示装置 7 0 1 の動作についてタイミングチャートを示す。図 2 1 ( A ) に示すタイミングチャートでは、図 1 7 ( A ) に示すタイミングチャートと同じように選択信号 MD\_L および選択信号 MD\_E を入力している。これにより、図 1 7 ( A ) に示すタイミングチャートと同じタイミングで第 1 の走査線 G 1 ( 1 ) 乃至 G 1 ( n ) 、第 2 の走査線 G 2 ( 1 ) 乃至 G 2 ( n ) に電圧が与えられる。

#### 【 0 2 1 6 】

図 2 1 ( B ) は、表示部 1 2 0 の駆動状態を模式的に示す。図 1 7 ( B ) とは異なり、図 2 0 のゲートドライバ 1 1 0 A が有するシフトレジスタ回路 1 1 1 A の出力信号 SR<sub>0 DD</sub> ( 1 ) 乃至 SR<sub>0 DD</sub> ( n / 2 ) 、ゲートドライバ 1 1 0 B が有するシフトレジスタ回路 1 1 1 B の出力信号 SR<sub>E V E N</sub> ( 1 ) 乃至 SR<sub>E V E N</sub> ( n / 2 ) 、選択信号 MD\_L 、および選択信号 MD\_E によって、第 1 の走査線 G 1 ( 1 ) 乃至 G 1 ( n ) の走査信号が High になることで、液晶表示領域 1 2 1 の表示内容が更新される。さらに第 2 の走査線 G 2 ( 1 ) 乃至 G 2 ( n ) の走査信号が High になることで、発光表示領域 1 2 2 の表示内容が更新される。したがって表示が更新される順番は、図 2 1 ( A ) のタイミングチャートと対応している。

#### 【 0 2 1 7 】

一例として、図 2 0 のシフトレジスタ回路 1 1 1 A の出力信号 SR<sub>0 DD</sub> ( 1 ) が High の期間について説明する。選択信号 MD\_L が High の期間に、選択回路 2 0 によって第 1 の走査線 G 1 ( 1 ) の走査信号が High になる。画素回路 7 5 0 C ( 1 , 1 ) 乃至画素回路 7 5 0 C ( m , 1 ) が階調信号により表示内容が更新されることを示す。

#### 【 0 2 1 8 】

図 2 0 のシフトレジスタ回路 1 1 1 A の出力信号 SR<sub>0 DD</sub> ( 1 ) が High の期間かつ選択信号 MD\_E が High の期間に、選択回路 2 0 によって第 2 の走査線 G 2 ( 1 ) の走査信号が High になる。画素回路 6 5 0 C ( 1 , 1 ) 乃至画素回路 6 5 0 C ( m , 1 ) が階調信号により表示内容が更新されることを示す。

#### 【 0 2 1 9 】

図 2 1 ( A ) では、ゲートドライバ 1 1 0 A が有するシフトレジスタ回路 1 1 1 A の出力信号 SR<sub>0 DD</sub> ( 1 ) が High の期間に、先に選択信号 MD\_L が High になり、続いて選択信号 MD\_E が High になる。図 2 1 ( B ) では、選択信号 MD\_L が High の期間に、液晶表示領域 1 2 1 の表示が先に更新されることを示す。続いて、選択信号 MD\_E が High の期間に発光表示領域 1 2 2 の表示が更新されることを示す。

#### 【 0 2 2 0 】

第 1 の走査線 G 1 ( j ) または第 2 の走査線 G 2 ( j ) は、シフトレジスタ回路 1 1 1 A 、および選択回路 2 0 を有するゲートドライバ 1 1 0 A で、走査線の選択を制御することができる。

#### 【 0 2 2 1 】

図 2 0 の表示装置 7 0 1 は、奇数行を制御するゲートドライバ 1 1 0 A および偶数行を制御するゲートドライバ 1 1 0 B に分けた構成においても、選択信号出力回路 3 0 による選択信号 MD\_L および選択信号 MD\_E を制御することで、図 1 6 の表示装置 7 0 0 と同じタイミングで動作させることができる。

#### 【 0 2 2 2 】

画素回路 7 2 0 C は、画素回路 7 5 0 C ( i , j ) および画素回路 6 5 0 C ( i , j ) の信号線 S 1 ( j ) を共有することで、より高精細な表示を行う表示装置を駆動することができる。さらにバッファ回路を大きくすることで、電流供給能力が向上するため、4 K や 8 K などの大きな解像度と、表示領域とをもつ表示装置を駆動することができる。

#### 【 0 2 2 3 】

10

20

30

40

50

図20で示した回路では、第1の走査線G1と、第2の走査線G2とは異なるタイミングで走査信号がHighになることで、信号線に与えられる第1の階調信号と、第2の階調信号とは、お互いに影響を及ぼさない。

#### 【0224】

以上、本実施の形態で示す構成、方法、駆動タイミングは、他の実施の形態で示す構成、方法、駆動タイミングと適宜組み合わせて用いることができる。

#### 【0225】

##### (実施の形態6)

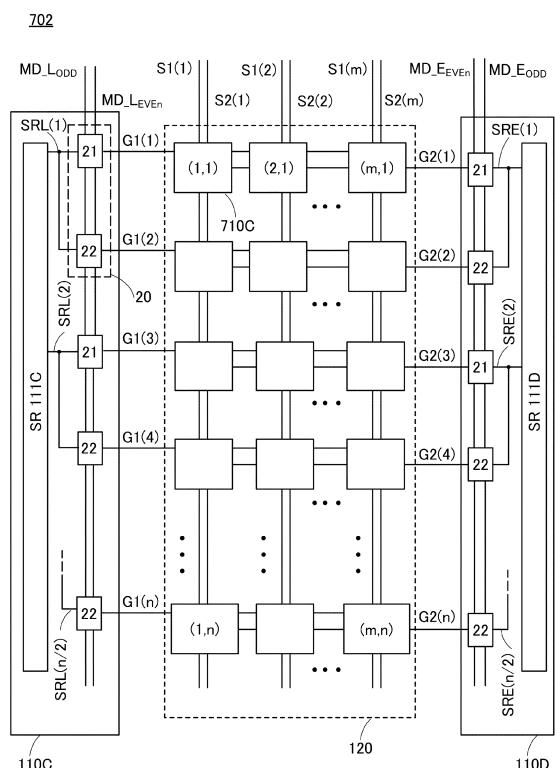

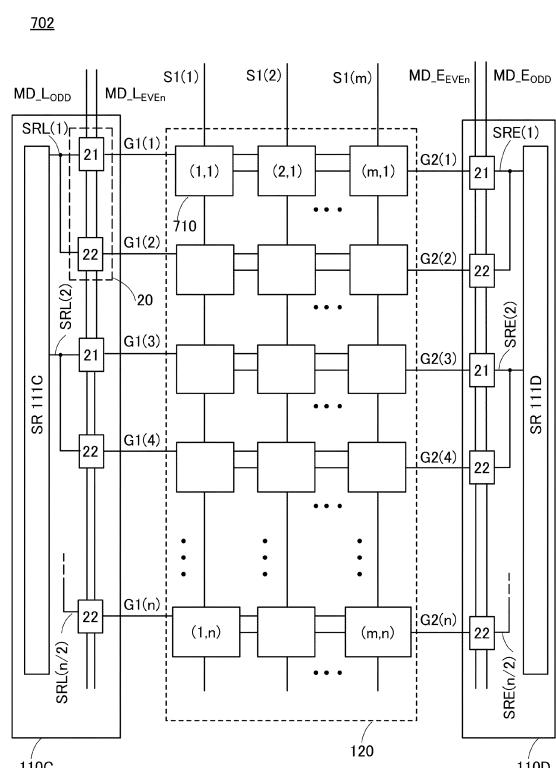

本実施の形態では、画素回路720Cを有する高精細な表示を行う表示装置において、液晶表示領域121および発光表示領域122を、異なる更新頻度で制御するゲートドライバの駆動方法について、図22乃至図26を用いて説明する。

#### 【0226】

図22は、表示装置702の構成を示すブロック図である。図16と異なるのは、ゲートドライバ110が、図22では液晶表示領域121の走査線を制御するゲートドライバ110Cと、発光表示領域122の走査線を制御するゲートドライバ110Dとに構成が分かれている点である。さらに、選択回路20の出力信号は、奇数行の走査線と偶数行の走査線に出力される。

#### 【0227】

図22の有する表示装置702のゲートドライバ110Cは液晶表示領域121の走査線を、ゲートドライバ110Dは発光表示領域122の走査線を、独立して選択制御することができる。図22で示すnは整数で、かつ2以上の偶数とする。

#### 【0228】

図23(A)は、図22の表示装置702の動作について、タイミングチャートを示す。一例として、シフトレジスタ回路111Cの出力信号SRL(1)、およびシフトレジスタ回路111Dの出力信号SRE(1)がHighの期間について、タイミングチャートの動作を説明する。

#### 【0229】

図22のシフトレジスタ回路111Cの出力信号SRL(1)がHighの期間において、選択信号MD\_L\_O\_D\_DがHighの期間に第1の走査線G1(1)の走査信号がHighになり、信号線S1(1)乃至S1(m)により、画素回路750C(i, 1)へ階調信号を書き込むことができる。

#### 【0230】

図22のシフトレジスタ回路111Cの出力信号SRL(1)がHighの期間において、選択信号MD\_L\_E\_V\_E\_NがHighの期間に第1の走査線G1(2)の走査信号がHighになり、信号線S1(1)乃至S1(m)により、画素回路750C(i, 2)へ階調信号を書き込むことができる。

#### 【0231】

図22のシフトレジスタ回路111Dの出力信号SRE(1)がHighの期間において、選択信号MD\_E\_O\_D\_DがHighの期間に第2の走査線G2(1)の走査信号がHighになり、信号線S1(1)乃至S1(m)により、画素回路650C(i, 1)へ階調信号を書き込みができる。

#### 【0232】

図22のシフトレジスタ回路111Dの出力信号SRE(1)がHighの期間において、選択信号MD\_E\_E\_V\_E\_NがHighの期間に第2の走査線G2(2)の走査信号がHighになり、信号線S1(1)乃至S1(m)により、画素回路650C(i, 2)へ階調信号の書き込みができる。

#### 【0233】

図23(B)は、液晶表示領域121と発光表示領域122の駆動状態を模式的に示す。シフトレジスタ回路111Cの出力信号SRL(1)乃至SRL(n/2)と、選択信号MD\_L\_O\_D\_DとMD\_L\_E\_V\_E\_Nと、ゲートドライバ110Dの有するシフトレジス

10

20

30

40

50

タ回路 111D の出力信号 SRE(1) 乃至 SRE(n/2) と、選択信号 MD\_E<sub>OD</sub><sub>D</sub> と MD\_E<sub>EVEN</sub> とにより、液晶表示領域 121 および発光表示領域 122 の表示内容が更新される順番を示す。

【0234】

図 23(B) は、表示部 120 の表示内容の更新状態を模式的に示す。シフトレジスタ回路 111C の出力信号 SRL(1) 乃至 SRL(n/2) と、選択信号 MD\_L<sub>ODD</sub> と、MD\_L<sub>EVEN</sub> とによって第 1 の走査線 G1(1) 乃至 G1(n) の走査信号に High が output されたことで液晶表示領域 121 の表示内容が更新され、シフトレジスタ回路 111D の出力信号 SRE(1) 乃至 SRE(n/2) と、選択信号 MD\_E<sub>ODD</sub> と、MD\_E<sub>EVEN</sub> とにより、第 2 の走査線 G2(1) 乃至 G2(n) の走査信号に High を output することで発光表示領域 122 の表示内容が更新される。したがって表示が更新される順番は、図 23(A) のタイミングチャートと対応している。

【0235】

一例として、図 22 のシフトレジスタ回路 111C の出力信号 SRL(1) が High のときについて説明する。選択信号 MD\_L<sub>ODD</sub> が High のときに、選択回路 20 によって第 1 の走査線 G1(1) の走査信号が High になり、画素回路 750C(1, 1) 乃至画素回路 750C(m, 1) が階調信号により表示内容が更新されることを示す。さらに選択信号 MD\_L<sub>EVEN</sub> が High のときに、選択回路 20 によって第 1 の走査線 G1(2) の走査信号が High になる。画素回路 750C(1, 2) 乃至画素回路 750C(m, 2) が階調信号により表示内容が更新されることを示す。

【0236】

同様に、図 22 のシフトレジスタ回路 111D の出力信号 SRE(1) が High のときについて説明する。選択信号 MD\_E<sub>ODD</sub> が High のときに、選択回路 20 によって第 2 の走査線 G2(1) の走査信号が High になり、画素回路 650C(1, 1) 乃至画素回路 650C(m, 1) が階調信号により表示内容が更新されることを示す。さらに選択信号 MD\_E<sub>EVEN</sub> が High のときに、選択回路 20 によって第 2 の走査線 G2(2) の走査信号が High になる。画素回路 650C(1, 2) 乃至画素回路 650C(m, 2) が階調信号により表示内容が更新されることを示す。

【0237】

図 22 で示した回路では、第 1 の走査線 G1 と、第 2 の走査線 G2 とは異なるタイミングで走査信号が High になることで、信号線 S1 に与えられる第 1 の階調信号と、第 2 の階調信号とは、お互いに影響を及ぼさないことを示す。

【0238】

表示装置 702 のゲートドライバは、液晶表示領域 121 または発光表示領域 122 を独立して制御するために構成をわけた。さらに奇数行と、偶数行とを選択回路 20 で制御する構成とした。さらに選択信号 MD\_L<sub>ODD</sub>、MD\_L<sub>EVEN</sub>、選択信号 MD\_E<sub>ODD</sub>、および MD\_E<sub>EVEN</sub> の駆動タイミングによって、画素回路 750C(i, j) と、画素回路 650C(i, j) に接続される走査線の選択制御ができる。

【0239】

図 24(A) 及び図 25(A) では図 22 の表示装置 702 の動作について図 23(A) とは異なるタイミングチャートを示す。ここでは、液晶表示領域 121 の表示と、発光表示領域 122 の表示が異なるタイミングで更新される例を示す。即ち、液晶表示領域 121 の表示と、発光表示領域 122 の表示の更新頻度が異なる例を示す。図 24(A) では、シフトレジスタ回路 111C の出力信号 SRL(1)、およびゲートドライバ 110D の有するシフトレジスタ回路 111D の出力信号 SRE(1) がそれぞれ High の期間について、タイミングチャートの動作を説明する。

【0240】

シフトレジスタ回路 111C の出力信号 SRL(1) と、選択信号 MD\_L<sub>ODD</sub> とが High の期間は、判定回路 21 により第 1 の走査線 G1(1) の走査信号に High を出力する。第 1 の走査線 G1(1) の走査信号が High の期間に、画素回路 750C(

10

20

30

40

50

i, 1) の階調信号が更新される。

【0241】

シフトレジスタ回路111Cの出力信号SRL(1)および選択信号MD\_L\_E\_V\_E\_NがHighの期間は、判定回路22によって第1の走査線G1(2)の走査信号にHighを出力する。第1の走査線G1(2)の走査信号がHighのとき、画素回路750C(i, 2)の階調信号が更新される。

【0242】

選択信号MD\_E\_O\_D\_DがLowの期間は、判定回路21により、出力信号SRE(1)の状態によらず、第2の走査線G2(1)の走査信号の出力はLowになる。選択信号MD\_E\_E\_V\_E\_NがLowの期間は、判定回路21により、出力信号SRE(1)の状態によらず、第2の走査線G2(1)の走査信号の出力はLowになる。

10

【0243】

図24(B)では、液晶表示領域121と発光表示領域122の駆動状態を模式的に示す。

【0244】

図24(B)は、表示部120の駆動状態を模式的に示す。シフトレジスタ回路111Cの出力信号SRL(1)乃至SRL(n/2)と、選択信号MD\_L\_O\_D\_Dと、MD\_L\_E\_V\_E\_Nとによって第1の走査線G1(1)乃至G1(n)の走査信号がHighになることで液晶表示領域121の表示内容が更新される。

【0245】

シフトレジスタ回路111Dの出力信号SRE(1)乃至SRE(n/2)と、選択信号MD\_E\_O\_D\_Dと、MD\_E\_E\_V\_E\_Nとにより、第2の走査線G2(1)乃至G2(n)の走査信号はLowになることで、発光表示領域122の表示内容は更新されない。

20

【0246】

図24(B)では、液晶表示領域121は表示内容が更新され、発光表示領域122は表示内容が更新されないため、図24(A)のタイミングチャートと対応している。

【0247】

図25(A)では、シフトレジスタ回路111Cの出力信号SRL(1)と、シフトレジスタ回路111Dの出力信号SRE(1)とがHighの期間について、タイミングチャートの動作を説明する。

30

【0248】

一例として、シフトレジスタ回路111Dの出力信号SRE(1)と、選択信号MD\_E\_O\_D\_DとがHighの期間は、判定回路21によって第2の走査線G2(1)の走査信号にHighが出力される。第2の走査線G2(1)の走査信号がHighのとき、画素回路650C(i, 1)の階調信号が更新される。

【0249】

シフトレジスタ回路111Dの出力信号SRE(1)および選択信号MD\_E\_E\_V\_E\_NがHighの期間は、判定回路22によって第2の走査線G2(2)の走査信号にHighが出力される。第2の走査線G2(2)の走査信号がHighのとき、画素回路650C(i, 2)の階調信号だけ更新される。

40

【0250】

選択信号MD\_L\_O\_D\_DがLowの期間は、判定回路21により、出力信号SRL(1)の状態によらず、第1の走査線G1(1)の走査信号の出力はLowになる。選択信号MD\_L\_E\_V\_E\_NがLowの期間は、判定回路21によって、出力信号SRL(1)の状態によらず、第1の走査線G1(1)の走査信号の出力はLowになる。

【0251】

図25(B)では、液晶表示領域121と発光表示領域122の駆動状態を模式的に示す。

【0252】

図25(B)は、表示部120の駆動状態を模式的に示す。シフトレジスタ回路111

50

Cの出力信号S R L ( 1 )乃至S R L ( n / 2 )と、選択信号M D \_ L \_ o \_ D \_ D と、M D \_ L \_ E \_ V \_ E \_ N とによって第1の走査線G 1 ( 1 )乃至G 1 ( n )の走査信号はL o w なることで液晶表示領域1 2 1の表示内容が更新されない。

【 0 2 5 3 】

シフトレジスタ回路1 1 1 Dの出力信号S R E ( 1 )乃至S R E ( n / 2 )と、選択信号M D \_ E \_ o \_ D \_ D と、M D \_ E \_ E \_ V \_ E \_ N とにより、第2の走査線G 2 ( j )の走査信号がH i g h なることで発光表示領域1 2 2の表示内容が更新される。

【 0 2 5 4 】

図2 5 ( B )では、発光表示領域1 2 2は表示内容が更新され、液晶表示領域1 2 1は表示内容が更新されないため、図2 5 ( A )のタイミングチャートと対応している。

10

【 0 2 5 5 】

図2 4 ( A )では、シフトレジスタ回路1 1 1 Cの出力信号S R L ( 1 )またはS R L ( 2 )がH i g h の期間に、選択信号M D \_ L \_ o \_ D \_ D またはM D \_ L \_ E \_ V \_ E \_ N がH i g h のときに液晶表示領域1 2 1の表示が更新される。

【 0 2 5 6 】

図2 5 ( A )では、シフトレジスタ回路1 1 1 Dの出力信号S R E ( 1 )またはS R E ( 2 )がH i g h の期間に、選択信号M D \_ E \_ o \_ D \_ D またはM D \_ E \_ E \_ V \_ E \_ N がH i g h のときに発光表示領域1 2 2の表示が更新される。

【 0 2 5 7 】

図2 4 ( A )および図2 5 ( A )では、選択信号による走査線の選択制御によって、液晶表示領域1 2 1または発光表示領域1 2 2をフレーム単位で停止させる例を示したが、同様にフレーム単位でシフトレジスタ回路を停止させても同じ効果を得ることができる。

20

【 0 2 5 8 】

さらに、画素回路7 5 0 C ( i , j )では静止画を、画素回路6 5 0 C ( i , j )では動画を再生するときに、静止画の場合は動画の場合に比べて表示内容の更新頻度を下げて駆動を行うなど、表示の内容に応じた最適な駆動を選択することができる。

【 0 2 5 9 】

さらに、画素回路7 5 0 C ( i , j )および画素回路6 5 0 C ( i , j )をもつ高精細な表示部1 2 0を、最適な駆動を行うことにより消費電力の低減ができる。

30

【 0 2 6 0 】

なお本発明の一様態は、選択回路2 0にて、偶数行と奇数行とを選択制御できるように示したが、選択回路にて選択できる行の数は2以上の整数でもよい。

【 0 2 6 1 】

図2 6 ( A )では図2 2の表示装置7 0 2の動作について、図2 4 ( A )とは異なるタイミングチャートを示す。ここでは、表示装置において、第1の表示領域と第2の表示領域とを有し、第1の表示領域に含まれる表示素子の表示の更新頻度は、第2の表示領域に含まれる表示素子と異なる例を示す。具体的には、液晶表示領域1 2 1または発光表示領域1 2 2の一方は、全面において表示が順次更新されるが、他方は、部分的に表示が更新される例を示す。シフトレジスタ回路1 1 1 Cおよびシフトレジスタ回路1 1 1 Dの1 0行目を中心に前後の動作をタイミングチャートで示す。

40

【 0 2 6 2 】

一例として、図2 6では、第1の走査線G 1 ( 7 )乃至G 1 ( 1 2 )と、第2の走査線G 2 ( 7 )乃至G 2 ( 1 2 )との動作を説明する。

【 0 2 6 3 】

シフトレジスタ回路1 1 1 Cの出力信号S R L ( 4 )、S R L ( 5 )、およびS R L ( 6 )と、シフトレジスタ回路1 1 1 Dの出力信号S R E ( 4 )、S R E ( 5 )、およびS R E ( 6 )が、H i g h の期間について、タイミングチャートの動作を示す。

【 0 2 6 4 】

図2 2のシフトレジスタ回路1 1 1 Cが出力信号S R L ( 4 )を選択回路2 0に与えたときの動作を説明する。選択信号M D \_ L \_ o \_ D \_ D がH i g h のときに、選択回路2 0によ

50

つて第1の走査線G1(7)の走査信号がHighになり、画素回路750C(1,7)乃至画素回路750C(m,7)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_L\_E\_V\_E\_NがHighのときに、選択回路20によって第1の走査線G1(8)の走査信号がHighになり、画素回路750C(1,8)乃至画素回路750C(m,8)が階調信号により表示内容が更新されることを示す。

#### 【0265】

図22のシフトレジスタ回路111Dが出力信号SRE(4)を選択回路20に与えたときの動作を説明する。選択信号MD\_E\_O\_D\_DおよびMD\_E\_E\_V\_E\_NがLowのときは、選択回路20によって第2の走査線G2(7)の走査信号がLowになり、画素回路650C(1,7)乃至画素回路650C(m,7)の表示内容が更新されなかったことを示す。さらに選択回路20によって第2の走査線G2(8)の走査信号がLowになり、画素回路650C(1,8)乃至画素回路650C(m,8)の表示内容が更新されなかったことを示す。

10

#### 【0266】

図22のシフトレジスタ回路111Cが出力信号SRL(5)を選択回路20に与えたときの動作を説明する。選択信号MD\_L\_O\_D\_DがHighのときに、選択回路20によって第1の走査線G1(9)の走査信号がHighになり、画素回路750C(1,9)乃至画素回路750C(m,9)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_L\_E\_V\_E\_NがHighのときに、選択回路20によって第1の走査線G1(10)の走査信号がHighになり、画素回路750C(1,10)乃至画素回路750C(m,10)が階調信号により表示内容が更新されることを示す。

20

#### 【0267】

図22のシフトレジスタ回路111Dが出力信号SRE(5)を選択回路20に与えたときの動作を説明する。選択信号MD\_E\_O\_D\_DがHighのときに、選択回路20によって第2の走査線G2(9)の走査信号がHighになり、画素回路650C(1,9)乃至画素回路650C(m,9)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_E\_E\_V\_E\_NがHighのときに、選択回路20によって第2の走査線G2(10)の走査信号がHighになり、画素回路650C(1,10)乃至画素回路650C(m,10)が階調信号により表示内容が更新されることを示す。

30

#### 【0268】

図22のシフトレジスタ回路111Cが出力信号SRL(6)を選択回路20に与えたときの動作を説明する。選択信号MD\_L\_O\_D\_DがHighのときに、選択回路20によって第1の走査線G1(11)の走査信号がHighになり、画素回路750C(1,11)乃至画素回路750C(m,11)が階調信号により表示内容が更新されることを示す。さらに、選択信号MD\_L\_E\_V\_E\_NがHighのときに、選択回路20によって第1の走査線G1(12)の走査信号がHighになり、画素回路750C(1,12)乃至画素回路750C(m,12)が階調信号により表示内容が更新されることを示す。

#### 【0269】

図22のシフトレジスタ回路111Dが出力信号SRE(6)を選択回路20に与えたときの動作を説明する。選択信号MD\_E\_O\_D\_DおよびMD\_E\_E\_V\_E\_NがLowのときは、選択回路20によって第2の走査線G2(11)の走査信号がLowになり、画素回路650C(1,11)乃至画素回路650C(m,11)の表示内容が更新されなかったことを示す。さらに選択回路20によって第2の走査線G2(12)の走査信号がLowになり、画素回路650C(1,12)乃至画素回路650C(m,12)の表示内容が更新されなかったことを示す。

40

#### 【0270】

図26(B)では、液晶表示領域121は表示内容が順次更新されるが、発光表示領域122は、出力信号SRE(5)の表示内容だけが更新される。

#### 【0271】

図26(B)は、表示部120の駆動状態を模式的に示す。出力信号SRL(1)乃至

50

S R L (  $n / 2$  ) と、選択信号 M D \_ L \_ O \_ D \_ D と、 M D \_ L \_ E \_ V \_ E \_ N とによって第 1 の走査線 G 1 ( 1 ) 乃至 G 1 (  $n$  ) の走査信号が H i g h になることで液晶表示領域 1 2 1 の表示内容が更新され、シフトレジスタ回路 1 1 1 D の出力信号 S R E ( 1 ) 乃至 S R E (  $n / 2$  ) と、選択信号 M D \_ E \_ O \_ D \_ D と、 M D \_ E \_ E \_ V \_ E \_ N とにより、第 2 の走査線 G 2 ( 1 ) 乃至 G 2 (  $n$  ) の走査信号が H i g h になることで発光表示領域 1 2 2 の表示内容が更新される。したがって表示が更新される順番は、図 2 6 ( A ) のタイミングチャートと対応している。

【 0 2 7 2 】

図 2 6 ( B ) では、選択信号により、特定の表示領域だけ表示内容を更新することができる。

10

【 0 2 7 3 】

一例として、画素回路 7 5 0 C (  $i, j$  ) では液晶表示領域 1 2 1 のすべてに静止画を表示し、画素回路 6 5 0 C (  $i, j$  ) では特定の発光表示領域 1 2 2 A のみ動画を再生することができる。静止画を表示するときは、動画を表示するときに比べて表示内容の更新頻度を下げて駆動を行うなど、表示の内容に合わせた最適な駆動を選択することができる。

【 0 2 7 4 】

画素回路 7 5 0 C (  $i, j$  ) および画素回路 6 5 0 C (  $i, j$  ) を有する高精細な表示部 1 2 0 を、最適な駆動を行うことにより、表示内容の更新頻度を最適化することで消費電力の低減ができる。

20

【 0 2 7 5 】

図 2 2 で示した回路では、第 1 の走査線 G 1 と、第 2 の走査線 G 2 とは異なるタイミングで走査信号が H i g h になることで、信号線に与えられる第 1 の階調信号と、第 2 の階調信号とは、お互いに影響を及ぼさない。

【 0 2 7 6 】

なお本発明の一様態は、選択回路 2 0 にて、偶数行と奇数行とを選択制御できるように示したが、選択回路にて選択できる行の数は 2 以上の整数でもよい。

【 0 2 7 7 】

図 1 4 ( A ) 乃至 ( D ) には、図 1 6 、図 2 0 、図 2 2 に示す回路で可能な表示パターンの一例を示す。なお、  $p$  は 1 以上の整数であり、図 1 4 では、  $p + 1$  フレーム乃至  $p + 4$  フレームまでの、表示パターンの更新状態を示す。

30

【 0 2 7 8 】

画素回路 7 5 0 C (  $i, j$  ) および画素回路 6 5 0 C (  $i, j$  ) を有する高精細な表示部を、選択信号 M D \_ L \_ O \_ D \_ D 、選択信号 M D \_ L \_ E \_ V \_ E \_ N 、選択信号 M D \_ E \_ O \_ D \_ D 、選択信号 M D \_ E \_ E \_ V \_ E \_ N 、および選択回路 2 0 により、走査線の駆動するタイミングを制御することができる。さらに表示内容に応じた最適な更新頻度を制御することができる。さらに、図 1 4 ( A ) 乃至 ( D ) に示すように、液晶表示領域 1 2 1 および発光表示領域 1 2 2 の特定の領域における表示内容の更新を、走査線の選択制御により自由に制御することができる。

【 0 2 7 9 】

40

以上、本実施の形態で示す構成、方法、駆動タイミングは、他の実施の形態で示す構成、方法、駆動タイミングと適宜組み合わせて用いることができる。

【 0 2 8 0 】

( 実施の形態 7 )

本実施の形態では、本発明の一態様の表示装置 7 0 0 の構成について、図 2 7 乃至図 3 1 を参照しながら説明する。

【 0 2 8 1 】

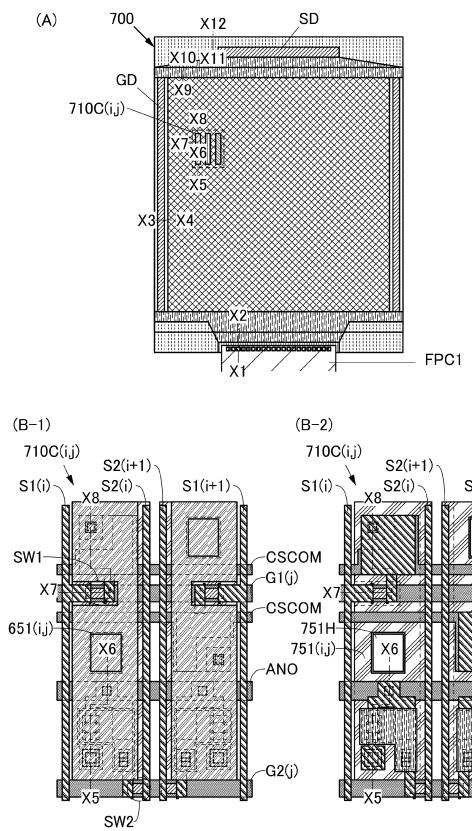

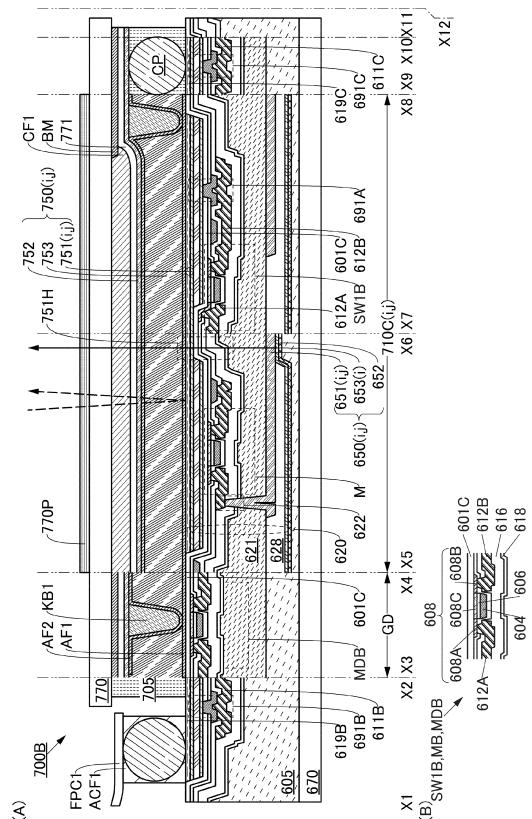

図 2 7 は本発明の一態様の表示装置 7 0 0 の構成を説明する図である。図 2 7 ( A ) は本発明の一態様の表示装置 7 0 0 の上面図である。図 2 7 ( B - 1 ) は図 2 7 ( A ) の表示装置 7 0 0 が有する画素回路 7 1 0 C (  $i, j$  ) の一部を説明する下面図であり、図 2

50

7 (B-2) は図27 (B-1) に図示する一部の構成を省略して説明する下面図である。

【0282】

また、図28 (A-1) は図27 (A) の表示装置700が有する画素回路710C (i, j) の一部を説明する下面図であり、図28 (A-2) は図28 (A-1) に図示する一部の構成を省略して説明する下面図である。図28 (B-1) は、図28 (A-1) と異なる開口位置について示した下面図である。図28 (B-2) は図28 (B-1) に図示する一部の構成を省略して説明する下面図である。

【0283】

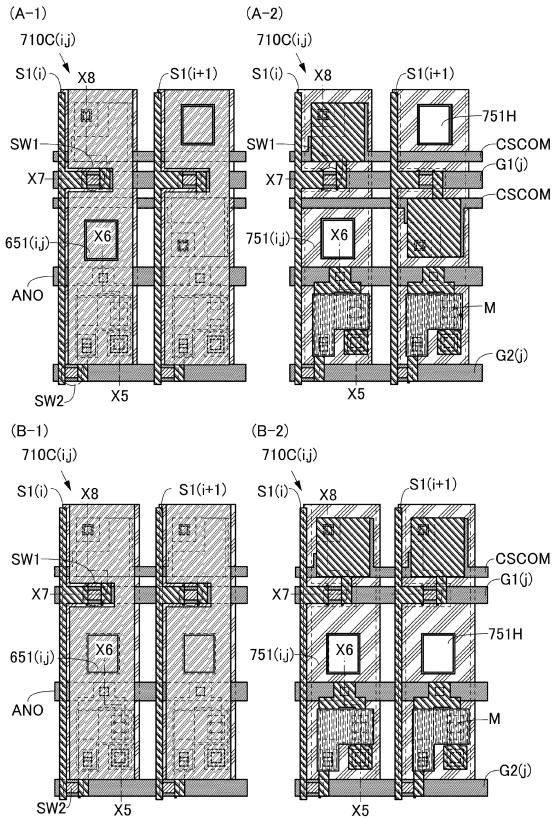

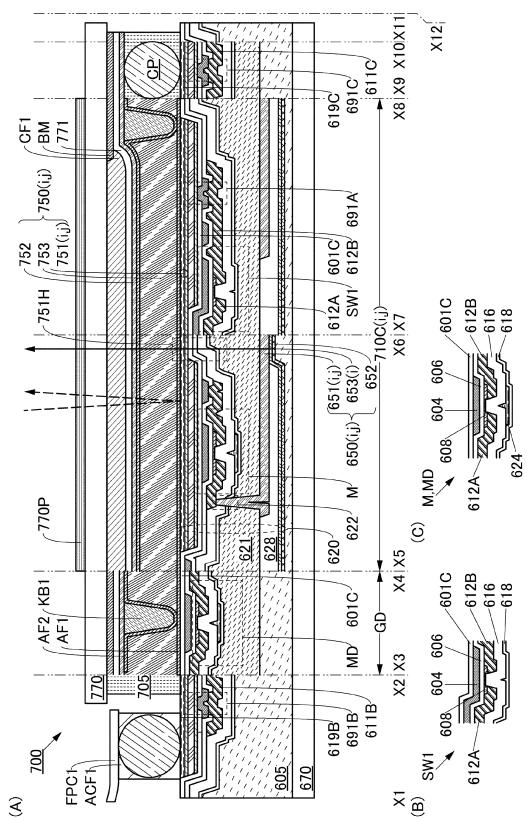

図29は本発明の一態様の表示装置700の構成を説明する図である。図29 (A) は図27 (A) の切断線X1-X2、X3-X4、X5-X6、X7-X8、X9-X10、X11-X12における断面図である。図29 (B) は表示装置700の一部の構成を説明する断面図であり、図29 (C) は表示装置700の他の一部の構成を説明する断面図である。

【0284】

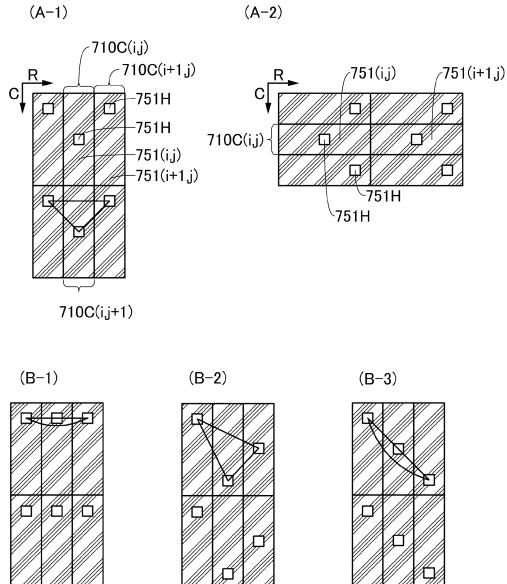

図30 (A-1) および図30 (A-2) は本発明の一態様の表示装置700に用いることができる開口部751Hの配置を説明する模式図である。

【0285】

<表示装置の構成例1. >

本実施の形態で説明する表示装置700は、信号線S1 (i) と、画素回路710C (i, j) と、を有する (図28 (A-1) および図28 (A-2) 参照)。

【0286】

画素回路710C (i, j) は、信号線S1 (i) と電気的に接続される。

【0287】

画素回路710C (i, j) は、画素回路750C (i, j) と、画素回路650C (i, j) を有し、画素回路750C (i, j) が有する表示素子750 (i, j) と、第1の導電膜と、第2の導電膜と、第2の絶縁膜601Cと、画素回路650C (i, j) が有する表示素子650 (i, j) と、を有する (図29 (A) 参照)。

【0288】

第1の導電膜は、表示素子750 (i, j) と電気的に接続される (図29 (A) 参照)。例えば、第1の導電膜を、表示素子750 (i, j) の第1の電極751 (i, j) に用いることができる。

【0289】

第2の導電膜は、第1の導電膜と重なる領域を備える。例えば、第2の導電膜を、トランジスタSW1に用いることができるトランジスタのソースまたはドレインとして機能する導電膜612Bに用いることができる。

【0290】

第2の絶縁膜601Cは、第2の導電膜と第1の導電膜の間に挟まれる領域を備える。

【0291】

画素回路710C (i, j) は、第2の導電膜と電気的に接続される。例えば、第2の導電膜をソースまたはドレインとして機能する導電膜612Bに用いたトランジスタを、画素回路710C (i, j) のトランジスタSW1に用いることができる (図29 (A) および図2参照)。

【0292】

第2の絶縁膜601Cは、開口部691Aを備える (図29 (A) 参照)。

【0293】

第2の導電膜は、開口部691Aにおいて第1の導電膜と電気的に接続される。例えば、導電膜612Bは、第1の電極751 (i, j) と電気的に接続される。

【0294】

画素回路710C (i, j) は、信号線S1 (i) と電気的に接続される (図2参照)。

10

20

30

40

50

。なお、導電膜 612A は、信号線 S1(i) と電気的に接続される(図 29(A) および図 2 参照)。

【0295】

第 1 の電極 751(i, j) は、第 2 の絶縁膜 601C に埋め込まれた側端部を備える。

【0296】

また、本実施の形態で説明する表示装置 700 の画素回路 710C(i, j) は、トランジスタ SW1 を備える。トランジスタ SW1 は、酸化物半導体を含む。

【0297】

また、本実施の形態で説明する表示装置 700 の表示素子 650(i, j) は、表示素子 750(i, j) が表示をする方向と同一の方向に表示をする機能を備える。例えば、外光を反射する強度を制御して表示素子 750(i, j) が表示をする方向を、破線の矢印で図中に示す。また、表示素子 650(i, j) が表示をする方向を、実線の矢印で図中に示す(図 29(A) 参照)。

【0298】

また、本実施の形態で説明する表示装置 700 の表示素子 650(i, j) は、表示素子 750(i, j) が表示をする領域に囲まれた領域に表示をする機能を備える(図 30(A-1) または図 30(A-2) 参照)。なお、表示素子 750(i, j) は、第 1 の電極 751(i, j) と重なる領域に表示をし、表示素子 650(i, j) は、開口部 751H と重なる領域に表示をする。

【0299】

また、本実施の形態で説明する表示装置 700 の表示素子 750(i, j) は、入射する光を反射する機能を備える反射膜と、反射する光の強さを制御する機能と、を有する。そして、反射膜は、開口部 751H を備える。なお、例えば、表示素子 750(i, j) の反射膜に、第 1 の導電膜または第 1 の電極 751(i, j) 等を用いることができる。

【0300】

また、表示素子 650(i, j) は、開口部 751H に向けて光を射出する機能を有する。

【0301】

また、本実施の形態で説明する表示装置 700 は、画素回路 710C(i, j) と、一群の画素回路 710C(i, 1) 乃至画素回路 710C(i, n) と、他の一群の画素回路 710C(1, j) 乃至画素回路 710C(m, j) と、第 1 の走査線 G1(j) と、を有する(図 1 参照)。なお、i は 1 以上 m 以下の整数であり、j は 1 以上 n 以下の整数であり、m および n は 1 以上の整数である。

【0302】

また、本実施の形態で説明する表示装置 700 は、第 2 の走査線 G2(j) と、配線 C COM と、配線 ANO と、を有する。

【0303】

一群の画素回路 710C(i, 1) 乃至画素回路 710C(i, n) は、画素回路 710C(i, j) を含み、行方向と交差する列方向(図中に矢印 C で示す方向)に配設される。

【0304】

また、他の一群の画素回路 710C(1, j) 乃至画素回路 710C(m, j) は、画素回路 710C(i, j) を含み、行方向(図中に矢印 R で示す方向)に配設される。

【0305】

第 1 の走査線 G1(j) は、行方向に配設される他の一群の画素回路 710C(1, j) 乃至画素回路 710C(m, j) と電気的に接続される。

【0306】

列方向に配設される一群の画素回路 710C(i, 1) 乃至画素回路 710C(i, n) は、信号線 S1(i) と電気的に接続される。

10

20

30

40

50

## 【0307】

例えば、図30(A-1)および図30(A-2)に示すように、画素内に設けられる開口部の位置は、隣接する画素において異なることが好ましい。ここでいう隣接する画素とは、行方向および列方向のいずれか、または行方向および列方向の双方を含むものとする。なお、例えば、第1の電極751(i,j)を反射膜に用いることができる。

## 【0308】

図30(B-1)乃至図30(B-3)は本発明の一態様の表示装置700に用いることができる開口部751Hの配置例を示した模式図である。

## 【0309】

図30(B-1)は図28(B-1)で下面図を示したが、図28(A-1)と比べるとCSOMの配線を減らすことができ、高精細化に対応した表示装置を提供することができる。

10

## 【0310】

図30(B-2)および図30(B-3)では三つの画素回路が有するそれぞれの第2の表示素子の開口部中心を線で結んだ距離が、図30(A-1)または図30(B-1)で示す配置より大きくすることで、第2の表示素子のように小さな開口でも、色を構成する3つの画素の表示面積を大きくすることで、色の表示品質を改善することができる。

## 【0311】

上記本発明の一態様の表示装置700は、表示素子750と、表示素子750と電気的に接続される第1の導電膜と、第1の導電膜と重なる領域を備える第2の導電膜と、第2の導電膜と第1の導電膜の間に挟まれる領域を備える絶縁膜と、第2の導電膜と電気的に接続される画素回路と、画素回路と電気的に接続される表示素子650と、を含み、第2の絶縁膜は開口部を備え、第2の導電膜は第1の導電膜と開口部で電気的に接続される。

20

## 【0312】

これにより、例えば同一の工程を用いて形成することができる画素回路を用いて、表示素子750と、表示素子750とは異なる方法を用いて表示をする表示素子650と、を駆動することができる。その結果、利便性または信頼性に優れた新規な表示装置を提供することができる。

## 【0313】

また、本実施の形態で説明する表示装置700は、端子619Bと、導電膜611Bと、を有する(図29(A)参照)。

30

## 【0314】

第2の絶縁膜601Cは、端子619Bおよび導電膜611Bの間に挟まれる領域を備える。また、第2の絶縁膜601Cは、開口部691Bを備える。

## 【0315】

端子619Bは、開口部691Bにおいて導電膜611Bと電気的に接続される。また、導電膜611Bは、画素回路710C(i,j)と電気的に接続される。なお、例えば、第1の電極751(i,j)または第1の導電膜を反射膜に用いる場合、端子619Bの接点として機能する面は、第1の電極751(i,j)の、表示素子750(i,j)に入射する光に向いている面と同じ方向に向いている。

40

## 【0316】

これにより、端子を介して電力または信号を、画素回路に供給することができる。その結果、利便性または信頼性に優れた新規な表示装置を提供することができる。

## 【0317】

また、本実施の形態で説明する表示装置700の表示素子750(i,j)は、液晶材料を含む層753と、第1の電極751(i,j)および第2の電極752と、を備える。なお、第2の電極752は、第1の電極751(i,j)との間に液晶材料の配向を制御する電界が形成されるように配置される。

## 【0318】

また、本実施の形態で説明する表示装置700は、配向膜AF1および配向膜AF2を

50

備える。配向膜 A F 2 は、配向膜 A F 1 との間に液晶材料を含む層 7 5 3 を挟むように配設される。

【0319】

また、本実施の形態で説明する表示装置 700 の表示素子 650 (i, j) は、第3の電極 651 (i, j) と、第4の電極 652 と、発光性の有機化合物を含む層 653 (i) と、を備える。

【0320】

第4の電極 652 は、第3の電極 651 (i, j) と重なる領域を備える。発光性の有機化合物を含む層 653 (i) は、第3の電極 651 および第4の電極 652 の間に配設される。そして、第3の電極 651 (i, j) は、接続部 622 において、トランジスタ M と電気的に接続される。

10

【0321】

また、本実施の形態で説明する表示装置 700 の画素回路 710C (i, j) は、着色膜 C F 1 と、遮光膜 B M と、絶縁膜 771 と、機能膜 770P と、を有する。

【0322】

着色膜 C F 1 は、表示素子 750 (i, j) と重なる領域を備える。遮光膜 B M は、表示素子 750 (i, j) と重なる領域に開口部を備える。

【0323】

絶縁膜 771 は、着色膜 C F 1 と液晶材料を含む層 753 の間または遮光膜 B M と液晶材料を含む層 753 の間に配設される。これにより、着色膜 C F 1 の厚さに基づく凹凸を平坦にすることができる。または、遮光膜 B M または着色膜 C F 1 等から液晶材料を含む層 753 への不純物の拡散を、抑制することができる。

20

【0324】

機能膜 770P は、表示素子 750 (i, j) と重なる領域を備える。機能膜 770P は、表示素子 750 (i, j) との間に基板 770 を挟むように配設される。

【0325】

また、本実施の形態で説明する表示装置 700 は、基板 670 と、基板 770 と、機能層 620 と、を有する。

【0326】

基板 770 は、基板 670 と重なる領域を備える。機能層 620 は、基板 670 および基板 770 の間に配設される。

30

【0327】

機能層 620 は、画素回路 710C (i, j) と、表示素子 650 (i, j) と、絶縁膜 621 と、絶縁膜 628 と、を含む。また、機能層 620 は、絶縁膜 618 および絶縁膜 616 を含む。

【0328】

絶縁膜 621 は、表示素子 750 (i, j) および表示素子 650 (i, j) の間に配設される。

【0329】

絶縁膜 628 は、絶縁膜 621 および基板 670 の間に配設され、表示素子 650 (i, j) と重なる領域に開口部を備える。第3の電極 651 (i, j) の周縁に沿って形成される絶縁膜 628 は、第3の電極 651 (i, j) および第4の電極の短絡を防止することができる。

40

【0330】

絶縁膜 618 は、絶縁膜 621 および表示素子 750 (i, j) の間に配設される領域を備え、絶縁膜 616 は、絶縁膜 618 および表示素子 750 (i, j) の間に配設される領域を備える。

【0331】

また、本実施の形態で説明する表示装置 700 は、接合層 605 と、封止材 705 と、構造体 K B 1 と、を有する。

50

## 【0332】

接合層605は、機能層620および基板670の間に配設され、機能層620および基板670を貼り合せる機能を備える。

## 【0333】

封止材705は、機能層620および基板770の間に配設され、機能層620および基板770を貼り合わせる機能を備える。

## 【0334】

構造体KB1は、機能層620および基板770の間に所定の間隙を設ける機能を備える。

## 【0335】

また、本実施の形態で説明する表示装置700は、端子619Cと、導電膜611Cと、導電体CPと、を有する。

10

## 【0336】

第2の絶縁膜601Cは、端子619Cおよび導電膜611Cの間に挟まれる領域を備える。また、第2の絶縁膜601Cは、開口部691Cを備える。

## 【0337】

端子619Cは、開口部691Cにおいて導電膜611Cと電気的に接続される。また、導電膜611Cは、画素回路710C(i, j)と電気的に接続される。

## 【0338】

導電体CPは、端子619Cと第2の電極752の間に挟まれ、端子619Cと第2の電極752を電気的に接続する。例えば、導電性の粒子を導電体CPに用いることができる。

20

## 【0339】

また、本実施の形態で説明する表示装置700は、駆動回路GDと、駆動回路SDと、を有する(図27(A)参照)。

## 【0340】

駆動回路GDは、第1の走査線G1(j)と電気的に接続される。駆動回路GDは、例えばトランジスタMDを備える。具体的には、画素回路710C(i, j)に含まれるトランジスタと同じ工程で形成することができる半導体膜を含むトランジスタをトランジスタMDに用いることができる(図29(A)および図29(C)参照)。

30

## 【0341】

駆動回路SDは、信号線S1(i)と電気的に接続される。駆動回路SDは、例えば端子619Bまたは端子619Cと同一の工程で形成することができる端子に導電材料を用いて電気的に接続される。

## 【0342】

以下に、表示装置を構成する個々の要素について説明する。なお、これらの構成は明確に分離できず、一つの構成が他の構成を兼ねる場合や他の構成の一部を含む場合がある。

## 【0343】

例えば第1の導電膜を、第1の電極751(i, j)に用いることができる。また、第1の導電膜を、反射膜に用いることができる。

40

## 【0344】

また、第2の導電膜を、トランジスタのソースまたはドレインの機能を備える導電膜612Bに用いることができる。

## 【0345】

## 《構成例1.》

本発明の一態様の表示装置700は、基板670、基板770、構造体KB1封止材705または接合層605、を有する。

## 【0346】

また、本発明の一態様の表示装置700は、機能層620、絶縁膜621、絶縁膜628、を有する。

50

**【 0 3 4 7 】**

また、本発明の一態様の表示装置 700 は、信号線 S1 (i)、第1の走査線 G1 (j)、第2の走査線 G2 (j)、配線 C S C O M、配線 A N O を有する。

**【 0 3 4 8 】**

また、本発明の一態様の表示装置 700 は、第1の導電膜または第2の導電膜を有する。

**【 0 3 4 9 】**

また、本発明の一態様の表示装置 700 は、端子 619B、端子 619C、導電膜 611B または導電膜 611C を有する。

**【 0 3 5 0 】**

また、本発明の一態様の表示装置 700 は、画素回路 710C (i, j)、トランジスタ SW1、を有する。

**【 0 3 5 1 】**

また、本発明の一態様の表示装置 700 は、表示素子 750 (i, j)、第1の電極 751 (i, j)、反射膜、開口部 751H、液晶材料を含む層 753、第2の電極 752、を有する。

**【 0 3 5 2 】**

また、本発明の一態様の表示装置 700 は、配向膜 AF1、配向膜 AF2、着色膜 CF1、遮光膜 BM、絶縁膜 771、機能膜 770P を有する。

**【 0 3 5 3 】**

表示装置 700 では、着色膜 CF1 は絶縁膜 621 と、表示素子 750 (i, j) との間に、表示素子 650 (i, j) の光が通過する開口部 751H と重なる位置に配置されてもよい。

**【 0 3 5 4 】**

また、本発明の一態様の表示装置 700 は、表示素子 650 (i, j)、第3の電極 651 (i, j)、第4の電極 652 または発光性の有機化合物を含む層 653 (i) を有する。

**【 0 3 5 5 】**

また、本発明の一態様の表示装置 700 は、第2の絶縁膜 601C を有する。

**【 0 3 5 6 】**

また、本発明の一態様の表示装置 700 は、駆動回路 GD または駆動回路 SD を有する。

**【 0 3 5 7 】****《基板 670》**

作製工程中の熱処理に耐えうる程度の耐熱性を有する材料を基板 670 等に用いることができる。具体的には厚さ 0.7 mm の無アルカリガラスを用いることができる。

**【 0 3 5 8 】**

例えば、第6世代 (1500 mm × 1850 mm)、第7世代 (1870 mm × 2200 mm)、第8世代 (2200 mm × 2400 mm)、第9世代 (2400 mm × 2800 mm)、第10世代 (2950 mm × 3400 mm) 等の面積が大きなガラス基板を基板 670 等に用いることができる。これにより、大型の表示装置を作製することができる。

**【 0 3 5 9 】**

有機材料、無機材料または有機材料と無機材料等の複合材料等を基板 670 等に用いることができる。例えば、ガラス、セラミックス、金属等の無機材料を基板 670 等に用いることができる。

**【 0 3 6 0 】**

具体的には、無アルカリガラス、ソーダ石灰ガラス、カリガラス、クリスタルガラス、石英またはサファイア等を、基板 670 等に用いることができる。具体的には、無機酸化物膜、無機窒化物膜または無機酸窒化物膜等を、基板 670 等に用いることができる。例

10

20

30

40

50

えば、酸化シリコン、窒化シリコン、酸窒化シリコン、アルミナ膜等を、基板 670 等に用いることができる。SUS またはアルミニウム等を、基板 670 等に用いることができる。

【0361】

例えば、シリコンや炭化シリコンからなる単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を基板 670 等に用いることができる。これにより、半導体素子を基板 670 等に形成することができる。

【0362】

例えば、樹脂、樹脂フィルムまたはプラスチック等の有機材料を基板 670 等に用いることができる。具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネートまたはアクリル樹脂等の樹脂フィルムまたは樹脂板を、基板 670 等に用いることができる。

10

【0363】

例えば、金属板、薄板状のガラス板または無機材料等の膜を樹脂フィルム等に貼り合わせた複合材料を基板 670 等に用いることができる。例えば、纖維状または粒子状の金属、ガラスもしくは無機材料等を樹脂フィルムに分散した複合材料を、基板 670 等に用いることができる。例えば、纖維状または粒子状の樹脂もしくは有機材料等を無機材料に分散した複合材料を、基板 670 等に用いることができる。

【0364】

また、単層の材料または複数の層が積層された材料を、基板 670 等に用いることができる。例えば、基材と基材に含まれる不純物の拡散を防ぐ絶縁膜等が積層された材料を、基板 670 等に用いることができる。具体的には、ガラスとガラスに含まれる不純物の拡散を防ぐ酸化シリコン層、窒化シリコン層または酸化窒化シリコン層等から選ばれた一または複数の膜が積層された材料を、基板 670 等に用いることができる。または、樹脂と樹脂を透過する不純物の拡散を防ぐ酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜等が積層された材料を、基板 670 等に用いることができる。

20

【0365】

具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート若しくはアクリル樹脂等の樹脂フィルム、樹脂板または積層体等を基板 670 等に用いることができる。

30

【0366】

具体的には、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミド等）、ポリイミド、ポリカーボネート、ポリウレタン、アクリル樹脂、エポキシ樹脂もしくはシロキサン結合を有する樹脂を含む材料を基板 670 等に用いることができる。

【0367】

具体的には、ポリエチレンテレフタレート（PET）、ポリエチレンナフタレート（PEN）、ポリエーテルサルファン（PES）またはアクリル等を基板 670 等に用いることができる。

【0368】

また、紙または木材などを基板 670 等に用いることができる。

40

【0369】

例えば、可撓性を有する基板を基板 670 等に用いることができる。

【0370】

なお、トランジスタまたは容量素子等を基板に直接形成する方法を用いることができる。また、例えば作製工程中に加わる熱に耐熱性を有する工程用の基板にトランジスタまたは容量素子等を形成し、形成されたトランジスタまたは容量素子等を基板 670 等に転置する方法を用いることができる。これにより、例えば可撓性を有する基板にトランジスタまたは容量素子等を形成できる。

【0371】

《基板 770》

50

例えば、透光性を備える材料を基板 770 に用いることができる。具体的には、基板 670 に用いることができる材料から選択された材料を基板 770 に用いることができる。具体的には厚さ 0.7 mm または厚さ 0.1 mm 程度まで研磨した無アルカリガラスを用いることができる。

【0372】

《構造体 KB1》

例えば、有機材料、無機材料または有機材料と無機材料の複合材料を構造体 KB1 等に用いることができる。これにより、構造体 KB1 等を挟む構成の間に所定の間隔を設けることができる。

【0373】

具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート、ポリシロキサン若しくはアクリル樹脂等またはこれらから選択された複数の樹脂の複合材料などを構造体 KB1 等に用いることができる。また、感光性を有する材料を用いて形成してもよい。

【0374】

《封止材 705》

無機材料、有機材料または無機材料と有機材料の複合材料等を封止材 705 等に用いることができる。

【0375】

例えば、熱溶融性の樹脂または硬化性の樹脂等の有機材料を、封止材 705 等に用いることができる。

【0376】

例えば、反応硬化型接着剤、光硬化型接着剤、熱硬化型接着剤または / および嫌気型接着剤等の有機材料を封止材 705 等に用いることができる。

【0377】

具体的には、エポキシ樹脂、アクリル樹脂、シリコーン樹脂、フェノール樹脂、ポリイミド樹脂、イミド樹脂、PVC (ポリビニルクロライド) 樹脂、PVB (ポリビニルブチラル) 樹脂、EVA (エチレンビニルアセテート) 樹脂等を含む接着剤を封止材 705 等に用いることができる。

【0378】

《接合層 605》

例えば、封止材 705 に用いることができる材料を接合層 605 に用いることができる。

【0379】

《絶縁膜 621》

例えば、絶縁性の無機材料、絶縁性の有機材料または無機材料と有機材料を含む絶縁性の複合材料を、絶縁膜 621 等に用いることができる。

【0380】

具体的には、無機酸化物膜、無機窒化物膜または無機酸化窒化物膜等またはこれらから選ばれた複数を積層した積層材料を、絶縁膜 621 等に用いることができる。例えば、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜等またはこれらから選ばれた複数を積層した積層材料を含む膜を、絶縁膜 621 等に用いることができる。

【0381】

具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート、ポリシロキサン若しくはアクリル樹脂等またはこれらから選択された複数の樹脂の積層材料もしくは複合材料などを絶縁膜 621 等に用いることができる。また、感光性を有する材料を用いて形成してもよい。

【0382】

これにより、例えば絶縁膜 621 と重なるさまざまな構造に由来する段差を平坦化することができる。

10

20

30

40

50

## 【0383】

## 《絶縁膜628》

例えば、絶縁膜621に用いることができる材料を絶縁膜628等に用いることができる。具体的には、厚さ1μmのポリイミドを含む膜を絶縁膜628に用いることができる。

## 【0384】

## 《第2の絶縁膜601C》

例えば、絶縁膜621に用いることができる材料を第2の絶縁膜601Cに用いることができる。具体的には、シリコンおよび酸素を含む材料を第2の絶縁膜601Cに用いることができる。これにより、画素回路または表示素子等への不純物の拡散を抑制することができる。

10

## 【0385】

例えば、シリコン、酸素および窒素を含む厚さ200nmの膜を第2の絶縁膜601Cに用いることができる。

## 【0386】

なお、第2の絶縁膜601Cは、開口部691A、開口部691Bまたは開口部691Cを有する。

## 【0387】

## 《配線、端子、導電膜》

導電性を備える材料を配線等に用いることができる。具体的には、導電性を備える材料を、信号線S1(i)、第1の走査線G1(j)、第2の走査線G2(j)、配線CSCOM、配線ANO、端子619B、端子619C、導電膜611Bまたは導電膜611C等に用いることができる。

20

## 【0388】

例えば、無機導電性材料、有機導電性材料、金属または導電性セラミックスなどを配線等に用いることができる。

## 【0389】

具体的には、アルミニウム、金、白金、銀、銅、クロム、タンタル、チタン、モリブデン、タンゲステン、ニッケル、鉄、コバルト、パラジウムまたはマンガンから選ばれた金属元素などを、配線等に用いることができる。または、上述した金属元素を含む合金などを、配線等に用いることができる。特に、銅とマンガンの合金がウエットエッチング法を用いた微細加工に好適である。

30

## 【0390】

具体的には、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等を配線等に用いることができる。

## 【0391】

具体的には、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などの導電性酸化物を、配線等に用いることができる。

40

## 【0392】

具体的には、グラフェンまたはグラファイトを含む膜を配線等に用いることができる。

## 【0393】

例えば、酸化グラフェンを含む膜を形成し、酸化グラフェンを含む膜を還元することにより、グラフェンを含む膜を形成することができる。還元する方法としては、熱を加える方法や還元剤を用いる方法等を挙げることができる。

## 【0394】

具体的には、導電性高分子を配線等に用いることができる。

## 【0395】

## 《第1の導電膜、第2の導電膜》

50

例えば、配線等に用いることができる材料を第1の導電膜または第2の導電膜に用いることができる。

【0396】

また、第1の電極751(i, j)または配線等を第1の導電膜に用いることができる。

【0397】

また、トランジスタSW1に用いることができるトランジスタの導電膜612Bまたは配線等を第2の導電膜に用いることができる。

【0398】

《トランジスタSW1、トランジスタSW2、トランジスタM》

10

例えば、ボトムゲート型またはトップゲート型等のトランジスタをトランジスタSW1、トランジスタSW2、トランジスタM等に用いることができる。

【0399】

例えば、14族の元素を含む半導体を半導体膜に用いるトランジスタを利用することができます。具体的には、シリコンを含む半導体を半導体膜に用いることができる。例えば、単結晶シリコン、ポリシリコン、微結晶シリコンまたはアモルファスシリコンなどを半導体膜に用いたトランジスタを用いることができる。

【0400】

例えば、酸化物半導体を半導体膜に用いるトランジスタを利用することができます。具体的には、インジウムを含む酸化物半導体またはインジウムとガリウムと亜鉛を含む酸化物半導体を半導体膜に用いることができる。

20

【0401】

一例を挙げれば、アモルファスシリコンを半導体膜に用いたトランジスタと比較して、オフ状態におけるリーク電流が小さいトランジスタをトランジスタSW1、トランジスタSW2、トランジスタM等に用いることができる。具体的には、酸化物半導体を半導体膜608に用いたトランジスタをトランジスタSW1、トランジスタSW2、トランジスタM等に用いることができる。

【0402】

これにより、アモルファスシリコンを半導体膜に用いたトランジスタを利用する画素回路と比較して、画素回路が画像信号を保持することができる時間を長くすることができる。具体的には、フリッカーの発生を抑制しながら、選択信号を30Hz未満、好ましくは1Hz未満より好ましくは一分に一回未満の頻度で供給することができる。その結果、情報処理装置の使用者に蓄積する疲労を低減することができる。また、駆動に伴う消費電力を低減することができる。

30

【0403】

トランジスタSW1に用いることができるトランジスタは、半導体膜608および半導体膜608と重なる領域を備える導電膜604を備える(図29(B)参照)。また、トランジスタSW1に用いることができるトランジスタは、導電膜612Aおよび導電膜612Bを備える。

【0404】

40

なお、導電膜604はゲートの機能を備え、絶縁膜606はゲート絶縁膜の機能を備える。また、導電膜612Aはソースの機能またはドレインの機能の一方を備え、導電膜612Bはソースの機能またはドレインの機能の他方を備える。

【0405】

また、導電膜604との間に半導体膜608を挟むように設けられた導電膜624を備えるトランジスタを、トランジスタMに用いることができる(図29(C)参照)。

【0406】

タンタルおよび窒素を含む厚さ10nmの膜と、銅を含む厚さ300nmの膜と、をこの順で積層した導電膜を導電膜604に用いることができる。

【0407】

50

シリコンおよび窒素を含む厚さ 400 nm の膜と、シリコン、酸素および窒素を含む厚さ 200 nm の膜と、を積層した材料を絶縁膜 606 に用いることができる。

【0408】

インジウム、ガリウムおよび亜鉛を含む厚さ 25 nm の膜を、半導体膜 608 に用いることができる。

【0409】

タンゲステンを含む厚さ 50 nm の膜と、アルミニウムを含む厚さ 400 nm の膜と、チタンを含む厚さ 100 nm の膜と、をこの順で積層した導電膜を、導電膜 612A または導電膜 612B に用いることができる。

【0410】

10

《表示素子 750 (i, j)》

例えば、光の反射または透過を制御する機能を備える表示素子を、表示素子 750 (i, j) 等に用いることができる。例えば、液晶素子と偏光板を組み合わせた構成またはシャッター方式の MEMS 表示素子等を用いることができる。反射型の表示素子を用いることにより、表示装置の消費電力を抑制することができる。具体的には、反射型の液晶表示素子を表示素子 750 に用いることができる。

【0411】

IPS (In-Plane-Switching) モード、TN (Twisted Nematic) モード、FFS (Fringe Field Switching) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optically Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどの駆動方法を用いて駆動することができる液晶素子を用いることができる。

20

【0412】

また、例えば垂直配向 (VA) モード、具体的には、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ECB (Electrically Controlled Birefringence) モード、CPA (Continuous Pinwheel Alignment) モード、ASV (Advanced Super-View) モードなどの駆動方法を用いて駆動することができる液晶素子を用いることができる。

30

【0413】

例えば、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。または、コレステリック相、スメクチック相、キューピック相、カイラルネマチック相、等方相等を示す液晶材料を用いることができる。または、ブルー相を示す液晶材料を用いることができる。

【0414】

40

《第 1 の電極 751 (i, j)》

例えば、配線等に用いる材料を第 1 の電極 751 (i, j) に用いることができる。具体的には、反射膜を第 1 の電極 751 (i, j) に用いることができる。

【0415】

《反射膜》

例えば、可視光を反射する材料を反射膜に用いることができる。具体的には、銀を含む材料を反射膜に用いることができる。例えば、銀およびパラジウム等を含む材料または銀および銅等を含む材料を反射膜に用いることができる。

【0416】

50

反射膜は、例えば、液晶材料を含む層 753 を透過してくる光を反射する。これにより、表示素子 750 (i, j) を反射型の液晶素子にすることができる。また、例えば、表

面に凹凸を備える材料を、反射膜に用いることができる。これにより、入射する光をさまざまな方向に反射して、白色の表示をすることができる。

【0417】

なお、第1の電極751(i, j)を反射膜に用いる構成に限られない。例えば、液晶材料を含む層753と第1の電極751(i, j)の間に反射膜を配設する構成を用いることができる。または、反射膜と液晶材料を含む層753の間に透光性を有する第1の電極751(i, j)を配置する構成を用いることができる。

【0418】

《開口部751H》

非開口部の総面積に対する開口部751Hの総面積の比の値が大きすぎると、表示素子750(i, j)を用いた表示が暗くなってしまう。また、非開口部の総面積に対する開口部751Hの総面積の比の値が小さすぎると、表示素子650(i, j)を用いた表示が暗くなってしまう。

【0419】

また、反射膜に設ける開口部751Hの面積が小さすぎると、表示素子650が射出する光から取り出せる光の効率が低下してしまう。

【0420】

多角形、四角形、楕円形、円形または十字等の形状を開口部751Hの形状に用いることができる。また、細長い筋状、スリット状、市松模様状の形状を開口部751Hの形状に用いることができる。また、開口部751Hを隣接する画素に寄せて配置してもよい。好みしくは、開口部751Hを同じ色を表示する機能を備える他の画素に寄せて配置する。これにより、表示素子650が射出する光が隣接する画素に配置された着色膜に入射してしまう現象(クロストークともいう)を抑制できる。

【0421】

《第2の電極752》

例えば、可視光について透光性を有し且つ導電性を備える材料を、第2の電極752に用いることができる。

【0422】

例えば、導電性酸化物、光が透過する程度に薄い金属膜または金属ナノワイヤーを第2の電極752に用いることができる。

【0423】

具体的には、インジウムを含む導電性酸化物を第2の電極752に用いることができる。または、厚さ1nm以上10nm以下の金属薄膜を第2の電極752に用いることができる。または、銀を含む金属ナノワイヤーを第2の電極752に用いることができる。

【0424】

具体的には、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛、アルミニウムを添加した酸化亜鉛などを、第2の電極752に用いることができる。

【0425】

《配向膜AF1、配向膜AF2》

例えば、ポリイミド等を含む材料を配向膜AF1または配向膜AF2に用いることができる。具体的には、所定の方向に配向するようにラビング処理または光配向技術を用いて形成された材料を用いることができる。