(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5495779号

(P5495779)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

|              |             |

|--------------|-------------|

| (51) Int.Cl. | F 1         |

| HO3M 9/00    | (2006.01)   |

| HO3L 7/00    | (2006.01)   |

| HO3K 5/00    | (2006.01)   |

|              | HO3M 9/00 B |

|              | HO3L 7/00 A |

|              | HO3K 5/00 X |

|              | HO3K 5/00 M |

請求項の数 10 (全 12 頁)

|           |                               |           |                                            |

|-----------|-------------------------------|-----------|--------------------------------------------|

| (21) 出願番号 | 特願2009-297376 (P2009-297376)  | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成21年12月28日 (2009.12.28)      | (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (65) 公開番号 | 特開2011-139246 (P2011-139246A) | (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (43) 公開日  | 平成23年7月14日 (2011.7.14)        | (72) 発明者  | 山崎 善一<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

| 審査請求日     | 平成24年11月27日 (2012.11.27)      | 審査官       | 北村 智彦                                      |

最終頁に続く

(54) 【発明の名称】送信装置および通信システム

## (57) 【特許請求の範囲】

## 【請求項 1】

入力された基準クロックをN (Nは2以上の整数) 遅倍した第1変換クロックと前記基準クロックをN×K (Kは自然数) 遅倍した第2変換クロックとを生成するクロック生成部と、

入力されたNビットの第1のパラレルデータ信号を、前記第1変換クロックに同期して第1のシリアルデータ信号に変換して出力する第1のパラレル/シリアル変換部と、

入力されたN×Kビットの第2のパラレルデータ信号を、前記第2変換クロックに同期して第2のシリアルデータ信号に変換して出力する第2のパラレル/シリアル変換部と、

を有し、

前記第1のシリアルデータ信号と前記第2のシリアルデータ信号とは位相が互いに異なり、

前記第1のシリアルデータ信号と前記第2のシリアルデータ信号の一方は、前記第1のシリアルデータ信号と前記第2のシリアルデータ信号の他方をパラレルデータ信号に変換するためのクロック信号であること

を特徴とする送信装置。

## 【請求項 2】

前記第2のパラレルデータ信号の配列を可変に設定するパラレルデータ設定部をさらに有することを特徴とする請求項1に記載の送信装置。

## 【請求項 3】

10

20

前記クロック生成部は、前記基準クロックに基づいて発振し、第1中間クロックを出力する第1の発振部と、

前記第1中間クロックを分周して分周クロックを生成する分周部と、を含み、

前記第1中間クロックまたは前記分周クロックを、前記第1または第2変換クロックとすることを特徴とする請求項1または2に記載の送信装置。

【請求項4】

前記第1中間クロックを遅延させる遅延部をさらに有し、

前記遅延部で遅延された遅延クロックを前記第2変換クロックとすることを特徴とする請求項3に記載の送信装置。

【請求項5】

前記第1変換クロックと前記第2変換クロックの位相差を設定する位相調整部をさらに有することを特徴とする請求項1ないし4のいずれかに記載の送信装置。

【請求項6】

前記第1および第2のシリアルデータ信号を出力する出力部をさらに備え、

前記出力部はバッファもしくは差動信号を出力する差動出力回路であることを特徴とする請求項1ないし5のいずれかに記載の送信装置。

【請求項7】

前記差動出力回路は、小振幅差動信号を出力するL V D S ドライバであることを特徴とする請求項6に記載の送信装置。

【請求項8】

請求項1ないし7のいずれかに記載の送信装置と、

前記送信装置から出力された前記第1のシリアルデータ信号を、前記第2のシリアルデータ信号に基づいて第3のパラレルデータ信号に変換する受信装置と、

を有することを特徴とする通信システム。

【請求項9】

前記受信装置は、前記第1のシリアルデータ信号を、前記第2のシリアルデータ信号に同期して前記第3のパラレルデータ信号に変換するシリアル／パラレル変換部を有することを特徴とする請求項8に記載の通信システム。

【請求項10】

前記受信装置は、前記第2のシリアルデータ信号に基づいて発振し、第2中間クロックを出力する第2の発振部と、

前記第1のシリアルデータ信号を、前記第2中間クロックに同期して前記第3のパラレルデータ信号に変換するシリアル／パラレル変換部を有することを特徴とする請求項9に記載の通信システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は送信装置、特に、シリアル出力を行う送信装置に関する。

【背景技術】

【0002】

複数の電子機器間でデータ通信を行う場合に、信号線の数を減少させるためにシリアルデータ通信を行うことが知られている（特許文献1、特許文献2参照）。

【0003】

特許文献1に記載された送信側デバイスは、PLL（Phase Locked Loop）回路によって、データ入力同期クロックを遙倍したシリアル出力同期クロックを出力している。また、送信側デバイスに入力されたパラレルデータ信号は、シリアル出力同期クロックに同期してシリアルデータ信号に変換される。

【0004】

受信側デバイスは、送信側デバイスから出力されたシリアル出力同期クロックに同期して、受信したシリアルデータ信号をパラレルデータ信号に変換する。

10

20

30

40

50

## 【0005】

特許文献2に記載された送信側デバイスでは、基準となるクロックを遅倍したシリアルクロックに同期してパラレルデータ信号をシリアルデータ信号に変換している。そして、基準となるクロックと同じ周波数を持つ転送クロックを出力している。

## 【0006】

受信側デバイスは内部にPLL回路を備え、受信した転送クロックを遅倍してシリアルクロックを生成し、これに同期してシリアルデータ信号をパラレルデータ信号に変換する。

## 【先行技術文献】

## 【特許文献】

10

## 【0007】

【特許文献1】特開2006-303915号公報

【特許文献2】特開2007-265261号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

しかしながら、特許文献1の送信側デバイスでは、シリアル出力同期クロックがLVDSドライバから小振幅差動信号として出力される一方で、シリアルデータ信号は、シリアル出力同期クロックに同期して動作する変換回路によってパラレルデータ信号から変換された上でLVDSドライバから小振幅差動信号として出力される。つまり、シリアルデータ信号とシリアル出力同期クロックとでは、変換回路が動作することによる遅延分だけ、信号の遷移タイミングのずれ(スキー)が生じる。このスキーは、送信側デバイスの電源電圧や温度などの動作条件や、送信側デバイスが作製された半導体プロセスによる素子特性のばらつきなどによって変動する。受信側デバイスは、この遅延時間が変動しても、送信側デバイスから受けたシリアルデータ信号を正確にデータをパラレルデータ信号に変換することが求められるので、複雑な設計となってしまう恐れがある。

20

## 【0009】

また、特許文献2に記載の送信側デバイスにおいても、PLL回路から出力された転送クロックはクロック送信回路から出力される一方で、シリアルデータ信号は、シリアルクロックに同期して動作する変換回路によってパラレルデータ信号から変換された上でデータ送信回路から出力される。このため特許文献1と同様の問題が生じる恐れがある。

30

## 【0010】

以上の問題を鑑みて成された本発明は、簡易な構成で精度の高い通信を実現できる通信装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0011】

上記目的を達成する本発明は、入力された基準クロックをN(Nは2以上の整数)遅倍した第1変換クロックと前記基準クロックをN×K(Kは自然数)遅倍した第2変換クロックとを生成するクロック生成部と、入力されたNビットの第1のパラレルデータ信号を、前記第1変換クロックに同期して第1のシリアルデータ信号に変換して出力する第1のパラレル/シリアル変換部と、入力されたN×Kビットの第2のパラレルデータ信号を、前記第2変換クロックに同期して第2のシリアルデータ信号に変換して出力する第2のパラレル/シリアル変換部と、を有し、前記第1のシリアルデータ信号と前記第2のシリアルデータ信号とは位相が互いに異なり、前記第1のシリアルデータ信号と前記第2のシリアルデータ信号の一方は、前記第1のシリアルデータ信号と前記第2のシリアルデータ信号の他方をパラレルデータ信号に変換するためのクロック信号であることを特徴とする送信装置である。

40

## 【発明の効果】

## 【0013】

本発明によれば、簡易な構成で精度の高い通信を実現できる。

50

## 【図面の簡単な説明】

## 【0014】

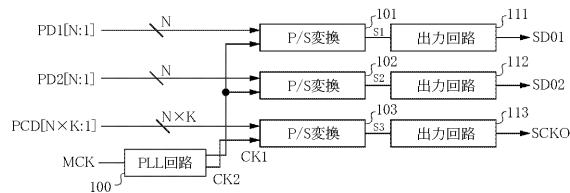

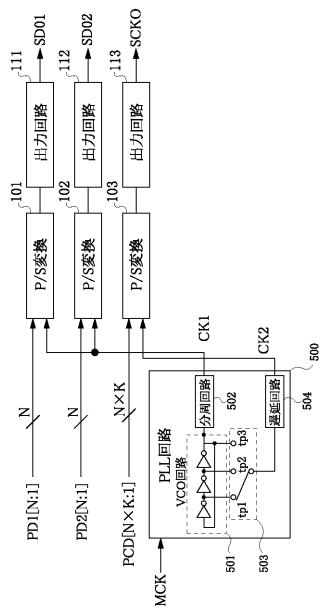

【図1】本発明に係る送信装置の構成例を示すブロック図である。

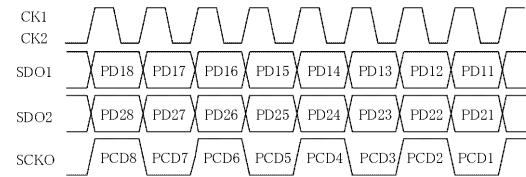

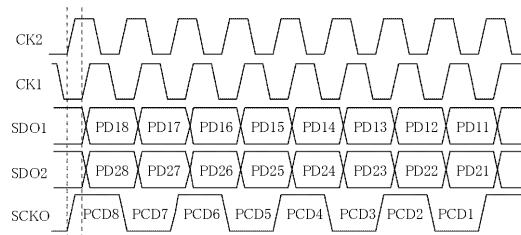

【図2】実施例1に係るタイミング図である。

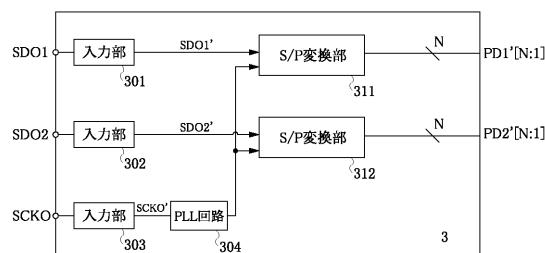

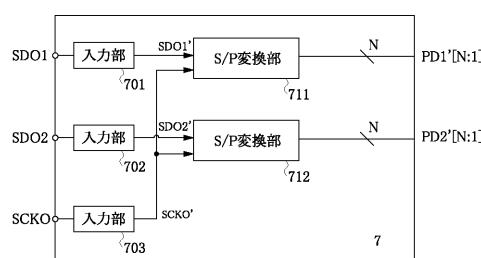

【図3】本発明に係る受信側デバイスの構成例を示すブロック図である。

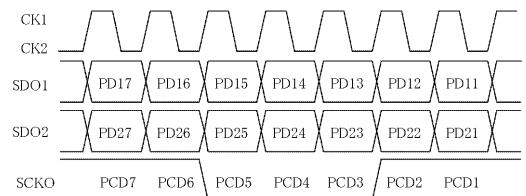

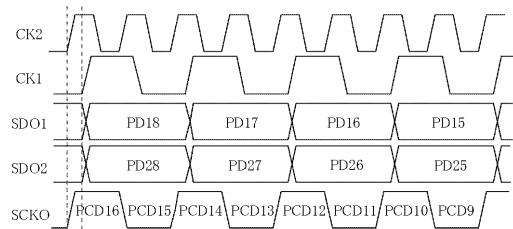

【図4】実施例2に係るタイミング図である。

【図5】本発明に係る送信装置の別の構成例を示すブロック図である。

【図6】実施例3に係るタイミング図である。

【図7】実施例3に係る別のタイミング図である。

【図8】本発明に係る受信側デバイスの別の構成例を示すブロック図である。

10

## 【発明を実施するための形態】

## 【0015】

(実施例1)

図面を参照しながら、本発明に係る第1の実施例を説明する。

## 【0016】

図1は、本発明を適用したシリアル通信回路の構成例を示すブロック図である。

## 【0017】

送信装置1は、クロック生成部であるPLL回路100、パラレル/シリアル変換部(P/S変換部)101～103と、出力部111～113とを含む。PLL回路100は、基準クロックMCKをN倍した第1変換クロックCK1と、基準クロックMCKをN×K倍した第2変換クロックCK2とを生成する。NとKは、それぞれ自然数である。P/S変換部101～103は、基準クロックMCKに同期して入力されたパラレルデータ信号をシリアルデータ信号に変換して出力し、出力部111～113は、P/S変換部101～103から出力されたシリアルデータ信号を例えればバッファして出力する。

20

## 【0018】

第1のパラレル/シリアル変換部であるP/S変換部101は、第1のパラレルデータ信号であるNビットのパラレルデータ信号PD1[N:1]とPLL回路100からの第1変換クロックCK1とが入力される構成となっている。パラレルデータ信号PD1[N:1]は第1変換クロックCK1に同期してNビットのシリアルデータS1に変換されて、出力部111によって例えればバッファされて第1のシリアルデータ信号SDO1として出力される。

30

## 【0019】

同様に、別の第1のパラレル/シリアル変換部であるP/S変換部102は、別の第1のパラレルデータ信号であるNビットのパラレルデータ信号PD2[N:1]とPLL回路100からの第1変換クロックCK1とが入力される構成となっている。パラレルデータ信号PD2[N:1]は第1変換クロックCK1に同期してNビットのシリアルデータS2に変換されて、出力部112によって例えればバッファされて別の第1のシリアルデータ信号SDO2として出力される。

## 【0020】

また、第2のパラレル/シリアル変換部であるP/S変換部103は、第2のパラレルデータ信号であるN×Kビットのパラレルクロックデータ信号PCD[N×K:1]とPLL回路100からの第2変換クロックCK2とが入力される構成となっている。パラレルクロックデータ信号PCD[N×K:1]は第2変換クロックCK2に同期してN×KビットのシリアルデータS3に変換されて、出力部113によって例えればバッファされて第2のシリアルデータ信号である転送クロックSCK0として出力される。後述するが、転送クロックSCK0は、第1のシリアルデータ信号をパラレルデータ信号に変換するために用いられるクロック信号である。

40

## 【0021】

ここで、電源変動や温度変化に対する特性の変化を揃えるためにもP/S変換部101～103で生じる遅延量が等しくなるように設計することが望ましい。具体的には、ある

50

ビットの信号に着目したときに P / S 変換部内で通過する論理ゲートの段数を揃えることが考えられる。また出力回路 111 ~ 113 も互いに同じ回路構成であることが望ましい。シリアルデータ信号と転送クロックとの位相が一致することが望ましいが、例えばシリアルデータ信号のデータレートに対して 1 / 10 以下の位相差であれば、問題にはならない。

#### 【 0 0 2 2 】

次に、図 1 と図 2 を参照しながら本実施例に係る動作を説明する。図 2 は、N = 8、K = 1 の場合、すなわち、第 1 変換クロック CK1 と第 2 変換クロック CK2 とが一致する場合の、第 1 および第 2 変換クロック CK1、CK2 とシリアルデータ信号 SDO1、SDO2 および SCK0 との関係を示すタイミング図である。

10

#### 【 0 0 2 3 】

図 2 において、P / S 変換部 103 に入力されるパラレルクロックデータ信号 PCD [N × K : 1] は上位ビット側から [High (H)、Low (L)、H、L、H、L、H、L] であって、P / S 変換部 103 からは上位ビット側から出力される。そのため、転送クロック SCK0 は、第 2 変換クロック CK2 に同期して H と L とが交互に切り替わる。シリアルデータ信号 SDO1 および SDO2 も同様に、第 1 変換クロック CK1 に同期して出力される。

#### 【 0 0 2 4 】

図 1 に示す送信装置の構成において P / S 変換部 101 ~ 103 および出力部 111 ~ 113 は、各データ間で同じ構成となっている。これにより、シリアル通信回路 1 の電源電圧、温度などの動作条件が変動したり、半導体プロセスに起因する素子特性がばらついたりしても、その影響が同様なものとなる。つまり、本発明によれば、シリアルデータ信号 SDO1 および SDO2 が遷移するタイミングと、転送クロック SCK0 が遷移するタイミングとは、相対的な関係が保たれる。これにより、従来技術で問題となっていた遅延時間のばらつきを低減し、理想的には 0 にすることが可能となる。

20

#### 【 0 0 2 5 】

受信側デバイス（以下、受信装置とも称す）の構成例を図 3 に示す。受信側デバイス 3 は、入力されたシリアルデータ信号 SDO1、SDO2 および転送クロック SCK0 を出力する入力部 301 ~ 303 と、PLL 回路 304 と、シリアル / パラレル変換部（S / P 変換部）311、312 を含む。

30

#### 【 0 0 2 6 】

入力部 301 ~ 303 は、例えばバッファを含んで構成されている。

#### 【 0 0 2 7 】

第 2 の発振部である PLL 回路 304 は入力部 303 から入力されるシリアルデータ信号である転送クロック SCK0' に基づいて発振し、第 2 中間クロックを出力する。本実施例では、第 2 中間クロックは転送クロック SCK0' を N 週倍したものとである。

#### 【 0 0 2 8 】

S / P 変換部 311 は、入力部 301 からのシリアルデータ信号 SDO1' と PLL 回路 304 からのクロックとが入力され、シリアルデータ信号 SDO1' を PLL 回路 304 からのクロックに同期してパラレルデータ信号 PDI1' [N : 1] に変換する。

40

#### 【 0 0 2 9 】

S / P 変換部 312 は、入力部 302 からのシリアルデータ信号 SDO2' と PLL 回路 304 からのクロックとが入力され、シリアルデータ信号 SDO2' を PLL 回路 304 からのクロックに同期してパラレルデータ信号 PDI2' [N : 1] に変換する。

#### 【 0 0 3 0 】

この構成によれば、シリアルデータ信号 SDO1'、SDO2' と転送クロック SCK0' に基づいて PLL 回路から出力されるクロックとの間のスキューが低減されるため、シリアルデータ信号をパラレルデータ信号に復元するためのタイミング設計が容易になる。

#### 【 0 0 3 1 】

50

以上で説明したように、本発明に係る第1の実施例によれば、転送クロックとシリアルデータ信号との、信号が遷移するタイミングの遅延時間のずれを低減することができ、簡易な構成で精度の高い通信を実現できる。また、受信側のデバイスの設計を容易にできる。

【0032】

(実施例2)

図面を参照しながら、本発明に係る第2の実施例を説明する。第1の実施例とは、Nの値と、転送クロックSCKOを生成するためのパラレルクロックデータ信号PCD[N×K:1]の配列とが異なっている。

【0033】

10

図4は、N=7かつK=1の場合の、第1および第2変換クロックCK1、CK2と、シリアルデータ信号SDO1、SDO2およびSCKOの関係を示すタイミング図である。第1変換クロックCK1は基準クロックMCKに対して7倍されたものであり、第2変換クロックCK2も基準クロックMCKに対して $7 \times 1 = 7$ 倍されたものとなる。本実施例においても、第1および第2変換クロックCK1、CK2の位相が一致している場合を例示している。

【0034】

図4において、P/S変換部103に入力されるパラレルクロックデータ信号PCD[N×K:1]は上位ビット側から[H、H、L、L、L、H、H]であって、P/S変換部103からは上位ビット側から出力される。このときの転送クロックSCKOは、周波数が基準クロックMCKと等しく、かつH期間とL期間との比が4:3である信号となる。

20

【0035】

以上の説明で明らかなのは、パラレルクロックデータ信号PCD[N×K:1]の配列を可変させることで、転送クロックSCKOの周波数やデューティー比を可変することができる。つまり、パラレルクロックデータ信号PCD[N×K:1]を可変に設定する不図示のパラレルデータ設定部を設けることで、回路構成を変更することなく、様々な通信規格に対応できるようになる。

【0036】

なお、受信側デバイスは、第1の実施例で説明したものと同様の構成を取ることができる。

30

【0037】

以上で説明したように、本発明に係る第2の実施例によれば、転送クロックとシリアルデータ信号との間のスキューレを低減することができ、簡易な構成で精度の高い通信を実現できる。また、受信側のデバイスの設計を容易にできる。さらに、パラレルクロックデータ信号PCD[N×K:1]を可変に設定することで様々な通信規格に対応できる。

【0038】

(実施例3)

図5ないし図8を参照しながら、本発明に係る第3の実施例を説明する。

【0039】

40

図5は、本実施例に係る送信装置5の構成例を示すブロック図である。図1に示す送信装置1と同一の構成に対しては同じ符号を付している。送信装置5は送信装置1と異なり、第1および第2転送クロックCK1、CK2の位相関係を変化させることができる。

【0040】

PLL回路500は、第1の発振部であるリングオシレータ型のVCO(Voltage Controlled Oscillator)回路501、分周部である分周回路502、位相調整部である位相選択回路503および遅延部である遅延回路504を含む。VCO回路501は、3個のインバータがリング状に接続されており、インバータ回路の駆動電流値を電圧信号によって制御することで出力される信号の周波数を制御する。VCO回路501は、PLL回路500に入力される基準クロックMCKに基づいて発振し

50

、基準クロック MCK を  $N \times K$  遅倍した第 1 中間クロックを出力するように構成されている。分周回路 502 は VCO 回路 501 から出力される信号に対して  $1/K$  倍の周波数の分周クロックを生成する。ここでは分周クロックが第 1 変換クロック CK1 として P/S 変換部 101、102 に与えられる。位相選択回路 503 は、不図示の制御部から供給される制御信号に応じて、リングオシレータを構成するインバータ回路の各出力 tp1、tp2、tp3 のいずれか 1 つを選択して遅延回路 504 に入力する。遅延回路 504 は、位相選択回路 503 を介して与えられた信号に対して、分周回路 502 で生じる遅延量と同等の遅延量を付加した遅延クロックを生成する。ここでは遅延クロックが第 2 変換クロック CK2 として出力される。

## 【0041】

10

図 6 は、 $N = 8$  かつ  $K = 1$  であり、位相選択回路 503 で tp1 が選択された場合の、第 1 および第 2 変換クロック CK1、CK2 と、シリアルデータ信号 SDO1、SDO2 および SCKO の関係を示すタイミング図である。図 6 において、P/S 変換部 103 に入力されるパラレルクロックデータ信号 PCD [ $N \times K : 1$ ] は上位ビット側から [H、L、H、L、H、L、H、L] であって、P/S 変換部 103 からは上位ビット側から出力される。本実施例においては第 1 および第 2 変換クロック CK1、CK2 は基準クロック MCK を 8 遅倍したもので、互いに位相が  $1/3$  周期ずれたものとなっている。

## 【0042】

図から明らかのように、シリアルデータ信号 SDO1、SDO2 は第 1 変換クロック CK1 に、転送クロック SCKO は第 2 変換クロック CK2 に同期しているために、シリアルデータ信号 SDO1、SDO2 と転送クロック SCKO とは互いに位相が異なっている。

20

## 【0043】

このように、シリアルデータ信号 SDO1、SDO2 と転送クロック SCKO との位相を互いに異ならせることで、受信側デバイスの構成をさらに簡略化することが可能になる。以下にその理由を説明する。

## 【0044】

30

図 7 に、受信側デバイス（受信装置）の構成例を示す。受信側デバイス 7 は、シリアルデータ信号 SDO1、SDO2 および転送クロック SCKO を受けて出力する入力部 701～703 と、シリアル／パラレル変換部（S/P 変換部）711、712 とを含む。

## 【0045】

入力部 701～703 は、例えばバッファを含んで構成されている。

## 【0046】

S/P 変換部 711 は、入力部 701 からのシリアルデータ信号 SDO1' と転送クロック SCKO' とが入力され、シリアルデータ信号 SDO1' を転送クロックに同期して第 3 のパラレルデータ信号であるパラレルデータ信号 PD1' [ $N : 1$ ] に変換する。

## 【0047】

S/P 変換部 712 は、入力部 702 からのシリアルデータ信号 SDO2' と転送クロック SCKO' とが入力され、シリアルデータ信号 SDO2' を転送クロックに同期して第 3 のパラレルデータ信号であるパラレルデータ信号 PD2' [ $N : 1$ ] に変換する。

40

## 【0048】

既に述べたとおり、シリアルデータ信号 SDO1、SDO2 と転送クロック SCKO との位相は互いに異なっている。そのため、同等の回路構成を有する入力部 701～703 から出力されるシリアルデータ信号 SDO1'、SDO2' と転送クロック SCKO' との位相も互いに異なっている。そのため、転送クロック SCKO' の立ち上がりあるいは立ち下がりのエッジに同期して、S/P 変換部 711、712 がシリアルデータ信号 SDO1'、SDO2' をラッチしても、十分なセットアップ時間を確保できる。つまり、図 3 に示したように受信側デバイスに PLL 回路を設けることが不要になるので、精度の高い通信を実現しながら、受信側デバイスの回路構成をさらに簡略化できるという効果が得られるものである。

50

## 【0049】

以上では  $K = 1$  の場合を説明したが、  $K$  はこれに限定されるものではない。一例として  $N = 8$ 、  $K = 2$  かつ、 パラレルクロックデータ信号  $PCD[8 \times 2 : 1]$  が、 上位ビット側から [H, L, H, L, . . ., H, L] と、 H と L とが交互に現れる場合を、 図 8 を参照しながら説明する。なお、 ここでは位相選択回路 503 は  $tp1$  を遅延回路 504 と接続するように制御されているものとする。

## 【0050】

$PLL$  回路 500 に入力される基準クロック  $MCK$  を 8 遅倍したものが第 1 変換クロック  $CK1$  に、  $8 \times 2 = 16$  遅倍したものが第 2 変換クロック  $CK2$  として  $PLL$  回路 500 から出力される。つまり、  $VCO$  回路 501 は基準クロック  $MCK$  の 16 遅倍で発振し、 分周回路 502 で 2 分周している。

10

## 【0051】

パラレルデータ信号  $PD1[N : 1]$  は第 1 変換クロック  $CK1$  に同期して  $P/S$  変換部 101 にてシリアル変換されて、 出力回路 111 からシリアルデータ信号  $SDO1$  として出力される。

## 【0052】

同様に、 パラレルデータ信号  $PD2[N : 1]$  は第 1 変換クロック  $CK2$  に同期して  $P/S$  変換部 102 にてシリアル変換されて、 出力回路 112 からシリアルデータ信号  $SDO2$  として出力される。

20

## 【0053】

また、 パラレルクロックデータ信号  $PCD[N \times K : 1]$  は第 2 変換クロック  $CK2$  に同期して  $P/S$  変換部 103 にてシリアル変換されて、 出力回路 113 から転送クロック  $SCKO$  として出力される。

## 【0054】

位相選択回路 503 にて  $tp1$  を選択しているので、 第 2 の変換クロック  $CK2$  は、 第 1 の変換クロック  $CK1$  に対して基準クロック  $MCK$  の  $1 / (N \times K \times 3) = 1 / 48$  周期だけ位相が異なっている。また、 シリアルデータ信号  $SDO1$ 、  $SDO2$  と転送クロック  $SCKO$  とは異なる変換クロックに同期している。そのため、 シリアルデータ信号  $SDO1$ 、  $SDO2$  は転送クロック  $SCKO$  の周期と同じデータレートを有し、 両者の位相は基準クロック  $MCK$  の  $1 / 48$  周期だけ異なっている。

30

## 【0055】

この場合にも、 受信側デバイスは図 7 に示したようなシリアルデータ信号  $SDO1$ 、  $SDO2$  を、 転送クロック  $SCKO$  の立ち上がりあるいは立ち下がりエッジに同期して動作する  $S/P$  変換部にてパラレルデータ信号に変換することができる。転送クロック  $SCKO$  の立ち上がりあるいは立ち下がりエッジを利用してできるので、 受信側デバイスに  $PLL$  回路を省略することができる利点は多く、 設計が容易になるだけでなく、 さらに構成部品を少なくできるので、 コストを低減することが可能となる。

## 【0056】

$VCO$  回路 501 は例示したものに限られず、 リングオシレータの段数を増加させれば、 第 1 および第 2 変換クロックの位相差をより細かく調整できるようになる。

40

## 【0057】

また、 図 5 に示した送信装置では、 リングオシレータのインバータからの出力がそのまま遅延回路 504 に与えられているが、 これらの出力を例えばインバタ回路で反転させるように構成しても良い。これによって、 第 1 および第 2 変換クロックの位相関係の調整をさらに行うことができる。インバタ回路は、 リングオシレータの各段に 1 個ずつ設けても良いし、 位相選択回路の後段に設けても良い。

## 【0058】

以上で説明したように、 本実施例によれば、 簡易な構成で精度の高い通信を実現することができ、 また、 受信側のデバイスの設計をさらに容易にすることができる。

50

## 【0059】

(その他)

ここまではパラレルデータ信号 P D 1、P D 2 とがある場合を例にとって説明してきたが、パラレルデータ信号の数はこれに限定されず、1個でも良いし、3個以上であってもよい。いずれの場合にも、スキューを低減することができるという本発明の効果に変わりはない。

## 【0060】

以上で説明した各実施例では、パラレルクロックデータ信号 P C D をパラレルデータ信号 P D 1、P D 2 のビット数に対して K 倍としていたが、パラレルデータ信号 P D 1、P D 2 のビット数をパラレルクロックデータ信号 P C D の K 倍のビット数に設定しても良い

10

。

## 【0061】

また、パラレルクロックデータ信号 P C D を N ビットとする一方でパラレルデータ信号 P D 1、P D 2 を  $N \times K$  ビットとして、さらに、パラレルデータ信号 P D 1、P D 2 のデータの K ビットを 1 単位として扱うことが考えられる。このようにすることで、第 1 および第 2 変換クロック C K 1、C K 2 が同一の周波数を有している場合でも、シリアルデータ信号 S D O 1、S D O 2 のデータレートを転送クロック S C K O に対して  $1 / K$  倍とすることができる。

## 【0062】

以上で説明した各実施例では、第 1 および第 2 変換クロック C K 1、C K 2 を出力できる P L L 回路を例示した。しかしながら、K = 1 に設定する場合には、必ずしも C K 1 と C K 2 を別々の出力とする必要はなく、どちらか一方に統一しても良い。これにより、送信装置の構成をさらに簡略化することが可能となる。

20

## 【0063】

また、各出力部は、バッファ以外にも L V D S ドライバのように差動信号を出力する差動出力回路であってもよい。小振幅差動信号を出力する L V D S ドライバは、一般に知られたものが利用できる。この場合には、受信側デバイスの各入力部も、差動信号を受信できる構成にする必要がある。

## 【0064】

以上で説明したように、本発明によれば、転送クロックとシリアルデータ信号とのスキューを低減することができ、簡易な構成で精度の高い通信を実現できる。また、受信側のデバイスの設計を容易にできる。つまり、以上で説明した送信装置と受信装置とを備える通信システムは、スキューが低減されているために精度の高い通信が実現でき、さらにその設計が容易にできるものである。

30

## 【符号の説明】

## 【0065】

M C K 基準クロック

C K 1 第 1 変換クロック

C K 2 第 2 変換クロック

S D O 1 シリアルデータ信号

40

S D O 2 シリアルデータ信号

S C K O 転送クロック

P C D パラレルクロックデータ信号

P D 1 パラレルデータ信号

P D 2 パラレルデータ信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2009-212992(JP,A)

特開2007-306545(JP,A)

特開2005-277888(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |                  |

|--------|------------------|

| H 03 M | 3 / 00 - 11 / 00 |

| H 03 K | 5 / 00           |

| H 03 L | 7 / 00           |