República Federativa do Brasil

Ministério do Desenvolvimento, Indústria,

Comércio e Serviços

Instituto Nacional da Propriedade Industrial

---

(11) BR 112018074342-9 B1

(22) Data do Depósito: 15/05/2017

(45) Data de Concessão: 09/01/2024

**(54) Título:** INTENSIDADE DE ACIONAMENTO DE CONTROLE ADAPTATIVO DE POTÊNCIA MULTIPLEXADA DE TRILHOS DE POTÊNCIA DE ALIMENTAÇÃO EM UM SISTEMA DE MULTIPLEXAÇÃO DE POTÊNCIA PARA UM CIRCUITO ENERGIZADO

**(51) Int.Cl.:** H03K 19/003.

**(52) CPC:** H03K 19/0016; H03K 19/00384.

**(30) Prioridade Unionista:** 12/05/2017 US 15/593,809; 15/02/2017 US 62/459,187; 27/05/2016 US 62/342,560.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** SHRADDHA SRIDHAR; YESHWANT NAGARAJ KOLLA; NEEL SHASHANK NATEKAR.

**(86) Pedido PCT:** PCT US2017032632 de 15/05/2017

**(87) Publicação PCT:** WO 2017/205096 de 30/11/2017

**(85) Data do Início da Fase Nacional:** 26/11/2018

**(57) Resumo:** Intensidade de disco de controle adaptativo de potência multiplexada de trilhos de potência de suprimento (204(N)) em um sistema de multiplexação de potência (200) para um circuito energizado (208) é divulgada. Um circuito de multiplexação de potência (201) no sistema de multiplexação de potência inclui uma pluralidade de circuitos de seleção de suprimento (216)(por exemplo, comutadores principais) cada qual acoplado entre um respectivo trilho de potência de suprimento e um trilho de potência de saída (206) acoplado a um circuito eletrificado (208). O circuito de multiplexação de potência (201) é configurado para ativar um circuito de seleção de fornecimento selecionado para comutar acoplamento de um trilho de potência de suprimento associado para o trilho de potência de saída para alimentar o circuito energizado. Em um exemplo, os circuitos de seleção de suprimento incluem, cada qual, uma pluralidade de circuitos de seleção de comutador de potência acoplado a um trilho de potência de fornecimento associado. Os circuitos de seleção de comutador de potência são configurados para serem ativados e desativados por um circuito de controle (222) para ajustar intensidade de disco de um trilho de potência de suprimento multiplexado baseado em condições operacionais, as quais podem ser relevantes para variações de desempenho.

"INTENSIDADE DE ACIONAMENTO DE CONTROLE ADAPTATIVO DE POTÊNCIA MULTIPLEXADA DE TRILHOS DE POTÊNCIA DE ALIMENTAÇÃO EM UM SISTEMA DE MULTIPLEXAÇÃO DE POTÊNCIA PARA UM CIRCUITO ENERGIZADO"

PEDIDOS PRIORITÁRIOS

[0001] Este pedido de patente reivindica prioridade junto ao Pedido de Patente Provisório Americano, cujo número de série é 62/342.560, depositado em 27 de Maio de 2016, e intitulado "REGULAGEM DE INTENSIDADE DE ACIONAMENTO ADAPTATIVO DE CIRCUITOS DE SELEÇÃO DE ALIMENTAÇÃO EM UM SISTEMA DE MULTIPLEXAÇÃO DE POTÊNCIA", o qual é incorporado a este documento por meio de referência em sua totalidade.

[0002] Este pedido de patente também reivindica prioridade junto ao Pedido de Patente Provisório Americano, cujo número de série é 62/459.187, depositado em 15 de Fevereiro de 2017, e intitulado "INTENSIDADE DE ACIONAMENTO DE CONTROLE ADAPTATIVO DE POTÊNCIA MULTIPLEXADA DE TRILHOS DE POTÊNCIA DE ALIMENTAÇÃO EM UM SISTEMA DE MULTIPLEXAÇÃO DE POTÊNCIA PARA UM CIRCUITO ENERGIZADO", o qual é ainda incorporado a este documento por meio de referência em sua totalidade.

[0003] Este pedido reivindica ainda prioridade junto ao Pedido de Patente Americano, cujo número de série é 15/593.809, depositado em 12 de Maio de 2017, e intitulado "INTENSIDADE DE ACIONAMENTO DE CONTROLE ADAPTATIVO DE POTÊNCIA MULTIPLEXADA DE TRILHOS DE POTÊNCIA DE ALIMENTAÇÃO EM UM SISTEMA DE MULTIPLEXAÇÃO DE POTÊNCIA PARA UM CIRCUITO ENERGIZADO", o qual é incorporado por meio de referência em sua totalidade.

## ANTECEDENTES

### I. Campo da Divulgação

[0004] A tecnologia da presente invenção se refere, de forma genérica, a sistemas de multiplexação de potência configurados para suprir energia, de forma seletiva, a partir de múltiplos trilhos de potência para circuitos operacionais.

### II. Antecedentes

[0005] Circuitos são, crescentemente, projetados com conservação de energia em mente. Isto se torna particularmente o caso para dispositivos eletrônicos portáteis que são alimentados através de baterias. Exemplos comuns incluem telefones e computadores laptop, dentre outros. O aumento indesejável do consumo de energia resulta em um consumo mais rápido da bateria e um tempo de vida útil mais curto da mesma. Um método de conservação de energia é a redução de uma frequência operacional de um circuito de acordo com a equação de potência ativa  $P = CV^2f$ . Entretanto, reduzir a frequência operacional resulta em um desempenho de circuito inferior (ou seja, velocidade). Outro método de conservação de energia é reduzir a tensão operacional, uma vez que, geralmente, a potência ativa reduz, quadraticamente, de acordo com uma dada redução na tensão operacional. Entretanto, reduzir a tensão operacional em um circuito reduz a velocidade de desempenho, a qual também pode ser indesejável. Além disso, determinadas células ou componentes de um circuito podem apresentar uma tensão operacional mínima abaixo das quais estas não poderão operar no sentido de leitura e escrita de dados, assim como no armazenamento de dados.

[0006] Para resolver o equilíbrio entre desempenho e consumo de energia, múltiplos domínios de tensão operacional ("domínios de tensão") estão sendo, crescentemente, providos em circuitos. Trajetos de circuitos são providos, os quais passam através de domínios de tensão múltiplos para prover diferentes tensões operacionais para diferentes componentes de um circuito. Prover múltiplos domínios de tensão permite que um domínio de tensão mais baixo forneça potência para componentes que não exigem níveis de tensão mínimos para conservar potência. Componentes que tanto possuem uma tensão operacional mínima para a funcionalidade de operação de memória quanto fornecem trajetos críticos onde o desempenho não pode ser sacrificado também permitem que o domínio de tensão mais baixo seja inferiorizado para conservar energia durante um modo de conservação de energia, ou amplificados para prover desempenho aumentado (ou seja, hiper desempenho), sem afetar a operação dos componentes no domínio de tensão superior.

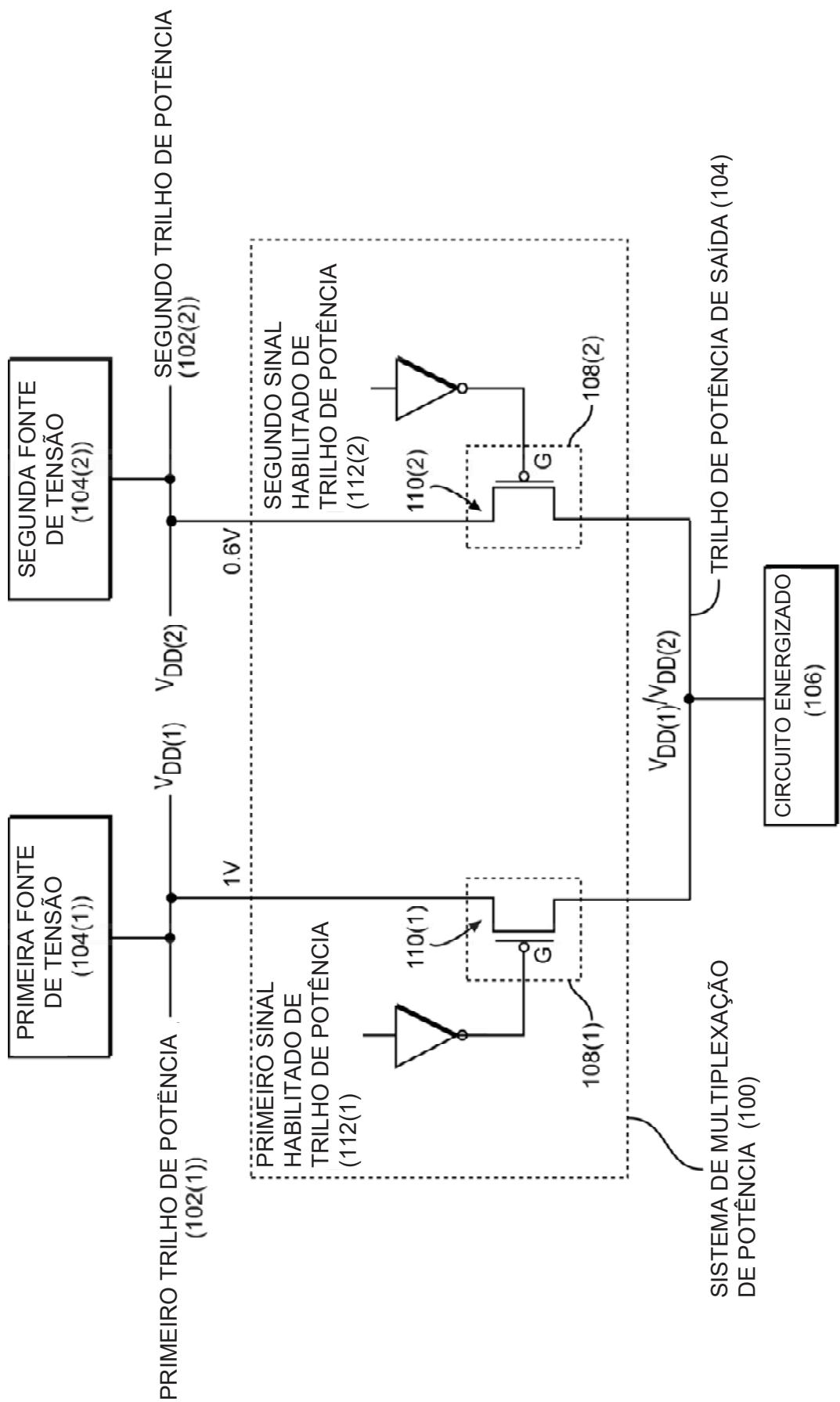

[0007] Neste sentido, um sistema de multiplexação de potência pode ser empregado para acoplar, seletivamente, um trilho de potência entre múltiplos trilhos de potência, os quais possuem diferentes domínios de tensão (ou seja, níveis de tensão) para suprir potência para um circuito. A figura 1 é um diagrama de bloco de tal sistema de multiplexação de potência 100 na figura 1, um primeiro trilho de potência de alimentação 102(1) e um segundo trilho de potência de alimentação 102(2) são providos. O primeiro trilho de potência de alimentação 102(1) é configurado para prover uma primeira fonte de tensão 104(1) em uma primeira

tensão  $V_{DD(1)}$ . O segundo trilho de potência de alimentação 102(2) é configurado para prover primeira e segunda fontes de tensão 104(2) em uma segunda tensão  $V_{DD(2)}$ . A primeira e a segunda fontes de tensão 104(1), 104(2) podem ser providas pela mesma ou por diferentes fontes de tensão (não mostradas). Por exemplo, a primeira tensão  $V_{DD(1)}$  pode ser de 1 Volt (V) e a segunda tensão  $V_{DD(2)}$  pode ser de 0,6V. Como um exemplo, o sistema de multiplexação de potência 100 pode ser configurado para acoplar seletivamente o primeiro trilho de potência de alimentação 102(1) ou o segundo trilho de potência de alimentação 102(2) para um trilho de potência de saída 104 acoplado para um circuito energizado 106 baseado em um modo operacional do circuito energizado 106. Por exemplo, caso o circuito energizado 106 seja um circuito de memória, tal como um arranjo de memória em um sistema baseado em processador, o sistema de multiplexação de potência 100 pode ser configurado para acoplar o primeiro trilho de potência de alimentação 102(1) para o trilho de potência de saída 104 durante operações de memória, e acoplar o segundo trilho de potência de alimentação 102(2) para o trilho de potência de saída 104 durante um modo inativo. Por exemplo, a segunda tensão  $V_{DD(2)}$  pode ser suficiente para retenção de memória no circuito energizado 106.

[0008] Com referência contínua à figura 1, o sistema de multiplexação de potência 100 inclui um primeiro circuito head switch 108(1) na forma de um transistor de semicondutor de óxido metálico (MOS) do tipo P (PMOS) 110(1). O transistor de PMOS 110(1) é acoplado entre o primeiro trilho de potência de alimentação 102(1) e o trilho de potência de saída 104. O transistor de PMOS 110(1) é

configurado para ser ativado e desativado em resposta a um estado de um primeiro trilho de potência de sinal habilitado 112(1) para acoplar e desacoplar, respectivamente, o primeiro trilho de potência de alimentação 102(1) para o trilho de potência de saída 104. O sistema de multiplexação de potência 100 ainda inclui um segundo circuito head switch108(2), ainda na forma de um transistor de PMOS 110(2) que é acoplado entre o segundo trilho de potência de alimentação 102(2) e o trilho de potência de saída 104. O segundo circuito head switch108(2) é configurado para acoplar e desacoplar, seletivamente, o segundo trilho de potência de alimentação 102(2) para e a partir do trilho de potência de saída 104 em resposta a um segundo trilho de potência de sinal habilitado 112(2).

[0009] O primeiro e o segundo transistores PMOS 110(1), 110(2) no primeiro e no segundo circuitos comutadores 108(1), 108(2) são dimensionados para prover a intensidade de acionamento (drive strength) desejada para suprir energia do primeiro e segundo trilhos de potência 102(1), 102(2) para o trilho de potência de saída 104. Entretanto, variações de temperatura de tensão de processo (PVT) podem variar a intensidade do acionamento do primeiro e do segundo transistores de PMOS 110(1), 110(2) a partir das suas intensidades de acionamento esperadas. O primeiro e o segundo transistores de PMOS 110(1), 110(2) podem ser superdimensionados e/ou transistores adicionais podem ser providos nos respectivos primeiro e segundo circuitos head switch 108(1), 108(2) para aumentar a intensidade de acionamento para prover uma margem de intensidade de acionamento na tensão  $V_{DD(1)}$ ,  $V_{DD(N)}$  provida pela primeira e

segunda fontes de tensão 104(1), 104(2) no trilho de potência de saída 104 quando os respectivos primeiro e segundo trilho de potência 102(1), 102(2) são acoplados ao trilho de potência de saída 104. Entretanto, aumentar a intensidade de acionamento através da alimentação de transistores superdimensionados e/ou transistores adicionais no sistema de multiplexação de potência 100 aumenta o consumo de energia.

#### SUMÁRIO DA INVENÇÃO

[0010] Os aspectos divulgados na descrição detalhada incluem a intensidade de controle adaptativo da potência multiplexada de trilhos de potência de alimentação em um sistema de multiplexação de potência para um circuito energizado. Nos aspectos exemplares descritos nesta divulgação, é proporcionado um circuito de multiplexação de potência no sistema de multiplexação de potência. O circuito de multiplexação de energia inclui uma pluralidade de circuitos de seleção de alimentação, cada um acoplado entre um respectivo trilho de potência de alimentação entre uma pluralidade de trilhos de potência de alimentação e um trilho de potência de saída, que é acoplado a um circuito energizado. O circuito de multiplexação de energia é configurado para ativar um circuito de seleção de alimentação selecionado entre a pluralidade de circuitos de seleção de alimentação para alternar o acoplamento de um trilho de potência de alimentação associado ao trilho de alimentação de saída para alimentar o circuito energizado. Para proporcionar a intensidade de controlar a intensidade de acionamento de um circuito de seleção de alimentação ativado no circuito de multiplexação de potência, os aspectos

exemplares descritos nesta divulgação também fornecem para cada circuito de seleção de alimentação no circuito de multiplexação de potência a ser configurado para seletivamente acionar uma tensão de uma fonte associada um trilho de potência para o trilho de potência de saída em uma intensidade de unidade controlada com base em um indicador de intensidade de unidade. Desta forma, como exemplo, a intensidade de acionamento do circuito de seleção de alimentação ativado pode ser controlada e ajustada de forma adaptável para compensar as variações da temperatura de tensão do processo (PVT) para reduzir a margem de intensidade do inversor e, consequentemente, o consumo de energia.

[0011] Como um exemplo, pode ser fornecido um sistema de multiplexação de potência que é configurado para controlar de forma adaptável a intensidade do inversor de energia multiplexada de um barramento de energia de alimentação lógico e um barramento de alimentação de memória em vários domínios de tensão para um arranjo de memória como um circuito energizado. A energia do barramento de alimentação da memória é multiplexada na matriz de memória para retenção de dados quando a tensão do barramento de alimentação da fonte lógica pode não ser suficiente para alimentar a matriz de memória para retenção de dados. O circuito de multiplexação de energia inclui um circuito de seleção de alimentação lógico configurado para acoplar seletivamente o barramento de alimentação da fonte lógica a um barramento de energia de saída, que é acoplado à matriz de memória. O circuito de multiplexação de energia também inclui um circuito de seleção de alimentação de memória configurado para acoplar seletivamente o barramento de

potência de alimentação de memória ao barramento de alimentação de saída. Os circuitos lógicos e de seleção de alimentação de memória incluem, cada qual, uma pluralidade de circuitos comutadores de alimentação lógicos e de memória (por exemplo, comutadores principais) acoplados entre os respectivos trilhos de alimentação lógico e de memória e o barramento de saída de energia. Cada um dos circuitos comutadores de alimentação lógicos e de memória possui uma intensidade de unidade associada. Cada um dos circuitos lógicos e de memória são configurados para serem ativados individualmente para acoplar os trilhos de alimentação lógico ou de memória ao barramento de saída, contribuindo para direcionar a tensão da lógica ativada ou barramento de alimentação de memória para o barramento de saída. Um circuito de controle é configurado para controlar a intensidade do atuador do circuito de seleção de fonte lógica ou de memória ativada. O circuito de seleção de alimentação lógico pode ser configurado para acoplar o trilho de alimentação de saída ao barramento de alimentação da fonte lógica para fornecer energia ao barramento de memória quando o barramento de alimentação da fonte lógica pode satisfazer uma tensão operacional mínima do domínio de memória. Desta maneira, como um exemplo não limitativo, a capacitância de desacoplamento intrínseca adicional do arranjo de memória é acoplada ao barramento de alimentação de energia lógica durante os modos de maior potência dos circuitos lógicos quando o barramento de alimentação de energia lógica pode satisfazer a tensão operacional mínima da matriz de memória. Os circuitos lógicos em um domínio lógico ainda podem ser alimentados separadamente a partir da matriz de memória se

o circuito de seleção do barramento de alimentação acoplar um barramento de alimentação da fonte de memória ao barramento de alimentação de saída. No entanto, quando o barramento de alimentação da fonte lógica não satisfaç a tensão operacional mínima da matriz de memória, o circuito de seleção de fonte de memória pode acoplar o barramento de alimentação de memória ao barramento de saída para alimentar a matriz de memória da fonte de alimentação de memória.

[0012] Neste sentido, em um aspecto exemplificativo, é proporcionado um sistema de multiplexação de potência. O sistema de multiplexação de potência compreende um circuito de multiplexação de energia. O circuito de multiplexação de energia compreende um primeiro circuito de seleção de alimentação acoplado entre um primeiro trilho de potência de alimentação tendo uma primeira tensão e um barramento de potência de saída acoplado a pelo menos um circuito energizado. O primeiro circuito de seleção de alimentação é configurado para conduzir seletivamente a primeira tensão no primeiro trilho de alimentação ao trilho de alimentação de saída em uma primeira intensidade de acionamento baseada em um primeiro indicador de intensidade de acionamento em resposta a um primeiro indicador de seleção de trilho de alimentação indicando um primeiro estado habilitado de seleção de trilho potência de alimentação. O circuito de multiplexação de energia também compreende um segundo circuito de seleção de alimentação acoplado entre um segundo trilho de alimentação de energia tendo uma segunda tensão e o trilho de alimentação de saída. O segundo circuito de seleção de alimentação é configurado para conduzir seletivamente a segunda tensão no segundo trilho de

alimentação ao trilho de alimentação de saída com uma segunda intensidade de unidade baseada em um segundo indicador de intensidade em resposta a um segundo indicador de seleção de trilho de alimentação indicando um segundo estado habilitado de seleção de trilho de potência de alimentação. O sistema de multiplexação de potência também compreende pelo menos um circuito de controle. O pelo menos um circuito de controle está configurado para monitorar uma tensão de saída do barramento de saída. Em resposta ao primeiro indicador de seleção de trilho de alimentação, indicando o primeiro estado de habilitação de seleção de trilho de alimentação, o pelo menos um circuito de controle é configurado para comparar um nível de tensão da tensão de saída no trilho de saída a um primeiro nível de tensão de referência associado ao primeiro circuito de seleção de alimentação e gera seletivamente o primeiro indicador de intensidade de acionamento com base na comparação do nível de tensão da tensão de saída no barramento de potência de saída até o primeiro nível de tensão de referência. Em resposta ao segundo indicador de seleção de trilho de alimentação indicando o segundo estado habilitado de seleção de trilho de potência de alimentação, o pelo menos um circuito de controle é configurado para comparar o nível de tensão da tensão de saída no trilho de saída com um segundo nível de tensão de referência associado o segundo circuito de seleção de alimentação e gera seletivamente o segundo indicador de intensidade de acionamento com base na comparação do nível de tensão da tensão de saída no barramento de saída para o segundo nível de tensão de referência.

[0013] Em outro aspecto exemplar, é fornecido um sistema de multiplexação de potência. O sistema de multiplexação de potência compreende um primeiro meio de alimentação para conduzir seletivamente uma primeira tensão em um primeiro trilho de alimentação a um trilho de potência de saída em uma primeira intensidade de acionamento baseada em um primeiro indicador de intensidade de acionamento em resposta a um primeiro indicador de seleção de trilho de alimentação indicando primeiro estado de habilitação de seleção de trilho de potência de alimentação. O sistema de multiplexação de potência também compreende um segundo meio de alimentação para conduzir seletivamente uma segunda tensão em um segundo trilho de alimentação ao trilho de potência de saída em uma segunda intensidade de unidade baseada em um segundo indicador de intensidade de acionamento em resposta a um segundo indicador de seleção de trilho de alimentação a um segundo estado habilitado de seleção de trilho de potência de alimentação. O sistema de multiplexação de potência também compreende um meio para monitorar uma tensão de saída do trilho de potência de saída. O sistema de multiplexação de potência também compreende um meio para comparar um nível de tensão da tensão de saída no trilho de potência de saída a um primeiro nível de tensão de referência associado a um primeiro circuito de seleção de alimentação, em resposta ao primeiro indicador de seleção de trilho de alimentação indicando o primeiro estado habilitado de seleção de trilho de potência de alimentação. O sistema de multiplexação de potência também compreende um meio para gerar, seletivamente, o primeiro indicador de intensidade de acionamento baseado nos meios para comparar o nível de tensão

da tensão de saída no barramento de potência de saída ao primeiro nível de tensão de referência, em resposta ao primeiro indicador de seleção de barramento de alimentação indicando o estado de habilitação da primeira seleção de trilho de alimentação. O sistema de multiplexação de potência também compreende um meio para comparar o nível de tensão da tensão de saída no trilho de potência de saída a um segundo nível de tensão de referência associado a um segundo circuito de seleção de alimentação em resposta ao segundo indicador de seleção de trilho de alimentação indicando o segundo estado habilitado de seleção de potência de alimentação. O sistema de multiplexação de potência também compreende um meio para gerar seletivamente o segundo indicador de intensidade de acionamento baseado nos meios para comparar o nível de tensão da tensão de saída no barramento de saída ao segundo nível de referência em resposta ao segundo indicador de seleção do barramento de alimentação indicando o estado habilitado de seleção do trilho de potência de alimentação da segunda fonte.

[0014] Em outro aspecto exemplificativo, é fornecido um método de controle adaptativo da intensidade do inversor de potência multiplexada a partir de trilhos de potência de alimentação em um circuito de multiplexação de potência para um circuito energizado. O método compreende monitorar uma tensão de saída de um trilho de potência de saída. Em resposta a um primeiro indicador de seleção de trilho de alimentação indicando um primeiro estado habilitado de seleção de trilho de potência de alimentação, o método também compreende comparar um nível de tensão da tensão de saída no trilho de alimentação de saída a um

primeiro nível de tensão de referência associado a um primeiro circuito de seleção de alimentação, gerando seletivamente um primeiro indicador de intensidade de acionamento baseado na comparação do nível de tensão da tensão de saída no barramento de potência de saída até o primeiro nível de tensão de referência e direcionando seletivamente uma primeira tensão em um primeiro barramento de alimentação ao barramento de saída de uma primeira intensidade de acionamento baseada no primeiro indicador de intensidade de acionamento. Em resposta a um segundo indicador de seleção de trilho de alimentação indicando um segundo estado de habilitação de seleção de trilho de alimentação, o método comprehende comparar o nível de tensão da tensão de saída no trilho de alimentação de saída a um segundo nível de tensão de referência associado a um segundo circuito de seleção de alimentação, gerar seletivamente um segundo indicador de intensidade de acionamento baseado na comparação do nível de tensão da tensão de saída no barramento de saída para o segundo nível de tensão de referência, e direcionar seletivamente uma segunda tensão em um segundo barramento de alimentação para o barramento de saída segunda intensidade da unidade com base no segundo indicador de intensidade da unidade.

#### BREVE DESCRIÇÃO DAS FIGURAS

[0015] A Figura 1 é um diagrama de blocos de um sistema de multiplexação de potência exemplar que é configurado para acoplar seletivamente um trilho de potência

de alimentação entre uma pluralidade de trilhos de potência de alimentação a um circuito alimentado;

[0016] A Figura 2 é um diagrama de blocos de um sistema de multiplexação de potência exemplificativo que é configurado para controlar de forma adaptável a potência de multiplexação de uma pluralidade de trilhos de alimentação para um trilho de potência de saída para alimentar um circuito alimentado baseado em uma tensão de saída que pode ser responsável por variações de desempenho;

[0017] A Figura 3 é um fluxograma que ilustra um processo exemplar de um circuito de controle na Figura 2, que controla de forma adaptável a intensidade de acionamento dos circuitos de seleção de alimentação ativos em um circuito de multiplexação de potência na Figura 2, com base em uma tensão de saída;

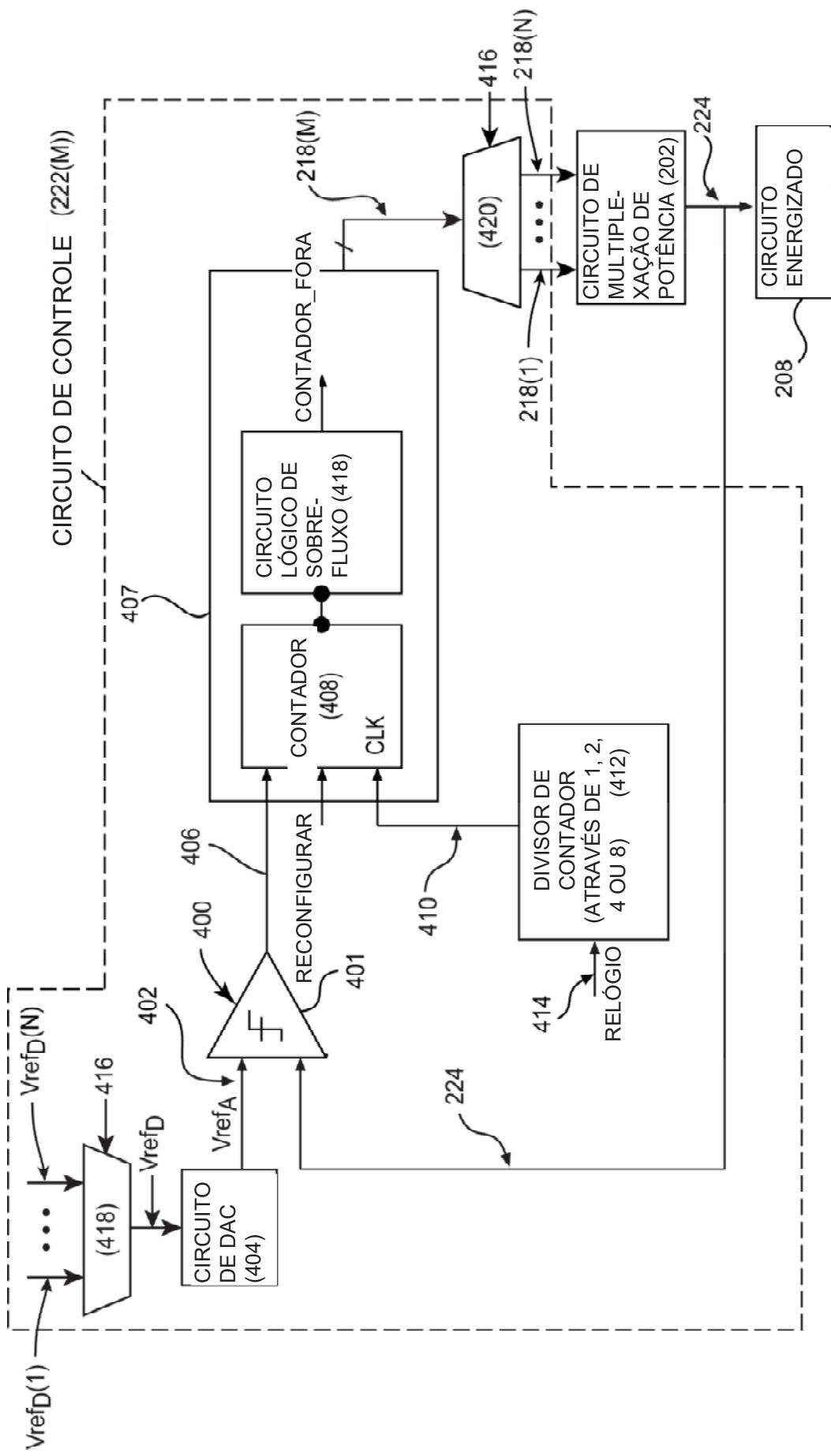

[0018] A Figura 4A é um diagrama de blocos de um circuito de controle exemplificativo que pode ser incluído no sistema de multiplexação de potência na Figura 2 para controlar de forma adaptativa a intensidade de acionamento de um circuito de seleção de alimentação ativo em um circuito de multiplexação de potência baseado em uma tensão de saída;

[0019] A Figura 4B é um diagrama de blocos de outro circuito de controle exemplificativo que pode ser incluído no sistema de multiplexação de potência na Figura 2 para controlar de forma adaptativa a intensidade de acionamento de um circuito de seleção de alimentação ativo em um circuito de multiplexação de potência baseado em uma tensão de saída;

[0020] A Figura 5 é um diagrama de blocos de outro sistema de multiplexação de potência exemplar que é

configurado para controlar de forma adaptativa a potência de multiplexação de uma pluralidade de trilhos de alimentação para um trilho de potência de saída para alimentar um circuito energizado baseado em uma tensão de saída no barramento de saída que pode ser responsável por variações de desempenho;

[0021] A Figura 6 é um diagrama de blocos de um circuito de multiplexação de potência exemplar que pode ser incluído no sistema de multiplexação de potência da Figura 5, em que o circuito de multiplexação de energia inclui adicionalmente um circuito de controle de queda de diodo configurado para ser ativado para fornecer uma conexão de queda de diodo entre um multiplexador fornecer o trilho de alimentação e o trilho de potência de saída, em resposta à comutação do acoplamento do trilho de alimentação de saída para um trilho de potência de alimentação selecionado diferente;

[0022] A Figura 7 é um diagrama de blocos de outro circuito de controle exemplificativo que pode ser incluído no sistema de multiplexação de potência da Figura 5 para controlar de forma adaptativa a intensidade de acionamento de um circuito de seleção de alimentação ativo e um circuito de controle de queda de diodo em um circuito de multiplexação de potência;

[0023] A Figura 8 é uma tabela lógica ilustrando uma operação exemplar de um circuito de controle na Figura 7 para controlar o circuito de controle de queda de diodo no circuito de multiplexação de potência na Figura 6 e controlar, de forma adaptativa, a intensidade de um circuito de seleção de alimentação selecionado ativado

acoplado ao trilho de energia de saída com base em uma tensão de saída no barramento de saída para considerar as variações de desempenho;

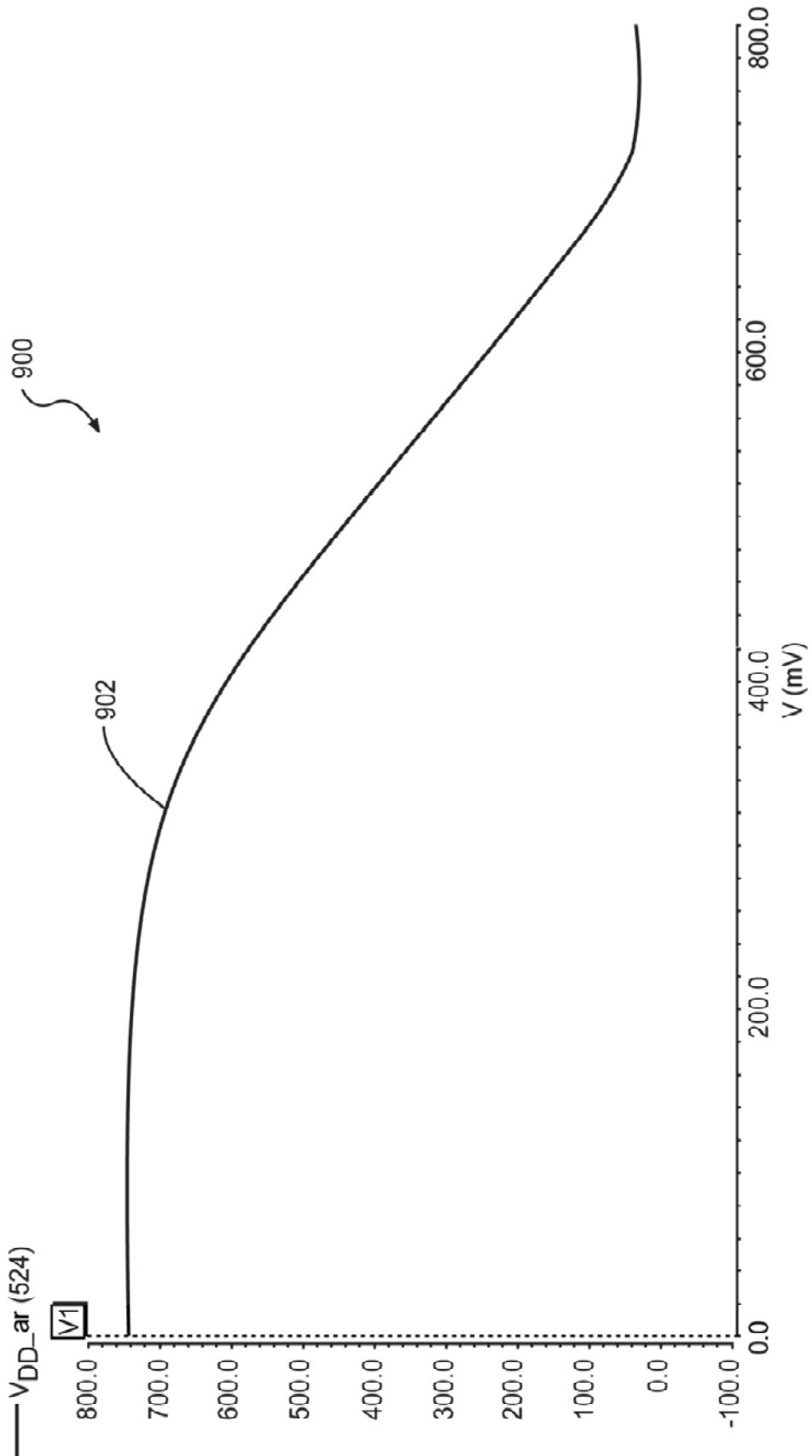

[0024] A Figura 9 é um gráfico que ilustra um gráfico exemplificativo de tensão de alimentação em um trilho de potência de alimentação transferido para o trilho de potência de saída no sistema de multiplexação de potência na Figura 5 como uma função do controle de intensidade do inversor do circuito de multiplexação de potência;

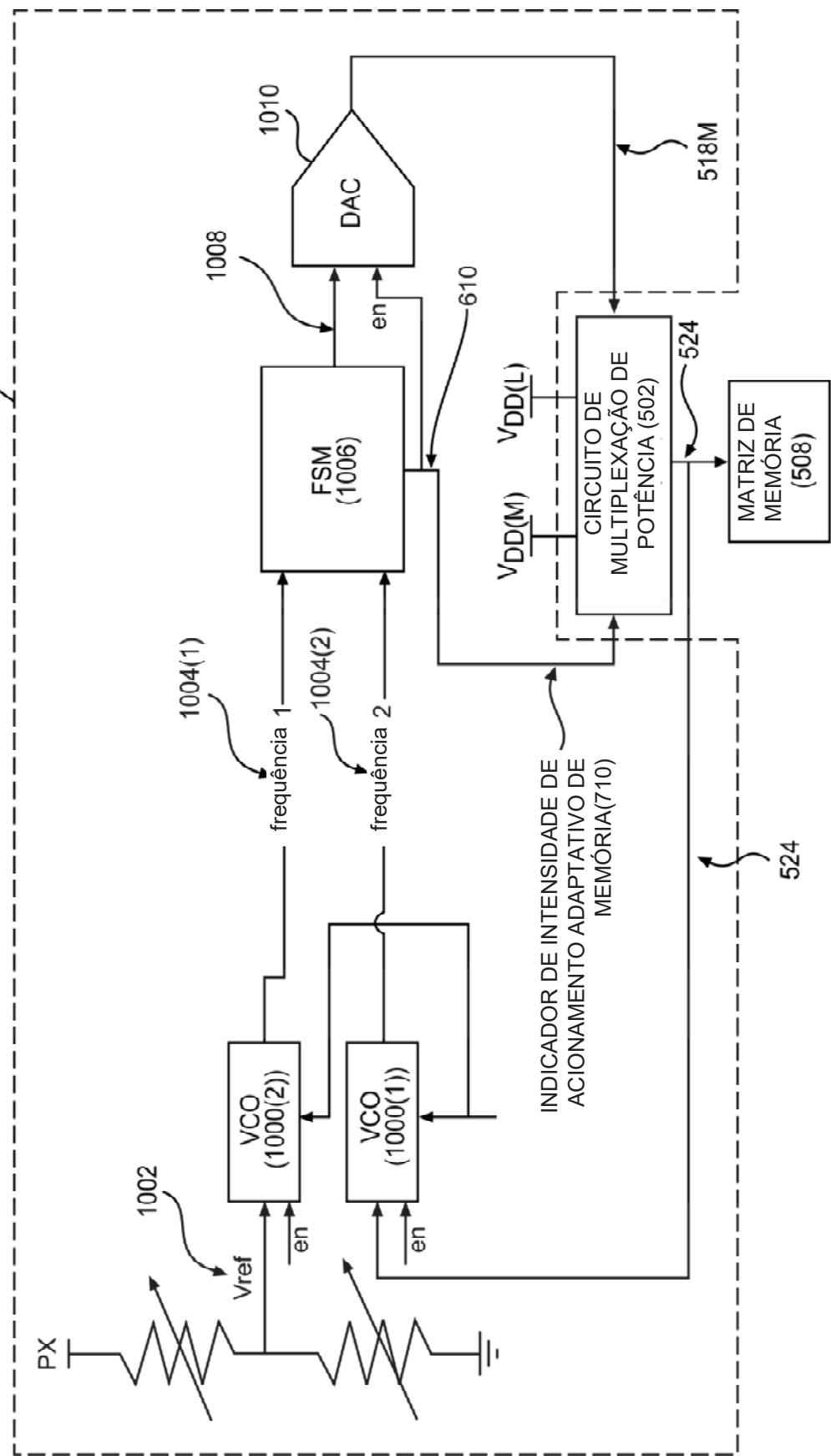

[0025] A Figura 10 é um diagrama de blocos de outro circuito de controle exemplificativo que pode ser incluído em um sistema de multiplexação de potência para controlar de forma adaptável a potência de multiplexação de uma pluralidade de barras de alimentação a um trilho de potência de saída para alimentar um circuito alimentado baseado em uma tensão de saída no trilho de potência de saída, incluindo, mas não se limitando a, circuitos de multiplexação de potência na Figura 2 e na Figura 5;

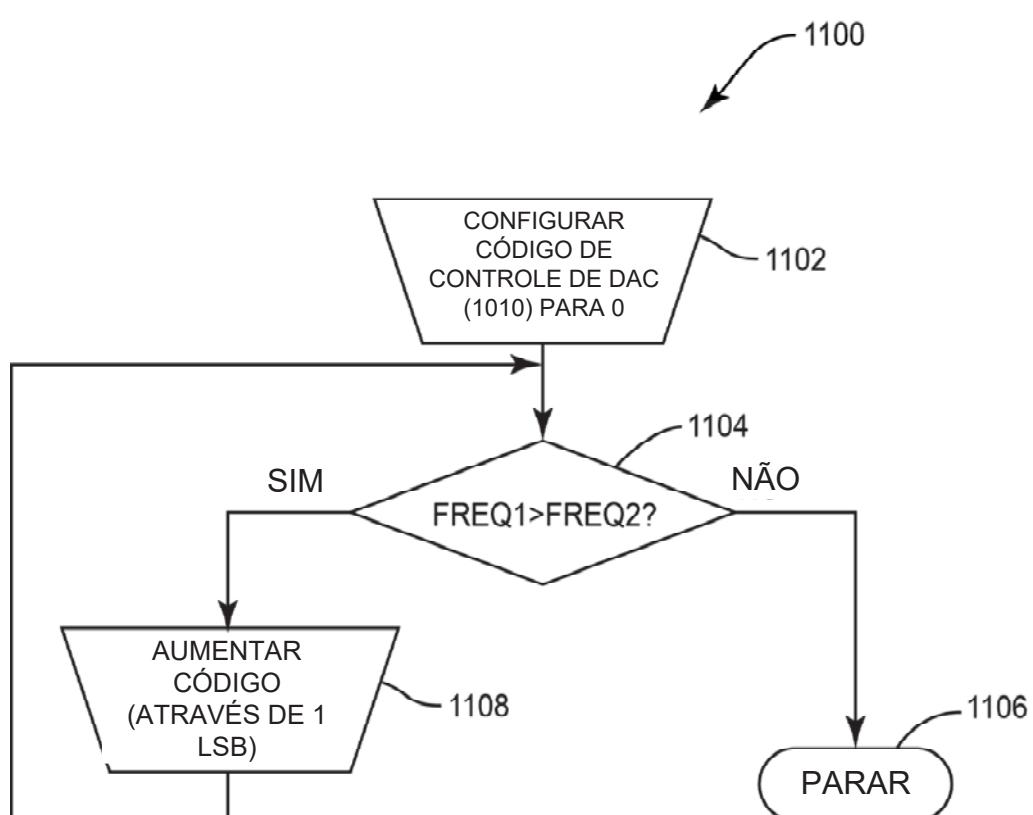

[0026] A Figura 11 é um fluxograma ilustrando um processo exemplificativo do circuito de controle na Figura 10 controlando, de forma adaptável, a intensidade de acionamento do circuito de seleção de alimentação ativo em um circuito de multiplexação de potência, incluindo mas não limitado aos circuitos de multiplexação de potência nas Figuras 2 e 5;

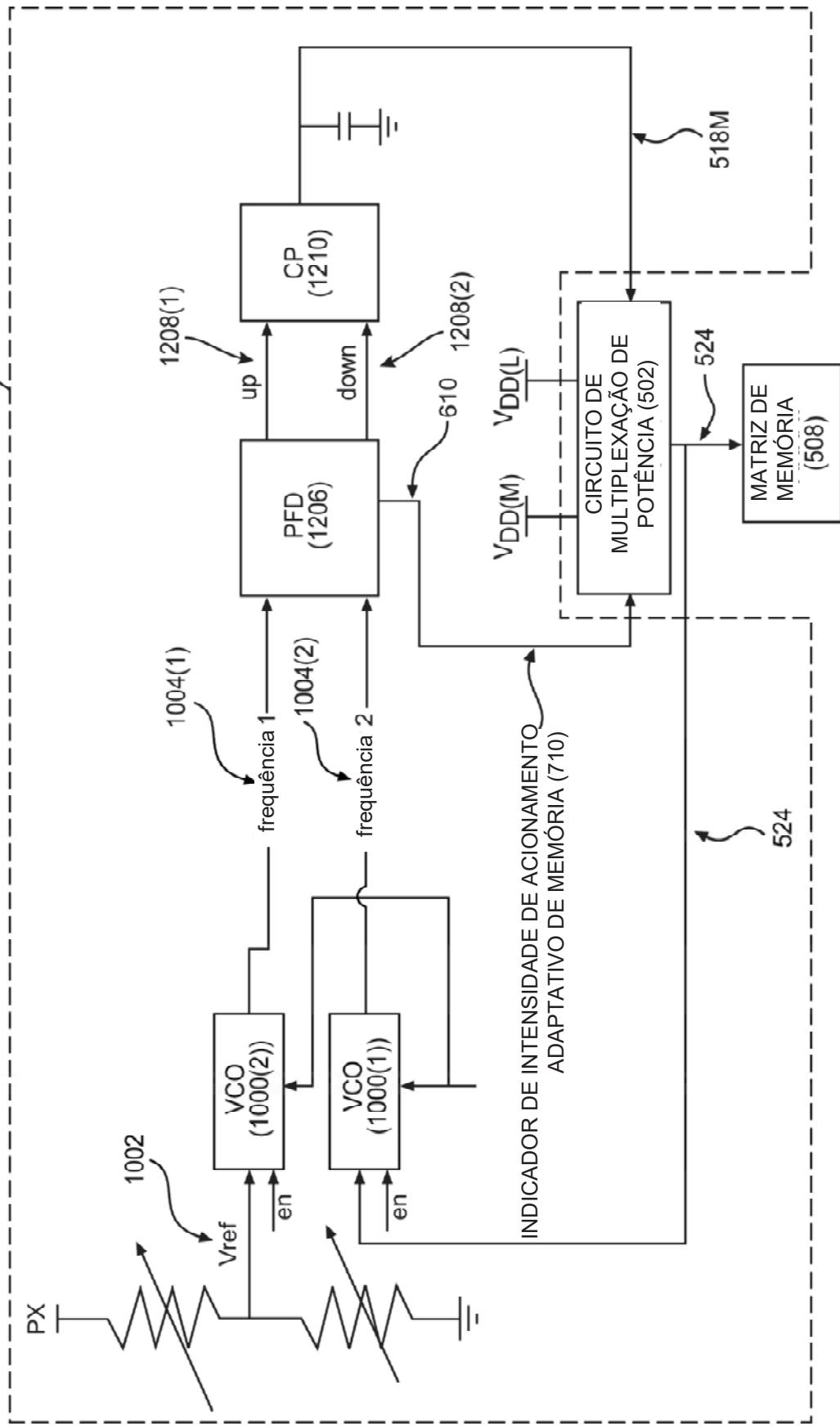

[0027] A Figura 12 é um diagrama de blocos de outro circuito de controle exemplificativo que pode ser incluído em um circuito de controle em um sistema de multiplexação de potência, incluindo mas não limitado aos circuitos de multiplexação de potência nas Figuras 2 e 5,

para controlar de forma adaptativa a intensidade de acionamento de um circuito ativo de seleção de alimentação no circuito de multiplexação de potência;

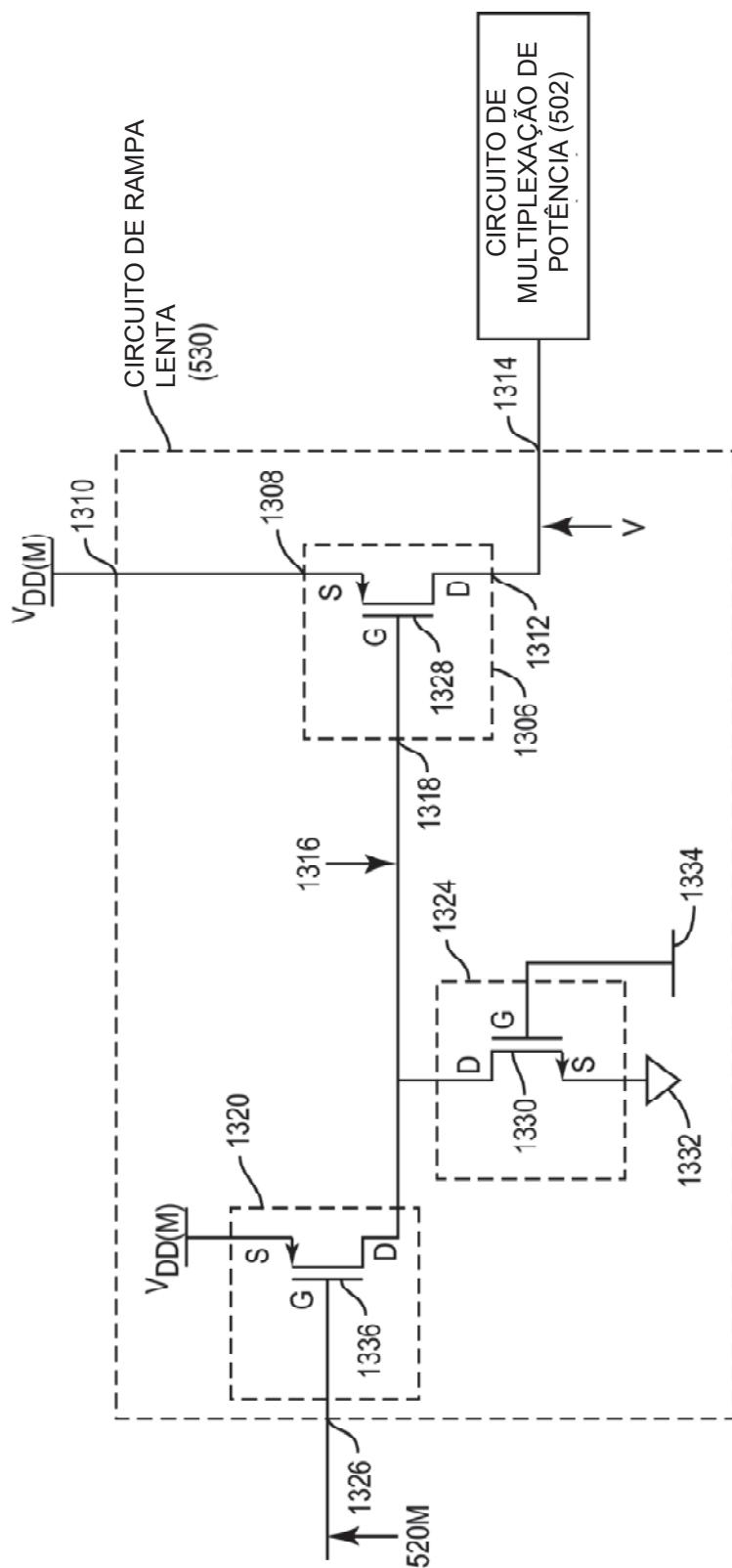

[0028] A Figura 13 é um diagrama de circuito de um circuito de controle de potência comutado exemplificativo que pode ser fornecido em um circuito de controle para fornecer gradualmente um sinal de tensão para reduzir ou evitar o ruído de alimentação relacionado com a corrente de precipitação; e

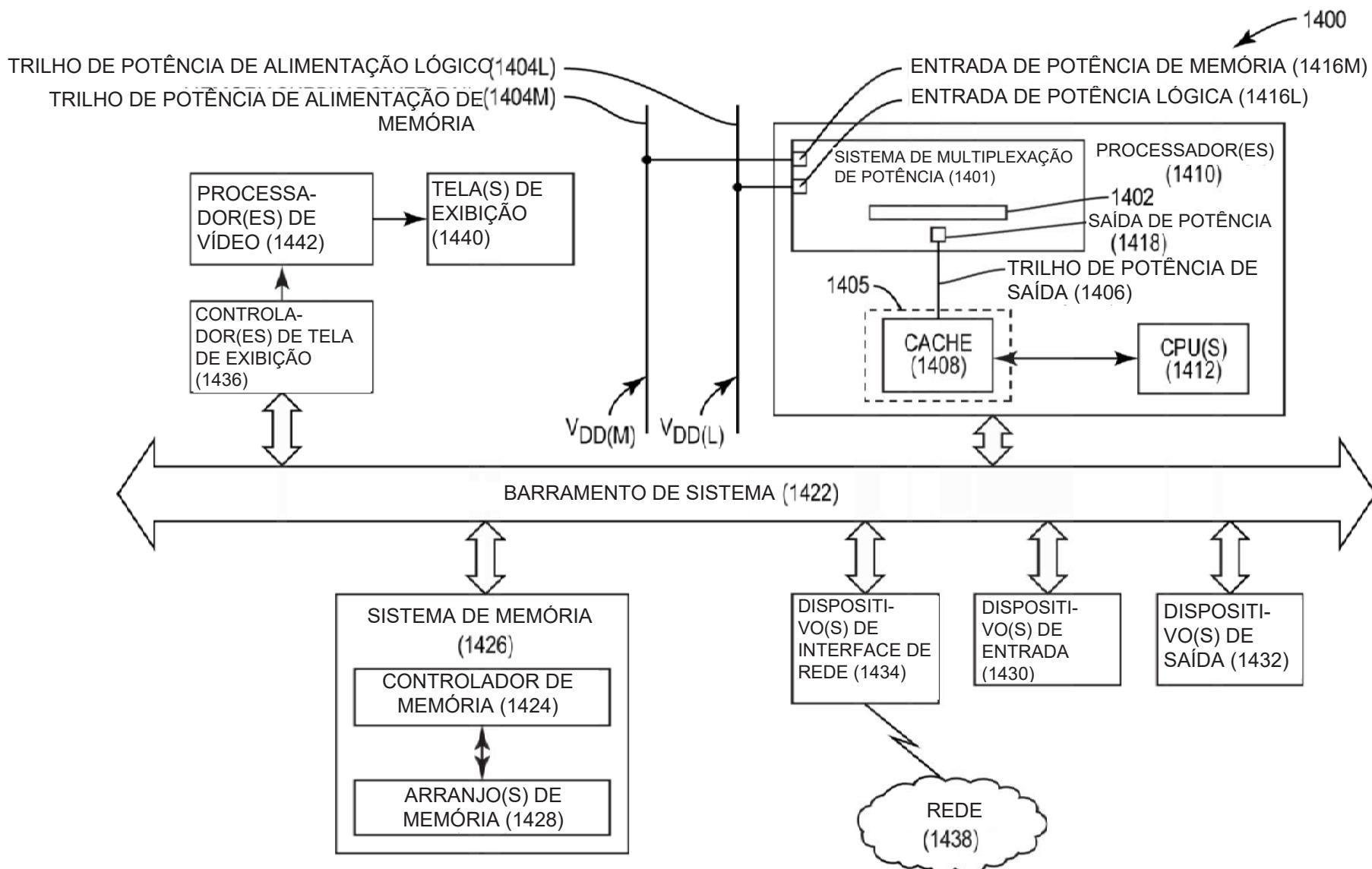

[0029] A Figura 14 é um diagrama de blocos de um sistema baseado em processador exemplificativo que inclui um sistema de multiplexação de potência que inclui um circuito de controle configurado para controlar de forma adaptativa a intensidade de um primeiro circuito de seleção de alimentação compreendendo um circuito de seleção de alimentação de memória e um segundo circuito de seleção de alimentação circuito de seleção de alimentação lógico para fornecer energia a partir de um trilho de potência de alimentação de memória associado e um trilho de potência de alimentação lógico a um conjunto de memória, com base em uma tensão de saída e de acordo com qualquer um dos aspectos revelados nesta invenção.

#### DESCRIÇÃO DETALHADA

[0030] Com referência agora às figuras do desenho, vários aspectos exemplares da presente divulgação são descritos. A palavra "exemplar" é usada nesta divulgação para significar "servir como exemplo, caso ou ilustração". Qualquer aspecto aqui descrito como "exemplar" não é

necessariamente para ser interpretado como preferido ou vantajoso em relação a outros aspectos.

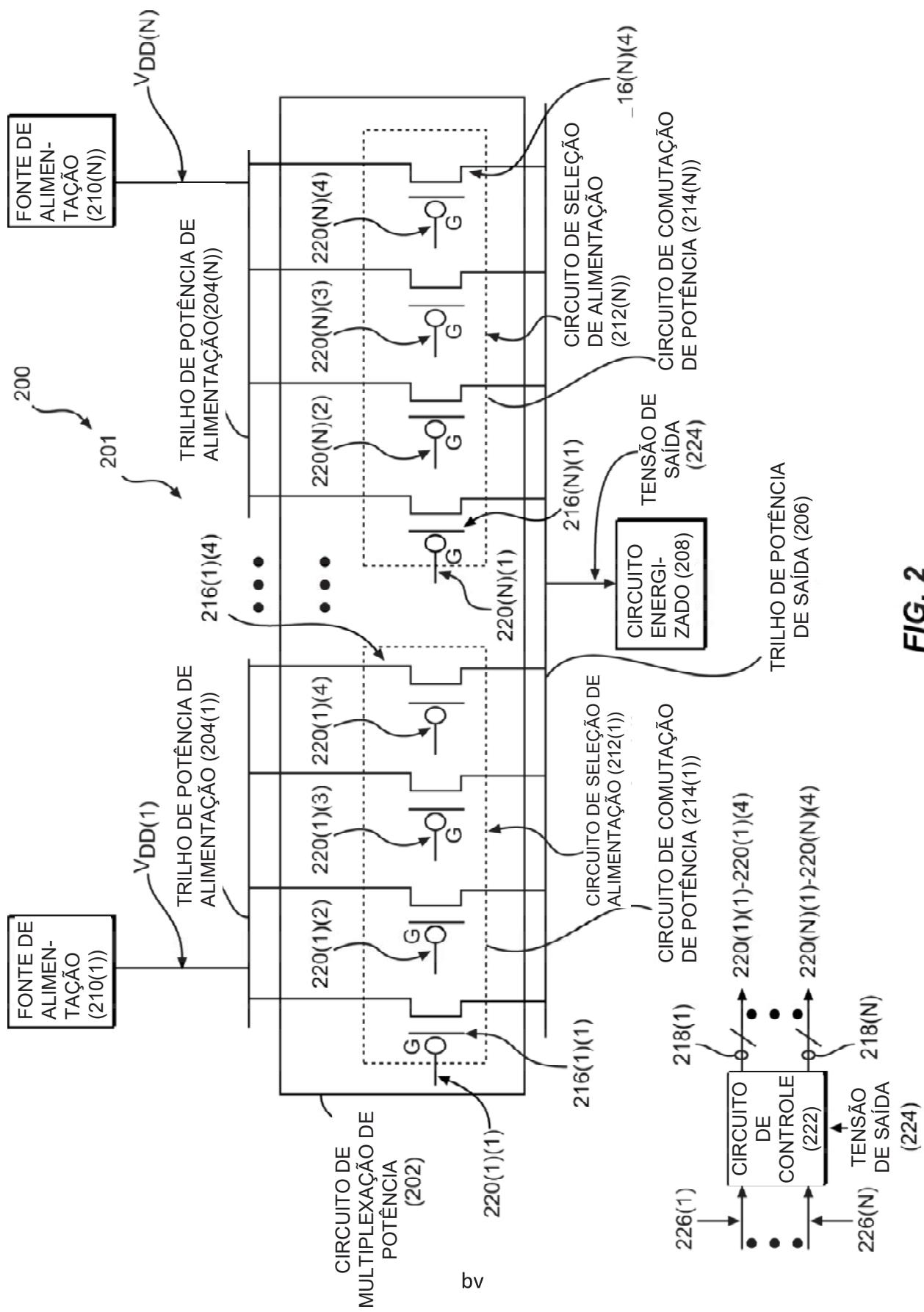

[0031] A Figura 2 é um diagrama de blocos de um sistema de multiplexação de potência exemplificativo 200 que é configurado para controlar de forma adaptativa a intensidade de acionamento de potência multiplexada de trilhos de potência de alimentação para um circuito energizado. Por exemplo, o sistema de multiplexação de potência 200 pode ser fornecido em um sistema em um chip (SoC) 201. O sistema de multiplexação de potência 200 inclui um circuito de multiplexação de potência 202. Como será discutido em mais detalhes abaixo, o circuito de multiplexação de potência 202 está configurado para selecionar um de uma pluralidade de trilhos de potência de alimentação 204 (1) a 204 (N) a ser acoplado a um trilho de potência de saída 206 para fornecer energia a um circuito energizado 208 acoplado ao trilho de potência de saída 206. Os trilhos de potência de alimentação 204 (1) a 204 (N) são acoplados a uma respectiva fonte de energia 210 (1) a 210 (N).

As fontes de energia 210 (1) a 210 (N) são configuradas para fornecer uma tensão respectiva  $V_{DD(1)}$  a  $V_{DD(N)}$  ao seu respectivo barramento de potência de alimentação 204 (1) a 204 (N). O circuito de multiplexação de potência 202 é configurado para acoplar uma tensão  $V_{DD(1)}$  a  $V_{DD(N)}$  de um trilho de potência de alimentação 204 (1) a 204 (N) ao trilho de alimentação de saída 206 para fornecer a tensão  $V_{DD(1)}$  a  $V_{DD(N)}$  para o circuito energizado 208 para operação.

[0032] Por exemplo, a primeira fonte de energia 210 (1) pode ser configurada para fornecer uma primeira

tensão  $V_{DD(1)}$  (por exemplo, 1 Volt (V)) que é uma voltagem maior do que uma segunda voltagem  $V_{DD(N)}$  (por exemplo, 0,6 V) fornecida pela fonte de energia 210 (N). Esta configuração de trilho de alimentação pode ser fornecida no sistema de multiplexação de potência 200, porque pode ser desejado acoplar o circuito de alimentação 208 a um trilho de alimentação que tenha uma tensão maior durante um modo de desempenho de operação mais alto e acoplar o circuito de alimentação 208 a outro trilho de potência de alimentação que tem uma tensão mais baixa durante um modo de desempenho inferior para conservar o consumo de energia, como um exemplo. Por exemplo, o circuito energizado (208) pode ser um circuito ou conjunto de memória que requer uma tensão de retenção mínima para reter os dados. O primeiro trilho de potência de alimentação 204 (1) pode ser configurado para fornecer a primeira tensão  $V_{DD(1)}$  capaz de exceder a tensão de retenção mínima para o circuito energizado 208. O segundo trilho de potência de alimentação 204 (N) pode ser acoplado a circuitos lógicos em um domínio lógico. Assim, se a segunda voltagem  $V_{DD(N)}$  for maior do que a voltagem de retenção mínima do circuito de potência 208, o sistema multiplexador de potência 200 pode comutar o acoplamento da segunda voltagem  $V_{DD(N)}$  para o trilho de potência de saída 206 para multiplexar a segunda voltagem  $V_{DD(N)}$  para o circuito alimentado 208 para operação. Isso pode ter o benefício de evitar ou reduzir a necessidade de fornecer capacitação de desacoplamento intencional no domínio lógico. Contudo, se a segunda voltagem  $V_{DD(N)}$  for inferior à tensão de retenção mínima do circuito energizado 208, o sistema de multiplexação de potência 200 pode comutar o acoplamento da primeira voltagem  $V_{DD(1)}$  para a

rampa de potência de saída 206 para fornecer a primeiro tensão  $V_{DD(1)}$  para o circuito alimentado 208 para operação.

[0033] Com referência continua à Figura 2, para ligar seletivamente um trilho de potência de alimentação 204 (1) a 204 (N) ao trilho de potência de saída 206 para fornecer uma tensão respectiva  $V_{DD(1)}$  a  $V_{DD(N)}$  ao circuito de potência 208, o circuito de multiplexação de potência 202 inclui uma pluralidade de circuitos de seleção de alimentação 212 (1) a 212 (N). Os circuitos de seleção de alimentação 212 (1) a 212 (N) são acoplados entre um trilho de potência de alimentação respectivo 204 (1) a 204 (N) e o trilho de potência de saída 206. O sistema de multiplexação de potência 200 é configurado para ativar um circuito de seleção de alimentação selecionado 212 (1) a 212 (N) para acoplar um trilho de potência de alimentação 204 (1) a 204 (N) ao trilho de alimentação de saída 206 para alimentar o circuito energizado 208 na respectiva voltagem  $V_{DD(1)}$  a  $V_{DD(N)}$ .

[0034] Para selecionar um trilho de potência de alimentação 204 (1) a 204 (N) a ser acoplado ao trilho de potência de saída 206, os circuitos de seleção de alimentação 212 (1) a 212 (N) neste exemplo incluem circuitos de comutação de potência respectivos 214(1) a 214 (N). A intensidade de acionamento de um circuito de chave de potência ativado 214 (1) a 214 (N) afeta sua intensidade de acionar a tensão  $V_{DD(1)}$  a  $V_{DD(N)}$  no trilho de potência de saída 206. A intensidade de acionamento de um circuito comutador do tipo liga/desliga 214 (1) a 214 (N) ajusta sua impedância de saída, que controla a queda de intensidade à corrente de comutação (IR), resultando na tensão de saída desejada. Por exemplo, à medida que a intensidade de acionamento de um

circuito comutador de energia 214 (1) a 214 (N) é aumentada, a impedância de saída do circuito de comutação de energia 214 (1) a 214 (N) é diminuída, reduzindo assim a queda IR e aumentando a voltagem de saída. Se a potência de acionamento de um circuito comutador de energia 214 (1) a 214 (N) for diminuída, a impedância de saída do circuito de comutação de energia 214 (1) a 214 (N) é aumentada, aumentando assim a queda da IR e diminuindo a voltagem de saída. As variações do PVT também podem afetar a intensidade da unidade. A intensidade de acionamento pode ser aumentada para compensar a redução da intensidade de acionamento devido às variações do PVT, por exemplo. Entretanto, aumentar a intensidade da unidade aumenta o poder de vazamento. Assim, o sistema de multiplexação de potência 200 proporciona a intensidade de controlar seletivamente a intensidade de acionamento dos circuitos de seleção de alimentação 212 (1) a 212 (N), que podem ser usados para compensar as variações de PVT. A margem de intensidade de acionamento pode ser reduzida como resultado, reduzindo assim a potência de vazamento enquanto ainda alcança a intensidade de acionamento desejada no trilho de potência de saída 206.

[0035] Assim, neste exemplo, para proporcionar a intensidade de controlar a intensidade de acionamento dos circuitos de seleção de alimentação ativados 212 (1) a 212 (N), cada um dos circuitos de chave de potência 214 (1) a 214 (N) inclui quatro (4) transistores de semicondutores de óxido metálico (MOS) (PMOS) do tipo P ligados em paralelo 216 (1) (1) a 216 (1) (4) e 216 (N) (1) a 216 (N) (4) (Transistores MOS (NMOS) do tipo N também podem ser empregados) acoplados entre um trilho de potência de

alimentação respectivo 204 (1) a 204 (N) e o trilho de alimentação de saída 206. Cada um dos transistores PMOS conectados em paralelo 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) possui uma intensidade de acionamento associada para acionar a respectiva tensão VDD (1) a VDD (N) no trilho de potência de saída 206. Assim, para controlar a intensidade geral do acionamento do circuito de seleção de alimentação 212 (1) a 212 (N), os respectivos transistores PMOS conectados em paralelo 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) são controlados individualmente para serem ativados ou desativados para contribuir para a condução da respectiva tensão VDD (1) a VDD (N) no trilho de potência de saída 206. Neste exemplo, cada um dos transistores PMOS 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) é configurado para receber um indicador de intensidade de acionamento associado 218 (1) a 218 (N) na forma dos respectivos sinais de seleção do comutador de energia 220 (1)(1) a 220 (1)(4) e 220 (N)(1) a 220 (N)(4). Assim, os indicadores de potência de acionamento 218(1) a 218 (N) podem ser considerados em um exemplo como palavras de código, cada um com sinais individuais ou bits indicando um estado de habilitação dos respectivos sinais de seleção de comutador de potência 220 (1)(1) a 220 (1)(4) e 220 (N)(1) e 220 (N)(4) formando as palavras de código para controlar o respectivo número de transistores de PMOS conectados em paralelo 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) que são ativados.

[0036] Neste exemplo, os sinais de seleção do comutador de alimentação 220 (1)(1) a 220 (1)(4) e 220 (N)(1) a 220 (N)(4) são acoplados às portas G dos respectivos transistores PMOS 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216

(N) (4). Assim, o estado dos sinais de seleção do comutador de alimentação 220 (1) (1) a 220 (1) (4) e 220 (N) (1) a 220 (N) (4) controla se seus respectivos transistores PMOS 216 (1) (1) a 216 (1) (4) e 216 (N) (1) a 216 (N) (4) são seletivamente ativados, e assim contribuem para acionar a respectiva tensão  $V_{DD(1)}$  a  $V_{DD(N)}$  no trilho de potência de saída 206. Se o estado dos sinais de seleção do interruptor de alimentação 220 (1) (1) a 220 (1) (4) e 220 (N) (1) a 220 (N) (4) é um estado de habilitação de seleção do comutador deste exemplo é um nível baixo lógico ('0') para ativar (ou seja, ligar) os transistores PMOS 216 (1) (1) a 216 (1) (4) e 216 (N) (1) a 216 (N) (4), os respectivos transistores PMOS 216 (1) (1) a 216 (1) (4) e 216 (N) (1) a 216 (N) (4) serão ativados para fornecer um caminho de fluxo de corrente entre o respectivo trilho de potência de alimentação 204 (1) a 204 (N) e o trilho de potência de saída 206. Se o estado dos sinais de seleção do interruptor de alimentação 220 (1) (1) a 220 (1) (4) e 220 (N) (1) a 220 (N) (4) é um estado de desativação da seleção do comutador de alimentação, os respectivos Os transistores de PMOS 216 (1) (1) a 216 (1) (4) e 216 (N) (1) a 216 (N) (4) serão desativados para não fornecer um caminho de fluxo de corrente entre o respectivo trilho de potência de alimentação 204 (1) a 204 (N) e o trilho de potência de saída 206.

[0037] Neste exemplo, para proporcionar o controle adaptativo da intensidade de acionamento de um circuito de seleção de alimentação ativado 212 (1) a 212 (N) acoplando um trilho de potência de alimentação 204 (1) a 204 (N) ao trilho de potência de saída 206, um o circuito de controle 222 é fornecido no sistema de multiplexação de

potência 200. O circuito de controle 222 é configurado para gerar os indicadores de intensidade de acionamento 218 (1) a 218 (N), que neste exemplo são os sinais de seleção de comutador de potência individuais, 220 (1)(1) a 220 (1)(4) e 220 (N)(1) a 220 (N)(4). Neste exemplo, os transistores PMOS 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) também atuam como head switches de potência, de modo que o circuito de controle 222 controla os estados de ativação e desativação de seleção de comutador de energia de cada um dos indicadores de potência de acionamento 218 (1) a 218 (N) para controlar qual o circuito de seleção de alimentação 212 (1) a 212 (N) é acoplado ao trilho de potência de saída 206, assim como os transistores PMOS individuais 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) são ativados e desativados com circuitos de seleção de alimentação ativados 212 (1) a 212 (N) para controlar a intensidade de acionamento. A este respeito, os transistores PMOS individuais 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) nos respectivos circuitos comutadores de potência 214 (1) a 214 (N) recebe os respectivos sinais de seleção de comutador de alimentação 220 (1)(1) a 220 (1)(4) e 220 (N)(1) a 220 (N)(4) para indicar a intensidade do inversor de alimentação circuito de seleção 212(1) a 212(N). Os transistores PMOS ativados 216 (1)(1) a 216 (1)(4) e 216 (N)(1) a 216 (N)(4) contribuem para a condução da tensão  $V_{DD(1)}$  a  $V_{DD(N)}$  para o trilho de potência de saída 206.

[0038] O circuito de controle 222 está configurado para controlar, de forma adaptativa, a intensidade de acionamento do circuito de seleção de alimentação ativado 212(1) a 212(N) com base no desempenho do sistema de multiplexação de potência 200. Desta maneira,

a intensidade de acionamento do circuito de seleção de alimentação ativado 212 (1) a 212 (N) pode ser ajustada durante a operação para considerar variações operacionais e/ou de PVT. Assim, em vez de proporcionar uma intensidade de acionamento fixa que pode desperdiçar margem de intensidade de acionamento necessária para atingir o desempenho desejado do sistema de multiplexação de potência 200, a intensidade de ajustar de forma adaptável a margem de intensidade de acionamento dos circuitos de seleção de alimentação ativados 212 (1) a 212 (N) permite que a margem de intensidade da unidade seja reduzida ao mesmo tempo que atinge o desempenho desejado.

[0039] A este respeito, com referência continua à Figura 2, o circuito de controle 222 está configurado para monitorar uma tensão de saída 224 do trilho de potência de saída 206. Em resposta a um indicador de seleção de trilho de potência de alimentação 226 (1) a 226 (N) indicando qual circuito de seleção de alimentação 212 (1) a 212 (N) deve ser ativado para acoplar o trilho de potência de alimentação associado 204 (1) a 204 (N) ao trilho de potência de saída 206, o circuito de controle 222 compara um nível de tensão de saída 224 no trilho de potência de saída 206 com um primeiro nível de tensão de saída predefinido associado ao circuito de seleção de alimentação 212 (1) a 212 (N) indicado conforme ativado com base no indicador de seleção do barramento de potência de alimentação 226 (1) a 226 (N). O circuito de controle 222 está configurado para gerar seletivamente os indicadores de intensidade de acionamento 218 (1) a 218 (N) com base na comparação do nível de tensão da tensão de saída 224 no trilho de potência de saída 206

com o nível de tensão de saída predefinido associado ao circuito de seleção de alimentação ativado 212 (1) a 212 (N). Desta forma, o circuito de controle 222 pode ser configurado para monitorar continuamente a tensão de saída 224 no trilho de potência de saída 206 para ajustar a intensidade de condução do circuito de seleção de alimentação ativado 212 (1) a 212 (N) com base nas variações de desempenho do sistema de multiplexação de potência 200 observado com base na tensão de saída 224.

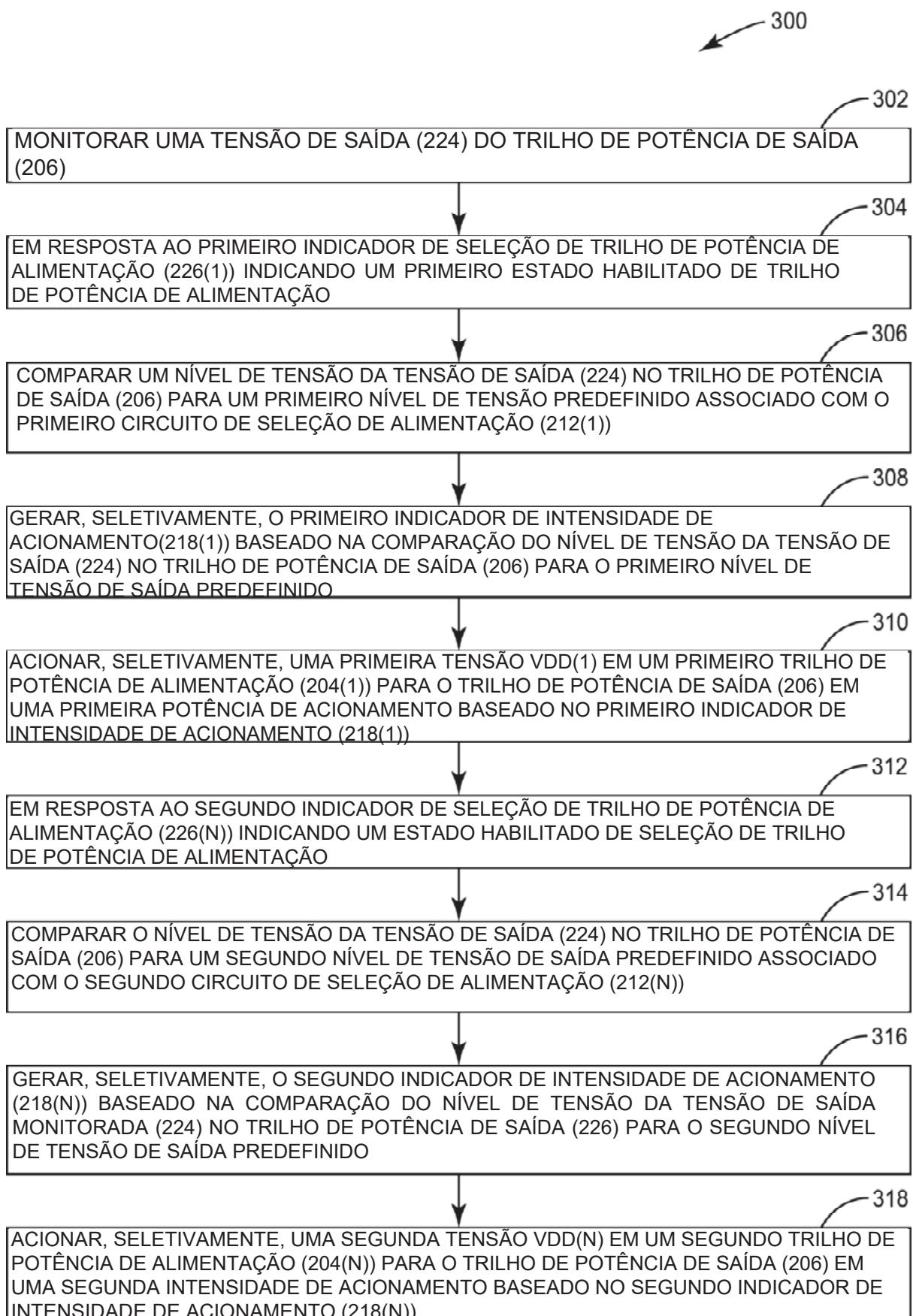

[0040] A Figura 3 é um fluxograma que ilustra um processo exemplificativo 300 do circuito de controle 222 na Figura 2 controlando de forma adaptável a intensidade de acionamento de um circuito de seleção de alimentação ativo 212 (1) a 212 (N) no circuito de multiplexação de potência 202, com base em uma tensão de saída 224 no trilho de potência de saída 206 para levar em conta as variações de desempenho. O processo 300 na Figura 3 será descrito em relação ao circuito de multiplexação de energia 202 incluindo dois (2) circuitos de seleção de alimentação 212(1) e 212 (N). No entanto, deve ser entendido que o processo 300 na Figura 3 é também aplicável para o circuito de multiplexação de potência 202 incluindo mais de dois (2) circuitos de seleção de alimentação 212 (1) a 212 (N).

[0041] Com referência à Figura 3, o circuito de controle 222 monitora a tensão de saída 224 do trilho de potência de saída 206 (bloco 302). Em resposta ao primeiro indicador de seleção de trilho de potência de alimentação 226 (1) indicando um primeiro estado de ativação de seleção de trilho de alimentação (bloco 304), o circuito de controle 222 compara um nível de tensão de saída 224 no trilho de

potência de saída 206 a um primeiro nível de tensão de saída predefinido associado ao primeiro circuito de seleção de alimentação 212 (1) (bloco 306). O circuito de controle 222 gera então seletivamente o primeiro indicador de intensidade de acionamento 218 (1) com base na comparação do nível de tensão de saída 224 no trilho de potência de saída 206 com o primeiro nível de tensão de saída predefinido (bloco 308). Em resposta, o circuito de multiplexação de potência 202 aciona seletivamente a primeira tensão VDD (1) no primeiro trilho de potência de alimentação 204 (1) para o trilho de potência de saída 206 em uma primeira intensidade de acionamento baseada no primeiro indicador de intensidade de acionamento 218 (1) (bloco 310). Contudo, em resposta ao segundo indicador de seleção de trilho de potência de alimentação 226 (N) indicando um segundo estado de ativação de seleção de trilho de alimentação (bloco 312), o circuito de controle 222 compara o nível de tensão da tensão de saída 224 no trilho de potência de saída 206 a um segundo nível de tensão de saída predefinido associado ao segundo circuito de seleção de alimentação 212 (N) (bloco 314).

O circuito de controle 222 gera seletivamente o segundo indicador de intensidade de acionamento 218 (N) com base na comparação do nível de tensão da tensão de saída 224 no trilho de potência de saída 206 com o segundo nível de tensão de saída predefinido (bloco 316). Em resposta, o circuito de multiplexação de energia 202 aciona seletivamente a segunda tensão VDD (N) no segundo trilho de potência de alimentação 204 (N) para o trilho de potência de saída 206 em uma segunda intensidade de acionamento baseada

no segundo indicador de intensidade de acionamento 218 (N) (bloco 318).

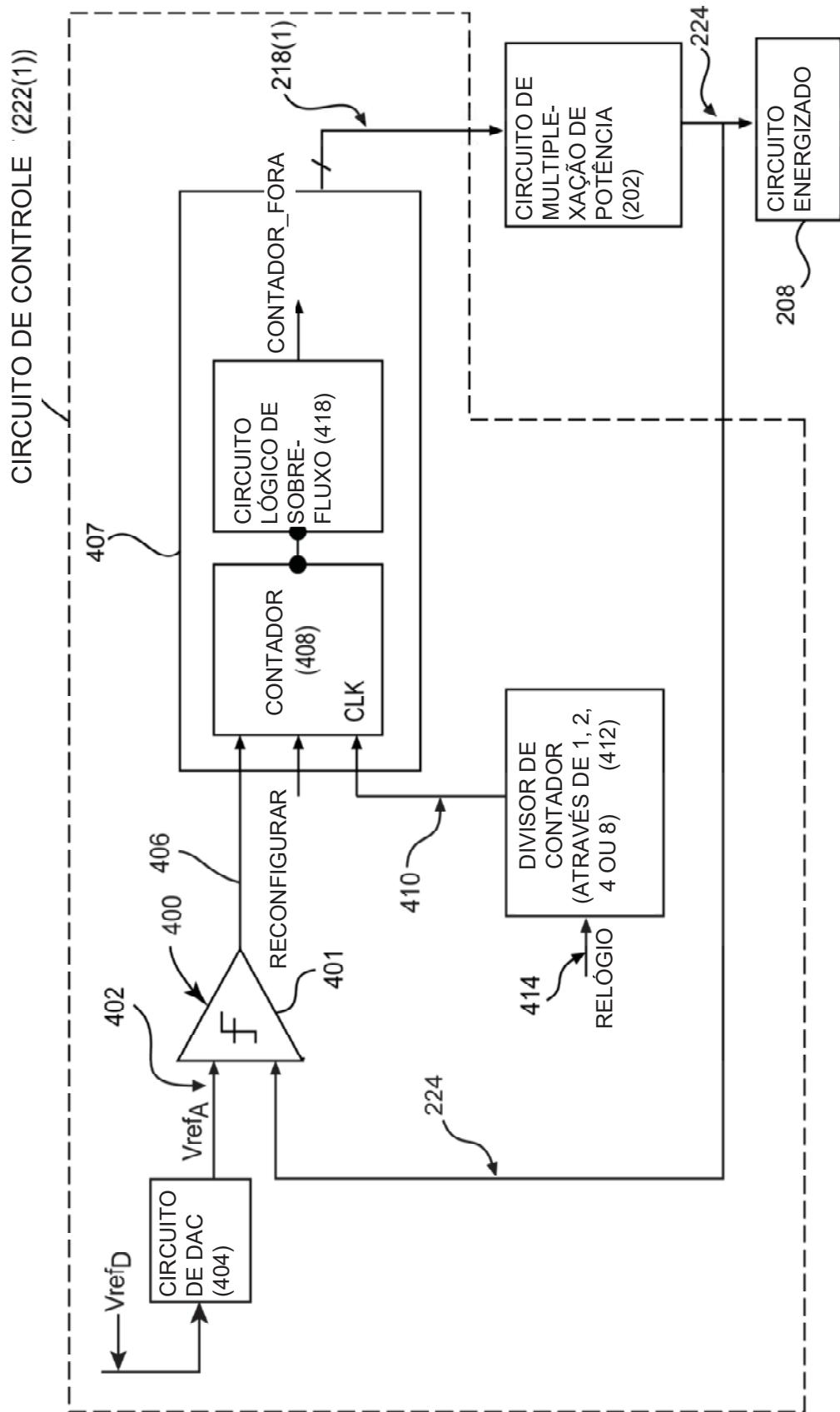

[0042] Diferentes circuitos de controle 222 podem ser fornecidos no sistema de multiplexação de potência 200 na Figura 2 para controlar de forma adaptativa a intensidade de acionamento da tensão  $V_{DD(1)}$  a  $V_{DD(N)}$  acionada no trilho de potência de saída 206. Neste sentido, a Figura 4A é um diagrama de blocos de um circuito de controle exemplificativo 222 (1) que pode ser fornecido como o circuito de controle 222 no sistema de multiplexação de potência 200 na Figura 2, por exemplo, para controlar de forma adaptativa a intensidade de acionamento de um sistema ativo do circuito de seleção de alimentação 212 (1) a 212 (N) com base na tensão de saída 224 no trilho de alimentação de saída 206 para ter em conta variações de desempenho. O circuito de controle 222 (1) na Figura 4A é mostrado como controlando apenas um (1) circuito de seleção de alimentação 212 (1) a 212 (N), e assim circuitos múltiplos de controle 222 (1) seriam fornecidos para controlar a intensidade de acionamento de cada circuito de seleção de alimentação 212 (1) a 212 (N). Contudo, note-se que o circuito de controle 222 (1) pode ser adaptado para controlar a intensidade de acionamento de cada um dos circuitos de seleção de alimentação 212 (1) a 212 (N). O circuito de controle 222 (1) ilustrado na Figura 4 é para controlar um (1) circuito de seleção de alimentação 212 (1) no circuito de multiplexação de energia 202.

[0043] A este respeito, com referência à Figura 4A, a tensão de saída 224 é acoplada a um circuito comparador 400 proporcionado na forma de um comparador analógico 401

neste exemplo. O circuito comparador 400 também recebe, como entrada, uma tensão de referência de saída VrefA402 para o circuito de seleção de alimentação 212 (1). A tensão de saída de referência 402 pode ter sido armazenada como uma voltagem de saída de referência digital V<sub>ref</sub> e convertida em um sinal analógico como a voltagem de saída de referência V<sub>refA</sub> por um circuito conversor digital/analógico (DAC) 404. O circuito comparador 400 é configurado para gerar um sinal de saída de comparação 406 indicando uma comparação maior ou menor do que no nível de tensão entre a tensão de saída 224 e a tensão de saída de referência 402 para determinar o desempenho do circuito de multiplexação de potência 202. O sinal de saída de comparação 406 é fornecido a um circuito de contador 407 que inclui um contador 408 configurado para aumentar ou diminuir um valor de contagem quando a tensão de saída 224 cai abaixo ou fica acima da tensão de saída de referência 402, respectivamente (ou vice-versa). O contador 408 pode ser cronometrado por um sinal de relógio 410 que é dividido por um divisor de relógio 412 a partir de um sinal de relógio principal 414 de tal modo que o contador 408 é ativado para cada ciclo de relógio do sinal de relógio 410. Um circuito lógico de transbordamento 418 é fornecido para lidar com as condições de transbordo do contador 408. O contador 408 produz o valor de contagem na forma do indicador de intensidade de acionamento 218 (1) a ser fornecido ao circuito de multiplexação de potência 202 (e o circuito de seleção de alimentação ativado 212 (1)) para controlar a intensidade de acionamento do circuito de seleção de alimentação 212 (1).

[0044] Os circuitos de controle 222 (1) na Figura 4A podem assegurar que a voltagem no trilho de potência de saída 206 não desce abaixo de uma tensão limite mínima projetada. O contador 408 pode contar para cima ou para baixo para levar em conta mudanças nas condições ambientais, tais como desvios de temperatura, mudanças na carga de trabalho, etc.

[0045] Alternativamente, como mostrado na Figura 4B, um circuito de controle compartilhado 222M pode ser fornecido que é multiplexado para ser capaz de controlar qualquer um dos circuitos de seleção de alimentação 212 (1) a 212 (N). Este circuito de controle 222M está configurado para emitir quaisquer sinais de seleção do comutador de corrente 220 (1) (1) a 220 (1) (4) e 220 (N) (1) a 220 (N) (4) para um circuito de seleção de alimentação selecionado 212(1) a 212(N). O circuito de controle 222M na Figura 4B possui componentes comuns com o circuito de controle 222(1) na Figura 4A, que são mostrados com números de elementos comuns. Como mostrado na Figura 4B, o circuito comparador 400 recebe, como entrada, a tensão de saída de referência VrefA 402 para um circuito de seleção de alimentação selecionado 212 (1) a 212 (N). Um sinal de seleção 416 introduzido em um circuito de multiplexação 418 controla a tensão de saída de referência digital V<sub>refo</sub>(1) a V<sub>refo</sub>(N) para um circuito de seleção de alimentação 212(1) a 212(N) passado para o circuito DAC 404 como referência de tensão de saída V<sub>refA</sub> 402. Um circuito de demultiplexação 420 é provido para controlar qual circuito de seleção de alimentação 212 (1) a 212 (N) no circuito de multiplexação de potência 202, o indicador de intensidade de acionamento 218 é provido para controlar a intensidade de

acionamento do circuito de seleção de alimentação selecionado 212 (1) a 212 (N).

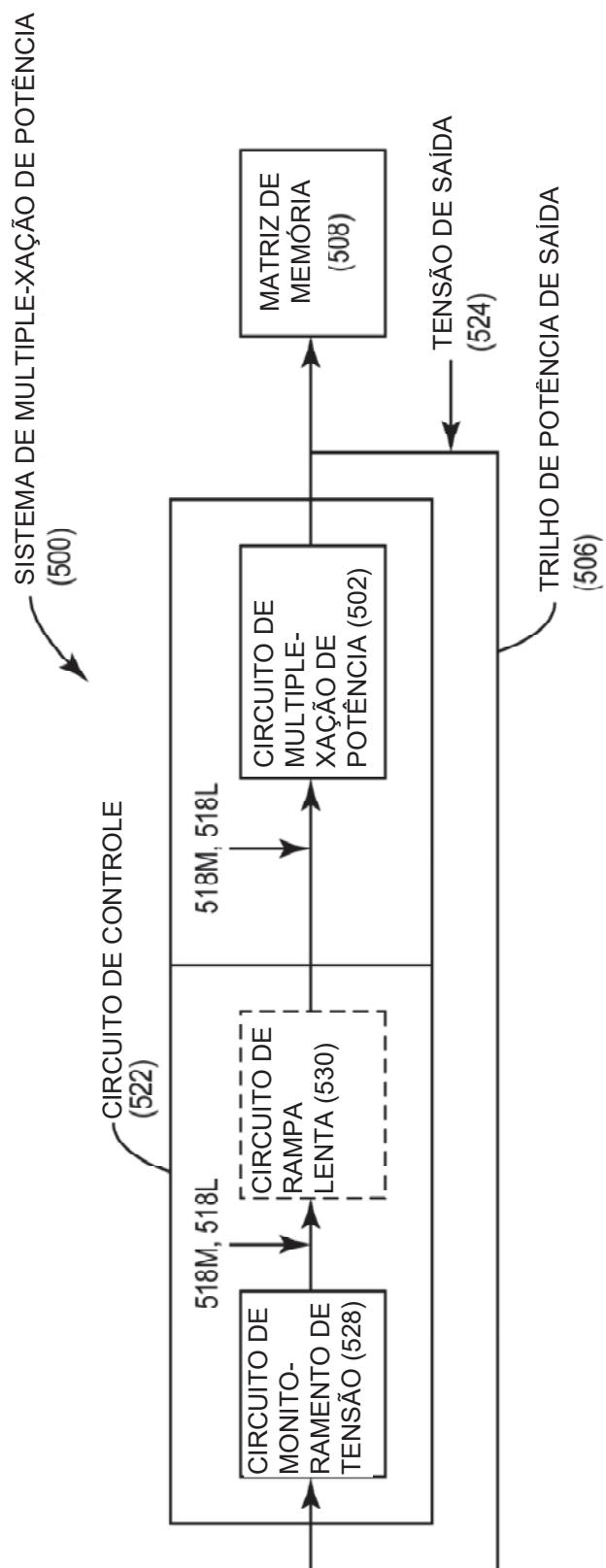

[0046] Outros tipos de circuitos de controle podem ser fornecidos em um sistema de multiplexação de potência, como o sistema de multiplexação de potência 200 na Figura 2, para controlar de forma adaptativa a intensidade de acionamento de uma tensão multiplexada acionada em um barramento de saída de energia. Por exemplo, a Figura 5 é um diagrama de blocos de outro sistema de multiplexação de potência exemplificativo 500 que é configurado para controlar de forma adaptativa a intensidade de acionamento de energia multiplexada de uma pluralidade de comutadores de alimentação para um comutador de potência de saída para alimentar um circuito energizado baseado em uma tensão de saída no trilho de energia de saída que pode levar em conta as variações de desempenho. Como aqui mostrado, um circuito de controle 522 é proporcionado para controlar de forma adaptativa a intensidade do acionamento de uma tensão multiplexada acionada por um circuito de multiplexação de potência 502 como uma voltagem de saída 524 em um barramento de saída 506 para alimentar um circuito energizado, o qual é mostrado como uma matriz de memória 508 neste exemplo. O circuito de controle 522, neste exemplo, inclui um circuito de monitorização de tensão 528 configurado para monitorar a tensão de saída 524 para ajustar a intensidade de acionamento da tensão de saída 524 multiplexada no trilho de potência de saída 506 para levar em conta as variações de desempenho monitoradas. O circuito de controle 522 também inclui um circuito de rampa lenta opcional 530 que é configurado para aumentar gradualmente os indicadores de potência da unidade

de memória e lógica 518M, 518L de uma maneira controlada, que gradualmente acelera circuitos de comutação de energia multiplexados para aumentar a voltagem multiplexada no trilho de alimentação de saída 506. Isto pode reduzir ou evitar o ruído de alimentação relacionado com corrente de pico no sistema de multiplexação de potência 500, evitando ou mitigando a perda de desempenho da matriz de memória 508 devido à comutação de barramentos de energia.

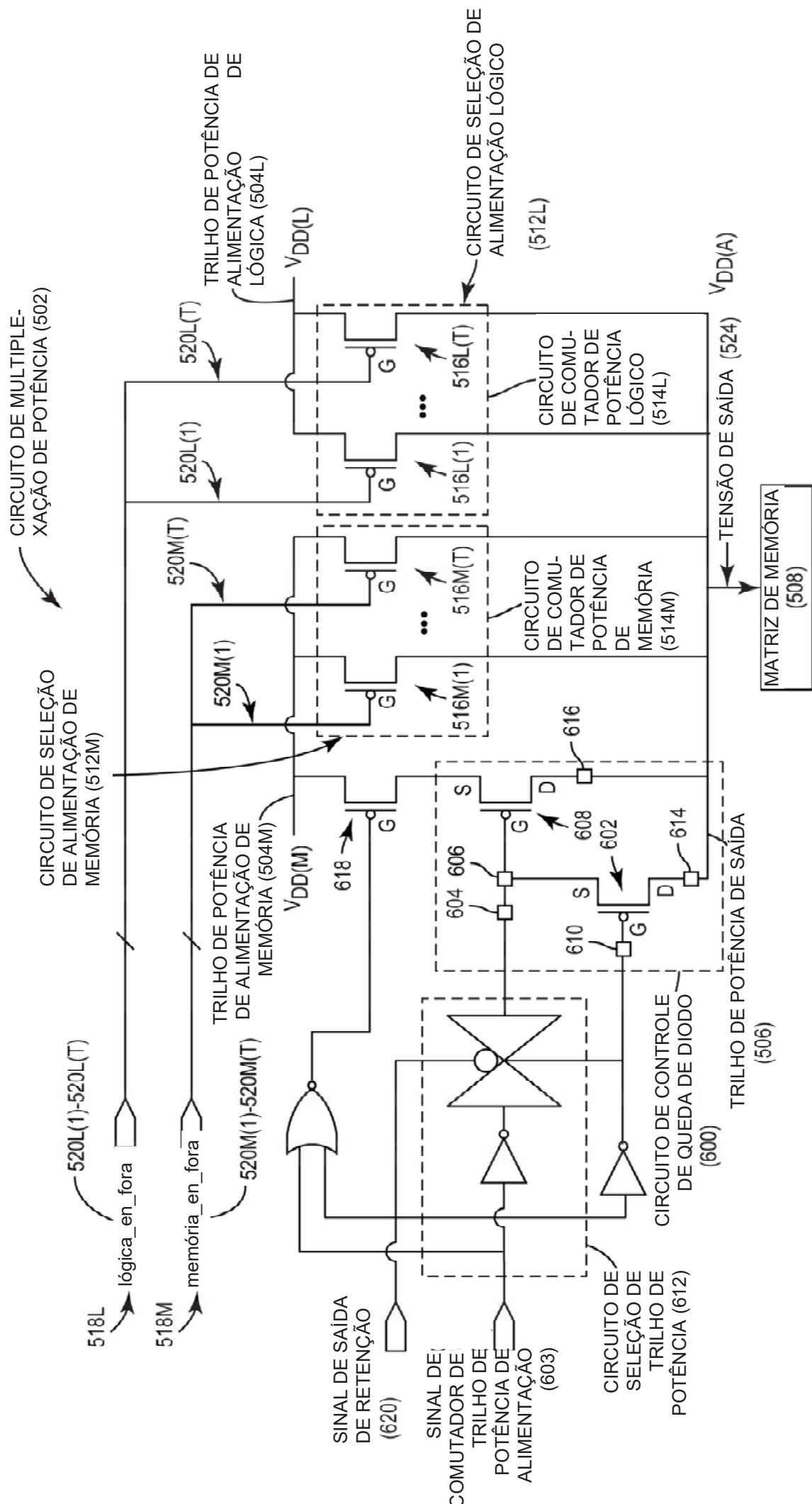

[0047] A Figura 6 é um diagrama de blocos do circuito exemplar de multiplexação de energia 502 no sistema de multiplexação de potência 500 da Figura 5. O circuito de multiplexação de energia 502 é configurado para multiplexar o acoplamento de um de um trilho de potência de alimentação lógica 504L e um trilho de alimentação de alimentação de memória 504M ao trilho de alimentação de saída 506 para fornecer energia ao arranjo de memória 508 acoplado ao trilho de alimentação de saída 506. O trilho de alimentação 504L de alimentação lógico e o trilho de alimentação 504M de alimentação de memória são acoplados a respectivas fontes de alimentação fornecendo uma tensão de memória  $V_{DD(M)}$  ou em um domínio de memória e uma tensão lógica  $V_{DD(L)}$  num domínio lógico. Para acoplar seletivamente o trilho de alimentação lógica 504L ou o trilho de alimentação 504M de memória ao trilho de alimentação de saída 506 para fornecer uma tensão lógica  $V_{DD(M)}$  de tensão de memória respectiva  $V_{DD(L)}$  ao agrupamento de memória 508, o circuito de multiplexação de energia 502 inclui circuitos de seleção de alimentação de memória e lógica 512M, 512L. Os circuitos de seleção de alimentação de memória e lógica 512M, 512L são acoplados entre o respectivo trilho de alimentação de alimentação de

memória 504M e o trilho de alimentação de alimentação lógico 504L. O sistema de multiplexação de potência 500 é configurado para ativar um dos circuitos de seleção de alimentação de memória e lógica 512M, 512L para acoplar um respectivo trilho de potência de alimentação de memória 504M e trilho de potência de alimentação lógico 504L ao trilho de alimentação de saída 506 para alimentar a matriz de memória 508 respectiva voltagem de memória VDD (M) e tensão lógica VDD (L).

[0048] Para selecionar o trilho de alimentação 504M de alimentação de memória e o barramento de alimentação 504L lógico acoplado ao barramento de saída 506, os circuitos de seleção de memória e de alimentação lógicos 512M, 512L, neste exemplo, incluem cada um dos circuitos de comutação de memória e lógica 514M, 514L, respectivamente no trilho de potência de saída 506. A intensidade de acionamento de uma memória ativada ou circuito de comutação de energia lógica 514M, 514L ajusta sua impedância de saída, que controla a comutação de uma queda de intensidade de corrente (IR) através da memória ou circuito de comutação de energia lógica 514M, 514L, resultando na tensão de saída desejada. Por exemplo, à medida que a potência de um circuito de memória ou lógica, 514M, 514L é aumentada, a impedância de saída da memória ou do circuito lógico 514M, 514L é diminuída, reduzindo assim a queda de IR e a respectiva tensão de memória ou lógica  $V_{DD(M)}$ ,  $V_{DD(L)}$  acionado no trilho de potência de saída 506. Se, no entanto, a intensidade de acionamento de um circuito de comutação lógica ou de memória 514M, 514L diminua, a impedância de saída da memória ou o circuito comutador lógico 514M, 514L aumentado, aumentando assim a

queda de IR e diminuindo a respectiva memória ou voltagem lógica VDD(M), VDD(L) acionado no trilho de potência de saída 506. As variações do PVT podem afetar a intensidade da unidade. A intensidade de acionamento pode ser aumentada, por exemplo, para compensar as variações do PVT. Entretanto, aumentar a intensidade da unidade aumenta o poder de vazamento. Assim, o sistema de multiplexação de potência 500 proporciona a intensidade de controlar seletivamente a intensidade de acionamento dos circuitos de seleção de alimentação de memória e lógica de 512M, 512L que podem ser usados para compensar as variações de PVT que podem reduzir a intensidade do inversor. A margem de intensidade de tração pode ser reduzida como resultado, reduzindo assim a potência de fuga enquanto ainda alcança a intensidade de condução desejada no trilho de potência de saída 506.

[0049] Neste exemplo, para proporcionar a intensidade de controlar a intensidade de acionamento dos circuitos de seleção de alimentação de memória e lógica ativados de 512M, 512L, cada um dos circuitos de comutação de memória e lógica 514M, 514L inclui uma pluralidade de transistores de PMOS conectados em paralelo 516M (1) a 516M(T) e 516L(1) a 516L(T), onde 'T' representa o número desejado de transistores PMOS 516 para incluir. Observe que os transistores NMOS também podem ser empregados. Os transistores PMOS 516M (1) a 516M (T) e 516L (1) a 516L(T) são acoplados entre uma respectiva memória e trilho de potência de alimentação lógica 504M, 504L e o trilho de alimentação de saída 506. Cada um dos transistores PMOS conectados em paralelo 516M (1) a 516M (T) e 516L (1) a 516L (T) possui uma intensidade de acionamento associada para

acionar a respectiva tensão de memória ou lógica VDD (M), VDD (L) no trilho de alimentação de saída 506. Assim, para controlar a intensidade geral do acionamento dos circuitos de seleção de memória e alimentação lógica 512M, 512L, os respectivos transistores PMOS conectados em paralelo 516M(1) a 516M(T) e 516L (1) a 516L (T) podem ser controlados individualmente para ser ativado ou desativado para contribuir para a condução da respectiva tensão de memória ou lógica VDD (M), VDD (L) para o trilho de potência de saída 506. Neste exemplo, cada um dos transistores PMOS 516M (1) a 516M (T) e 516L (1) a 516L (T) é configurado para receber uma memória associada ou indicador de intensidade da unidade lógica 518M, 518L na forma da respectiva memória e sinais lógicos de seleção do comutador de alimentação 520M (1) a 520M (T), 520L (1) a 520L (T). Assim, os indicadores de potência de memória e lógica 518M, 518L podem ser considerados em um exemplo como palavras de código, cada uma com sinais individuais ou bits indicando um estado de ativação da respectiva memória individual e sinais de seleção de comutador lógico 520M (1) a 520M (T), 520L (1) a 520L (T) formando as palavras de código para controlar o respectivo número de transistores PMOS conectados em paralelo 516M (1) a 516 (1) (T) e 516L (1) a 516L (T) que estão ativados.

[0050] Neste exemplo, os sinais de seleção de comutador de energia lógico e de memória 520M (1) a 520M (T), 520L (1) a 520L (T) são acoplados às portas G dos respectivos transistores PMOS 516M (1) a 516M (T) e 516 L (1) a 516L (T). Assim, o estado dos sinais de seleção do comutador de energia lógico e de memória 520M (1) a 520M (T), 520L (1) a 520L (T) controla se os respectivos

transistores PMOS 516M (1) -516M (T) e 516L (1) a 516L (T) são seletivamente ativados e, portanto, contribuem para acionar as respectivas tensões de memória e lógica  $V_{DD(M)}$ ,  $V_{DD(L)}$  no trilho de alimentação de saída 506. Se o estado da memória ou dos sinais de seleção do comutador de alimentação lógico 520M (1) a 520M (T), 520L (1) a 520L (T) é um estado de habilitação de seleção do interruptor de energia, que neste exemplo é um nível baixo lógico ('0'), os respectivos transistores PMOS 516M (1) a 516M (T) e 516L (1) a 516L (T) serão ativados para fornecer um caminho de fluxo de corrente entre a respectiva memória ou barramento de potência de alimentação lógica 504M, 504L e a saída trilho de potência 506. Se o estado da memória ou dos sinais de seleção da chave de alimentação lógica 520M (1) a 520M (T), 520L (1) a 520L (T) é um estado de desativação da seleção do comutador de alimentação, os respectivos transistores PMOS 516M (1) a 516M (T) e 516L (1) a 516L (T) serão desativados para não fornecer um caminho de fluxo de corrente entre o respectivo barramento de alimentação 504M e 504L de memória e lógica, e o trilho de alimentação de saída 506.

[0051] Com referência contínua à figura 6, para manter a tensão de memória  $V_{DD(M)}$  no trilho de alimentação de saída 506 para alimentar a matriz de memória 508 durante a comutação do acoplamento do trilho de alimentação de saída 506 do trilho de alimentação de alimentação de memória 504M para a fonte lógica do trilho de potência 504L, mas ao mesmo tempo evitando a criação de um caminho de condução cruzada de corrente entre os trilhos de alimentação de memória e lógica 504M, 504L, o circuito de multiplexação de energia 502 também inclui um circuito de controle de queda de diodo

600. O circuito de controle de queda de diodo 600 é fornecido na forma de um transistor de PMOS 602 neste exemplo. O circuito de controle de queda de diodo 600 é configurado para ser ativado para criar uma conexão de queda de diodo entre um trilho de potência de alimentação de memória 504M e o trilho de alimentação de saída 506 para um modo de operação de queda de diodo em resposta a comutação do acoplamento do barramento de alimentação de memória 504M para o trilho de alimentação lógica 504L, para o trilho de alimentação de saída 206. A este respeito, o circuito de controle de queda de diodo 600 está configurado para receber um sinal de comutador de trilho de potência de alimentação 603 indicando um estado de comutação de trilho de potência de alimentação ao trilho de alimentação de alimentação lógico 504L. Em resposta ao sinal de comutador de trilho de energia de alimentação 603 indicando um estado de habilitação de trilho de potência de alimentação para o trilho de alimentação de alimentação lógico 504L, o circuito de controle de descarte de diodo 600 estabelece uma conexão de queda de diodo entre o trilho de potência de alimentação de memória 504M e o trilho de alimentação de saída 506 em um modo de operação de queda de diodo.

[0052] Mais especificamente, neste exemplo, o circuito de controle de queda de diodo 600 inclui uma entrada de queda de diodo 604 acoplada a uma primeira entrada de seleção de trilho de alimentação 606 de um primeiro circuito de interruptor de energia 608. O circuito de controle de queda de diodo 600 também inclui uma entrada de controle de queda de diodo 610 acoplada à porta G do transistor PMOS 602 configurado para receber o sinal de comutador de alimentação

de energia 603 de um circuito de seleção de barramento de alimentação 612. O circuito de controle de queda de diodo 600 também inclui uma saída de queda de diodo 614 acoplada ao dreno D do transistor de PMOS 602 e acoplada a uma primeira saída de potência 616 do circuito comutador de energia 608. O circuito de controle de queda de diodo 600 é configurado para estabelecer uma conexão de queda de diodo em um modo de operação de queda de diodo entre a entrada de seleção de barramento de alimentação 606 e a saída de potência 616, em resposta ao sinal de comutação de barramento de alimentação 603 indicando que o comutador de alimentação está no trilho de alimentação 504M de alimentação de memória ao trilho de alimentação 504L de alimentação lógica. Um sinal 620 de saída de retenção controla a passagem do sinal 603 do comutador de energia de alimentação para a entrada de queda de diodo 604. Também em resposta ao sinal 603 do comutador do trilho de potência de alimentação indicando o estado de habilitação do comutador de alimentação de energia 504M para o trilho de alimentação de energia lógica 504L, o circuito de seleção de trilho de alimentação 612 é desativado para apresentar uma alta impedância ao poder entrar de seleção de trilho 606. Assim, no modo de operação de queda de diodo, a porta G e o dreno D de um transistor PMOS head switch 618 são acoplados em conjunto para colocar o primeiro transistor PMOS head switch 618 em uma configuração de queda de diodo.

[0053] Neste exemplo, a condução cruzada de corrente só pode ocorrer em uma direção entre o trilho de alimentação de alimentação de memória 504M com a maior tensão de memória VDD (M) ao barramento de alimentação de alimentação lógico 504L com a tensão lógica mais baixa V<sub>DD(L)</sub>.

Assim, o diodo do circuito de controle de queda 600 está configurado para regular a tensão no trilho de alimentação de saída 506 em uma configuração de polarização direta neste exemplo. Por exemplo, com a tensão de memória  $V_{DD(M)}$  no trilho de potência de alimentação de memória 504M sendo maior que a tensão lógica  $V_{DD(L)}$  no trilho de potência de alimentação lógica 504L, o circuito de controle de queda de diodo 600 estará em uma configuração de polarização direta. O circuito de controle de queda de diodo 600 é configurado para permitir que a corrente flua do trilho de alimentação de alimentação de memória 504M para o trilho de alimentação de saída 506 para manter uma tensão de saída  $V_{DD(A)}$  no trilho de alimentação de saída 506. Em um exemplo, o circuito de controle de queda de diodo 600 é configurado para regular a tensão de saída  $V_{DD(A)}$  no trilho de alimentação de saída 506 para uma tensão limite do circuito de controle de queda de diodo 600 menor que a tensão de memória  $V_{DD(M)}$  a tensão de saída  $V_{DD(A)}$  no trilho de alimentação de saída 506 descarrega para a tensão limite do circuito de controle de queda de diodo 600 menor que a tensão de memória  $V_{DD(M)}$ , o circuito de controle de queda de diodo 600 permitirá que a corrente flua para manter a tensão (por exemplo, 0,8 V) para uma tensão limite (por exemplo, 0,2 V) do circuito de controle de queda de diodo 600 menor que a tensão de memória  $V_{DD(M)}$  (por exemplo, 1 V). Desta maneira, a tensão de saída  $V_{DD(A)}$  é continuamente fornecida à matriz de memória 508 durante o modo de operação de queda de diodo mesmo quando se conecta o acoplamento do trilho de alimentação de fonte de memória 504M ao trilho de alimentação de fonte lógica 504L, ao trilho de alimentação de saída 506, mas sem criar um caminho de condução cruzada.

de corrente entre o trilho de alimentação de alimentação de memória 504M ao trilho de alimentação de alimentação lógico 504L. Para reduzir o consumo de energia durante o modo de operação de queda de diodo, o arranjo de memória 508 pode ser configurado para estar em um estado de retenção ou consumo de energia reduzido onde apenas correntes de fuga são retiradas do trilho de alimentação de saída 506 em um exemplo não limitativo.

[0054] Após a comutação do acoplamento do trilho de alimentação de alimentação de memória 504M para o trilho de alimentação de alimentação lógico 504L, para o trilho de alimentação de saída 506, o modo de operação de queda de diodo pode ser descontinuado. A este respeito, o sinal 603 do comutador de alimentação de energia é controlado para indicar um estado de desativação do comutador de alimentação de energia. Em resposta, o circuito de controle de queda de diodo 600 encerra a conexão de queda de diodo entre o trilho de potência de alimentação de memória 504M e o trilho de alimentação de saída 506. Um caminho de condução cruzada atual não é criado quando o modo de operação de queda de diodo é descontinuado, porque somente o indicador de intensidade do atuador de memória 518M ou o indicador de intensidade de acionamento lógico 518L é controlado para estar em um estado de habilitação de seleção de barramento de alimentação para selecionar apenas o circuito de memória de comutador de energia 514M ou o circuito de comutação de energia lógica 514L para acoplar o trilho de alimentação de memória ou lógica 504M, 504L ao trilho de alimentação de saída 506 a qualquer momento fora do modo de operação de queda do diodo.

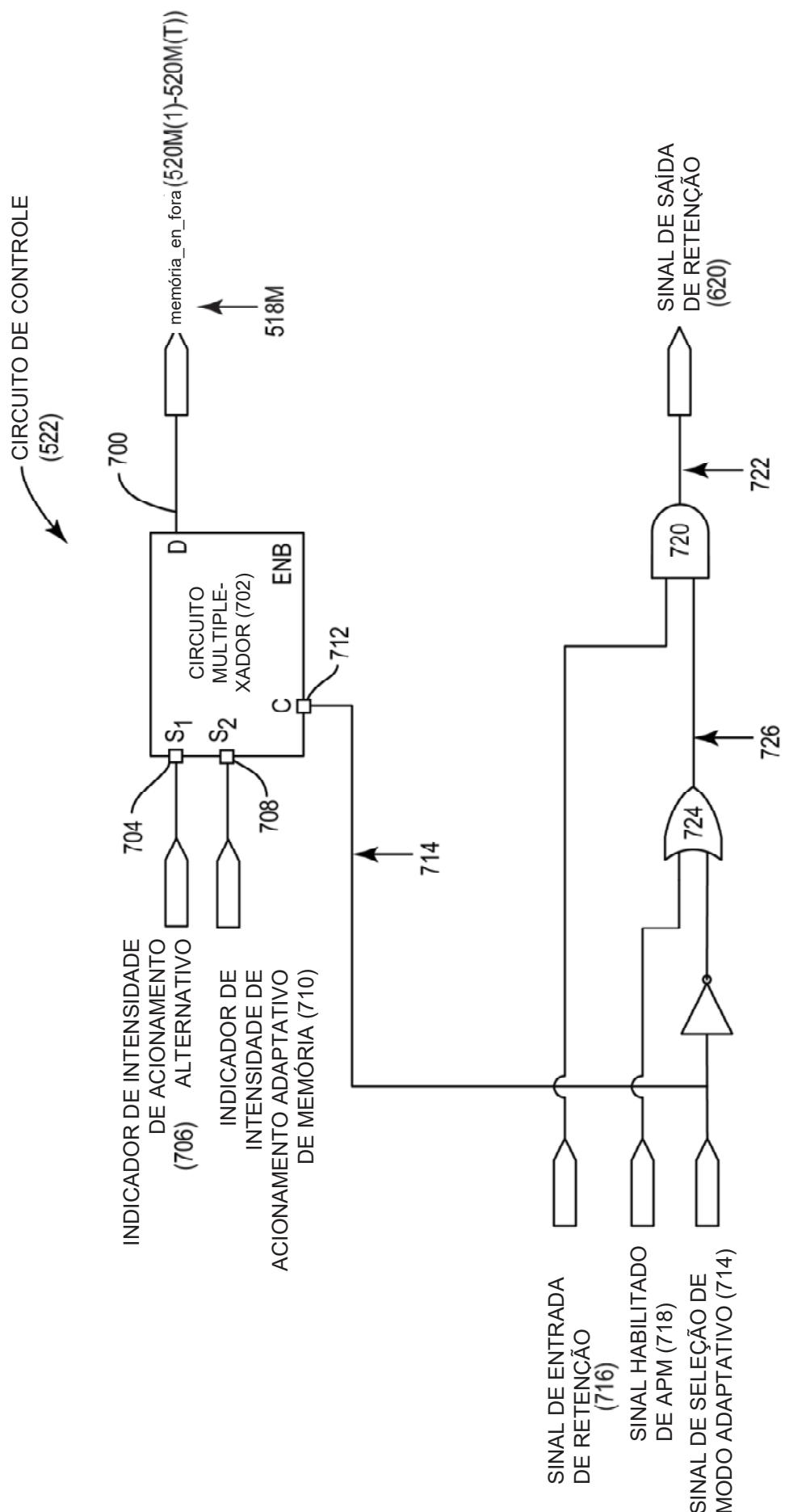

[0055] A Figura 7 é um diagrama de blocos do circuito de controle 522 que pode ser incluído no sistema de multiplexação de potência 500 da Figura 5 para controlar de forma adaptativa a intensidade de acionamento de um circuito de seleção de alimentação de memória ativa ou lógica 512M, 512L e o circuito de controle de queda de diodo 600 o circuito de multiplexação de energia 502 na Figura 6. O circuito de controle 522 é configurado para fornecer os modos operacionais ilustrados em uma tabela lógica 800 na Figura 8. Ambos serão discutidos em conjunto um com o outro abaixo.

[0056] Com referência à Figura 7, o indicador de intensidade do acionamento de memória 518M é fornecido como uma saída 700 de um circuito multiplexador 702. O circuito multiplexador 702 inclui uma primeira entrada 704 configurada para receber um primeiro indicador de intensidade de acionamento de bypass 706, e uma segunda entrada 708 configurada para receber um indicador de intensidade de acionamento adaptável de memória 710. O circuito multiplexador 702 controlado para passar o indicador de intensidade de bypass 706 para o indicador de intensidade do acionamento de memória 518M se for desejado realizar bypass sobre a operação de intensidade de acionamento adaptativa do circuito de multiplexação de potência 502 ao ligar o barramento de alimentação de memória 504M do trilho de potência de saída 506 na Figura 6. Por exemplo, o indicador de intensidade de bypass 706 pode ser uma configuração fixa para cada um dos sinais de seleção de comutador de energia 520M (1) a 520M (T) como todos ativados (por exemplo, todos lógicos '0') por exemplo ou qualquer outro fixo configuração. Desta maneira, a intensidade do

atuador da tensão de memória  $V_{DD(M)}$  não é variada. O circuito multiplexador 702 também é configurado para ser controlado para passar o indicador de intensidade da unidade adaptável à memória 710 para o indicador de intensidade do acionamento de memória 518M se for desejado controlar de forma adaptável a operação de intensidade de acionamento do circuito de multiplexação de potência 502 ao acoplar o barramento de alimentação de memória 504M para o trilho de alimentação de saída 506 na Figura 6. Por exemplo, o indicador 710 de intensidade da unidade adaptável à memória pode ser a saída do contador do indicador de intensidade do acionamento de memória 218 (1) no circuito de controle 222 (1) na Figura 4A como um exemplo. O indicador 710 de intensidade de acionamento adaptável à memória controlará os sinais de seleção do comutador de energia de memória 520M (1) a 520M (T) para controlar quais transistores PMOS 516M (1) a 516M (T) na Figura 5 são ativados.

[0057] Continuando a referência à Figura 7, o circuito multiplexador 702 também inclui uma entrada de seleção 712 configurada para receber um sinal de seleção de modo adaptativo 714 para controlar se o indicador de intensidade de acionamento de bypass 706 da primeira entrada 704 ou o indicador de intensidade de acionamento adaptável de memória 710 da segunda entrada 708 é passada para a saída 700 como o indicador de intensidade da unidade de memória 518M. A este respeito, se o sinal de seleção do modo adaptativo 714 estiver em um estado de desativação do modo adaptativo, o circuito do multiplexador 702 passa o indicador de intensidade do acionamento de bypass 706 da primeira entrada 704 para a saída 700. Se o sinal de seleção de modo

adaptativo 714 estiver em um estado de ativação de modo adaptativo, o circuito de multiplexação 702 passa o indicador de intensidade de acionamento adaptável de memória 710 da segunda entrada 708 para a saída 700. Se o sinal de seleção do modo adaptativo 714 é lógico baixo (isto é, lógico '0'), isto faz com que o circuito multiplexador 702 emita o indicador de intensidade do acionamento de bypass 706 da primeira entrada 704 para a saída 700 como o indicador de intensidade do acionamento de memória 518M. Se o sinal de seleção do modo adaptativo 714 for lógico alto (isto é, T lógico) neste exemplo, o sinal de seleção do modo adaptativo 714 está num estado de ativação do modo adaptativo neste exemplo para proporcionar controle adaptativo da intensidade do acionamento.

[0058] Para controlar a operação do modo de queda de diodo explicada no circuito de controle 522 na Figura 6, o circuito de controle 522 na Figura 7 é também configurado para controlar a geração do sinal de saída de retenção 620. Como discutido anteriormente na Figura 6, o sinal de saída de retenção 620 é configurado para controlar se o sinal 603 do comutador de energia de alimentação é passado. Se o sinal de seleção do modo adaptativo 714 é lógico baixo (isto é, lógico '0') para fazer com que o circuito multiplexador 702 emita o indicador de intensidade do acionamento de bypass 706 da primeira entrada 704 para a saída 700 como o indicador de intensidade do acionamento de memória 518M, uma retenção sinal de entrada 716 e sinal de habilitação de multiplexação de potência adaptativa (APM) 718 estão em estados de não preocupação (x), porque uma porta 720 baseada em AND na Figura 7 passará o sinal de entrada de

retenção 716 para uma saída 722 para o sinal de saída de retenção 620. Isto também é mostrado na tabela lógica 800 na Figura 8 para o estado "Bypass de ASR", em que o sinal de seleção do modo adaptativo 714 é lógico '0'. Assim, o sinal de entrada de retenção 716 controlará se o sinal 603 do comutador de alimentação de energia é passado para o circuito de controle de queda de diodo 600.

[0059] Em um estado de "Colapso" como mostrado na tabela lógica 800 na Figura 8, o sinal de seleção do modo adaptativo 714 é definido para um lógico "1" para estar no estado de ativação do modo adaptativo com o sinal de ativação APM 718 e o sinal de entrada de retenção 716 definido como lógico '0'. Isto faz com que o circuito multiplexador 702 forneça o indicador de intensidade de acionamento de bypass 706 desde a primeira entrada 704 para a saída 700 como o indicador de intensidade do acionamento de memória 518M. Uma porta 724 baseada em "OU" irá gerar um lógico '0' na sua saída 726 para uma porta 720 baseada em AND para gerar um lógico '0' para o sinal de saída de retenção 620 para desativar a operação de queda de diodo do circuito 600 de controle de queda de diodos.

[0060] Como mostrado na Figura 8, para configurar, de forma adaptativa, o controle da potência de acionamento da potência de memória multiplexada  $V_{DD(M)}$  no trilho de potência de saída 506 na Figura 5, um estado "ASR Habilitado" permite que o sinal de seleção de modo adaptável 714 seja definido para um lógico '1' para estar no estado de ativação do modo adaptativo. Isto faz com que o circuito multiplexador 702 forneça o indicador de intensidade de acionamento de bypass 706 desde a primeira entrada 704 para

a saída 700 como o indicador de intensidade do acionamento de memória 518M. O sinal de habilitação APM 718 é ajustado para um valor lógico '0' e o sinal de entrada de retenção 716 é ajustado para um valor lógico '1'. Isto faz com que a porta baseada em AND 720 emita um lógico '0' como o sinal de saída de retenção 620 para desabilitar a operação do modo de queda de diodo do circuito de controle de queda de diodo 600. Então, como mostrado na Figura 8, para um estado "Habilitado" para controlar de forma adaptativa os sinais de seleção da comutador de alimentação de memória 520M (1) a 520M (T) para controlar quais transistores PMOS 516M (1) a 516M (T) na Figura 5 são ativados para controlar a intensidade de acionamento da tensão de memória  $V_{DD(M)}$  do trilho de alimentação de alimentação de memória 504M acoplado ao barramento de alimentação de saída 506, o sinal de seleção de modo adaptativo 714 é ajustado para um lógico '1' para estar no estado habilitado de modo adaptável. Isto faz com que o circuito multiplexador 702 forneça o indicador de intensidade de acionamento de bypass 706 desde a primeira entrada 704 para a saída 700 como o indicador de intensidade do acionamento de memória 518M. O sinal de habilitação APM 718 é ajustado para um T lógico e o sinal de entrada de retenção 716 é ajustado para um lógico '0'. Isto faz com que a porta baseada em 'E' 720 emita um lógico '0' como o sinal de saída de retenção 620 para desabilitar a operação do modo de queda de diodo do circuito de controle de queda de diodo 600.

[0061] Como mostrado na Figura 8, no estado 504M, 504L de "Comutação Entre Trilhos de alimentação de Abastecimento", o sinal de seleção de modo adaptativo 714 é

ajustado para um lógico '1' para estar no estado de habilitação de modo adaptativo para controlar de forma adaptável a intensidade de acionamento do inversor da tensão de memória  $V_{DD(M)}$  a partir do trilho de potência de alimentação de memória 504M acoplado ao trilho de alimentação de saída 506. Isto faz com que o circuito multiplexador 702 forneça o indicador de intensidade de acionamento de bypass 706 desde a primeira entrada 704 para a saída 700 como o indicador de intensidade do acionamento de memória 518M. O sinal de habilitação APM 718 é ajustado para um lógico '1' e o sinal de entrada de retenção 716 é ajustado para um lógico '1'. Isto faz com que a porta 720 baseada em 'E' emita um lógico '1' como o sinal de saída de retenção 620 para permitir a operação do modo de queda de diodo do circuito 600 de controle de queda de diodos.