(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6982977号

(P6982977)

(45) 発行日 令和3年12月17日(2021.12.17)

(24) 登録日 令和3年11月25日(2021.11.25)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/335 (2011.01)

F 1

H01L 27/146

H04N 5/335

A

請求項の数 21 (全 17 頁)

(21) 出願番号 特願2017-85612 (P2017-85612)

(22) 出願日 平成29年4月24日 (2017.4.24)

(65) 公開番号 特開2018-186137 (P2018-186137A)

(43) 公開日 平成30年11月22日 (2018.11.22)

審査請求日 令和2年4月2日 (2020.4.2)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 110003281

特許業務法人大塚国際特許事務所

(72) 発明者 熊野 秀臣

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 今井 聖和

最終頁に続く

(54) 【発明の名称】 固体撮像装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素を有する画素アレイ部と、前記画素アレイ部の周辺に配置された周辺回路部とを含む固体撮像装置を製造する製造方法であって、

前記画素アレイ部を構成する素子および前記周辺回路部を構成する素子を有する半導体基板の上に配線構造を形成する工程と、

前記画素アレイ部における前記配線構造に複数の光導波路を形成するための複数の開口を形成する工程と、

前記複数の開口に光導波路材料が充填されるように前記画素アレイ部および前記周辺回路部に前記光導波路材料からなる膜を形成する工程と、

前記光導波路材料からなる前記膜を平坦化する工程と、

前記周辺回路部における平坦化された前記膜をエッティングする工程と、を含み、

前記配線構造は、層間絶縁膜の溝に配置された導電性パターンと、前記導電性パターンを覆う拡散防止膜とを含み、前記導電性パターンは、第1方向に平行な複数の主ラインと、前記複数の主ラインを相互に接続する複数の補助ラインとを含み、

前記第1方向に直交する第2方向における前記複数の主ラインの各々の幅は、250nm以上かつ2000nm以下であり、

前記複数の主ラインにおける隣り合う主ラインの間隔は、500nm以下であり、

前記第1方向における前記複数の補助ラインの各々の幅は、400nmより小さく、

前記複数の主ラインが、第1ラインと、第2ラインと、前記第1ラインと前記第2ライ

10

20

ンとの間に配置された第3ラインと、を含み、

前記第1方向に平行で前記第1ラインに重なる第1辺、および、前記第1方向に平行で前記第2ラインに重なる第2辺を有する正方形の領域が、前記正方形の領域の中に前記複数の補助ラインの少なくとも1つを含むように定義され、

前記正方形の領域の中における前記導電性パターンの面積を前記正方形の領域の面積で除した値が0.9以下であり、これにより、前記膜の圧縮応力によって前記導電性パターンから前記拡散防止膜が剥がれることが抑制される、

ことを特徴とする固体撮像装置の製造方法。

#### 【請求項2】

前記第2方向における前記複数の主ラインの各々の幅は、前記第1方向における前記複数の補助ラインの各々の幅より大きい、

ことを特徴とする請求項1に記載の固体撮像装置の製造方法。

#### 【請求項3】

複数の画素を有する画素アレイ部と、前記画素アレイ部の周辺に配置された周辺回路部とを含む固体撮像装置を製造する製造方法であって、

前記画素アレイ部を構成する素子および前記周辺回路部を構成する素子を有する半導体基板の上に配線構造を形成する工程と、

前記画素アレイ部における前記配線構造に複数の光導波路を形成するための複数の開口を形成する工程と、

前記複数の開口に光導波路材料が充填されるように前記画素アレイ部および前記周辺回路部に前記光導波路材料からなる膜を形成する工程と、

前記光導波路材料からなる前記膜を平坦化する工程と、

前記周辺回路部における平坦化された前記膜をエッチングする工程と、を含み、

前記配線構造は、層間絶縁膜の溝に配置された導電性パターンと、前記導電性パターンを覆う拡散防止膜とを含み、前記導電性パターンは、第1方向に平行な複数の主ラインと、前記複数の主ラインを相互に接続する複数の補助ラインとを含み、前記第1方向に直交する第2方向における前記複数の主ラインの各々の幅は、前記第1方向における前記複数の補助ラインの各々の幅より大きく、

前記第2方向における前記複数の主ラインの各々の幅は、250nm以上かつ2000nm以下であり、

前記第1方向における前記複数の補助ラインの各々の幅は、400nm以上かつ2000nm以下であり、

前記複数の主ラインが、第1ラインと、第2ラインと、前記第1ラインと前記第2ラインとの間に配置された第3ラインと、を含み、

前記第1方向に平行で前記第1ラインに重なる第1辺、および、前記第1方向に平行で前記第2ラインに重なる第2辺を有する正方形の領域が、前記正方形の領域の中に前記複数の補助ラインの少なくとも1つを含むように定義され、

前記正方形の領域の中における前記導電性パターンの面積を前記正方形の領域の面積で除した値が0.75以下であり、これにより、前記膜の圧縮応力によって前記導電性パターンから前記拡散防止膜が剥がれることが抑制される、

ことを特徴とする固体撮像装置の製造方法。

#### 【請求項4】

前記第2方向における前記複数の主ラインの各々の幅は、400nm以上である、

ことを特徴とする請求項1乃至3のいずれか1項に記載の固体撮像装置の製造方法。

#### 【請求項5】

前記複数の主ラインにおける隣り合う主ラインの間隔は、140nm以上かつ500nm以下である、

ことを特徴とする請求項1乃至4のいずれか1項に記載の固体撮像装置の製造方法。

#### 【請求項6】

前記複数の主ラインにおける隣り合う任意の主ラインと前記複数の補助ラインにおける

10

20

30

40

50

隣り合う任意の補助ラインとによって囲まれる部分の面積が  $5\ 6\ 0\ 0\ 0\ 0\ nm^2$  以上かつ  $2\ 0\ 0\ 0\ 0\ 0\ nm^2$  以下である、

ことを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の固体撮像装置の製造方法。

#### 【請求項 7】

前記導電性パターンにおける前記複数の主ラインの数は、12 以上である、

ことを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の固体撮像装置の製造方法。

#### 【請求項 8】

前記配線構造は、複数の配線層を含み、前記導電性パターンは、前記複数の配線層のうち最上の配線層に配置されている、

ことを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の固体撮像装置の製造方法。 10

#### 【請求項 9】

前記導電性パターンは、銅を主成分とする配線層である、

ことを特徴とする請求項 8 に記載の固体撮像装置の製造方法。

#### 【請求項 10】

前記拡散防止膜は、炭化シリコン (SiC) および酸化炭化シリコン (SiOC) の少なくとも一方を含む、

ことを特徴とする請求項 9 に記載の固体撮像装置の製造方法。

#### 【請求項 11】

前記配線構造は、前記拡散防止膜の上に絶縁膜を有し、前記絶縁膜は、 $5\ 0\ 0\ nm$  以下の厚さを有する、

ことを特徴とする請求項 10 に記載の固体撮像装置の製造方法。 20

#### 【請求項 12】

前記膜をエッチングする工程では、前記複数の光導波路と同一材料で構成され前記複数の光導波路から伸びた部分が前記配線構造の上に残るように前記膜をエッチングする、

ことを特徴とする請求項 1 乃至 11 のいずれか 1 項に記載の固体撮像装置の製造方法。

#### 【請求項 13】

前記配線構造は、前記周辺回路部に配置された光導波路を有しない、

ことを特徴とする請求項 12 に記載の固体撮像装置の製造方法。

#### 【請求項 14】

前記膜をエッチングする工程では、前記複数の光導波路から伸びた前記部分が前記導電性パターンの上には存在しないように前記膜をエッチングする、

ことを特徴とする請求項 12 又は 13 に記載の固体撮像装置の製造方法。 30

#### 【請求項 15】

前記複数の光導波路は、窒化シリコンまたは酸化シリコンを含む、

ことを特徴とする請求項 12 乃至 14 のいずれか 1 項に記載の固体撮像装置の製造方法。

。

#### 【請求項 16】

前記層間絶縁膜は、酸化シリコンまたは酸化炭化シリコンを含む、

ことを特徴とする請求項 1 乃至 15 のいずれか 1 項に記載の固体撮像装置の製造方法。

#### 【請求項 17】

前記導電性パターンは、前記複数の主ラインおよび前記複数の補助ラインのいずれかに接続されたプラグを含む、

ことを特徴とする請求項 1 乃至 16 のいずれか 1 項に記載の固体撮像装置の製造方法。 40

#### 【請求項 18】

前記複数の補助ラインは、前記複数の主ラインのうち少なくとも 2 つの主ラインを相互に接続し他の主ラインを接続しないように前記第 2 方向に平行に伸びた補助ラインを含む、

ことを特徴とする請求項 1 乃至 17 のいずれか 1 項に記載の固体撮像装置の製造方法。

#### 【請求項 19】

前記複数の補助ラインは、前記複数の主ラインのうち第 1 グループを構成する主ライン

50

を相互に接続する第1補助ラインと、前記複数の主ラインのうち第2グループを構成する主ラインを相互に接続する第2補助ラインとを含み、前記第1グループを構成する主ラインの少なくとも一部は、前記第2グループを構成する主ラインと異なり、前記第1方向における前記第1補助ラインの位置と、前記第1方向における前記第2補助ラインの位置とが互いに異なる。

ことを請求項1乃至17のいずれか1項に記載の固体撮像装置の製造方法。

#### 【請求項20】

前記導電性パターンは、固定電圧が印加されるパターンである。

ことを特徴とする請求項1乃至19のいずれか1項に記載の固体撮像装置の製造方法。

#### 【請求項21】

10

前記導電性パターンは、前記周辺回路部に配置されている。

ことを特徴とする請求項1乃至20のいずれか1項に記載の固体撮像装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、固体撮像装置の製造方法の製造方法に関する。

##### 【背景技術】

##### 【0002】

固体撮像装置の画素数の増大に伴って、信号ラインにおける信号の遅延時間を低減することが重要となっている。そのため、配線層の材料として銅を主成分とする材料が使用されることが多くなってきた。1つの配線層には、信号ラインの他に、電源ラインおよび接地ラインも配置されうる。よって、信号ラインとともに電源ラインおよび接地ラインも銅を主成分とする材料で構成されうる。銅を主成分とする材料で信号ライン、電源ラインおよび接地ライン等のパターンを形成するために、ダマシンプロセスが使用されうる。よく知られているように、ダマシンプロセスは、層間絶縁膜に溝を形成しその溝に配線材料が充填されるように配線材料の膜を形成し、その後に当該膜の不要な部分を除去するためにCMP工程を実施するプロセスである。

20

##### 【0003】

固体撮像装置では、固定パターンノイズを低減するために、電源ラインおよび接地ラインにおける電圧降下を小さくする必要があり、そのために、電源ラインおよび接地ライン等のパターンの幅を広くしたいとの要求がある。あるいは、制御信号等を伝達するための信号ラインにおいても、電圧降下を小さくすることが求められることがあるかもしれない。

30

##### 【0004】

パターンの幅を広くすると、CMP工程においてディシングが発生しうる。配線材料のCMP工程は、配線材料の研磨レートが絶縁材料の研磨レートよりも高い条件で実施されるので、パターンの幅が広い領域では、パターンの幅が狭い領域よりも研磨レートが高くなるために配線材料が過剰に研磨されて窪みが形成される（特許文献1参照）。これがディシングである。ディシングを低減するための技術として、幅が広いパターンに対して、破線を構成するように複数のスリットを設けることが考えられる。

40

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

##### 【特許文献1】特開2009-259967号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0006】

しかしながら、幅が広いパターンに対して破線を構成するように複数のスリットを設けると、該パターンの上に形成される膜と該パターンとの密着性（結合力）が低下し、該パターンから該膜が剥がれやすくなりうる。膜の剥がれが生じると、固体撮像装置の信頼性

50

が低下する。信頼性の低下は歩留まりの低下にも影響しうる。

#### 【0007】

本発明は、層間絶縁膜の溝に導電性パターンが配置された構造を有する固体撮像装置の信頼性を向上させるために有利な技術を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

本発明の1つの側面は、複数の画素を有する画素アレイ部と、前記画素アレイ部の周辺に配置された周辺回路部とを含む固体撮像装置を製造する製造方法に係り、前記製造方法は、前記画素アレイ部を構成する素子および前記周辺回路部を構成する素子を有する半導体基板の上に配線構造を形成する工程と、前記画素アレイ部における前記配線構造に複数の光導波路を形成するための複数の開口を形成する工程と、前記複数の開口に光導波路材料が充填されるように前記画素アレイ部および前記周辺回路部に前記光導波路材料からなる膜を形成する工程と、前記光導波路材料からなる前記膜を平坦化する工程と、前記周辺回路部における平坦化された前記膜をエッチングする工程と、を含み、前記配線構造は、層間絶縁膜の溝に配置された導電性パターンと、前記導電性パターンを覆う拡散防止膜とを含み、前記導電性パターンは、第1方向に平行な複数の主ラインと、前記複数の主ラインを相互に接続する複数の補助ラインとを含み、前記第1方向に直交する第2方向における前記複数の主ラインの各々の幅は、250nm以上かつ2000nm以下であり、前記複数の主ラインにおける隣り合う主ラインの間隔は、500nm以下であり、前記第1方向における前記複数の補助ラインの各々の幅は、400nmより小さく、前記複数の主ラインが、第1ラインと、第2ラインと、前記第1ラインと前記第2ラインとの間に配置された第3ラインと、を含み、前記第1方向に平行で前記第1ラインに重なる第1辺、および、前記第1方向に平行で前記第2ラインに重なる第2辺を有する正方形の領域が、前記正方形の領域の中に前記複数の補助ラインの少なくとも1つを含むように定義され、前記正方形の領域の中における前記導電性パターンの面積を前記正方形の領域の面積で除した値が0.9以下であり、これにより、前記膜の圧縮応力によって前記導電性パターンから前記拡散防止膜が剥がれることが抑制される。10

#### 【発明の効果】

#### 【0009】

本発明によれば、層間絶縁膜の溝に導電性パターンが配置された構造を有する固体撮像装置の信頼性を向上させるために有利な技術が提供される。30

#### 【図面の簡単な説明】

#### 【0010】

【図1】本発明の1つの実施形態のカメラおよびそれを構成する固体撮像装置の構成を示す図。

【図2】画素アレイ部を構成する画素の構成例を示す図。

【図3】固体撮像装置に配置される導電性パターン(a)および予備実験のための導電性パターン(b)を模式的に示す図。

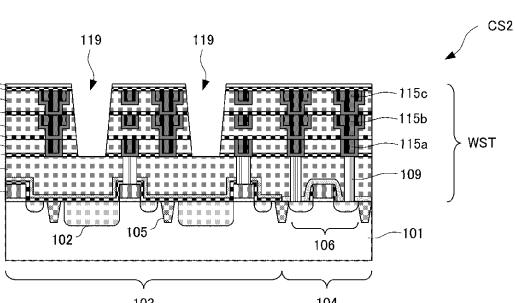

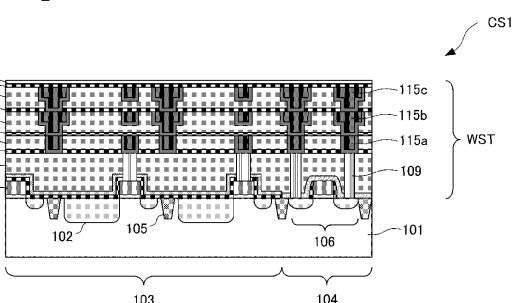

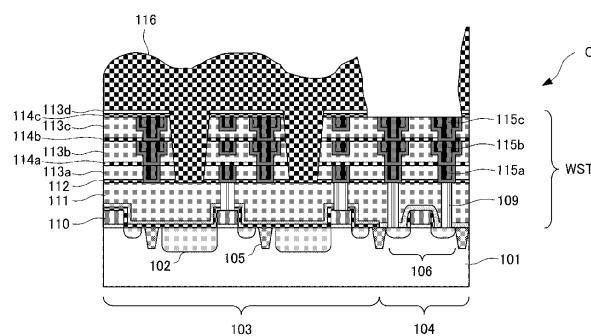

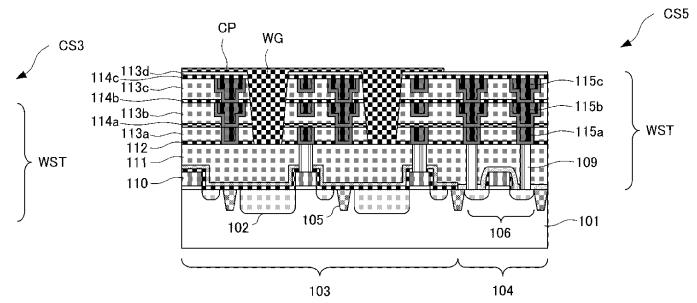

【図4A】固体撮像装置の構造および製造方法を示す模式的な断面図。

【図4B】固体撮像装置の構造および製造方法を示す模式的な断面図。

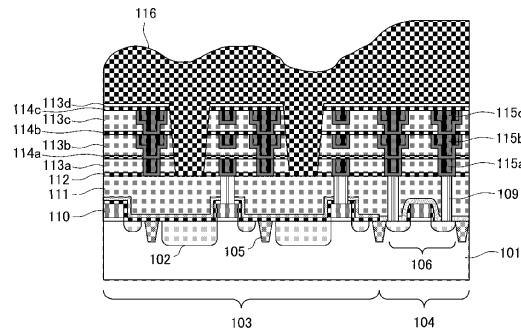

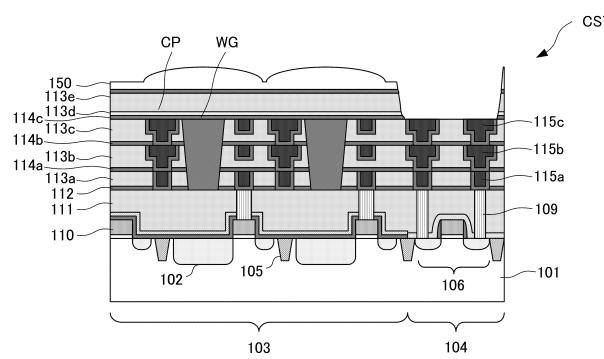

【図4C】固体撮像装置の構造および製造方法を示す模式的な断面図。

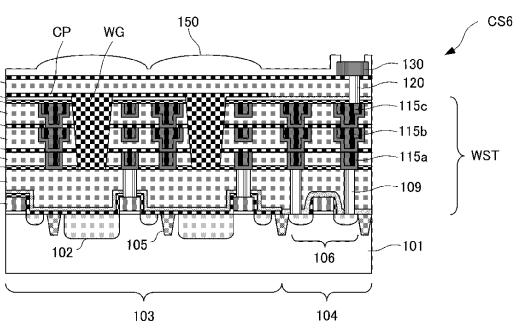

【図4D】固体撮像装置の構造および製造方法を示す模式的な断面図。

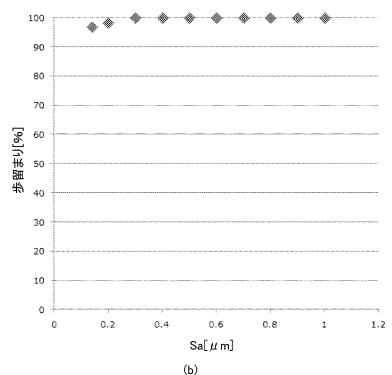

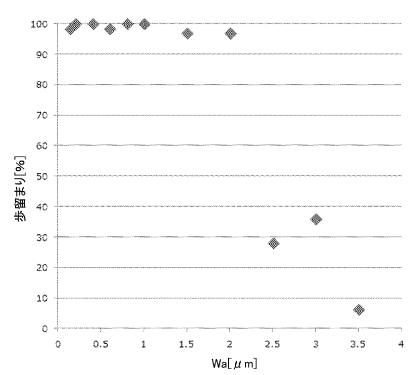

【図5】主ラインの幅と拡散防止膜の剥がれによる歩留まりの低下との関係を評価した結果(a)、および、主ラインの間隔と拡散防止膜の剥がれによる歩留まりの低下との関係を評価した結果(b)を示す図。

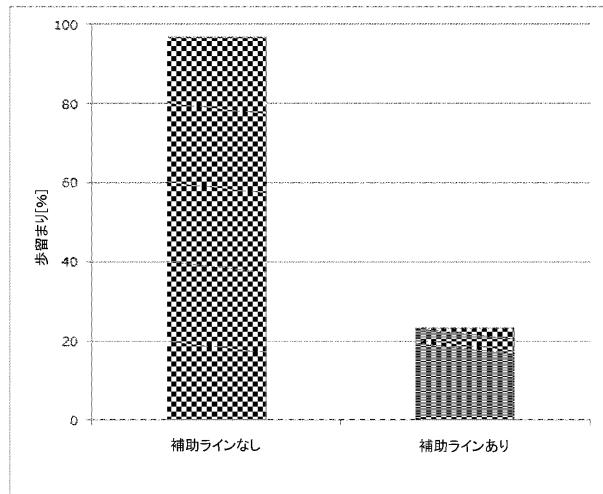

【図6】補助ラインを有しない導電性パターンと補助ラインを有する導電性パターンについて拡散防止膜の剥がれによる歩留まりの低下を評価した結果を示す図。

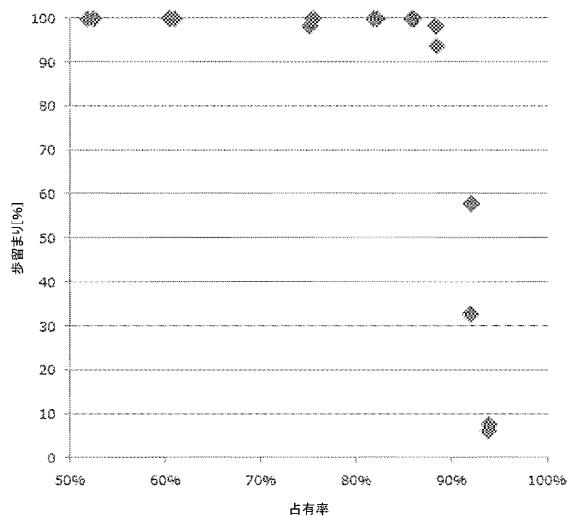

【図7】補助ラインの幅が400nmより小さい条件の下で導電性パターンの占有率と拡散防止膜の剥がれるによる歩留まり低下との関係を評価した結果を示す図。

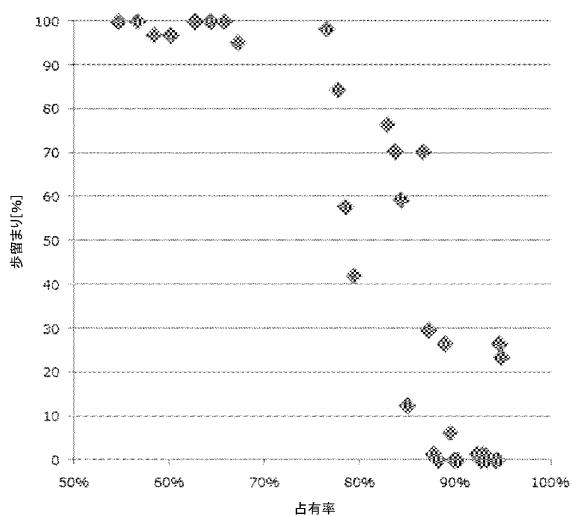

【図8】補助ラインの幅が400nm以上かつ2000nm以下の条件の下で導電性パタ40

【図9】補助ラインの幅が2000nm以上の条件の下で導電性パタ50

ーンの占有率と拡散防止膜の剥がれるによる歩留まり低下との関係を評価した結果を示す図。

【図9】本発明の第3実施形態の導電性パターンの構成を示す図。

【発明を実施するための形態】

【0011】

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。本実施形態は、後述する光導波路を有する表面照射型の固体撮像装置において特に好適であるが、光導波路を有しない表面照射型の固体撮像装置にも適用可能であり、裏面照射型の固体撮像装置にも適用可能である。

【0012】

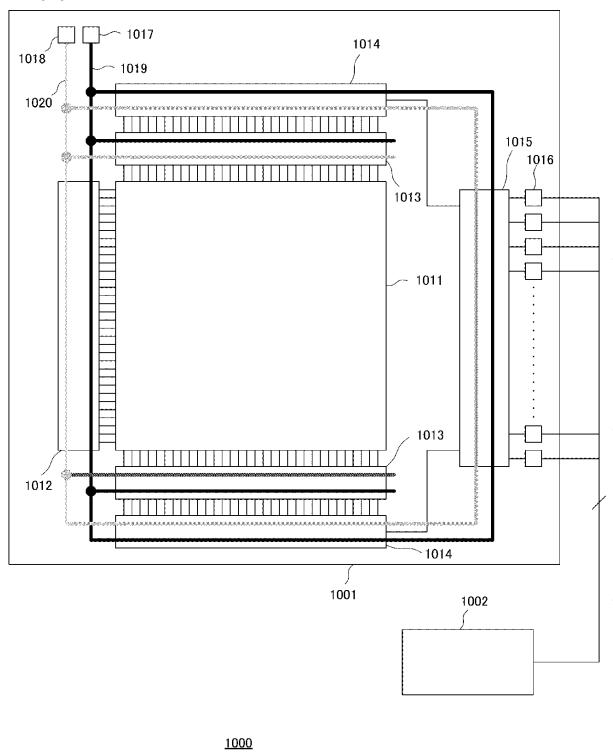

まず、後述の第1乃至第3実施形態において共通な事項について説明する。図1には、本発明の1つの実施形態のカメラ1000の構成が示されている。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パソコンコンピュータ、携帯端末）も含まれる。カメラ1000は、固体撮像装置1001と、固体撮像装置1001から出力される信号を処理する処理部1002とを備えている。固体撮像装置1001は、画素アレイ部1011と、行選択回路（例えば、垂直走査回路）1012と、読出回路1013と、列選択回路（例えば、水平走査回路）1014と、出力回路1015とを備えうる。画素アレイ部1011は、複数の行および複数の列を構成するように配置された複数の画素を有する。読出回路1013は、複数の列回路を有し、該複数の列回路は、行選択回路1012によって選択された画素から、画素アレイ部1011の複数の列信号線を介して、信号を読み出す。各列回路は、例えば、アンプ、CDS回路、演算回路、A/D変換器等を含みうる。列選択回路1014は、画素アレイ部1011のうち行選択回路1012によって選択された複数の画素から読出回路1013によって読み出された信号を順次に出力回路1015に伝送する。図1に示された例では、画素アレイ部1011の一方の側に1つの組の読出回路1013および列選択回路1014が配置され、画素アレイ部1011の他方の側に他の1つの組の読出回路1013および列選択回路1014が配置されている。出力回路1015は、例えば、複数の出力バッファを含みうる。

【0013】

固体撮像装置1001は、更に、出力回路1015を構成する複数の出力バッファからの信号を出力する複数の出力パッド1016と、電源電圧パッド1017と、接地電圧パッド1018と、電源電圧ライン1019と、接地電圧ライン1020とを備えうる。電源電圧ライン1019は、電源電圧パッド1017に接続され、画素アレイ部1011、行選択回路1012、読出回路1013、列選択回路1014および出力回路1015に電源電圧を供給する。電源電圧パッド1017および電源電圧ライン1019は、複数系統に分割されていてもよい。接地電圧ライン1020は、接地電圧パッド1018に接続され、画素アレイ部1011、行選択回路1012、読出回路1013、列選択回路1014および出力回路1015に接地電圧を供給する。

【0014】

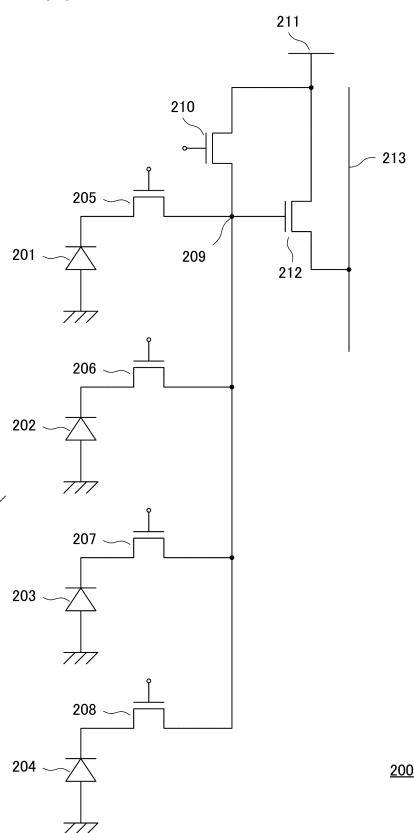

図2には、画素アレイ部1011を構成する画素の構成例が示されている。画素は、1又は複数の光電変換部を有する構成要素である。通常は、1つのマイクロレンズを共有する光電変換部が1つの画素を構成しうる。例えば、1つのマイクロレンズに対して設けられた光電変換部が1つであれば、1つの光電変換部が1つの画素を構成しうる。また、1つのマイクロレンズに対して設けられた光電変換部が2つであれば、2つの光電変換部が1つの画素を構成しうる。

【0015】

図2に示された例では、4つの光電変換部201、202、203、204と、4つの転送トランジスタ205、206、207、208と、1つのリセットトランジスタ210と、1つの増幅トランジスタ212とで1つの画素セル200が構成されている。ここで、1つの画素セル200によって4つの画素が構成されてもよいし、2つの画素が構成

10

20

30

40

50

されてもよいし、1つの画素が構成されてもよい。画素セル200は、電荷電圧変換部209を含みうる。電荷電圧変換部209は、フローティングディフェュージョンを含みうる。光電変換部201、202、203、204は、入射光の光量に応じた電荷を発生し蓄積する。転送トランジスタ205、206、207、208は、それぞれ光電変換部201、202、203、204に蓄積された電荷を電荷電圧変換部209に転送する。

#### 【0016】

画素アレイ部1011以外の構成要素(図1の例では、行選択回路1012、読出回路1013、列選択回路1014、出力回路1015、出力パッド1016、電源電圧パッド1017、接地電圧パッド1018)は、周辺回路部を構成する。

#### 【0017】

図2に示された例では、光電変換部201、202、203、204は、アノードが接地電圧ラインに接続され、カソードが転送トランジスタ205、206、207、208に接続されたフォトダイオードで構成されている。電荷電圧変換部209は、増幅トランジスタ212のゲートに接続されている。増幅トランジスタ212のドレインは、電圧供給ライン211に接続され、増幅トランジスタ212のソースは、列信号線213に接続されている。増幅トランジスタ212は、そのゲートに与えられる電圧に応じた電圧を列信号線213に出力する。列信号線213は、前述の読出回路1013の列回路に接続されている。リセットトランジスタ210は、ドレインが電圧供給ライン211に接続され、ソースが電荷電圧変換部209に接続されていて、電荷電圧変換部209の電圧を設定する。電圧供給ライン211には、第1電圧および第2電圧が選択的に供給されうる。電圧供給ライン211に第1電圧が供給されている状態でリセットトランジスタ210が導通状態にされると、画素セル200は、増幅トランジスタ212が列信号線213を駆動することができる状態である選択状態に設定される。電圧供給ライン211に第2電圧が供給されている状態でリセットトランジスタ210が導通状態にされると、画素セル200は、増幅トランジスタ212が列信号線213を駆動することができない状態である非選択状態に設定される。

#### 【0018】

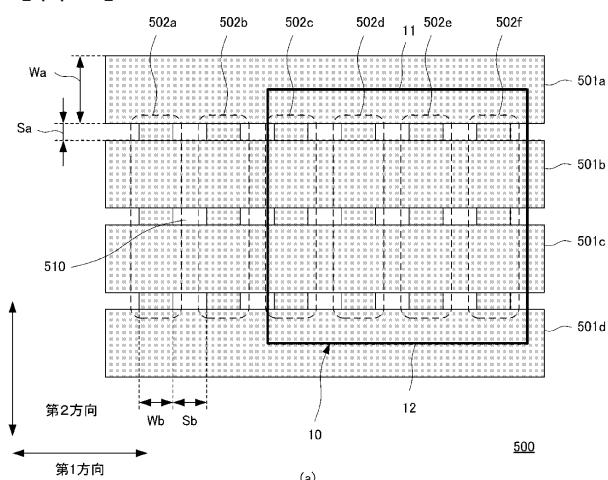

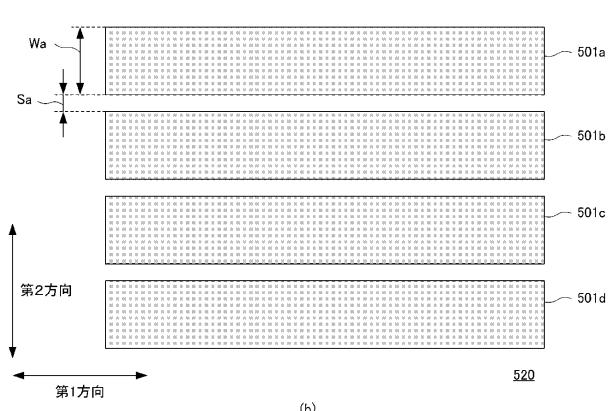

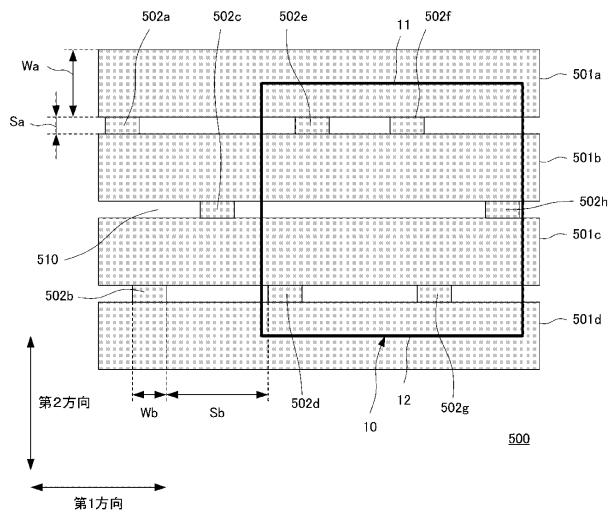

図3(a)には、固体撮像装置1001に配置されうる導電性パターン500が模式的に示されている。導電性パターン500は、固定電圧(例えば、電源電圧、接地電圧)が印加されるパターンでありうる。例えば、前述の電源電圧ライン1019および接地電圧ライン1020は、図3(a)に模式的に示される導電性パターン500で構成されうる。信号ラインも、導電性パターン500で構成されてもよい。また、画素アレイ部に配置されるラインも、導電性パターン500で構成されてもよい。なお、図3(a)では、作図上の便宜のために、導電性パターン500の全長の一部が切り出して示されている。一例において、導電性パターン500を構成する主ライン501の数は8~16、例えば12でありうる。

#### 【0019】

以下では、互いに直交する第1方向および第2方向を基準として説明を行う。しかし、これは導電性パターン500の構成要素の構造および寸法を説明するための便宜的な表現に過ぎず、導電性パターン500が固体撮像装置1001において配置される方向を限定するものではない。

#### 【0020】

導電性パターン500は、半導体基板の上に配置された配線構造において、層間絶縁膜の溝に配置される。導電性パターン500は、第1方向に平行な複数の主ライン501と、複数の主ライン501を相互に接続する複数の補助ライン502とを含む。ここで、複数の主ライン501を相互に区別して説明する際には、501a、501b、501c、501dのように記載する。また、複数の補助ライン502を相互に区別して説明する際には、502a、502b、502c、502d、502e、502fのように記載する。

#### 【0021】

10

20

30

40

50

以下では、第2方向における主ライン501の幅をW<sub>a</sub>とし、第1方向における補助ライン502の幅をW<sub>b</sub>とする。また、隣り合う主ライン501の間隔（例えば、主ライン501aと主ライン501bとの間隔）をS<sub>a</sub>とし、隣り合う補助ライン502の間隔（例えば、補助ライン502aと補助ライン502bとの間隔）をS<sub>b</sub>とする。隣り合う主ライン501の間に複数の補助ライン502を設けることによって、破線を構成するように配置された複数のスリット510が形成される。

#### 【0022】

以下、図4A～図4Dを参照しながら固体撮像装置1001の構造をその製造方法とともに説明する。固体撮像装置1001は、複数の画素を有する画素アレイ部103（前述の画素アレイ部1011に相当）と、画素アレイ部103の周辺に配置された周辺回路部104とを含む。固体撮像装置1001は、半導体基板101と、半導体基板101の上に配置された配線構造WSTとを備える。

10

#### 【0023】

断面図CS1には、半導体基板101の上に配線構造WSTが形成された状態が模式的に示されている。半導体基板101は、画素アレイ部103を構成する素子（例えば、光電変換部102（前述の光電変換部201～204に相当））、および、周辺回路部104を構成する素子（例えば、トランジスタ106）を有する。また、半導体基板101は、素子分離105を有する。配線構造WSTは、半導体基板101の上にゲート絶縁膜を介して配置されたゲート110、ゲート110の上に配置された層間絶縁膜111、および、層間絶縁膜111に埋め込まれたコンタクトプラグ109を含みうる。コンタクトプラグ109は、例えば、タンゲステンを主成分とする材料で構成され、層間絶縁膜111等とコンタクトプラグ109との間には、例えば、チタンまたは窒化チタン等からなるバリアメタルが配置されうる。

20

#### 【0024】

配線構造WSTは、更に、エッチングストップ膜112、複数の配線層115および複数の層間絶縁膜113および拡散防止膜114を含みうる。エッチングストップ膜112は、後述の光導波路の形成の際に使用されうる。複数の配線層を相互に区別して説明する際には、115a～115cのように記載する。また、複数の層間絶縁膜113を相互に区別して説明する際には、113a～113dのように記載する。また、複数の拡散防止膜114を相互に区別して説明する際には、114a～114cのように記載する。エッチングストップ膜112は、後述の光導波路の形成の際に使用されうる。

30

#### 【0025】

配線層115は、層間絶縁膜113に溝を形成し、その溝を埋めるように導電性材料（例えば、銅を主成分とする材料）からなる膜を形成し、その後、層間絶縁膜113の上の膜をCMP工程で除去することによって形成されうる導電性パターンを含みうる。溝と導電性パターンとの間には、バリアメタル層が形成されうる。バリアメタル層は、例えばチタン、タンタルおよび窒化タンタルのいずれかによって形成される層を含みうる。

#### 【0026】

拡散防止膜114は、導電性材料を構成する金属原子（銅原子）が層間絶縁膜113中に拡散することを防止する機能を有する。拡散防止膜114の屈折率が高い場合、拡散防止膜114を通して光が伝搬し、感度低下および混色の原因となりうる。したがって、拡散防止膜114の屈折率は低いことが望ましく、1.9以下であることが望ましい。拡散防止膜114は、例えば、炭化シリコン(SiC)および酸化炭化シリコン(SiOC)の少なくとも一方を含む層でありうる。拡散防止膜114cの上には層間絶縁膜113dが形成されうる。層間絶縁膜113dは、例えば、酸化シリコン(SiO)および酸化炭化シリコン(SiOC)の少なくとも一方を含む膜でありうる。集光率を向上させるためには、層間絶縁膜113dは薄い方が望ましく、例えば500nm以下の厚さを有しうる。ただし、層間絶縁膜113は、応力の低減のために、例えば100nm以上の厚さを有しうる。

40

#### 【0027】

10

20

30

40

50

断面図 C S 2 には、光導波路を形成するための開口 119 を配線構造 W S T に形成する工程が示されている。開口 119 は、光電変換部 102 の上に配置される。断面図 C S 3 には、開口 119 に光導波路材料 116 を充填する工程が示されている。光導波路材料 116 は、例えば、窒化シリコンまたは酸化シリコンでありうる。配線構造 W S T の上に形成された光導波路材料 116 からなる膜は、例えば、100 ~ 600 MPa 程度の高い圧縮応力を有しうる。一例において、開口 119 を光導波路材料 116 で完全に埋めるためには、光導波路材料 116 からなる膜の厚さを 2 μm 程度にする必要があり、これが高い圧縮応力を発生させうる。

#### 【 0028 】

周辺回路部 104 における配線層 115c は、図 3 (a) に例示されたような導電性パターン 500 を有しうる。配線層 115c の導電性パターン 500 の上には、拡散防止膜 114c および層間絶縁膜 113d が形成されうる。また、拡散防止膜 114c の上には、層間絶縁膜 113d を介して、光導波路材料 116 からなる高い圧縮応力を有する膜が配置されうる。よって、拡散防止膜 114c は、光導波路材料 116 からなる膜の高い圧縮応力の影響を受けうる。そのため、断面図 C S 4 に例示されように、配線層 115c に配置された導電性パターン 500 と拡散防止膜 114c との界面にせん断力が発生し、層間絶縁膜 113c および配線層 115c に配置された導電性パターン 500 から拡散防止膜 114c が剥がれうる。なお、拡散防止膜 114c の剥がれが起こらない場合においても、層間絶縁膜 113c および配線層 115c に配置された導電性パターン 500 に対する拡散防止膜 114c の密着性が低下し、これが以後において拡散防止膜 114c が剥がれる原因になりうる。ここでは、最も剥がれが起こりやすい拡散防止膜 114 について例示したが、配線層 115a からの拡散防止膜 114a の剥がれ、および、配線層 115b からの拡散防止膜 114b の剥がれも起こりうる。このような剥がれを防止するために、導電性パターン 500 の構成に対して後述のような制限ないし設計規則が与えられうる。

#### 【 0029 】

以下では、後述の制限ないし設計規則の遵守によって拡散防止膜 114 の剥がれが防止された場合における後続工程を説明する。断面図 C S 5 には、光導波路材料 116 からなる膜を平坦化しパターニングする工程が示されている。まず、光導波路材料 116 からなる膜が CMP 工程によって平坦化されうる。次いで、周辺回路部 104 の上にある光導波路材料 116 からなる膜がエッティングによって除去されうる。これにより、光導波路 W G および、光導波路 W G から伸びた部分 C P が形成されうる。部分 C P は、光導波路 W G と同一材料で構成され、複数の光導波路 W G を相互に連結する。

#### 【 0030 】

断面図 C S 6 には、層間絶縁膜 113e、プラグ 120、導電膜 130 およびマイクロレンズ 150 を形成する工程が示されている。まず、層間絶縁膜 113e が形成され、層間絶縁膜 113e にビアホールが形成され、該ビアホールに導電材料を充填することによってプラグ 120 が形成される。プラグ 120 は、配線層 115c に配置された導電性パターン 500 等の導電性パターンに接続されるように構成されうる。プラグ 120 は、例えば、タンゲステンで構成されうる。次いで、プラグ 120 に接続されるようにパッドを含む導電膜が形成される。導電膜 130 は、例えば、アルミニウムで構成されうる。次いで、光導波路 W G に整合するようにマイクロレンズ 150 が形成される。マイクロレンズ 150 は、例えば、窒化シリコンで構成されうる。

#### 【 0031 】

次いで、半導体基板 101 (シリコン) とその上に酸化シリコン膜との界面順位をするため、水素ガスを含んだ雰囲気中で熱処理が行われうる。これにより、半導体基板 101 (シリコン) のダンギリングボンドが水素で終端される。この熱処理は、例えば 400 程度の温度で行われうる。この熱処理により、半導体基板 101 には熱応力が加わる。すると、仮に導電性パターン 500 が後述の設計規則を遵守して設計されていない場合、断面図 C S 7 に例示されるように、密着性が低下した配線層 115c の導電性パターン 500 と拡散防止膜 114c との界面を起点として拡散防止膜 114c が剥がれうる。

10

20

30

40

50

**【0032】**

拡散防止膜114cが剥がれると、それによってパーティクルが発生し、ウェハ内における固体撮像装置1001の歩留まりが低下しうる。また、拡散防止膜114cの下の導電性パターン500が露出すると、導電性パターン500を構成する材料によって製造装置が汚染されうる。以下で説明する制限ないし設計基準は、このような問題を解決するために有利である。

**【0033】****(第1実施形態)**

以下、本発明の第1実施形態を説明する。図3(a)に例示される導電性パターン500は、図1および図2に例示される固体撮像装置1001の配線層115、例えば周辺回路部104の配線層115に配置されうる。ここで、導電性パターン500は、複数の配線層115a~115cのうち少なくとも最上の配線層115cに配置されうる。導電性パターン500は、固定電圧(例えば、電源電圧、接地電圧)が印加されるパターンでありうるが、信号ラインに適用されてもよい。

10

**【0034】**

以下、導電性パターン500を周辺回路部104の最上の配線層115cに配置した場合において拡散防止膜114cの剥がれによる歩留まりの低下を評価した結果を説明する。なお、導電性パターン500が複数の配線層115a~115cのうち最上の配線層115cに配置された場合において拡散防止膜114cの剥がれが最も顕著に現れうる。したがって、導電性パターン500が最上の配線層115cより下の配線層115a、115bに配置された場合は、以下で説明される歩留まりよりも高い歩留まりが得られる。

20

**【0035】**

まず、予備実験として、図3(b)に示されるように主ライン501のみからなる導電性パターン520(補助ライン502を有しない導電性パターン)を使って主ラインの幅Waと主ライン501の間隔Saとの好ましい範囲を決定した。図5(a)には、配線層115cに配置された導電性パターン520の主ライン501の幅Waと拡散防止膜114cの剥がれによる歩留まりの低下との関係を評価した結果が示されている。この評価において、隣り合う主ライン501の間隔Saは140nmとされた。図5(b)には、配線層115cに配置された導電性パターン520における隣り合う主ライン501の間隔Saと拡散防止膜114cの剥がれによる歩留まりの低下との関係を評価した結果が示されている。この評価において、主ライン501の幅Waは2000nmとされた。図5(a)、図5(b)の評価結果より、主ライン501の幅Waを250nm以上かつ2000nm以下(0.25μm以上かつ2μm以下)とすることによって、拡散防止膜114cの剥がれによる歩留まりの低下を抑えることができることが分かる。

30

**【0036】**

図6には、補助ライン502を有しない導電性パターン520(図3(b))と補助ライン502を有する導電性パターン500(図3(a))とについて拡散防止膜114cの剥がれによる歩留まりの低下を評価した結果が示されている。この評価では、主ライン501の幅Waは2000nmとされ、主ライン501の間隔Saは140nmとされた。隣り合う主ライン501の間に複数の補助ライン502を配置することによって、図3(a)に例示されるように、補助ライン502を有する導電性パターン500は、破線を構成するように配置された複数のスリット510を有する。補助ライン502を有する導電性パターン500では、補助ライン502を有しない導電性パターン520に比べて著しく歩留まりが低下することが分かる。これは、補助ライン502を設けることによって、層間絶縁膜113cと拡散防止膜114cとの接触面積が小さくなり、逆に、密着性が低い補助ライン502と拡散防止膜114cとの接触面積が大きくなるからであると推察される。しかし、補助ライン502を設けないので、導電性パターンの抵抗値を低下させることができない。つまり、補助ライン502を設けると拡散防止膜114cの剥がれによって歩留まりが低下し、補助ライン502を設けないと導電性パターンの抵抗値を低下させることができないという課題が存在する。

40

50

## 【0037】

本発明者は、上記のような課題を導電性パターン500の占有率を適正化することによって解決した。図7には、補助ライン502の幅Wbが400nmより小さい条件の下で導電性パターン500の占有率と拡散防止膜114cの剥がれるによる歩留まり低下との関係を評価した結果が示されている。なお、固体撮像装置1001の歩留まりが良いことは、固体撮像装置1001の信頼性が良いことを意味する。占有率は、導電性パターン500の面積(AP)を正方形の領域10の面積(A)で除した値を占有率(=AP/A)として定義される。

## 【0038】

ここで、正方形の領域10は、(a)正方形の領域10が、第1方向に平行な第1辺11および第2辺12を有し、かつ、

(b)複数の主ライン501が、第1辺11に重なる第1ラインと、第2辺12に重なる第2ラインと、第1ラインと第2ラインとの間に配置された少なくとも1つのラインとを含み、かつ、

(c)正方形の領域10が、少なくとも1つの補助ライン502を含む、

ように定義される。図3(a)に示された例では、例えば、主ライン501aが第1辺11に重なる第1ライン、主ライン501dが第2辺12に重なる第2ラインであり、主ライン501b、501cが第1ラインと第2ラインとの間に配置された第3ラインである。

## 【0039】

換言すると、正方形の領域10は、第1方向に平行で第1ラインに重なる第1辺11、および、第1方向に平行で第2ラインに重なる第2辺12を有し、正方形の領域10の中に複数の補助ライン502の少なくとも1つを含むように定義される。

## 【0040】

一例において、正方形の領域10は、各辺が5000nm以上かつ20000nm以下の寸法を有しうる。また、一例において、第1ライン(501a)と第2ライン(501d)との間に配置された少なくとも2つのライン(501b、501c)の数は、5~15の範囲内(例えば10)でありうる。

## 【0041】

図7より、補助ライン502を設けることによる歩留まりの低下を抑える観点では、占有率は、0.9以下であることが好ましく、0.85以下であることが更に好ましいことが分かる。また、導電性パターン500の抵抗値を低下させる観点では、占有率の下限値は、より大きい値であることが好ましく、例えば、0.33、0.5、0.6、0.7または0.8とされうる。ここで、補助ライン502の幅Wbが小さければ小さいほど、歩留まりの低下が抑えられる。しかしながら、補助ライン502の幅Wbを小さくすることは、導電性パターン500の抵抗値を小さくするためには不利に作用する。よって、補助ライン502の幅Wbは、導電性パターン500の抵抗値を小さくする観点において、10nm以上とされ、好ましくは50nm以上とされ、更に好ましくは100nm以上とされうる。

## 【0042】

図7に示された評価において、占有率は、主ライン501の幅Wa、主ライン501の間隔Sa、補助ライン502の幅Wb、補助ライン502の間隔を種々の値にすることによって変更されている。ここで、導電性パターン500の抵抗値の低下およびレイアウト面積の縮小の観点において、主ライン501の幅Waは、250nm以上かつ2000nm以下であることが好ましく、400nm以上かつ2000nm以下であることが更に好ましい。また、導電性パターン500の抵抗値を低下させつつ拡散防止膜114cの剥がれによる歩留まりの低下を抑える観点において、複数の主ライン501の各々の幅Waは、複数の補助ライン502の各々の幅Wbより大きいことが好ましい。

## 【0043】

10

20

30

40

50

また、拡散防止膜 114c の剥がれによる歩留まりの低下を抑えつつレイアウト面積を縮小する観点において、主ライン 501 の間隔 Sa は、140 nm 以上かつ 500 nm 以下であることが好ましい。

#### 【0044】

また、導電性パターン 500 の抵抗値を低下させつつ拡散防止膜 114c の剥がれによる歩留まりの低下を抑える観点において、スリット 510 の面積は、 $560000 \text{ nm}^2$  以上かつ  $2000000 \text{ nm}^2$  以下であることが好ましい。ここで、スリット 510 は、複数の主ライン 501 における隣り合う任意の主ライン 501 と複数の補助ライン 502 における隣り合う任意の補助ライン 502 とによって囲まれる部分である。導電性パターン 500 における複数の主ライン 501 の数は、12 以上でありうる。

10

#### 【0045】

導電性パターン 500 は、複数の主ライン 501 および複数の補助ライン 502 のいずれかに接続されたプラグ（例えばプラグ 120）を含みうる。導電性パターン 500 は、該プラグを介して、導電性パターン 500 の下および／または上に配置された配線層および／またはパッド等の導電体に接続されうる。

#### 【0046】

##### （第2実施形態）

以下、本発明の第2実施形態を説明する。なお、第2実施形態として言及しない事項は、第1実施形態に従いうる。図8には、補助ライン 502 の幅 Wb が 400 nm 以上かつ 2000 nm 以下の条件の下で導電性パターン 500 の占有率 と拡散防止膜 114c の剥がれるによる歩留まり低下との関係を評価した結果が示されている。図8より、補助ライン 502 を設けることによる歩留まりの低下を抑える上で、占有率 は、0.75 以下であることが好ましく、0.73 以下であることが更に好ましいことが分かる。また、導電性パターン 500 の抵抗値を低下させる観点において、占有率 の下限値は、より大きい値であることが好ましく、例えば、0.33、0.5、0.6 または 0.7 とされうる。

20

#### 【0047】

図8に示された評価において、占有率 は、主ライン 501 の幅 Wa、主ライン 501 の間隔 Sa、補助ライン 502 の幅 Wb、補助ライン 502 の間隔を種々の値にすることによって変更されている。ここで、導電性パターン 500 の抵抗値の低下およびレイアウト面積の縮小の観点において、主ライン 501 の幅 Wa は、250 nm 以上かつ 2000 nm 以下であることが好ましく、400 nm 以上かつ 2000 nm 以下であることが更に好ましい。また、導電性パターン 500 の抵抗値を低下させつつ拡散防止膜 114c の剥がれによる歩留まりの低下を抑える観点において、複数の主ライン 501 の各々の幅 Wa は、複数の補助ライン 502 の各々の幅 Wb より大きいことが好ましい。

30

#### 【0048】

また、拡散防止膜 114c の剥がれによる歩留まりの低下を抑えつつレイアウト面積を縮小する観点において、主ライン 501 の間隔 Sa は、140 nm 以上かつ 500 nm 以下であることが好ましい。

40

#### 【0049】

また、導電性パターン 500 の抵抗値を低下させつつ拡散防止膜 114c の剥がれによる歩留まりの低下を抑える観点において、スリット 510 の面積は、 $560000 \text{ nm}^2$  以上かつ  $2000000 \text{ nm}^2$  以下であることが好ましい。ここで、スリット 510 は、複数の主ライン 501 における隣り合う任意の主ライン 501 と複数の補助ライン 502 における隣り合う任意の補助ライン 502 とによって囲まれる部分である。

#### 【0050】

##### （第3実施形態）

第3実施形態は、導電性パターン 500 の構成が第1および第2実施形態と異なる。図9には、本発明の第3実施形態の導電性パターン 500 が示されている。なお、第3実施形態として言及しない事項は、第1又は第2実施形態に従いうる。

50

**【0051】**

第3実施形態では、複数の補助ライン502は、複数の主ライン501のうち少なくとも2つの主ラインを相互に接続し他の主ラインを接続しないように第2方向に平行に延びた補助ラインを含む。例えば、補助ライン502a、502e、502fは、主ライン501aと主ライン501bとを接続するが、他の主ライン501c、501dを接続しないように、第2方向に平行に延びている。また、補助ライン502b、502d、502gは、主ライン501cと主ライン501dとを接続するが、他の主ライン501a、501bを接続しないように、第2方向に平行に延びている。

**【0052】**

他の観点において、複数の補助ライン502は、複数の主ライン501のうち第1グループを構成する主ラインを相互に接続する第1補助ラインと、複数の主ライン501のうち第2グループを構成する主ラインを相互に接続する第2補助ラインとを含む。例えば、主ライン501a、501bは、第1グループを構成し、補助ライン502a、502e、502fは、第1グループを構成する主ライン501a、501bを相互に接続する第1補助ラインである。また、主ライン501b、501cは、第2グループを構成し、補助ライン502cは、第2グループを構成する主ライン501b、501cを相互に接続する第2補助ラインである。ここで、第1グループを構成する主ライン501の少なくとも一部は、第2グループを構成する主ライン501と異なり、第1方向における第1補助ラインの位置と、第1方向における第2補助ラインの位置とが互いに異なる。

**【符号の説明】****【0053】**

500：導電性パターン、501（501a～501d）：主ライン、502（502a～502h）：補助ライン、Wa：主ラインの幅、Sa：主ラインの間隔、Wb：補助ラインの幅、Sb：補助ラインの間隔、101：半導体基板、102：光電変換部、103：画素アレイ部、104：周辺回路部、WST：配線構造、110：ゲート、111：層間絶縁膜、112：エッチングストップ膜、113（113a～113d）：層間絶縁膜、114（114a～114c）：拡散防止膜、115（115a～115c）：配線層、116：光導波路材料、WG：光導波路、10：正方形の領域、11：第1辺、12：第2辺

10

20

【図1】

【図2】

【図3】

(a)

(b)

【図4A】

【図4B】

【図4C】

【図4D】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2004-063702(JP,A)

特開2015-230929(JP,A)

特開2009-272568(JP,A)

特開2005-311015(JP,A)

特開2015-076533(JP,A)

特開2011-216865(JP,A)

特開2005-079207(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/335