## (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2018/025166 A1

(43) International Publication Date

08 February 2018 (08.02.2018)

(51) International Patent Classification:

*C30B 25/18* (2006.01)      *H01L 21/762* (2006.01)

*C30B 29/40* (2006.01)

(21) International Application Number:

PCT/IB2017/054668

(22) International Filing Date:

31 July 2017 (31.07.2017)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

62/370,169      02 August 2016 (02.08.2016)      US

62/378,126      22 August 2016 (22.08.2016)      US

15/662,201      27 July 2017 (27.07.2017)      US

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(71) Applicant: QMAT, INC. [US/US]; 2424 Walsh Avenue, Santa Clara, California 95051 (US).

(72) Inventor: HENLEY, Francois J.; 19101 Via Tesoro Ct, Saratoga, California 95070 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(54) Title: SEED WAFER FOR GAN THICKENING USING GAS- OR LIQUID-PHASE EPITAXY

FIG. 1A

(57) Abstract: Embodiments relate to fabricating a wafer including a thin, high-quality single crystal GaN layer serving as a template for formation of additional GaN material. A bulk ingot of GaN material is subjected to implantation to form a subsurface cleave region. The implanted bulk material is bonded to a substrate having lattice and/or Coefficient of Thermal Expansion (CTE) properties compatible with GaN. Examples of such substrate materials can include but are not limited to AlN and Mullite. The GaN seed layer is transferred by a controlled cleaving process from the implanted bulk material to the substrate surface. The resulting combination of the substrate and the GaN seed layer, can form a template for subsequent growth of overlying high quality GaN. Growth of high-quality GaN can take place utilizing techniques such as Liquid Phase Epitaxy (LPE) or gas phase epitaxy, e.g., Metallo-Organic Chemical Vapor Deposition (MOCVD) or Hydride Vapor Phase Epitaxy (HVPE).

## SEED WAFER FOR GaN THICKENING USING GAS- OR LIQUID-PHASE EPITAXY

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The instant nonprovisional patent application claims priority to U.S. Provisional Patent Appl. 62/370,169 filed August 2, 2016, and also to U.S. Provisional Patent Appl. 62/378,126 filed August 22, 2016, both of which are incorporated by reference in their entireties herein for all purposes.

### BACKGROUND

[0002] Incorporated by reference in its entirety herein for all purposes, is published U.S. Patent Appl. No. 2014/0197419.

### SUMMARY

[0003] Embodiments relate to fabricating a wafer including a thin, high-quality single crystal GaN seed layer serving as a template for forming additional GaN material. A bulk ingot of GaN material is subjected to implantation to form a subsurface cleave region. The implanted bulk material is bonded to a substrate having lattice and/or Coefficient of Thermal Expansion (CTE) properties compatible with GaN. Examples of such substrate materials can include but are not limited to AlN and Mullite. The GaN seed layer is transferred by a controlled cleaving process from the implanted bulk material to the substrate surface. The resulting combination of the underlying substrate and the GaN seed layer, can form a template for subsequent growth of additional overlying high quality GaN material. This growth of high-quality GaN can take place utilizing techniques such as Liquid Phase Epitaxy (LPE) or vapor phase epitaxy, e.g., Metallo-Organic Chemical Vapor Deposition (MOCVD) or Hydride Vapor Phase Epitaxy (HVPE). The substrate bearing the seed layer and the additional GaN grown thereon, may be incorporated into an electro-optical device such as a high-brightness light emitting diode.

### BRIEF DESCRIPTION OF THE DRAWINGS

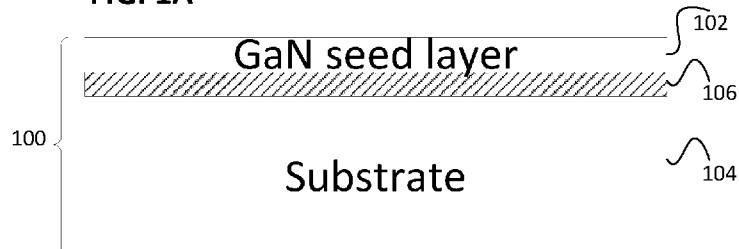

[0004] Figure 1A shows a simplified view of a seed wafer which may be prepared according to an embodiment.

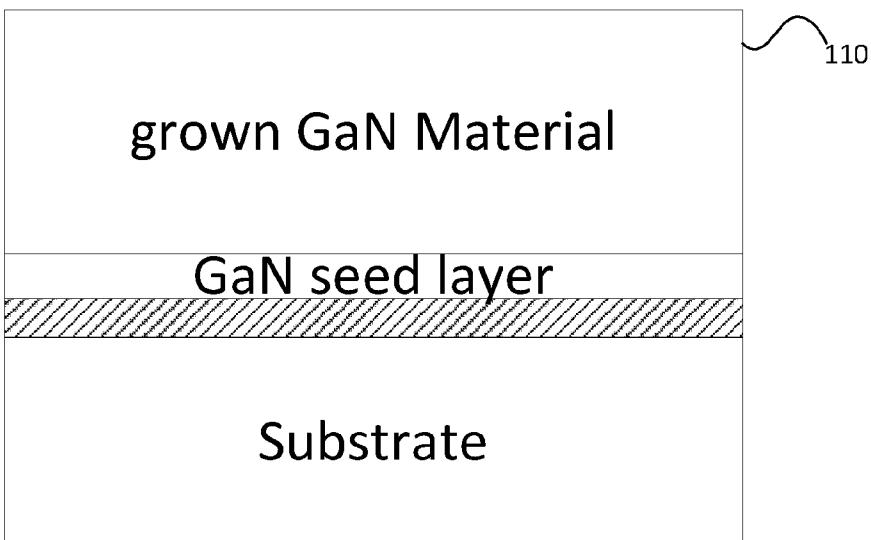

[0005] Figure 1B shows further processing of the seed wafer of Figure 1A to create an optoelectronic device.

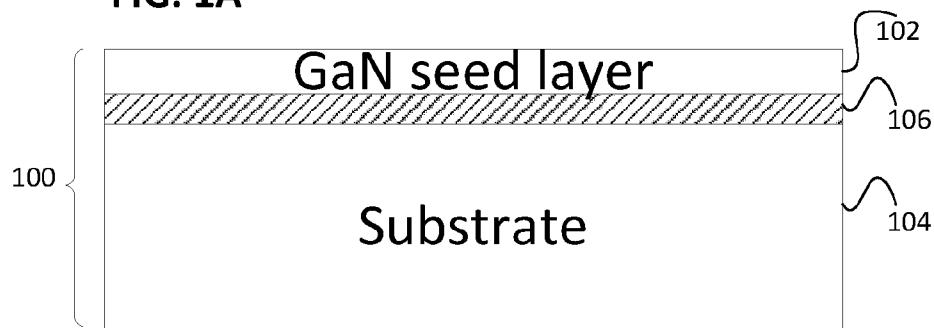

[0006] Figure 1C shows polar and non-polar forms of GaN.

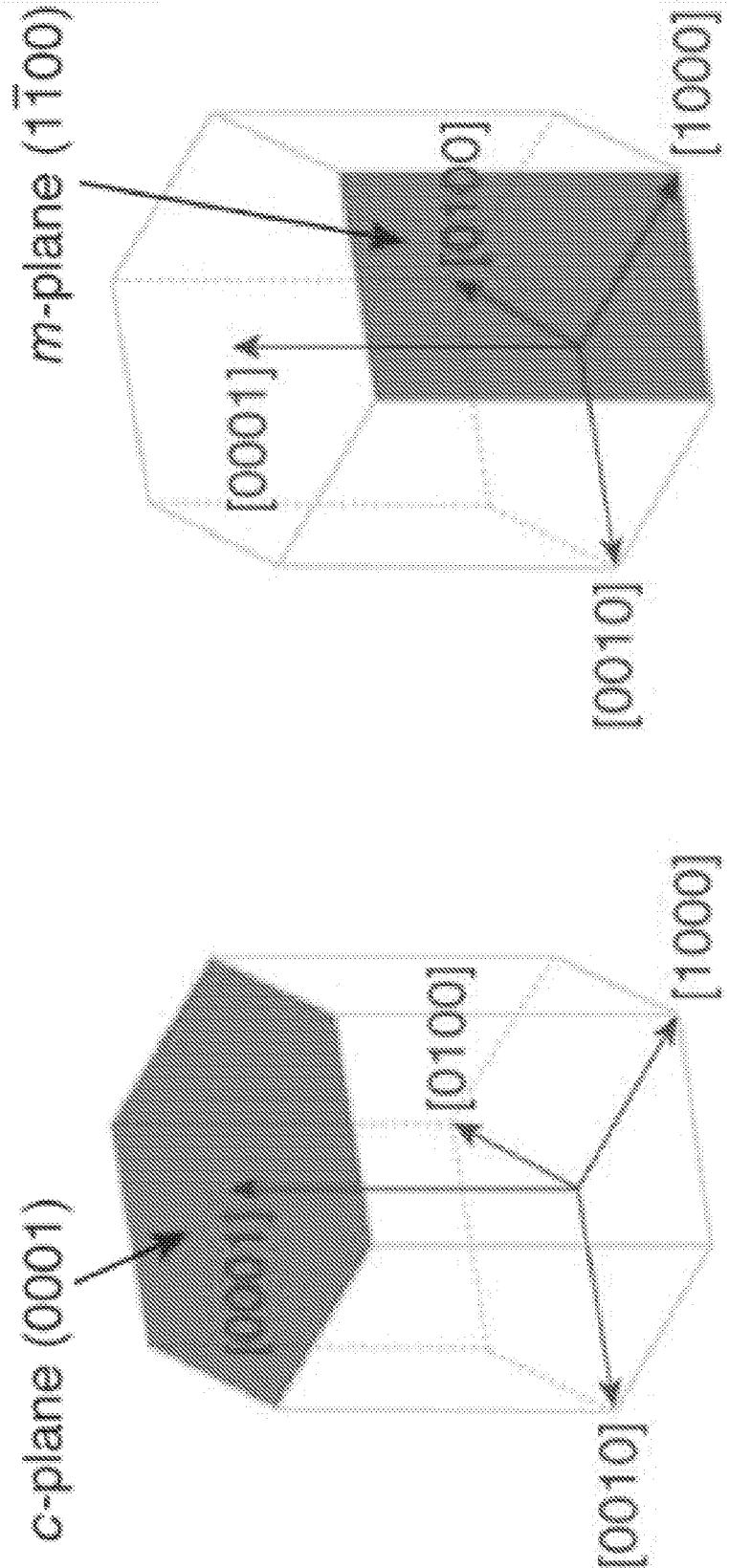

[0007] Figure 1D shows Ga and N faces of polar GaN.

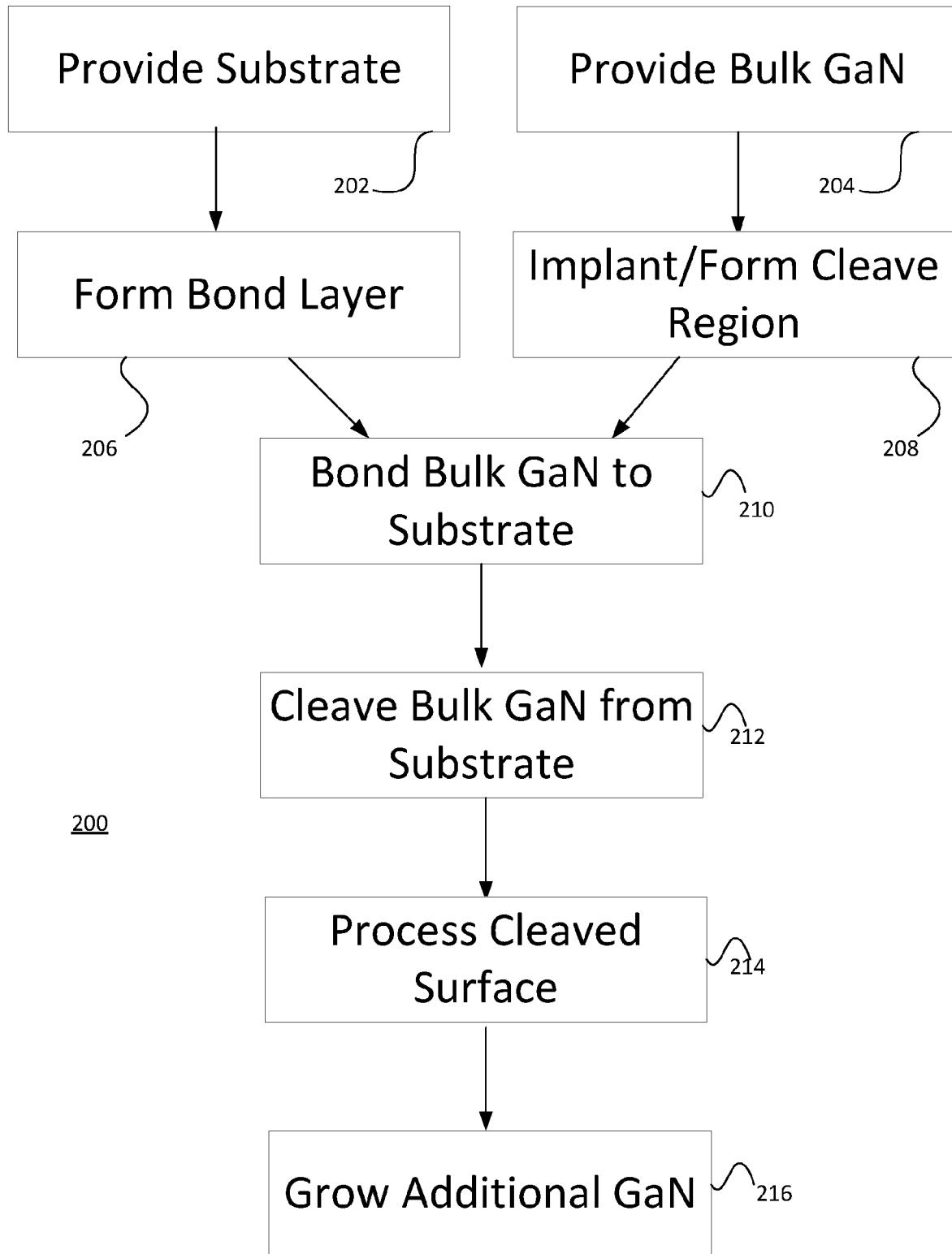

[0008] Figure 2A shows a simplified flow diagram of a process according to an embodiment.

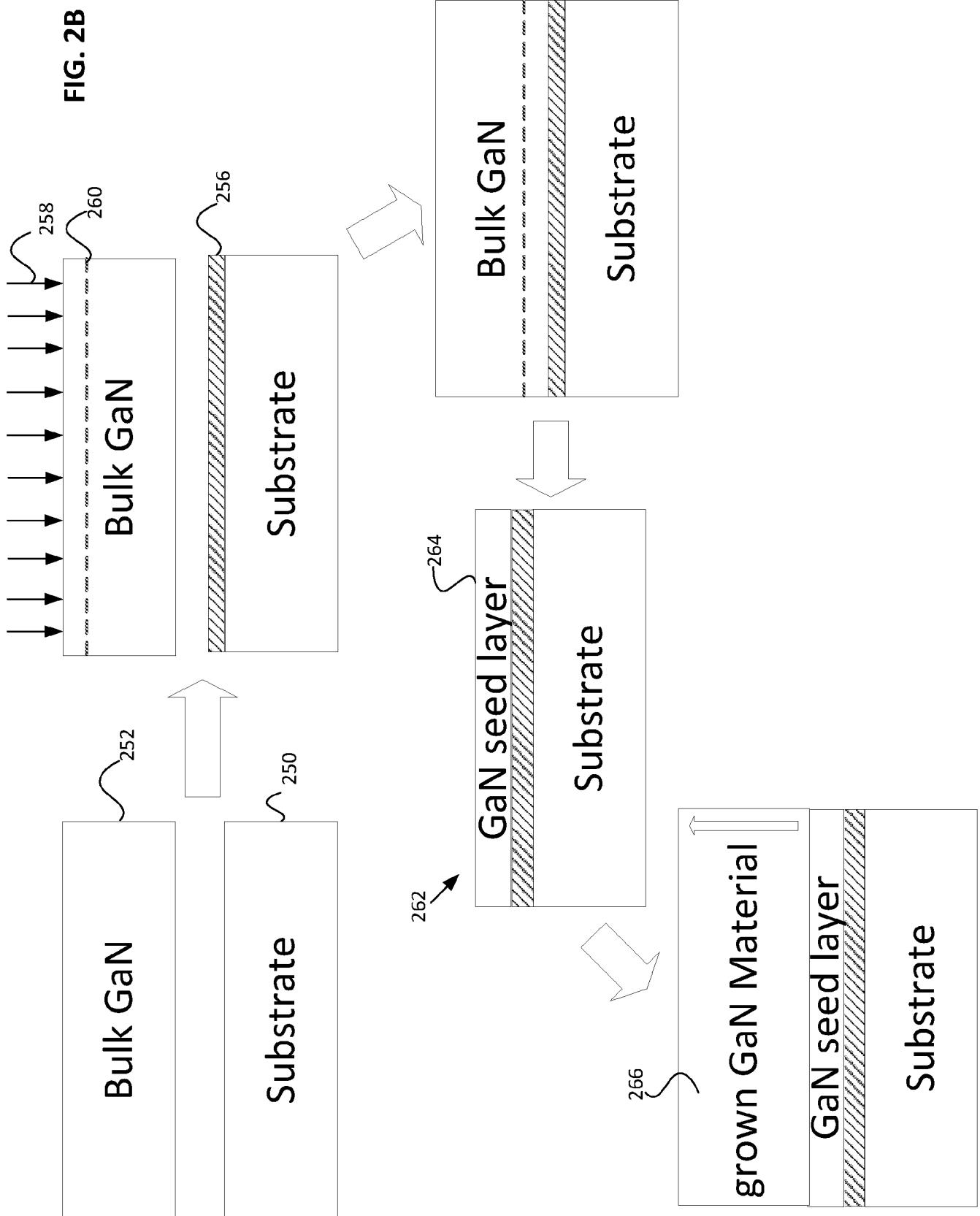

[0009] Figure 2B shows a simplified view of a process of GaN growth according to an embodiment.

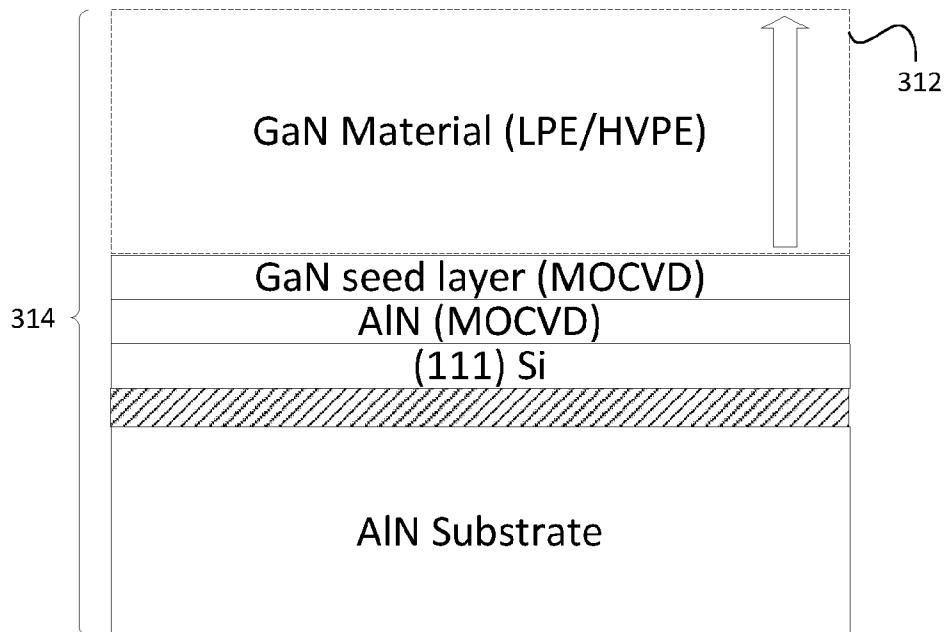

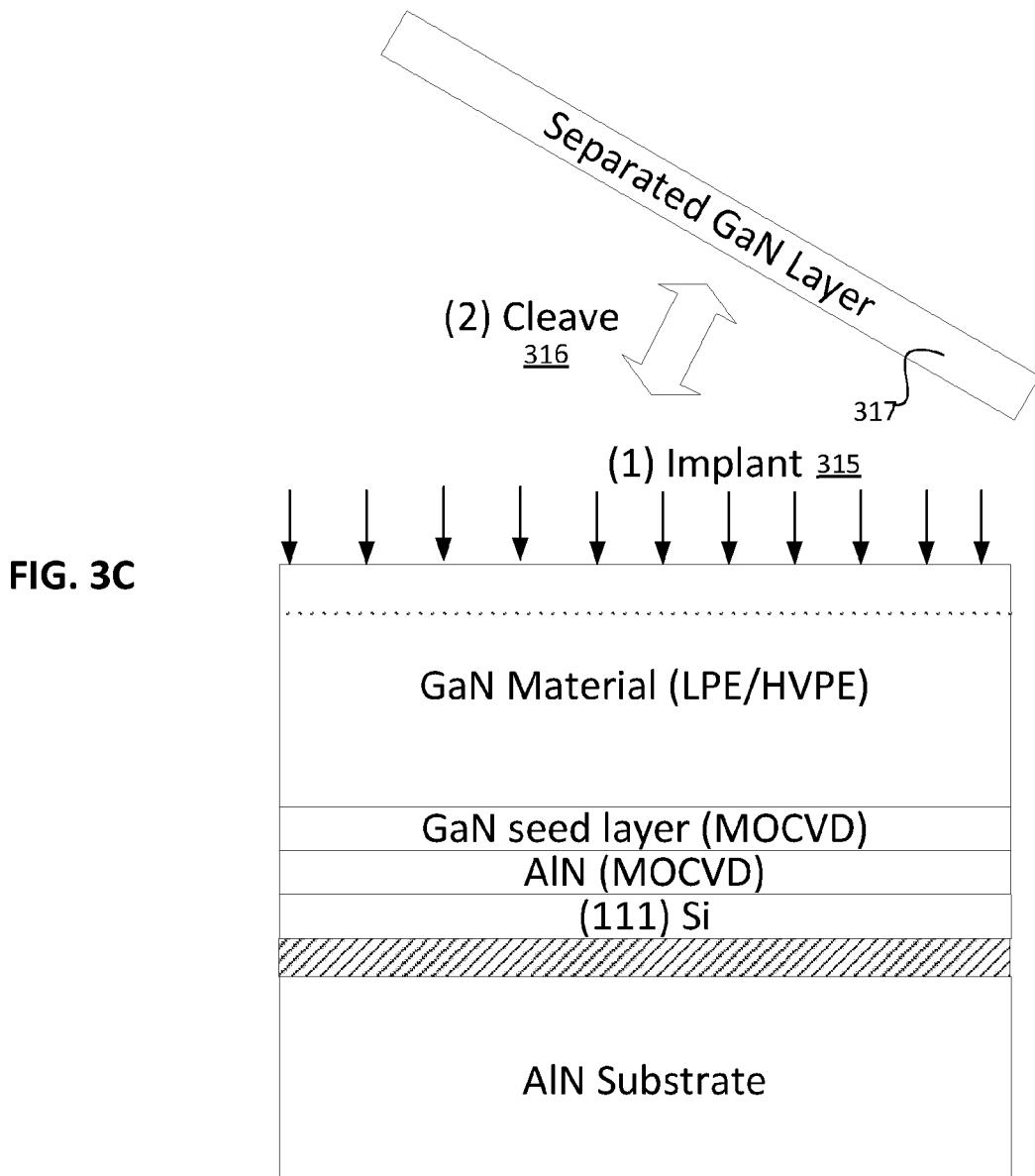

[0010] Figures 3A-C show a simplified view of a process according to an embodiment.

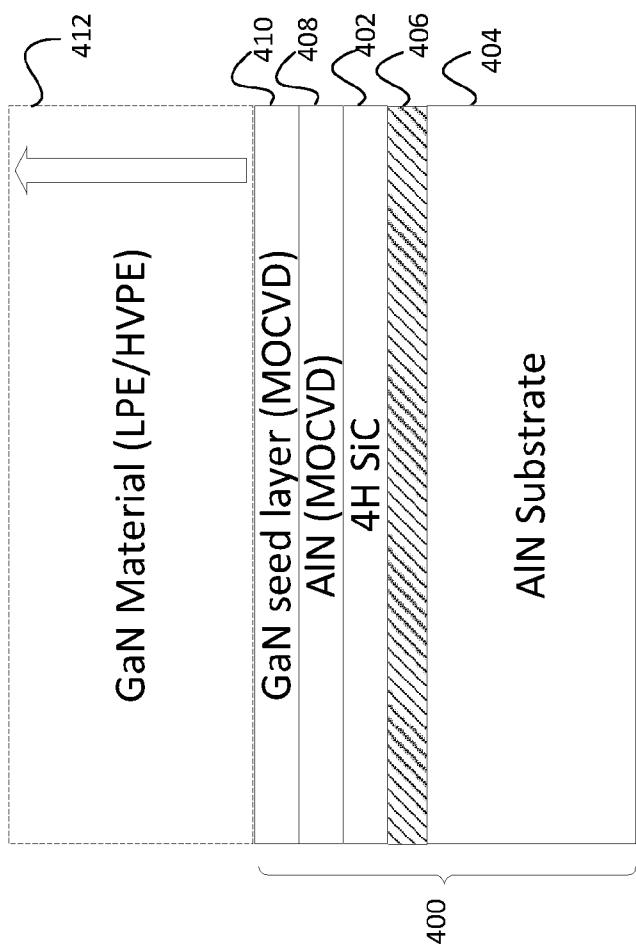

[0011] Figure 4 shows a simplified view of a process according to an embodiment.

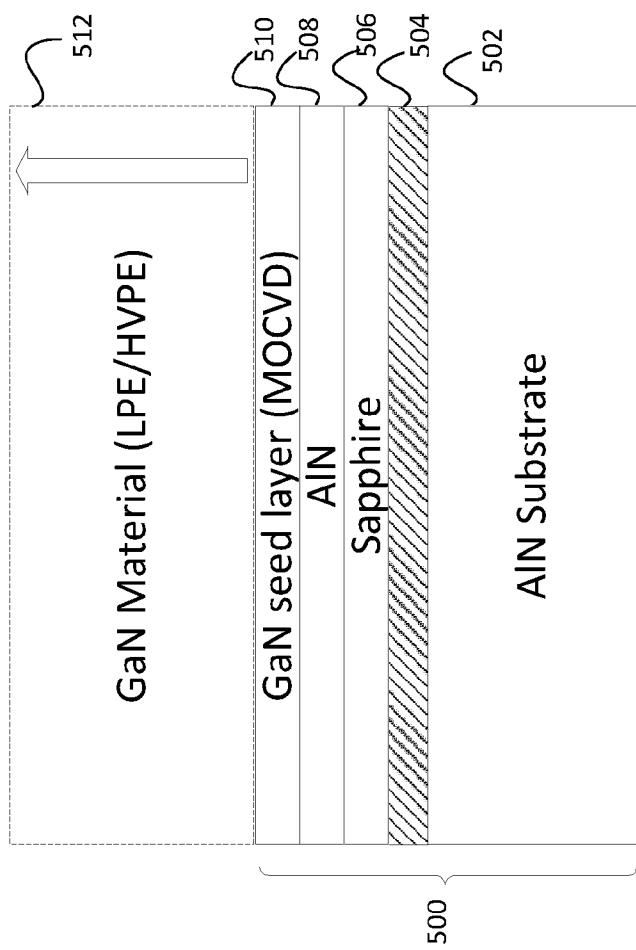

[0012] Figure 5 shows a simplified view of a process according to an embodiment.

#### DETAILED DESCRIPTION

[0013] Semiconducting materials find many uses, for example in the formation of logic devices, solar cells, and increasingly, illumination. One type of semiconductor device that can be used for illumination is the high-brightness light emitting diode (HB-LED). In contrast with traditional incandescent or even fluorescent lighting technology, HB-LED's offer significant advantages in terms of reduced power consumption and reliability.

[0014] An optoelectronic device such as a HB-LED may rely upon materials exhibiting semiconductor properties, including but limited to type III/V materials such as gallium nitride (GaN) that is available in various degrees of crystalline order. However, these materials are often difficult to manufacture.

[0015] One fabrication approach is illustrated in Figures 1A-B. There, a seed workpiece 100 is provided. This template blank comprises a thin, high quality seed layer 102 of GaN overlying a substrate 104 and separated therefrom by a dielectric layer 106, which typically comprises an oxide.

[0016] According to certain embodiments the substrate material may be selected to have Coefficient of Thermal Expansion (CTE) properties that are compatible with GaN material. Particular examples of possible candidates for substrate materials include AlN, Mullite, Molybdenum and Tungsten. An example table is given below.

| MATERIAL | CTE                                 |

|----------|-------------------------------------|

| GaN      | $5.5 \times 10^{-6} \text{ K}^{-1}$ |

|                                                            |                                     |

|------------------------------------------------------------|-------------------------------------|

| AlN                                                        | $5.2 \times 10^{-6} \text{ K}^{-1}$ |

| Mullite ( $3\text{Al}_2\text{O}_3 \bullet 2\text{SiO}_2$ ) | $5.4 \times 10^{-6} \text{ K}^{-1}$ |

| Molybdenum                                                 | $5.0 \times 10^{-6} \text{ K}^{-1}$ |

| Tungsten                                                   | $4.5 \times 10^{-6} \text{ K}^{-1}$ |

**[0017]** If the material can meet thermal, chemical and mechanical requirements, the substrate can comprise glass, quartz, metal or metal alloy, or other composites, and the like. In other embodiments, the substrate can comprise any homogeneous, graded, or multilayered material, or any combination of these. That is, the substrate can be made of almost any monocrystalline, polycrystalline, or even amorphous type substrate. Using engineered alloys, the base material can be adjusted to better match the GaN expansion coefficient. For example, a Molybdenum-Copper (Mo:Cu) alloy can be adjusted to better match bulk GaN.

**[0018]** As shown in Figure 1B, processing the exposed surface of the GaN seed layer of the seed template may allow for the formation of additional thickness 110 of high quality GaN material. That additional thickness of GaN material (with or without the accompanying substrate and/or dielectric material) may ultimately be incorporated into a larger optoelectronic device structure (such as a HB-LED).

**[0019]** Typically, a thickness on the order of a few hundred microns to a few centimeters may be grown over the seed layer by the epitaxial process. According to various embodiments, the additional GaN material may be grown to a significantly greater thickness than the underlying seed layer. For example, GaN growth thickness of a few millimeters to a few centimeters would allow wafering operations such as grinding, polishing and multi-wire wafer sawing to singulate the GaN material typically into separate free-standing substrates of 200-500um in thickness. According to certain embodiments, the seed layer has a thickness of between about 100-5000nm, and the additional GaN has a thickness of between about 0.01-10cm. In some embodiments the seed layer has a thickness of between about 0.5-2um, and the additional GaN has a thickness of between about 0.5-2cm. In particular embodiments the seed layer has a thickness of between about 0.5-1um, and the additional GaN has a thickness of between about 0.5-1cm

**[0020]** One approach for growing the additional high-quality GaN material upon the workpiece bearing the seed layer, is through Liquid Phase Epitaxy (LPE). Such LPE involves the growth of solid, single crystal GaN from a liquid solution. LPE may take place under different conditions such as temperature, pressure, solute, solvent, and concentration. Examples

are described by Mori et al, “Growth of GaN Crystals by Na Flux Method”, ECS Journal of Solid State Science and Technology, vol. 2, issue 8 (2013), and by Ehrentraut and Meissner, “Chapter 11 A Brief Review on the Na-Flux Method Toward Growth of Large-Size GaN Crystal”, from Technology of Gallium Nitride Crystal Growth, Ehrentraut, Meissner, and Bockowski, Eds. (2010), both of which are incorporated by reference in their entireties herein for all purposes.

**[0021]** LPE performed utilizing dilute solutions may offer certain benefits. One is to permit the application of lower growth rates for improved thickness control. Another may be to apply lower growth temperatures for improved structural perfection and stoichiometry and to reduce the detrimental effects of thermal expansion differences of substrate and epilayer. A third benefit of dilute LPE may be to reduce the risk of unwanted spontaneously nucleated crystallites.

**[0022]** LPE may offer certain benefits as compared to vapor phase techniques. In particular, from a thermodynamics perspective there is a significantly smaller difference in Gibbs free energy between reactants in the liquid phase and products in the solid phase, as compared to reactants in the vapor phase and products in the solid phase. Due to the near-equilibrium conditions occurring during layer deposition using LPE, the structural perfection of the layers may be superior and quasi-atomically flat surfaces and interfaces may be achieved. Also, generally excellent stoichiometry of the layers can be obtained.

**[0023]** Of course, embodiments are not limited to use of seed workpieces in connection with LPE, and vapor phase epitaxy can also be employed to thicken the GaN material from the initial seed layer. One example of vapor phase epitaxy is Metallo-Organic Chemical Vapor Deposition (MOCVD). Another example of vapor phase epitaxy is Hydride Vapor Phase Epitaxy (HVPE). Examples of HVPE approaches are described by Vladimir Dmitriev and Alexander Usikov, in “Chapter 1 Hydride Vapor Phase Epitaxy of Group III Nitride Materials”, from III-Nitride Semiconductor Materials, Imperial College Press., and by Motoki et al., “Preparation of 2-inch GaN Substrates”, Proc. 21st Century COE Joint Workshop on Bulk Nitrides IPAP Conf. Series 4 pp. 32–37, both of which are incorporated by reference in their entireties herein for all purposes.

**[0024]** Various types of GaN may be employed as the seed layer. For example, wurtzite GaN-based materials exists in both polar and non-polar forms. Figure 1C shows non-polar GaN exhibiting an m-plane (1100). GaN in its non-polar form is relatively expensive.

[0025] As also shown in Figure 1C, polar GaN exhibits a c-plane (0001). Figure 1D shows that polar GaN is characterized by having an N face and a Ga face.

[0026] Certain embodiments may feature the N face of the polar GaN seed layer bonded to the dielectric, with the Ga face of the GaN seed layer exposed for further processing (e.g., thickening by epitaxial techniques). This is because the Ga face has traditionally proven more amenable to the growth of high quality GaN than the N face.

[0027] It is emphasized, however, that other embodiments are possible. For example some applications (e.g., power electronics) may call for growth of GaN material from the N face, rather than from the Ga face. Incorporated by reference herein for all purposes are the following articles: Xun Li et al., "Properties of GaN layers grown on N-face free-standing GaN substrates", Journal of Crystal Growth 413, 81-85 (2015); A.R.A. Zauner et al., "Homo-epitaxial growth on the N-face of GaN single crystals: the influence of the misorientation on the surface morphology", Journal of Crystal Growth 240, 14-21 (2002). Accordingly, template blank structures of alternative embodiments could feature a GaN layer having an N face that is exposed, rather than a Ga face.

[0028] Described now in detail, are layer transfer processes which may be useful for example in fabricating a GaN-containing template blank structure such as is shown in Figure 1A. Specifically, particular embodiments transfer thin layers of material utilized in electronic devices (e.g., GaN for optoelectronic devices), from a donor bulk material to the substrate.

[0029] Figure 2A is shows a simplified flow of a process according to an embodiment. Figure 2B shows an overview of the exemplary process 200 according to an embodiment.

[0030] In a first step 202, a substrate 250 is provided. As described above, that substrate may have lattice and/or CTE properties compatible with the form of GaN that is to be used. Possible candidate substrate materials comprise AlN and Mullite.

[0031] In a second step 204, bulk GaN 252 is provided. The bulk GaN may be a crystal of polar or non-polar GaN. In a particular embodiment the bulk GaN (and/or the substrate) may be 2" wafers, but they are not limited to being of any specific size or dimension.

[0032] In a third step 206, the substrate is prepared to receive the GaN. This may involve the formation of an oxide bond layer 256. Although not shown, the surface of the bulk GaN 252 to be bonded may also be treated to have a bond layer added or processed to be more compatible with the bond step 210.

[0033] In particular embodiments, this bond layer can be formed by exposure to oxidizing conditions. In some embodiments this bond layer may be formed by the addition of oxide, e.g., as spin-on-glass (SOG), or other spin on material (e.g., XR-1541 hydrogen silsesquioxane electron beam spin-on resist available from Dow Corning), and/or SiO<sub>2</sub> formed by Plasma Enhanced Chemical Vapor Deposition (PECVD) or oxide sputtering techniques.

[0034] In a fourth step 208, the bulk GaN is subject to implantation of particles 258 (e.g., hydrogen ions) to form a subsurface cleave region 260. In some embodiments this cleave region may lie at a depth of between about 10-20 um underneath the surface of the bulk material. In other embodiments the cleave region may lie at a depth of between 0.05-2um underneath the surface of the bulk material.

[0035] Forming a cleave region may depend upon factors such as the target material, the crystal orientation of the target material, the nature of the implanted particle(s), the dose, energy, and temperature of implantation, and the direction of implantation. Such implantation may share one or more characteristics described in detail in connection with the following patent applications, all of which are incorporated by reference in their entireties herein: U.S. Patent Application No. 12/789,361; U.S. Patent Application No. 12/730,113; U.S. Patent Application No. 11/935,197; U.S. Patent Application No. 11/936,582; U.S. Patent Application No. 12/019,886; U.S. Patent Application No. 12/244,687; U.S. Patent Application No. 11/685,686; U.S. Patent Application No. 11/784,524; U.S. Patent Application No. 11/852,088.

[0036] In certain embodiments the thickness of material of the implanted surface of the donor is cleaved from the bulk material using the cleave region formed by using relatively high H<sup>+</sup> proton implant energies in the MeV range. This produces a detached layer of semiconductor material having a thickness of between about 10-20 um. In other embodiments using bonded layer-transfer, thinner cleaved layers of 0.05-1 um may be used. For producing GaN cleaved films of these thicknesses, lower H<sup>+</sup> proton implant energies ranging from approximately 5-180keV may be used. For example, 40keV H<sup>+</sup> proton energy would produce a GaN cleaved film of approximately 0.25um in thickness. It is understood that H<sub>2</sub><sup>+</sup> can also be utilized for this implant step. In such cases, the dose rate would be doubled while the effective H<sup>+</sup> energy would be halved. For example, a80keV H<sub>2</sub><sup>+</sup> implant could have the same detached layer thickness (range) than a 40keV H<sup>+</sup> implant. However, the dose rate would be double the H<sup>+</sup> dose rate for the same implant current.

[0037] In step 210, bonding is performed by placing the oxide-bearing surface of the substrate in contact with the implanted face of the bulk GaN, followed by heating. Other acts may be performed at this time, such as touch polishing, plasma treatment and cleaning prior to bonding.

[0038] Step 212 shows the subsequent controlled cleaving process to release the bulk GaN from the substrate. Specifically, the application of energy results in cleaving along the cleave plane in the donor bulk GaN material. This cleaving produces the desired GaN seed template blank 262 bearing the cleaved thin GaN seed layer 264.

[0039] The cleaving may take place utilizing the application of various forms of energy, and may exhibit one or more of the characteristics disclosed in any of the patent applications incorporated by reference above. In a particular embodiment, this cleaving may take place utilizing a compressional force applied in the form of a static gas in a high pressure chamber containing the implanted bulk material. The application of energy in various forms to accomplish cleaving according to particular embodiments is also described in the U.S. Patent No. 6,013,563 incorporated by reference herein for all purposes.

[0040] As described in further detail below, a cleaving process may itself comprise one or more steps. For example, cleaving may comprise initiation performed under certain conditions, followed by propagation performed under different conditions.

[0041] Returning to Figure 2A, step 214 involves further steps, such as treatment of the surface of the seed GaN layer. Such treatment may reduce roughness in the exposed surface, making it more amenable to addition of high quality GaN as discussed earlier in connection with FIG. 1B. Surface treatment can involve thermal, chemical, and/or plasma treatments.

[0042] In step 216, Figure 2A further shows the growth of additional GaN 266 over the GaN seed layer. As mentioned previously, this GaN growth can comprises liquid phase epitaxial growth and/or vapor phase epitaxial growth.

[0043] The above sequence of steps provide a method according to certain embodiments of the present invention. Other alternatives can also be provided where steps may be added, one or more steps may be removed, or one or more steps may be provided in a different sequence. For example in an alternative embodiment, the bulk GaN could itself include a bonding material, with particle implantation taking place before or after formation of that bonding material.

[0044] It is further noted that various embodiments could involve the use of bond-and-release systems, in which the GaN seed layer and substrate are later separated from each other. Additional description of such bond and release approaches are described in U.S. Patent Appl.

No. 15/186,185, filed June 17, 2016, now published as U.S. Patent Publication No. 2016/0372628 and incorporated by reference herein for all purposes.

**[0045]** Methods according to embodiments of the invention can be used in a variety of applications. Examples include but are not limited to optoelectronic devices, semiconductor device packaging, photovoltaic cells, MEMS devices, and others.

**[0046]** According to certain embodiments, a free standing film may be separated from a bulk material. In one embodiment, a free standing layer of semiconductor material such as single crystal GaN, having a thickness of 10  $\mu\text{m}$  or greater, may be cleaved from a bulk ingot utilizing high energy implantation. Cleaving the ingot in this manner substantially reduces the amount of semiconductor material that is otherwise lost to the kerf in a conventional blade cutting process. In addition to enhancing the efficiency of the cleave action, managing parameters such as ion dose and temperature profile is also important to limit and control the radiation damage to the material that is separated. The resulting cleaved free standing film may be particularly suited for use in illumination, for example LEDs or laser devices.

**[0047]** For purposes of this disclosure, a "free standing film" or "free standing layer" is defined as a film of material that can maintain its structural integrity (i.e. not crumble or break apart), without being in contact with a supporting member such as a handle or transfer substrate. Typically, very thin films (for example GaN films thinner than about 5-10  $\mu\text{m}$ ) are unable to be handled without breaking. Conventionally, such thin films are manipulated using a supporting structure, which may also be needed to create the thin film in the first place. Handling of thicker films (i.e. GaN films having a thickness of between 10-50  $\mu\text{m}$ ) may be facilitated by the use of a support, but such a support is not mandatory. Accordingly embodiments of the present invention relate the fabrication of free standing films having a thickness of greater than 10  $\mu\text{m}$ . Also for purposes of the following disclosure, the terms "substrate" and "tile" are employed interchangeably.

**[0048]** Embodiments in accordance with the present invention are not limited to forming free standing films. Alternative embodiments may involve the formation of films supported by a substrate. Moreover, irrespective of whether the films used in various applications are truly free-standing or supported with handling or transfer substrates during processing, processed devices are usually mounted onto a mechanical interface such as a metal base for the final application as an integral part of a lighting module.

[0049] Also for purposes of the following disclosure, "bulk material" refers to a material present in bulk form. Examples of such bulk material include a substantially circular ingot or boule of single crystal GaN as grown, or a grown single crystal GaN ingot having sides shaved to exhibit other than a substantially circular cross-sectional profile. Still other examples of bulk materials are described herein.

[0050] In a specific embodiment, the present method may be applied successively to transfer multiple layers from a single ingot, e.g., GaN boule or a thickness of GaN mounted onto a suitable substrate such as a metal base substrate. That is, the method can be repeated to successively cleave slices (similar to cutting slices of bread from a baked loaf) according to a specific embodiment. Of course, there can be other variations, modifications, and alternatives.

[0051] As mentioned previously, various surface treatment processes may be employed at one or more stages. According to certain embodiments, the exposed surface of material grown from a substrate is polished to reduce roughness resulting from any cleaving process. The combination of the polished cleaved material and the underlying substrate may then be transferred as an added value material for further processing and incorporation into an optoelectronic device.

[0052] While the above description references surface treatment utilizing polishing, this is not required in all embodiments, and alternatives could employ polishing in combination with other surface treatment, or even surface treatment that does not involve polishing. For example, according to some embodiments the surface treatment could include an anneal. In particular embodiments the anneal could take place in the presence of an overlying cap layer, for example comprising AlN or SiO<sub>2</sub>. The annealing could be performed in a furnace (e.g. typically where the cap layer is present), or could be performed within a MOCVD chamber (e.g. where no cap layer is present).

[0053] Surface treatment (e.g. comprising polishing, annealing, and/or cap layer formation) could also include etching processes. Examples of etching processes can include but are not limited to plasma etching, and/or chemical etching. Chemical assisted ion beam etching (CAIBE) is one example of a type of chemical etching. Wet chemical etching is another example of chemical etching.

[0054] The above sequence of steps provide a method according to certain embodiments of the present invention. Other alternatives can also be provided where steps may be added, one or more steps may be removed, or one or more steps may be provided in a different sequence. For

example in an alternative embodiment, substrate bonding could take place after the cleaving, with the cleaving resulting in a free standing film in turn bonded to the substrate.

[0055] No specific crystal orientation is required of the donor bulk GaN material. Thus a donor comprising a GaN ingot may exhibit one of the typical crystalline orientations, for example (0001).

[0056] As mentioned above, materials utilized during a layer transfer process may be specifically selected according to their properties, including their thermal properties. Thus substrates and/or layers may comprise material(s) having a coefficient of thermal expansion (CTE) compatible with conditions expected to be encountered during the process. For example, the linear coefficient of thermal expansion of GaN ( $\alpha_{\text{GaN}}$ ) is about  $5.5 \times 10^{-6} \text{ K}^{-1}$ .

[0057] Examples of such materials having CTE compatibility with GaN may include certain glasses. Other examples of materials having CTE compatibility with GaN can include but are not limited to, metal or metal alloys. Possible suitable metals may include Molybdenum or Tungsten, while candidate metal alloys may comprise molybdenum, such as copper molybdenum alloys or molybdenum tungsten alloys.

[0058] Embodiments are not specifically limited to particular materials mentioned so far. Examples of various layers which may be used can include barrier layers, thermo-compression bond layers, a mirror layer, and the GaN buffer and device growth layers. Barrier layers are layers that protect the integrated films from contamination, inter-mixing and other deleterious effects during thermal processing such as the GaN device layer formation step(s). Such layers can include AlN, HfN, TiB<sub>2</sub>, Pt, Ta among other well known barrier layer materials. Other such layers serving as encapsulation layers may also be desirable to enhance surface properties such as porosity and roughness. For example, a nickel layer (polished or not depending on the specific application) may serve as an encapsulating layer on a Molybdenum alloy substrate to provide good bond yield and uniform surface characteristics. Other coating layers can include but are not limited to nickel-gold alloys, ruthenium, chromium or silver.

[0059] Subsequent steps to grow the devices from the GaN layer (e.g., in Figure 1B) may involve metal-organic chemical vapor deposition (MOCVD) of GaN at roughly 1000 °C for 2-3 hours. Accordingly, the use of appropriate buffer and/or barrier layers may ensure thermal survivability of desired features.

[0060] Together, the layers form an engineered GaN growth substrate, and may achieve one or more of the following possible features and potential benefits for the HB-LED device manufacturers.

[0061] One possible benefit is a reduction in lattice mismatch. In particular, this benefit may be achieved by using a thin, high-quality GaN layer for epitaxial growth.

[0062] Another possible benefit is a low incidence of threading dislocation density (TDD)/Defects. According to embodiments, these defects may be reduced to at or below Free Standing GaN levels, using a thin, high-quality GaN layer.

[0063] Still another possible benefit is a reduction in CTE-Mismatch. Use of a CTE-matched substrate engineered to match the GaN layer through the epitaxial growth temperature, may thereby eliminate CTE mismatch induced layer stresses, cracks and defects.

[0064] Yet another possible benefit is the realization of high electrical and thermal conductivity. The use of a metal substrate and thermally and electrically conductive internal layers, may allow the growth substrate to be used as the mounting substrate for the HB-LED package/luminaire in the final vertical LED structure. High thermal and electrical conductivity allows higher External Quantum Efficiency (EQE), higher Wall Plug Efficiency (WPE), and may eliminate certain back-end manufacturing steps. Proposed embodiments may allow vertical LED contact structure with desired thermal conductivity of the multi-stack substrate exceeding 5-30 W/cm<sup>2</sup>-K, and electrical resistance of the multi-stack substrate (related to the electrical conductivity) may be less than 1x10<sup>-4</sup> Ohm-cm<sup>2</sup>.

[0065] Embodiments may offer a possible benefit of enhanced optical efficiency. In particular, the integration of an internal reflector under the GaN growth film, may allow the use of the substrate within the final HB-LED package, with further savings in back-end manufacturing steps such as mirror layer growth and lift-off/bond steps. A reflection layer can comprise a metal such as silver, gold, aluminum. Use of a thin silver layer, for example, could support a reflectivity exceeding 75% in the 400-500nm spectral range, which may be a desirable feature to achieve high external quantum efficiency.

[0066] The reflection layer can comprise a dielectric layer stack. Such a dielectric layer stack may be made electrical conductive, in a manner that balances conductivity with reflective properties. Examples of parameters which can be controlled to form a dielectric layer stack exhibiting the desired properties can include but are not limited to, a number of layers in the

stack, a thickness of layers in the stack, specific materials included in the stack, and/or the presence of dopant(s).

[0067] Still another possible benefit is the ability to use a smaller device size. Embodiments may offer a low droop and thus efficient devices can be operated at higher current density. With up to 10X or even more devices able to be made on a substrate, epitaxial and packaging costs can be substantially lowered.

[0068] Embodiments may also be employed for GaN-based electronic devices. In such embodiments, the layers can be modified with a thermally conductive, electrically insulating intervening layer below the GaN device layer. In a particular embodiment, the integrated mirror layer of an LED embodiment could be substituted with a thin (e.g. 20-50 um) insulating layer that would allow good GaN electronic device operation but also allow good thermal heat transfer. Such an intervening layer can be a material having good thermal conductivity and high electrical resistivity. Depending on the desired performance and cost targets, materials such as AlN (Aluminum Nitride) and Sapphire can be suitable.

[0069] One key application of the layer-transfer technology, may be to fabricate a functionally equivalent substrate to a free-standing GaN wafer for HB-LED and laser diode device manufacturing. Possible commercial advantages achieved in using free-standing GaN may include but are not limited to (i) better HB-LED performance (up to 100% higher in lumens/watt) and (ii) lower cost of epitaxial device layer manufacturing due to 30-50% less epitaxial growth chamber time by the elimination of graded buffers. In addition, the more efficient device offers substantial savings in packaging as well as competitive differentiation.

[0070] The use of conventional free-standing GaN substrates in device manufacturing is currently limited by cost and size limitation (e.g. 2" and 4" diameters presently). Both of these limitations are considered fundamental and strongly linked to the present methods of manufacturing GaN crystals by hydride vapor phase epitaxy (HVPE) or ammonothermal (Ga or GaN in supercritical ammonia/mineralizer) growth approaches.

[0071] HVPE and ammonothermal growth methods are slow and costly. Higher quality GaN usually necessitates less than 100-200 microns per hour using HVPE. Ammonothermal growth may be slower, but with somewhat better crystal quality.

[0072] As the GaN bulk crystal is grown conventionally, defects such as dislocations generally work themselves out of the crystal by edge termination. This strongly ties the crystal diameter to the rate of dislocation reduction, and hence the HVPE and ammonothermal growth methods are

generally limited to small crystal diameters for making high-quality GaN. Defect levels achievable on commercially available bulk or free-standing GaN (FS-GaN) 2" substrates are about  $10^4$ - $10^6$  defects/cm<sup>2</sup>.

[0073] Because of the slow growth rate and use of wiresaws to fabricate these substrates, FS-GaN prices are currently in the \$1,000-\$2,000 (2" wafer) and \$3,000-\$5,000 (4" wafer). Because of the high cost of these substrates, their use is limited to R&D (High-Electron Mobility Transistor (HEMT) and optoelectronic) as well as blue/UV laser diode manufacturing.

[0074] Although HB-LED device performance has been shown to improve as much as 100% using these higher quality substrates by eliminating the "droop effect", their high cost and limitation to small wafer diameters has prohibited their use. The use of high-quality GaN as a growth medium reduces or eliminates device "droop" (brightness efficiency drops with increasing current), a parasitic device characteristic that increases device area to achieve higher lumens/W efficiency and control areal power dissipation. The tailing off or droop of the emission power limits efficiency to about 100-120 lumens/watt for sapphire substrate-based devices but FS-GaN substrate HB-LED devices have been shown to yield over 200 lumens/watt.

[0075] This low-droop translates to an ability to increase the current density that in turn will lead to as much as a 10X reduction in the size of HB-LED devices fabricated on substrates utilizing high-quality GaN material according to embodiments.

[0076] Thus as indicated above, embodiments may benefit the HB-LED industry in numerous areas, including but not limited to cost, packaging, and reliability.

[0077] It is noted that certain embodiments previously described (e.g., in connection with Figure 2B) utilize implantation of particles to form a cleave region at a depth into the workpiece. In some embodiments, accelerated particles could be directed in a manner (e.g. energy) calculated to form a cleave region at or near an interface between additional material and an underlying workpiece. The presence of the implanted particles in a region at or near this interface, could ultimately reduce an amount of applied energy required to initiate and/or propagate cleaving in a cleave region located proximate to the interface.

[0078] And while the above description has focused upon forming an additional material on a workpiece comprising a single crystal seed GaN layer to form a multi-layer structure, this is also not required. According to alternative embodiments, the additional material could be present on a workpiece. One example of such additional material is single-crystal SiC, (111) silicon, single-

crystal and metal films where the material can serve as a seed layer for GaN heteroepitaxial growth.

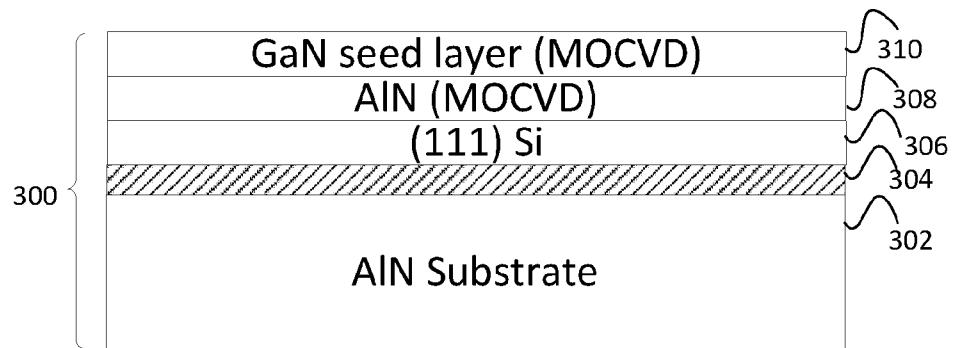

[0079] Specifically, Figure 3A shows a simplified view of an embodiment of a template workpiece featuring (111) single crystal silicon. Relative thicknesses of the various layers shown in Figure 3A are not drawn to scale.

[0080] The template workpiece 300 of Figure 3A comprises a polycrystalline AlN substrate 302 bearing an oxide bonding layer 304. That oxide bonding layer may have a thickness, for example, of between about 200-400 nm.

[0081] Attached to the oxide bonding layer 304 is a single crystal silicon layer 306. This single crystal silicon layer has a (111) crystal plane orientation, which may have an intentional off-cut angle of between about 0.1-0.5°.

[0082] The single crystal silicon layer may have a thickness of between about 100-200nm. It may be formed on the template substrate by separation from a high quality ingot utilizing a layer transfer process, for example in certain embodiments a controlled cleaving process as is described herein.

[0083] In one possible embodiment, a thin layer of AlN 308 is in turn formed over the single crystal silicon layer. This AlN layer is formed by MOCVD to a thickness of between about 100-200nm. Capping the silicon, it serves as a precursor layer to the GaN seed layer that is to be grown. Other low-temperature nucleation layer compositions that serve to promote high-quality GaN growth can also be utilized. Incorporated by reference herein for all purposes, is Pinnington et al., “InGaN/GaN multi-quantum well and LED growth on wafer-bonded sapphire-on-polycrystalline AlN substrates by metalorganic chemical vapor deposition”, Journal of Crystal Growth 310 (2008) 2514–2519.

[0084] In particular, Figure 3A further shows a GaN seed layer 310 overlying the AlN capping layer. That GaN seed layer is grown at high quality overlying the AlN layer 308, also utilizing MOCVD techniques.

[0085] The surface of the high quality GaN layer offered by the workpiece, in turn serves as a template for the growth of additional GaN material to achieve substantial thicknesses. This is shown in Figure 3B, where further high quality GaN material 312 is grown to greater thickness over the GaN seed layer utilizing techniques such as LPE and/or HVPE.

[0086] In certain embodiments, additional high quality GaN material grown by LPE would be expected to have a defect density of  $\sim 1 \times 10^6 - 5 \times 10^7 \text{ cm}^{-2}$ . According to some embodiments,

additional high quality GaN material grown by HVPE would be expected to have a defect density of  $\sim 1 \times 10^6$  -  $1 \times 10^7$  cm $^{-2}$ .

[0087] The multi-layer workpiece 314 of Figure 3B, can in turn serve as a donor for separation of high quality GaN layers to be incorporated into electronic devices (such as HB-LEDs and power electronic devices). As shown in Figure 3C, this may be accomplished by successive implant 315 and controlled cleaving 316 to produce separated GaN layer 317.

[0088] In some embodiments that separated GaN layer may be free standing. In other embodiments that separated GaN layer may be bonded to a temporary handle substrate or permanent target substrate.

[0089] It is noted that (111) single crystal silicon on polycrystalline AlN offers a good match in CTE with the overlying grown GaN. Referring to Table 1, the CTE match, dominated by the polycrystalline AlN base substrate would be about 0.2ppm/C. This would allow a few hundred microns of additional GaN to be grown without cracking. The single crystal silicon also offers workable lattice matching (~17%) with the overlying grown GaN.

[0090] The general method to calculate the critical thickness  $h_c$  of GaN grown on a base substrate with a net differential CTE mismatch utilizes critical energy release rate to delaminate thin-films by buckling. Such methods are explained by Hutchinson and Suo in “Mixed Mode Cracking in Layered Materials”, Advances in Applied Mechanics, Vol. 29, pp. 63-187 (1992), which is incorporated by reference in its entirety herein for all purposes.

[0091] Using the thermal mismatch generated film stress as the driving energy ( $\sigma = E \Delta\alpha \Delta T$ , where E=Young’s Modulus,  $\Delta\alpha$  = CTE mismatch and  $\Delta T$  = temperature differential), the equation linking this driving energy to the critical thickness characterizing the onset of film cracking/delamination is:

$$G = 0.5 (1-v^2) \sigma^2 h/E \quad (1)$$

Where G is the energy release rate,  $\sigma$  is the thermal mismatch generated film stress, h is the film thickness and E is Young’s modulus.

[0092] At the onset of buckling, the energy release rate will equal or exceed the critical energy release rate for the GaN film. This critical energy  $G_c$  is about 2 J/m $^2$ . Equation (1) can be rewritten for this condition to solve for the critical thickness  $h_c$  as:

$$h_c = 2 E G_c / ((1-v^2) \sigma^2) \quad (2)$$

[0093] Using E=300GPa for GaN,  $\nu = 0.38$  for the material parameters and  $\Delta T = 1000^\circ\text{C}$  as the temperature differential between growth and room temperature, a  $0.2\text{ppm}^\circ\text{C}$  ( $\Delta\alpha$ ) CTE mismatch will generate a 60 MPa film stress and allow up to approximately 380  $\mu\text{m}$  GaN thickness on the AlN substrate without cracking. This is a sufficiently thick GaN film to be considered as a practical donor seed substrate for subsequent layer-transfer to manufacture a GaN device template for applications such as HB-LED, power electronics and RF (Radio-Frequency) GaN. Of course, a thinner GaN film can also serve directly as a template substrate for such applications.

[0094] Materials other than (111) single crystal silicon, however, may offer a more close alignment in lattice spacing with GaN. One example of such a material is single crystal silicon carbide (SiC).

[0095] Single crystal SiC is available in a variety of forms, including 3C, 4H, and 6H. The 4H SiC form offers a close lattice match (~4%) with GaN. Of course, 3C, 6H, or other SiC polytypes may also be utilized according to various embodiments.

[0096] Accordingly, Figure 4 shows a simplified view of an alternative embodiment of a GaN seed workpiece 400 featuring a 4H SiC layer 402 bonded to an underlying AlN substrate 404 through a bonding layer 406. That bonding layer may be an oxide bonding layer, including but not limited to spin-on-glass, for example. Again, a MOCVD AlN layer 408 can serve as a precursor layer to the MOCVD GaN seed layer 410, which in turn serves as the template for thickened GaN 412 which may be grown upon the seed template workpiece utilizing LPE and/or HVPE techniques.

[0097] Here it is noted that the AlN precursor of this particular embodiment may be optional. Other low-temperature nucleation layers (or even none) could alternatively be selected depending on the layer itself.

[0098] As with the embodiment of Figure 3A, the 4H type SiC layer is formed by a controlled cleaving from a bulk substrate. Here, that controlled cleaving process may comprise implanting the bulk SiC material with particles, followed by exposure to relatively high temperatures of around 600-900 $^\circ\text{C}$ . Exemplary particle implantation conditions to form a cleave region in the 4H type SiC is  $5-10 \times 10^{16} \text{ H}^+/\text{cm}^2$  at 300 $^\circ\text{C}$  implantation temperature, and 180keV proton energy, 800-900 $^\circ\text{C}$  anneal for about 2 hours to achieve cleaving and transfer of the SiC. Incorporated by reference herein for all purposes is Amarasinghe et al., "Properties of H+ Implanted 4H-SiC as

Related to Exfoliation of Thin Crystalline Films", ECS Journal of Solid State Science and Technology, 3 (3) pp. 37-42 (2014).

[0099] In order to reduce exposure of the seed workpiece to excessively high thermal budgets (high anneal temperature causing bonded substrate breakage and/or impractically long anneal time) associated with cleaving of SiC, it may be possible to subject an implanted (4H or other polytype) SiC bulk ingot to thermal energy prior to bonding and cleaving. This additional thermal exposure may take the form of annealing and/or laser treatment to weaken the bond between the SiC bulk ingot and remaining SiC material overlying the cleave region formed by the implantation. The purpose of lowering the bonded thermal budget is to allow layer transfer of the SiC film onto the target substrate without breaking the bonded pair. The implanted SiC donor substrate can be thermally annealed to lower the bonded pair cleaving thermal budget using methods explained, for example in U.S. Patent No. 6,162,705 and/or U.S. Patent 6,013,563, both of which are incorporated by reference in their entireties herein for all purposes.. Thermal annealing at a level short of blistering would be effective. As an example, reducing the temperature to a level of about 25-50°C lower than that required to develop blistering would be effective in limiting the post-bond anneal thermal budget.

[0100] Figure 5 shows another possible embodiment of a process. In particular, this approach uses a thin layer of layer-transferred single crystal sapphire ( $\text{Al}_2\text{O}_3$ ) as the initial growth surface.

[0101] The template workpiece 500 of Figure 5 comprises an AlN substrate 502 bearing an oxide bonding layer 504. That oxide bonding layer may have a thickness, for example, of between about 200-400 nm.

[0102] Attached to the oxide bonding layer 504 is a sapphire layer 506. This sapphire layer may have a c-cut orientation in order to provide desirable lattice matching. However, other forms of single crystal sapphire are known and could potentially be used, including a-cut, m-cut, and r-cut oriented materials.

[0103] The sapphire layer may have a thickness of between about 0.1-5 $\mu\text{m}$ . It may be formed on the template substrate by separation from a high quality ingot utilizing a controlled cleaving process as is described herein.

[0104] A thin layer of epitaxially grown AlN 508 is in turn formed over the single crystal sapphire layer. This AlN layer is formed by MOCVD to a thickness of between about 50-200nm. Alternatively, the AlN (e.g., ~20-80 nm in thickness) could be formed by physical vapor

deposition (PVD) techniques. Capping the sapphire, the AlN layer serves as a precursor layer to the GaN seed layer that is to be formed.

[0105] In particular, Figure 5 further shows a GaN seed layer 510 overlying the AlN capping layer. That GaN seed layer is formed at high quality overlying the AlN layer 508, also utilizing MOCVD techniques. The GaN may be polar or non-polar, and may be c-plane or of another type.

[0106] It is noted that a polycrystalline AlN (P-AlN) has a lower CTE mismatch with c-plane GaN than the CTE difference between GaN and sapphire. The thermal conductivity of P-AlN is also substantially higher than sapphire. This will reduce the magnitude of thermal gradients arising in the template workpiece, and improve temperature uniformity during processing.

[0107] The surface of the high quality GaN layer offered by the workpiece, in turn serves as a template for the growth of additional GaN material to achieve substantial thicknesses. This is shown in Figure 5, where further high quality GaN material 512 is grown to greater thickness over the GaN seed layer utilizing techniques such as LPE and/or HVPE.

[0108] One possible benefit of the use of a layer transferred sapphire layer is that even though there is some (~13%) lattice mismatch between the sapphire and the GaN grown thereon, the CTE match of the substrate is still an advantage for thick GaN growth. Also, the use of sapphire as growth surface for GaN is well-researched, for example as described by the Pinnington et al. article that is incorporated by reference above.

[0109] In summary, embodiments as shown in Figures 3A-C, 4, and 5 allow the formation of donor workpieces comprising high quality GaN material, by incorporating CTE/lattice compatible materials such as (111) Si, N type SiC, and/or sapphire. Controlled cleaving processes allow those CTE/lattice compatible materials to be separated from large diameter (e.g., > 2") bulk materials, thereby also allowing the overlying grown GaN to exhibit the same corresponding large area. These substrates can in turn be utilized to manufacture GaN-based devices such as HB-LED, power electronics and RF-GaN. These can be cost-effectively fabricated in large-diameter (4"-12") sizes on insulating or conductive base substrates. Using polycrystalline AlN as a base substrate for example, its high thermal conductivity and electrical resistivity could be used for lateral power device structures. Use of an electrically conductive molybdenum substrate (and a conductive bonding layer) could be beneficial for fabricating vertical power devices. The integration of an optically reflective bond layer could also allow top

emitting LED structures and together with a conductive base substrate, a top emitting vertical LED structure.

[0110] It is further noted that the choice of material for both the workpiece and for the additional layer, can play a role in determining a character of the stress/strain experienced by the additional layer. For example, the choice of workpiece/additional layer may also determine a relative mismatch in coefficient in thermal expansion between them, which in turn can contribute to both the polarity and magnitude of stress/strain arising in the additional layer over a range of temperatures. In view of the above, the workpiece and/or the additional layer materials can be carefully selected to achieve a desired layer of stress/strain within the additional layer over various processing steps.

[0111] In specific embodiments, a silicon dioxide or AlN layer can be applied through sputtering or PECVD and optionally densified prior to an implant step. If a film or film stack is applied, it may be of limited total thickness to allow the implant at the selected energy to penetrate into the bulk at the desired cleave depth. Of course there can be other variations, modifications, and alternatives.

[0112] In accordance with particular embodiments, the high energy particles can be generated using a particle accelerator. Here, the accelerator can either be a linear accelerator, a plasma immersion ion implantation tool, an ion shower. Under appropriate conditions, mass-selected or non mass-selected implant technologies can be used.

[0113] In a specific embodiment the particles cause formation of a plurality of gettering sites or an accumulation region within a cleave region, which is provided beneath the surface region to define a thickness of the bulk material that is to be detached (in some embodiments as a free standing layer). The first plurality of high energy particles may provide an implant profile having a peak concentration and a distribution spatially disposed within a depth of the semiconductor substrate. The distribution can have a width of about 2 $\mu$ m and less, where this depth variation of an implant concentration profile is called the longitudinal straggle. For a 2 MeV hydrogen implant in GaN, the implant depth is about 25 $\mu$ m, and the straggle is about 0.7 $\mu$ m.

[0114] In certain embodiments, the cleave region is maintained at a first temperature, which can be provided directly or indirectly. That is, the temperature can be provided by convection, conduction, radiation, or a combination of these techniques according to a specific embodiment. Additionally, the high-energy particle beam may also provide part of the thermal energy and in

combination with an external temperature source to achieve the desired implant temperature. In certain embodiments, the high-energy particle beam alone may provide the entire thermal energy desired for implant. That is, the high energy particle beam can be provided that directly causes energy to be converted into thermal energy to increase the temperature of the substrate or bulk material. Of course there can be other variations, modifications, and alternatives.

[0115] Depending upon the application, according to particular embodiments smaller mass particles are generally selected to decrease the energy requirement for implantation to a desired depth in a material and to reduce a possibility of damage to the material region according to a preferred embodiment. That is, smaller mass particles more easily travel through the substrate material to the selected depth without substantially damaging the material region that the particles traverse through. For example, the smaller mass particles (or energetic particles) can be almost any charged (e.g., positive or negative) and or neutral atoms or molecules, or electrons, or the like. In a specific embodiment, the particles can be neutral or charged particles including ions such as ion species of hydrogen and its isotopes, rare gas ions such as helium and its isotopes, and neon, or others depending upon the embodiment. The particles can also be derived from compounds such as gases, e.g., hydrogen gas, water vapor, methane, and hydrogen compounds, and other light atomic mass particles. Alternatively, the particles can be any combination of the above particles, and or ions and or molecular species and or atomic species. The particles generally have sufficient kinetic energy to penetrate through the surface to the selected depth underneath the surface.

[0116] For example, using hydrogen as the implanted species into a GaN surface as an example, the implantation process is performed using a specific set of conditions. Implantation dose ranges of hydrogen from about  $5 \times 10^{16}$  to about  $5 \times 10^{17}$  atoms/cm<sup>2</sup>, and preferably the dose of implanted hydrogen is less than about  $2 \times 10^{17}$  atoms/cm<sup>2</sup>, and may be less than about  $5 \times 10^{16}$  atoms/cm<sup>2</sup>. Implantation energy ranges from about 0.5 MeV and greater to about 2 MeV for the formation of thick films useful for opto-electronic applications. In certain bonded substrate embodiments implantation energy may be below 500keV, for example 5-180 keV. Implantation temperature ranges from about -50 to about +500 Degrees Celsius, may be between about 100-500 Degree Celsius, and is preferably less than about 700 Degrees Celsius to prevent a possibility of hydrogen ions from diffusing out of the implanted GaN material. Of course, the type of ion used and process conditions depend upon the application.

**[0117]** For higher implant energies, it is particularly useful to have a substantially pure proton implantation (e.g., positive or negatively charged) to allow for a maximum range of the cleaving plane within the reusable substrate. Using GaN as an example, the energy range of implantation can be quite large and span from a few keV for template formation for HB-LED or GaN power electronics applications where a subsequent epitaxial growth is needed to fabricate the GaN device structure, to many MeV yielding substrates measuring tens of micron in thickness for use as a kerfless free-standing wafer starting material. The general range of implant depth as a function of the implant energy can be calculated using, for example SRIM 2013 (Stopping Range In Matter) or a Monte Carlo simulation program (<http://www.srim.org/>). In a specific embodiment, the GaN film thickness ranges from about 0.05 micrometers to about 1 micrometers using proton implant energy ranges from about 5keV to about 180 keV. In other embodiments the GaN film may be a free standing GaN layer having a thickness from about 10 micrometers to about 70 micrometers. Of course there can be other variations, modifications, and alternatives.

**[0118]** The terms "detached" or "transferred GaN thickness" in this context mean that the GaN film thickness formed by the implanted ion range can be released to a free standing state or released to a permanent substrate or a temporary substrate for eventual use as a free standing substrate, or eventually mounted onto a permanent substrate. In some embodiments, the GaN material is sufficiently thick and free from a handle or transfer substrate, which acts as a supporting member. Of course, the particular process for handling and processing of the film will depend on the specific process and application.

**[0119]** Embodiments may optionally perform a thermal treatment process on the semiconductor substrate or bulk material to further form the plurality of gettering sites within the cleave region. That is, the thermal treatment process anneals out and/or quenches the cleave region to fix the plurality of first particles in place. The thermal treatment provides a fixed network of defects that can act as efficient sites for gettering and accumulating particles in a subsequent implantation or particle accumulation/diffusion process.

**[0120]** Without being tied to a particular theory or mechanism, in a specific embodiment, the increased temperature is believed to precipitate a network of permanent defects, and may also trap a substantial portion of hydrogen from the first plurality of particles. The defect layer, which is substantially permanent, provides a site for efficient collection and trapping of particles

from a subsequent implant and/or diffusion process, which will be described in more detail throughout the present specification and more particularly below.

**[0121]** In accordance with one embodiment, the optional thermal treatment can occur using conduction, convection, radiation, or any combination of these techniques. The particle beam may also provide part of the thermal energy and in combination with an external temperature source to achieve the desired implant temperature. In certain embodiments, the particle beam alone may provide the entire thermal energy desired for implant. Of course, there can be other variations, modifications, and alternatives.

**[0122]** A specific embodiment may include subjecting the surface region of the semiconductor substrate or bulk material to a second plurality of high energy particles, which may be generated using a linear accelerator or other accelerated ion implanter such as a PIII system. The method may include a second plurality of high energy particles, which are provided in the semiconductor substrate or bulk material. The second particles are introduced into the cleave region, which increases a stress level of the cleave region from a first stress level to a second stress level from the second plurality of high velocity particles. In a specific embodiment, the second stress level is suitable for a subsequent cleaving process. In a particular embodiment, the semiconductor substrate or bulk material is maintained at a second temperature, which is higher than the first temperature.

**[0123]** Using hydrogen as the species implanted into the bulk single crystal GaN material in the second implantation step as an example, the implantation process is performed using a specific set of conditions. Implantation dose ranges from about  $5 \times 10^{16}$  to about  $5 \times 10^{17}$  atoms/cm<sup>2</sup>, and preferably the dose is less than about  $1 \times 10^{17}$  atoms/cm<sup>2</sup>. Implantation energy ranges from about 5keV and greater to about 0.5 MeV and greater for the formation of thicker films. Implant dose rate can be provided at about 500 microamperes to about 100 milliamperes and a total dose rate can be calculated by integrating an implantation rate over the expanded beam area. Implantation temperature ranges from about -50 Degree Celsius to about 700 Degrees Celsius, and is preferably less than about 500 Degrees Celsius. In a specific embodiment, the temperature and dose are selected to allow for efficient capture of molecular hydrogen, while there may be some diffusion of mono-atomic hydrogen. Of course, the type of ion used and process conditions depend upon the application.

**[0124]** For higher implant energies, it may be useful to have a substantially pure proton implantation (e.g., positive or negatively charged) to allow for a maximum range of the cleaving

plane within the reusable substrate. Using GaN as an example, the energy range of implantation can be large and span from a few keV for template formation for HB-LED or GaN power electronics applications where a subsequent epitaxial growth is needed to fabricate the GaN device structure, to many MeV yielding substrates measuring tens of micron in thickness for use as a kerfless free-standing wafer starting material. The general range of implant depth as a function of the implant energy can be calculated using, for example SRIM 2013 (Stopping Range In Matter) or a Monte Carlo simulation program (<http://www.srim.org/>). In a specific embodiment, the GaN film thickness ranges from about 0.05 micrometers to about 1 micrometers using proton implant energy ranges from about 5keV to about 180 keV. In some embodiments the GaN film may be a free standing GaN layer having a thickness from about 10 micrometers to about 70 micrometers. Of course there can be other variations, modifications, and alternatives.

**[0125]** Effectively, the implanted particles add stress or reduce fracture energy along a plane parallel to the top surface of the substrate or bulk material at the selected depth. The energies depend, in part, upon the implantation species and conditions. These particles reduce a fracture energy level of the substrate or bulk material at the selected depth. This allows for a controlled cleave along the implanted plane at the selected depth. Implantation can occur under conditions such that the energy state of the substrate or bulk material at all internal locations is insufficient to initiate a non-reversible fracture (i.e., separation or cleaving) in the substrate or bulk material. It should be noted, however, that implantation does generally cause a certain amount of defects (e.g., micro-defects) in the substrate or bulk material that can typically at least partially be repaired by subsequent heat treatment, e.g., thermal annealing or rapid thermal annealing.

**[0126]** A mass-selected high-energy implant approach, which has the appropriate beam intensity could be used to manufacture thicker cleaved bulk materials. To be cost-effective, the implant beam current should be on the order of a few tens of milliamps of  $H^+$  or  $H^-$  ion beam current. If the system can implant such sufficiently high energies,  $H_2^+$  ions can also be advantageously utilized for achieving higher dose rates. Ion implant apparatuses useful for embodiments of the present invention have been made recently available by the use of DC electrostatic particle accelerators such as the DYNAMITRON proton accelerator available from Ion Beam Applications SA, Belgium). Other forms of DC electrostatic accelerators which may be used include Van de Graaff or Tandem Van de Graaff accelerator types.

**[0127]** Still other forms of particle accelerators suitable for use in accordance with embodiments of the present invention may include radio frequency (RF) particle accelerators such as a cyclotron or a RF linear accelerator (RF Linac). Examples of possible particle accelerator types include radio-frequency quadrupole linear accelerator (RFQ-Linac) or Drift-Tube Linac (DTL), or RF (Radio)-Focused Interdigitated (RFI) technology. These are available from companies such as Accsys Technology Inc. of Pleasanton, California, Linac Systems, LLC of Albuquerque, NM 87109, and others.

**[0128]** In a specific embodiment, these approaches use RF acceleration of an extracted proton beam to increase the total energy of the proton beam from a range of approximately 20-100 keV to 0.5 to 7 MeV or more. The output beam is usually on the order of a few millimeters in diameter and for use in this application would require the use of beam expansion to the order of a few hundred millimeters on a side to a meter or more in order to keep the power flux impinging on the target surface from becoming too large and possibly overheating or damaging the target surface. The proton current available with these technologies can be up to 100 mA or more. As a specific example, assuming 100 kW of beam power, a 3.25 MeV RFQ/RFI-Linac would yield a proton beam current of about 31 mA. Using a dose of approximately  $1 \times 10^{17}$  H/cm<sup>2</sup> and an expanded beam of about 500mm x 500mm, the GaN area processed per hour at the target implantation dose is about 0.7 square meters while the power flux is kept to about 13 Watts/cm<sup>2</sup>. This combination of parameters makes this approach particularly practical for cost effective HB-LED substrate material production. Of course, there can be other variations, alternatives, and modifications.

**[0129]** Optionally, specific embodiments may include a thermal treatment process after the implanting process. According to a specific embodiment, the present method uses a thermal process ranging from about 150 to about 800 Degrees Celsius for GaN material. In an embodiment, the thermal treatment can occur using conduction, convection, radiation, or any combination of these techniques. The high-energy particle beam may also provide part of the thermal energy and in combination with an external temperature source to achieve the desired implant temperature. In certain embodiment, the high-energy particle beam alone may provide the entire thermal energy desired for implant. In a preferred embodiment, the treatment process occurs to season the cleave region for a subsequent cleave process. Of course, there can be other variations, modifications, and alternatives.

[0130] Specific embodiments may include a cleave initiation step, wherein some energy is applied to the cleave portion to begin cleaving. As described in detail below, this cleave initiation could involve the application of different types of energy, having different characteristics.

[0131] Specific embodiments include a step of freeing the thickness of detachable material, (which may or may not be free standing), using a cleaving process. In a specific embodiment, the step of freeing can be performed using a controlled cleaving process. The controlled cleaving process provides a selected energy within a portion of the cleave region of the donor bulk GaN material. As merely an example, the controlled cleaving process has been described in U.S. Patent No. 6,013,563 titled Controlled Cleaving Process, commonly assigned to Silicon Genesis Corporation of San Jose, California, and hereby incorporated by reference for all purposes. As shown, the method in accordance with an embodiment of the present invention frees the thickness of material (which may be free standing) from the substrate or bulk material to completely remove the thickness of material. Of course, there can be other variations, alternatives, and modifications.

[0132] A method may use one or more patterned regions to facilitate initiation of a cleaving action. In a specific embodiment, the present method provides a semiconductor substrate having a surface region and a thickness. The method includes subjecting the surface region of the semiconductor substrate to a first plurality of high energy particles generated using a particle accelerator to form a patterned region of a plurality of gettering sites within a cleave region. In a preferred embodiment, the cleave region is provided beneath the surface region to define a thickness of material to be detached. The semiconductor substrate is maintained at a first temperature. The method also includes subjecting the semiconductor substrate to a treatment process, e.g., thermal treatment. The method includes subjecting the surface region of the semiconductor substrate to a second plurality of high energy particles, which have been provided to increase a stress level of the cleave region from a first stress level to a second stress level. The method includes initiating the cleaving action at a selected region of the patterned region to detach a portion of the thickness of detachable material using a cleaving process and freeing the thickness of detachable material using a cleaving process.

[0133] In one embodiment, the patterned implant sequence subjects the surface to a dose variation where the initiation area is usually developed using a higher dose and/or thermal budget sequence. Propagation of the cleaving action to complete the cleaving action can occur using

additional dosed regions to guide the propagating cleave front. Alternatively, cleaving propagation can be accomplished by following a depth that is guided using stress-control. Propagation of the cleaving can be achieved by following a natural crystallographic cleave plane. One or more of these techniques may be applied in conjunction with one another. Some or most of the area may be implanted at a lesser dose or not implanted at all depending on the particular cleaving technique used. Such lower dosed regions can help improve overall productivity of the implantation system by reducing the total dose needed to detach each film from the substrate.

**[0134]** In a specific embodiments, methods can perform other processes. For example, the method can place the thickness of detached material on a support member, which is later processed. Additionally or optionally, the method in accordance with an embodiment of the present invention performs one or more processes on the semiconductor substrate or bulk material before subjecting the surface region with the first plurality of high energy particles, or between the implanting step(s) and the cleaving step. Depending upon the particular embodiment, the processes can be for the formation of illumination devices, or layers used within a cell process, integrated circuits, optical devices, any combination of these, and the like. Of course, there can be other variations, modifications, and alternatives.

**[0135]** As described above, improved techniques for removing a thin film of material from a substrate using a controlled cleaving action are provided. This technique allows an initiation of a cleaving process on a substrate using a single or multiple cleave region(s) through the use of controlled energy (e.g., spatial distribution) and selected conditions to allow an initiation of a cleave front(s) and to allow it to propagate through the substrate to remove a thin film of material from the substrate.

**[0136]** In a specific embodiment, a process is provided for forming a film of material from a donor using a controlled cleaving process. The process includes a step of introducing energetic particles (e.g., charged or neutral molecules, atoms, or electrons having sufficient kinetic energy) through a surface of a donor to a selected depth underneath the surface, where the particles are at a relatively high concentration to define a thickness of donor material (e.g., thin film of detachable material) above the selected depth. To cleave the donor material, the method provides energy to a selected region of the donor to initiate a controlled cleaving action in the donor, whereupon the cleaving action is made using a propagating cleave front(s) to free the donor material from a remaining portion of the donor.

**[0137]** A cleave may be initiated by subjecting the material with sufficient energy to fracture the material in one region, causing a cleave front, without uncontrolled shattering or cracking. The cleave front formation energy (E) must often be made lower than the bulk material fracture energy (E<sub>tna</sub>) at each region to avoid shattering or cracking the material. The directional energy impulse vector in diamond cutting or the scribe line in glass cutting are, for example, the means in which the cleave energy is reduced to allow the controlled creation and propagation of a cleave front. The cleave front is in itself a higher stress region and once created, its propagation requires a lower energy to further cleave the material from this initial region of fracture. The energy required to propagate the cleave front is called the cleave front propagation energy (4). The relationship can be expressed as:

$$E_c = E_p + [\text{cleave front stress energy}]$$

**[0138]** A controlled cleaving process is realized by reducing E<sub>p</sub> along a favored direction(s) above all others and limiting the available energy to below the E<sub>p</sub> of other undesired directions. In any cleave process, a better cleave surface finish occurs when the cleave process occurs through only one expanding cleave front, although multiple cleave fronts do work.

**[0139]** Numerous benefits are achieved over pre-existing techniques using the present invention. In particular, the present invention uses controlled energy and selected conditions to preferentially cleave a thin film of material from a donor which includes multi-material sandwiched films. This cleaving process selectively removes the thin film of material from the substrate while preventing a possibility of damage to the film or a remaining portion of the substrate. Accordingly, the remaining substrate portion can be re-used repeatedly for other applications.

**[0140]** Additionally, the present invention uses a relatively low temperature during the controlled cleaving process of the thin film to reduce temperature excursions of the separated film, donor, or multi-material films according to other embodiments. This lower temperature approach allows for more material and process latitude such as, for example, cleaving and bonding of materials having substantially different thermal expansion coefficients. In other embodiments, the present invention limits energy or stress in the substrate to a value below a cleave initiation energy, which generally removes a possibility of creating random cleave initiation sites or fronts. This reduces cleave damage (e.g., pits, crystalline defects, breakage, cracks, steps, voids, excessive roughness) often caused in pre-existing techniques. Moreover, embodiments can

reduce damage caused by higher than necessary stress or pressure effects and nucleation sites caused by the energetic particles as compared to pre-existing techniques.

**[0141]** A variety of techniques can be used to implant the energetic particles into the GaN material. These techniques include ion implantation using, for example, beam line ion implantation equipment manufactured from companies such as Applied Materials, Eaton Corporation, Varian, and others. Alternatively, implantation occurs using a plasma immersion ion implantation ("PIII") technique. Examples of plasma immersion ion implantation techniques are described in "Recent Applications of Plasma Immersion Ion Implantation," Paul K. Chu, Chung Chan, and Nathan W. Cheung, SEMICONDUCTOR INTERNATIONAL, pp. 165-172, June 1996, and "Plasma Immersion Ion Implantation--A Fledgling Technique for Semiconductor Processing," P. K. Chu, S. Qin, C. Chan, N. W. Cheung, and L. A. Larson, MATERIALS SCIENCE AND ENGINEERING REPORTS: A REVIEW JOURNAL, pp. 207-280, Vol. R17, Nos. 6-7, (Nov. 30, 1996), which are both hereby incorporated by reference for all purposes. Of course, techniques used depend upon the application.

**[0142]** A basic configuration of one PIII system may utilize a target holder supporting the target to be implanted. The target holder may comprise a high-voltage isolated cooled chuck with electrostatic or mechanical clamping to allow the target material to be thermally contacted to the target holder. This can be accomplished by conduction cooling (e.g. through an elastomer or other compliant layer allowing efficient contacting of the backside of the target) or by convection cooling (e.g. by developing gas pressure between the backside of the target and the target holder). Sometimes, a combination of conduction and convection cooling may be employed. During this plasma soak time, the target is directly immersed in the plasma.

**[0143]** A target holder and target may be briefly pulsed to a large negative voltage (-V). During this time, a sheath free of charged particles is developed around the target holder assembly. The voltage is dropped across the thickness of the sheath.

**[0144]** Implantation occurs by the positive charges diffusing across the plasma/sheath interface to accelerate and strike the surface of the target holder assembly with energy equal to V. For example, a pulse of -40kV could accelerate H<sup>+</sup> protons within a hydrogen plasma to an energy of 40keV. This implantation process continues at a rate determined by parameters such as the plasma density and ion specie. To avoid arcing, the high-voltage may be applied for a brief period of time and repeated at a selected repetition rate. Typical PIII operating parameters can be 20-1000Hz repetition frequency (Fr), and pulse widths (Tp) of a few microseconds to more

than 100 microseconds. If the peak ion current (I<sub>ion</sub>) and effective target holder area (A) are known, the dose rate can be calculated as:

$$\text{Dose Rate (ions/cm}^2\text{)} = \text{I}_{\text{ion}} \times \text{Fr} \times \text{Tp} / qA, \text{ where } q \text{ is the electronic charge.}$$

[0145] When charged particles hit the target holder assembly, secondary electrons are ejected from the surface to be accelerated in the reverse direction. The electron yield (number of electrons emitted per positive charged particle implanted) is called gamma ( $\gamma$ ).