(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6936641号

(P6936641)

(45) 発行日 令和3年9月22日(2021.9.22)

(24) 登録日 令和3年8月31日(2021.8.31)

(51) Int.Cl.

F 1

|                    |                  |             |

|--------------------|------------------|-------------|

| <b>HO4N 19/52</b>  | <b>(2014.01)</b> | HO4N 19/52  |

| <b>HO4N 19/96</b>  | <b>(2014.01)</b> | HO4N 19/96  |

| <b>HO4N 19/433</b> | <b>(2014.01)</b> | HO4N 19/433 |

| <b>HO4N 19/463</b> | <b>(2014.01)</b> | HO4N 19/463 |

請求項の数 8 (全 11 頁)

(21) 出願番号 特願2017-132261 (P2017-132261)

(22) 出願日 平成29年7月5日 (2017.7.5)

(65) 公開番号 特開2019-16896 (P2019-16896A)

(43) 公開日 平成31年1月31日 (2019.1.31)

審査請求日 令和2年6月19日 (2020.6.19)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 110003281

特許業務法人大塚国際特許事務所

(72) 発明者 ノン マクセル

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 マイケル ロー ジー フェルナンデス

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 リー アンソニー ティー グラホ

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】画像処理装置、画像処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

四分木空間分割により画像領域を再帰的に分割することで得られる複数のブロックのそれについて、符号化に関連する符号化情報を取得する取得手段と、

前記画像領域を前記ブロックよりも小さいサイズを有する複数のサブブロックに分割した場合における該複数のサブブロックのそれぞれについて、該サブブロックの座標位置と、該サブブロックを含むブロックの符号化情報と、を関連づけてメモリに格納する格納制御手段と、

前記画像領域における第1のブロックに含まれている複数のサブブロックのうち1つのサブブロックと隣接する隣接サブブロックの座標位置と関連づけられて前記メモリに格納されている符号化情報と、前記第1のブロックの符号化情報と、を用いて符号化処理を行う符号化手段と

を備え、

前記隣接サブブロックは、前記第1のブロックに隣接している第2のブロックに含まれている複数のサブブロックのうち前記1つのサブブロックと隣接しているサブブロックであることを特徴とする画像処理装置。

## 【請求項 2】

前記格納制御手段は、それぞれのサブブロックの座標位置と、該サブブロックが属するブロックの符号化情報と、を関連づけて前記メモリに格納することを特徴とする請求項1に記載の画像処理装置。

**【請求項 3】**

前記符号化情報は動きベクトルであることを特徴とする請求項 1 又は 2 に記載の画像処理装置。

**【請求項 4】**

前記符号化手段は、前記第 1 のブロックの動きベクトルと、前記隣接サブブロックの座標位置と関連づけられて前記メモリに格納されている動きベクトルと、の差分を符号化することを特徴とする請求項 3 に記載の画像処理装置。

**【請求項 5】**

前記画像領域は、画像を四分木空間分割により分割した C T U ( C o d i n g T r e e U n i t ) であることを特徴とする請求項 1 乃至 4 の何れか 1 項に記載の画像処理装置。

10

**【請求項 6】**

前記ブロックは C U ( C o d i n g U n i t ) であり、前記サブブロックは四分木空間分割における最小サイズを有する C U であることを特徴とする請求項 1 乃至 5 の何れか 1 項に記載の画像処理装置。

**【請求項 7】**

画像処理装置が行う画像処理方法であって、

前記画像処理装置の取得手段が、四分木空間分割により画像領域を再帰的に分割することで得られる複数のブロックのそれぞれについて、符号化に関連する符号化情報を取得する取得工程と、

20

前記画像処理装置の格納制御手段が、前記画像領域を前記ブロックよりも小さいサイズを有する複数のサブブロックに分割した場合における該複数のサブブロックのそれぞれについて、該サブブロックの座標位置と、該サブブロックを含むブロックの符号化情報と、を関連づけてメモリに格納する格納制御工程と、

前記画像処理装置の符号化手段が、前記画像領域における第 1 のブロックに含まれている複数のサブブロックのうち 1 つのサブブロックと隣接する隣接サブブロックの座標位置と関連づけられて前記メモリに格納されている符号化情報と、前記第 1 のブロックの符号化情報と、を用いて符号化処理を行う符号化工程と

を備え、

30

前記隣接サブブロックは、前記第 1 のブロックに隣接している第 2 のブロックに含まれている複数のサブブロックのうち前記 1 つのサブブロックと隣接しているサブブロックであることを特徴とする画像処理方法。

**【請求項 8】**

コンピュータを、請求項 1 乃至 6 の何れか 1 項に記載の画像処理装置の各手段として機能させるためのコンピュータプログラム。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、符号化技術に関するものである。

**【背景技術】****【0 0 0 2】**

動画像の圧縮記録の符号化方式として、H . 2 6 5 / H E V C ( H i g h E f f i c i e n c y V i d e o C o d i n g ) 符号化方式（以下、H E V C）が知られている。H E V C では、動画像を構成する各フレームの画像は、四分木空間分割によって C T U ( C o d i n g T r e e U n i t ) と呼ばれる画素ブロックに分割される。また、C T U を更に再帰的に四分木空間分割することもできる。H E V Cにおいて C T U が取り得るブロックサイズには  $64 \times 64$ 、 $32 \times 32$ 、 $16 \times 16$  がある。また、C T U を再帰的に四分木空間分割することで得られる C U ( C o d i n g U n i t ) が取り得るブロックサイズには  $64 \times 64$ 、 $32 \times 32$ 、 $16 \times 16$ 、 $8 \times 8$  がある。H E V C では符号化処理は C U を単位に行われる。特許文献 1 には、ブロックサイズが可変の圧縮方式にお

40

いても、画像変動時に符号化効率を上げながら画質も向上させるための技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2015-115903号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

H E V C における動きベクトルの符号化では、自ブロック (CU) と隣接するそれぞれのブロック (CU) の動きベクトルから 1 つを選択し、該選択した動きベクトルと自ブロックの動きベクトルとの差分を符号化している。このような符号化を行うためには、自ブロックと隣接するブロックの動きベクトルを取得する必要がある。

【0005】

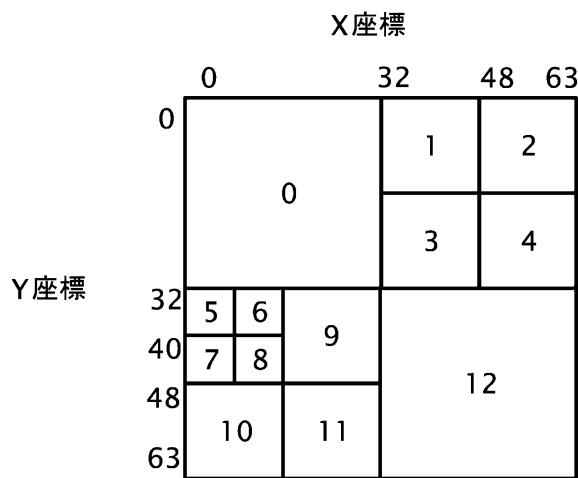

図 1 には、縦 64 画素 × 横 64 画素の CTU を示しており、CTU の左上隅の座標位置 (X 座標、Y 座標) = (0, 0)、CTU の右下隅の座標位置 (X 座標、Y 座標) = (63, 63)、である。この CTU は再帰的な四分木空間分割により 13 個の CU に分割されている。CU に付された番号 0 ~ 12 は該 CU の読み出し順 (符号化順) を示しており、所謂モートン序列である。以下では、番号 N (N = 0 ~ 12) が付された CU を CU (N) と称する。

【0006】

CU (N) の動きベクトルを符号化するためには、CU (N) と隣接し且つ CU (N) と規定の位置関係にあるそれぞれの CU の動きベクトルを参照し、そのうち発生する符号量が最小となる動きベクトルを特定する必要がある。ここで、CU (9) の動きベクトルを符号化するべく、CU (0) の動きベクトルを参照するケースを考える。CU (N) の動きベクトルは、CN (N) の座標位置 (例えば左上隅の座標位置) と関連づけてメモリで管理されているため、CU (N) の動きベクトルをメモリから読み出すためには、該 CU (N) の座標位置を特定する必要がある。CU (9) の座標位置 (左上隅の座標位置) は (16, 32) であり、サイズは縦 16 画素 × 横 16 画素である。また、CU (0) の座標位置 (左上隅の座標位置) は (0, 0) であり、サイズは縦 32 画素 × 横 32 画素である。然るに、CU (0) の動きベクトルをメモリから読み出すためには、現在着目している CU (9) の座標位置に対して X 座標方向に「-16」、Y 座標方向に「-32」だけオフセットした位置を求める必要がある。

【0007】

また、CU (12) の動きベクトルを符号化するべく、CU (3) の動きベクトルを参照するケースを考える。CU (12) の座標位置 (左上隅の座標位置) は (32, 32) であり、サイズは縦 32 画素 × 横 32 画素である。また、CU (3) の座標位置 (左上隅の座標位置) は (32, 16) であり、サイズは縦 16 画素 × 横 16 画素である。然るに、CU (3) の動きベクトルをメモリから読み出すためには、現在着目している CU (12) の座標位置に対して X 座標方向に「0」、Y 座標方向に「-16」だけオフセットした位置を求める必要がある。

【0008】

このように、CTU を四分木空間分割した場合、全ての CU のサイズが同じになるとは限らないので、その場合、上記のオフセット量は一定値にはならない。然るに、隣接する CU の動きベクトルを取得するためには、該 CU の位置を毎回計算する必要があり、処理が煩雑となる。

【0009】

本発明はこのような問題に鑑みてなされたものであり、隣接するブロック (CU) の符号化情報の取得をより高速に行うための技術を提供する。

【課題を解決するための手段】

10

20

30

40

50

## 【0010】

本発明の一様態は、四分木空間分割により画像領域を再帰的に分割することで得られる複数のブロックのそれぞれについて、符号化に関する符号化情報を取得する取得手段と、

前記画像領域を前記ブロックよりも小さいサイズを有する複数のサブブロックに分割した場合における該複数のサブブロックのそれぞれについて、該サブブロックの座標位置と、該サブブロックを含むブロックの符号化情報と、を関連づけてメモリに格納する格納制御手段と、

前記画像領域における第1のブロックに含まれている複数のサブブロックのうち1つのサブブロックと隣接する隣接サブブロックの座標位置と関連づけられて前記メモリに格納されている符号化情報と、前記第1のブロックの符号化情報と、を用いて符号化処理を行う符号化手段と

を備え、

前記隣接サブブロックは、前記第1のブロックに隣接している第2のブロックに含まれている複数のサブブロックのうち前記1つのサブブロックと隣接しているサブブロックであることを特徴とする。

## 【発明の効果】

## 【0011】

本発明の構成によれば、隣接するブロック(CU)の符号化情報の取得をより高速に行うことができる。

20

## 【図面の簡単な説明】

## 【0012】

【図1】CTUの構成例を説明する図。

【図2】画像処理装置の機能構成例を示すブロック図。

【図3】画像処理装置がCTUを符号化するために行う処理のフローチャート。

【図4】CTUを8画素×8画素のMCUを単位に分割した分割例を示す図。

【図5】登録情報の構成例を示す図。

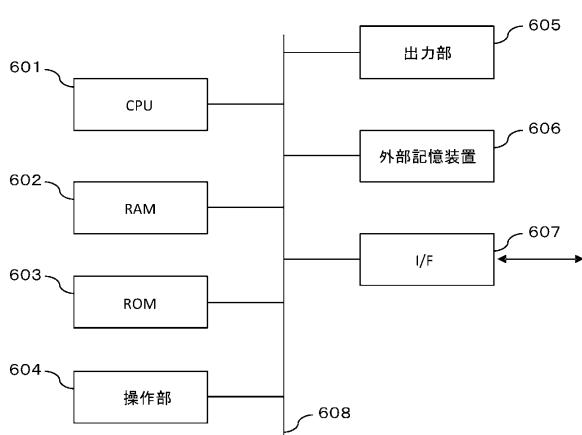

【図6】コンピュータ装置のハードウェア構成例を示すブロック図。

## 【発明を実施するための形態】

## 【0013】

30

以下、添付図面を参照し、本発明の実施形態について説明する。なお、以下説明する実施形態は、本発明を具体的に実施した場合の一例を示すもので、特許請求の範囲に記載した構成の具体的な実施例の1つである。

## 【0014】

## [第1の実施形態]

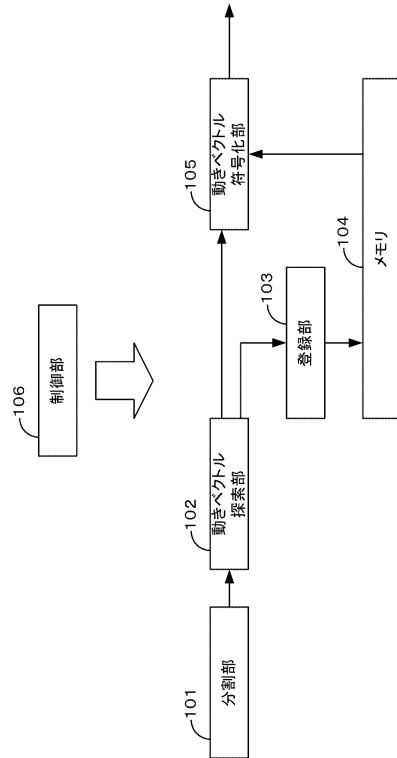

本実施形態では動画像を構成する各フレームの画像を符号化する画像処理装置について説明する。先ず、本実施形態に係る画像処理装置の機能構成例について、図2のブロック図を用いて説明する。なお、図2は、動画像の符号化において動きベクトルの符号化に係る構成を示したものであって、動画像の符号化に係る全ての構成を示したものではない。つまり、図2に示した構成は、動画像に対してインター／イントラ予測符号化を行う画像処理装置の構成において、動きベクトルの符号化を行うための構成を抜粋したものである。なお、動画像の符号化において動きベクトルの符号化以外の処理については従来と同様であるため、これに係る詳細な説明は省略する。

40

## 【0015】

分割部101は、動画像を構成する各フレームの画像(入力画像)を取得し、該入力画像を四分木空間分割によって再帰的に分割する。分割部101は先ず、入力画像を四分木空間分割により複数のCTU(Coding Tree Unit)に分割し、更に該CTUを再帰的に四分木空間分割することでCU(Coding Unit)を得る。

## 【0016】

動きベクトル探索部102は、分割部101により分割されたCUごとに動きベクトル

50

を探索する。CUごとの動きベクトルの探索処理については周知であるため、これに係る説明は省略する。

#### 【0017】

登録部103は、CTUを四分木空間分割における最小分割サイズのCU(以下、MCUと称する)を単位に分割した場合におけるそれぞれのMCUの座標位置と、分割部101が分割したそれぞれのCUのうち該MCUが属するCUの動きベクトルと、を関連づけてメモリ104に登録する。

#### 【0018】

動きベクトル符号化部105は、CUの動きベクトルを符号化する。CUの動きベクトルの符号化では、該CUと隣接し且つ該CUと規定の位置関係にある隣接CUの動きベクトルのうち、発生する符号量が最も小さくなると推定される動きベクトルを特定し、該特定した動きベクトルと該CUの動きベクトルとの差分を符号化する。制御部106は、分割部101、動きベクトル探索部102、登録部103、動きベクトル符号化部105の動作制御を行う。10

#### 【0019】

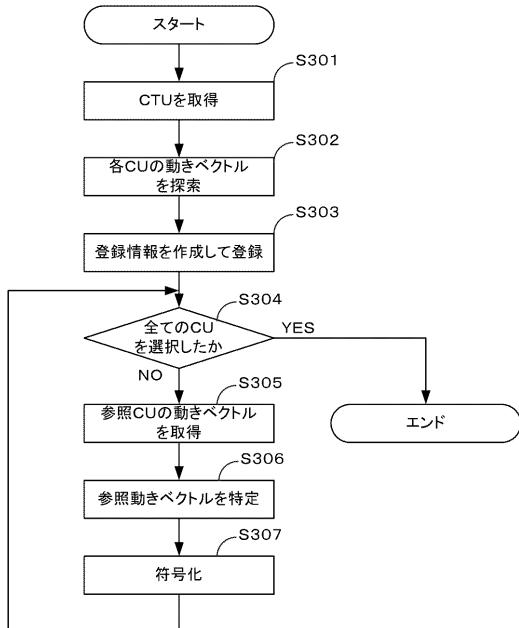

次に、上記の画像処理装置が1つのCTUを符号化するために行う処理について、図3のフローチャートに従って説明する。従って、画像処理装置は1枚の入力画像を構成するそれぞれのCTUについて図3のフローチャートに従った処理を行うことで、該入力画像におけるそれぞれのCUの動きベクトルに対する符号化を行うことができる。以下では一例として、分割部101から図1に示したCTUが動きベクトル符号化部105に入力されたものとして説明する。また、以下では、MCUの座標位置、CUの座標位置のそれぞれは、MCUの左上隅の座標位置、CUの左上隅の座標位置、とする。20

#### 【0020】

ステップS301では、動きベクトル符号化部105は、分割部101が入力画像を四分木空間分割により分割することで生成した図1のCTUを取得する。図1のCTUについては上記の通りである。

#### 【0021】

ステップS302では、動きベクトル探索部102は、図1の各CU(CU(0)~CU(12))について動きベクトルを探索する。

#### 【0022】

ステップS303では、登録部103は、図1のCTUを8画素×8画素のCU(MCU)を単位に分割した場合におけるそれぞれのMCUの座標位置と、該MCUが属するCUについてステップS302で探索した動きベクトルと、を関連づけて管理する登録情報を作成し、該作成した登録情報をメモリ104に登録する。30

#### 【0023】

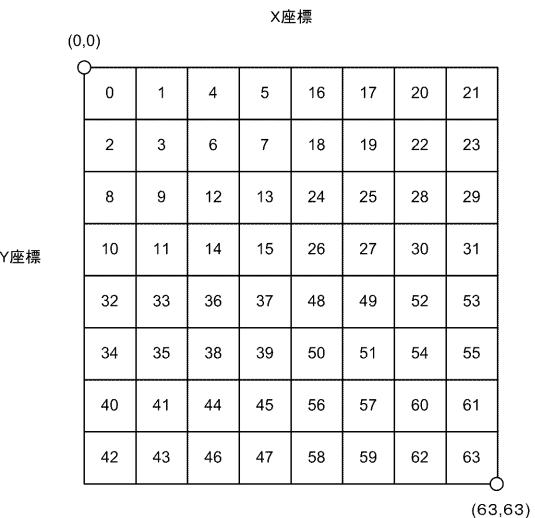

ここで、図1のCTUを8画素×8画素のMCUを単位に分割した場合における分割例を図4に示す。各マスはMCUを表しており、マスに記された番号は符号化順(符号化順はモートン序列に従っている)を示している。以下では、番号M(M=0~63)が付されたMCUをMCU(M)と称する。

#### 【0024】

上記の通り、CTUのサイズは64画素×64画素であり、これを8画素×8画素のサイズを有するMCUを単位に分割するため、図4に示す如く、このCTUは縦8個、横8個のMCUに分割されることになる。このような場合、何れのMCUも何れかのCUに含まれることになる。例えば、CU(0)にはMCU(0)~MCU(15)が含まれている。また例えば、CU(3)にはMCU(24)~MCU(27)が含まれている。登録部103が生成する登録情報では、CU(N)の動きベクトルを、CU(N)に含まれているそれぞれのMCUの座標位置と関連づけて管理している。例えば、CU(0)の動きベクトルについては、MCU(0)~MCU(15)のそれぞれの座標位置と関連づけて登録情報で管理されている。また例えば、CU(3)の動きベクトルについては、MCU(24)~MCU(27)のそれぞれの座標位置と関連づけて登録情報で管理されている。40

。

### 【0025】

登録情報の構成例を図5に示す。MCU(0)～MCU(15)は何れもCU(0)に属するMCUである。然るに、登録情報では、CU(0)の動きベクトルの成分(Vx0, Vy0)は、MCU(0)～MCU(15)のそれぞれの座標位置(0, 0)、(8, 0)、(0, 8)、(8, 8)…(24, 24)と関連づけられている。また、MCU(20)～MCU(23)は何れもCU(2)に属するMCUである。然るに、登録情報では、CU(2)の動きベクトルの成分(Vx2, Vy2)は、MCU(20)～MCU(23)のそれぞれの座標位置(48, 0)、(56, 0)、(48, 8)、(56, 8)と関連づけられている。

10

### 【0026】

図3に戻って、次に、ステップS304では、動きベクトル符号化部105は、図1のCTUにおける全てのCUを選択したか否か(全てのCUの動きベクトルを符号化したか否か)を判断する。この判断の結果、図1のCTUにおける全てのCUを選択した場合には、図1のCTUに対する図3のフローチャートに従った処理は終了する。一方、図1のCTUにおいて未選択のCUが残っている場合には、処理はステップS305に進む。

### 【0027】

ステップS305では、動きベクトル符号化部105は、図1のCTUにおいて未選択のCUのうち1つを選択CUとして選択する。CUの選択は、CUの符号化順に従って行われる。そして動きベクトル符号化部105は、選択CUの動きベクトルを符号化するために参照する参照CUの動きベクトルをメモリ104から取得する。例えば、選択CUとしてCU(11)を選択した場合、参照CUはCU(8)～CU(10)(動きベクトルが符号化済みのCU)となる。

20

### 【0028】

ここで、メモリ104から参照CUの動きベクトルを読み出す場合には、参照CUに含まれているMCUのうち選択CUの左上隅のMCUと隣接するMCUと関連づけて登録情報で管理されている動きベクトルを読み出す。例えば、選択CUの座標位置を(x, y)とすると、座標位置(x - 8, y - 8)、(x, y - 8)、(x - 8, y)のそれぞれと関連づけて登録情報で管理されている動きベクトルを取得する。

### 【0029】

30

従来では、参照CUの動きベクトルを取得する為には、選択CUの座標位置から参照CUの座標位置へのオフセット量を求める必要があり、選択CUの座標位置から該オフセット量だけオフセットした座標位置と関連づけられている動きベクトルを取得していた。これに対し、本実施形態では、CUの動きベクトルを該CUに含まれているそれぞれのMCUと関連づけて管理しているので、参照CUの動きベクトルは、選択CUと隣接するMCUから取得することができる。これにより、選択CUの座標位置から参照CUの座標位置へのオフセット量を求めることなく、参照CUの動きベクトルを取得することができる。

### 【0030】

例えば、図1においてCU(12)が選択CUであり、参照CUがCU(3)である場合、従来であれば、CU(3)の動きベクトルを取得するためには、CU(12)の座標位置に対するCU(3)の座標位置のオフセット量を求める必要があった。係る点、本実施形態の場合、CU(12)の左上隅に隣接するCU(3)のMCU(26)からCU(3)の動きベクトルを取得することができるため、上記のオフセット量を求めることなくCU(3)の動きベクトルを取得することができる。

40

### 【0031】

ステップS306では、動きベクトル符号化部105は、ステップS305で取得したそれぞれの動きベクトルのうち、選択CUの動きベクトルとの差分が最小の動きベクトルを参照動きベクトルとして特定する。

### 【0032】

ステップS307では、動きベクトル符号化部105は、選択CUの動きベクトルと参

50

照動きベクトルとの差分を符号化する。動きベクトル符号化部 105 による符号化結果は、入力画像に対する符号化データに含められて出力される。入力画像に対する符号化処理には、インター予測（画面間予測、動き補償予測）を行うインター予測符号化モード、イントラ予測（画面内予測）を行うイントラ予測符号化モード、の 2 つの予測符号化モードが採用されている。入力画像に対する符号化処理では、この 2 つの予測符号化モードのうち制御部 106 によって設定された予測符号化モードに対応する符号化（インター予測符号化 / イントラ予測符号化）を行う。何れの予測符号化モードにおいても、「イントラ予測 / インター予測、量子化、エントロピー符号化などの一連の処理」は、CU の単位で行われる。

## 【0033】

10

なお、入力画像に対する符号化データの出力先については特定の出力先に限らず、画像処理装置内のメモリであっても良いし、LAN やインターネット等のネットワークを介して画像処理装置に接続されている外部の装置であっても良い。そして処理はステップ S304 に戻る。

## 【0034】

なお、本実施形態で用いた具体的な数値は説明を具体的に行うために使用したものであり、上記の処理は、上記の数値に限ったものではなく、任意の数値であって良い。例えば、上記の説明では MCU のサイズを 8 画素 × 8 画素としたが、これは CU のサイズ（8 画素 × 8 画素）よりも小さいサイズの一例であって、これに限るものではなく、例えば、MCU のサイズを 4 画素 × 4 画素としても良い。また、CTU のサイズは 64 画素 × 64 画素に限らず、32 画素 × 32 画素であっても良い。

20

## 【0035】

また、上記の説明では、MCU と、該 MCU を含む CU の動きベクトルと、を関連づけるために登録情報を作成したが、このような関連づけを行うための方法は特定の方法に限らない。

## 【0036】

また、図 2 ではメモリ 104 は画像処理装置内に設けられたメモリとしているが、メモリ 104 は、画像処理装置の外部に設けられたメモリであっても良い。また、本実施形態では、動きベクトルを符号化する構成について説明したが、動きベクトルは CU の符号化に関連する符号化情報の一例として説明したものであって、符号化情報は動きベクトルに限らない。例えば、イントラ予測とインター予測のいずれが選択されたかを示す情報や、イントラ予測モードを示す情報であってもよい。このような場合、画像処理装置は、次のような動作でもって符号化処理を行う。

30

## 【0037】

先ず、四分木空間分割により画像領域を再帰的に分割することで得られる複数のブロックのそれについて、符号化に関連する符号化情報を取得する。そして、着目ブロックの符号化情報を、画像領域をブロックよりも小さいサブブロックを単位に分割した場合に着目ブロックに属するサブブロック、と関連づけてメモリに格納する（格納制御）。そして、画像領域における第 1 のブロックと隣接する第 2 のブロックに属するサブブロックのうち第 1 のブロックと隣接する隣接サブブロックと関連づけられている符号化情報をメモリから取得する。そして、該取得した符号化情報と、第 1 のブロックの符号化情報と、を用いて符号化処理を行う。

40

## 【0038】

## [ 第 2 の実施形態 ]

図 2 に示した各機能部はハードウェアで実装しても良いが、メモリ 104 を除く各機能部をソフトウェア（コンピュータプログラム）で実装しても良い。前者の場合、このようなハードウェアは、デジタルカメラ、スマートフォン、タブレット端末、ネットワークカメラなどのコンピュータ装置に組み込んでも良い。一方、後者の場合、図 2 に示した各機能部（メモリ 104 を除く）に対応するコンピュータプログラムを実行可能なプロセッサを有するコンピュータ装置は、上記の画像処理装置に適用することができる。図 2 に示

50

した各機能部（メモリ 104 を除く）に対応するコンピュータプログラムを実行可能なプロセッサを有するコンピュータ装置のハードウェア構成例について、図6のブロック図を用いて説明する。

#### 【0039】

CPU601は、RAM602やROM603に格納されているコンピュータプログラムやデータを用いて処理を実行する。これによりCPU601は、コンピュータ装置全体の動作制御を行うと共に、画像処理装置が行うものとして上述した各処理を実行若しくは制御する。

#### 【0040】

RAM602は、ROM603や外部記憶装置606からロードされたコンピュータプログラムやデータ、I/F（インターフェース）607を介して外部から受信したデータを格納するためのエリアを有する。更にRAM602は、CPU601が各種の処理を実行する際に用いるワークエリアを有する。このようにRAM602は、各種のエリアを適宜提供することができる。上記のメモリ104はRAM602で実装しても良い。

10

#### 【0041】

ROM603には、書換不要のコンピュータプログラム（例えば、BIOSのコンピュータプログラムや起動プログラム）やデータ（例えば、コンピュータ装置の設定データ）が格納されている。

#### 【0042】

操作部604は、キーボードやマウスなどのユーザインターフェースにより構成されており、ユーザが操作することで各種の指示をCPU601に対して入力することができる。

20

#### 【0043】

出力部605は、CRTや液晶画面などにより構成されている表示装置、壁面などに画像や文字を投影する投影装置、などの機器により構成されており、CPU601による処理結果を画像や文字などでもって表示／投影する。表示装置はタッチパネル画面であっても良い。

#### 【0044】

外部記憶装置606は、ハードディスクドライブ装置に代表される大容量情報記憶装置である。外部記憶装置606には、OS（オペレーティングシステム）や、画像処理装置が行うものとして上述した各処理をCPU601に実行させるためのコンピュータプログラムやデータが保存されている。外部記憶装置606に保存されているコンピュータプログラムには、図2に示した各機能部（メモリ104を除く）の機能をCPU601に実現させるためのコンピュータプログラムが含まれている。また、外部記憶装置606に保存されているデータには、上記の登録情報や動きベクトル符号化部105が符号化に用いる符号化パラメータなどが含まれている。外部記憶装置606に保存されているコンピュータプログラムやデータは、CPU601による制御に従って適宜RAM602にロードされ、CPU601による処理対象となる。上記のメモリ104は外部記憶装置606で実装しても良い。

30

#### 【0045】

I/F607は、外部の機器とのデータ通信を行うためのインターフェースとして機能するものであり、例えば、動画像を撮像する撮像装置をI/F607に接続し、該I/F607を介して上記の動画像を構成する各フレームの画像を取得することができる。また、I/F607には、LANやインターネットなどのネットワークに接続するためのネットワークインターフェースが含まれていても良く、上記の説明における様々な情報をI/F607を介して外部の機器から取得しても良い。

40

#### 【0046】

上記のCPU601、RAM602、ROM603、操作部604、出力部605、外部記憶装置606、I/F607は何れもバス608に接続されている。なお、図6に示したハードウェア構成は、上記の画像処理装置に適用可能なコンピュータ装置のハードウ

50

エア構成の一例に過ぎない。

**【0047】**

(その他の実施例)

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

**【符号の説明】**

**【0048】**

101：分割部 102：動きベクトル探索部 103：登録部 104：メモリ 105：動きベクトル符号化部 106：制御部

**【図1】**

**【図2】**

【図3】

【図4】

【図5】

| MCUの座標位置         | 動きベクトル       |

|------------------|--------------|

| MCU(0):(0, 0)    | (Vx0, Vy0)   |

| MCU(1):(8, 0)    | (Vx0, Vy0)   |

| MCU(2):(0, 8)    | (Vx0, Vy0)   |

| MCU(3):(8, 8)    | (Vx0, Vy0)   |

| ⋮                | ⋮            |

| MCU(15):(24, 24) | (Vx0, Vy0)   |

| MCU(16):(32, 0)  | (Vx1, Vy1)   |

| MCU(17):(40, 0)  | (Vx1, Vy1)   |

| MCU(18):(32, 8)  | (Vx1, Vy1)   |

| MCU(19):(40, 8)  | (Vx1, Vy1)   |

| MCU(20):(48, 0)  | (Vx2, Vy2)   |

| MCU(21):(56, 0)  | (Vx2, Vy2)   |

| MCU(22):(48, 8)  | (Vx2, Vy2)   |

| MCU(23):(56, 8)  | (Vx2, Vy2)   |

| MCU(24):(32, 16) | (Vx3, Vy3)   |

| ⋮                | ⋮            |

| MCU(32):(0, 32)  | (Vx5, Vy5)   |

| MCU(33):(8, 32)  | (Vx6, Vy6)   |

| MCU(34):(0, 40)  | (Vx7, Vy7)   |

| MCU(35):(8, 40)  | (Vx8, Vy8)   |

| ⋮                | ⋮            |

| MCU(48):(32, 32) | (Vx12, Vy12) |

| ⋮                | ⋮            |

| MCU(62):(48, 56) | (Vx12, Vy12) |

| MCU(63):(56, 56) | (Vx12, Vy12) |

【図6】

---

フロントページの続き

(72)発明者 エロル ジェイソン ディー アルザドン

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 岩井 健二

(56)参考文献 国際公開第2012/120661(WO,A1)

特開2010-010950(JP,A)

特開2008-048200(JP,A)

国際公開第2013/118216(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H04N 19/00 - 19/98