(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5094441号

(P5094441)

(45) 発行日 平成24年12月12日(2012.12.12)

(24) 登録日 平成24年9月28日(2012.9.28)

(51) Int.Cl.

H03F 3/45 (2006.01)

F 1

H03F 3/45

A

請求項の数 18 (全 13 頁)

(21) 出願番号 特願2008-9991 (P2008-9991)

(22) 出願日 平成20年1月21日 (2008.1.21)

(65) 公開番号 特開2009-171479 (P2009-171479A)

(43) 公開日 平成21年7月30日 (2009.7.30)

審査請求日 平成22年11月26日 (2010.11.26)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100100310

弁理士 井上 学

(74) 代理人 100098660

弁理士 戸田 裕二

(72) 発明者 林 昌宏

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 マイクロデバイス事業部内

(72) 発明者 吉永 真樹

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 マイクロデバイス事業部内

最終頁に続く

(54) 【発明の名称】 演算増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

差動入力信号のレベルを変換して差動出力するレベル変換回路と、

前記レベル変換回路の差動出力が入力される差動増幅器と、

前記差動増幅器の出力に入力が接続される出力段と、

を備えて構成され、

前記レベル変換回路と前記差動増幅器との組合せが、前記差動入力信号のレベル差の検出と、該レベル差に応じた前記出力段に対する駆動能力の制御とを共通に行い、

前記レベル変換回路は、

前記差動入力信号の一方を入力とし、前記入力に所定の電圧を加えた第1の電位と前記第1の電位より高電位の第2の電位を出力する第1の出力対と、

前記差動入力信号の他方を入力とし、前記所定の電圧を加えた第3の電位と前記第3の電位より高電位の第4の電位を出力する第2の出力対とを有し、

前記差動増幅器は、

前記第2の電位及び前記第4の電位の出力を入力とし、それぞれの一端が第1の接続部で互いに接続される第1導電型トランジスタの差動対と、

前記第1の電位及び前記第3の電位の出力を入力とし、それぞれの一端が第2の接続部で互いに接続される第2導電型トランジスタの差動対と、

前記第1導電型トランジスタの差動対それぞれの他端が接続される第1の電流電圧変換回路と、

10

20

前記第2導電型トランジスタの差動対それぞれの他端が接続される第2の電流電圧変換回路と、

前記第1導電型トランジスタの差動対及び前記第2導電型トランジスタの差動対に流れる電流を低減する駆動電流制御回路と、を有し、

前記第1の電流電圧変換回路は第1の電源に接続され、

前記第2の電流電圧変換回路は前記第1の電源より低電位の第2の電源に接続され、

前記第1の接続部と前記第2の接続部とが、前記駆動電流制御回路を介して前記第1の電源と前記第2の電源に対して直列に接続されていることを特徴とする演算増幅器。

#### 【請求項2】

請求項1において、

10

前記第1導電型トランジスタの差動対は、前記第2の電位及び前記第4の電位の出力がゲートに入力され、ソース同士が前記第1の接続部で接続されるN型MOSトランジスタの差動対であり、

前記第2導電型トランジスタの差動対は、前記第1の電位及び前記第3の電位の出力がゲートに入力され、ソース同士が前記第2の接続部で接続されるP型MOSトランジスタの差動対であり、

前記N型MOSトランジスタの差動対それぞれのドレインが前記第1の電流電圧変換回路に接続され、

前記P型MOSトランジスタの差動対それぞれのドレインが前記第2の電流電圧変換回路に接続され、

20

前記駆動電流制御回路により、前記N型MOSトランジスタの差動対及び前記P型MOSトランジスタの差動対のゲート-ソース間電圧が減少することを特徴とする演算増幅器。

#### 【請求項3】

請求項1において、

前記駆動電流制御回路は抵抗素子を含んで構成されていることを特徴とする演算増幅器。

#### 【請求項4】

請求項1において、

前記第1導電型トランジスタの差動対それぞれの一端に、前記第1の接続部に対して第1の耐圧保護素子が直列に接続され、

30

前記第2導電型トランジスタの差動対それぞれの一端に、前記第2の接続部に対して第2の耐圧保護素子が直列に接続されていることを特徴とする演算増幅器。

#### 【請求項5】

請求項1において、

前記差動入力信号が無い定常状態にて前記第1の電流電圧変換回路の出力電圧を第1の所定電圧以下に抑えるための第1の抵抗素子が、前記第1の電流電圧変換回路の出力と前記第1の電源間に接続され、

前記差動入力信号が無い定常状態にて前記第2の電流電圧変換回路の出力電圧を第2の所定電圧以下に抑えるための第2の抵抗素子が、前記第2の電流電圧変換回路の出力と前記第2の電源間に接続され、

40

前記第1の所定電圧は、前記出力段を構成する第1のトランジスタに電流が流れない状態になるための閾値電圧であり、

前記第2の所定電圧は、前記出力段を構成する第2のトランジスタに電流が流れない状態になるための閾値電圧であることを特徴とする演算増幅器。

#### 【請求項6】

請求項1において、

前記レベル変換回路は、

前記第1の電源に接続される電流源とドレインが前記第2の電源に接続されるMOSトランジスタとの間に、ドレインとゲートを接続したP型MOSトランジスタ及びドレイン

50

とゲートを接続したN型MOSトランジスタとを含んで構成され、

前記出力段は、

前記第1の電流電圧変換回路の出力を入力とするソース接地P型MOSトランジスタと、前記第2の電流電圧変換回路の出力を入力とするソース接地N型MOSトランジスタを備えることを特徴とする演算増幅器。

【請求項7】

請求項1において、

前記第1の電流電圧変換回路は、前記第1導電型トランジスタの差動対それぞれのドレンにそれぞれのドレンが接続され、かつ、前記第1導電型トランジスタの差動対の一方のドレンに共通のゲートが接続され、かつ、前記第1導電型トランジスタの差動対の他方のドレンが出力となっている第1の能動負荷トランジスタ対を含んで構成され、

10

前記第2の電流電圧変換回路は、前記第2導電型トランジスタの差動対それぞれのドレンにそれぞれのドレンが接続され、かつ、前記第2導電型トランジスタの差動対の一方のドレンに共通のゲートが接続され、かつ、前記第2導電型トランジスタの差動対の他方のドレンが出力となっている第2の能動負荷トランジスタ対を含んで構成されることを特徴とする演算増幅器。

【請求項8】

請求項4において、

前記第1および第2の耐圧保護素子はダイオードを含んで構成されていることを特徴とする演算増幅器。

20

【請求項9】

請求項4において、

前記第1および第2の耐圧保護素子はMOSトランジスタを含んで構成されていることを特徴とする演算増幅器。

【請求項10】

入力信号の電位を変換して第1の電位と前記第1の電位より高電位の第2の電位を出力する第1のレベル変換回路と、

前記入力信号の電位を変換して第3の電位と前記第3の電位より高電位の第4の電位を出力する第2のレベル変換回路と、

前記第2の電位及び前記第4の電位の出力がゲートに入力され、ソース同士が前記第1の接続部で接続されるN型MOSトランジスタの差動対と、

30

前記第1の電位及び前記第3の電位の出力がゲートに入力され、ソース同士が前記第2の接続部で接続されるP型MOSトランジスタの差動対と、

前記N型MOSトランジスタの差動対それぞれのドレンが接続される第1の電流電圧変換回路と、

前記P型MOSトランジスタの差動対それぞれのドレンが接続される第2の電流電圧変換回路と、

前記第1及び第2の電流電圧変換回路の出力と電気的に接続され、前記第1及び第2の電流電圧変換回路により制御される出力段と、

前記N型MOSトランジスタの差動対及び前記P型MOSトランジスタの差動対に流れ

る電流を低減する駆動電流制御回路と、を有し、

40

前記第1の電流電圧変換回路は第1の電源に接続され、

前記第2の電流電圧変換回路は前記第1の電源より低電位の第2の電源に接続され、

前記第1の接続部と前記第2の接続部とが、前記駆動電流制御回路を介して前記第1の電源と前記第2の電源に対して直列に接続されていることを特徴とする演算増幅器。

【請求項11】

請求項10において、

前記駆動電流制御回路により、前記N型MOSトランジスタの差動対及び前記P型MOSトランジスタの差動対に流れる電流によって電位降下が発生して、前記ゲート-ソース間の電圧が減少することを特徴とする演算増幅器。

50

**【請求項 12】**請求項 10 において、前記駆動電流制御回路は抵抗素子を含んで構成されていることを特徴とする演算増幅器

。

**【請求項 13】**請求項 10 において、前記N型MOSトランジスタの差動対それぞれのソースに、前記第1の接続部に対して第1の耐圧保護素子が直列に接続され、前記P型MOSトランジスタの差動対それぞれのソースに、前記第2の接続部に対して第2の耐圧保護素子が直列に接続されていることを特徴とする演算増幅器。

10

**【請求項 14】**請求項 10 において、前記入力信号差が無い定常状態にて前記第1の電流電圧変換回路の出力電圧を第1の所定電圧以下に抑えるための第1の抵抗素子が、前記第1の電流電圧変換回路の出力と前記第1の電源間に接続され、前記入力信号差が無い定常状態にて前記第2の電流電圧変換回路の出力電圧を第2の所定電圧以下に抑えるための第2の抵抗素子が、前記第2の電流電圧変換回路の出力と前記第2の電源間に接続され、前記第1の所定電圧は、前記出力段を構成する第1のトランジスタに電流が流れない状態になるための閾値電圧であり、

20

前記第2の所定電圧は、前記出力段を構成する第2のトランジスタに電流が流れない状態になるための閾値電圧であることを特徴とする演算増幅器。**【請求項 15】**請求項 10 において、前記第1及び第2のレベル変換回路それぞれは、前記第1の電源に接続される電流源とドレインが前記第2の電源に接続されるMOSトランジスタとの間に、ドレインとゲートを接続したP型MOSトランジスタ及びドレインとゲートを接続したN型MOSトランジスタとを含んで構成され、前記出力段は、前記第1の電流電圧変換回路の出力を入力とするソース接地P型MOSトランジスタと、前記第2の電流電圧変換回路の出力を入力とするソース接地N型MOSトランジスタを備えることを特徴とする演算増幅器。

30

**【請求項 16】**請求項 10 において、前記第1の電流電圧変換回路は、前記N型MOSトランジスタの差動対それぞれのドレインにそれぞれのドレインが接続され、かつ、前記N型MOSトランジスタの差動対の一方のドレインに共通のゲートが接続され、かつ、前記N型MOSトランジスタの差動対の他方のドレインが出力となっている第1の能動負荷トランジスタ対を含んで構成され、前記第2の電流電圧変換回路は、前記P型MOSトランジスタの差動対それぞれのドレインにそれぞれのドレインが接続され、かつ、前記P型MOSトランジスタの差動対の一方のドレインに共通のゲートが接続され、かつ、前記P型MOSトランジスタの差動対の他方のドレインが出力となっている第2の能動負荷トランジスタ対を含んで構成されるこ

とを特徴とする演算増幅器。

40

**【請求項 17】**請求項 13 において、前記第1および第2の耐圧保護素子はダイオードを含んで構成されていることを特徴とする演算増幅器。**【請求項 18】**請求項 13 において、前記第1および第2の耐圧保護素子はMOSトランジスタを含んで構成されていること

50

を特徴とする演算増幅器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は演算増幅器に関し、特に電源電圧が高く駆動力の高い演算増幅器に関する。

【背景技術】

【0002】

従来、演算増幅器として、電流源に並列に2つの素子が接続され、その2つの素子の間に入力レベル差があるときのみ電流源の電流供給能力を増加する構成を有するものがあつた（例えば、特許文献1～3参照）。

10

【0003】

また、従来、演算増幅器として、ボルテージホロワの入力レベル差、すなわち、入力と出力とのレベル差が所定の値を超えたとき電流源の電流供給能力を増加する構成を有するものがあつた（例えば、特許文献4および5参照）。

【0004】

【特許文献1】特開平11-136044号公報

【特許文献2】特開2004-128815号公報

【特許文献3】特開平11-88076号公報

【特許文献4】特開2006-157607号公報

【特許文献5】特開2000-349570号公報

20

【発明の開示】

【発明が解決しようとする課題】

【0005】

演算増幅器は様々な用途で用いられるが、大きな容量性負荷を駆動するためのバッファ回路としても使用される。このような用途において、多数の駆動力の高い演算増幅器を一つのICに集積することが求められる。駆動力を高くするためには、演算増幅器の駆動電流を増加させればよいが、消費電力の増加が問題となる。

【0006】

高いスルーレートと低消費電力化の両立を図る手段として、電源電圧が低い（例えば5V以下である）応用においては、演算増幅器の入力電位差を検出する回路を用い、入力電位差を検出した時に駆動力制御回路により演算増幅器の動作電流を増加させるものがあつた。入力信号に変化が無い期間は駆動電流を少なくし、入力信号が変化したことを検出した場合のみ駆動電流を増加させることにより、非動作時の消費電力を低減しながら、動作時の高スルーレートを実現している。このような考え方に基づく方式は、電源電圧が低い（例えば5V以下である）応用においては従来から提案されており、その方式の一つとして、電流源に並列に2つの素子が接続され、その2つの素子の間に入力レベル差があるときのみ電流源の電流供給能力を増加する構成を有するもの（特許文献1～3など）や、ボルテージホロワの入力レベル差、すなわち、入力と出力とのレベル差が所定の値を超えたとき電流源の電流供給能力を増加する構成を有するもの（特許文献4、5など）があつた。

30

【0007】

これらの方では、信号を増幅する回路に加えて検出回路や制御回路が別に必要となる。検出回路や制御回路は信号を増幅する回路（信号増幅回路）や出力を駆動する回路（出力駆動回路）と並列に設けられるため、電力を消費する。この追加された回路（追加回路）の消費電力は、電源電圧が比較的低い応用においては影響が小さいため、充分な効果を得ることができた。

【0008】

これまでに述べたように、電源電圧が、例えば5V以下であるような、比較的低い電圧での応用における演算増幅器の低消費電力化は、既に提案されている入力電位差（入力レベル）検出回路や制御回路を用いる方式で対応可能であった。しかし、電源電圧の低い場

40

50

合に比べて、電源電圧が高い場合、例えば5V以上である場合には消費電力は電源電圧に比例するため、信号增幅回路や出力駆動回路と並列に設けられる追加回路が定常的に消費する電流による発熱の影響が大きくなるという問題があること、さらには、多数の演算增幅器を一つのICに集積することが要求された場合に、消費電力による発熱が原因で集積できる回路数が制限されてしまうという問題があることを、本発明の発明者らは独自に見出した。その結果、入力電位差を検出して演算增幅器の駆動力を制御する方式を電源電圧の高い応用において上記の問題を解消しつつ行うためには、駆動力の制御に必要な回路が定常的に消費する電力をさらに低減する必要があるという課題があることが新たに判明した。

#### 【0009】

10

一方、上記の特許文献1～5は、いずれも低圧回路を前提とした構成を開示しているため、当然ながら、駆動力の制御に必要な回路が定常的に消費する電力をさらに低減する必要があるという上記の課題について、一切、開示していない。そのため、その課題を解決するための手段についても、一切、開示していない。

#### 【0010】

本発明は上記の課題を解決するためのものであり、比較的高い電源電圧（例えば5V以上）で使用される演算增幅器において、定常動作時の消費電力を低減しながらスルーレートが改善される回路方式を提供することを目的としている。

#### 【課題を解決するための手段】

#### 【0011】

20

本発明の代表的なものの一例を示せば以下の通りである。すなわち、本発明の演算增幅器は、差動入力信号のレベルを変換して差動出力するレベル変換回路と、前記レベル変換回路の差動出力に入力が直列接続された差動増幅器とを備えて構成され、前記レベル変換回路と前記差動増幅器との組合せが、前記差動入力信号のレベル差の検出と、該レベル差に応じた前記差動増幅器の出力段に対する駆動能力の制御とを共通に行うことを特徴とする。

#### 【0012】

30

より具体的に言えば、本発明の演算増幅器は、入力信号の電位を変換して2つの電位を出力する第一および第二のレベル変換回路と、前記第一、第二のレベル変換回路の2つある出力のうち、直流電位の高い側の出力を入力とし、ソースを共通接続した第一の差動トランジスタ対と、もう一方の直流電位の低い側の出力を入力とし、ソースを共通接続した第二の差動トランジスタ対との互いのソース同士が電気的に接続されて成る差動トランジスタ対回路と、前記第一および第二の差動トランジスタ対の各々のドレインとそれぞれ接続された第一および第二の電流電圧変換回路と、前記第一および第二の電流電圧変換回路の出力と電気的に接続され、かつ、該第一および第二の電流電圧変換回路によって制御される出力段とを備えて構成されていることを特徴とする。

#### 【発明の効果】

#### 【0013】

40

本発明によれば、比較的高い電源電圧（例えば5V以上）で使用される演算増幅器において、定常動作時の消費電力を低減しながらスルーレートを改善することが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0014】

本発明の1つの顕著な特徴は、レベル変換回路と入力段差動増幅器とを直列に接続し、これらの組合せで入力レベルの検出と入力信号の増幅（出力段を駆動する能力の制御）とを共通に行う点である。上述の特許文献1～5に開示される構成は、いずれも入力レベル検出回路が、入力段増幅器とは別に、かつ、それに対して並列に接続されているが、本発明はその別個の入力レベル検出回路を省略できる分、レベル変換回路の追加接続による消費電力の増加分のみに抑えることができ、もって演算増幅器全体の消費電力の低減が可能となる。入力レベルの検出と入力信号の増幅とを共通に行うことが可能なのは、高圧回路においては直流電圧に余裕があるためである。直流電圧に余裕のない低圧回路を前提とし

50

た上述の特許文献 1 ~ 5 記載の構成は、入力段増幅回路に対して直列にレベル変換回路を設けることができないが、高圧回路への応用を目的とした本発明においては、それが可能となる。

【0015】

次に、本発明の好適な実施形態について、以下、実施例として図を用いて説明する。

【実施例1】

【0016】

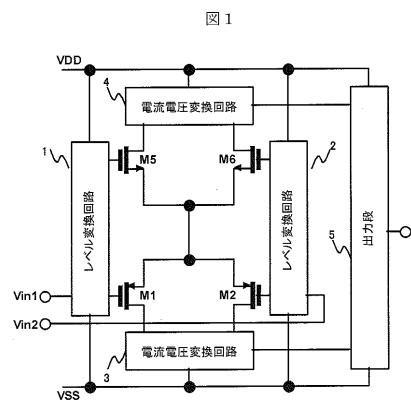

図 1 は本発明の基本原理を示すブロック図である。入力信号  $V_{in1}$ ,  $V_{in2}$  はそれぞれレベル変換回路 1, 2 に入力される。レベル変換回路は 2 つの出力を持ち、それぞれ PMOS 差動対、NMOS 差動対に出力される。PMOS トランジスタ M1, M2 と NMOS トランジスタ M5, M6 はそれぞれ差動トランジスタ対を構成している。M1 と M2 のドレインは電流電圧変換回路 3 に、M5 と M6 のドレインは電流電圧変換回路 4 と接続される。電流電圧変換回路は、差動トランジスタ対の出力電流を電圧に変換して、出力段 5 を駆動する。

【0017】

一般的な演算増幅器では、差動トランジスタ対は定電流源によってバイアスされる。このため、差動トランジスタ対の消費電流を制御するためには、定電流源を制御する必要があった。一方、本発明ではレベル変換回路を用いることで、M1 と M2、M5 と M6 の差動トランジスタ対同士を直列に接続している。この構成をとることで、 $V_{in1} = V_{in2}$  の場合には、レベル変換回路の 2 つの出力電圧差により、2 組の差動トランジスタ対のゲート ソース間電圧を制御することができる。 $V_{in1} = V_{in2}$  の場合、差動トランジスタ対で消費する電流は、2 組の差動トランジスタ対のゲート ソース間電圧、つまりレベル変換回路の 2 つの出力電圧差によって決まる。よって、レベル変換回路の出力電圧差を、2 組の差動トランジスタ対を構成する P 型、N 型 MOS トランジスタのスレッショルド電圧の和以下に設定することで、定常時の消費電流の低減が実現できる。また、入力信号に差が生じた場合、 $V_{in1} < V_{in2}$  では M1 と M6、 $V_{in1} > V_{in2}$  では M2 と M5 のゲート ソース間電圧がスレッショルド電圧以上となる。入力信号差に M1 と M6、または M2 と M5 のゲート ソース間電圧は比例する。よって、入力信号差に比例した駆動電流の制御が可能となっている。

【0018】

回路動作を、入力信号差の無い定常状態と差が生じた動作状態に分けて説明する。

【0019】

最初に入力信号差の無い場合、つまり  $V_{in1}$  と  $V_{in2}$  が等しい場合について説明する。入力信号  $V_{in1}$  と  $V_{in2}$  はそれぞれレベル変換回路 1、レベル変換回路 2 に入力されている。レベル変換回路はある一定の電圧を入力された電圧に加算して M5 と M6 で構成される PMOS 差動対と M1 と M2 で構成される NMOS 差動対に出力する。このとき、前記 PMOS 差動対と前記 NMOS 差動対に出力される電位の差分は、差動対を構成する PMOS と NMOS のスレッショルド電圧の和程度に設定することが望ましい。差動対に流れる電流は、レベル変換回路の 2 つある出力の電圧差と差動対を構成する PMOS と NMOS の特性で決まっており、上記のように設定することにより、入力信号差が無い状態では定常電流をほとんど流さない状態に制御することが可能である。

【0020】

次に、入力信号に差が生じた動作状態について説明する。 $V_{in1} > V_{in2}$  の場合を考える。レベル変換回路は、入力信号に一定の電圧を加えた 2 つの電位を出力するため、M1 のゲート電位は M2 のゲート電位よりも ( $V_{in1} - V_{in2}$ ) 高く、M5 のゲート電位も M6 のゲート電位よりも ( $V_{in1} - V_{in2}$ ) 高くなる。入力信号に差が無い状態で、レベル変換回路の出力電位差が 2 つの差動トランジスタ対を形成する PMOS と NMOS のスレッショルド電圧の和に設定されているとする。M6 のゲートと M1 のゲートとの間にかかる電圧は、PMOS と NMOS のスレッショルド電圧の和よりも ( $V_{in1} - V_{in2}$ ) 小さくなる。よって、M1 と M6 はオフ状態となる。一方、M5 のゲートと

10

20

30

40

50

M2のゲートにかかる電圧は、PMOSとNMOSのスレッショルド電圧の和よりも( $V_{in1} - V_{in2}$ )大きくなる。よって、M2とM5はオン状態となり、駆動電流が流れる。駆動電流は電流電圧変換回路3、4により電圧に変換され、出力段を制御する。 $V_{in1} < V_{in2}$ の場合、同様にM5のゲートとM2のゲートとの間にかかる電圧は、PMOSとNMOSのスレッショルド電圧の和よりも( $V_{in1} - V_{in2}$ )小さくなる。よって、M2とM5はオフ状態となる。一方、M6のゲートとM1のゲートにかかる電圧は、PMOSとNMOSのスレッショルド電圧の和よりも( $V_{in1} - V_{in2}$ )大きくなる。よって、M1とM2はオン状態となり、駆動電流が流れる。この電流は電流電圧変換回路で電圧信号に変換され、出力段を制御する。

【実施例2】

10

【0021】

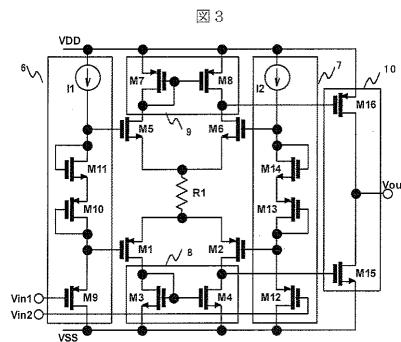

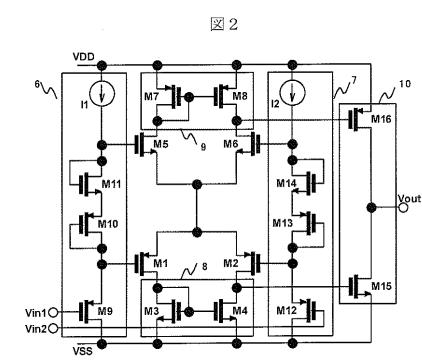

図2に本発明の別の実施例を示す。PMOSトランジスタM1、M2とNMOSトランジスタM5、M6はそれぞれ差動トランジスタ対を構成している。差動トランジスタ対のドレインは、それぞれNMOSトランジスタM3とM4で構成される能動負荷8とPMOSトランジスタM7、M8から成る能動負荷9に接続されている。トランジスタM9、M10、M11と電流源I1はレベル変換回路6を、トランジスタM12、M13、M14と電流源I2はレベル変換回路7を構成しており、M9とM12のゲートにそれぞれ信号 $V_{in1}$ と $V_{in2}$ が入力されている。NMOSトランジスタM15とPMOSトランジスタM16は出力段10を構成しており、M15、M16ともにソース接地で構成することにより高い駆動力と広い出力範囲の実現が可能である。また、ソース接地で出力段を構成しているため、負荷が容量性の場合には定常状態の場合にM15とM16をオフさせて電流が流れる経路を無くし、出力電圧を一定に保つことが可能である。これにより、定常状態では出力段で消費する電流を無くすことができる。本発明では差動トランジスタ対を直列に接続する構成を取っているため、差動対から電流電圧変換回路を用いて2つの出力を取り出すことにより、回路を追加することなく出力段をソース接地一般的なソースフォロワや電流源負荷のソース接地形式では定常的に電流を流す必要があるため、低電力化が可能となる。なお、本実施例では、レベル変換回路の出力電圧差をMOSトランジスタと定電流源で決定したが、電位差を発生させることができれば良いため、抵抗やバイポーラトランジスタを用いて構成することもできる。抵抗の抵抗値は任意に決定できるため、MOSトランジスタよりも詳細にレベル変換回路の出力電圧を設定できるという利点を持つ。バイアス電流源と入力トランジスタの位置関係も任意に組替えが可能である。また、出力段は、MOSトランジスタによるソース接地形式を用いたが、他の形式を用いることもできる。一例として、バイポーラトランジスタに置き換えることもできる。これにより、駆動力が増加するといった効果が得られる。電流電圧変換回路も、本実施例では能動負荷形式を用いたが、抵抗負荷など別の形式で構成してもよい。

20

【0022】

30

図2の回路動作を、入力信号差の無い定常状態と差が生じた動作状態に分けて説明する。

【0023】

40

最初に入力信号差の無い場合、つまり $V_{in1}$ と $V_{in2}$ が等しい場合について説明する。入力信号 $V_{in1}$ と $V_{in2}$ はそれぞれレベル変換回路6のM9、レベル変換回路7のM12のゲートに入力されている。M9に入力された $V_{in1}$ は、定電流源I1とM9によって決まるゲートソース電圧を加えた電位を差動トランジスタ対のM1へのゲートへ出力される。また、前記の電位にI1とダイオード接続されたM10、M11によって決まる電圧を加えたものがM5に出力される。回路形式は対称であり、M1とM2のゲート電位、及びM5とM6のゲート電位は等しい。このときに差動トランジスタ対に流れる定常電流は、レベル変換回路の2つの出力電位差と2つの差動トランジスタ対のトランジスタによって決まる。

【0024】

この実施例においては、レベル変換回路のM1とM10、M5とM11のサイズ比は同

50

じにすることにより、定常消費電流の制御が可能である。サイズ比を同じにすることで差動トランジスタ対のゲート ソース間電圧が決まり、サイズ比と  $I_1$  で決まる電流が定常電流として流れる。レベル変換部のトランジスタサイズと差動トランジスタ対のMOSサイズを  $m : n$  にしたとする。この時、入力電圧差が無い場合の定常電流としては、 $n / m * I_1$  となる。回路は対称であるので、M2とM13, M6とM14のサイズ比に関しても同じとする。レベル変換回路の2つの出力電位差を生成する回路を、差動トランジスタ対と同様のNMOSとPMOSを直列接続した構成とすることにより、プロセスや温度の変動に対しても、レベル変換回路と差動トランジスタ対が変化を打ち消す方向に変化するようにし、定常電流の変化を小さくできる。

【0025】

10

次に、入力信号に差が生じた動作状態について説明する。 $V_{in1} > V_{in2}$  の場合を考える。レベル変換回路は、入力信号に一定の電圧を加えた2つの電位を出力するため、M1のゲート電位はM2のゲート電位よりも $V_{in1} - V_{in2}$ だけ高く、M5のゲート電位もM6のゲート電位よりも $V_{in1} - V_{in2}$ だけ高くなる。入力信号に差が無い状態で、レベル変換回路の出力電位差が2つの差動トランジスタ対を形成するPMOSとNMOSのスレッショルド電圧の和に設定されているとする。M6のゲートとM1のゲートとの間にかかる電圧は、PMOSとNMOSのスレッショルド電圧の和よりも $V_{in1} - V_{in2}$ だけ小さくなる。よって、M1とM6はオフ状態となる。一方、M5のゲートとM2のゲートにかかる電圧は、PMOSとNMOSのスレッショルド電圧の和よりも $V_{in1} - V_{in2}$ だけ大きくなる。よって、M2とM5はオン状態となり、駆動電流が流れる。M5を流れた電流はM7とM8で構成される能動負荷によりミラーされ、M16をオフさせる。M2を流れた電流はM3とM4で構成される能動負荷によりミラーされ、M15をオンさせる。

【実施例3】

【0026】

20

図3に本発明の別の実施例を示す。図3では駆動電流制御回路として抵抗R1を用いている。ここでは抵抗を用いることで、差動トランジスタ対に流れる電流によって電位降下が発生してゲート ソース間電圧が減少し、消費電流の低減が可能である。レベル変換回路と差動トランジスタ対以外に駆動電流を制御できるパラメータが増え、定常電流と動作時の駆動力制御の調整が可能となる。R1を大きくした場合、差動トランジスタ対に流れる定常電流と動作時に流れる電流も減少する。なお、図2では駆動電流制御回路として抵抗を用いたが、トランジスタやその他の受動素子等を用いても構わない。

【実施例4】

【0027】

30

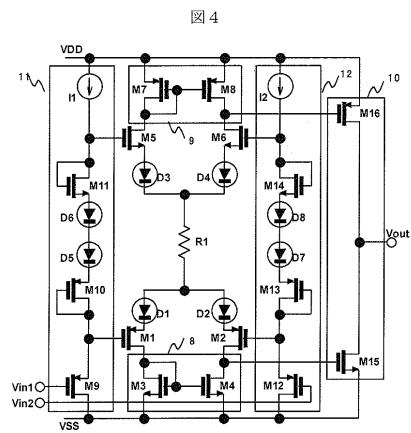

図4に本発明の別の実施例を示す。差動対に用いているトランジスタのゲート ソース間耐圧以上の入力電圧振幅差が入力された場合、トランジスタが破壊されてしまう。本発明は電源電圧が比較的高い場合の応用を想定しているため、ゲート ソース間の耐圧がドレイン ソース間耐圧よりも低いトランジスタを使用した場合には、耐圧を超える可能性がある。これを防ぐために、本実施例では耐圧保護のために耐圧保護素子の一例としてダイオードD1～D8を追加している。耐圧保護用ダイオードの働きを説明するため、 $V_{in1} > V_{in2}$  の場合を考える。 $V_{in1} - V_{in2}$  がトランジスタM1, M2, M5, M6のゲート ソース耐圧の2倍以上であるとする。このとき、M2とM5はオン状態、M1とM6はオフ状態である。M2とM5には電流が流れしており、R1で電位降下が発生するため、適切なR1を選べばM2とM5への過電圧印加を防ぐことができる。一方、オフ状態のM1とM6のそれぞれのゲート間には、 $V_{in1} - V_{in2}$  がそのままM1とM6のゲート ソース間に加わってしまう。このため、差動対のソース部分に耐圧保護ダイオードD1, D2, D3, D4を設置し、これを介してPMOSとNMOSの差動対を接続する。これにより、オフ状態のM1とM6のゲート ソース間には電圧がかからず、 $V_{in1} - V_{in2}$  のほとんどがD1とD6に印加される。よって、M1とM6の破壊を防ぐことが可能になる。レベル変換回路の耐圧保護ダイオードD5, D6, D7, D8は、

40

50

それぞれ D 1 , D 3 , D 2 , D 4 に対応しており、温度が変動した場合などに差動対とレベル変換回路の特性が同様に変化するように対応させたもので、耐圧保護が目的では無い。よって、レベル変換回路部の耐圧保護ダイオードは省略可能である。また、耐圧保護素子はダイオードに限定されず、想定される過電圧に耐えられる耐圧を持つMOSトランジスタを耐圧保護素子として用いても構わない。

【実施例 5】

【0028】

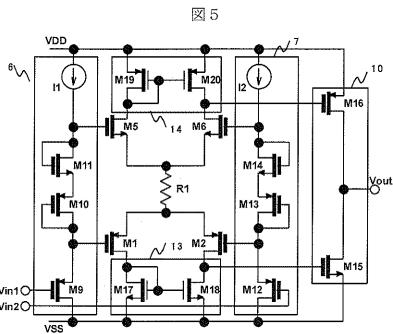

図 5 に本発明の別の実施例を示す。演算増幅器が大きな負荷を駆動する場合、出力段の MOS トランジスタサイズは演算増幅器を構成する他のトランジスタよりも大きいため、10 入力電圧差の無い定常状態で出力段の MOS トランジスタのゲート-ソース間にスレッショルド電圧  $V_{th}$  以上の電圧が入力されると、出力段にはトランジスタサイズに比例した電流が流れるため、消費電力が問題となる。この実施例では、電流電圧変換回路 13 を構成する NMOS トランジスタ M 17 , M 18 を、出力段の NMOS トランジスタ M 15 よりも  $V_{th}$  が低いトランジスタで構成している。同様に、電流電圧変換回路 14 を構成する PMOS トランジスタ M 19 , M 20 を、出力段の PMOS トランジスタ M 16 よりも  $V_{th}$  が低いトランジスタで構成している。入力電圧差の無い定常状態においては、出力段の PMOS 、 NMOS が消費する電流は、定常状態で電流電圧変換回路が出力する電圧 20 、つまり、出力段の MOS トランジスタのゲート-ソース間電圧によって決まる。このため、電流電圧変換回路を構成する MOS トランジスタの  $V_{th}$  を、出力段を構成する MOS トランジスタの  $V_{th}$  よりも低くすることで、定常状態における電流電圧変換回路の出力電圧を、出力段の MOS トランジスタの  $V_{th}$  以下に設定することができ、出力段の MOS トランジスタをオフした状態にすることが可能となる。なお、本実施例とは逆に出力段の  $V_{th}$  を高くしても良い。

【実施例 6】

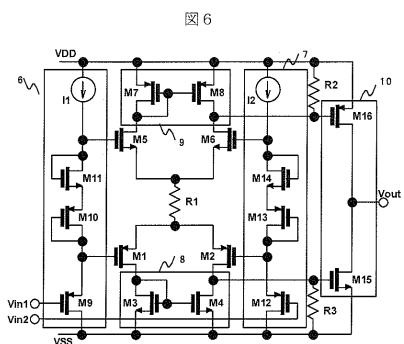

【0029】

図 6 に本発明の別の実施例を示す。本実施例では、電流電圧変換回路 8 , 9 の出力に抵抗  $R_2$  ,  $R_3$  を接続している。この抵抗を追加することにより、図 5 の実施例で説明したように、定常状態における電流電圧変換回路の出力電圧を、出力段の MOS トランジスタの  $V_{th}$  以下にして、定常的な出力段での消費電流を低減している。  $R_2$  と  $R_3$  の抵抗値は、差動トランジスタ対に流れる電流に対して設計する必要がある。入力信号に信号差が生じた場合、差動トランジスタ対が駆動電流を流すが、抵抗  $R_2$  ,  $R_3$  の抵抗値を駆動電流に対して小さくしすぎた場合、駆動電流が抵抗を流れてしまうことで出力段のトランジスタのゲート-ソース間電圧が低くなり、充分な駆動力を得られなくなる。また、本実施例では抵抗  $R_1$  を駆動電流制限回路として用いているが、省略も可能である。30

【実施例 7】

【0030】

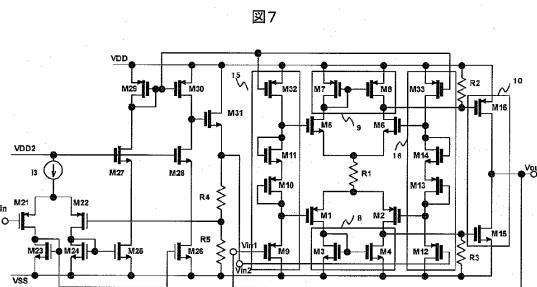

図 7 に本発明の別の実施例を示す。この回路は、  $V_{in}$  から入力された電圧を、抵抗  $R_4$  ,  $R_5$  の抵抗値を  $r_4$  ,  $r_5$  とすると、  $(r_4 + r_5) / r_5$  倍し、本発明の演算増幅器をボルテージホロワとして用いたバッファを介して出力している。この回路では、レベル変換回路の低電力化を行うため、演算増幅器の前段の情報を用いてバイアス電流を制御している。なお、演算増幅器前段の増幅回路の構成は、実施例の形式に限定されない。40

【0031】

回路動作を説明する。電源  $V_{DD2}$  -  $V_{SS}$  間の入力信号  $V_{in}$  は、定電流限  $I_3$  によってバイアスされた差動トランジスタ対 M 21 , M 22 によって電流に変換される。変換された電流は、M 23 と M 25 、 M 24 と M 26 のカレントミラー対によって折り返される。 M 25 で折り返された電流は、ゲート接地回路 M 27 を介して  $V_{DD2}$  よりも高い電源  $V_{DD}$  に接続されたカレントミラー M 29 , M 30 で再び折り返される。この電流は、M 26 によって折り返された電流と比較され、ソースフォロワを構成する M 31 に入力される。抵抗  $R_4$  ,  $R_5$  で分圧された電圧が  $V_{in}$  と等しくなるように帰還がかかるため、ソースフォロワの出力電位は、  $V_{in}$  の  $(r_4 + r_5) / r_5$  倍となる。この電圧は、ボ

ルテージホロワとして用いられる本発明の演算増幅器に入力され、バッファされて出力される。演算増幅器のレベル変換回路 15, 16 は、前段の M29, M30 で構成されるカレントミラーを用いて、バイアス電流を生成している。演算増幅器の入力  $V_{in1}$ ,  $V_{in2}$  が増加したときには、M32, M33 が流すバイアス電流がレベル変換回路出力の動作速度が遅くなってしまうため、バイアス電流を多く流すことが求められる。一方。 $V_{in1}$ ,  $V_{in2}$  が減少したときには、M9, M12 がレベル変換回路の動作速度を決定するため、バイアス電流は小さくても良い。また、変化しないときには、レベル変換回路は定常状態であるため電流は少なくても良い。このように、レベル変換回路のバイアス電流が動作速度を決めているのは、演算増幅器の入力電圧が増加する場合である。前段の M29 に流れる電流は、演算増幅器の入力電圧が増加する場合に多く、減少または入力が等しい場合には減少するので、M29 を用いてレベル変換回路の電流を生成することで、定常状態での電力消費量を減少させることができる。 10

#### 【0032】

以上、本発明の各実施例によれば、レベル変換回路を用いることで入力信号差の検出回路と駆動能力制御回路を従来のような並列接続ではなく直列接続で実現したことにより、入力電圧が等しいときには演算増幅器で消費する電流を減らすことで消費電力を低減し、入力電圧に差が生じた時には演算増幅器で消費する電流を増加させ、スルーレートを改善することが可能となる。

#### 【0033】

尚、本発明の各実施例において、トランジスタは MOS を用いたが、バイポーラトランジスタで構成することも可能である。また、各実施例で用いた変形は、互いに組み合わせても有効である。レベル変換回路は上部電源側からバイアス電流を与えたが、下部電極側から与えてもよい。入力に関しても同様で、実施例では下部電源側から入力したが、上部電極側から入力しても良い。

#### 【図面の簡単な説明】

#### 【0034】

【図1】本発明の演算増幅器の基本原理を示すブロック図である。

【図2】本発明の演算増幅器の一実施例図である。

【図3】本発明の演算増幅器に駆動電流制御回路を加えた一実施例図である。

【図4】本発明の演算増幅器に耐圧保護用回路を加えた一実施例図である。 30

【図5】本発明の演算増幅器に駆動段低消費電力化を加えた一実施例図である。

【図6】本発明の演算増幅器に駆動力制御のための抵抗を加えた一実施例図である。

【図7】本発明の演算増幅器にレベル変換回路の低消費電力化を加えた一実施例図である。

#### 【符号の説明】

#### 【0035】

1, 2, 6, 7, 11, 12, 15, 16 レベル変換回路、

3, 4, 8, 9, 13, 14 電流電圧変換回路、

5, 10 出力段、

M1, M2, M7, M8, M9, M10, M12, M13, M16, M19, M20, 40

M21, M22, M29, M30 PMOS、

M3, M4, M5, M6, M9, M10, M11, M14, M15, M17, M18,

M23, M24, M25, M26, M27, M28, M31 NMOS、

I1, I2, I3 定電流源、

D1 ~ D8 耐圧保護用ダイオード、

R1, R2, R3, R4, R5 抵抗。

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

---

フロントページの続き

(72)発明者 松本 隆

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 マイクロデバイス事業部内

審査官 高橋 義昭

(56)参考文献 米国特許第06262633(US, B1)

米国特許第05343164(US, A)

特開2000-293997(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03F 3/45