(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4723888号

(P4723888)

(45) 発行日 平成23年7月13日(2011.7.13)

(24) 登録日 平成23年4月15日(2011.4.15)

(51) Int.Cl.

H03L 7/093 (2006.01)

F 1

H03L 7/08

E

請求項の数 10 (全 13 頁)

(21) 出願番号 特願2005-85252 (P2005-85252)

(22) 出願日 平成17年3月24日 (2005.3.24)

(65) 公開番号 特開2005-278191 (P2005-278191A)

(43) 公開日 平成17年10月6日 (2005.10.6)

審査請求日 平成20年1月22日 (2008.1.22)

(31) 優先権主張番号 10/808864

(32) 優先日 平成16年3月24日 (2004.3.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン・パークウェイ エヌイー 11110

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

最終頁に続く

(54) 【発明の名称】 P L L その他同種類のループ・フィルタ・コンデンサの漏れ電流補償

## (57) 【特許請求の範囲】

## 【請求項 1】

信号シンセサイザであって、前記信号シンセサイザのチャージ・ポンプと発振器の間に接続された、前記チャージ・ポンプからの電荷を蓄積し、かつ、前記発振器に対する少なくとも第1の制御信号を生成するためのループ・フィルタを備える信号シンセサイザにおいて、前記ループ・フィルタが、

第1のノードで前記発振器に接続された抵抗に接続された、前記発振器に対する前記第1の制御信号を生成するための減衰コンデンサと、

整合コンデンサと、

前記減衰コンデンサ及び前記整合コンデンサに接続され、(1)検出および相殺回路の入力に印加される第1の基準電圧に整合させるべく前記整合コンデンサの両端間に電圧をドライブし、かつ、(2)前記整合コンデンサの両端間への前記電圧のドライブに関連する第1の電流に基づいて、前記減衰コンデンサの漏れ電流を補償するべく前記減衰コンデンサに印加される第2の電流を生成するよう機能する検出および相殺回路と、

前記第1のノードに接続された相互コンダクタ回路と、

前記相互コンダクタ回路及び前記発振器に接続された、前記発振器に対する第2の制御信号を生成するための相互コンダクタ・コンデンサとを備える信号シンセサイザ。

## 【請求項 2】

前記信号シンセサイザが P L L であり、

前記抵抗の第1の側が前記第1のノードで前記減衰コンデンサに接続され、

10

20

前記抵抗の第2の側が前記チャージ・ポンプおよび前記発振器の両方に接続され、前記第1の制御信号が、前記抵抗の前記第2の側の第2の電圧に基づいて生成される、請求項1に記載の発明。

#### 【請求項3】

前記検出および相殺回路が、

前記整合コンデンサの両端間の電圧と前記第1の基準電圧の差に基づいて電圧差信号を生成するようになされた演算増幅器(o p アンプ)と、

第1のトランジスタであって、(1)前記o p アンプから前記第1のトランジスタのゲートで前記電圧差信号を受け取り、かつ、(2)第1のトランジスタ出力信号を前記整合コンデンサに印加するべく接続された第1のトランジスタと、

10

第2のトランジスタであって、(1)前記o p アンプから前記第2のトランジスタのゲートで前記電圧差信号を受け取り、かつ、(2)第2のトランジスタ出力信号を前記減衰コンデンサに印加するべく接続された第2のトランジスタとを備えた、請求項1に記載の発明。

#### 【請求項4】

前記発振器が、前記発振器の中心周波数を設定するべく前記第2の制御信号を使用するようになされた、請求項1に記載の発明。

#### 【請求項5】

前記相互コンダクタ回路が、(1)前記第1のノードと(2)前記相互コンダクタ・コンデンサの間に接続されたアナログ相互コンダクタ(g m)セルをさらに備え、前記g mセルが、前記第1のノードの前記電圧と前記g mセルの入力に印加される第2の基準電圧(たとえば、 $V_{REF}$ )の差に基づいて、前記相互コンダクタ・コンデンサに印加される第1のg m出力信号を生成するようになされた、請求項1に記載の発明。

20

#### 【請求項6】

前記相互コンダクタ回路が、(1)前記第1のノードの前記電圧と前記第2の基準電圧の差をデジタル的に累積し、かつ、(2)前記累積した差に基づいて前記相互コンダクタ・コンデンサに印加されるg m出力信号を生成するようになされたデジタルg m経路をさらに備えた、請求項1に記載の発明。

#### 【請求項7】

前記デジタルg m経路が、

30

前記第1のノードの前記電圧と前記第2の基準電圧の間のデジタル差を生成するようになされた比較器と、

前記デジタル差を累積するようになされたアキュムレータと、

前記アキュムレータからの累積デジタル差を前記g m出力信号に変換するようになされた変換器とを備えた、請求項6に記載の発明。

#### 【請求項8】

信号シンセサイザであって、前記信号シンセサイザのチャージ・ポンプと発振器の間に接続された、前記チャージ・ポンプからの電荷を蓄積し、かつ、前記発振器に対する少なくとも第1の制御信号を生成するためのループ・フィルタを備える信号シンセサイザにおいて、前記ループ・フィルタは、

40

抵抗と、

第1のノードで前記抵抗に接続された減衰コンデンサと、

前記発振器に対する前記第1の制御信号を生成するべく接続された相互コンダクタ・コンデンサと、

前記第1のノード及び前記相互コンダクタ・コンデンサの間に接続され、(1)基準電圧と前記第1のノードの電圧の差をデジタル的に累積し、かつ、(2)前記累積した差に基づいて前記相互コンダクタ・コンデンサに印加される第1のg m出力信号を生成するようになされたデジタルg m経路とを備える信号シンセサイザ。

#### 【請求項9】

前記ループ・フィルタがさらに、(1)前記第1のノードと(2)前記相互コンダクタ

50

・コンデンサの間に接続されたアナログ相互コンダクタ ( $g_m$ ) セルを備え、前記  $g_m$  セルは、前記第1のノードの前記電圧と前記基準電圧の差に基づいて第2の  $g_m$  出力信号を発生するようになされ、前記第2の  $g_m$  出力信号はまた前記相互コンダクタ・コンデンサに印加される請求項8に記載の発明。

#### 【請求項10】

信号シンセサイザであって、前記信号シンセサイザのチャージ・ポンプと発振器の間に接続された、前記チャージ・ポンプからの電荷を蓄積し、かつ、前記発振器に対する少なくとも第1の制御信号を生成するためのループ・フィルタを備える信号シンセサイザにおいて、前記ループ・フィルタは、

第1の側上で前記チャージ・ポンプ及び前記発振器に接続され、第2の側上で第1のノードに接続される抵抗と、

前記発振器に対する前記第1の制御信号の生成に寄与するべく前記発振器に接続された相互コンダクタ・コンデンサと、

前記第1のノード及び前記相互コンダクタ・コンデンサの間に接続され、(1)(i)前記ループ・フィルタ内の前記第1のノードの電圧及び(iii)第1基準電圧の差をデジタル的に累積し、かつ、(2)前記累積した差に基づいて、前記相互コンダクタ・コンデンサの漏れ電流を補償するべく前記相互コンダクタ・コンデンサに印加される第1の  $g_m$  出力信号を生成するようになされたデジタル  $g_m$  経路とを備える信号シンセサイザ。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は電子工学に関し、詳細にはコンデンサを備えたループ・フィルタを有するチャージ・ポンプ位相同期ループおよび他の信号シンセサイザに関する。

##### 【背景技術】

##### 【0002】

位相同期ループ(PLL)は、周期入力信号に対して一定の位相関係を有する周期出力信号を生成する回路である。PLLは、様々な種類の測定、マイクロプロセッサおよび通信アプリケーションに幅広く使用されている。参照によりその教示が本明細書に組み込まれている、Floyd M. Gardner、「Charge-Pump Phase-Locked Loops」、IEEE Trans. Commun., Vol. COM-28, 1849~1858頁、1980年11月に記載されているチャージ・ポンプPLLは、数ある種類の位相同期ループのうちの1つである。

30

##### 【0003】

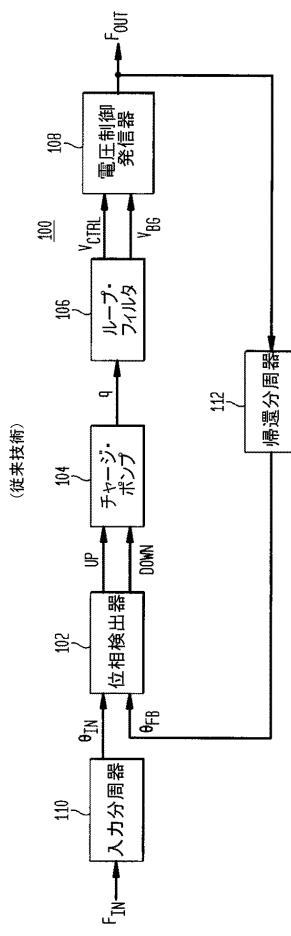

図1は、従来のチャージ・ポンプ位相同期ループ100のブロック図を示したものである。位相検出器(PD)102は、入力信号の位相 $I_N$ と帰還信号の位相 $F_B$ を比較し、UP信号U( $I_N$ が $F_B$ をリードしている場合)もしくはDOWN信号D( $F_B$ が $I_N$ をリードしている場合)のいずれかの誤差信号を生成している。誤差信号パルスの幅は、 $I_N$ と $F_B$ の差の大きさを表している。

##### 【0004】

チャージ・ポンプ104は、PD102からの誤差信号(UもしくはDのいずれか)と等価の一定量の電荷 $q$ を生成している。誤差信号がUP信号であったか、あるいはDOWN信号であったかどうかに応じて、ループ・フィルタ106内の1つまたは複数のコンデンサに電荷 $q$ が追加されるか、あるいは控除される。典型的な実施態様では、ループ・フィルタ106は、チャージ・ポンプ104から正味電荷を蓄積する積分器として動作している。図1に示すように、ループ・フィルタ106は、電圧制御発振器(VCO)108に対して、低利得入力 $V_{CTRL}$ および高利得入力 $V_{BG}$ の2つの入力を生成している。電圧制御発振器は、周波数がVCO入力電圧 $V_{CTRL}$ および $V_{BG}$ の関数である周期出力信号(図1の $F_{OUT}$ )を生成するデバイスであり、較正時に高利得入力電圧 $V_{BG}$ を使用して中心周波数が設定され、また、低利得入力電圧 $V_{CTRL}$ は、定常信号経路として機能している。VCO出力信号 $F_{OUT}$ は、PLL100からの出力信号として使用さ

40

50

れる以外に、P D 1 0 2 に対する帰還信号を生成するべく使用されている。

**【0005】**

出力信号  $F_{OUT}$  の周波数を入力信号  $F_{IN}$  の周波数の分数もしくは倍数のいずれかにする必要がある場合、任意選択の入力分周器 1 1 0 および帰還分周器 1 1 2 を入力経路および帰還経路にそれぞれ配置することができる。

**【0006】**

P L L 1 0 0 のような P L L に関する詳細な情報については、参照によりその教示が本明細書に組み込まれている米国特許第 5, 9 4 2, 9 4 9 号を参照されたい。

**【0007】**

図 1 には示されていないが、上で説明したように、P L L 1 0 0 などの従来のチャージ・ポンプ P L L のループ・フィルタは、コンデンサを使用して実施されている。このような P L L を適切に動作させるためには、これらのループ・フィルタ・コンデンサのゲート酸化膜漏れ電流による悪影響を回避することが重要である。このような漏れ電流による悪影響を回避するための従来の手法は、酸化膜の厚さが比較的分厚い（たとえば、50～70 オングストロームの）コンデンサをループ・フィルタに使用することであるが、残念なことには、このようなコンデンサには比較的広い実装面積が必要である。したがって、酸化膜の厚さが比較的薄く（たとえば、17 オングストローム）、それに対応して実装面積が比較的狭いコンデンサを使用してチャージ・ポンプ P L L 中にループ・フィルタを実装することが望ましい。10

**【非特許文献 1】** Floyd M. Gardner、「Charge-Pump Phase-Locked Loops」、IEEE Trans. Commun., Vol. COM-28、1849～1858 頁、1980 年 11 月20

**【特許文献 1】** 米国特許第 5, 9 4 2, 9 4 9 号

**【非特許文献 2】** J. D. H. Alexander、「Clock Recovery from Random Binary Signals」、Electronic Letters、1975 年 10 月

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0008】**

本発明の原理による、酸化膜の厚さが比較的分厚い比較的大型のコンデンサを使用する必要のないループ・フィルタに使用されるコンデンサのゲート酸化膜漏れ電流による悪影響を緩和するチャージ・ポンプ P L L のためのループ・フィルタ・アーキテクチャにより、従来技術が抱えている問題が対処される。30

**【課題を解決するための手段】**

**【0009】**

本発明の一実施形態によれば、信号シンセサイザ（たとえば、P L L）は、信号シンセサイザのチャージ・ポンプと発振器の間に接続された、チャージ・ポンプから電荷を蓄積し、かつ、発振器に対する少なくとも第 1 の制御信号を生成するためのループ・フィルタを備えている。

**【0010】**

信号シンセサイザを動作させるための技法の 1 つによれば、ループ・フィルタは、抵抗に接続された減衰コンデンサと、整合コンデンサと、（1）第 1 の基準電圧に整合させるべく整合コンデンサの両端間に電圧をドライブし、かつ、（2）整合コンデンサの両端間への電圧のドライブに関連する第 1 の電流に基づいて、減衰コンデンサに印加される、減衰コンデンサの漏れ電流を補償するための第 2 の電流を生成するようになされた検出および相殺回路とを備えている。40

**【0011】**

信号シンセサイザを動作させるための他の技法によれば、ループ・フィルタは、抵抗と、第 1 のノードで抵抗に接続された減衰コンデンサと、発振器に対する第 1 の制御信号を生成するべく接続された相互コンダクタ・コンデンサと、（1）基準電圧と第 1 のノード

の電圧の差をデジタル的に累積し、かつ、(2)累積した差に基づいて、相互コンダクタ・コンデンサに印加される第1のg m出力信号を生成するようになされたディジタルg m経路とを備えている。

#### 【0012】

必ずしもその必要はないが、2つの技法を単一の実施態様に組み合わせができる。

#### 【0013】

本発明の他の態様、特徴および利点については、以下の詳細な説明、特許請求の範囲および添付の図面からより完全に明確になるであろう。添付の図面では、同様の参照符号は、類似もしくは同じ構成要素を表している。

10

#### 【発明を実施するための最良の形態】

#### 【0014】

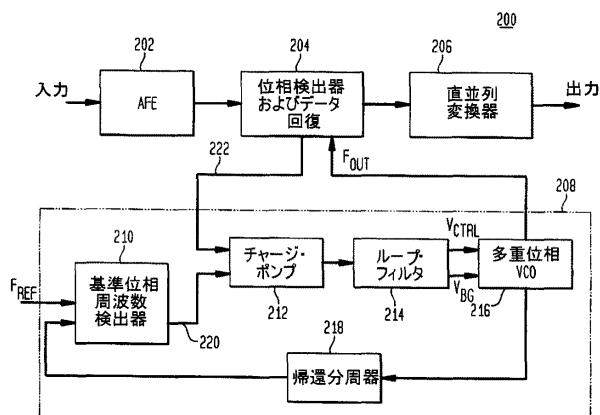

図2は、本発明の一実施形態によるクロック/データ回復(CDR)回路200を高水準ブロック図で示したものである。CDR回路200は、アナログ・フロント・エンド(AFE)202、位相検出器/データ回復(PD/DR)回路204、直並列変換器206およびチャージ・ポンプPLL208を有している。基準位相/周波数検出器210、チャージ・ポンプ212、ループ・フィルタ214、多重位相VCO216および帰還分周器218を備えたPLL208は、図1に示すPLL100と同じ基本アーキテクチャを有している。一実施態様では、VCO216は、CMOS論理レベルの8つの出力位相を生成する4段差動リング発振器である。したがって、VCO216は既知のデータ転送速度の1/4の速度で動作し、また、4または5の帰還分周器は、入力データ転送速度の1/16もしくは1/20の局部基準クロックに対するトレーニングを許容している。

20

#### 【0015】

CDR回路200の目的は、受け取ったアナログ入力信号中に符号化されているデータを回復することである。詳細には、AFE202は、線路成端インピーダンスを提供し、入力信号に若干の利得を付与している。PD/DR回路204は、PLL208のVCO216によって生成される多重位相クロック信号 $F_{OUT}$ に基づいて入力信号からデータを回復している。また、直並列変換器206は、回復データを併合し、下流側でさらに処理するための並列出力データ(たとえば、16ビット・ワードあるいは20ビット・ワード)を生成している。

30

#### 【0016】

PD/DR回路204を適切に動作させるためには、PLL208によって生成されるクロック信号 $F_{OUT}$ は適切な周波数を有していなければならず、また、入力信号中に符号化されているデータに十分に同期させなければならない。周波数整合および位相同期を提供するために、チャージ・ポンプ212は、基準位相/周波数検出器(PFD)210からUPおよびDN信号220を受け取り(PLL208が「ロック・ツー・リファレンス」モードで動作している場合)、また、PD/DR回路204からUPおよびDN信号222を受け取っている(PLL208が「ロック・ツー・データ」モードで動作している場合)。

40

#### 【0017】

CDR回路200は、特定のレベルでは、2つの異なる位相同期ループを有效地に有していると言える。このようなループの1つは、図2に明示されている、本明細書においてはPLL208と呼んでいる、PFD210がチャージ・ポンプ212にUP/DNを提供しているループである。このループは、「ロック・ツー・リファレンス」モードの間、位相同期ループである。もう1つのループも同じくチャージ・ポンプ212、ループ・フィルタ214およびVCO216を備えているが、このループは、チャージ・ポンプ212に対するUP/DN信号の生成をPFD210ではなく、PD/DR204に依存している。このもう1つのループは、「ロック・ツー・データ」モードの間、位相同期ループである。

#### 【0018】

50

P F D 2 1 0 は、「ロック・ツー・リファレンス」モードの間、帰還分周器 2 1 8 からの帰還信号の位相と局部基準クロック信号  $F_{REF}$  の位相を比較し、検出した位相誤差の大きさによって幅が変化する U P および D N パルス 2 2 0 を生成している。このモードの間、高利得入力信号  $V_{BG}$  を使用して V C O 2 1 6 の中心周波数が設定される。

#### 【0019】

P D / D R 回路 2 0 4 は、「ロック・ツー・データ」モードの間、P L L 2 0 8 のチャージ・ポンプ 2 1 2 に印加する位相情報（すなわち U P / D OWN パルス 2 2 2 ）を生成するべく、「アレキサンダ」位相検出器すなわちバンバン位相検出器を使用して、P L L 出力クロック信号  $F_{OUT}$  の位相と入力信号の位相を比較している。P D / D R 回路 2 0 4 からの位相情報は、実際の入力位相誤差の 1 ビット量子化であり、更新毎に一定量の電荷をループ・フィルタに帯電させるべく、チャージ・ポンプ 2 1 2 によって使用される。アレキサンダ位相検出器に関する詳細な情報については、参照によりその教示が本明細書に組み込まれている、J . D . H . Alexander、「Clock Recovery from Random Binary Signals」、Electronic Letters、1975年10月を参照されたい。10

#### 【0020】

「ロック・ツー・リファレンス」あるいは「ロック・ツー・データ」のいずれかのモードで、入力位相誤差の極性によって電荷パルスの極性が決定される。P D / D R 回路 2 0 4 および P F D 2 1 0 からの U P / D N パルスにより、V C O 2 1 6 は、適切な周波数および位相を有する P L L 出力クロック信号  $F_{OUT}$  を生成することができる。「ロック・ツー・リファレンス」モードでは、V C O 2 1 6 の出力は、必ずしも入力データ転送速度の整数スケーリングに等しい必要はないが、それに近い基準周波数  $F_{REF}$  に対して位相および周波数が同期している。システムのスタート・アップの間、データ転送速度の整数スケーリングに十分に近い V C O 動作周波数を得るべく、この「ロック・ツー・リファレンス」モードが使用される。したがって V C O の動作周波数は、埋込み周波数検出器を持たない P D / D R 2 0 4 のブル・レンジの範囲内であり、システムが「ロック・ツー・リファレンス」モードから「ロック・ツー・データ」モードへスイッチされると、データに対する位相同期が得られる。20

#### 【0021】

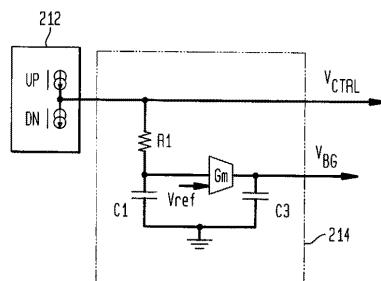

図 3 は、図 2 に示す P L L 2 0 8 のチャージ・ポンプ 2 1 2 およびループ・フィルタ 2 1 4 を略図で示したものである。チャージ・ポンプ 2 1 2 は、受け取った個々の U P / D N パルスの幅から決定される一定の時間の間、ループ・フィルタ 2 1 4 に正もしくは負の電流を流している。電流の大きさで掛け合わされたパルスの幅が、ループ・フィルタ 2 1 4 に注入される電荷の量を決定している。この電荷パケットが寄生コンデンサ（図示せず）を充電し、かつ、抵抗 R 1 を通って流れ、コンデンサ C 1 （「減衰コンデンサ」とも呼ばれる）を充電する。コンデンサ C 1 上の長期電圧と抵抗 R 1 の両端間の電圧が加算され、それにより、図 2 に示す V C O 2 1 6 に印加される低利得入力電圧  $V_{CTR}$  が決定される。30

#### 【0022】

相互コンダクタ・セル G m は、コンデンサ C 1 上の電圧と基準電圧  $V_{REF}$  の差に比例する電流を生成し、かつ、コンデンサ C 3 （「相互コンダクタ・コンデンサ」とも呼ばれる）に注入している。コンデンサ C 3 上の電圧は、P L L 2 0 8 の負の帰還作用（たとえば、V C O 2 1 6 から P F D 2 1 0 への P L L 帰還ループによって、ループを同期させるべく低利得入力電圧  $V_{CTR}$  がドライブされる）によって、コンデンサ C 1 の両端間の電圧が基準電圧  $V_{REF}$  に等しくなるまで調整される。（P D / D R 2 0 4 も同じくチャージ・ポンプ 2 1 2 に対する U P / D N 信号を生成することができることに留意されたい。）コンデンサ C 3 は、相互コンダクタ・セル G m からの電流を集積し、高利得入力電圧  $V_{BG}$  に基づいて V C O 2 1 6 の中心周波数を設定している。 $V_{BG}$  は最終値に到達して安定するが、 $V_{CTR}$  は、位相同期を維持するべく連続的に更新される。40

#### 【0023】

### 減衰コンデンサのゲート漏れ電流

大きなゲート漏れ電流が減衰コンデンサ C<sub>1</sub> に関連している場合、図 2 に示す CDR 回路 200 は、通常、2つの理由でその性能が低下することになる。第1の理由は、積分器の1つがその原点から外れ、そのため極の周波数が場合によっては非常に高くなり、ループの安定性が損なわれることである。これは、ゲート漏れが存在することにより、コンデンサ C<sub>1</sub> に抵抗が並列に結合された回路と等価になることによるものである。この寄生抵抗 R<sub>PARA</sub> の大きさが抵抗 R<sub>1</sub> の大きさの数桁倍未満である場合、極の周波数が極めて高くなる。極周波数が、PFD 206 を使用した PLL ( すなわち PLL 208 ) もしくは PDR 204 を使用した PLL ( すなわち図 2 に示す「もう1つのループ」) のいずれかの閉ループ 3dB 周波数に対して高い場合、位相マージンの損失が生じることになる。10

#### 【0024】

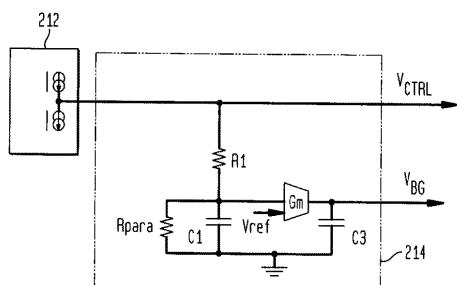

図 4 は、図 2 に示す PLL 208 のチャージ・ポンプ 212 およびループ・フィルタ 214 を略図で示したもので、コンデンサ C<sub>1</sub> のゲート漏れ電流の影響が寄生抵抗 R<sub>PARA</sub> で示されている。

#### 【0025】

チャージ・ポンプから見た入力インピーダンス Z(s) は、次の式(1)で与えられる。20

$$Z(s) = \frac{(R_{PARA} + R_1) + sR_{PARA}R_1C_1}{s(R_{PARA} + R_1)C_2 + s^2R_{PARA}R_1C_1C_2 + 1 + sR_{PARA}C_1}, \quad (1)$$

ここで、C<sub>2</sub> ( 図 4 には図示せず ) は、ノード V<sub>CTR\_L</sub> の寄生容量である。寄生抵抗 R<sub>PARA</sub> は無限大であるため、限界内では、インピーダンス Z(s) は、次の式(2)で表すことができる。

#### 【数1】

$$Z(s) = \frac{\left( R_1 + \frac{1}{sC_1} \right)}{sC_2 \left( R_1 + \frac{1}{sC_2} \right)}, \quad (2)$$

ここで、ループを安定に維持するためには、C<sub>1</sub> の大きさは、C<sub>2</sub> の大きさよりはるかに大きい ( たとえば、少なくとも 100 倍 ) ことが好ましい。

#### 【0026】

典型的な実施態様では、約 100 キロオームの最小値を寄生抵抗 R<sub>PARA</sub> に持たせることができ、また、約 12 キロオームの最大値を抵抗 R<sub>1</sub> に持たせることができる。寄生抵抗は、抵抗 R<sub>1</sub> より ( 最小でも ) ほぼ 1 衡大きいため、積分器の原点の移動は小さいことが期待される。したがって「ロック・ツー・リファレンス」モードであっても、あるいは「ロック・ツー・データ」モードであっても、ゲート漏れ電流による位相マージンの変化を無視することができ、また、ループの安定性に対する寄生抵抗 ( つまりゲート漏れ抵抗 ) の影響は最小である。チャージ・ポンプの出力抵抗 ( 図示せず ) も同様の効果を有しており、ほとんどの設計の場合、同じく安定性に対する影響を無視することができることに留意されたい。40

#### 【0027】

ループ・フィルタ 減衰コンデンサ C<sub>1</sub> にゲート漏れ電流が存在することによって CDR

50

回路 200 の性能が低下する第 2 の理由は、静位相オフセットが生成されることによるものである。コンデンサ C1 を介した直流漏れ電流は、チャージ・ポンプ 212 によって供給する必要がある。これは、UP 信号と DN 信号の間に常に平均化された正味の差を持たせることによってのみ実施することができるが、この差が静位相オフセットの原因になつてている。この望ましくない位相オフセットは、PLL の負の帰還によって生成され、通常、PDL / DR 回路 204 がもはやデータの「目」の中心でデータをサンプリングすることができないため、データ回復プロセスのビット誤り率 (BER) が大きくなる。たとえば、約 100 キロオームの寄生抵抗  $R_{PARA}$  を有するコンデンサ C1 は、その両端間の公称電圧が 0.5 ボルトで約 5 マイクロアンペアの漏れ電流を有することになり、それにより 20 マイクロアンペアの公称チャージ・ポンプ電流に対して大きな静位相オフセットが生成され、通常、ビット誤りがもたらされることになる。約 1.6 マイクロアンペアの漏れ電流を有する 17 オングストロームのコンデンサは、データ転送速度が十分に速い場合、同じくビット誤りをもたらすことになるより小さい静位相オフセットを生成することになる。漏れ電流の大きさとそれによってもたらされる静位相オフセットとの間の直接の関係は、使用するまさにその PD、入力位相ジッタおよびデータ・ストリーム上の符号間干渉の量、さらにはループ動力学および様々なコンポーネント中に生成される無秩序雑音の量の複雑な関数であることは当業者には認識されよう。

#### 【0028】

したがって、ループ・フィルタ減衰コンデンサ C1 のゲート漏れ電流は、安定性に影響を及ぼしていないように思われるが、それらは、所望するレベルの CDR 性能を妨げるだけの十分な静位相オフセットをもたらすことがある。

#### 【0029】

##### 相互コンダクタ・コンデンサのゲート漏れ電流

既に説明したように、図 3 に示す相互コンダクタ・セル Gm は、発振器の中心周波数を有効に設定するべく、その電流をコンデンサ C3 上に集積している。相互コンダクタ・コンデンサ C3 がゲート漏れの問題を抱えている場合、相互コンダクタ・セル Gm の実効出力抵抗が小さくなり、積分器の利得が減少する。この寄生抵抗に電流を供給し、所望の出力電圧を維持するために、相互コンダクタ・セル Gm に非ゼロ入力を印加することが可能である。

#### 【0030】

ゲート漏れを説明する前に、相互コンダクタ・セル Gm の出力抵抗は、約 5 ~ 10 メガオームである。この出力抵抗をたとえば 500 キロオームにするためには、1 枝小さくなければならない。また、相互コンダクタ・セル Gm の利得は、通常、1 ボルト当たり約 2.2 マイクロアンペアである。これは、1 マイクロアンペアの出力、したがって 0.5 V の出力電圧を生成するためには 0.5 V の入力が必要であることを意味している（寄生抵抗が 500 キロオームと仮定して）。この場合、線形範囲は残されず ( $V_{dd} = 1.0$  V)、相互コンダクタ・セル Gm は非線形になる。さらに、相互コンダクタ・セル Gm の出力中の最大直流バイアス電流は 500 ナノアンペアであり、したがって寄生抵抗の両端間の電圧をサポートするべく追い出すことができる最大電流である。これは、他の場合に必要な最大電流の半分である。この量のゲート漏れでは回路が適切に機能しないことは明らかであろう。

#### 【0031】

##### 減衰コンデンサのゲート漏れ電流の検出および相殺

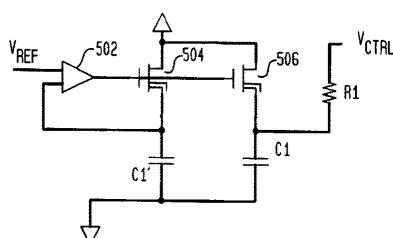

図 5 は、本発明の一実施形態による、図 2 に示すチャージ・ポンプ 212 およびループ・フィルタ 214 を略図で示したものである。この実施形態では、op アンプ 502 は、相互コンダクタ基準電圧  $V_{REF}$  と整合コンデンサ C1' の両端間の電圧の差の関数である信号を生成し、トランジスタ 504 および 506 のゲートに印加している。したがって op アンプ 502 は、そのために必要な電流を検出している間、整合コンデンサ C1' の両端間に基準電圧  $V_{REF}$  を強制している。整合検出コンデンサ C1' に対するループ・フィルタ減衰コンデンサ C1 の比率に応じてトランジスタ 506 のサイズによって設定さ

10

20

30

40

50

れる電流をスケーリングすることにより、減衰コンデンサ C 1 の漏れ電流の影響を緩和し、さらには相殺することができる。

#### 【 0 0 3 2 】

この手法を使用して、結果として生じるゲート漏れ電流による悪影響を相殺することにより、ゲート酸化膜の厚さが比較的薄い(たとえば、約 17 オングストロームの)減衰コンデンサ C 1 を使用して図 2 に示す P L L 2 0 8 を実装することができる。

#### 【 0 0 3 3 】

##### 相互コンダクタ・コンデンサのゲート漏れ電流の検出および相殺

図 3 に示す相互コンダクタ・コンデンサ C 3 のゲート漏れ電流は、相互コンダクタ・コンデンサ C 3 の電圧が広範囲に及んでおり、処理変動を有している可能性があるため、その検出および相殺が比較的困難である。相互コンダクタ・コンデンサのゲート漏れ電流を検出し、かつ、相殺する手法の 1 つは、オフセット漏れ電流に電流を提供することができるよう、相互コンダクタ・セル G m の利得をスケール・アップすることである。他の手法は、アナログ相互コンダクタ積分器を離散時間等価に置き換えることである。この手法には、ゲート漏れ電流に対して鈍感な電圧出力を有する利点がある。さらに他の手法は、相互コンダクタ・セルからゲート漏れ電流を追い出すために必要な入力参照オフセット電圧を検出し、かつ、相殺するべく、相互コンダクタ積分器を離散時間帰還ループで覆うことである。

#### 【 0 0 3 4 】

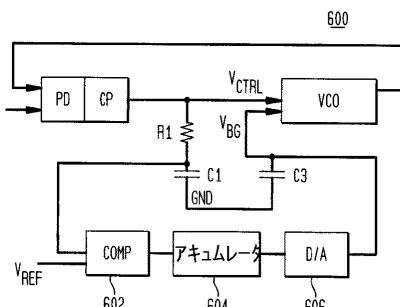

図 6 は、本発明の他の実施形態による P L L 6 0 0 を略図で示したものである。図 2 に示す P L L 2 0 8 に使用することができる P L L 6 0 0 は、アナログ相互コンダクタ積分器を離散時間等価に置換する手法の一例である。詳細には、図 3 に示す相互コンダクタ・セル G m が、比較器 6 0 2 、ディジタル・アキュムレータ 6 0 4 およびディジタル - アナログ変換器 (D / A) 6 0 6 に置換されている。

#### 【 0 0 3 5 】

詳細には、比較器 6 0 2 は、減衰コンデンサ C 1 の両端間の電圧をサンプリングし、かつ、基準電圧  $V_{REF}$  と比較し、この 2 つの電圧の差に応じた大きさおよび符号のディジタル値を生成している。アキュムレータ 6 0 4 は、比較器 6 0 2 から受け取るディジタル値を常に累積し、また、D / A 変換器 6 0 6 は、得られた累積値をアナログ出力に変換している。このアナログ出力は、アナログ VCO 入力電圧信号  $V_{BG}$  を生成するべくコンデンサ C 3 に印加される。D / A 変換器 6 0 6 は、一実施態様ではアナログ電圧信号を生成する電圧源として機能し、他の実施態様ではアナログ電流信号を生成する電流源として機能している。電流源ではなく電圧源によってコンデンサ C 3 をドライブする場合、ゲート漏れ電流の影響が問題になる。

#### 【 0 0 3 6 】

ディジタル経路を積分器として作用させるために、比較器 6 0 2 がコンデンサ C 1 の電圧をサンプリングする速度を極めて遅くする(たとえば、閉ループ P L L の 3 dB 周波数より 3 极超低い周波数より高い周波数)ことができ、あるいはアキュムレータの利得を小さくするか、もしくは折点周波数がたとえば閉ループ P L L の等価 3 dB 周波数より 3 极以上低い、コンデンサ C 1 の電圧から  $V_{BG}$  までの低域通過フィルタ効果が存在するよう、比較的遅いサンプルレートと比較的小さいアキュムレータ利得の両方のいくつかの適切な組合せにすることができる。また、コンデンサ C 3 は、閉ループ P L L 応答の時定数より極めて短い時定数で D / A 出力のステップ応答をフィルタリングしなければならず、それにより、D / A 変換器の出力の変化が、データ / 位相検出器への入力部における、ピット誤りの原因になる位相ランプ / 周波数ステップとは見なされないことが保証される。VCO への D / A 出力電圧が変化することができる速度を遅くすることにより、広帯域 P L L ループは、VCO に対する高利得入力での電圧変化を補償することができる。

#### 【 0 0 3 7 】

特定のタイプの比較器およびアキュムレータがどこからその入力を引き出すかは、実施態様によって様々であり、設計特化トレードオフを可能にしている。

10

20

30

40

50

## 【0038】

この手法を使用して、結果として生じるゲート漏れ電流による悪影響を相殺することにより、ゲート酸化膜の厚さが比較的薄い(たとえば、約17オングストロームの)コンデンサC3を使用してPLL600を実装することができる。

## 【0039】

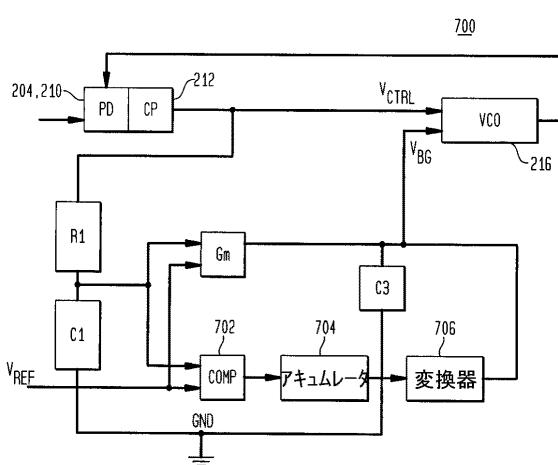

図7は、本発明のさらに他の実施形態によるPLL700を略図で示したものである。図2に示すPLL208に使用することができるPLL700は、ディジタル・アキュムレータをアナログ相互コンダクタ積分器と並列に実装する手法の一例である。この場合、並列ディジタル・アキュムレータを使用してコンデンサC3のゲート漏れ電流および他のあらゆる直流漏れ電流を補償している間、連続時間積分器によって主要な性能が提供される。この実施形態では、ディジタル・アキュムレータは、比較器702、ディジタル・アキュムレータ704、およびアキュムレータ704からの累積ディジタル値をコンデンサC3に印加される電流信号に変換する電流源(Idac)706を備えていることに留意されたい。10

## 【0040】

この手法によれば、相互コンダクタ・セルGmがコンデンサC3のゲート漏れ電流を補償するための直流電流を供給するために、相互コンダクタ・セルに非ゼロ差動入力が印加される。比較器を使用してこの差動入力電圧を検出し、かつ、ループを安定化させるだけの十分な長さの時間期間に渡って比較器の出力を積分することにより、ディジタル・ワードを生成することができ、それによりC3のゲート漏れ電流を補償する電流を生成するIdac706がドライブされる。20

## 【0041】

Idacの出力電流が変化すると、Idacの出力電流とゲート漏れ電流の間の電流の差がコンデンサ上に集積される際に、VCOに対する高利得入力VBGが変化する。主PLL帰還ループは、位相検出器(PD)およびチャージ・ポンプ(CP)を介して相互コンダクタ・セルへの入力部の電圧を調整することができるため、Idacの元の出力変化に等しい量だけ、反対の符号で相互コンダクタ・セルの出力電流が変化する。20

## 【0042】

ディジタル積分器の時定数がGm段およびコンデンサC3に関連する時定数より少なくとも2桁遅いと仮定すると、ループ全体が安定した状態を維持することになる。30

## 【0043】

対処すべき複数の二次効果が存在している。1つは、比較器の入力参照オフセットと相互コンダクタ・セル自身の入力参照オフセットの差である。この二次効果を解決する方法の1つは、相互コンダクタ・セルと比較器の両方に同じ差動対を使用し、相互コンダクタ・セルと比較器の両方の入力参照オフセット電圧がほぼ正確に同じになることを保証することである。

## 【0044】

もう1つの難点は、最下位ビット(LSB)が100ナノアンペア程度のIdacを生成することである。この場合、ゲート漏れ電流の極性が分かっているため、ゲート漏れ電流を補償するべくディジタル・ビットを使用して相互コンダクタ・セルの出力段のバイアス電流を調整することができる。個別のD/A変換器ブロックは不要である。40

## 【0045】

他の難点は、新しい経路がディジタル・ループであるため、Idacの出力が脈動することに起因している。Idacの出力のこの脈動は、コンデンサC3の両端間の電圧に三角波をもたらすように思われるが、この場合、三角波がもたらされることはない。実際、帯域幅がはるかに広い主PLLループが代わりにコンデンサC1の電圧を調整している。コンデンサC1の電圧を調整することにより、相互コンダクタ・セルからの出力電流によってIdacからの電流の変化が補償される。したがってIdacの出力が変化するとコンデンサC3の両端間の電圧が若干変化し、この変化に適応するべくコンデンサC1の両端間の電圧の値が変化すると再び安定する。この脈動は、コンデンサC3を大きい値に維50

持し、I d a c の L S B ステップ・サイズを小さい値に維持し、あるいはその両方のいくつかの組合せによって任意に小さい値に維持することができる。

**【 0 0 4 6 】**

この脈動が許容不可能になると、ゲート漏れ電流は主として直流項であるため、若干の初期期間が経過した後、適応ループをターン・オフすることができ、それにより残留誤差および順応ループをターン・オフした時点から温度変化によって生成されるあらゆる誤差に適応するべく主相互コンダクタ・セルが放置される。相互コンダクタ・セルの線形範囲内で良好であるためには、温度によるゲート漏れ電流の変化は、十分に小さい変化でなければならない。

**【 0 0 4 7 】**

この手法を使用して、結果として生じるゲート漏れ電流による悪影響を相殺することにより、ゲート酸化膜の厚さが比較的薄い(たとえば、約17オングストロームの)コンデンサC3を使用してPLL700を実装することができる。

**【 0 0 4 8 】**

図5に示す減衰コンデンサC1のゲート漏れ電流の影響を検出し、かつ、相殺するための技法、および図6および7に示す相互コンダクタ・コンデンサC3のゲート漏れ電流の影響を検出し、かつ、相殺するための技法は、個別に実施することができるが、好ましい実施形態では、ゲート酸化膜の厚さが比較的薄い両方のコンデンサの実施を可能にするべく、個々のコンデンサのための技法が結合されている。

**【 0 0 4 9 】**

以上、本発明について、位相同期ループのコンテキストの中で説明したが、本発明は、遅延同期ループ(DLL)などの他のタイプの信号シンセサイザのコンテキストの中で実施することも可能である。

**【 0 0 5 0 】**

明確に言及されていない限り、個々の数値および範囲は、その値もしくは範囲の値に「約」あるいは「ほぼ」という語が概ね前置きされているものとして解釈されたい。

**【 0 0 5 1 】**

また、本発明の性質を説明するべく上で説明し、かつ、図に示した部品の詳細、材料および構造に対する当業者による様々な変更が、特許請求の範囲に示されている本発明の範囲を逸脱することなく可能であることは理解されよう。

**【 0 0 5 2 】**

特許請求の範囲における図面番号および/または図面参照ラベルの使用は、クレームの解釈を容易にするべく、特許請求の範囲に記載されている主題の1つまたは複数の可能実施形態の識別を意図したものである。このような使用を、対応する図面に示す実施形態にこれらの特許請求の範囲を必然的に限定するものとして解釈してはならない。

**【 図面の簡単な説明 】**

**【 0 0 5 3 】**

**【 図1】**従来のチャージ・ポンプ位相同期ループのブロック図である。

**【 図2】**本発明の一実施形態によるクロック/データ回復(CDR)回路の高水準プロック図である。

**【 図3】**図2に示すPLLのチャージ・ポンプおよびループ・フィルタの略図である。

**【 図4】**コンデンサC1のゲート漏れ電流の影響を寄生抵抗R<sub>P A R A</sub>で示す、図2のPLLのチャージ・ポンプおよびループ・フィルタの略図である。

**【 図5】**本発明の一実施形態による、図2に示すチャージ・ポンプおよびループ・フィルタの略図である。

**【 図6】**本発明の他の実施形態によるPLLの略図である。

**【 図7】**本発明のさらに他の実施形態によるPLLの略図である。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

---

フロントページの続き

(74)代理人 100096943

弁理士 白井 伸一

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 ウィリアム ビー・ wilson

アメリカ合衆国 18062 ペンシルヴァニア, マッカンジー, ブライアウッド ドライヴ 4

964

審査官 上田 智志

(56)参考文献 特開昭64-022113(JP,A)

特開平09-294051(JP,A)

特開平11-027141(JP,A)

米国特許第05659588(US,A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/06 - 7/23,

H03H 11/04