## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-158735 (P2007-158735A)

(43) 公開日 平成19年6月21日 (2007.6.21)

(51) Int.Cl. F I テーマコード (参考) **HO3M 3/04 (2006.01)** HO3M 3/04 5JO22

**HO3M 3/04 (2006.01)** HO3M 3/04 5JO22 **HO3M 1/74 (2006.01)** HO3M 1/74 5JO64

#### 審査請求 未請求 請求項の数 4 OL (全 12 頁)

|                    |                                                        | - 114.4. |                     |

|--------------------|--------------------------------------------------------|----------|---------------------|

| (21) 出願番号 (22) 出願日 | 特願2005-351429 (P2005-351429)<br>平成17年12月6日 (2005.12.6) | (71) 出願人 |                     |

|                    |                                                        |          | 東京都千代田区大手町二丁目6番2号   |

|                    |                                                        | (74)代理人  | 100080001           |

|                    |                                                        |          | 弁理士 筒井 大和           |

|                    |                                                        | (72) 発明者 | 工藤 純也               |

|                    |                                                        |          | 東京都千代田区丸の内二丁目4番1号 株 |

|                    |                                                        |          | 式会社ルネサステクノロジ内       |

|                    |                                                        | (72) 発明者 | 松浦 達治               |

|                    |                                                        |          | 東京都千代田区丸の内二丁目4番1号 株 |

|                    |                                                        |          | 式会社ルネサステクノロジ内       |

|                    |                                                        | (72) 発明者 | 笠原 真澄               |

|                    |                                                        |          | 東京都千代田区丸の内二丁目4番1号 株 |

|                    |                                                        |          | 式会社ルネサステクノロジ内       |

|                    |                                                        |          | 最終百に続く              |

#### (54) 【発明の名称】半導体集積回路装置

## (57)【要約】

インタを用いた単位要素のローテーションにより、入力信号周波数近辺の雑音を低減し、S/N比を改善する。 【解決手段】A/D変換器に設けられたDEM15において、量子化器から出力された信号は3ビットの2進数に変換され、カウンタ18により、使用するポインタと単位要素の使用の方向(昇順/降順)が制御される。記録されたポインタ位置と入力信号を加算することにより、ポインタを移動し、量子化器からの入力×(i)は、シフトされy(i)として、D/A変換器へ出力され、単

【課題】デルタシグマA/D変換器において、N個のポ

【選択図】図4

位要素のシフトが行われる。

#### 【特許請求の範囲】

### 【請求項1】

サンプリング周波数の1 / 4 の周波数以外の信号をデジタル変換するバンドパスデルタ シ グ マ 型 の A / D 変 換 器 を 備 え た 半 導 体 集 積 回 路 装 置 で あ っ て 、

前記A/D変換器は、

入力された信号をデジタル信号に変換して量子化する量子化器と、

D/A変換器と、

前 記 D / A 変 換 器 に 設 け ら れ た D / A 変 換 器 の 単 位 要 素 を 動 的 に ロ ー テ ー シ ョ ン す る エ レメントマッチング部を備え、

前記エレメントマッチング部は、

前記量子化器から出力された単位要素の位置を記憶するN個のポインタを備え、

前記ポインタにより単位素子をシフトし、そのシフト方向を昇順、または降順に反転さ せることを特徴とする半導体集積回路装置。

#### 【請求項2】

請求項1記載の半導体集積回路装置において、

前記エレメントマッチング部は、

サンプリング周波数×k(=1,3,5,・・・N-1)/(2×ポインタ数)=入力 信号周波数となるように、前記D/A変換器の単位要素をローテーションすることを特徴 とする半導体集積回路装置。

#### 【請求項3】

請求項1または2記載の半導体集積回路装置において、

前 記 ポ イ ン タ は 、 レ ジ ス タ か ら な る こ と を 特 徴 と す る 半 導 体 集 積 回 路 装 置 。

#### 【請求項4】

請 求 項 1 ~ 3 の い ず れ か 1 項 に 記 載 の 半 導 体 集 積 回 路 装 置 に お い て 、

前記エレメントマッチング部は、

前記 D / A 変換器の単位要素を 1 2 個の前記ポインタを用いてローテーションし、サン プリング周波数の 7 / 2 4 にミスマッチ ノイズ伝達特性のノッチ点を持たせることを特徴 とする半導体集積回路装置。

【発明の詳細な説明】

#### 【技術分野】

[00001]

本 発 明 は 、 A / D 変 換 器 に お け る S / N ( Signal / Noise ) 比 の 改 善 技 術 に 関し、特に、バンドパスデルタシグマ型のA/D変換器における単位要素(エレメント) のばらつきによる雑音の低減に有効な技術に関する。

## 【背景技術】

[0002]

ラ ジ オ 受 信 機 や 携 帯 電 話 な ど の 中 間 周 波 数 を 用 い て 復 調 を 行 う 無 線 通 信 に は 、 バ ン ド パ スデルタシグマA/D(Analog/Digital)変換器が広く用いられている。

こ の マ ル チ ビ ッ ト デ ル タ シ グ マ A / D 変 換 器 に 設 け ら れ た D / A 変 換 器 を 構 成 す る 単 位 要 素 ( エ レ メ ン ト ) の バ ラ ツ キ に よ り 生 じ る 雑 音 ( ミ ス マ ッ チ 丿 イ ズ ) を 軽 減 す る 方 法 と し て、該雑音の伝達特性に周波数特性をもたせ、使用する信号帯域内の雑音を低減する手法 、ミスマッチノイズシェーピングが知られている。

## [0004]

ローパス型マルチビットデルタシグマA/D変換器では、ミスマッチノイズの伝達特性 をハイパス型とすることにより、信号として使用する低周波数帯域内の雑音を低減できる

#### [00005]

これを実現する手法として、DWA(Data Weighted Averagin g)などが知られている(たとえば、非特許文献1参照)。

10

20

30

40

10

20

30

40

50

[0006]

これに対し、バンドパス型マルチビットデルタシグマ A / D 変換器では、入力信号周波数 f i n でノイズが減少する周波数帯域、いわゆるノッチをもつ雑音の伝達特性が必要となる。

[0007]

多くの場合、バンドパスデルタシグマA/D変換器では、入力信号周波数finとサンプリング周波数fsとの間に、fin=fs/4という関係が成り立つように、入力信号周波数finとサンプリング周波数fsとを設定する。この場合、bandpass mismatch shaping アルゴリズムが用いられる(たとえば、非特許文献2参照)。

[0008]

一方で、使用目的による制約から、入力信号周波数 f i n = サンプリング周波数 f s / 4 の関係が成り立たない場合があり、この時には雑音伝達特性の任意の周波数にノッチを作る必要がある。この場合には、2次 D W A やベクトル量子化器が用いられる(たとえば、非特許文献 3 ~ 8 参照)。

【非特許文献1】Ywvs Greerts, et al, 'DESIGN OF MULTI-BIT DELTA-SIGMA A/D CONVERTERS', p74~p97, Kuuewer Academic Publishers

【非特許文献 2】 T. Shui, et al, 'Mismatch Shaping for a Current-Mode Multibit Delta-Sigma DAC', JSSC 1999, Mar. pp331~pp338

【非特許文献 3】R.K.Henderson, et al.'Dynamic Element Matching with Arbitrary Noise Shaping Function', ISCAS1996, pp293~pp296

【非特許文献 4】R.Schreier, et.al, 'Noise-shaped multi-bit D/A CONVERTER emplying unit elements, 'Electronics Letters, Sept. 1995, Vol. 31, No. 20, pp. 1712~pp. 1713

【非特許文献 5】 Tao Shui, R. Schreier, F. Hudson。'Mismatch-shaping DAC for Lowpass and Bandpass multi-bit Delta-Sigma Modulators' ISCAS 1998, I-352-355

【非特許文献 6】 A. Yasuda, H. Tanimoto, T. Iida, 'A Third order Delta-Sigma Modulator using second-order Noise shaping Dynamic Element Matching', JSSC 1998, Dec. pp. 1879~pp. 1886 【非特許文献 7】 T. Ueno, A. Yasuda, T. Yamaji, T. Itakura, 'A Fourth-order Bandpass Delta-Sigma Modulator using second-order bandpass Noise-shaping DEM'ESSCIRC 2001

【非特許文献 8】 V. Colonna, et. al, 'A 10.7 MHz Self-Calibrated SC Multibit 2nd-Order Bandpass Modulators'ESSCIRC 2002

【発明の開示】

【発明が解決しようとする課題】

[0009]

ところが、上記のようなデルタシグマA/D変換器による雑音の軽減技術では、次のような問題点があることが本発明者により見い出された。

[0010]

デルタシグマ型A/D変換器を無線通信機に使用する場合には、受信する周波数帯域、

受信機の中間周波数、 A / D 変換器のサンプリング周波数、およびその高調波が互いに干渉しないように、中間周波数とサンプリング周波数を決定する必要があり、自由にこれらの周波数を選ぶことはできない。

[0011]

しかし、DWA、bandpass mismatch sharpingといったミスマッチノイズシェーピング法では、サンプリング周波数fsに対して、ミスマッチノイズの伝達特性を自由に設定することができないために、入力信号周波数が、0近傍あるいは、fs/4から外れている場合にミスマッチノイズを低減することができず、S/N比は改善しないという問題がある。

[0012]

また、ミスマッチノイズの伝達特性の任意周波数にノッチ点を持たせる場合、 2 次 D W A は、サンプル周波数 f s より高い周波数で論理を動作する必要があり、消費電力が増加してしまい、高速 A / D 変換器の実現が困難である。さらに、ベクトル量子化器を用いる方法では複雑な論理回路を必要とし、面積、電流が増大するという欠点がある。

[0013]

本発明の目的は、デルタシグマA / D 変換器において、N 個のポインタを用いた単位要素のローテーションにより、入力信号周波数近辺の雑音を低減し、S / N 比を改善することのできる技術を提供することにある。

[0014]

本発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0015]

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のと おりである。

[0016]

本発明は、サンプリング周波数の1/4の周波数以外の信号をデジタル変換するバンドパスデルタシグマ型A/D変換器を備えた半導体集積回路装置であって、該A/D変換器は、入力された信号をデジタル信号に変換して量子化する量子化器と、D/A変換器と、該D/A変換器に設けられたD/A変換器の製造上のばらつきを持つ単位要素を動的にローテーションするエレメントマッチング部を備え、該エレメントマッチング部は、前記量子化器から出力された単位要素の位置を記憶するN個のポインタを備え、該ポインタにより単位素子をシフトし、シフト方向を昇順、または降順に反転させるものである。

[0017]

また、本願のその他の発明の概要を簡単に示す。

[0018]

本発明は、前記エレメントマッチング部が、サンプリング周波数 f s x k ( = 1 , 3 , 5 , ・・・N - 1 ) / ( 2 x ポインタ数 N ) = 入力信号周波数 f i n を満足するように D / A 変換器の単位要素をローテーションするものである。

[0019]

また、本発明は、前記ポインタが、レジスタよりなるものである。

[ 0 0 2 0 ]

さらに、本発明は、前記エレメントマッチング部が、 D / A 変換器の単位要素を 1 2 個のポインタを用いてローテーションし、サンプリング周波数の 7 / 2 4 にミスマッチノイズ伝達特性のノッチ点を持たせるものである。

【発明の効果】

[0021]

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明 すれば以下のとおりである。

[0022]

50

40

10

20

10

20

30

40

50

( 1 ) A / D 変換器における雑音を大幅に低減し、S / N 比を改善することができる。

#### [0023]

(2)上記(1)により、半導体集積回路装置の性能を向上させることができ、該半導体集積回路装置をラジオ受信機などの電子システムに用いることにより、受信性能を向上させることができる。

【発明を実施するための最良の形態】

#### [0024]

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

[ 0 0 2 5 ]

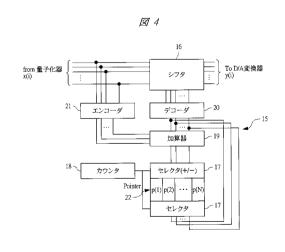

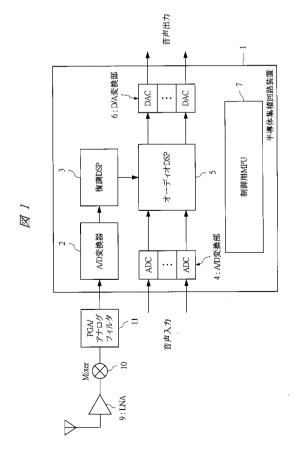

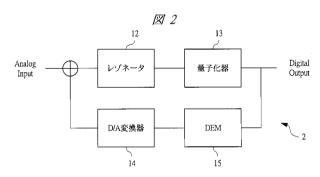

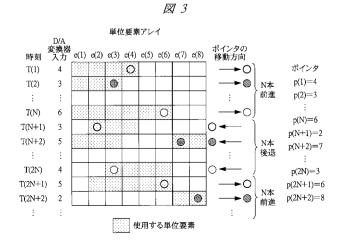

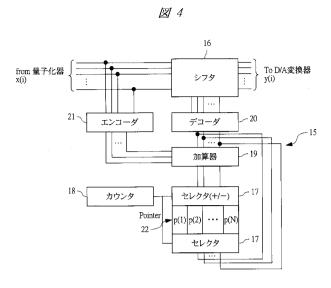

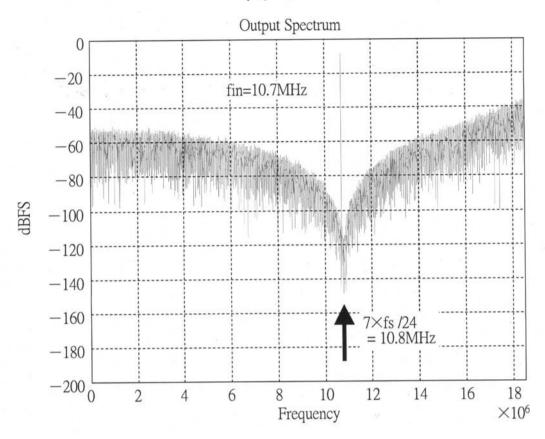

図1は、本発明の一実施の形態による半導体集積回路装置のブロック図、図2は、図1の半導体集積回路装置に設けられたA/D変換器の一例を示すブロック図、図3は、図2のA/D変換器に設けられたDEMのアルゴリズムを示した説明図、図4は、図3に示したローテーションアルゴリズムを実現するDEMのブロック図、図5は、図4のDEMにおけるミスマッチノイズの伝達特性を示した説明図、図6は、図2のA/D変換器のミスマッチノイズの低減例を示す周波数スペクトラムの説明図である。

[0026]

本実施の形態において、半導体集積回路装置1は、たとえば、カーオーディオなどに用いられるマイクロコンピュータである。半導体集積回路装置1は、図1に示すように、A/D変換器2、復調DSP(Digital Signal Processor)3、A/D変換部4、オーディオDSP5、D/A変換部6、および制御用MPU(Multi Processing Unit)7から構成される。

[ 0 0 2 7 ]

A / D変換器 2 は、バンドパス型デルタシグマ A / D変換器からなり、入力された中間周波数信号 I F のアナログ信号をデジタル信号に変換する。アンテナ 8 を介して受信した信号は、LNA(Low Noise Amp) 9 によって増幅され、後段に接続されたミキサ 1 0 により 1 0 . 7 M H z 程度に変換された後、該ミキサ 1 0 の後段に接続された P G A ( P r o g r a m m a b l e G a i n A m p l i f i e r ) / アナログフィルタ 1 1 で任意の出力レベルに増幅、ならびにフィルタリングし、中間周波数信号 I F として A / D 変換器 2 に出力する。

[0028]

A/D変換器2の出力部には、復調DSP3が接続されている。復調DSP3は、中間周波数信号IFを復調し、音声信号に復元する。A/D変換部4は、複数のA/D変換器から構成されており、たとえば、CDプレーヤなどから出力された音声信号をデジタル信号に変換する。

[0029]

オーディオDSP5には、復調DSP3、およびA/D変換部4がそれぞれ接続されている。このオーディオDSP5は、音声信号の加工(たとえば、イコライザや音場補正など)を行う。

[ 0 0 3 0 ]

D / A 変換部 6 は、複数の D / A 変換器から構成されており、オーディオ D S P 5 に接続されている。該オーディオ D S P 5 によって処理された音声信号をアナログ信号に変換する。 D / A 変換部 6 に変換されたアナログ信号は、後段に接続されたアンプなどに出力信号として出力される。制御用 M P U 7 は、半導体集積回路装置 1 におけるすべての制御を司る。

[0031]

図2は、A/D変換器2の構成例を示すブロック図である。

[ 0 0 3 2 ]

A / D 変換器 2 は、レゾネータ 1 2 、量子化器 1 3 、 D / A 変換器 1 4 、ならびに D E

20

30

40

M (エレメントマッチング部) 1 5 から構成されている。レゾネータ 1 2 は、バンドパスフィルタとして用いられる。量子化器 1 3 は、レゾネータ 1 2 を介して入力された中間周波数信号 I F をデジタル信号に変換して量子化する。

#### [0033]

D / A 変換器 1 4 は、量子化器 1 3 から出力されたデジタル信号をアナログ信号に変換する。 D E M ( D y n a m i c E l e m e n t M a t c h i n g ) 1 5 は、使用する D / A 変換器 1 4 の単位要素を動的にローテーションし、該単位要素の製造ばらつきなどによる雑音(ミスマッチノイズ)を低減する。

#### [ 0 0 3 4 ]

DEM15は、量子化器13とD/A変換器14との間に設けられており、該DEM15によって、量子化器13とD/A変換器14との単位要素の接続が動的にスイッチされる。つまり、同一の量子化器出力値に対して、使用されるD/A変換器の単位要素の組み合わせを変えることができる。

## [0035]

ここで、単位素子をローテーションするアルゴリズムによって、ミスマッチノイズの伝達特性は異なる周波数特性を持つことになる。ミスマッチノイズの伝達特性が入力信号周波数 finの近傍でノッチを持てば、この周波数帯域で雑音が軽減され S/N比が改善することになる。

#### [0036]

図3は、DEM15におけるアルゴリズムを示した説明図である。この図3では、一例として量子化器13、およびD/A変換器14を3ビット(8単位素子)とし、N本のポインタを使う場合の単位素子のローテーション方法を示している。

### [0037]

まず、時刻 T ( 1 ) に量子化器 1 3 が 4 を出力したとする。このとき、 D / A 変換器 1 4 は、単位要素配列のうち、 e ( 1 ) , e ( 2 ) , e ( 3 ) , e ( 4 ) を使用して、 4 を出力する。

#### [0038]

ここで、使用された単位要素の位置、 4 をポインタ p ( 1 )に記録する。次の時刻 T ( 2 )に、量子化器 1 4 の出力は 3 で、 e ( 1 ), e ( 2 ), e ( 3 )を使用し、 D / A 変換器 1 4 は 3 を出力し、ポインタ p ( 2 )に 3 を記録する。

#### [0039]

これをN回繰り返し、ポインタ p ( 1 )・・・・, p ( N )を記録する。そして、時刻 T ( N + 1 )に量子化器出力が 3 であったとき、 D / A 変換器 1 4 は、ポインタ p ( 1 )に記録された e ( 4 )から降順に 3 個の単位要素を、すなわち e ( 4 ), e ( 3 ), e ( 2 )を用いて 3 を出力し、ポインタ p ( 1 )には 2 を記録する。この手順を繰り返し、時刻 T ( 2 N + 1 )には、ポインタ p ( 1 )に記録された 2 から昇順に単位要素を使用して、 D / A 変換器 1 4 は出力を行う。

#### [0040]

ここで、たとえば、時刻 T (N+2) のように前回に記録されたポインタ位置が 3 であって、降順に 5 を出力する場合、 e (3), e (2), e (1) を用い、そして循環的に e (8) に戻って、 e (8), e (7) の 5 個の単位要素でデータを出力し、ポインタ位置を e (7) とする。

#### [0041]

同様に昇順の場合に、e(8)に達した場合は、e(1)に循環的に戻って単位要素を使用する。これを数式により表すと、E個の単位要素配列をe(1),e(2)・・・,e(k)、時刻T(n)におけるD/A変換器14の入力をDin(n)、D/A変換器14の出力をDout(n)、D/A変換器14における単位要素のポインタ位置をP(n)として、

#### [0042]

【数1】

$$Dout(n) = \sum_{k=P(n)}^{P(n)+Din(n)} e(k)$$

ポインタ移動が昇順の場合

[0043]

【数2】

$$Dout(n) = \sum_{k=P(n)+E-Din(n)+1}^{P(n)+E} e(k)$$

ポインタ移動が降順の場合

10

[0044]

となる。

[0045]

ここで、 e ( k + E ) = e ( k ) と定義しておく。

[0046]

図 4 は、図 3 に示したローテーションアルゴリズムを実現する D E M 1 5 の構成例を示すブロック図である。

[0047]

DEM15は、図示するように、シフタ16、セレクタ17、カウンタ18、加算器19、デコーダ20、エンコーダ21、ならびにポインタp(1)~p(N)からなるポインタ22から構成される。ポインタp(1)~p(N)は、たとえば、レジスタからなる

[0048]

デコーダ 2 0 は量子化器 1 3 から出力された信号をバイナリコードにデコードする。エンコーダ 2 1 は、加算器 1 9 の演算結果をエンコードしてシフタに出力する。

[0049]

量子化器 1 3 から出力された信号は、 3 ビットの 2 進数に変換され、カウンタ 1 8 により、使用するポインタと単位要素の使用の方向 (昇順/降順)が制御される。記録されたポインタ位置と入力信号を加算することにより、ポインタを移動し、これにより、量子化器 1 3 からの入力 x (i)は、シフトされ y (i)として、 D / A 変換器 1 4 へ出力され、単位要素のシフトが行われる。

[0050]

たとえば、ポインタ数が N=1 2 とした場合、 2 4 / f s 周期で、昇順あるいは降順の要路素子のローテーションが行われることから、 D / A 変換器 1 4 のミスマッチによる / イズの伝達特性には、図 5 に示すように、 1 x f s / 2 4 , 3 x f s / 2 4 , 5 x f s / 2 4 , 7 x f s / 2 4 , 9 x f s / 2 4 , 1 1 x f s / 2 4 に周波数にノッチをそれぞれ持つことになる。

[ 0 0 5 1 ]

[0052]

図 6 に、 D / A 変換器 1 4 を構成する単位要素に製造ばらつきがある A / D 変換器 2 の出力における周波数スペクトラムを示す。

[0053]

図示するように、入力信号周波数 finが10.7MHzの近傍でノイズが抑圧されて

. .

20

30

おり、高いS/N比が得られていることがわかる。このように、DEM15のポインタ2 2の数を適切に選ぶことにより、比較的高い自由度でミスマッチノイズの伝達特性にノッチ点をつくることができる。

[0054]

このように、N個のポインタ22を用いて、D/A変換器14の単位素子をローテーションすることにより、ミスマッチの雑音伝達関数にfs/(2N)、およびその整数倍の周波数にピークあるいはノッチを持つ周波数特性を持たせることができる。

[0055]

それにより、本実施の形態によれば、A/D変換器2のミスマッチノイズを大幅に低減し、S/N比を改善することができる。

[0056]

また、 D E M 1 5 の回路規模を小さくすることができるので、チップレイアウト面積を小さくし、半導体集積回路装置 1 の消費電流を低減することができる。

[0057]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

[0058]

たとえば、中間周波数が10.7MHzで、サンプリング周波数 f s が37.05MHzの場合に、ポインタ数 N = 5 として、単位要素のローテーション周期を10としてもよい。

[0059]

よって、3 / 1 0 × f s = 1 1 . 0 M H z にミスマッチノイズの伝達特性のノッチができることになる。この場合、入力周波数帯域が1 0 . 7 M H z ± 0 . 1 M H z からはずれているが、この周波数帯域であってもミスマッチノイズは充分に抑制されており、要求されるS / N 比がそれほど高くない場合には、ポインタ数を減らして、より少ない回路規模でS / N 比の改善を実現することができる。

【産業上の利用可能性】

[0060]

本発明は、受信機に用いられるA/D変換器のS/N比を改善し、低雑音を実現する技術に適している。

【図面の簡単な説明】

- [0061]

- 【図1】本発明の一実施の形態による半導体集積回路装置のブロック図である。

- 【 図 2 】 図 1 の 半 導 体 集 積 回 路 装 置 に 設 け ら れ た A / D 変 換 器 の 一 例 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【 図 3 】 図 2 の A / D 変 換 器 に 設 け ら れ た D E M の ア ル ゴ リ ズ ム を 示 し た 説 明 図 で あ る 。

- 【図4】図3に示したローテーションアルゴリズムを実現するDEMのブロック図である

- 【図5】図4のDEMにおけるミスマッチノイズの伝達特性を示した説明図である。

- 【図 6 】図 2 の A / D 変換器によるミスマッチノイズの低減例を示す周波数スペクトラムの説明図である。

【符号の説明】

- [0062]

- 1 半導体集積回路装置

- 2 A / D 変換器

- 3 復調 D S P

- 4 A / D 変換部

- 5 オーディオDSP

- 6 D / A 変換部

50

10

20

30

- 7 制御用MPU

- 8 アンテナ

- 9 L N A

- 10 ミキサ

- 11 PGA/アナログフィルタ

- 12 レゾネータ

- 1 3 量子化器

- 1 4 D / A 変換器

- 15 DEM (エレメントマッチング部)

- 16 シフタ

- 17 セレクタ

- 18 カウンタ

- 1 9 加算器

- 20 デコーダ

- 21 エンコーダ

- 22 ポインタ

# 【図1】

## 【図2】

【図3】

【図4】

# 【図5】

【図6】

## フロントページの続き

(72)発明者 中根 秀夫

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 山本 崇也

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5J022 AB02 BA01 CA01 CF07 CG01

5J064 AA01 BA03 BC05 BC06 BC07 BC08 BC16 BC21 BD01