(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5177887号

(P5177887)

(45) 発行日 平成25年4月10日(2013.4.10)

(24) 登録日 平成25年1月18日(2013.1.18)

(51) Int.Cl.

F 1

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)G02F 1/1343

G02F 1/1368

請求項の数 6 (全 11 頁)

(21) 出願番号 特願2008-324657 (P2008-324657)

(22) 出願日 平成20年12月19日 (2008.12.19)

(65) 公開番号 特開2010-145862 (P2010-145862A)

(43) 公開日 平成22年7月1日 (2010.7.1)

審査請求日 平成23年7月4日 (2011.7.4)

(73) 特許権者 302020207

株式会社ジャパンディスプレイセントラル

埼玉県深谷市幡羅町一丁目9番地2

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100095441

弁理士 白根 俊郎

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1基板と第2基板との間に液晶層を保持した構成の液晶表示装置であって、

前記第1基板は、

絶縁基板と、

前記絶縁基板の上に配置されたゲート線と、

前記絶縁基板及び前記ゲート線を覆うように配置された第1絶縁膜と、

前記第1絶縁膜の上に配置された第1電極と、

前記第1絶縁膜の上において前記ゲート線と交差するように配置されたソース線と、

前記第1絶縁膜の上において前記ソース線から離間し、前記ゲート線と対向するように

配置されたシールド電極と、

前記第1絶縁膜、前記第1電極、前記ソース線、及び、前記シールド電極を覆うように

配置された第2絶縁膜と、

前記第2絶縁膜の上において、前記第1電極と対向するように配置され、且つ、前記シ

ルド電極と電気的に接続され、前記第1電極と対向するスリットが形成された第2電極

と、

を備えたことを特徴とする液晶表示装置。

## 【請求項 2】

前記シールド電極は、前記第1電極と同一材料であることを特徴とする請求項1に記載

の液晶表示装置。

**【請求項 3】**

前記シールド電極は、前記ソース線と同一材料であることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 4】**

前記絶縁基板の上に配置されたコモン電位のコモン配線を備え、

前記第 2 電極は、前記第 1 絶縁膜及び前記第 2 絶縁膜を貫通するコンタクトホールを介して前記コモン配線に電気的に接続されたことを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 5】**

前記第 2 電極は、画素がマトリクス状に配置された表示エリアの全域にわたって一面に形成されたことを特徴とする請求項 4 に記載の液晶表示装置。 10

**【請求項 6】**

前記第 1 絶縁膜の上に配置され前記第 1 電極に接続されたドレイン電極を含むスイッチング素子を備えたことを特徴とする請求項 1 に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、液晶表示装置に係り、特に、液晶表示装置を構成する一方の基板に一対の電極を備えた構造の液晶表示装置に関する。 20

**【背景技術】****【0002】**

近年、平面表示装置が盛んに開発されており、中でも液晶表示装置は、軽量、薄型、低消費電力などの特徴を生かして、各種分野に適用されている。このような液晶表示装置は、一対の基板間に液晶層を保持した構成であり、画素電極とコモン電極との間の電界によって液晶層を通過する光に対する変調率を制御し、画像を表示するものである。

**【0003】**

このような液晶表示装置において、広視野角化の観点から、横電界（フリンジ電界も含む）を利用した構造が特に注目されている。In-Plane Switching (IPS) モードや、Fringe Field Switching (FFS) モードなどの横電界モードの液晶表示装置は、アレイ基板に形成された画素電極とコモン電極とを備え、アレイ基板の主面に対してほぼ平行な横電界で液晶分子をスイッチングする。 30

**【0004】**

例えば、特許文献 1 によれば、窒化シリコンで構成された FFS 絶縁膜を介して画素電極と共通電極とを形成し、電極間に電圧を印加して基板面に対して主に平行な横電界を発生させて液晶分子を駆動する技術が開示されている。

**【特許文献 1】特開 2008-116484 号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

上述したような横電界方式において、異なる電位の導電層の間に絶縁膜の界面が位置している場合、この界面に電荷が蓄積しやすい。たとえば、特許文献 1 のような構成の場合、ゲート配線と画素電極あるいは共通電極との間に 2 種類の絶縁膜（層間絶縁膜及び平坦化膜）が介在しており、これらの絶縁膜の間の界面が帯電しやすい。 40

**【0006】**

このような不所望な帯電は、焼き付きなどの表示不良の原因となる。

**【0007】**

この発明の目的は、表示品位を改善することが可能な液晶表示装置を提供することにある。

**【課題を解決するための手段】****【0008】**

この発明の一態様によれば、

第1基板と第2基板との間に液晶層を保持した構成の液晶表示装置であって、

前記第1基板は、

絶縁基板と、

前記絶縁基板の上に配置されたゲート線と、

前記絶縁基板及び前記ゲート線を覆うように配置された第1絶縁膜と、

前記第1絶縁膜の上に配置された第1電極と、

前記第1絶縁膜の上において前記ゲート線と直交するように配置されたソース線と、

前記第1絶縁膜の上において前記ソース線から離間し、前記ゲート線と対向するように配置されたシールド電極と、

前記第1絶縁膜、前記第1電極、前記ソース線、及び、前記シールド電極を覆うように配置された第2絶縁膜と、

前記第2絶縁膜の上において、前記第1電極と対向するように配置され、且つ、前記シールド電極と電気的に接続され、前記第1電極と対向するスリットが形成された第2電極と、

を備えたことを特徴とする液晶表示装置が提供される。

#### 【発明の効果】

#### 【0009】

この発明によれば、表示品位を改善することが可能な液晶表示装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0010】

以下、この発明の一実施の形態に係る液晶表示装置について図面を参照して説明する。ここでは、一方の基板に第1電極及び第2電極を備え、これらの間に形成される横電界（基板の主面にほぼ平行な電界）を主に利用して液晶分子をスイッチングする液晶モードとして、FFSモードの液晶表示装置を例に説明する。

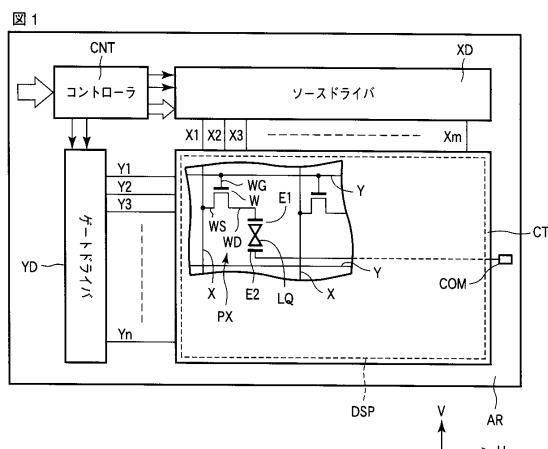

#### 【0011】

図1に示すように、液晶表示装置は、アクティブマトリクスタイプの液晶表示装置であって、液晶表示パネルLPNを備えている。この液晶表示パネルLPNは、アレイ基板（第1基板）ARと、アレイ基板ARに対向して配置された対向基板（第2基板）CTと、これらのアレイ基板ARと対向基板CTとの間に保持された液晶層LQと、を備えて構成されている。このような液晶表示パネルLPNは、画像を表示する表示エリア（アクティブエリア）DSPを備えている。この表示エリアDSPは、 $m \times n$ 個のマトリクス状に配置された複数の画素PXによって構成されている（但し、m及びnは正の整数）。

#### 【0012】

アレイ基板ARは、表示エリアDSPにおいて、各画素PXに配置された $m \times n$ 個の第1電極（画素電極）E1、各画素PXの行方向Hに沿ってそれぞれ延出したn本のゲート線Y（Y1～Yn）、各ゲート線Yと交差するように各画素PXの列方向Vに沿ってそれぞれ延出したm本のソース線X（X1～Xm）、各画素PXにおいてゲート線Yとソース線Xとの交差部を含む領域に配置された $m \times n$ 個のスイッチング素子W、第1電極E1と絶縁膜を介して対向するように配置された第2電極（コモン電極）E2などを備えている。

#### 【0013】

各ゲート線Yは、表示エリア外に引き出され、コントローラCNTによって制御されるゲートドライバYDに接続されている。各ソース線Xは、表示エリア外に引き出され、コントローラCNTによって制御されるソースドライバXDに接続されている。第2電極E2は、コントローラCNTなどから供給されたコモン電位のコモン配線COMに接続されている。

#### 【0014】

ゲートドライバYDは、コントローラCNTによる制御に基づいてn本のゲート線Yに

10

20

30

40

50

順次走査信号（駆動信号）を供給する。また、ソースドライバX Dは、コントローラC N Tによる制御に基づいて各行のスイッチング素子Wが走査信号によってオンするタイミングでm本のソース線Xにそれぞれ映像信号（駆動信号）を供給する。各行の第1電極E 1は、第2電極E 2の電位に対して、対応するスイッチング素子Wを介して供給される映像信号に応じた画素電位にそれぞれ設定される。

## 【0015】

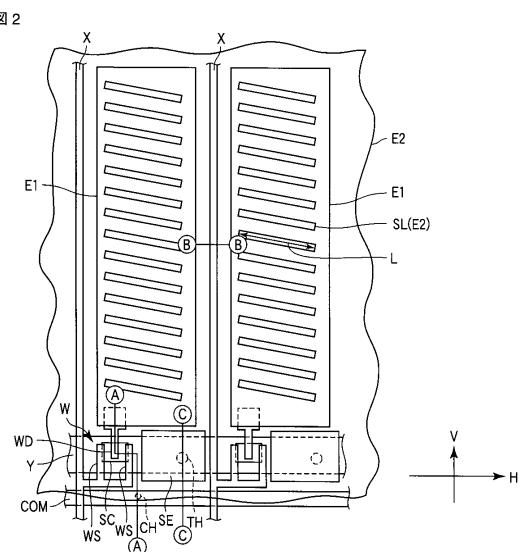

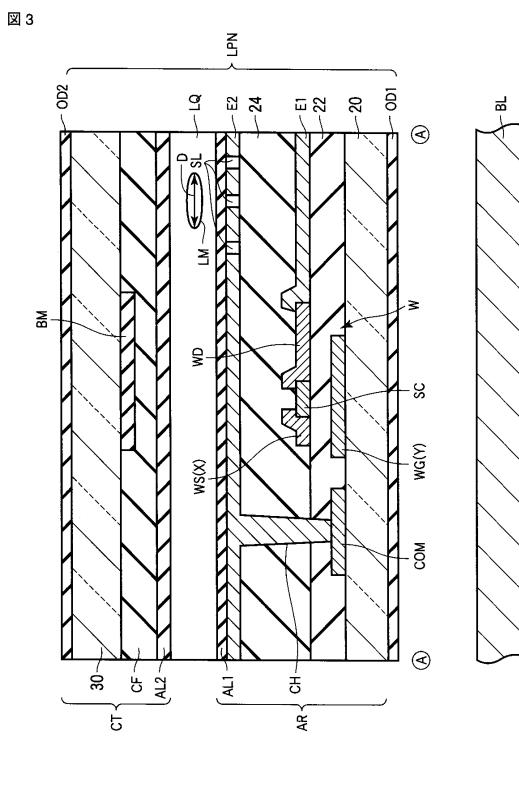

液晶表示パネルL P Nの構造について、以下により詳細に説明する。

## 【0016】

図2及び図3に示すように、アレイ基板A Rは、ガラス板などの光透過性を有する絶縁基板2 0を用いて形成されている。このアレイ基板A Rにおいて、ゲート線Yは、絶縁基板2 0の上に配置されている。また、コモン配線C O Mも同様に、絶縁基板2 0の上に配置されている。このコモン配線C O Mは、ゲート線Yと同様に、行方向Hに沿って延出している。このようなゲート線Y及びコモン配線C O Mは、例えば同一材料を用いて同一工程で形成可能であり、モリブデン、アルミニウム、タンクステン、チタンなどの導電材料によって形成されている。

10

## 【0017】

このような絶縁基板2 0、ゲート線Y及びコモン配線C O Mは、第1絶縁膜であるゲート絶縁膜2 2によって覆われている。このゲート絶縁膜2 2は、例えば窒化シリコン（Si N）などの無機系材料によって形成されている。

## 【0018】

ソース線Xは、ゲート絶縁膜2 2の上に配置されている。このソース線Xは、ゲート絶縁膜2 2を介してゲート線Y及びコモン配線C O Mと略直交している。このようなソース線Xは、例えばチタン／アルミニウム／チタンの積層体によって形成されている。

20

## 【0019】

第1電極E 1は、ゲート絶縁膜2 2の上に配置されている。つまり、この第1電極E 1は、ソース線Xと同一層に配置されている。各ソース線Xは、隣接する第1電極E 1の間に配置されている。すなわち、第1電極E 1は、各画素においてソース線Xから離間するように2本のソース線Xの間に配置されている。

## 【0020】

第1電極E 1は、ソース線Xなどとは異なる材料によって形成され、例えば、インジウム・ティン・オキサイド（ITO）やインジウム・ジンク・オキサイド（IZO）などの光透過性を有する導電材料によって形成されている。また、この第1電極E 1は、各画素P Xにおいて画素形状に対応した島状、例えば、略四角形に形成されている。

30

## 【0021】

これらのゲート絶縁膜2 2、ソース線X及び第1電極E 1は、第2絶縁膜であるパッシベーション膜2 4によって覆われている。このパッシベーション膜2 4は、例えば窒化シリコン（Si N）などの無機系材料によって形成されている。

## 【0022】

第2電極E 2は、パッシベーション膜2 4の上に配置されている。この第2電極E 2は、パッシベーション膜2 4を介して各画素P Xの第1電極E 1と対向する。つまり、パッシベーション膜2 4は、第1電極E 1と第2電極E 2との間に介在する層間絶縁膜として機能する。

40

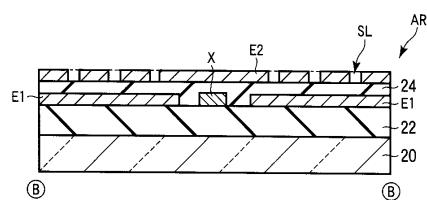

## 【0023】

このような第2電極E 2は、表示エリアD S Pの全体にわたって一面に配置されている。すなわち、この第2電極E 2は、各画素P Xに対応して配置されるとともに画素間にも配置された概ねベタ状である。つまり、第2電極E 2は、図3に示したようにゲート線Y及びコモン配線C O Mに対向するとともに、図4に示したようにソース線Xともに対向するように配置されている。なお、図4では、アレイ基板A Rの主要部のみを図示している。第2電極E 2は、第1電極E 1と同様に、例えばITOやIZOなどの光透過性を有する導電材料によって形成されている。

50

## 【0024】

第2電極E2には、第1電極E1と対向するスリットSLが形成されている。ここでは、第2電極E2のスリットSLは、例えば、略長方形状あるいは略長円形状に形成されている。図2に示した例では、このスリットSLは、その長軸Lが行方向H及び列方向Vと非平行となるように形成されている。このような複数のスリットSLは、列方向Vに並んでいるが、この形状に限らない。例えば、列方向Vに縦長の画素の上側半分と下側半分とでスリットSLの向きが異なっていても良い。

## 【0025】

この第2電極E2は、コモン配線COMに電気的に接続されている。コモン配線COMと第2電極E2との間には、ゲート絶縁膜22及びパッシベーション膜24が介在している。第2電極E2は、これらのゲート絶縁膜22及びパッシベーション膜24を貫通するコンタクトホールCHを介してコモン配線COMに電気的に接続されている。

10

## 【0026】

スイッチング素子Wは、例えば、薄膜トランジスタ(TFT)によって構成されている。スイッチング素子Wの半導体層SCは、例えば、ポリシリコンやアモルファスシリコンなどによって形成可能であり、ここではアモルファスシリコンによって形成され、ボトムゲート型のトランジスタを構成している。

## 【0027】

スイッチング素子Wのゲート電極WGは、ゲート線Yに電気的に接続されている。このゲート電極WGは、ゲート線Yと同一材料を用いて同一工程で形成可能であり、ここでは、絶縁基板20の上においてゲート線Yと一体的に形成されている。このゲート電極WGは、ゲート絶縁膜22によって覆われている。

20

## 【0028】

スイッチング素子Wの半導体層SCは、ゲート絶縁膜22の上においてゲート電極WGと対向するように島状に配置されている。

## 【0029】

スイッチング素子Wのソース電極WS及びドレイン電極WDは、ゲート絶縁膜22の上に配置されている。ソース電極WSは、ソース線Xに電気的に接続される(あるいはソース線Xと一体的に形成される)とともに、半導体層SCにコンタクトしている。ドレイン電極WDは、第1電極E1に電気的に接続されるとともに、ソース電極WSから離れて半導体層SCにコンタクトしている。つまり、第1電極E1とスイッチング素子Wのドレイン電極WDとは、スルーホールを介すことなく直接接続されている。

30

## 【0030】

これらのソース電極WS及びドレイン電極WDは、ソース線Xと同一材料を用いて同一工程で形成可能である。このような半導体層SC、ソース電極WS及びドレイン電極WDは、パッシベーション膜24によって覆われている。

## 【0031】

このような構成のアレイ基板ARの液晶層LQに接する面は、配向膜AL1によって覆われている。

## 【0032】

一方、対向基板CTは、ガラス板などの光透過性を有する絶縁基板30を用いて形成されている。図3に示したように、対向基板CTは、絶縁基板30の内面(すなわち液晶層LQに対向する面)に、各画素PXを区画するブラックマトリクスBMを備えている。

40

## 【0033】

ブラックマトリクスBMは、絶縁基板30上において、アレイ基板ARに設けられたゲート線Yやソース線X、さらにはスイッチング素子Wなどの配線部に対向するように格子状に配置されている。このブラックマトリクスBMは、例えば黒色に着色された樹脂材料やクロム(Cr)などの遮光性の金属材料によって形成されている。

## 【0034】

特に、カラー表示タイプの液晶表示装置においては、対向基板CTは、ブラックマトリ

50

クス B M によって囲まれた領域にカラーフィルタ層 C F を備えている。カラーフィルタ層 C F は、絶縁基板 3 0 上に配置され、互いに異なる複数の色、例えば赤色、青色、緑色といった 3 原色にそれぞれ着色された樹脂によって形成されている。赤色着色樹脂、青色着色樹脂、及び緑色着色樹脂は、それぞれ赤色画素、青色画素、及び緑色画素に対応して配置されている。

【 0 0 3 5 】

上述したような横電界を利用した液晶モードにおいては、対向基板 C T の液晶層 L Q に接する面が平坦であることが望ましく、対向基板 C T は、さらに、カラーフィルタ層 C F の表面の凹凸を平坦化するように比較的厚い膜厚で配置されたオーバーコート層などを備えていることが望ましい。

10

【 0 0 3 6 】

対向基板 C T の液晶層 L Q に接する面は、配向膜 A L 2 によって覆われている。配向膜 A L 1 及び A L 2 は、例えばポリイミドによって形成されている。

【 0 0 3 7 】

上述したようなアレイ基板 A R と対向基板 C T とは、それぞれの配向膜 A L 1 及び配向膜 A L 2 が対向するように配置されている。このとき、アレイ基板 A R と対向基板 C T との間には、図示しないスペーサ（例えば、樹脂材料によって一方の基板と一体的に形成された柱状スペーサ）が配置され、これにより、所定のギャップが形成される。アレイ基板 A R と対向基板 C T とは、所定のギャップが形成された状態でシール材によって貼り合わせられている。

20

【 0 0 3 8 】

液晶層 L Q は、これらのアレイ基板 A R の配向膜 A L 1 と対向基板 C T の配向膜 A L 2 との間に形成されたギャップに封入された液晶分子 L M を含む液晶組成物によって構成されている。

【 0 0 3 9 】

配向膜 A L 1 及び配向膜 A L 2 は、液晶層 L Q に含まれる液晶分子 L M の配向を規制するようにラビング処理されている。液晶層 L Q に含まれる液晶分子 L M は、配向膜 A L 1 及び配向膜 A L 2 による規制力によって配向されている。配向膜 A L 1 及び配向膜 A L 2 のラビング方向は、第 2 電極 E 2 に形成されたスリット S L の長軸と非平行且つ非直角である。

30

【 0 0 4 0 】

透過型の液晶表示パネル L P N を備えた液晶表示装置は、さらに、液晶表示パネル L P N に対してアレイ基板 A R 側に配置された照明ユニットすなわちバックライトユニット B L を備えている。このバックライトユニット B L は、アレイ基板 A R 側から液晶表示パネル L P N を照明する。このようなバックライトとしては、種々の形態が適用可能であり、また、光源として発光ダイオード（L E D）を利用したもののや冷陰極管（C C F L）を利用したものなどのいずれでも適用可能であり、詳細な構造については説明を省略する。

【 0 0 4 1 】

この液晶表示装置は、液晶表示パネル L P N の一方の外面（すなわちアレイ基板 A R の液晶層 L Q と接触する面とは反対の面）に設けられた光学素子 O D 1 を備え、また、液晶表示パネル L P N の他方の外面（すなわち対向基板 C T の液晶層 L Q と接触する面と反対の面）に設けられた光学素子 O D 2 を備えている。

40

【 0 0 4 2 】

これらの光学素子 O D 1 及び O D 2 は、それぞれ偏光板を含み、例えば、第 1 電極 E 1 と第 2 電極 E 2 との間に電位差が形成されていない（つまり、第 1 電極 E 1 と第 2 電極 E 2 との間に電界が形成されていない）無電界時において、液晶表示パネル L P N の透過率が最低となる（つまり、黒色画面を表示する）ノーマリーブラックモードを実現している。

【 0 0 4 3 】

すなわち、このような液晶表示装置においては、無電界時には、液晶分子 L M は、その

50

長軸 D が配向膜 A L 1 及び配向膜 A L 2 のラビング方向 S と平行な方位を向くように配向されている。このような状態では、バックライトユニット B L からのバックライト光は、光学素子 O D 1 を透過した後、液晶表示パネル L P N を透過し、光学素子 O D 2 に吸収される（黒色画面表示）。

【 0 0 4 4 】

第 1 電極 E 1 と第 2 電極 E 2 との間に電位差が形成された場合（つまり、第 1 電極 E 1 にコモン電位とは異なる電位の電圧が印加された電圧印加時）には、第 1 電極 E 1 と第 2 電極 E 2 との間に横電界（フリンジ電界）が形成される。この横電界は、スリット S L を介してその長軸 L に対して直交する方位に形成される。

【 0 0 4 5 】

このとき、液晶分子 L M の配向状態は、例えば液晶分子 L M の長軸 D がラビング方向 S から横電界に平行な方向を向くように変化する。このように、液晶分子 L M の長軸 D の方位がラビング方向 S から変化すると、液晶層 L Q を透過する光に対する変調率が変化する。このため、バックライトユニット B L から出射され液晶表示パネル L P N を透過したバックライト光の一部は、第 2 光学素子 O D 2 を透過する（白色画面表示）。つまり、液晶表示パネル L P N の透過率は、電界の大きさに依存して変化する。横電界を利用した液晶モードでは、このようにして選択的にバックライト光を透過し、画像を表示する。

【 0 0 4 6 】

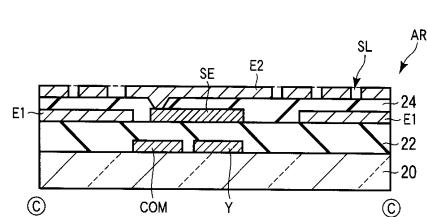

ところで、この実施の形態においては、液晶表示装置は、ゲート線 Y と第 2 電極 E 2 との間に電気的にシールドするシールド電極 S E を備えている。すなわち、図 2 及び図 5 に示すように、シールド電極 S E は、ゲート絶縁膜 2 2 の上においてソース線 X から離間し、ゲート線 Y と対向するように配置されている。なお、図 5 では、アレイ基板 A R の主要部のみを図示している。このようなシールド電極 S E は、パッシベーション膜 2 4 によって覆われている。

【 0 0 4 7 】

第 2 電極 E 2 は、パッシベーション膜 2 4 を介してシールド電極 S E と対向し、パッシベーション膜 2 4 を貫通するスルーホール T H を介してシールド電極 S E と電気的に接続されている。つまり、シールド電極 S E は、第 2 電極 E 2 と同様に、コモン電位に設定されている。

【 0 0 4 8 】

このような構成によれば、異なる電位の導電層の間に絶縁膜の界面が位置しなくなる。すなわち、この実施の形態によれば、ゲート絶縁膜 2 2 とパッシベーション膜 2 4 とが直接重なる部分において絶縁膜の界面が形成される。このような界面では、膜質の差などに起因してチャージしやすい。

【 0 0 4 9 】

本実施形態では、絶縁基板 2 0 上において同一層に配置されたゲート線 Y 及びコモン配線 C O M と、パッシベーション膜 2 4 上において同一層に配置された第 2 電極 E 2 との間に、ゲート絶縁膜 2 2 及びパッシベーション膜 2 4 が介在する。ここで、コモン配線 C O M と第 2 電極 E 2 とは実質的に同電位であり、たとえこれらの間に絶縁膜の界面が介在しても、チャージアップすることはない。一方で、ゲート線 Y と第 2 電極 E 2 とは異なる電位であり、これらの間に絶縁膜の界面が存在する場合、チャージアップするおそれがある。

【 0 0 5 0 】

そこで、ゲート線 Y と第 2 電極 E 2 との間に位置するゲート絶縁膜 2 2 上にシールド電極 S E を配置したことにより、ゲート絶縁膜 2 2 とパッシベーション膜 2 4 とが直接重なることがなく、チャージアップの原因となる界面が形成されない。このため、チャージアップに起因した焼き付などの不良の発生を抑制することができ、表示品位を改善することが可能となる。

【 0 0 5 1 】

なお、このシールド電極 S E は、コモン電位となることから、同一層に配置されるソ-

10

20

30

40

50

ス線 X 及び第 1 電極 E 1 とは電気的に絶縁されている。つまり、シールド電極 S E とソース線 X 及び第 1 電極 E 1 とは互いに離間している。

【 0 0 5 2 】

このようなシールド電極 S E は、ゲート絶縁膜 2 2 の上に配置される他の導電層、例えば第 1 電極 E 1 あるいはソース線 X と同一材料によって形成可能である。これによれば、シールド電極 S E は、第 1 電極 E 1 あるいはソース線 X と同一工程で形成可能である。このため、シールド電極 S E を形成するための別個の工程を追加する必要がなく、材料の利用効率の改善、さらには、製造コストの増大を抑制できる。

【 0 0 5 3 】

なお、製造プロセス上の制約がある場合、シールド電極 S E は、ソース線 X と同一材料によって形成することがより望ましい。具体的には、第 2 電極 E 2 とコモン配線 C O M とを接続するコンタクトホール C H 及び第 2 電極 E 2 とシールド電極 S E とを接続するスルーホール T H を同時に形成する場合、このエッチング工程においては、コンタクトホール C H がゲート絶縁膜 2 2 及びパッシベーション膜 2 4 を確実に貫通する一方で、スルーホール T H がパッシベーション膜 2 4 を貫通してシールド電極 S E で留まるような選択比に設定される。

【 0 0 5 4 】

このとき、第 1 電極 E 1 を形成するような I T O などの導電材料は、スルーホール T H を形成するエッティングによって削られやすく、接続抵抗の上昇を招いたり、最悪の場合は除去されて導通を確保できなくなったりする場合もある。

10

20

【 0 0 5 5 】

一方で、ソース線 X を形成する金属材料は、エッティングの際の選択比によって確実に残留させる制御が容易である。したがって、導通の信頼性を確保しやすい。

【 0 0 5 6 】

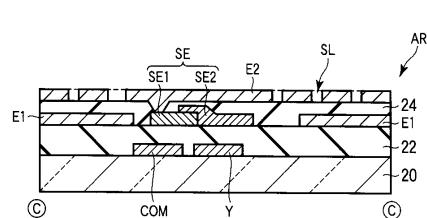

図 5 に示した例では、シールド電極 S E は、第 1 電極 E 1 あるいはソース線 X と同一材料によって単一の導電層として形成したが、複数の導電層を組み合わせて形成しても良い。

【 0 0 5 7 】

例えば、図 6 に示した例では、シールド電極 S E は、スルーホール T H を介して第 2 電極 E 2 とコンタクトするコンタクト部 S E 1 と、主としてゲート線 Y と第 2 電極 E 2 との間に介在するシールド部 S E 2 とによって構成されている。なお、図 6 では、アレイ基板 A R の主要部のみを図示している。

30

【 0 0 5 8 】

コンタクト部 S E 1 については、上述した通り、導通の信頼性を確保する上で、ソース線 X を形成する金属材料によって形成することが望ましい。シールド部 S E 2 は、第 1 電極 E 1 と同一材料によって形成されている。

【 0 0 5 9 】

このような構成であっても、先に示した例と同様の効果が得られる。

【 0 0 6 0 】

以上説明したように、この実施の形態によれば、良好な表示品位を実現することが可能な液晶表示装置を提供することができる。

40

【 0 0 6 1 】

なお、この発明は、上記実施形態そのものに限定されるものではなく、その実施の段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてよい。

【 図面の簡単な説明 】

【 0 0 6 2 】

【 図 1 】図 1 は、この発明の一実施の形態に係る横電界を利用した液晶モードの液晶表示

50

装置の構成を概略的に示す図である。

【図2】図2は、図1に示した液晶表示装置に適用される画素の構成例を概略的に示す平面図である。

【図3】図3は、図2に示した画素をA-A線で切断したスイッチング素子を含む構造を概略的に示す断面図である。

【図4】図4は、図2に示した画素をB-B線で切断したソース線を含む構造を概略的に示す断面図である。

【図5】図5は、図2に示した画素をC-C線で切断したシールド電極を含む構造を概略的に示す断面図である。

【図6】図6は、図2に示した画素をC-C線で切断したシールド電極を含む他の構造を概略的に示す断面図である。 10

【符号の説明】

【0063】

L P N ... 液晶表示パネル

A R ... アレイ基板 C T ... 対向基板 L Q ... 液晶層

D S P ... 表示エリア P X ... 画素

Y ... ゲート線 X ... ソース線 C O M ... コモン配線 W ... スイッチング素子

E 1 ... 第1電極(画素電極) E 2 ... 第2電極(コモン電極) S L ... スリット

2 2 ... ゲート絶縁膜(第1絶縁膜) 2 4 ... パッシベーション膜(第2絶縁膜)

3 0 ... 絶縁基板 B M ... ブラックマトリクス C F ... カラーフィルタ層

S E ... シールド電極 S E 1 ... コンタクト部 S E 2 ... シールド部

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100100952

弁理士 風間 鉄也

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100070437

弁理士 河井 将次

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 森田 伸

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

審査官 佐藤 洋允

(56)参考文献 特開2007-233317 (JP, A)

特開平11-186561 (JP, A)

特開平10-221705 (JP, A)

特開2002-221736 (JP, A)

特開2001-183699 (JP, A)

特開2008-216858 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1343 - 1 / 1345

G 02 F 1 / 135 - 1 / 1368