(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5455299号

(P5455299)

(45) 発行日 平成26年3月26日(2014.3.26)

(24) 登録日 平成26年1月17日(2014.1.17)

|               |                   |

|---------------|-------------------|

| (51) Int.Cl.  | F 1               |

| HO 1 L 21/02  | (2006.01)         |

| HO 1 L 27/12  | (2006.01)         |

| HO 1 L 21/762 | (2006.01)         |

| HO 1 L 21/336 | (2006.01)         |

| HO 1 L 29/786 | (2006.01)         |

| HO 1 L 27/12  | HO 1 L 27/12 B    |

| HO 1 L 21/76  | HO 1 L 21/76 D    |

| HO 1 L 29/78  | HO 1 L 29/78 627D |

請求項の数 10 (全 22 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-290447 (P2007-290447)  |

| (22) 出願日  | 平成19年11月8日 (2007.11.8)        |

| (65) 公開番号 | 特開2009-117688 (P2009-117688A) |

| (43) 公開日  | 平成21年5月28日 (2009.5.28)        |

| 審査請求日     | 平成22年10月26日 (2010.10.26)      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (74) 代理人  | 100103159<br>弁理士 加茂 裕邦                         |

| (72) 発明者  | 秋元 健吾<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 右田 勝則                                          |

(56) 参考文献 特開2005-093680 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

歪み点が750以上である第1の基板上に剥離層を形成し、前記剥離層に段差を設け、前記剥離層上に、前記段差を埋める第1の接合層を形成する工程と、

単結晶シリコン基板である半導体基板の表面から一定の深さに損傷層を形成し、該損傷層が形成された前記半導体基板の表面に、下地絶縁膜を形成し、前記下地絶縁膜上に、第2の接合層を形成する工程と、

前記第1の接合層と、前記第2の接合層とを貼り合わせて前記損傷層で剥離することで、前記第1の基板上に半導体層を形成し、前記半導体層を有する半導体素子を形成する工程と、

前記半導体素子を前記剥離層に設けられた前記段差から剥離することで可撓性基板である第2の基板上に転置する工程と、を有し、

前記剥離層が前記段差により厚くなっている領域に前記半導体素子が形成されることを特徴とする半導体装置の作製方法。

## 【請求項 2】

歪み点が750以上である第1の基板上に剥離層を形成し、前記剥離層に段差を設け、前記剥離層上に、前記段差を埋める第1の接合層を形成する工程と、

単結晶シリコン基板である半導体基板の表面から一定の深さに損傷層を形成し、該損傷層が形成された前記半導体基板の表面に、下地絶縁膜を形成する工程と、

前記第1の接合層と、前記下地絶縁膜とを貼り合わせて前記損傷層で剥離することで、

10

20

前記第1の基板上に半導体層を形成し、前記半導体層を有する半導体素子を形成する工程と、

前記半導体素子を前記剥離層に設けられた前記段差から剥離することで可撓性基板である第2の基板上に転置する工程と、を有し、

前記剥離層が前記段差により厚くなっている領域に前記半導体素子が形成されることを特徴とする半導体装置の作製方法。

【請求項3】

単結晶シリコン基板である半導体基板の表面から一定の深さに損傷層を形成し、該損傷層が形成された前記半導体基板の表面に、下地絶縁膜を形成し、前記下地絶縁膜上に剥離層を形成し、前記剥離層に段差を設け、前記剥離層上に第1の接合層を形成する工程と、

歪み点が750以上である第1の基板の表面と、前記第1の接合層とを貼り合わせて前記損傷層で剥離することで、前記第1の基板上に半導体層を形成し、前記半導体層を有する半導体素子を形成する工程と、

前記半導体素子を前記剥離層に設けられた前記段差から剥離することで可撓性基板である第2の基板上に転置する工程と、を有し、

前記剥離層が前記段差により厚くなっている領域に前記半導体素子が形成されることを特徴とする半導体装置の作製方法。

【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第1の接合層はCMPにて平坦化されていることを特徴とする半導体装置の作製方法。

【請求項5】

歪み点が750以上である第1の基板上に第1の接合層を形成する工程と、

単結晶シリコン基板である半導体基板の表面から一定の深さに損傷層を形成し、該損傷層が形成された前記半導体基板の表面に、下地絶縁膜を形成し、前記下地絶縁膜上に剥離層を形成し、前記剥離層に段差を設け、前記剥離層上に前記段差を埋める第2の接合層を形成する工程と、

前記第1の接合層と、前記第2の接合層とを貼り合わせて前記損傷層で剥離することで、前記第1の基板上に半導体層を形成し、前記半導体層を有する半導体素子を形成する工程と、

前記半導体素子を前記剥離層に設けられた前記段差から剥離することで可撓性基板である第2の基板上に転置する工程と、を有し、

前記剥離層が前記段差により厚くなっている領域に前記半導体素子が形成されることを特徴とする半導体装置の作製方法。

【請求項6】

請求項5において、

前記第2の接合層はCMPにて平坦化されていることを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至請求項6のいずれか一項において、

前記半導体素子を第2の基板上に転置する工程において、前記第1の基板上の各半導体素子が形成される領域の、前記剥離層の膜厚は略均一であることを特徴とする半導体装置の作製方法。

【請求項8】

請求項1乃至請求項7のいずれか一項において、

前記剥離層は、金属材料で形成される第1の剥離層と、絶縁材料で形成される第2の剥離層とで形成することを特徴とする半導体装置の作製方法。

【請求項9】

請求項8において、

前記第1の剥離層がタンゲステン膜であり、前記第2の剥離層が酸化シリコン膜である

10

20

30

40

50

ことを特徴とする半導体装置の作製方法。

【請求項 10】

請求項 8 又は請求項 9 において、

前記第 2 の剥離層に段差部を形成することを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の作製方法に関する。特に、可撓性基板上に半導体装置を作製する半導体装置の作製方法に関する。

【背景技術】

10

【0002】

半導体装置を設ける基板として可撓性基板を用いることで、フレキシブルな半導体装置を作製する技術が開発されている（特許文献 1 を参照）。可撓性基板上に半導体層を有する半導体装置の作製方法として、可撓性基板上に半導体層を直接形成する方法が挙げられる。しかし、好ましくは、必要な耐熱性を有する基板上に剥離層を形成し、該剥離層上に半導体層を有する素子を形成し、該剥離層をきっかけとして可撓性基板に素子を転置する方法を用いる。

耐熱性を有する基板としては、耐熱性ガラスなどの絶縁性基板を用い、剥離層は、例えば、スパッタリング法等により設ける。

【0003】

20

一方、耐熱性ガラスなどの絶縁性基板に単結晶シリコン層を設けた半導体装置が開示されている（特許文献 2 を参照）。この半導体装置は、歪み点が 750 以上の結晶化ガラスの全面を絶縁性シリコン膜で保護し、水素イオン注入剥離法により得られる単結晶シリコン層を該絶縁性シリコン膜上に固着した構成を有する。

【特許文献 1】特開 2003-204049 号公報

【特許文献 2】特開平 11-163363 号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

耐熱性を有する基板上に剥離層を形成し、その上に半導体層を有する素子を形成し、前記剥離層をきっかけとして可撓性基板に素子を転置する場合、歩留まり良く転置できることが望ましい。しかしながら所望する半導体層を有する素子のサイズ、工程温度上限、あるいは半導体層を有する素子の構造の厚さによっては、転置工程時にクラックが発生する。

【0005】

本発明は、耐熱性及び耐薬品性の低い基板上に、信頼性の高い半導体装置を作製することを課題の一とする。また、耐熱性及び耐薬品性の低い基板上に半導体装置を歩留まり良く作製することを課題の一とする。

【課題を解決するための手段】

【0006】

本発明の半導体装置の作成方法の一は、上記課題を達成するために、耐熱性を有する基板上に TFT が形成される構造にて、前記耐熱性を有する基板と TFT との間に剥離層を形成する工程を有する。さらに所望する半導体装置が形成される隙間（すなわち平面上で半導体装置と、半導体装置と、の間の領域）の、剥離層の膜厚を変える、すなわち剥離層に段差を設ける加工工程を有する。

【0007】

この構造により、例え前記剥離層をきっかけとして可撓性基板に素子を転置する工程にてクラックが入るのを避けられない状態でも、所望の素子自体へのダメージを避け、歩留まりを高くすることができる。なぜなら、所望する半導体装置が形成される間の領域のみ比較的脆弱となり、クラックが優先的に入るからである。

【0008】

30

40

50

所望する半導体装置が形成される間の領域は、後に素子を個別に分離するとき余白となる領域であり、この領域のクラックは歩留まりに影響することは無い。

#### 【0009】

尚、好適には、前記剥離層は、タンゲステン上に酸化シリコンを積層する構造とする。そしてこのとき、剥離層の膜厚を変える工程では、酸化シリコンの膜厚を変える。スパッタ成膜の酸化シリコン膜厚については、200 nm ~ 500 nmとする。すなわち、この範囲にて段差を設ける。

#### 【0010】

上記原理の一つは、剥離層であるタンゲステン膜とその上層に形成された酸化シリコンの積層構造の各膜厚にて、タンゲステン膜厚が一定のとき、酸化シリコン膜厚が厚いほど剥離転置時に剥離しやすく、逆に酸化シリコン膜厚が薄くなれば剥離転置時に基板に残りやすい傾向がある、という本発明者らの経験に基づいたものである。本発明者の標準とするプロセスでは、酸化シリコン膜厚 200 nm 以上にて剥離が可能であることが判っている。本発明者はこの原理を、酸化シリコン膜の膜厚が厚いほど、欠陥や転位などが増え、剥離の切掛けが出来やすくなるものと考察する。

10

#### 【0011】

もう一つの上記原理は、剥離転置の際、特に構造の境目に、クラックが出来やすい、あるいは基板に残りやすいという現象に基づいたものである。本発明者はこの現象を、構造が異なる部分にて、両領域の応力の差からクラックの切掛けが出来やすいため、と考察する。すなわち剥離層部分で構造の違いがあっても、そこにクラックが出来やすいと考えられる。

20

#### 【0012】

尚、膜厚が厚くなるにつれ、欠陥や転位などが増え、剥離の切掛けが出来やすくなることから、剥離層が他の材料からなる単層の場合でも、局所的に膜厚を変えることでクラックの入りやすさを制御できると考えられる。すなわち本発明において、剥離層は単層でも、2層以上の積層構造でも有効である。

#### 【0013】

本発明の作成方法は、耐熱性を有する基板上に剥離層を形成し、該剥離層上に半導体層を有する素子を形成する場合に用いられる一方、耐熱性を有する基板上に、水素イオン注入剥離法により得られる単結晶シリコン層を固着した構成にも適用できる。

30

#### 【0014】

耐熱性を有する基板上に単結晶シリコン層を固着するときは、前記耐熱性を有する基板と、前記単結晶シリコン層との間に剥離層を形成する。より詳細には、耐熱性を有する基板と水素イオン注入剥離法により得られる単結晶シリコン層が設けられたシリコンウエハ基板とを貼りあわせる工程前に、シリコンウエハ基板もしくは耐熱性を有する基板、いずれかの張り合わせ面に剥離層を形成する。この酸化シリコンは成膜後、フォトリソグラフィー及びプラズマエッチングにより、所望する半導体装置間の膜厚を選択的に薄くする。

#### 【0015】

上記手段の剥離層を形成した後、さらに絶縁層を形成する。この絶縁層を C M P ( C h e m i c a l M e c h a n i c a l P o l i s h i n g ) にて平坦化し、接合層を形成する。すなわち耐熱性を有する基板とシリコンウエハ基板のいずれかの面に接合層が形成される。もしくは、両方の基板に接合層を設けても良い。接合層を介し耐熱性を有する基板とシリコンウエハ基板を貼りあわせた後、損傷層を境に単結晶シリコン層が設けられた耐熱性を有する基板と、シリコンウエハ基板とを引き剥がす。その後耐熱性を有する基板上にて所望の素子を形成後、粘着シート等により可撓性基板に剥離転置する。

40

#### 【0016】

本発明の一は、第 1 の基板上に剥離層を形成し、前記剥離層に段差を設け、前記剥離層上に、表面の平坦性が高い第 1 の接合層を形成し、半導体基板の表面から一定の深さに損傷層を形成し、該損傷層が形成された半導体基板上に表面に、下地絶縁膜を形成し、前記下地絶縁膜上に、第 2 の接合層を形成し、前記第 1 の接合層と、前記第 2 の接合層とを貼り

50

合わせて前記損傷層で剥離することで、前記第1の基板上に半導体層を形成し、前記半導体層を有する半導体素子を形成し、前記半導体素子を第2の基板上に転置することを特徴とする半導体装置の作製方法である。

#### 【0017】

本発明の一は、第1の基板上に表面の平坦性が高い第1の接合層を形成し、半導体基板の表面から一定の深さに損傷層を形成し、該損傷層が形成された半導体基板上に表面に、下地絶縁膜を形成し、前記下地絶縁膜上に剥離層を形成し、前記剥離層に段差を設け、前記剥離層上に表面の平坦性が高い第2の接合層を形成し、前記第1の接合層と、前記第2の接合層とを貼り合わせて前記損傷層で剥離することで、前記第1の基板上に半導体層を形成し、前記半導体層を有する半導体素子を形成し、前記半導体素子を第2の基板上に転置することを特徴とする半導体装置の作製方法である。

10

#### 【0018】

上記構成の本発明において、好ましくは、前記耐熱性を有する基板は、ガラス基板である。

#### 【0019】

上記構成の本発明において、好ましくは、前記半導体基板は単結晶シリコン基板である。

#### 【発明の効果】

#### 【0020】

本発明によれば、剥離層に段差を設けることで、その段差が可撓性基板に半導体装置を剥離転置するときの、クラック発生領域の選択性に作用し、半導体装置へのクラック発生を防止するので、半導体装置の製造歩留まりを向上させることができる。

20

#### 【発明を実施するための最良の形態】

#### 【0021】

本発明の実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態及び実施例の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

#### 【0022】

30

#### (実施の形態1)

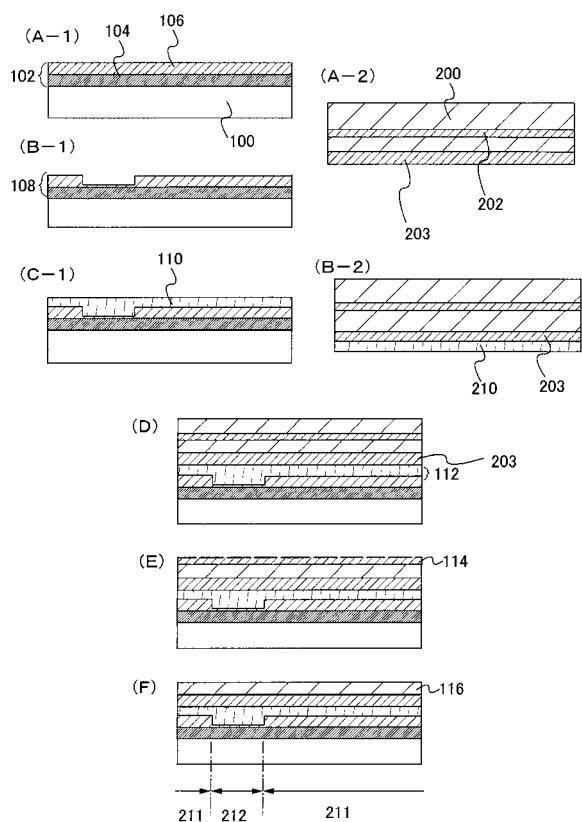

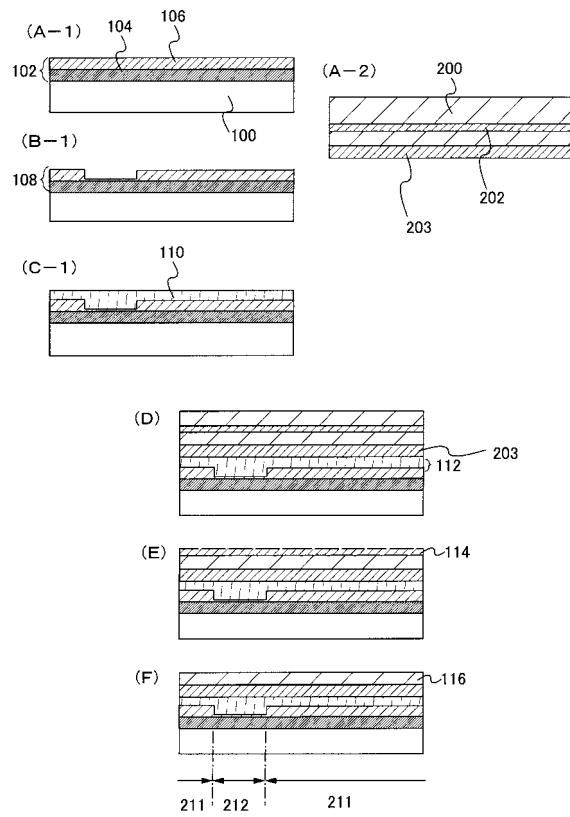

本実施の形態では、本発明に係る半導体装置の作製方法の例について、図面を参照して説明する。本発明に係る半導体装置の作製方法では、まず、第1の基板100と半導体基板200を用いる。

#### 【0023】

第1の基板100は、作製工程に耐えうる程度に高耐熱性及び高耐薬品性等であればよく、基板の材料は特定のものに限定されない。例えば、ガラス基板、石英基板、シリコン基板若しくはステンレス基板等又はこれらの基板上に絶縁膜を形成した基板を用いることができる。本実施の形態では、ガラス基板を用いる。

#### 【0024】

40

半導体基板200の材料としては、代表的にはシリコン又はゲルマニウムを用いる。または、ガリウムヒ素、インジウムリン等の化合物半導体を用いても良い。また、半導体基板200は単結晶半導体基板に限定されず、多結晶半導体基板であってもよい。本実施の形態では、単結晶シリコン基板を用いる。

#### 【0025】

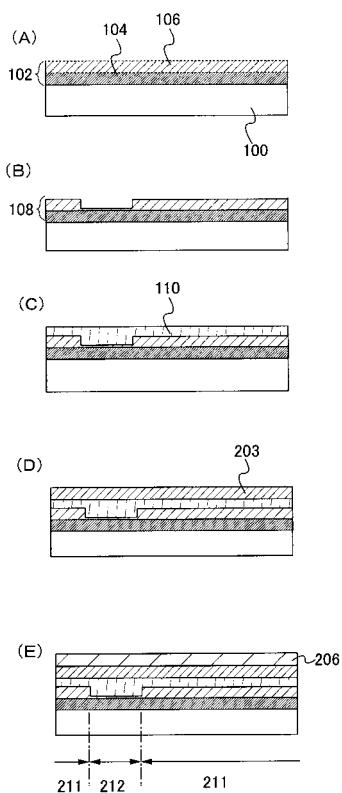

まず、第1の基板100上に剥離層102を形成する(図1(A-1)を参照)。剥離層102は単層であってもよいし、積層に形成しても良い。本実施の形態では、剥離層102は積層構造を有し、第1の剥離層104上に第2の剥離層106が形成されている。

#### 【0026】

剥離層102は、スパッタリング法を用いて、タンクスチタン、モリブデン、チタン、タン

50

タル、ニオブ、ニッケル、コバルト、ジルコニウム、亜鉛、ルテニウム、ロジウム、パラジウム、オスミウム、イリジウム及び珪素から選択された元素、又はこれらの元素を主成分とする合金材料、又はこれらの元素を主成分とする化合物材料からなる層を、単層で、又は複数の層を積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

【0027】

剥離層102が単層構造の場合には、好ましくは、タングステン、モリブデン、又はタングステンとモリブデンの混合物を含む層を形成する。または、タングステンの酸化物若しくはタングステンの酸化窒化物を含む層、モリブデンの酸化物若しくはタングステンの酸化窒化物を含む層、又はタングステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タングステンとモリブデンの混合物とは、例えば、タングステンとモリブデンの合金に相当する。

10

【0028】

剥離層102が積層構造の場合には、好ましくは、1層目として金属層を形成し、2層目として金属酸化物層を形成する。代表的には、1層目として、タングステン、モリブデン、又はタングステンとモリブデンの混合物を含む層を形成し、2層目として、これらの酸化物、窒化物、酸化窒化物又は窒化酸化物を含む層を形成する。

【0029】

剥離層102として、1層目に金属層、2層目に金属酸化物層の積層構造を形成する場合には、金属層としてタングステンを含む層を形成し、その上に金属酸化物からなる絶縁層を形成すると、タングステンを含む層と絶縁層との界面に金属酸化物層としてタングステンの酸化物を含む層が形成されるため、これを活用してもよい。さらには、金属層の表面に対して、熱酸化処理、酸素プラズマ処理、又はオゾン水等の酸化力の強い溶液による処理等を行って金属酸化物層を形成してもよい。例えば、タングステン上に酸化シリコンを成膜して、タングステンと酸化シリコンとの間にタングステン酸化物を形成しても良い。しかし、タングステンの酸化物と酸化シリコンとは密着し難く、剥離には有利であるが、作製工程において意図せず剥離してしまう可能性がある。一方、タングステンと酸化シリコンとの間にタングステン窒化物を形成すると、作製工程における意図しない剥離を防止することはできるが、剥離し難くなるという問題がある。そのため、剥離層と窒化シリコンとの間に設ける層は、実施者の意思に応じて適宜設定するとよい。

20

【0030】

更には、剥離層102として、1層目に金属層、2層目に金属窒化物層又は金属酸化窒化物層を形成してもよい。代表的には、1層目にタングステンを含む層を形成し、2層目に、窒化タングステン層又は酸化窒化タングステン層を形成すればよい。

【0031】

剥離層102の膜厚は、本実施の形態では、第1の剥離層104としてタングステン膜を30nmで、第2の剥離層106として酸化シリコン膜を300nmで形成する。第1の剥離層104及び第2の剥離層106は、スパッタリング法又はCVD法等により形成することができる。第1の剥離層104及び第2の剥離層106は、スパッタリング法により形成することが好ましい。

30

【0032】

なお、第1の剥離層104としてタングステン膜を形成し、第2の剥離層106としてCVD法により酸化シリコンを形成する場合には、第1の剥離層104であるタングステン膜を成膜した直後にN<sub>2</sub>Oプラズマ処理を行うことが好ましい。

40

【0033】

次に、剥離層102の表面に段差を設ける。具体的には、所望の半導体素子の下のSiO<sub>2</sub>膜の膜厚を保持し、前記所望の半導体素子が形成されていない領域はSiO<sub>2</sub>膜の膜厚を薄くする。パターンの形成にはレジストマスクを用いる。所望のパターンを有するレジストマスクが形成された状態で、第2の剥離層106すなわち酸化シリコン膜をエッチングする。このエッチングの方法は、ドライエッチング又はウェットエッチングのいずれで

50

も良い。また酸化シリコン膜は、後に可撓性基板等に剥離転置可能な膜厚の範囲で薄くする。ここでは膜厚 200 nmまでエッティングする。

【0034】

次に、剥離層 108 上に、絶縁膜である第1の接合層 110 を形成する。第1の接合層 110 は表面が親水性を有する材料により設ける。第1の接合層 110 としては、酸化シリコン膜が適している。特にシランガス、ジシランガス、トリシランガス又は有機シランガス等のシラン系ガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。シランガスを用いる場合、二酸化窒素又は一酸化二窒素との混合ガスを用いることが好適である。有機シランガスとしては、珪酸エチル (TEOS: 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、トリメチルシラン (TMS:  $(\text{CH}_3)_3\text{SiH}$ )、テトラメチルシクロテトラシリコサン (TMCTS)、オクタメチルシクロテトラシリコサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン ( $\text{SiH}(\text{OC}_2\text{H}_5)_3$ ) 又はトリスジメチルアミノシラン ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) 等のシリコン含有化合物を用いることができる。化学気相成長法としては、プラズマ CVD、熱 CVD 又は光 CVD を用いればよい。

【0035】

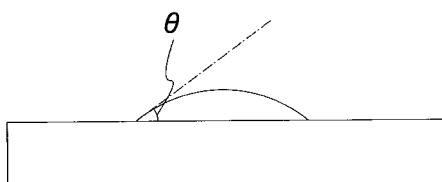

なお、本明細書中において、親水性とは、固体表面における水の接触角により定義される。接触角とは、滴下したドットの淵における、形成面と液滴の接線がなす角度のことを指す(図12を参照)。固体表面に水を滴下した際の接触角が0°以上90°以下であるときには該固体表面は親水性であるとし、90°以上180°以下であるときには該固体表面は撥水性であるとする。

【0036】

上記の、親水性表面を有する第1の接合層 110 は 50 nm 以上 500 nm 以下の厚さで設けるとよい。前記厚さは、剥離層 102 の表面の段差を十分埋める大きさが必要であり、すなわち段差に応じた膜厚とする。

【0037】

前記第1の接合層 110 は、凹凸を有している。表面に凹凸を有すると、後の工程にて二つの基板上の接合層を接合する際に、接合層間の接触面積が小さくなり、十分な接合強度を確保することが困難である。そのため、第1の接合層 110 を平坦化する。

【0038】

第1の接合層 110 の平坦化は、剥離層の全面を均一に平坦化できる方法により行うとよい。このような工程として、例えば、CMP や逆スパッタリング法が挙げられる。但し、これに限定されず、物理的エッティング方法又は化学的エッティング方法等、平坦性を高めることのできる処理であれば、処理方法は特に問わない。

【0039】

上記第1の接合層 110 の平坦化後の膜厚は、所望する素子の形成される領域では、5 nm 以上あることが好ましい。膜厚に上限は無いものの、スループットを考慮し、好適には 100 nm 以下とする。

【0040】

上記のように第1の基板 100 上に薄膜を形成する一方で、半導体基板 200 にも処理を行う。

【0041】

半導体基板 200 には、まず表面から一定の深さの位置に、損傷層 202 を形成する。損傷層 202 は、清浄化された半導体基板 200 の表面から、電界で加速されたイオンを所定の深さに注入することで形成される。イオンの注入では、第1の基板 100 上に形成する半導体層(以下、LTS层という。)の厚さを考慮して加速電圧等を調整する。LTS 層の厚さは、5 nm 以上 500 nm 以下、好ましくは 10 nm 以上 200 nm 以下である。損傷層 202 の形成には、水素、不活性ガス又はハロゲンを用いる。不活性ガスとしてはヘリウムが挙げられ、ハロゲンとしてはフッ素が挙げられる。

【0042】

10

20

30

40

50

損傷層 202 の形成ではイオンを高ドーズ条件にて注入するため、半導体基板 200 の表面が粗くなる場合がある。この、表面の荒れを防ぐためには、イオン注入される表面に、保護膜を設けておくとよい。この保護膜は、酸化シリコン膜、窒化シリコン膜又は窒化酸化シリコン膜等により 0.5 nm 以上 200 nm 以下の厚さで設ければよい。

#### 【 0043 】

なお、ここでイオン注入時の高ドーズ条件とは、本発明を実施する者が目的に応じて適宜設定すればよい。このドーズ条件により、損傷層 202 が半導体基板表面からどれだけの深さの位置に形成されるかが決定される。例えば、加速電圧を 60 kV、ドーズ量を  $2.0 \times 10 \text{ cm}^{-2}$  とすると、半導体基板表面から約 150 nm の深さの位置に損傷層 202 が形成される。

10

#### 【 0044 】

次に、半導体基板表面に、下地絶縁膜 203 を形成する。下地絶縁膜 203 としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜 ( $\text{SiO}_x\text{N}_y$ ) 等の絶縁膜を用いる。代表的な一例は下地絶縁膜 203 として 2 層構造から成り、 $\text{SiH}_4$ 、及び  $\text{N}_2\text{O}$  を反応ガスとして成膜される酸化窒化シリコン膜を 100 ~ 150 nm、 $\text{SiH}_4$ 、 $\text{NH}_3$ 、及び  $\text{N}_2\text{O}$  を反応ガスとして成膜される窒化酸化シリコン膜を 50 ~ 100 nm、の厚さに積層形成する構造が採用される。また、下地絶縁膜 203 の一層として膜厚 10 nm 以下の窒化シリコン膜 ( $\text{SiN}$  膜)、或いは窒化酸化シリコン膜 ( $\text{SiN}_x\text{O}_y$  膜 ( $X > Y$ )) を用いることが好ましい。また、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、を順次積層した 3 層構造を用いてもよい。下地絶縁膜 203 は基板から TFT にナトリウム等の可動イオンが侵入することを防ぐためのプロッキング層として機能する。また、下地絶縁膜 203 はバッファ層として機能する。

20

#### 【 0045 】

次に、第 1 の基板 100 と接合する面に、表面の平坦性が高い絶縁膜である第 2 の接合層 210 を形成する (図 1 (B-2) を参照)。第 2 の接合層 210 は、酸化シリコン膜により形成することが好ましい。酸化シリコン膜としては上述のように有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましく、シランガス、ジシランガス又はトリシランガス等シラン系ガスを用いて、化学気相成長法により作製される酸化シリコン膜を適用してもよい。化学気相成長法による成膜では、半導体基板 200 に形成した損傷層 202 から脱ガスが起こらない温度 (例えば、350 以下) とする。また、単結晶若しくは多結晶半導体基板から LSS 層を剥離する熱処理には、成膜温度よりも高い熱処理温度が適用される。

30

#### 【 0046 】

なお、化学気相成長法としては、プラズマ CVD 法、熱 CVD 法又は光 CVD 法を用いれば良い。特に TEOS と  $\text{O}_2$  によりプラズマ CVD を用いて、又は  $\text{SiH}_4$  と  $\text{NO}_2$  により熱 CVD 法を用いて形成すると、接合層に適した平坦な酸化シリコン膜を低温 (350 以下) で形成する事ができるため、好ましい。

40

#### 【 0047 】

また、第 2 の接合層 210 となる酸化シリコン膜は、オゾン水と過酸化水素とを含む薬液で形成してもよいし、オゾン水で形成しても良い。その場合には、膜厚は 0.5 nm 以上 5 nm 以下で良い。また、接合層は水素又はフッ素で終端した半導体表面であってもよい。

#### 【 0048 】

なお、第 1 の接合層 110 と半導体基板 200 との接合強度に問題がなければ、第 2 の接合層 210 を形成することなく、第 1 の接合層 110 と半導体基板 200 とを直接接合しても良い。

#### 【 0049 】

同様に、剥離層 102 と第 2 の接合層 210 との接合強度に問題がなければ、第 1 の接合層 110 を形成することなく、剥離層 102 と第 2 の接合層 210 とを直接接合しても良

50

い。

#### 【0050】

つまり、接合強度に問題がなければ、必ずしも第1の基板100上と半導体基板200上の双方に接合層を形成しなくともよい。接合層を形成しないことで、半導体装置の作製工程において、スループットを向上させることができる。

#### 【0051】

次に、第1の基板100上に形成された第1の接合層110と、半導体基板200上に形成された第2の接合層210とを密接させて接合する(図1(D)を参照)。これにより、接合形成層112が形成される。第1の接合層110と第2の接合層210とを密接させることで、室温でも接合することが可能である。より強固に接合するためには、第1の基板100と半導体基板200を押圧すれば良い。更には、熱処理を加えることが好ましい。加圧した状態で熱処理をしても良い。加圧した状態で熱処理を行うことで、第1の接合層110と第2の接合層210との接合がより強固になるため、接合層間の剥離を低減することができ、歩留まりが向上する。また、得られる半導体装置の信頼性が向上する。

10

#### 【0052】

接合を形成する面が異種材料である場合、低温で接合する際には接合を形成する面を清浄化する。清浄化した、第1の接合層110と第2の接合層210とを密接させると、表面間引力により接合形成層112が形成される。清浄化した表面を親水性表面とするためにには、多数の水酸基を付着させればよい。例えば、第1の接合層110又は第2の接合層210の表面を、酸素プラズマ処理若しくはオゾン処理することで、これらの表面を親水性にすることができる。このように表面を親水性にする処理を加えると、表面の水酸基が作用して水素結合により強固な接合が形成される。

20

#### 【0053】

また、良好な接合を形成するために、接合を形成する面を活性化しても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合、アルゴン等の、不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを照射することができる。イオンビームの照射により、第1の接合層110又は第2の接合層210の表面に未結合手が露出し、非常に活性な表面が形成される。または、プラズマ照射若しくはラジカル処理を行ってもよい。接合を形成する面に対してこのような表面処理を行うことにより、200乃至400程度の温度で、第1の接合層110と第2の接合層210が異種材料であっても、接合形成層112を容易に形成することができる。表面を活性化して接合する方法は、当該表面を高度に清浄化しておくことが要求されるので、真空中で行うことが好ましい。また、更に好ましくは高真空中で行う。

30

#### 【0054】

接合形成層112の接合強度を高めるためには、接合後に加熱処理又は加圧処理を行うことが好ましい。接合形成層112が室温にて貼り合わせられた場合には、接合後に熱処理を行うことが、特に好ましい。加熱処理又は加圧処理を行うことで、接合を形成する面において接合に寄与する主な結合を、水素結合から共有結合に変換することができ、接合強度が向上する。加熱処理の温度は、第1の基板100の耐熱温度以下で行う。加圧処理においては、接合面に対して垂直な方向に圧力を加える。ここで加える圧力は、第1の基板100と半導体基板200の機械的強度を考慮して決定する。

40

#### 【0055】

次に、半導体基板200が貼り合わせられた第1の基板100に熱処理を行い、損傷層202内の任意の位置を劈開面として、半導体基板200を第1の基板100から剥離する。剥離には物理的手段を用いればよい。熱処理の温度は第1の接合層110及び第2の接合層210の成膜温度以上、第1の基板100の耐熱温度以下で行うことが好ましい。例えば、400乃至600の熱処理を行うことにより、損傷層202に形成された微小さな空洞の体積変化が起り、損傷層202に沿って劈開することが可能となる。接合形成層112は第1の基板100と接合しているので、第1の基板100上には半導体基板2

50

00と同じ結晶性のLTSS層が残存することとなる。

【0056】

なお、物理的手段とは、力学的手段または機械的手段を指し、何らかの力学的エネルギー（機械的エネルギー）を変化させる手段を指しており、その手段は、代表的には機械的な力を加えること（例えば、人間の手や把治具で引き剥がす処理や、ローラーを回転させながら分離する処理）である。

【0057】

LTSS層116は、上記剥離工程後にCMP等を用いて、平坦化及び薄膜化されることが好ましい。例えば、単結晶半導体基板の所定の深さに、水素、ヘリウムに代表される不活性ガス、又はフッ素に代表されるハロゲンのイオンを注入し、その後熱処理を行って表層の単結晶シリコン層を剥離するイオン注入剥離法で形成することができる。また、ポーラスシリコン上に単結晶シリコンをエピタキシャル成長させ、ポーラスシリコン層をウォータージェットで劈開して剥離する方法を適用しても良い。LTSS層116の厚さは5nm乃至500nm、好ましくは10nm乃至200nmである。なお、本発明はこれに限定されず、LTSS層の平坦化及び薄膜化は逆スパッタリング法にて行ってもよい。更には、CMPと逆スパッタリング法を併用して平坦化及び薄膜化を行ってもよい。

10

【0058】

また、損傷層202を劈開面として半導体基板200を剥離する前に、剥離を容易に行うためのきっかけを形成してもよい。さらには、半導体基板200を剥離する際、第1の基板100又は半導体基板200の少なくとも一方の表面に光又は熱により剥離可能な粘着シートを設けて、第1の基板100及び半導体基板200のいずれかを固定し、他方を引き剥がすと、剥離が更に容易になる。このとき、第1の基板100又は半導体基板200の他方に支持部材を設けることで、容易に引き剥がすことができる。

20

【0059】

なお、図示していないが、LTSS層116と接合形成層114の間にバリア層を設けても良い。バリア層は、第1の基板100として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属のような可動イオン不純物が拡散してLTSS層116が汚染されることを防止できる材質の膜を形成する。また、第1の剥離層104又は第2の剥離層106からの不純物の拡散を防止することもできる。バリア層として、例えば、窒素含有絶縁層を用いることができる。窒素含有絶縁層は窒化シリコン膜、窒化酸化シリコン膜若しくは酸化窒化シリコン膜を単層で、又は積層して形成することができる。例えば、LTSS層116側から酸化窒化シリコン膜と、窒化酸化シリコン膜と、を積層して形成することで、窒素含有絶縁膜によりバリア層を設けることができる。

30

【0060】

なお、ここで酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が55～65原子%、窒素が1～20原子%、Siが25～35原子%、水素が0.1～10原子%の範囲で含まれるものと定義する。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15～30原子%、窒素が20～35原子%、Siが25～35原子%、水素が15～25原子%の範囲で含まれるものと定義する。

40

【0061】

なお、本発明は上記の説明に限定されない。第2の接合層210が不要な場合には特に形成しなくても良い（図3を参照）。なお、接合層が不要な場合とは、接合層を形成しなくとも、貼り合わせ面と被貼り合わせ面が良好に貼り合わせられる場合をいう。第1の接合層110及び第2の接合層210の一方のみを形成し、又は双方を形成しないことで、工程が削減され、スループットが向上する。

【0062】

以上説明したように、本発明により素子領域211と、その間すなわち素子間領域212との間に段差が設けられた剥離層により、可撓性基板への転写時の歩留まりを向上させることができる（図1～図4参照）。

50

**【 0 0 6 3 】**

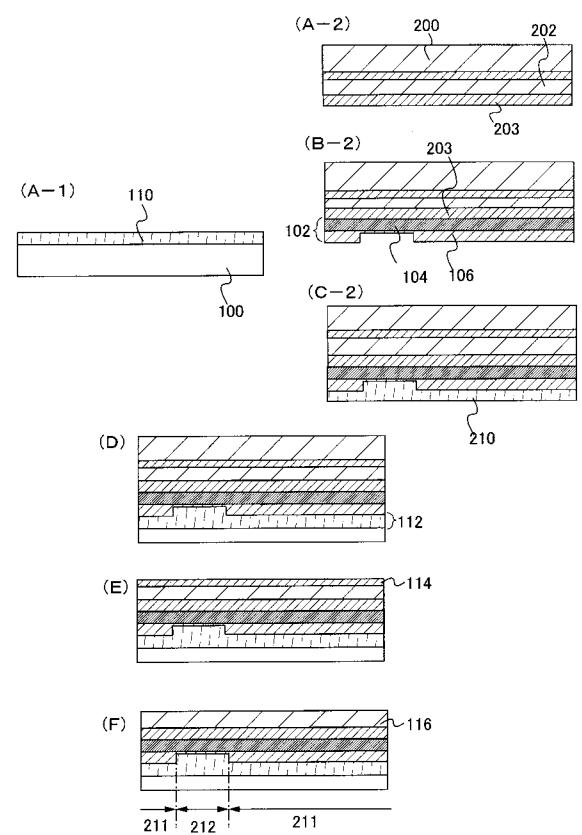

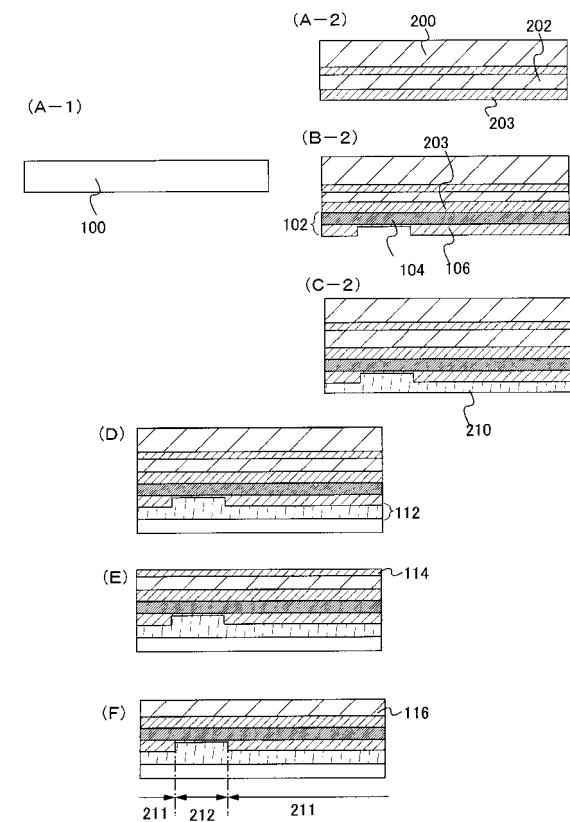

(実施の形態 2 )

本発明は、実施の形態 1 にて説明した形態に限定されず、例えば、剥離層を半導体基板上に形成しても良い。このような形態について、以下に説明する。なお、重複する点については、説明を省略する。

**【 0 0 6 4 】**

図 4 は、剥離層を半導体基板上に形成する形態の一例を示す。

**【 0 0 6 5 】**

まず、半導体基板 2 0 0 に実施の形態 1 と同様にドープを行って損傷層 2 0 2 を形成する (図 4 ( A - 2 ) を参照)。

10

**【 0 0 6 6 】**

次に、損傷層 2 0 2 が形成された半導体基板 2 0 0 上に、実施の形態 1 と同様に剥離層 1 0 2 を形成する (図 4 ( B - 2 ) を参照)。

**【 0 0 6 7 】**

次に、剥離層 1 0 2 に段差を設け、さらに絶縁膜を形成する。

**【 0 0 6 8 】**

次に、絶縁膜を平坦化し、第 2 の接合層 2 1 0 を形成する。なお、平坦化は C M P 法により行なうことが好ましい (図 4 ( C - 2 ) を参照)。

20

**【 0 0 6 9 】**

半導体基板 2 0 0 に処理を行う一方で、第 1 の基板 1 0 0 上に実施の形態 1 と同様に、表面の平坦性が高い絶縁膜である第 1 の接合層 1 1 0 を形成する (図 4 ( A - 1 ) を参照)。

**【 0 0 7 0 】**

以上のように処理を行なった第 1 の基板 1 0 0 と、半導体基板 2 0 0 と、を貼り合わせる。つまり、実施の形態 1 と同様に、第 1 の接合層 1 1 0 と第 2 の接合層 2 1 0 とを接合させ、接合形成層 1 1 2 を形成することができる (図 4 ( D ) を参照)。

**【 0 0 7 1 】**

次に、半導体基板 2 0 0 を損傷層で剥離することで、第 1 の基板上に半導体層を形成する (図 4 ( E ) を参照)。更には、半導体層を平坦化することで、L T S S 層 1 1 6 を形成する。

30

**【 0 0 7 2 】**

なお、本発明は上記の説明に限定されない。第 1 の接合層 1 1 0 が不要な場合には特に形成しなくても良い (図 5 を参照)。なお、接合層が不要な場合とは、接合層を形成しなくとも、貼り合わせ面と被貼り合わせ面が良好に貼り合わせられる場合をいう。第 1 の接合層 1 1 0 及び第 2 の接合層 2 1 0 の一方のみを形成し、又は双方を形成しないことで、工程が削減され、スループットが向上する。

**【 0 0 7 3 】**

尚、剥離層を第 1 の剥離層、第 2 の剥離層の順で形成する 2 層構造とし、第 1 の剥離層と、第 2 の剥離層との間で剥離する構造の場合、実施の形態 1 では、剥離層 2 の一部が残り、実施の形態 2 では、剥離層 1 の一部が残ることとなる。所望の構造が形成されるように、いずれかを選択することができる。

40

(実施の形態 3 )

本発明は、実施の形態 1 および実施の形態 2 にて説明した形態にて好適に用いられるが、接合層および半導体基板を用いず、第 1 の基板 1 0 0 上に直接所望の半導体素子を形成しても良い。このような形態について、図 5 を用い以下に説明する。なお、重複する点については、説明を省略する。

**【 0 0 7 4 】**

まず、第 1 の基板 1 0 0 上に実施の形態 1 と同様に、剥離層 1 0 2 を形成する。

**【 0 0 7 5 】**

次に、剥離層 1 0 2 に段差を設け、剥離層 1 0 8 を形成し、さらに絶縁膜 1 1 0 を形成す

50

る。

【0076】

次に、絶縁膜を平坦化し、さらに下地絶縁膜203を形成する。

【0077】

下地絶縁膜203は、酸化シリコン、窒化シリコン、窒化酸化シリコン、酸化窒化シリコン等の絶縁材料の単層膜または積層膜で形成することができる。これらの絶縁膜はCVD法、スパッタ法で形成することができる。下地絶縁膜203を形成することで、半導体膜の基板側の界面準位密度を低減すること、基板からアルカリ金属などの汚染物質が半導体膜に侵入することを防ぐ、などの効果がある。

【0078】

その上に、半導体膜206を形成する。半導体膜206は、非単結晶半導体膜であり、多結晶半導体で形成されたものが好ましい。半導体材料としては、シリコンが好ましく、その他、シリコンゲルマニウムおよびゲルマニウムを用いることができる。これらは公知の手段（スパッタ法、LPCVD法、またはプラズマCVD法等）で成膜することによって得る。

10

【0079】

以上の工程により、実施の形態1あるいは実施の形態2のように、必要な耐熱性を有する基板上に剥離層を形成し、該剥離層上に半導体層を形成することができる。本実施の形態で形成される半導体層は非単結晶であり、実施の形態1あるいは実施の形態2の工程にて形成されるものより、若干半導体層の結晶性は低くなるものの、より少ない工程を経るためスループットの向上を見込むことができる。

20

【0080】

（実施の形態4）

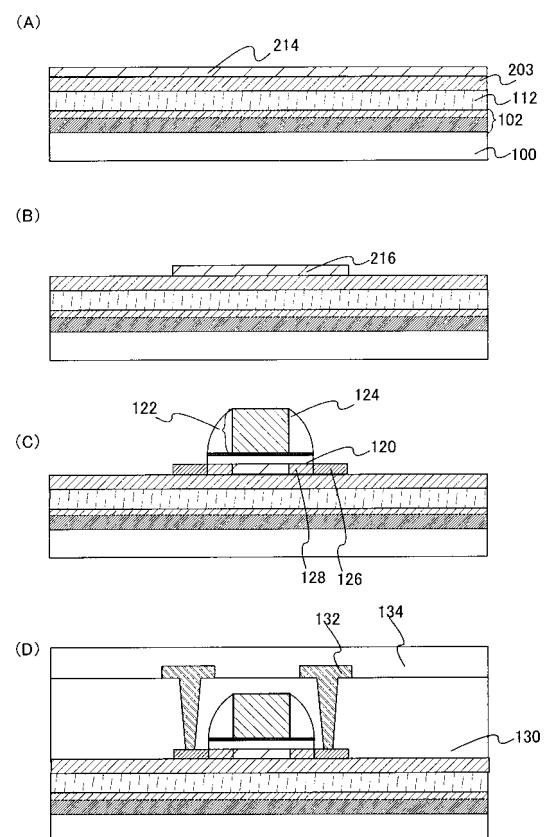

実施の形態1、又は実施の形態2、実施の形態3にて説明したように、SOI基板を作製し、該SOI基板を用いて半導体装置を作製することができる。本実施の形態では、本発明を適用した薄膜集積回路の作製方法について、図面を参照してより詳細に説明する。尚、本実施の形態では、LTSS層及び非単結晶半導体膜は、半導体膜と称する。

【0081】

図7(A)は、実施の形態1、又は実施の形態2、実施の形態3にて説明したように作製したSOI基板を示す。但し、素子領域211部分のみを表している。まず、SOI基板の半導体膜214を所望の形状となるようパターンを形成する（図7(B)を参照）。パターンの形成にはレジストマスクを用いる。所望のパターンを有するレジストマスクが形成された状態で、半導体膜214をエッティングし、半導体膜216を形成する。このときのエッティング条件は、LTSS層に対するエッティングレートが高く、接合形成層112に対するエッティングレートの低い条件とすればよく、ドライエッティング又はウエットエッティングのいずれかを選択する。

30

【0082】

次に、ゲート絶縁膜120、ゲート電極層122及びサイドウォール124を順次形成し、半導体膜216にソース領域又はドレイン領域126及びLDD領域128を形成する（図7(C)を参照）。

40

【0083】

ゲート絶縁膜120は、酸化シリコン、窒化シリコン、酸化窒化シリコン又は窒化酸化シリコン等により形成する。形成には、CVD法、スパッタリング法、プラズマCVD法等を用いればよい。膜厚は、5nm以上200nm以下とする。なお、ゲート絶縁膜120は、図示する構造に限定されず、全面に形成されていても良い。

【0084】

ゲート電極層122は、CVD法、スパッタリング法又は液滴吐出法等を用いて形成することができる。ゲート電極層122は、タンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅から選ばれた元素又は前記元素を主成分とする合金材料若しくは化合物材料で形成すればよい。ゲート電極層122にアルミニウムを使用する際には、タンタル

50

を添加して合金化した A 1 - T a 合金を用いるとヒロックが抑制される。また、ネオジムを添加して合金化した A 1 - N d 合金を用いると、ヒロックが抑制されるだけでなく、抵抗の低い配線を形成することができる。そのため、A 1 - T a 合金又は A 1 - N d 合金を用いることが好ましい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体膜や A g P d C u 合金を用いてもよい。また、単層でも積層でもよい。例えば、窒化チタン膜とモリブデン膜から構成される 2 層の積層構造又は膜厚 5 0 n m のタンゲステン膜と膜厚 5 0 0 n m のアルミニウムとシリコンの合金膜と膜厚 3 0 n m の窒化チタン膜を積層した 3 層の積層構造としてもよい。また、3 層の積層構造とする場合、第 1 の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第 2 の導電膜のアルミニウムとシリコンの合金膜に代えてアルミニウムとチタンの合金膜を用いてもよいし、第 3 の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。ゲート電極層 1 2 2 は単層で形成してもよいし、積層で形成してもよい。例えば、主成分がモリブデンである膜により形成すればよい。

#### 【 0 0 8 5 】

ゲート電極層 1 2 2 の側面にはサイドウォール 1 2 4 を設ける。サイドウォール 1 2 4 は、絶縁膜を全面に形成し、選択的にエッチングすることにより行う。なお、絶縁膜種はゲート絶縁膜 1 2 0 と同様である。

#### 【 0 0 8 6 】

ソース領域又はドレイン領域 1 2 6 、及び L D D 領域 1 2 8 は、一導電型の不純物元素を添加することにより形成する。ソース領域又はドレイン領域 1 2 6 は一導電型の不純物が高濃度に導入された高濃度不純物領域であり、L D D 領域 1 2 8 は一導電型の不純物が低濃度に導入された高濃度不純物領域である。濃度の異なる領域を作り分けるためには、低濃度不純物領域を、絶縁膜を介したドープにより形成し、高濃度不純物領域をペアドープにより形成すればよい。または、低濃度不純物領域及び高濃度不純物領域の双方に低濃度に不純物を導入し、その後、高濃度不純物領域にのみ不純物を高濃度に導入してもよい。なお、L D D 領域とは半導体層が多結晶シリコン膜により形成されている T F T において、信頼性の向上を目的として形成される領域である。半導体層が多結晶シリコンである T F T においてオフ電流を抑えることは重要であり、特に、画素回路などのアナログスイッチとして用いる場合には十分に低いオフ電流が要求される。しかし、ドレイン接合部の逆バイアス強電界により、オフ時にも欠陥を介するリーク電流が存在する。L D D 領域により、ドレイン端近傍の電界を緩和するため、オフ電流を低減させることができる。また、ドレイン接合部の逆バイアス電界をチャネル形成領域と L D D 領域の接合部と、L D D 領域とドレイン領域の接合部とに分散させることができ、電界が緩和されるため、リーク電流が低減される。その後アニールを行うことで、不純物の活性化を行う。

#### 【 0 0 8 7 】

次に、絶縁膜 1 3 0 を形成し、所望の位置に開口部を形成する。絶縁膜 1 3 0 に設けられた開口部を介して、半導体膜 2 1 6 のソース領域及びドレイン領域に接続されるように、ソース電極及びドレイン電極を形成する。その後、絶縁膜 1 3 4 を形成する（図 7 ( D ) を参照）。なお、絶縁膜 1 3 4 は必要のない場合には設けなくても良い。

#### 【 0 0 8 8 】

絶縁膜 1 3 0 を選択的に形成する。絶縁膜 1 3 0 はポリイミドやアクリル等に代表される有機材料からなる膜を、スピニコート法等により形成すればよい。パターンの形成に際しては、ソース領域及びドレイン領域 1 2 6 を露出するように開口部を形成する。なお、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、又は窒化酸化シリコン膜のような無機材料からなる膜上に有機材料からなる膜を形成してもよい。または、これらの無機材料のみで形成してもよい。

#### 【 0 0 8 9 】

次に、絶縁膜 1 3 4 を第 2 の基板 1 3 6 に固着する（図 8 ( E ) を参照）。第 2 の基板はすなわち可撓性基板が有効であり、この材料としては、P E T ( ポリエチレンテレフタレート ) 、P E N ( ポリエチレンナフタレート ) 、P E S ( ポリエーテルスルホン ) 、ポリ

10

20

30

40

50

プロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、ポリフタールアミド等からなるプラスチック基板または纖維質の材料からなる紙がある。

【0090】

また、第2の基板136としては、プリプレグを用いることで、後に作製されるSOI基板や半導体装置の点圧、線圧による破壊を防ぐことが可能である。プリプレグの代表例としては、ポリビニルアルコール系纖維、ポリエステル系纖維、ポリアミド系纖維、ポリエチレン系纖維、アラミド系纖維、ポリパラフェニレンベンゾビスオキサゾール纖維、ガラス纖維、または炭素纖維等の纖維体に、エポキシ樹脂、不飽和ポリエステル樹脂、ポリイミド樹脂又はフッ素樹脂等のマトリックス樹脂を有機溶剤で希釈したワニスを含浸させた後、乾燥して有機溶剤を揮発させてマトリックス樹脂を半硬化させたものである。

10

【0091】

また、第2の基板136としては、アルミニシリケートガラス、アルミニホウケイ酸ガラス又はバリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板を用いることができる。

【0092】

次に、剥離層102をきっかけとして、第1の基板100から薄膜集積回路を剥離する。剥離は、加熱処理又はウェットエッチング等を用いればよい。

【0093】

この剥離が問題なく行えればよいが、工程の熱処理条件によっては、工程中のピーリング等を避けるため、剥離層をある程度強固にする必要がある。このためやむなく、剥離工程時に、基板面内のいずれかに剥離不良、クラックなどの欠陥が残ってしまうことがある。この条件について、図8(F)で説明する。

20

【0094】

図8(F)では、素子領域210と素子間領域212との境界付近を、剥離層の厚さの違いで説明している。剥離層の薄い素子間領域212は、素子領域210に比べて、剥離しにくくなっている。そのため、素子間領域212では耐熱性基板側に剥離層残渣218が残る、あるいは第2の基板側に転置された層にクラック220が発生する可能性がある。しかしながら素子領域210にはこれを避けることが出来る。そのため、素子の歩留まりを上げることができる。

30

【0095】

以上のように、半導体装置に設けられた薄膜集積回路が有するトランジスタを形成することができるが、本実施の形態は一例に過ぎない。即ち、本発明は本実施の形態に限定されず、実施の形態1又は実施の形態2にて説明したSOI基板を用いて作製する、如何なるトランジスタにも適用することができる。

【0096】

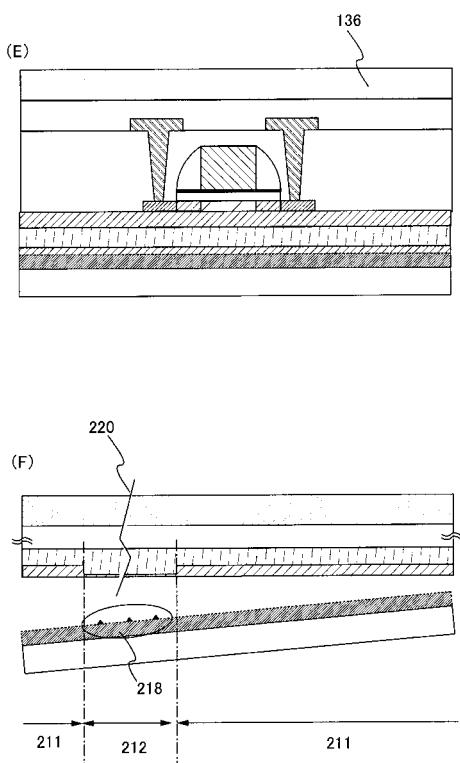

(実施の形態5)

次に、実施の形態1、又は実施の形態2、実施の形態3を適用して作製したSOI基板を用いて作製した半導体装置の一例として、マイクロプロセッサ300を図9に示す。このマイクロプロセッサ300は、演算回路301(Arithmetic logic unit。ALUともいう。)、演算回路制御部302(ALU Controller)、命令解析部303(Instruction Decoder)、割り込み制御部304(Interrupt Controller)、タイミング制御部305(Timing Controller)、レジスタ306(Register)、レジスタ制御部307(Register Controller)、バスインターフェース308(Bus I/F)、ROM309(Read Only Memory)、及びROMインターフェース310(ROM I/F)を有する。

40

【0097】

バスインターフェース308を介してマイクロプロセッサ300に入力された命令は、命令解析部303に入力され、デコードされた後、演算回路制御部302、割り込み制御部

50

304、レジスタ制御部307及びタイミング制御部305に入力される。演算回路制御部302、割り込み制御部304、レジスタ制御部307及びタイミング制御部305は、デコードされた命令に基づき各種制御を行う。具体的に、演算回路制御部302は、演算回路301の動作を制御するための信号を生成する。また、割り込み制御部304は、マイクロプロセッサ300のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部307は、レジスタ306のアドレスを生成し、マイクロプロセッサ300の状態に応じてレジスタ306の読み出しや書き込みを行う。タイミング制御部305は、演算回路301、演算回路制御部302、命令解析部303、割り込み制御部304、レジスタ制御部307の動作のタイミングを制御する信号を生成する。例えば、タイミング制御部305は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記の各種回路に供給する。なお、図9に示すマイクロプロセッサ300は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。10

#### 【0098】

このようなマイクロプロセッサ300は、可撓性を有する基板上に接合される工程の際、素子内へのクラックが抑えられるので、歩留まりの向上を図ることができる。

#### 【0099】

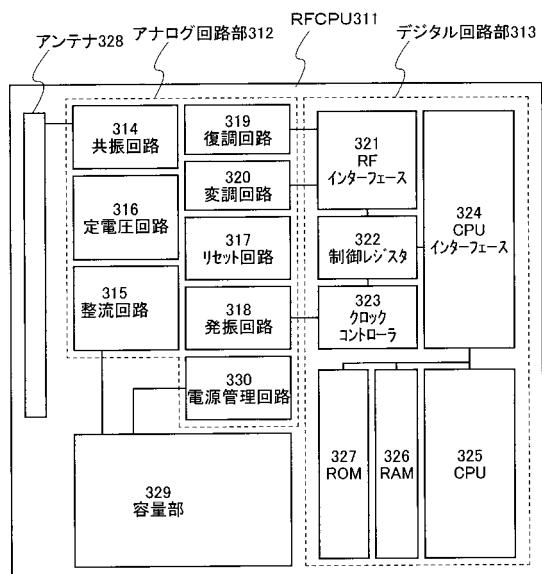

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について図10を参照して説明する。図10は無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「RFCPU」という）の一例を示す。RFCPU311は、アナログ回路部312及びデジタル回路部313を有している。アナログ回路部312とは、共振容量を有する共振回路314、整流回路315、定電圧回路316、リセット回路317、発振回路318、復調回路319と、変調回路320を有している。デジタル回路部313は、RFインターフェース321、制御レジスタ322、クロックコントローラ323、CPUインターフェース324、CPU325、RAM326及びROM327を有している。20

#### 【0100】

このような構成のRFCPU311の動作は概略以下の通りである。アンテナ328が受信した信号は共振回路314により誘導起電力を生じさせる。誘導起電力は、整流回路315を経て容量部329に充電される。この容量部329はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部329はRFCPU311と一体形成されている必要はなく、別部品としてRFCPU311を構成する絶縁表面を有する基板に取り付けられていれば良い。30

#### 【0101】

リセット回路317は、デジタル回路部313をリセットし、初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路318は、定電圧回路316により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路319は、例えば振幅変調（ASK）方式の受信信号の振幅の変動を二値化する。変調回路320は、送信データを振幅変調（ASK）方式の送信信号の振幅の変動により送信する。変調回路320は、共振回路314の共振点を変化させることで通信信号の振幅を変化させていく。クロックコントローラ323は、電源電圧又はCPU325における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成する。電源電圧の監視は電源管理回路330が行う。40

#### 【0102】

アンテナ328からRFCPU311に入力された信号は復調回路319で復調された後、RFインターフェース321で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ322に格納される。制御コマンドには、ROM327に記憶されているデータの読み出し、RAM326へのデータの書き込み、CPU325への演算命令など

が含まれている。CPU325は、CPUインターフェース324を介してROM327、RAM326及び制御レジスタ322にアクセスする。CPUインターフェース324は、CPU325が要求するアドレスより、ROM327、RAM326及び制御レジスタ322のいずれかに対するアクセス信号を生成する機能を有する。

【0103】

CPU325の演算方式は、ROM327にOS(オペレーティングシステム)を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、プログラムを用いて残りの演算をCPU325が実行する方式を適用することができる。10

【0104】

本発明を適用したSOI基板を用いた半導体装置を、可撓性を有する基板上に接合される工程の際、素子内へのクラックが抑えられるので、歩留まりの向上を図ることができる。

【0105】

以上のように、本発明を適用したSOI基板を用いてマイクロプロセッサ又はRFCPUを作製することができる。しかし、本実施の形態は一例に過ぎない。即ち、本発明は本実施の形態に限定されず、実施の形態1又は実施の形態2にて説明したSOI基板を用いて作製する、如何なる半導体装置にも適用することができる。

【0106】

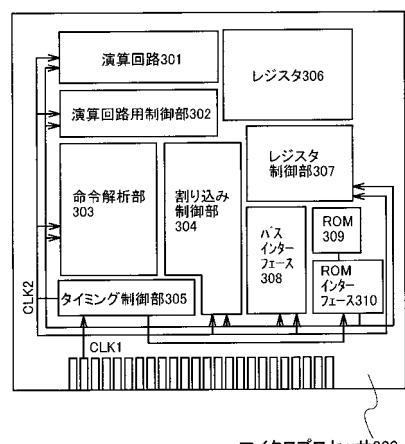

(実施の形態6)

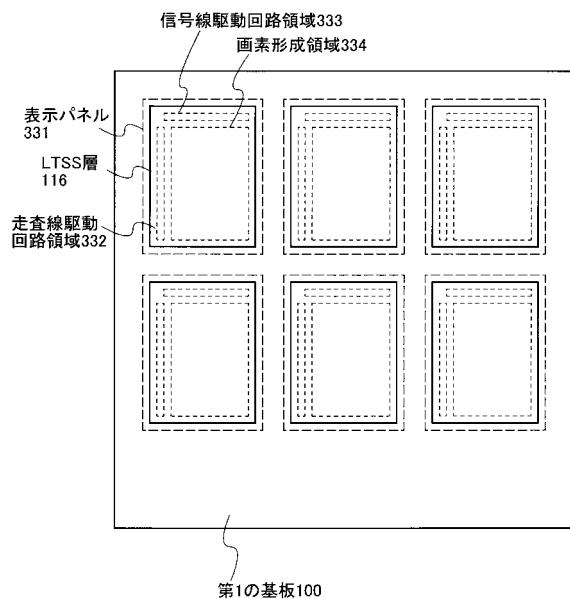

本発明を適用して作製したSOI基板を用いて表示パネルを作製することもできる。本実施の形態では、このような表示パネルについて説明する。

【0107】

図11は実施の形態1、又は実施の形態2を適用し、第1の基板100として、大面積基板を用い、半導体基板200を貼り合わせて、第1の基板上にLTSS層116を形成する場合を示す。大面積基板からは複数の表示パネルを切り出すため、LTSS層116は、表示パネル331の形成領域に合わせて接合することが好ましい。単結晶半導体基板に比べて、表示パネルを形成する大面積基板は面積が大きいため、LTSS層116は図11のように分割して配置することが好ましい。表示パネル331は、走査線駆動回路領域332、信号線駆動回路領域333及び画素形成領域334を有し、これらの領域が含まれるようにLTSS層116を第1の基板100に接合する。尚、実施の形態3を適用した場合は半導体層を基板一面に形成できるので、この操作は不要である。30

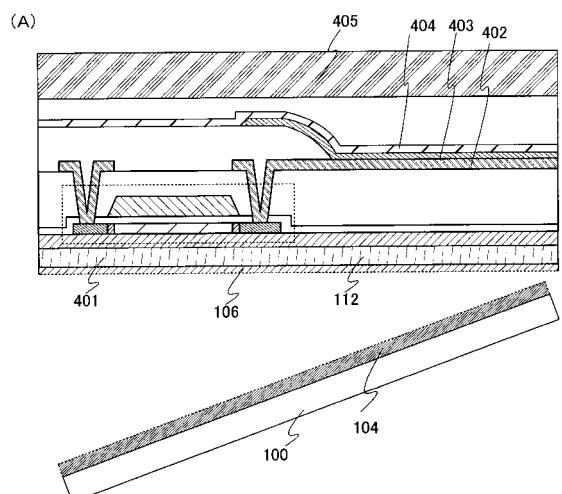

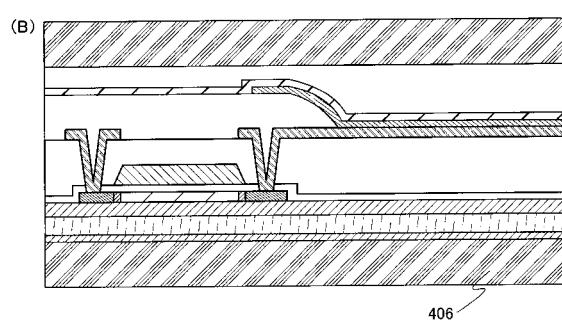

【0108】

図12は実施の形態1又は実施の形態2を適用して形成されたLTSS層、または実施の形態3を適用して形成された非単結晶半導体膜、の何れかを用いた半導体層により画素トランジスタ401が構成される発光表示パネルの画素の一例の断面図を示す。

【0109】

図12(A)において、画素トランジスタ401は第1の電極402に接続され、第1の電極402上にはEL層403が形成され、EL層403上には第2の電極404が形成されている。図12(A)は、第1の基板100上に発光表示パネルを形成し、剥離した様子を示す。転置される第2の基板として、プラスチック基板405を用いている。なお、図12(A)では、第1の剥離層104と第2の剥離層106との境界にて剥離されているが、本発明はこれに限定されない。40

【0110】

図12(B)は、図12(A)において転置した発光表示パネルの下にプラスチック基板406を設けた構成を示す。このようにプラスチック基板406を設けることで、発光表示パネルの耐衝撃性等を高め、信頼性を向上させることができる。

【0111】

本発明を適用したSOI基板を用いて発光表示パネルを作製することができる。しかし、

10

20

30

40

50

本実施の形態は一例に過ぎない。即ち、本発明は本実施の形態に限定されず、実施の形態1又は実施の形態2にて説明したSOI基板を用いて作製する、如何なる半導体装置にも適用することができる。

【0112】

このように、可撓性を有する大面積基板に本発明を適用した発光表示パネルを設けることも可能である。発光表示パネルは一つの装置あたりの面積が大きく、一箇所でも素子に欠損があると全体が不良になるが、本発明を適用し、これらを図1乃至図5に何れかにおける素子領域211にて形成することで、可撓性を有する基板上に接合される工程の際、素子内へのクラックが抑えられ、歩留まりの向上を図ることができる。

【0113】

尚、実施の形態4にて説明したマイクロプロセッサも同一基板上に形成すれば、表示パネル内にコンピュータの機能を搭載することもできる。同様に、非接触でデータの入出力が可能なディスプレイを作製することもできる。

【図面の簡単な説明】

【0114】

【図1】本発明のSOI基板の作製方法の一例を説明する図。

【図2】本発明のSOI基板の作製方法の一例を説明する図。

【図3】本発明のSOI基板の作製方法の一例を説明する図。

【図4】本発明のSOI基板の作製方法の一例を説明する図。

【図5】本発明のSOI基板の作製方法の一例を説明する図。

【図6】本発明のSOI基板を用いたトランジスタの作製方法の一例を説明する図。

【図7】本発明のSOI基板を用いたトランジスタの作製方法の一例を説明する図。

【図8】本発明を適用したSOI基板を用いた半導体装置の一例を説明する図。

【図9】本発明を適用したSOI基板を用いた半導体装置の一例を説明する図。

【図10】本発明を適用したSOI基板を用いた発光表示パネルの一例を説明する図。

【図11】本発明を適用したSOI基板を用いた発光表示パネルの一例を説明する図。

【図12】本明細書中における親水性の定義を説明する図。

【符号の説明】

【0115】

100 第1の基板

30

102 剥離層

104 第1の剥離層

106 第2の剥離層

108 剥離層

110 第1の接合層

112 接合形成層

114 接合形成層

116 L T S S 層

120 ゲート絶縁膜

122 ゲート電極層

124 サイドウォール

126 ドレイン領域

128 L D D 領域

130 絶縁膜

134 絶縁膜

136 第2の基板

200 半導体基板

202 損傷層

203 下地層

206 半導体膜

40

50

|       |               |    |

|-------|---------------|----|

| 2 1 0 | 接合層           |    |

| 2 1 1 | 素子領域          |    |

| 2 1 2 | 素子間領域         |    |

| 2 1 4 | 半導体膜          |    |

| 2 1 6 | 半導体膜          |    |

| 2 1 8 | 剥離層残渣         |    |

| 2 2 0 | クラック          |    |

| 3 0 0 | マイクロプロセッサ     |    |

| 3 0 1 | 演算回路          |    |

| 3 0 2 | 演算回路制御部       | 10 |

| 3 0 3 | 命令解析部         |    |

| 3 0 4 | 制御部           |    |

| 3 0 5 | タイミング制御部      |    |

| 3 0 6 | レジスタ          |    |

| 3 0 7 | レジスタ制御部       |    |

| 3 0 8 | バスインターフェース    |    |

| 3 0 9 | R O M         |    |

| 3 1 0 | R O Mインターフェース |    |

| 3 1 1 | R F C P U     |    |

| 3 1 2 | アナログ回路部       | 20 |

| 3 1 3 | デジタル回路部       |    |

| 3 1 4 | 共振回路          |    |

| 3 1 5 | 整流回路          |    |

| 3 1 6 | 定電圧回路         |    |

| 3 1 7 | リセット回路        |    |

| 3 1 8 | 発振回路          |    |

| 3 1 9 | 復調回路          |    |

| 3 2 0 | 変調回路          |    |

| 3 2 1 | R Fインターフェース   |    |

| 3 2 2 | 制御レジスタ        | 30 |

| 3 2 3 | クロックコントローラ    |    |

| 3 2 4 | C P Uインターフェース |    |

| 3 2 5 | C P U         |    |

| 3 2 6 | R A M         |    |

| 3 2 7 | R O M         |    |

| 3 2 8 | アンテナ          |    |

| 3 2 9 | 容量部           |    |

| 3 3 0 | 電源管理回路        |    |

| 3 3 1 | 表示パネル         |    |

| 3 3 2 | 走査線駆動回路領域     | 40 |

| 3 3 3 | 信号線駆動回路領域     |    |

| 3 3 4 | 画素形成領域        |    |

| 4 0 1 | 画素トランジスタ      |    |

| 4 0 2 | 電極            |    |

| 4 0 3 | E L 層         |    |

| 4 0 4 | 電極            |    |

| 4 0 5 | プラスチック基板      |    |

| 4 0 6 | プラスチック基板      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

マイクロプロセッサ300

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

H 01 L 21 / 02

H 01 L 21 / 336

H 01 L 21 / 762

H 01 L 27 / 12

H 01 L 29 / 786