(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4439593号

(P4439593)

(45) 発行日 平成22年3月24日(2010.3.24)

(24) 登録日 平成22年1月15日(2010.1.15)

(51) Int.Cl.

H01L 29/78 (2006.01)

F 1

H01L 29/78 301S

H01L 29/78 301J

請求項の数 14 (全 29 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平9-528732                  |

| (86) (22) 出願日 | 平成9年2月4日(1997.2.4)           |

| (65) 公表番号     | 特表2000-504881(P2000-504881A) |

| (43) 公表日      | 平成12年4月18日(2000.4.18)        |

| (86) 國際出願番号   | PCT/US1997/002108            |

| (87) 國際公開番号   | W01997/029519                |

| (87) 國際公開日    | 平成9年8月14日(1997.8.14)         |

| 審査請求日         | 平成16年1月23日(2004.1.23)        |

| (31) 優先権主張番号  | 08/597,711                   |

| (32) 優先日      | 平成8年2月7日(1996.2.7)           |

| (33) 優先権主張国   | 米国(US)                       |

|           |                                                                                                                                      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | サンダーバード・テクノロジーズ、インコ<br>ーポレイテッド<br>アメリカ合衆国、27709-3739<br>ノース・キャロライナ、リサーチ・トライ<br>アングル・パーク、ピー・オー・ボックス<br>13739、ペリメーター・パーク・ド<br>ライヴ 1000 |

| (74) 代理人  | 弁理士 奥山 尚男                                                                                                                            |

| (74) 代理人  | 弁理士 秋山 暢利                                                                                                                            |

| (74) 代理人  | 弁理士 奥山 尚一                                                                                                                            |

最終頁に続く

(54) 【発明の名称】 フェルミしきい値型電界効果型トランジスタ及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電型の半導体基板(21)と、

前記半導体基板の一表面(21a)において該基板内に位置する、空間的に隔たった第2の導電型のソース領域(23)及びドレイン領域(24)と、

前記半導体基板表面において該基板内に位置し、前記ソース領域から前記ドレイン領域まで拡がった、前記第2の導電型の第1のタブ領域(62)及び前記第2の導電型の第3のタブ領域(66)と、

前記空間的に隔たったソース領域及びドレイン領域の間において、前記基板表面上に位置するゲート絶縁層(26)と、

前記ソース領域及びドレイン領域と前記ゲート絶縁層にそれぞれ接触する、ソース電極(31)、ドレイン電極(32)、及びゲート電極(28)と、

を備えるフェルミしきい値型電界効果型トランジスタにおいて、

前記第1のタブ領域(62)と前記第3のタブ領域(66)との間に位置し、前記基板表面の真下において前記ソース領域から前記ドレイン領域まで拡がった、前記第1の導電型の埋め込まれた第2のタブ領域(64)を具備し、

前記ソース領域及びドレイン領域は、前記第1のタブ領域(62)内にソース底(23a)及びドレイン底(24a)を有するとともに、前記第1のタブ領域(62)は、さらに、前記ソース底から前記ドレイン底まで拡がっていること、

を特徴とするフェルミしきい値型電界効果型トランジスタ。

10

20

**【請求項 2】**

前記第1のタブ領域(62)は、前記半導体基板(21)内に位置する第2の導電型の領域であるとともに、前記空間的に隔たったソース領域及びドレイン領域は、前記半導体基板内において前記タブ領域(62)内に位置するように構成されたことを特徴とする請求項1に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 3】**

前記第3のタブ領域(66)は、前記半導体基板内に位置し、前記ソース領域から前記ドレイン領域まで拡がるとともに、前記基板表面から前記基板内に第1の深さ(Y<sub>1</sub>)まで拡がった、前記第2の導電型の領域から成り、

前記埋め込まれた第2のタブ領域(64)は、前記基板内に前記第1の深さ(Y<sub>1</sub>)と第2の深さ(Y<sub>2</sub>)の間で拡がり、

前記第1のタブ領域(62)は、前記基板内に前記第2の深さ(Y<sub>2</sub>)と第3の深さ(Y<sub>3</sub>)の間で拡がった、前記第2の導電型の領域から成ることを特徴とする請求項1に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 4】**

前記第1のタブ領域(62)は、前記基板内に前記基板表面から第3の深さ(Y<sub>3</sub>)まで拡がった、前記第2の導電型の領域から成り、

前記基板内に前記第3の深さ(Y<sub>3</sub>)未満の第2の深さ(Y<sub>2</sub>)まで拡がった、前記第1の導電型の第2のタブ領域(64)を備え、

前記基板内に第2の深さ(Y<sub>2</sub>)未満の第1の深さ(Y<sub>1</sub>)まで拡がった、前記第2の導電型の第3のタブ領域(66)を備え、

前記空間的に隔たったソース領域及びドレイン領域の底は、前記第1のタブ領域内に位置し、かつ、前記基板内を前記第3の深さ(Y<sub>3</sub>)未満の第4の深さ(Y<sub>4</sub>)に位置するように構成されたことを特徴とする請求項1に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 5】**

前記ゲート電極は前記第1の導電型の多結晶シリコン層(28)を含むことを特徴とする請求項1に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 6】**

前記ゲート電極は、前記第1の導電型の多結晶シリコン層を含むことを特徴とする請求項2に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 7】**

前記ゲート電極は、前記第1の導電型の多結晶シリコン層を含むことを特徴とする請求項3に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 8】**

前記第4の深さ(Y<sub>4</sub>)は、前記第2の深さ(Y<sub>2</sub>)より大きいことを特徴とする請求項4に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 9】**

前記ゲート電極は、前記第1の導電型の多結晶シリコン層を含むことを特徴とする請求項4に記載のフェルミしきい値型電界効果型トランジスタ。

**【請求項 10】**

フェルミしきい値型電界効果型トランジスタを製造するための方法であって、

半導体基板(21)内に、第1の導電型の領域(70)と、前記第1の導電型の領域(70)内の第2の導電型の第1のタブ領域(62)と、該第1のタブ領域内の前記第1の導電型の第2のタブ領域(64)とを形成するステップであって、前記第2のタブ領域を形成した後も前記半導体基板(21)の表面に前記第1の導電型の領域(70)が露出している、ステップと、

前記第1の導電型の領域(70)及び前記第2のタブ領域に接するように、前記半導体基板上にエピタキシャル層(76)を形成し、さらに該エピタキシャル層(76)内に第3のタブ領域(66)を形成するステップと、

10

20

30

40

50

前記第3のタブ領域(66)と前記第2のタブ領域(64)と前記第1のタブ領域(62)内に、ソース底(23a)及びドレイン底(24a)が第1のタブ領域(62)内に位置するように空間的に隔たった前記第2の導電型のソース領域(23)及びドレイン領域(24)を形成するステップと、

を含むことを特徴とするフェルミしきい値型電界効果型トランジスタの製造方法。

#### 【請求項11】

前記第1のタブ領域及び第2のタブ領域を形成する前記ステップは、

前記半導体基板内に前記第2の導電型のイオンを注入して、前記第1のタブ領域を形成するステップと、

前記第1のタブ領域内に前記第1の導電型のイオンを注入して前記第1のタブ領域の一部をカウンタドープし、それによって前記第2のタブ領域を形成するステップと、

を含むことを特徴とする請求項10に記載のフェルミしきい値型電界効果型トランジスタの製造方法。 10

#### 【請求項12】

前記エピタキシャル層(76)を形成し、さらに該エピタキシャル層(76)内に第3のタブ領域(66)を形成するステップは、

前記半導体基板上にドープされていない半導体層をエピタキシャル的に形成するステップと、

前記ドープされていない半導体層内に前記第2の導電型のイオンを注入し、それによって前記半導体層を第2の導電型にドープし前記第3のタブ領域を形成するステップと、 20

を含むことを特徴とする請求項10に記載のフェルミしきい値型電界効果型トランジスタの製造方法。

#### 【請求項13】

前記空間的に隔たったソース領域及びドレイン領域を形成する前記ステップには、前記第3のタブ領域(66)内に、かつ該第3のタブ領域(66)を貫通させて前記第2のタブ領域(64)内に、さらに該第2のタブ領域(64)を貫通させて前記第1のタブ領域(62)内に前記第2の導電型のイオンを注入するステップが含まれることを特徴とする請求項10に記載のフェルミしきい値型電界効果型トランジスタの製造方法。

#### 【請求項14】

前記空間的に隔たったソース領域及びドレイン領域を形成する前記ステップは、前記第3のタブ領域(66)に接してゲート酸化物(26)及びゲート電極(28)を形成するステップの後に実行されることを特徴とする請求項10に記載のフェルミしきい値型電界効果型トランジスタの製造方法。 30

#### 【発明の詳細な説明】

##### 発明の分野

本発明は、電界効果型トランジスタ(field effect transistor)、特に集積回路電界効果型トランジスタ及びその製造方法に関する。

##### 発明の背景

電界効果型トランジスタ(FET)は、論理デバイス、メモリデバイス、およびマイクロプロセッサなどのような大規模集積回路(VLSI)や超大規模集積回路(ULSI)への適用における主たる実用デバイスとなっている。その理由は、集積回路型FETがその性質から高インピーダンス、高密度、低電力デバイスだからである。多くの研究及び開発活動では、FETのスピード及び集積密度を改善すること、そしてその電力消費を減少させることが焦点となっている。 40

高速かつ高性能の電界効果型トランジスタは、ともに「フェルミしきい値電界効果型トランジスタ(Fermi Threshold Field Effect Transistor)」と題されたA.W.ビナル(A.Ibert W.Vinal)氏による米国特許第4,984,043号及び第4,990,974号に開示されている。これらの特許はいずれも本発明の譲受人に譲渡されている。前記特許には、デバイスのしきい値電圧を半導体物質のフェルミ電位の2倍に設定することによって反転が必要とされない拡大モードで作動する金属酸化物電界効果型トランジスタ(MO

S F E T (metal oxide semiconductor field effect transistor) )が記述されている。当業者にはよく知られているように、フェルミ電位とは半導体物質のエネルギー状態が一つの電子によって占拠される確率が1 / 2となるような電位として定義される。上記ビナルの特許明細書において記述されているように、しきい値電圧がフェルミ電位の2倍に設定されるとき、しきい値電圧の、酸化物の厚さ、チャネル長、ドレイン電圧、及び基板ドーピングに対する依存性が消滅する。さらに、しきい値電圧がフェルミ電位の2倍に設定されるとき、酸化物とチャネルとの間の基板表面における垂直方向の電界が最小となり、実際には実質上ゼロとなる。その結果、チャネル内のキャリア移動度は最大となり、熱電子効果が大きく減少した高速デバイスが実現される。デバイス性能は、実質上、デバイスの大きさには依存しない。

フェルミしきい値F E Tは既に知られているフェルミF E Tデバイスと比較して大きな改善であったにもかかわらず、フェルミF E Tの容量を低減させる必要が存在した。こうしたことから、ともに「ゲート及び拡散容量の減少した、フェルミしきい値電界効果型トランジスタ (Fermi Threshold Field Effect Transistor With Reduced Gate and Diffusion Capacitance) 」と題されたビナル (Albert W.Vinal) 氏による米国特許第5,194,923号及び第5,369,295号において、伝導キャリアが、キャリアの伝導性を維持するために半導体表面において生成されるべき反転層が必要とされることなく、ゲート下の基板の所定の深さでチャネル内を流れることができる、フェルミF E Tが開示されている。従って、チャネル電荷の平均的な深さではゲート容量の一部として基板の誘電率を含ませる必要がある。その結果、ゲート容量は可成り減少する。

前記米国特許第5,194,923号及び第5,369,295号に記述されているように、低容量フェルミF E Tは、所定の深さと、基板とは反対の導電型でドレイン及びソースと同一の導電型を有するフェルミ・タブ領域を使用することにより望ましく実現される。このフェルミ・タブは基板表面から所定の深さに達し、ドレイン及びソース拡散はフェルミ・タブ境界内のフェルミ・タブ内に形成される。このフェルミ・タブによって、ソース、ドレイン、チャネル、及びフェルミ・タブが全て、異ったドーピング濃度でドーピングされた同一の導電型を有する単接合トランジスタ (unijunction transistor) が形成される。このようにして低容量フェルミF E Tが提供される。フェルミ・タブを含む低容量フェルミF E Tをここでは「低容量フェルミF E T」又は「タブF E T」と呼ぶこととする。

フェルミF E T及び低容量フェルミF E Tは既に知られているF E Tデバイスと比較して大きな改善であるにもかかわらず、単位チャネル幅当たりの電流を増大させるためのさらなる必要性が存在する。当業者にはよく知られているように、より高い電流のフェルミF E Tデバイスによれば、大きな集積密度、そして(あるいは)論理回路、メモリ、マイクロプロセッサ、及び他の集積回路デバイスにおけるもっと大きな速度が実現される。これに関して、「高電流フェルミF E T」と題された、ビナル (Albert W.Vinal) 氏及び本発明者への米国特許第5,374,836号には、フェルミ・タブ領域及びソース領域と同一の導電型の、ソース領域に隣接するとともにドレイン領域と対向する、インジェクタ (injector) 領域を含むフェルミF E Tが記述されている。このインジェクタ領域は、フェルミ・タブの比較的低いドーピング濃度とソースの比較的高いドーピング濃度との中間にあるドーピングレベルで好ましくドーピングされる。このインジェクタ領域によってチャネル内に注入されたキャリアの深さが制御されるとともに、チャネル内にキャリアをゲート下の所定の深さにまで注入することが強化される。米国特許第5,374,836号によるトランジスタをここでは「高電流フェルミF E T」と呼ぶこととする。

ソース・インジェクタ領域はソース領域を囲むソース・インジェクタ・タブ領域であることが好ましい。ドレイン・インジェクタ・タブ領域も提供することができる。ソース・インジェクタ領域に隣接するところからフェルミF E Tのゲート電極に隣接するところまで達するゲート側壁スペーサーも、ピンチオフ電圧を低下させ、かつ、フェルミF E Tの飽和電流を増大させるために提供することが可能である。基板と同一の導電型にある底漏れ制御領域 (bottom leakage control region) もまた提供することができる。

フェルミFET、低容量フェルミFET、及び高電流フェルミFETは既に知られているFETデバイスと比較して大きな改善であるにもかかわらず、低電圧での動作を改善する更なる必要性が存在する。当業者にはよく知られているように、現在のところ、一般的に5ボルト、3ボルト、1ボルト、あるいはそれ以下の電源電圧で動作する、低電力携帯用及び/又はバッテリ電源用デバイスに大きな関心が寄せられている。

ある与えられたチャネル長に対して、動作電圧を低下させれば横方向の電界が線形的にドロップする。非常に低い電圧では、横方向の電界があまりに低く、チャネル内のキャリアが飽和速度に達することが妨げられる。この結果、有効ドレイン電流が陥しくドロップする。このドレイン電流のドロップによって、ある与えられたチャネルに対して使用可能な回路速度を得るための動作電圧の低下が効果的に制限される。

低電圧におけるタブFETの動作を改善するため、「定域タブ・フェルミしきい値電界効果型トランジスタ及びその製造方法(Contored-Tub Fermi-Threshold Field Effect Transistor and Method of Forming Same)」と題された本発明者による米国出願第08/351,643号には、不均一なタブの深さを有する定域フェルミ・タブ領域を含むフェルミFETが記述されている。特に、フェルミ・タブはチャネル領域の下よりもソース及び/又はドレインの下の方が深くなっている。こうして、タブ基板間接合はチャネル領域の下よりもソース及び/又はドレインの下の方が深い。拡散容量はそれによって一様なタブ深さを有するフェルミ・タブと比較して減少し、その結果、高い飽和電流が低電圧において生成される。

特に、米国出願第08/351,643号による定域タブ・フェルミしきい値電界効果型トランジスタは第1の導電型の半導体基板と、半導体基板表面においてその半導体基板内に第2の導電型の空間的に隔てられたソース領域及びドレイン領域を有する。第2の導電型のチャネル領域も、空間的に隔てられたソース領域及びドレイン領域の間ににおいて、半導体基板表面においてその半導体基板内に形成される。第2の導電型のタブ領域も半導体基板表面においてその半導体基板内に含まれる。タブ領域は、基板表面より空間的に隔てられたソース領域及びドレイン領域の少なくとも一方の下に第1の所定の深さまで達し、基板表面よりチャネル領域の下に第2の所定の深さまで達する。第2の所定の深さは第1の所定の深さよりも小さい。ゲート絶縁層及び、ソース接触子、ドレイン接触子及びゲート接触子(コンタクト)も含まれる。基板接触子も含ませることができる。

第2の所定の深さ、すなわちチャネルに隣接する定域タブの深さ、は前記米国特許第5,194,923号及び第5,369,295号に定義されているようなフェルミFET基準を満足することができるように選ばれる。特に、第2の所定の深さは、ゲート電極がアース電位にあるときに、チャネル底において基板表面に垂直な静電界がゼロになるように選ばれる。第2の所定の深さも、半導体基板のフェルミ電位の2倍となった電界効果型トランジスタのしきい値電圧を生成するように選ばれる。第1の所定の深さ、すなわちソース及び/又はドレインに隣接する定域タブの深さは、ソース接触子及び/又はドレイン接触子にゼロのバイアスが印加された際に、ソース及び/又はドレイン下のタブ領域を空乏化する好ましく選ばれる。

最新の超小型電子技術が進展したため、製作回線幅は実質的に1ミクロン未満にまで減少している。回線幅(linewidth)がこのように減少したことによって、チャネル長が実質的に1ミクロン未満、電流処理技術によれば一般的に1/2ミクロン未満であるところの「短チャネル」FETが生み出されている。

米国特許第5,194,923号及び米国特許第5,369,295号の低容量フェルミFET、米国特許第5,374,836号の高電流フェルミFET、及び米国出願第08/351,643号の定域タブ・フェルミFETは低電圧において高い性能を有する短チャネルFETを提供するために使用することが可能である。しかしながら、回線幅が減少するにつれ、処理制限(processing limitation)によってFETを製作する際に到達可能な大きさ及び電導性が制限されることはあることは当業者であれば認識できよう。このため、回線幅が減少した場合、処理状態によってはフェルミFETトランジスタを再最適化してこれらの処理制限に適応させることが要求されることもある。

フェルミF E Tトランジスタを処理制限に適応させるために再最適化することは、本発明者の譲受人に譲渡された「短チャネル・フェルミしきい値電界効果型トランジスタ(Short Channel Fermi-Threshold Field Effect Transistors)」と題された米国特許出願第08/505,085号に記述されている。詳細に関してはこの特許出願を参照する。ここに引用された「短チャネル・フェルミしきい値電界効果型トランジスタ」と題された米国特許出願第08/505,085号の短チャネル・フェルミF E Tには、フェルミ・タブをその深さ方向に越えて拡がり、かつフェルミ・タブをその横方向にも越えて拡がる、空間的に隔たったソース領域及びドレイン領域が含まれる。ソース領域及びドレイン領域がタブを越えて拡がるために、基板との接合が形成され、電荷共有状態が生じる。この状態を補償するためには、基板のドーピングを増大させなければならない。ソース領域及びドレイン領域が非常に小さく離れているために、望ましくタブの深さが減る。この結果、ゲート電極がしきい値電位にあるときには、酸化物：基板間界面において基板に垂直な静電界に変化が生じる。一般的な長チャネル・フェルミF E Tトランジスタでは、この電界は基本的にゼロである。短チャネル・デバイスでは、この電界はM O S F E Tトランジスタよりもかなり低いが、長チャネル・フェルミF E Tトランジスタよりはいくぶん高い。特に、本発明による短チャネル・フェルミF E Tトランジスタは、第1の導電型の半導体基板と、半導体基板表面においてその基板内に位置し、基板表面より第1の深さまで達する、第2の導電型のタブ領域とを有する。またこの短チャネル・フェルミF E Tトランジスタは、タブ領域内に位置する、第2の導電型の空間的に隔たったソース領域及びドレイン領域も含む。この空間的に隔たったソース領域及びドレイン領域は基板表面より第1の深さを越えて拡がり、さらに横方向に互いから離れて、タブ領域を越えて拡がる。

空間的に隔たったソース領域及びドレイン領域の間ににおいて、タブ領域内に位置し、基板表面より前記第1の深さよりも小さい第2の深さまで達する、第2の導電型のチャネル領域も含まれる。第1及び第2の深さの少なくとも一方は、ゲート電極がしきい値電位にあるときに、基板表面に垂直な静電界を、基板表面から第2の深さまでの間で最小化するように選ばれる。たとえば、従来のM O S F E Tにおいて静電界が $10^5$ V/cmよりも大きいのに対して、短チャネル・フェルミF E Tでは $10^4$ V/cmの大きさの静電界を生成することが可能である。これとは対照的に、米国特許第5,194,923号及び米国特許第5,369,295号によるタブF E Tは $10^3$ V/cmよりも小さい（またそれよりもかなり小さくなることがしばしば起こる）静電界を生成することができる。これは従来のM O S F E Tに比較すれば基本的にゼロである。第1及び第2の深さは、半導体基板のフェルミ電位の2倍となる電界効果型トランジスタのしきい値電圧を生成するようを選ぶことができ、さらに、しきい値電圧がゲート電極に印加された際に、第2の導電型のキャリアがチャネル内を、第2の深さで、ソース領域からドレイン領域まで流れるようにすることができ、また、しきい値電圧を越える電圧がゲート電極に印加された際には、チャネル内に反転層を生成させることなく、第2の深さから基板表面に向かって拡がりながら流れることができるように選ぶこともできる。トランジスタはさらにゲート絶縁層と、ソース接触子、ドレイン接触子、及びゲート接触子も含む。基板接触子も含むことができる。

集積回路電界効果型トランジスタの継続的な小型化によって、1ミクロンをかなり下回る大きさまでチャネル長が減少した。この集積回路電界効果型トランジスタの継続的な小型化にしばしばかなり高い基板ドーピングレベルが要求される。高いドーピングレベルと、より小さな装置に必要とされるかもしれない減少した作動電圧によって、フェルミF E Tと従来のM O S F E Tデバイスの両方のソース領域及びドレイン領域に付随した容量が大きく増大するかもしれない。

特に、フェルミF E Tが1ミクロン未満の大きさにされると、ソースにおけるドレイン誘導障壁降下(D I B L (Drain Induced Barrier Lowering))が増大するために、タブの深さがかなり浅くなってしまう。残念ながら、短チャネル・フェルミF E Tについて既に記述された変更を以てさえ、ドレイン誘導障壁降下及びトランジスタ漏れを制御するのに望ましい深さ及びドーピングレベルが製造するには困難なサイズに達するかもしれない。

10

20

30

40

50

さらに、チャネル内における高いドーピングレベルによってキャリア移動度が減少するかもしれない、それによってフェルミFET技術の高電流利点も減少するかもしれない。ドレン電圧を減少させつつ、基板ドーピングレベルがより高まることによって接合容量も増大するかもしれない。

#### 発明の目的と概要

以上の説明から、本発明の目的は、改良されたフェルミしきい値電界効果型トランジスタ（フェルミFET（Fermi-threshold field effect transistor））を提供することにある。

本発明の他の目的は、改良された金属酸化物半導体電界効果型トランジスタ（MOSFET（metal oxide semiconductor feild effect transistor））を提供することにある。10

本発明の更に他の目的は、短チャネル長に適合したフェルミFET及びMOSFETを提供することにある。

本発明の更に他の目的は、チャネルの高いドーピングレベルを必要としない、かつ、超浅のタブの深さを必要としない、短チャネル・フェルミFET及びMOSFETを提供することにある。

本発明のもう更に他の目的は、短チャネル・フェルミFET及びMOSFETを製造する方法を提供することにある。

本発明によれば、これらの目的及び他の目的は、ドレンバイアスの結果としてソース領域からタブ領域内へのキャリアの注入を減少させるために、タブ領域内にソース領域及びドレン領域との間でドレン電界を終止させる手段（以下、ドレン電界終止手段）を備えたフェルミFETによって実現される。今は亡きフェルミFETの発明者の記念に「ビナルFET（Vinal-FET）」とここでは呼ばれる、ドレン電界終止手段を備えた短チャネル・フェルミFETは、フェルミFETと同様に、チャネル内での低い垂直方向の電界をなお許容しながら、過度なドレン誘導障壁降下を抑制する。加えて、ビナルFETはかなりより高いキャリア移動度を実現し、同時にソース・ドレン間接合容量を大きく減少させる。20

ドレン電界終止手段は、ソース領域とドレン領域の間で、基板表面の真下にソース領域からドレン領域まで拡がる、埋め込まれたカウンタドープ（counterdoped）された層によって実現される。特に、ビナルFETは、第1の導電型の半導体基板と、半導体基板の一表面においてその基板内に位置する第2の導電型のタブ領域を備える。第2の導電型の空間的に隔たったソース領域及びドレン領域は前記半導体基板表面においてタブ領域内に含まれる。第1の導電型の埋め込まれたドレン電界終止領域もまたタブ領域内に含まれる。ドレン電界終止領域は基板表面の真下をソース領域からドレン領域まで拡がる。ゲート絶縁層と、ソース電極、ドレン電極、及びゲート電極もまた含まれる。こうして、ビナルFETは、ドレンのバイアスによってキャリアがソース領域からタブ領域内に注入されることを抑制する付加的なカウンタドープされた埋め込まれたドレン電界終止領域を備えたフェルミFETと見做してもよい。30

ビナルFETは三重タブ構造と見做してもよい。特に、第1の導電型の半導体基板には、その半導体基板の一表面においてその基板内に位置し、その基板表面より基板内に第1の深さまで拡がった、第2の導電型の第1のタブ領域が含まれる。第1の導電型の第2のタブ領域は、第1のタブ領域内に含まれ、かつ、基板表面より基板内に第1の深さ未満の第2の深さまで拡がる。第2の導電型の第3のタブ領域は、第2のタブ領域内に含まれ、かつ、基板表面より基板内に第2の深さ未満の第3の深さまで拡がる。第2の導電型の空間的に隔たったソース領域及びドレン領域は第1のタブ領域内に含まれ、かつ、基板表面より基板内に第3の深さよりも大きい第4の深さまで拡がる。ゲート絶縁層と、ソース電極、ドレン電極、及びゲート電極も与えられる。トランジスタの実施の一態様において、ソース領域及びドレン領域は、基板内に、第3深さよりも大きく第2の深さよりも小さな第4の深さまで投影される。他の実施の態様において、ソース領域及びドレン領域は、基板内に、第2深さよりも大きく第1の深さよりも小さな第4の深さまで投影される。

ビナルFETは、第1の導電型にある基板内で第2の導電型の空間的に隔たったソース領域及びドレイン領域の間に拡がった、3枚の別個の層を備えた電界効果型トランジスタと見做してもよい。第2の導電型の第1の層は、ソース領域からドレイン領域まで拡がり、かつ、基板表面より基板内に第1の深さまで拡がる。第1の導電型の第2の層は、ソース領域からドレイン領域まで拡がり、かつ、基板表面より基板内に第1の深さから第2の深さまで拡がる。第2の導電型の第3の層は、ソース領域からドレイン領域まで拡がり、かつ、基板表面より基板内に第2の深さから第3の深さまで拡がる。ビナルFETの第1の実施の態様において、ソース領域及びドレイン領域は半導体基板内にソース底及びドレイン底を有するとともに、第2及び第3の層は両方ともにソース底からドレイン底まで拡がる。ビナルFETの第2の実施の態様において、第3の層のみがソース底からドレイン底まで拡がり、第2の層はソース側壁からドレイン側壁まで拡がる。

ドレイン電界終止手段は、タブ領域内に埋め込まれた第1の導電型の領域、第1のタブ領域内の第1の導電型の第2のタブ領域、又はソース及びドレインの間に拡がる第1の導電型の第2の層によって具体化され、チャネル内での低い垂直方向の電界をなお許容しながら、過度なドレイン誘導障壁降下を抑制する。より高いキャリア移動度とソース・ドレイン接合容量の大きな減少が実現される。

ビナルFETのドレイン電界終止手段は、従来にMOSFETにおいて、前記利点の少なくともいくつかを与えることができるよう使用してもよい。特に、従来のMOSFETは、第1の導電型の半導体基板と、その半導体基板の一表面においてその基板内に含まれる第2の導電型の空間的に隔たったソース領域及びドレイン領域とを備えてよい。第1の導電型の第1の層は、半導体基板の一表面においてその基板内に含まれ、ソース領域からドレイン領域まで拡がるとともに、基板表面より基板内に第1の深さまで拡がる。第2の導電型の第2の層は、基板内に含まれ、ソース領域からドレイン領域まで拡がるとともに、基板表面より基板内に第1の深さから第2の深さまで拡がる。第2の層、又は、第1及び第2の層は、第1及び第2のタブ領域をそれぞれ定義するためのソース底からドレイン底まで拡がってよい。

ビナルFETを製造する好ましい方法によれば、第3のタブ領域（又は第1の層）がエピタキシャル的に形成され、このためそれはドレイン電界終止領域（又は第2のタブ領域又は第3の層）に関してカウンタドープされることを必要としない。第3のタブ領域又は第1の層をエピタキシャル的に形成することによって、ある与えられたドーピングレベルに対してより高いキャリア移動度が得られる場合がある。従って、ビナルFETを製造する好ましい方法には、基板表面から第1のタブ領域を埋め込むステップと、第1のタブ領域内に第2のタブ領域を埋め込むステップが含まれる。その後、エピタキシャル的な堆積が実行され、あるいは本来の場所にドープ又は注入されて、第2のタブ領域内に第3のタブ領域が形成される。その後、多結晶ゲート電極が従来の技術を使って形成され、ソース領域及びドレイン領域が注入される。こうして、チャネルのキャリア移動度が増大する。

#### 【図面の簡単な説明】

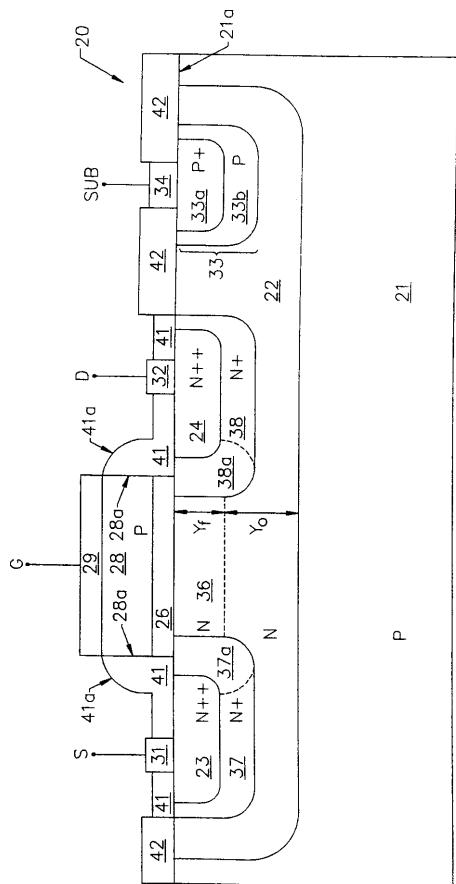

図1は米国特許出願第08/037,636号によるNチャネル高電流フェルミFETの断面図である。

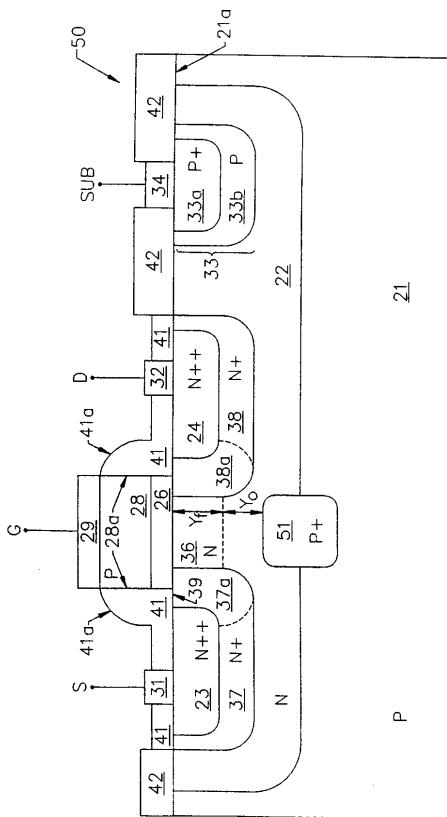

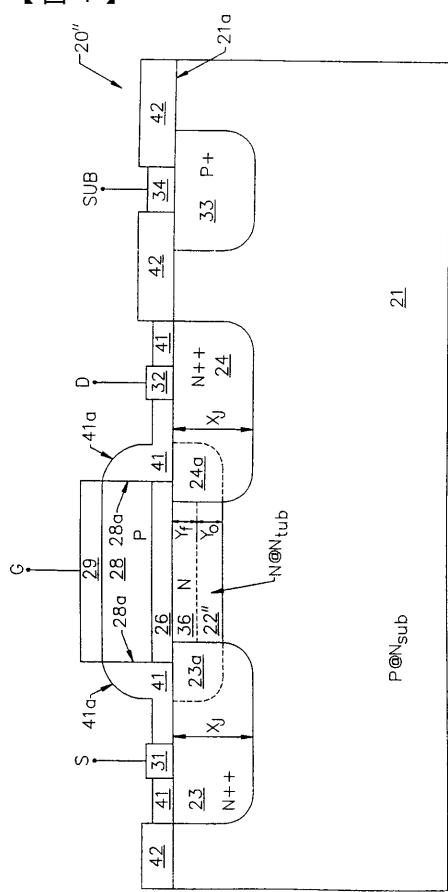

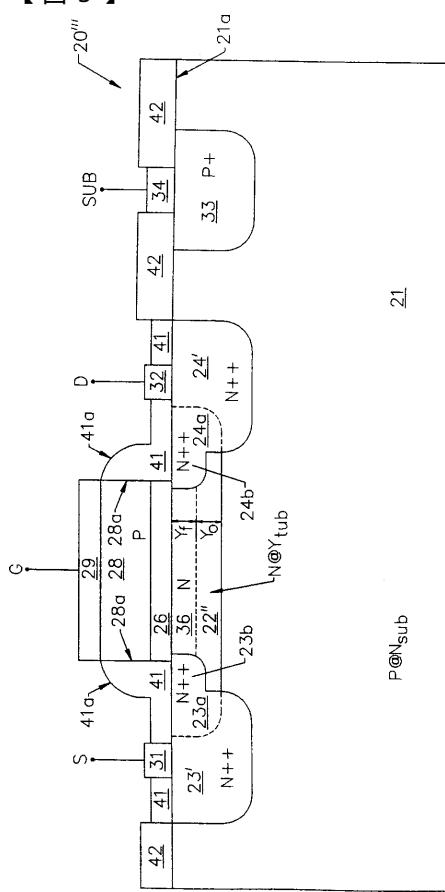

図2Aは米国特許第5,374,836号による短チャネル低漏れ電流フェルミFETの第1の実施態様を示した断面図である。

図2Bは米国特許第5,374,836号による短チャネル低漏れ電流フェルミFETの第2の実施態様を示した断面図である。

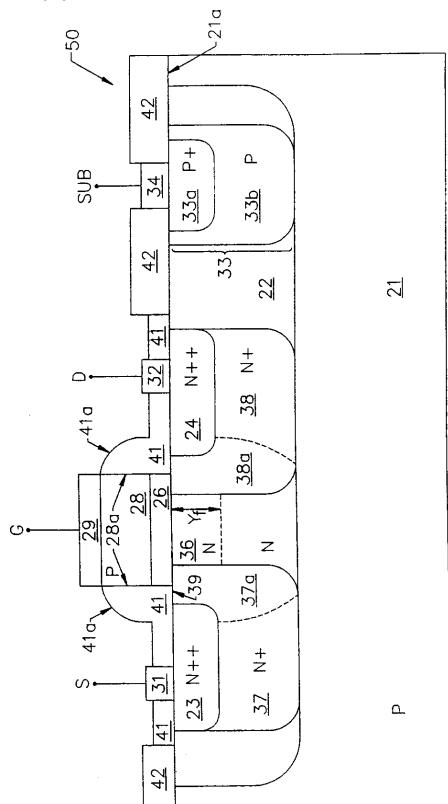

図3は米国特許出願第08/037,636号によるNチャネル定域タブ・フェルミFETの断面図である。

図4は米国特許出願第08/505,085号によるNチャネル短チャネル・フェルミFETの断面図である。

図5は米国特許出願第08/505,085号によるNチャネル短チャネル・フェルミFETの第2の実施態様を示した断面図である。

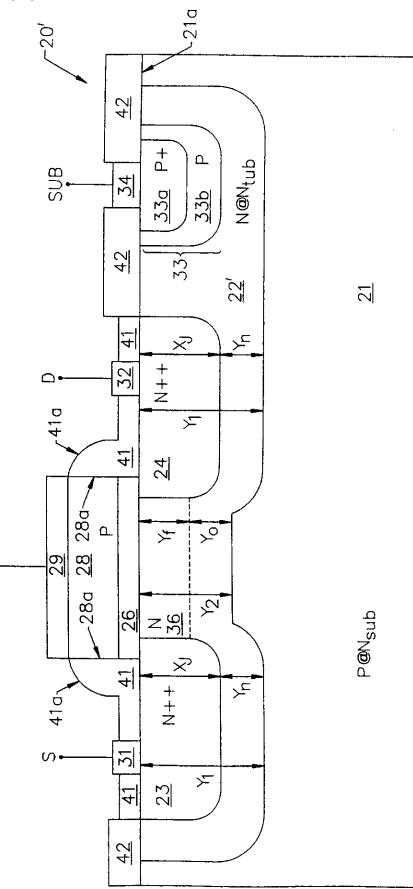

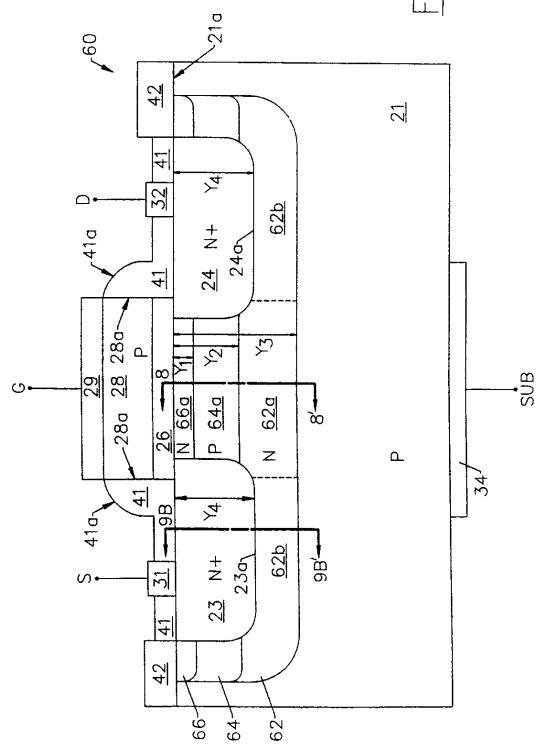

図6は本発明によるビナルFETの第1の実施態様を示した断面図である。

10

20

30

40

50

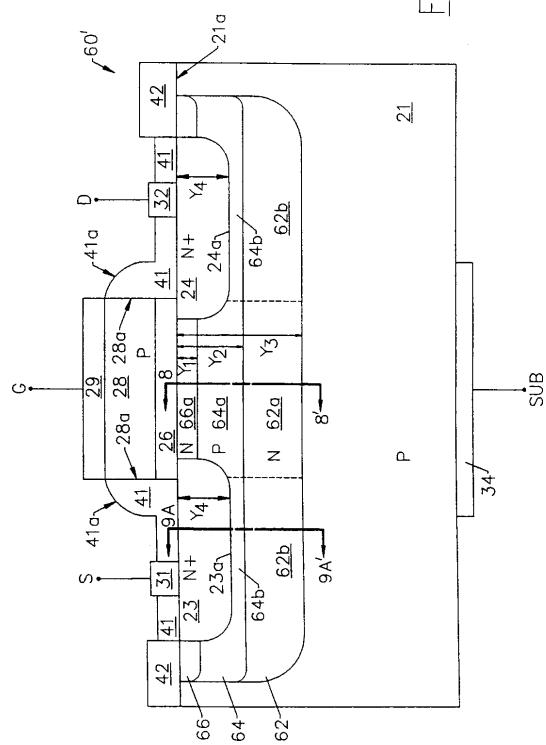

図7は本発明によるビナルFETの第2の実施態様を示した断面図である。

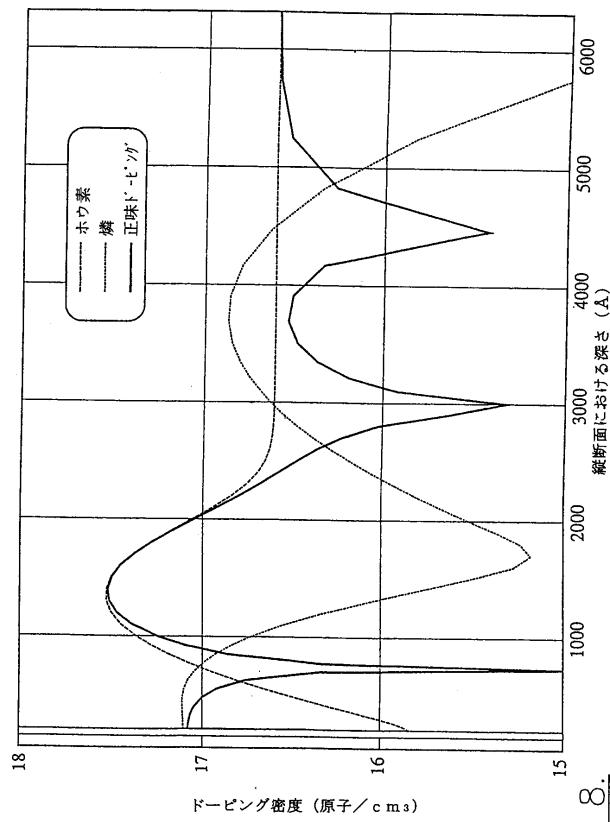

図8は図6及び図7のビナルFETのライン8-8に沿った正味のドーピングプロファイルをグラフ的に示した図である。

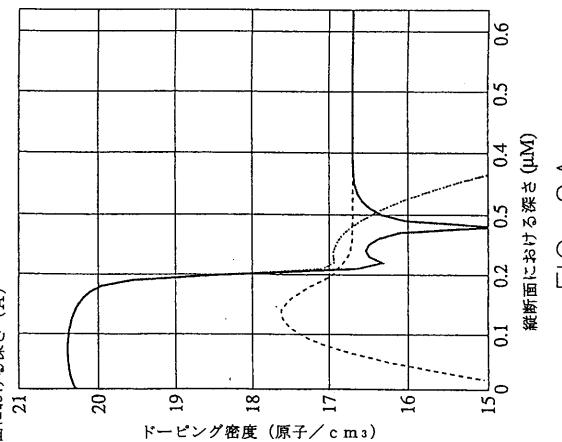

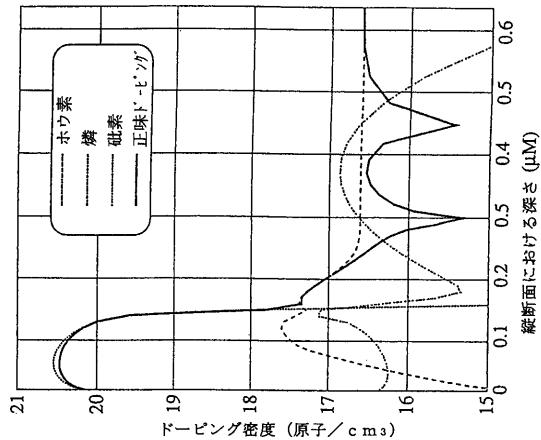

図9A及び図9Bは図6及び図7のライン9A-9A及びライン9B-9Bに沿った正味のドーピングプロファイルをそれぞれグラフ的に示した図である。

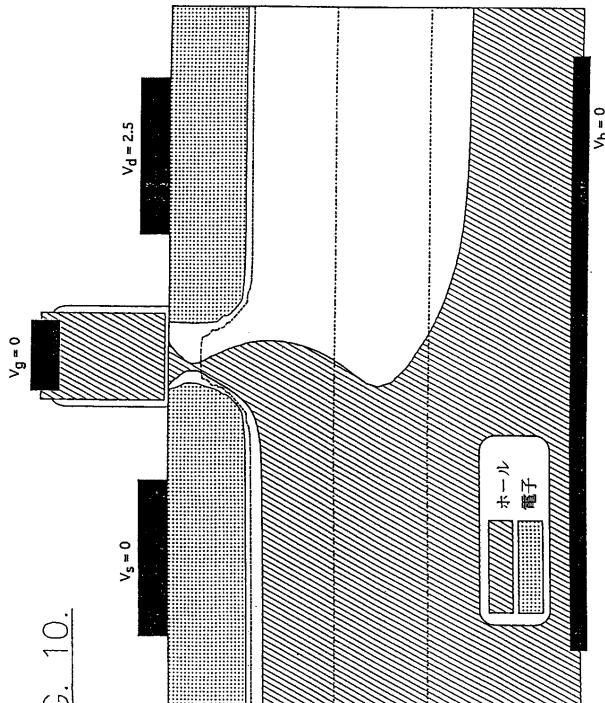

図10、11、及び12は図7のビナルFETに対するシミュレーション結果を示した図である。

図13は図6及び図7のビナルFETのドレイン電界終止領域に対する最小の好ましいドーピングを示した図である。

図14は印加電圧に対するソース容量又はドレイン容量をグラフ的に示した図である。 10

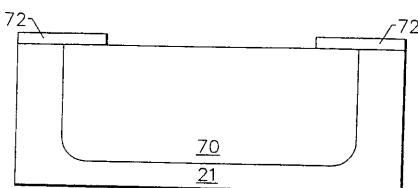

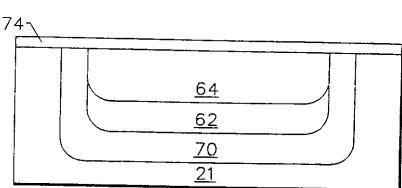

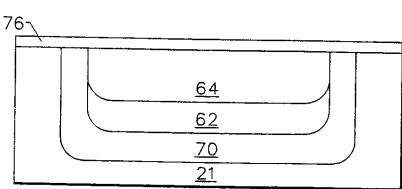

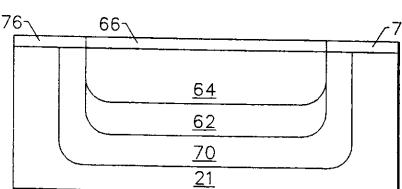

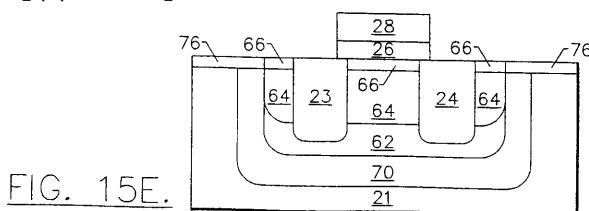

図15Aから15Eは中間製作ステップにおける図6のビナルFETの断面図である。

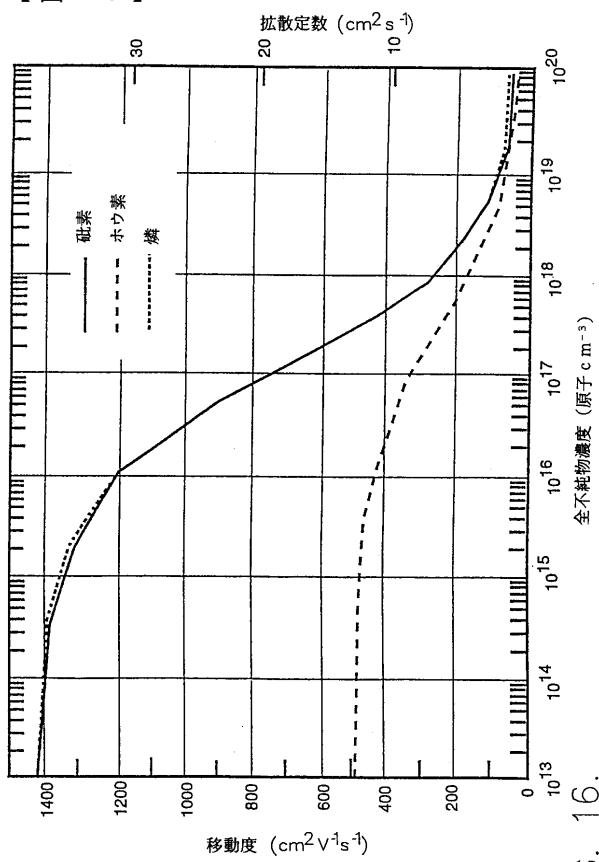

図16は全不純物濃度の関数としてシリコン内におけるキャリア移動度をグラフ的に示した図である。

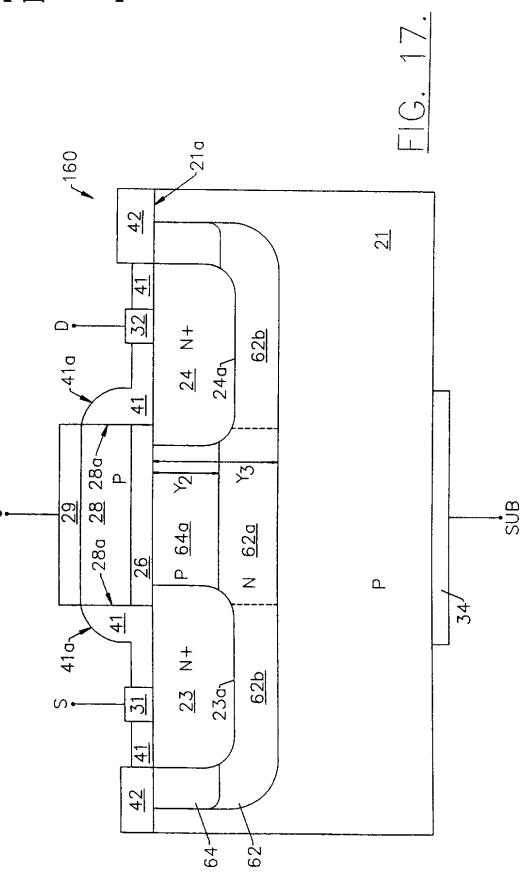

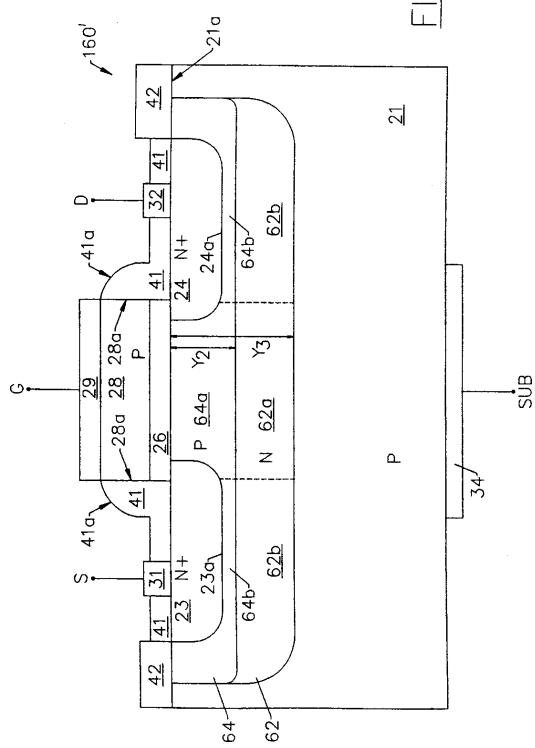

図17及び図18は本発明による高性能MOSFETの断面図である。

#### 詳細な説明

以下、図面を参照して本発明の好ましい実施の形態をより詳細に説明する。本発明は、しかしながら、多くの形態において実施することが可能であり、以下に記述される実施形態に限定されるものではない。むしろ、これらの実施形態は開示を周到かつ徹底したものとし、当業者に向けて本発明の範囲を十分に明らかにすべく提供されるものである。図面では、分かりやすくするために層や領域の厚さが誇張して描かれている。また、類似部分には一貫して類似符号が付されている。 20

本発明によるドレイン電界終止領域を含む短チャネル・フェルミしきい値FET（「ビナルFET」とも呼ばれる）を説明する前に、米国特許第5,194,923号及び第5,369,295号による、ゲート及び拡散容量の減少したフェルミしきい値FET（これは「低容量フェルミFET」又は「タブFET」とも呼ばれる）が、米国特許第5,374,836号による高電流フェルミしきい値FETとともに説明される。米国特許出願第08/351,643号による定域タブ・フェルミFETもまた説明される。米国特許出願第08/505,085号による短チャネル・フェルミFETもまた説明される。より完全な説明についてはこれらの特許及び出願を参照するとよい。詳細については、それらの開示内容を参照する。本発明によるビナルFETについては以下に説明される。 30

（ゲート及び拡散容量の減少したフェルミFET）

ここではフェルミ・タブを含む低容量フェルミFETを概観する。それ以上の詳細については米国特許第5,194,923号及び第5,369,295号を参照することにする。

従来のMOSFETデバイスにはキャリア伝導性を維持するために半導体表面に生成される反転層が必要とされる。この反転層の深さは一般的に100以下である。こうした環境のもと、ゲート容量は基本的にその厚さで分割されたゲート絶縁層の誘電率である。換言すれば、チャネル電荷は表面にあまりに近いので、基板の誘電体特性の効果はゲート容量を決定するのに重要ではない。

もし伝導キャリアがゲート下のチャネル領域内に閉じ込められるならば、ゲート容量は減少することが可能である。このときチャネル電荷の平均的深さにはゲート容量を計算するための基板の誘電率が含まれる必要がある。一般的に、低容量フェルミFETのゲート容量は次式によって与えられる。 40

$$C_g = \frac{1}{\frac{Y_f}{\beta \epsilon_s} + \frac{T_{ox}}{\epsilon_i}} \quad (1)$$

ここで、 $Y_f$ はフェルミ・チャネルと呼ばれる伝導チャネルの深さ、 $\epsilon_s$ は基板の誘電率、そして $\beta$ は表面下のフェルミ・チャネル内を流れる電荷の平均的深さを決定する因子である。 $\beta$ はソースからチャネルに注入されたキャリアの深さに対する依存性に依存する。低容量フェルミFETでは、 $\beta \sim 2$ である。 $T_{ox}$ はゲート酸化物層の厚さ、 $\epsilon_i$ はその誘電 50

率である。

低容量フェルミFETには所定の深さを有するフェルミ・タブ領域が含まれる。このフェルミ・タブ領域は基板の導電型とは反対かつドレイン及びソースの導電型と同一の導電型を有する。フェルミ・タブは基板表面より所定の深さまで下方に拡がり、ドレイン及びソース拡散はこのフェルミ・タブ境界内部のフェルミ・タブ領域内に形成される。フェルミ・タブの好ましい深さはフェルミ・チャネルの深さ $Y_f$ と空乏の深さ $Y_o$ との和である。所定の深さ $Y_f$ と幅 $Z$ を有するフェルミ・チャネル領域はソース拡散及びドレイン拡散の間に拡がる。フェルミ・チャネルの導電率はゲート電極に印加される電圧によって制御される。

ゲート容量はフェルミ・チャネルの深さと、フェルミ・チャネル内におけるキャリア分布によって主に決定され、ゲート酸化物層の厚さには比較的依存しない。拡散容量は[フェルミ・タブの深さと基板内における空乏の深さ $Y_o$ との和]と拡散 $X_d$ の深さとの間の差に反比例的に依存する。拡散の深さはフェルミ・タブの深さ $Y_f$ 未満であることが好ましい。フェルミ・タブ領域のドーパント濃度はフェルミ・チャネルの深さがMOSFET内の反転層の深さの3倍より大きくなることができるよう選択することが好ましい。

よって、低容量フェルミFETには第1の表面を有する第1の導電型の半導体基板と、第1の表面においてその基板内に第2の導電型のフェルミ・タブ領域と、第1の表面においてフェルミ・タブ内に第2の導電型の空間的に隔てられたソース領域及びドレイン領域と、空間的に隔てられたソース領域及びドレイン領域の間に、第1の表面においてフェルミ・タブ領域内に第2の導電型のチャネルが含まれる。チャネルは第1の表面より第1の所定の深さ( $Y_f$ )まで達し、タブ領域はチャネルより第2の所定の深さ( $Y_o$ )まで達する。ゲート絶縁層は空間的に隔てられたソース領域及びドレイン領域の間ににおいて、第1の表面においてその基板上に与えられる。ソース電極、ドレイン電極、及びゲート電極はソース領域及びドレイン領域とゲート絶縁層をそれぞれ電気的に接触させるために与えられる。

少なくとも第1及び第2の所定の深さは、ゲート電極に電界効果型トランジスタのしいき値電圧を印加させた際に、第1の深さにおいて第1の表面に垂直な静電場がゼロとなるように選ばれる。第1及び第2の所定の深さは、ゲート電極に電界効果型トランジスタのしきい値電圧を越えた電圧が印加された際に、第2の導電型のキャリアがチャネル内をソースからドレインに向かって、第1の所定の深さから第1の表面に向かって拡がりながら流れることができるようにも選ばれる。キャリアはフェルミ・タブ領域内に反転層を形成することなく、第1の表面の真下をソースからドレインに向かって流れる。第1及び第2の所定の深さは、ゲート絶縁層に隣接した基板表面において、基板接触子と基板との間の電圧とポリシリコンゲート電極とゲート電極との間の電圧との和に等しく逆の電圧を生み出すことができるようにも選ばれる。

基板がドーピング密度 $N_s$ でドーピングされ、かつ、ケルビン温度T度において固有キャリア濃度 $n_s$ 、誘電率 $\epsilon_s$ を有し、電界効果型トランジスタには電気的に基板を接触させるための基板接触子が含まれ、チャネルが基板表面から第1の所定の深さ $Y_f$ で達し、フェルミ・タブ領域がチャネルより第2の所定の深さ $Y_o$ で達し、フェルミ・タブ領域が $N_s$ の因子倍で与えられるドーピング密度でドーピングされ、ゲート電極にはドーピング密度 $N_p$ でドーピングされた第1の電導率型のポリシリコン層が含まれるとすると、第1の所定の深さ( $Y_f$ )は次式に等しいものとなる。

$$Y_f = \sqrt{\frac{2\epsilon_s}{qN_s\alpha} \frac{kT}{q} \ln\left(\frac{N_p}{N_s}\right)}, \quad (2)$$

ここで $q = 1.6 \times 10^{-19}$ クーロン、 $K = 1.38 \times 10^{-23}$ ジュール/ケルビン (Joule/Kelvin) である。また第2の所定の深さ( $Y_o$ )は次式に等しいものとなる。

$$Y_o = \sqrt{\frac{2\epsilon_s \Phi_s}{qN_s\alpha(\alpha+1)}}, \quad (3)$$

10

20

30

40

50

ここで、 $s$ は $\frac{1}{f} + (kT/q) \cdot L n(\dots)$ に等しく、 $f$ は半導体基板のフェルミ電位である。

(高電流フェルミFETの構造)

図1には、米国特許第5,374,836号によるNチャネル高電流フェルミFETが示されている。Pチャネル・フェルミFETはN及びP領域の導電型を逆転させることによって得られることは当業者には明らかであろう。

図1に示されているように、高電流フェルミFET20は、第1の導電型、ここではP型の、基板表面21aを含む半導体基板21内で製作される。第2の導電型、ここではN型のフェルミ・タブ領域22は基板表面21aにおいて基板21内に形成される。空間的に隔てられたソース領域及びドレイン領域23、24は、それぞれ第2の導電型、ここではN型、を有し、基板表面21aにおいてフェルミ・タブ領域22内に形成される。このソース領域及びドレイン領域23、24を基板表面21aの溝(trench)内に形成することもできることは当業者には明らかであろう。10

ゲート絶縁層26はソース領域及びドレイン領域23、24の間ににおいて、基板表面21aの基板21上にそれぞれ形成される。当業者には明らかなように、ゲート絶縁層は一般的に二酸化シリコンである。しかしながら、窒化シリコン及び他の絶縁体も使用可能である。

ゲート電極は基板21とは反対側のゲート絶縁層26上に形成される。ゲート電極は第1の導電型、ここではP型、の多結晶体シリコン(ポリシリコン)からできたゲート電極であることが好ましい。導体ゲート電極層は一般的に金属ゲート電極層29であって、ゲート絶縁層26とは反対側のポリシリコンゲート電極28上に形成される。ソース電極31及びドレイン電極32も、一般的に金属であって、ソース領域23及びドレイン領域24の上にそれぞれ形成される。20

第1の導電型、ここではP型、の基板接触子33も図示されているようにフェルミ・タブ内又はタブ22の外側のいずれかにおける基板内21に形成される。図示されているように、基板接触子33はドーピングされた第1の導電型、ここではP型、であって、それには比較的重くドーピングされた33aと比較的軽くドーピングされた領域33bが含まれる。基板電極34によって基板への電気的な接触が実現される。

これまでに図1に関して説明された構造は、米国特許第5,194,923号及び第5,369,295号による低容量フェルミFETに対応するものである。これらの出願に既に説明されているように、チャネル36はソース領域及びドレイン領域23、24の間に生成される。図1中において $Y_f$ と記されたチャネルの表面21aからの深さと、図1において $Y_o$ と記されたチャネル底からフェルミ・タブ22の底までの深さは、基板21とタブ領域22とポリシリコンゲート電極28とのドーピングレベルとともに、前記(2)式及び(3)式の関係を使用して高性能の低容量電界効果型トランジスタを与えることができるよう選ばれる。30

また、図1には、第2の導電型、ここではN型、のソース・インジェクタ領域37aがソース領域23に隣接するとともにドレイン領域と対向するように与えられている。ソース・インジェクタ領域によって、キャリアがチャネル36に注入される深さを制御することにより高電流フェルミFETが与えられる。ソース・インジェクタ領域37aはソース領域23とドレイン領域24との間にのみ拡がることができる。図1に示されているように、ソース・インジェクタ領域はソース領域23を囲んでソース・インジェクタ・タブ領域37を形成することができるようになることが好ましい。またソース領域23を、その側面と底面の上をソース・インジェクタ・タブ領域37で完全に取り囲むことができる。あるいはまた、ソース領域23をその側面上でソース・インジェクタ・タブ領域37で取り囲み、底ではソース・インジェクタ・タブ領域37から突き出るようにすることもできる。あるいは更にまた、ソース・インジェクタ領域37aを基板21内で、フェルミ・タブ22と基板21との接合部にまで拡げることもできる。ドレイン・インジェクタ領域38a、好ましくはドレイン領域24を囲むドレイン・インジェクタ・タブ領域38も与えることが好ましい。40

ソース・インジェクタ領域37a及びドレイン・インジェクタ領域38a、又はソース・インジェクタ・タブ領域37及びドレイン・インジェクタ・タブ領域38は、フェルミ・タブ22の比較的低いドーピングレベルとソース23及びドレイン24の比較高いドーピングレベルの中間にあるドーピングレベルでドーピングされた第2の導電型、ここではN型、であることが好ましい。このために、図1に示されているように、フェルミ・タブ22はNで記され、ソース及びドレイン・インジェクタ領域37、38はN+で記され、ソース領域及びドレイン領域23、24はN++で記される。接合型トランジスタはこのようにして形成される。

高電流フェルミFETによって現状のFETの約4倍もの駆動電流が与えられる。ゲート容量は従来のFETデバイスの約半分である。ソース・インジェクタ・タブ領域37のドーピング濃度によってチャネル領域36に注入されるキャリアの深さが、一般的に1000にまで制御される。ソース・インジェクタ・タブ領域37のドーピング濃度は一般的に $2 \times 10^{18}$ であり、注入された主たるキャリアの望ましい最大深さと少なくとも同程度の深さを好ましく持つ。あるいはまた、以下に記述されるように、ソース・インジェクタ・タブ領域37はフェルミ・タブ領域22と同程度の深さにまで達してサブスレショルド漏れ電流を最小化することができる。チャネル36に注入されたキャリア濃度はドレインと対向するソース・インジェクタ領域37aのドーピング濃度を超えることはできないことが示される。ソース・インジェクタ領域37aのドレインと対向する部分の幅は一般的に0.05~0.15μmの範囲内にある。ソース領域及びドレイン領域23、24のドーピング濃度はそれぞれ、一般的に $1 \times 10^{19}$ 以上である。フェルミ・タブ22の深さ $Y_T = (Y_f + Y_o)$ はドーピング濃度が近似的に $1.8 \times 10^{16}$ であれば近似的に2200である。

図1に示されているように、高電流フェルミFET20は基板表面21a上にゲート側壁スペーサ41も含むことができ、これはソース・インジェクタ領域37aに隣接するところからポリシリコンゲート電極28に隣接するところまで拡がる。ゲート側壁スペーサ41はドレイン・インジェクタ領域38aに隣接するところからポリシリコン・ゲート・インジェクタ領域28に隣接するところまでも好ましく拡がっている。特に、図1に示されているように、ゲート側壁スペーサ41はポリシリコン・ゲート電極の側壁28aから拡がり、ソース及びドレイン・インジェクタ領域37a、38aそれぞれの上に横たわる。ゲート側壁スペーサ41はポリシリコン・ゲート電極28を取り囲むようにすることが好ましい。また、以下詳細に説明されるように、ゲート絶縁層26は基板表面21a上でソース・インジェクタ領域37a及びドレイン・インジェクタ領域38a上に張り出し、ゲート側壁スペーサ41もソース・インジェクタ領域37及びドレイン・インジェクタ領域38上に張り出すようにするのが好ましい。

ゲート側壁スペーサ41によって以下に説明する仕方でフェルミFET20のピンチオフ電圧が下がるとともに飽和電流が増大する。ゲート側壁スペーサはゲート絶縁層26の誘電率よりも大きな誘電率を有する絶縁体であることが好ましい。このため、たとえばゲート絶縁層26が二酸化シリコンならば、ゲート側壁スペーサは窒化シリコンであることが好ましい。ゲート絶縁層26が窒化シリコンであるならば、ゲート側壁スペーサは窒化シリコンの誘電率よりも大きな誘電率の絶縁体であることが好ましい。

図1に示されているように、ゲート側壁スペーサ41はソース領域及びドレイン領域23、24それぞれの上に拡がることもでき、ソース電極及びドレイン電極31、32はそれぞれ、ゲート側壁スペーサ領域の拡張部内に形成することができる。従来の電界酸化物又は他の絶縁体領域42によってソース接触子、ドレイン接触子、及び基板の接触子が分離される。ゲート側壁スペーサの外側表面41aは断面図において湾曲しているように図示されているが、三角形の断面積を生じさせる直線的な外部表面あるいは長方形の断面積を生じさせる直角的な外部表面などの、他の形状も使用することも当業者には理解できよう。

(低漏れ電流フェルミしきい値電界効果型トランジスタ)

ここでは図2A及び図2Bを参照して、米国特許第5,374,836号による、短チャ

10

20

30

40

50

ネルを有し、低漏れ電流を生み出すフェルミFETを説明する。これらのデバイスを、以下、「低漏れ電流フェルミFET」と呼ぶことにする。図2Aの低漏れ電流フェルミFET50には第1の導電型、ここではP型、を有するとともに基板21と比較して高い濃度でドーピングされた、底漏れ電流制御領域51が含まれる。このため、図2AにはP+と記されている。図2Bの低漏れ電流フェルミFET60には、フェルミ・タブ22の深さにまで好ましく達する、拡張されたソース及びドレイン・インジェクタ領域37a、38aが含まれる。

図2Aにおいて、底漏れ電流制御領域51はソース領域及びドレイン領域23、24の対向する終端の延長部分の間を基板21を横切って拡がり、かつ、フェルミ・タブ22の深さの上部からフェルミ・タブ22の深さの下部に拡がる。またそれはフェルミ・チャネル36の下方、かつそれと一列に並ぶような位置にある。前記数式との関連に関して言えば、フェルミ・チャネル36から底漏れ電流制御領域51の上端までの深さは $Y_0$ でラベル付けされている。図2AのフェルミFETの残りのは、チャネルがより短くなっているということを除けば、図1のものと同一である。図2Aのデバイスの高電流特性を持たない低漏れ電流低容量の短チャネル・フェルミFETを提供するために、ゲート側壁スペーサ領域41とともに、インジェクタ領域37a及び38aと(又は)インジェクタ・タブ37及び38を省略することは当業者には理解できよう。

底漏れ電流制御領域51によって短チャネル・フェルミFETにおけるドレイン誘導注入が最小化される。すなわち、これらのフェルミFETは、低い拡散空乏容量を維持しながら、近似的に $0.5\mu m$ のチャネル長を有する。たとえば、5ボルトでは、 $3 \times 10^{-13}$ A以下に漏れ電流を維持できる。

底漏れ電流制御領域は(2)式及び(3)式を使用して設計することができる。ここで図2Aと図2Bに示されているように、 $Y_0$ はチャネルから底漏れ電流制御領域の上端部までの深さである。因子 $\alpha$ は底漏れ電流制御領域51のP+ドーピングとフェルミ・タブ22のNドーピングとの間の比である。因子 $\beta$ は底漏れ電流制御領域内、すなわちゲート28の下方で約0.15に設定することが好ましい。ソース領域及びドレイン領域23、24の下では、因子 $\gamma$ は拡散空乏容量を最小化するために1.0に設定する。換言すれば、基板21とフェルミ・タブ22のドーピング濃度はソース領域及びドレイン領域の下方ではほぼ等しい。従って、前記設計パラメータと $0.5\mu m$ のチャネル長に対して、底漏れ制御領域51内のドーピング濃度は近似的に $5 \times 10^{17}$ となり、5ボルトのドレイン又はソース拡散電位が与えられたタブ接合領域で部分的な空乏化を維持(サポート)するには十分な深さである。

図2Bにおいて、底漏れ制御の代替となる設計ではソース・インジェクタ領域37aとドレイン・インジェクタ領域38aの深さがフェルミ・タブの深さ( $Y_f + Y_0$ )まで達することが好ましい。図2Bに示されているように、ソース・インジェクタ・タブ37及びドレイン・インジェクタ・タブ38の全体的な深さはフェルミ・タブの深さまで達するのが好ましい。インジェクタ・タブ37及び38の底とフェルミ・タブ22の底との間の間隔距離はチャネル長の半分未満で、ゼロに近づくことが好ましい。これらの条件のもとでは、インジェクタ領域37及び38は約 $1.5 \times 10^{18} / cm^3$ のドーピング濃度を有する。基板接触子領域33bの深さもフェルミ・タブの深さに近づくようにすることが好ましい。図2BのフェルミFET60の残りは、短チャネルが描かれていること以外は図1のものと同一である。

#### (定域タブ・フェルミしきい値電界効果型トランジスタ)

ここでは図3を参照して、米国出願第08/037,636号による定域タブ・フェルミFETを説明する。Pチャネル・フェルミFETはN及びP領域の導電型を逆転することによって得られることは当業者には理解できよう。図3に示されているように、定域タブ・フェルミFET20は、図1の一様な深さを有するタブ22ではなく定域タブ22が存在するということを除けば、図1の高電流フェルミFET20と同様である。インジェクタ・タブ及びインジェクタ・領域は存在するけれども図示されていない。

図3において、定域タブ22'は、基板表面21aから空間的に隔てられたソース領域及

10

20

30

40

50

びドレイン領域 23、24 の少なくとも一方の下方にそれぞれ第 1 の所定の深さ  $Y_1$  まで達する。定域タブ 22' は、また、基板表面 21a からチャネル領域 36 の下方に第 2 の所定の深さ  $Y_2$  まで達する。本発明によれば、定域タブ 22' を形成するのに、 $Y_2$  は  $Y_1$  とは異っており、また  $Y_2$  は  $Y_1$  未満であることが好ましい。別の言い方をすれば、タブ 22' と基板 21 との間の接合が、ソース領域及びドレイン領域 23 と 24 から離れるように、チャネル下のタブ FET 基準によって指図される位置よりも下方に押し下げられ、ソースあるいはドレインの拡散容量が減少する。こうして定域タブ・フェルミ FET が低電圧で動作することが可能となる。タブ 22' がソース領域 23 又はドレイン領域 24 のどちらかの下方に輪郭が描かれるだけだと、非対称的なデバイスが生み出されることは当業者には理解されよう。しかしながら、ソース領域及びドレイン領域の下方にタブの輪郭が描かれる対称的なデバイスが好ましく形成される。

第 2 の所定の深さ  $Y_2$  は米国特許第 5,194,923 号と米国特許第 5,369,295 号による低容量フェルミ FET (タブ FET) の基準に基づいて決定される。これらの基準は深さ  $Y_f$  及び  $Y_o$  を決定し、それらが一緒になって第 2 の所定の深さ  $Y_2$  を形成するものであって、既に説明がなされている。

第 1 の所定の深さ  $Y_1$  は第 2 の所定の深さ  $Y_2$  よりも大きくなるように選ばれる。第 1 の所定の深さも、ゼロ電圧がソース接触子 31 とドレイン接触子 32 にそれぞれ印加された際に、第 1 の所定の深さ  $Y_1$  とソース及び / 又はドレイン領域の間のタブ領域 22' が空乏化されるように選ばれるのが好ましい。かくして、 $Y_n$  でラベル付けされた領域全体はゼロのソース・バイアス又はドレイン・バイアスのもとで全体的に空乏化されるのが好ましい。この基準に基いて、 $Y_1$  が次式で決定される。

$$Y_n = \sqrt{\frac{kT_{LTD}}{q} \left( \frac{N_{sub} N_{tub}}{N_i^2} \right) \frac{2\varepsilon_s}{qN_{sub}} \frac{1}{\left( 1 + \frac{N_{sub}}{N_{tub}} \right)}} \quad (4)$$

ここで  $N_{sub}$  は基板 21 のドーピング濃度、 $N_{tub}$  は定域タブ 22' のドーピング濃度である。

(短チャネル・フェルミ FET)

図 4 は米国特許出願第 08/505,085 号による短チャネル・N チャネル・フェルミ FET 20 を示した図である。P 短チャネル・フェルミ FET は N 及び P 領域の導電型を逆転させることによって得られることは当業者には理解できよう。図 4 に示されているように、フェルミ・タブ 22' は基板表面 21a より第 1 の深さ ( $Y_f + Y_o$ ) まで達する。空間的に隔てられたソース領域及びドレイン領域 23、24 はそれぞれ、領域 23a と 24a によって図示されているように、タブ領域の中に位置する。しかしながら、ソース領域及びドレイン領域 23、24 は更にそれぞれ基板表面 21a よりタブの深さを越えたところまで拡がる。ソース領域及びドレイン領域 23、24 は更にまた横方向に基板表面 21a に沿って、タブ領域を越えたところまで拡がる。

チャネルの深さ  $Y_f$  とチャネルからのタブの深さ  $Y_o$  は、ゲート電極がしきい値電位にあるときに、基板表面から深さ  $Y_f$  までのチャネル 36 内において基板表面に垂直な静電場を最小化するように選ばれる。既に説明されたように、これらの深さはまた、半導体基板 21 のフェルミ電位の 2 倍にある電界効果型トランジスタのしきい値電圧を生み出すことができるようにも好ましく選ばれる。これらの深さはまた、ゲート電極に電界効果型トランジスタのしきい値電圧を越える電圧が印加された際に、第 2 の導電型のキャリアが深さ  $Y_f$  から基板表面 21a に向かって拡がりながら、ソース領域からドレイン領域までチャネル内を流れることができるようにも選ばれる。キャリアはチャネル領域内を、チャネル内に反転層を生成することなく基板表面の下をソース領域からドレイン領域まで流れる。従って、最適ではないが、図 4 のデバイスではなお、オフ状態でのゲート容量がかなり減少するとともに、従来の MOSFET トランジスタよりかなり高い飽和電流を生成することができる。ドレイン容量は標準的な MOSFET デバイスと同様となる。

図 4 において、ソース領域及びドレイン領域が基板表面に垂直な深さ方向にタブ領域を越

10

20

30

40

50

えて拡がるとともに、基板表面 21a と平行に横方向にも拡がっていることが理解できる。しかしながら、寄生側壁容量 (parasitic sidewall capacitance) を減少させるためには、タブ 22 が横方向にソース領域及びドレイン領域を越えて拡がることが好ましい。その結果、ソース領域及びドレイン領域はただ深さ方向にタブを通って突き出る形となる。

図 5 には米国特許出願第 08 / 505,085 号による短チャネル・フェルミ FET の第 2 の実施形態が図示されている。トランジスタ 20 は、ソース及びドレイン拡張領域 23b 及び 24b がそれぞれ基板表面 21a において基板 21 内にソース領域及びドレイン領域 23、24 にそれぞれ隣接する様に、しかもチャネル 36 内まで拡がるように与えられていること以外、図 4 のトランジスタ 20 に類似している。

図 5 に示されているように、ソース及びドレイン拡張領域 23b、24b はそれぞれが、ソース領域及びドレイン領域 23、24 の濃度と近似的に同じ濃度で重くドーピング ( $N^{++}$ ) されている。拡張 23b、24b は従来の MOSFET の軽くドーピングされたドレイン構造ほど軽くはドーピングされてはいないことは理解できよう。むしろ、それらはソース領域及びドレイン領域と同じドーピング濃度でドーピングされており、漏れを減少させ、飽和電流を改善することができる程度に実際的であることが好ましい。

ソース及びドレイン拡張領域 23b、24b によって前記電荷共有によるドレイン電圧に対する感度が減少する。残念ながら、図 5 のデバイスは一般的に図 1 及び図 2 の十分に囲まれたソース領域及びドレイン領域ほど低い容量を示さない。ソース及びドレイン拡張領域 23b、24b の大きさを維持するため、ソース領域及びドレイン領域そのものに対して使用されるような軽く、速く移動するドーパントではなく、ヒ素又はインジウムのような重く、遅く移動するドーパントをソース及びドレイン拡張領域に対して使用することが好ましいことは当業者には理解できよう。

#### (ドレイン電界終止領域を有する短チャネル・フェルミ FET )

以下、本発明による、ビナル FET とも呼ばれる、短チャネル・フェルミしきい値電界効果型トランジスタの構造を説明する。当業者であれば、P 型チャネル・ビナル FET は N 型領域と P 型領域の導電型を逆転させることによって得られることは理解できよう。

図 6 及び図 7 はそれぞれビナル FET の第 1 及び第 2 の実施態様を示している。図 6 に示されているように、ビナル FET 60 は第 1 の導電型、ここでは P 型、の半導体基板 21 を備える。当業者であれば、半導体基板 21 は主要な半導体基板上に形成された一層以上のエピタキシャル層を含み、それによって基板表面 21a が主要となる半導体素材の外側表面ではなくエピタキシャル層の外側表面となるように構成してもよいことは理解できよう。

なお図 6 において、第 2 の導電型 (ここでは N 型) の第 1 のタブ領域 62 は半導体基板 21 の表面 21a において基板内に形成され、基板表面 21a より基板内に第 3 の深さ  $Y_3$  まで拡がる。第 1 の導電型 (ここでは P 型) の第 2 のタブ領域 64 は第 1 のタブ領域 62 内に含まれる。第 2 のタブ領域 64 は基板表面 21a より基板 21 内に第 3 の深さ  $Y_3$  未満の第 2 の深さ  $Y_2$  まで拡がる。第 1 のタブ領域 62 内にある第 2 のタブ領域 64 は第 1 のタブ領域を越えて横方向に拡がってもよい。第 2 のタブ領域 64 は以下で説明されるドレイン電界終止 (DFT (Drain Field Terminating)) 領域を形成する。第 2 の導電型 (ここでは N 型) の第 3 のタブ領域 66 は第 2 のタブ領域 64 に含まれる。第 3 のタブ領域 66 は基板表面 21a より基板 21 内に第 2 の深さ  $Y_2$  未満の第 1 の深さ  $Y_1$  まで拡がる。第 3 のタブ領域 66 は以下で説明されるようにエピタキシャル層内に形成されるのが好ましい。

なお図 6 を参照すれば、第 2 の導電型 (ここでは N+ 型) の空間的に隔たったソース領域 23 及びドレイン領域 24 がそれぞれ第 1 のタブ領域 62 内に形成され、基板表面 21a より基板 21 内に第 4 の深さ  $Y_4$  まで拡がる。図 6 に示されているように、第 4 の深さ  $Y_4$  は第 1 の深さ  $Y_1$  よりも大きい。図 6 に示されているように、第 4 の深さ  $Y_4$  は第 2 の深さ  $Y_2$  よりも大きくもあるが、しかし第 3 の深さ  $Y_3$  よりも小さい。従って、ソース拡散及びドレイン拡散 23、24 はそれぞれ第 3 及び第 2 のタブ領域 66、64 を貫通し、第 1 の

10

20

30

40

50

タブ領域 6 2 内に拡がる。図 7 に示されているようなビナル F E T 6 0 ' の第 2 の実施態様において、第 4 の深さ  $Y_4$  は第 1 の深さ  $Y_1$  よりも大きく、しかし第 2 の深さ  $Y_2$  より小さい。その結果、ソース拡散及びドレイン拡散 2 3、2 4 は第 3 のタブ領域 6 6 を貫通し、第 2 のタブ領域 6 4 内に拡がるが、第 1 のタブ領域 6 2 には達しない。

図 6 及び図 7 それぞれのビナル F E T ドラインジスタ 6 0 及び 6 0 ' はゲート絶縁層 2 6 と、第 1 の導電型（ここでは P 型）の多結晶シリコン層 2 8 を含むゲート電極も含む。ソース接触子、ゲート接触子及びドレイン接触子 3 1、2 9、3 2 もまた既に説明したように含まれる。基板接触子は表面 2 1 a の反対側に示されているが、以前の実施態様におけるもののように表面 2 1 a に隣接するように形成してもよい。

図 6 及び図 7 のビナル F E T 6 0 及び 6 0 ' はソース領域及びドレイン領域 2 4 の間に拡がる、基板 2 1 内の層という観点からも説明してよい。この観点から見ると、第 3 のタブ 6 6 は基板表面においてその基板内に、ソース領域 2 3 からドレイン領域 2 4 の間に拡がるとともに基板表面から基板内に第 1 の深さ  $Y_1$  まで拡がる、第 2 の導電型の第 1 の層 6 6 a を生み出す。第 2 のタブ領域 6 4 は基板内に、ソース領域 2 3 からドレイン領域 2 4 の間に拡がるとともに基板内に基板表面からの第 1 の深さ  $Y_1$  から第 2 の深さ  $Y_2$  まで拡がる、第 1 の導電型の第 2 の層 6 4 a を生み出す。第 2 の層 6 4 a は以下説明されるようなドレイン電界終止手段として作用する。第 1 のタブ 6 2 は基板内に、ソース領域 2 3 からドレイン領域 2 4 の間に拡がるとともに基板内に基板表面からの第 2 の深さ  $Y_2$  から第 3 の深さ  $Y_3$  まで拡がる、第 2 の導電型の第 3 の層 6 2 a を生み出す。

このように見ると、図 6 の実施態様では、第 3 の層 6 2 a は、領域 6 2 b で示されているようにソース底 2 3 a からドレイン底 2 4 a まで拡がってもいる。図 7 の実施態様では、第 2 及び第 3 の層 6 4 a、6 2 a は、それぞれ領域 6 4 b 及び 6 2 b で示されているように、両方ともソース底 2 3 a からドレイン底 2 4 a まで拡がっている。

図 6 及び図 7 のビナル F E T は、もともとのタブ内のカウンタドープされた埋め込まれたタブ 6 4 を含むタブ F E T と見做してもよい。あるいはその代わりに、ビナル F E T はチャネル領域 6 6 a の真下に第 1 の導電型の埋込層 6 4 a を含むタブ F E T と見做してもよい。以下に詳細に説明されるように、第 2 の層 6 4 a を含む第 2 のタブ 6 4 は、印加されたドレインバイアスによってキャリアがソース領域からチャネル領域内又はチャネル領域の下に注入されることを抑制することによってソース領域をシールドするためのドレイン電界終止手段 (D F T) として作用する。従って、第 2 のタブ 6 4 と第 2 の層 6 4 a はドレイン電界終止 (D F T (Drain Field Termination)) 領域とも呼ばれる。

#### (ビナル F E T の動作)

以下、図 6 及び図 7 のビナル F E T ドラインジスタ 6 0、6 0 ' の動作を説明する。ビナル F E T はフェルミ F E T と同様に、チャネル内で垂直方向の低電界をなお許容しながら、過度のドレイン誘導障壁降下 (D I B L (Drain Induced Barrier Lowering)) を抑制する。加えて、ビナル F E T はよりかなり高い移動度を実現し、ソース・ドレイン間接合容量も減少させる。ビナル F E T は、寄生的な高容量なしに合理的なソース及びドレインの深さも実現する、非常に薄い、非常に低いアルファ値を有するフェルミ F E T ドラインジスタと見做してよい。

ビナル F E T デバイスにはドレイン電界終止 (D F T) 領域が第 2 のタブ 6 4 又は第 2 の層 6 4 a の形態で含まれる。D F T 領域は（特に図 7 の構造に対して）ソース領域 2 3 に対する遮蔽（シールド）として作用し、それによって、バイアスが接触子 3 2 に印加された結果としてのキャリアのソース領域から第 1 の層 6 6 a に対応するチャネルの中又は下への注入が減少し、かつ好ましく抑制される。

第 1 のタブ 6 2 は D F T 領域（深さ  $Y_2$ ）の底縁（bottom edge）を構成して、それが無かつたらデバイスしきい値を増大させるかもしれない D F T 領域の余分なドーパントの効果を減少させることを助ける。第 1 のタブ 6 2 はソース領域及びドレイン領域に付随する容量をかなり低下させる場合もある。この容量は図 6 のトランジスタ 6 0 のソース領域及びドレイン領域の双方に存在する。図 7 のトランジスタ 6 0 ' では、初期的な（ゼロのバイアスが印加された）ソース容量はソース：D F T 領域（2 3 : 6 4 b）間接合によって決

10

20

30

40

50

定されるが、しかしソース電位が増大すると、残存するDFTのドーパント原子はソース領域の下の領域で空乏化され、接合容量が急速に降下する。

ドレイン誘導キャリア注入 (Drain induced carrier injection) によって短チャネル・フェルミFETデバイスが、チャネルがより短くなるような理想的な状態から離れてしまった。既に説明したように、フェルミFETにおける望まれない漏れを減少させるために、タブ領域は薄くされ、そして／又は、基板ドーピングレベルが増大され、それによってトランジスタのしきい値の減少も引き起こされる。

チャネル長が $1 / 2$ ミクロンより短くなるように継続的に小型化するには、動作電圧をより低くする必要があるが、しかし、ソースとドレイン間の距離をより小さくすればソース拡散におけるドレイン電界の強さが一層増大する。動作電圧を低下させることによって、しきい値電圧の有効なオーバヘッドが減少し、それによって短チャネル・フェルミFETさえ高いしきい値又は高い漏れのどちらかによる性能損失に悩まされ始める。10

それとは対照的に、本発明によるビナルFETによれば、ソース領域及びドレイン領域の間ににおける第1の層66a及び第2(DFT)の層64aから生み出される、低垂直電界、低しきい値のフェルミFET型領域が提供される。DFT領域はソース拡散及びドレイン拡散の間の漏れを減少させ、かつ好ましく抑制させることができるほど十分に深い。DFT領域は、ソース領域及びドレイン領域の間の領域が正常な動作条件の下で十分に空乏化されないように構成されることが好ましい。空乏化されないドーパント原子はドレイン電界終止サイトとして作用し、ドレイン電界がソース電極に到達することを抑制する。

図8は、図6及び図7のビナルFETに対する、ソース及びドレイン間での基板表面21aに垂直な8-8'ラインに沿った、正味のドーピングプロフィールをグラフ的に示している。図8はまた、正味のドーピングプロフィールを生成するのに使用できる、個々のドーパント要素(ホウ素、リン)の分布もグラフ的に示している。図9A及び図9Bは、ソース領域又はドレイン領域内での、基板表面に垂直な9A-9A'ライン及び9B-9B'ラインにそれぞれ沿った、正味のドーピングプロフィールを示している。図9Aは、図6のビナルFET60に対する正味のドーピングプロフィールを示しており、図9Bは、図7のビナルFET60'に対する正味のドーピングプロフィールを示している。20

極めて短いデバイスにおいて、薄い第3のタブ62によって低い漏れ及び／又は低いしきい値が実現される。従って、初期的なビナルFETデバイスは $0.25\mu m$ の引込チャネル(drawn channel)と、60のゲート酸化物と、2.5ボルトの最大ドレイン電圧とを使ってシミュレーションされた。30

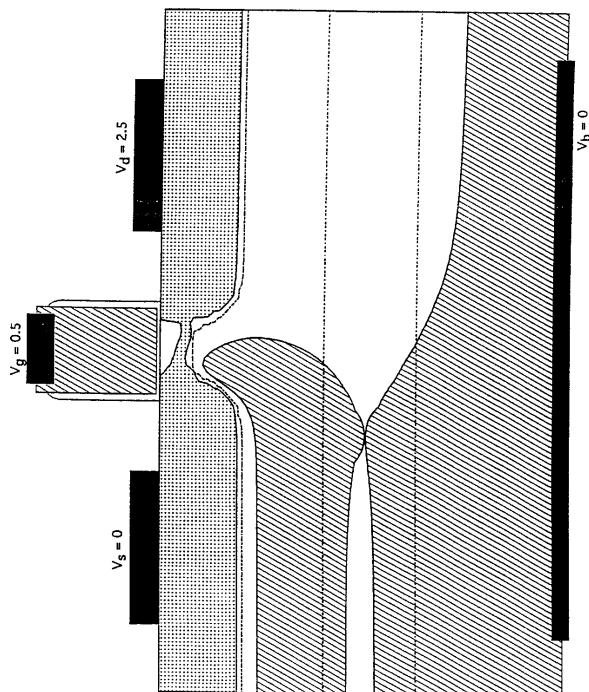

図10はPISCES2シミュレーションにおけるビナルFETの断面図である。図10は移動キャリアについて基板の空乏化された領域を示している。 $1 \times 10^{10} / cm^3$ より大きな電子及びホールが示されている。接触子の位置も示されている。シミュレーションの条件は $V_s = V_b = V_g = 0$ ボルト及び $V_d = 2.5$ ボルトである。 $V_s$ 、 $V_b$ 、 $V_g$ 、 $V_d$ はそれぞれソース、基板、ゲート、及びドレインにそれぞれ印加される電圧である。

図10は図7のNチャネル・ビナルFETの空乏化されていないシリコンを示している。図7のビナルFET60'は図6のビナルFET60と比較して、与えられた回線幅としきい値電圧に対して漏れが低下する電位を有する。この性能の改善に対して不利な点もあり、それは図6によるデバイスよりもかなり薄くなった空乏領域を有する、ソース:DFT間接合によってドレイン容量がやや高くなる場合があるということである。図10において、ソース電極は左側にある。ソース電極、ゲート電極、及び基板電極はゼロボルトにあり、そしてドレイン電極は2.5ボルトにある。トランジスタは「オフ」状態にある。断面図の中の細かい平行線を引かれた領域は自由ホール濃度が $1 \times 10^{10}$ ホール/ $cm^3$ より大きな領域に対応する。ドットのある影の領域は電子濃度が $1 \times 10^{10}$ 個/ $cm^3$ より大きな領域に対応する。それゆえ、影のない領域は移動電荷が十分に空乏かされたと仮定される。すなわち、キャリア濃度は固有レベル $n_i = 1.45 \times 10^{10}$ 個/ $cm^3$ 未満である。PN接合は点線で表されている。図10には3つ存在する。40

図10に示されているように、たとえチャネル領域のドーピングがソース領域及びドレイン領域のドーピングに一致しても、DFT構造のドーピング及びスペーシングは、ソース50

領域とドレイン領域との間の領域が自由ホール過多 (aexcess of free holes) を含むように決められる。これによってチャネル容積において電界終止サイトとして作用するのに必要とされる自由キャリアが供給され、漏れを増大させかねないソース領域から注入されるキャリアの数が大きく減少される。また、ドレイン領域の下の空乏領域にも注目する。第1のタブ構造62は全体の空乏幅を大きく拡大し、接合容量をかなり低下させる。

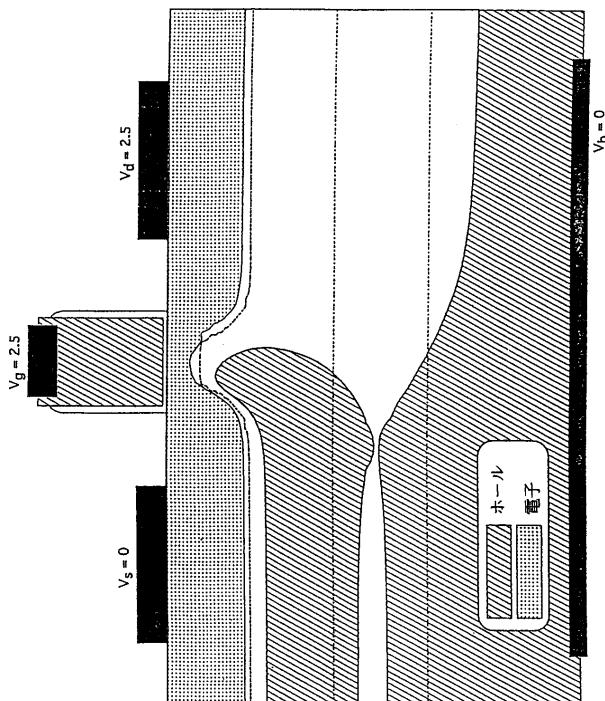

図11は、ゲート電極のバイアスが近似的にしきい値電圧（約0.550ボルト）にあることを除けば、図10と同一視される。図11には、 $1 \times 10^{13} / \text{cm}^3$ より大きな電子と、 $1 \times 10^{10} / \text{cm}^3$ より大きなホールが示されている。これらの条件下で、チャネル領域はちょうど第3のタブ：DFT間接合の近くに形成される。ソース拡散とドレイン拡散との間の第3のタブにある影の領域はおおよそ中性のシリコンである。この領域におけるキャリアは印加されたドレインバイアスだけの影響を受ける。図12も、 $V_g = 2.5$ ボルトに設定されたゲート電極上のゲートバイアスを除けば、図9と同一視される。 $1 \times 10^{15} / \text{cm}^3$ より大きな電子と、 $1 \times 10^{10} / \text{cm}^3$ より大きなホールが示されている。この図は飽和状態にあるトランジスタを示している。チャネル領域の大部分は、ソース領域から注入されたキャリア過多となっている。これらの伝導キャリアは印加されたドレインバイアスと、ゲートバイアスのしきい値より上の部分 ( $V_g - V_t$ ) の両方の影響を受ける。

DFT領域64aのドーピングには3つの条件が含まれることが好ましい。最初に、DFTはその上のチャネル領域66aを十分に空乏化するのに正確に十分な少数電荷を供給する。この電荷は次式で与えられる。

$$N_{cdep} = \bar{N}_c Y_1 \quad (5)$$

ここで  $N_c$  はチャネル領域における平均ドーピング（濃度）を表す。 $Y_1$  はチャネルの深さである。しかしながら、ソースとドレイン領域が十分に空乏化されるのに十分な電荷が存在することが好ましいという他の制約が存在する。各領域は次式のように DFT の体積を空乏化する。

$$W_{DFT} = \sqrt{\frac{2\epsilon_s N^+ \Phi_b + V_a}{qN_{DFT}(N_{DFT} + N^+)}} , \text{ ここで、 } \Phi_b = \frac{kT}{q} \ln \left( \frac{N^+}{N_{DFT}} \right) \quad (6)$$

ここで、 $N_{DFT}$  及び  $N^+$  はそれぞれ DFT 領域 64a のドーピング及びソース領域及びドレイン領域 23、24 のドーピングを表す。また、 $V_a$  は拡散（ソース又はドレインのどちらか）に印加された基板に関する電圧を表す。上記 (5) 式で要求される電荷が、最大電位にある拡散によって形成される接合を満足するのに必要とされたものと比較して小さいことを示すことができると仮定すると、近似的な最小 DFT は有効幅 ( $L_{eff}$ ) の近似的に 40 % を消費するであろう濃度と仮定してよい。

(6) 式の  $W_{DFT}$  を  $0.4 * L_{eff}$  に設定し、 $V_a$  を  $V_d$  に設定すると、(6) 式は次式のように  $N_{DFT}$  について解くことができる。

$$N_{DFT} = \frac{2\epsilon_s (\Phi_b + V_d)}{q(0.4L_{eff})^2} \quad (7)$$

(7) 式は、 $Y_1$  から  $Y_2$  の近似的に 150 %までの、ソース拡散とドレイン拡散との間の DFT 構造のドーピングレベルに対する最小必要条件を表している。PISCES2 シミュレーションは、DFT 構造の最大ドーピングレベルに対応する深さが近似的に  $Y_2$  であるときに、漏れが非常に低いデバイスを示した。ソース拡散及びドレイン拡散の下の空乏化が残存する DFT 電荷を十分に空乏化し、かつ、付加的な拡散電位が、最低位タブの下の基板電荷上で近似的に 0.5 ボルトに終わり始めるように、(1.5  $Y_1$  から  $Y_2$  までの) DFT 構造の底部分のプロフィールと第1のタブ構造の密度と幅を設定することによって、ソース容量及びドレイン容量を最適化してよい。

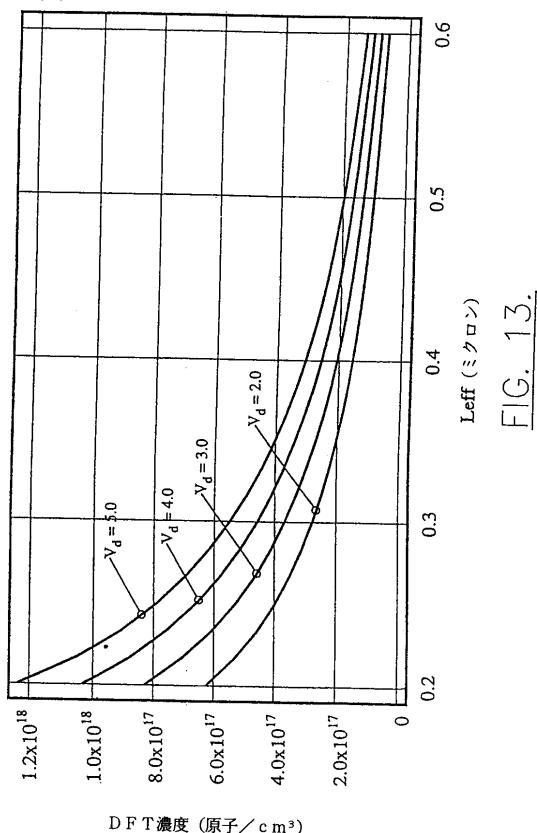

図13は(7)式によるDFTの最上部の好ましいドーピング（濃度）を示した図である。動作電圧が 2 から 5 ボルトでの、 $0.2 \mu\text{m}$  から  $0.6 \mu\text{m}$  までのチャネル長が示されおり、SUPREM4 シミュレーションと PISCES2 シミュレーションの結果と一致

10

20

30

40

50

することが示されている。

第1のタブ62は深さY<sub>2</sub>から深さY<sub>3</sub>まで拡がり、DFT領域によって空乏化されるように設計されるべきであるという点で第3のタブ66に類似している。第1のタブ62の幅を増大させることは接合容量に対して正の効果を与えるが、しかしこれに最大の望ましい深さに到達することが好ましいことが示される。第1のタブ66の幅が広がるとついには、ソース及びドレイン電極の印加バイアスによって生み出される空乏領域内に基板21がもはや含まれなくなるほど、下側の接合をソース領域及びドレイン領域23、24の底23aと24aから十分に遠くに移動させてしまう。加えて、もし第1のタブ濃度が、基板21とDFT領域による空乏化がもはや第1のタブ内ですべての多数キャリアを空乏化しないならば、トランジスタは、漏れレベルが高くなり、基板結合が乏しくなり、ラッチアップしやすくなる場合がある。10

こうしたことから、第1のタブに対する実用的な厚さの目標は、経験的には、第2の層(DFT)64aと近似的に同一の厚さである。この厚さによって基板とDFT構造の下縁とによる完全な空乏化以上のが許容される。

図10から分かるように、第1のタブの厚さ及びドーピング密度は、(8)式( $N_{DFT}$ と $N_{FT}$ はそれぞれDFT層64aと第1のタブ62のドーピング濃度を表す)で与えられるDFT(第1のタブ間接合)による空乏化された幅と、(9)式で与えられる第1のタブ(基板間接合)による空乏化幅との和が全体の第1のタブ幅よりも大きくなるように、調整されることが好ましい。ここで(8)式と(9)式は次式で表される。20

$$W_{DFT:FT} = \sqrt{\frac{2kT\epsilon_s N_{DFT} L_D \left(\frac{N_{DFT}}{N_{FT}}\right)}{Q^2 N_{FT} (N_{FT} + N_{DFT})}} \quad (8)$$

及び

$$W_{Sub:FT} = \sqrt{\frac{2kT\epsilon_s N_{Sub} L_D \left(\frac{N_{Sub}}{N_{FT}}\right)}{Q^2 N_{FT} (N_{FT} + N_{Sub})}} \quad (9)$$

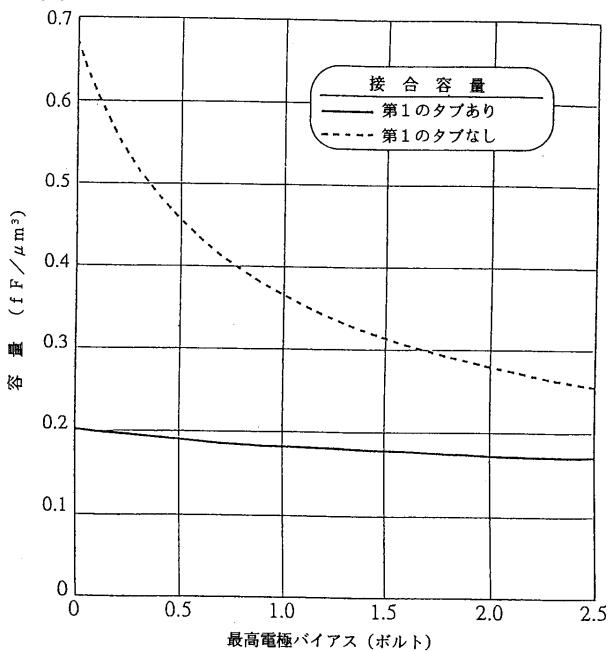

この結果、化学的にN型の領域(ピナルFETのNチャネル版)が少数キャリア(Nチャネル変形に対してはホール)過多によって正常に占められることとなる。その領域はあたかもP型であるかのように電気的に振る舞い、図14で示されたような滑らかな容量曲線を生じさせる。これによって、タブ領域における余分な接合による寄生的ラッチアップが回避され、ソース拡散及びドレイン拡散の電圧降下が改善される。30

含まれる接合は険しいものであるが、一般的に「階段(step)」接合ではないことに注意すべきである。それゆえ、全空乏化幅は次式に従って各接合で分離される。

$$N_d x_n = N_a x_p \quad (10)$$

ここで、 $N_a$ と $N_d$ は接合のP型側とN型側におけるアクセプタ濃度及びドナー濃度である。 $x_p$ と $x_n$ はそれぞれ接合のP型及びN型側における空乏化領域の幅である。第1のタブの幅を、(10)式のみによる、DFT:第1のタブ間接合と基板:第1のタブ間接合によって生み出された空乏化幅の和の75%に、それらの接合の第1のタブ側で設定する。次に(8)式、(9)式、(10)式、及び75%幅の仮定を組み合わせ、かつ再整理して、次式で与えられる、 $N_{DFT}$ 、 $N_{FT}$ 、及び基板ドーピングレベル $N_{sub}$ に対する第1のタブの最大幅を定義することができる。40

$$Y_3 - Y_2 = \frac{0.75}{N_{FT}} \times \left( \sqrt{\frac{4kT\epsilon_s (N_{DFT} + N_{FT})}{Q^2 N_{DFT} N_{FT}} L_D \left(\frac{N_{DFT} N_{FT}}{D_i^2}\right)} + \sqrt{\frac{4kT\epsilon_s (N_{Sub} + N_{FT})}{Q^2 N_{Sub} N_{FT}} L_D \left(\frac{N_{Sub} N_{FT}}{D_i^2}\right)} \right) \quad (11)$$

この(11)式が、PISECES2のような装置シミュレータを使用して第1のタブの厚さ及びドーピングレベルを望ましい容量及び漏れ特性を実現するように調節するための解析のための出発点を好ましく定義することは当業者には理解できよう。50

## (ビナルFETの製造工程)

次に、図15Aから15Eを参照して、図6のビナルFETトランジスタ60を形成するための好ましい工程を説明する。図7のビナルFETはソースおよびドレイン領域の埋め込みの深さを減少させることによって得られることは理解できよう。相補的なトランジスタは導電型を逆転させることによって得られる。

一般的に、製造方法は、第1の導電型の半導体基板内に、第2の導電型の第1のタブ領域と、第1のタブ領域内に第1の導電型の第2のタブ領域を形成するステップを含む。第1及び第2のタブ領域に隣接するように、半導体基板上に第2の導電型の層がエピタキシャル的に形成される（本来の位置にドープされ、又は続いて第2の導電型にドープされる）。次に第2の導電型のエピタキシャル層内と第2のタブ領域内に、空間的に隔たった第2の導電型のソース領域及びドレイン領域が形成される。ソース領域及びドレイン領域は第1のタブ内に拡がってもよい。10

次に、図15Aを参照する。製造工程はN型又はP型の基板から始まり、従来のようにマスク72を使ってP型井戸（型領域）70を埋め込む。図15Bを参照する。従来のスクリーン酸化が実行されてスクリーン酸化物74が形成され、そして第1のタブ62のイオン注入と第1のタブ62内の第2のタブ（DFT）64のイオン注入とが実行される。第1及び第2の型のイオンの従来的な注入が使用される。第2のタブは第1のタブよりも以前に注入してよい。次に活性化アニールが実行される。

次に、図15Cを参照する。スクリーン酸化物74は取り除かれ、そしてエピタキシャル層76のエピタキシャル的な堆積が実行される。その後、図15Dのように、第2の導電型のイオンを使用して第3のタブ66が層76内に埋め込まれる。マスクされた、又はマスクされない埋め込みを使用してよい。エピタキシャル的な堆積を行ってそれによって第2の層をエピタキシャル的に堆積させながら、エピタキシャル層を第2の導電型に同時にドープする際に層76の本来の位置でのドーピングを使用してよいことも理解される。20

その後、図15Eのように、従来の技術を使用して、ゲート酸化物26が形成され、そしてポリシリコンゲート28が形成され、ドープされる。ソース領域及びドレイン領域23、24はその後、ポリシリコンゲート28をマスクとして使用することによって埋め込まれる。そして次にソース接触子、ドレイン接触子、及び基板接触子が与えられ、図6のトランジスタ60が形成される。

図15Aから図15Eまでの工程で重要なことは、シリコンの薄いエピタキシャル層76を第3のタブ66を形成するために利用することである。当業者であれば、非常に類似した垂直プロフィールがエピタキシーの使用又は複雑なく得られ、動作可能なビナルFET装置がこの方法で構成されることは理解できよう。しかしながら、エピタキシーはチャネル領域66a内の伝導キャリア移動度を最大化させるのに使用されることが好ましい。従来的なフェルミFET及び、より程度が少なく「埋め込まれたチャネル」のFETトランジスタのように、ビナルFETの垂直電界が低下することによってシリコン表面上における伝導キャリアによる有効移動度の損失が減少する。フェルミFET及びビナルFETは、伝導キャリアを、それらが多数キャリア型にある領域内に流すことによって更に有効移動度を改善させ、正味のドーピング濃度は従来のMOS-FETよりも低下する。ビナルFETはチャネル領域66aをカウンタドープする必要をなくすことによって、有効移動度を更に改善させることができる。3040

正味のキャリア移動度は一般的に、フォノン散乱、格子欠陥、表面の粗さ、そして全体的な不純物濃度を含むいくつかの異なる機構の結果である。電界効果型デバイスのソース領域とドレイン領域との間を流れる伝導キャリアは、いくつかの異なるタイプの散乱を経験することになる。各散乱タイプはデバイスのさまざまな構造上の詳細による確率集合（probability set）と印加電圧を伴う。各機構は散乱事象間の平均時間 $\tau$ を有する。一つの時間間隔の間に発生する散乱の全確率はそのとき次式で表されるような個々の散乱機構の確率の組合せで与えられる。

$$\frac{dt}{\tau_T} = \sum_i \frac{dt}{\tau_i} \quad (12)$$

10

20

30

40

50

ここで $i$ は各散乱機構を表す。それゆえ、散乱事象間の全平均時間は組成原因による個々の確率の最小のものよりも小さい。移動度は次式によって散乱確率と関係付けられる。

$$\mu = \frac{q}{m^*} \tau \quad (13)$$

こうして、全移動度は次式で与えられるように各個別の散乱機構に付随する移動度と関係する。

$$\frac{1}{\mu} = \sum_i \frac{1}{\mu_i} \quad (14)$$

散乱寿命に注意すると、全キャリア移動度は組成原因による個々の確率の最小のものよりも小さい。個々の機構移動度の一つが他のものよりも小さくなるとき、そときそれは主要な機構となり、他にものの相対的寄与を減少させる。

10

現行のサブミクロンデバイスにおいて、ドーパント原子による散乱はそうした主要な機構となっている。極短チャネルトランジスタは、デバイスをターンオフするのに必要なチャネルのドーピングレベルが制限因子となるポイントに到達している。図16は、3つの主なドーパント要素の全不純物濃度の関数として、300におけるシリコンのキャリア（電子及びホール）移動度を示している。これは、リチャード S.ミラー（Richard S. Miller）氏とセドア I.カミン（Theodore I.Kamins）氏著の「集積回路のためのデバイスエレクトロニクス（第2版）（Device Electronics for Integrated Circuits, Second Edition）」（1986年）の33ページから引用された。0.25 μmのチャネル長を有する表面チャネルMOSFETデバイスにおいて、 $2 \times 10^{18} \text{ cm}^{-3}$ 以上の全体的なチャネルドーピングが共通して見られる。このため、より長いデバイスに使用されるより低い濃度と比較して、性能の実質的な損失が生じる。

20

図11を再び参照する。 $2 \times 10^{18} \text{ cm}^{-3}$ のチャネルドーピングに付随する移動度 $\mu$ は $235 \text{ cm}^2 / \text{V} \cdot \text{sec}$ である。チャネル長がサブミクロン範囲内にあるNチャネルビナルFETでは伝導が起こる第3のタブ領域の正味のN型ドーパント濃度が $5.0 \times 10^{16}$ から $2.0 \times 10^{17}$ までであることが要求される。第3のタブを形成するためのイオン注入を使用するには、DFT領域（約 $4 \times 10^{17}$ のP型）を上記正味のN型レベルまでカウンタドープすることが必要とされるのが一般的である。非ドーピングに関係した原因を無視し、かつタブのドーピングが $5.0 \times 10^{16}$ に設定されると仮定すると、P型ドーパントが $4.0 \times 10^{17}$ かつN型ドーパントが $4.5 \times 10^{17}$ （カウンタドープされて $+5.0 \times 10^{16}$ ）と仮定している図13から得られる正味のチャネル移動度は、 $320 \text{ cm}^2 / \text{V} \cdot \text{sec}$ となる。この移動度は上記MOSFETよりも良いが、より良い性能が可能である。特に、図15Aから図15Eに説明された工程を利用すると、DFT領域64aのP型ドーピングは第3のエピタキシャル的に形成されたタブ66内では無視できる存在となって、第3のタブの正味のかつ全体のドーピングが $5 \times 10^{16}$ となることが許される。こうして、移動度は $900 \text{ cm}^2 / \text{V} \cdot \text{sec}$ まで大きく増大する。

30

（高性能MOSFET）

ビナルFETのドレン電界終止領域はカウンタドープされたチャネルを有する従来のMOS-FETの設計にも適用できる。図17及び図18は第2（DFT）のタブ64及び第1のタブ62を使用する従来のMOS-FETの2つの実施態様を示している。図17及び図18は第3のタブ66を失ったビナルFETとも見做してもよい。あるいはその代わりに、図17及び図18は第1のタブ62が付加された従来のMOS-FETと見做してよい。ビナルFETのように一般的には実行しないが、短チャネルMOSFETの改善性能が図17及び図18の構造から得られる。

40

（ビナルFETの設計基準のまとめ）

以下、本発明によるビナルFETの設計基準をまとめておく。ここに使用される数式が一定のドーパントプロフィールと完全に層の境目がはっきりしたトランジスタを仮定しているとき、以下のようなシミュレーション及び/又は実験データはデバイスを最適化するのに使用されることが好ましい。

$Y_3 - Y_2$ ：第1のタブ領域の垂直の広がりで、DFT、基板、及び第1のタブのドーピン

50

グ密度の関数として(11)式において定義される。

$Y_2 - Y_1$ : DFT領域の垂直の広がりである。このパラメータに対しての幅広い範囲がトランジスタ性能に影響を与えることなく可能である。最適化の有用な出発点は $Y_1$ の値の150%である。

$Y_1$ : 第2のタブ領域の垂直の広がりである。より高い動作電圧( $V_d$ )又はより狭いチャネル( $L_{eff}$ )に対して一般的により小さな数が必要とされ、幅広く可変でもある。最適化の有用な出発点は次式で与えられる。

$$Y_1 = \frac{5.5(L_{eff})}{\sqrt{V_{d\ max}}} \quad (15)$$

10

$N_{DFT}$ : DFT領域の平均ドーピング濃度は、有効チャネル長 $L_{eff}$ の関数として(7)式で定義された、最大ドレイン電圧の関数である。

$N_{FT}$ : 第1のタブ領域の平均ドーピング濃度は、(11)式で定義された、 $N_{DFT}$ 、 $N_{sub}$ 、及び基板濃度の関数である。

$N_{TT}$ : 第3のタブ領域又は「フェルミタブ」の平均ドーピング濃度は一般的に長チャネル( $> 1 \mu m$ )に対して $1 \times 10^{16}$ に設定され、チャネルが短くされるにつれ一般的に増大する。例えば $0.25 \mu m$ において、 $N_{TT}$ は近似的に $1 \times 10^{17}$ である。漏れ電流のシミュレーションを使用して漏れに対してこの濃度を「調整(tune)」するのに使用してよい。

$N_{poly}$ : ポリシリコンのドーピング(濃度)は一般的にしきい値電圧において弱い役割を果たすが、工程の安定性や複雑さの理由から、それは通常、約 $1 \times 10^{20}$ に置かれる。

(使用される変数の表)

$C_g$ : ゲート容量

すなわち、ゲート電極の $dQ/dV$ で与えられる。

$Y_f$ : 伝導チャネルの深さ

ここで、伝導チャネルは、トランジスタが完全にオンになったときに伝導キャリアがソースとドレインとの間を流れるところの、ゲート酸化物下の領域である。

: キャリアの深さ因子

すなわち、 $Y_f$ をキャリアの平均的深さに関係付ける数学的な係数である。

$s$ : 基板の誘電率

30

$\epsilon_s$ : ポリシリコンのゲート電極と基板との間の絶縁誘電体の誘電率

$T_{ox}$ : ポリシリコンのゲート電極と基板との間の絶縁誘電体の厚さ

$Z$ : ソースからドレインへのラインに垂直なFETトランジスタの幅

$Y_o$ : フェルミタブの深さ

すなわち、基板表面から、ゲート電極下の、フェルミタブと井戸型領域の間に形成された冶金学的な接合までの距離である。

$Y_1$ : 基板表面から、ゲート電極下の、第2のフェルミタブ(第2の導電型の表面層)とDFT領域の間に形成された冶金学的な接合までの、シリコン表面に垂直な距離

$Y_2$ : 基板表面から、ゲート電極下の、第1のフェルミタブ(第2の導電型の底層)とDFT領域の間に形成された冶金学的な接合までの、基板表面に垂直な距離

40

$Y_3$ : 基板表面から、ゲート電極下の、第1のフェルミタブ(第2の導電型の最下層)と井戸型領域又は基板との間に形成された冶金学的な接合までの、基板表面に垂直な距離

$N_{DFT}$ : ( $N_{64}$ )とも呼ばれる、ドレイン電界終止(DFT)領域の平均的なドーピングレベル

$N_{FT}$ : ( $N_{62}$ )とも呼ばれる、第1のタブ領域(図6、図7における62a)の平均的なドーピングレベル

$V_a$ : トランジスタの任意のソース又はドレインターミナルに印加される電圧

$V_a$ 、 $V_d$ 、 $V_g$ 、 $V_s$ : ソース、ドレイン、ゲート、又は基板にそれぞれ印加される電圧

$b$ : p-n接合のビルトイン電位((6)式参照)

$W_{DFT:FT}$ : DFT領域(64a)と第1のタブ領域(62a)が出会うp-n接合によって

50

形成された、空乏領域の垂直の広がり

$W_{FT:sub}$ ：基板（21）と第1のタブ領域（62a）が出会うp-n接合によって形成された、空乏領域の垂直の広がり

$L_{eff}$ ：ソース拡散の縁からドレイン拡散の縁までの、基板表面に平行な最短距離

これは、 $L_{66a}$ で表される。

$L_o$ ：電流方向に平行に測定されたポリシリコンゲート電極の幅

これは、 $L_2$ で表される。

本図面及び本明細書において、本発明の好ましい実施の一般形態が開示してきた。そこには特定の用語が使用されてきたが、それらは一般的かつ記述的な意味合いにおいてのみ使用されているものであり、何ら限定を意図するものではない。本発明のおよぶ範囲は以下に述べられる請求の範囲によって明確にされる。

10

【図1】

FIG. 1.

【図2A】

FIG. 2A.

【図2B】

FIG. 2B.

【 四 3 】

21

FIG. 3.

【図4】

FIG. 4.

【 図 5 】

21

FIG. 5.

【図6】

【図7】

【図8】

【図9 A】

FIG. 9 A.

【図 9B】

FIG. 9B.

【図 10】

FIG. 10.

【図 11】

FIG. 11.

【図 12】

FIG. 12.

【図 13】

【図 14】

Figure 14

【図 15A】

【図 15B】

【図 15C】

【図 15D】

【図 15E】

【図 16】

【図 17】

FIG. 16.

【図 18】

FIG. 18.

---

フロントページの続き

(74)代理人

弁理士 有原 幸一

(72)発明者 デネン,マイケル・ウイリアム

アメリカ合衆国、27615 ノース・キャロライナ、ローリー、ウィンドジャマー・ドライブ

8820

審査官 川村 裕二

(56)参考文献 特開平07-312423 (JP, A)

特表平07-503582 (JP, A)

特開昭62-219966 (JP, A)

特開平07-297295 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78