(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6305030号

(P6305030)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 31/08 (2006.01)H01L 27/146

H01L 31/00A

A

請求項の数 16 (全 13 頁)

(21) 出願番号 特願2013-242363 (P2013-242363)

(22) 出願日 平成25年11月22日 (2013.11.22)

(65) 公開番号 特開2015-103629 (P2015-103629A)

(43) 公開日 平成27年6月4日 (2015.6.4)

審査請求日 平成28年11月17日 (2016.11.17)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】光電変換装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

MOSトランジスタを含む周辺回路部と、光電変換素子及び前記光電変換素子で生じた信号を増幅する増幅素子が配されたウェル、及び前記ウェルに所定の電圧を供給するためのコンタクトを有する画素回路部と、を備える光電変換装置の製造方法であって、

前記光電変換素子、前記増幅素子、前記コンタクトが配される部分、及び前記MOSトランジスタのゲート電極を覆う誘電体膜を形成する工程と、

前記誘電体膜における前記光電変換素子を覆う部分と前記増幅素子を覆う部分とを覆い、前記周辺回路部分と前記コンタクトが配される部分とを露出させるレジストを形成する工程と、

前記誘電体膜における前記光電変換素子を覆う部分及び前記増幅素子を覆う部分をレジストによって保護して残存させつつ、前記ゲート電極の側面に前記誘電体膜の残存物によりサイドスペーサが形成され且つ前記コンタクトが配される部分の前記誘電体膜に開口が形成されるように、前記誘電体膜をエッチングする工程と、

を有し、

前記コンタクトを前記開口に形成することを特徴とする光電変換装置の製造方法。

## 【請求項 2】

前記コンタクトの形成は、前記開口を介して前記ウェルに不純物を注入することで、前記ウェルよりも不純物濃度の高い不純物領域を形成する段階を含むことを特徴とする請求項1に記載の光電変換装置の製造方法。

**【請求項 3】**

前記MOSトランジスタのドレインを形成するための、前記不純物領域を形成するための不純物と同一導電型の不純物の注入を、前記不純物領域を形成するための不純物の注入と並行して行うことを特徴とする請求項2に記載の光電変換装置の製造方法。

**【請求項 4】**

前記不純物領域を形成するための不純物のドーズ量は、 $5 \times 10^{14}$  [ions/cm<sup>2</sup>] 以上、 $5 \times 10^{16}$  [ions/cm<sup>2</sup>] 以下であることを特徴とする請求項2又は3に記載の光電変換装置の製造方法。

**【請求項 5】**

前記コンタクトの形成は、前記開口形成後の前記誘電体膜上に、前記画素回路部および前記周辺回路部に渡って絶縁膜を形成し、10

前記絶縁膜の前記不純物領域となる領域の上に位置する部分にコンタクトホールを形成し、前記コンタクトホールを介して前記領域に不純物を注入する段階を含むことを特徴とする請求項4に記載の光電変換装置の製造方法。

**【請求項 6】**

前記コンタクトホールは前記開口よりも幅が小さいことを特徴とする請求項5に記載の光電変換装置の製造方法。

**【請求項 7】**

前記不純物領域を形成する際に注入された不純物とは反対の導電型の不純物を、前記コンタクトホールを介して前記不純物領域となる領域に注入する段階を含むことを特徴とする請求項5又は6に記載の光電変換装置の製造方法。20

**【請求項 8】**

前記不純物領域となる領域の上に前記コンタクトホールを形成する前又は後に、前記絶縁膜の前記MOSトランジスタのドレインとなる領域の上に位置する部分にコンタクトホールを形成する段階を含むことを特徴とする請求項5乃至7のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 9】**

前記コンタクトの形成は、前記不純物領域に接続するコンタクトプラグを形成する段階を含むことを特徴とする請求項2乃至8のいずれか1項に記載の光電変換装置の製造方法。30

**【請求項 10】**

前記不純物領域は、素子分離用の絶縁物で囲まれていることを特徴とする請求項2乃至9のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 11】**

前記サイドスペーサを形成する前に、前記MOSトランジスタのドレインを形成するための不純物の注入と、前記增幅素子を形成するための不純物の注入とを並行して行うことを特徴とする請求項1乃至10のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 12】**

前記誘電体膜は酸化シリコン層と窒化シリコン層とを含む複層膜であることを特徴とする請求項1乃至11のいずれか1項に記載の光電変換装置の製造方法。40

**【請求項 13】**

前記誘電体膜は水素を含む窒化シリコン層を有することを特徴とする請求項1乃至12のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 14】**

前記開口を覆う誘電体膜を形成した状態で、前記MOSトランジスタをシリサイド化することを特徴とする請求項1乃至12のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 15】**

前記増幅素子はMOSトランジスタであり、前記誘電体膜をエッチングする工程において、前記誘電体膜の、前記増幅素子として機能する前記MOSトランジスタの上に配されている部分はエッチングされないことを特徴とする請求項1乃至14のいずれか1項に記50

載の光電変換装置の製造方法。**【請求項 1 6】**

前記画素回路部は、前記光電変換素子を複数有し、

前記コンタクトは、平面視において、前記複数の光電変換素子の少なくとも 2 つの間に

あることを特徴とする請求項 1 乃至 1 5 のいずれか 1 項に記載の光電変換装置の製造方法

。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明はMOSトランジスタを含む光電変換装置の製造方法に関する。

10

**【背景技術】****【0 0 0 2】**

光電変換装置はデジタルスチルカメラ、ビデオカムコーダーを中心とする撮像装置に用いられ、需要が広がっている。特に近年、デジタルスチルカメラで用いられる光電変換装置は、APS-C サイズや 35 mm フィルムサイズというような大きなサイズが広く用いられるようになっている。これらの光電変換装置として MOS 型光電変換装置が用いられている。このような光電変換装置では、画素回路部において発生されるノイズを低減することが必要となっている。

**【0 0 0 3】**

光電変換装置の出力信号にシェーディングと呼ばれる濃淡が生じることがある。光電変換素子に光が入射して生じた光電荷は、電圧に変換されて電気信号となる。電圧としての電気信号は、半導体の持つ基準電位に対して電気信号分を上乗せされている。このために、撮像面内の位置によって半導体の基準電位が異なる値をとると、それに応じて光電変換装置に入射される光の強度が一定でも光電変換装置の出力信号が異なる値をとることになる。この結果、光電変換装置の出力の画像に現れる濃淡をシェーディングと呼ぶ。前述のように近年需要を伸ばしている大きなサイズの撮像面を有するセンサにおいては、シェーディングにより画像性能が大きく損なわれる問題がある。このシェーディングを低減する方法として、画素部の共通ウェルに基準電圧を供給するためのウェルコンタクトを設ける方法がある（特許文献 1）。

20

**【先行技術文献】**

30

**【特許文献】****【0 0 0 4】**

【特許文献 1】特開 2006 - 073737 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 5】**

ウェルコンタクトの形成方法としては、BPSG 等の層間絶縁膜形成後にコンタクトホールを形成した後にコンタクトホールを介して不純物を注入する方法が考えられる。しかしこの方法では不純物注入後に高温のアニール処理を行うことができないため、ウェルコンタクトに注入した不純物の熱拡散および活性化が十分に行われず、ウェルコンタクトの抵抗が高くなる問題があげられる。

40

**【0 0 0 6】**

本発明の目的は、画素回路部のウェルコンタクトを形成する上で有利な光電変換装置の製造方法を提供する。

**【課題を解決するための手段】****【0 0 0 7】**

本発明の光電変換装置の製造方法は、MOSトランジスタを含む周辺回路部と、光電変換素子及び前記光電変換素子で生じた信号を增幅する増幅素子が配されたウェル、及び前記ウェルに所定の電圧を供給するためのコンタクトを有する画素回路部と、を備える光電変換装置の製造方法であって、前記光電変換素子、前記増幅素子、前記コンタクトが配さ

50

れる部分、及び前記MOSトランジスタのゲート電極を覆う誘電体膜を形成する工程と、前記誘電体膜における前記光電変換素子を覆う部分と前記増幅素子を覆う部分とを覆い、前記周辺回路部分と前記コンタクトが配される部分とを露出させるレジストを形成する工程と、前記誘電体膜における前記光電変換素子を覆う部分及び前記増幅素子を覆う部分をレジストによって保護して残存させつつ、前記ゲート電極の側面に前記誘電体膜の残存物によりサイドスペーサが形成され且つ前記コンタクトが配される部分の前記誘電体膜に開口が形成されるように、前記誘電体膜をエッチングする工程とを有し、前記コンタクトを前記開口に形成することを特徴とする。

**【発明の効果】**

**【0008】**

本発明によれば、ノイズが抑制された光電変換装置を製造することができる。

10

**【図面の簡単な説明】**

**【0009】**

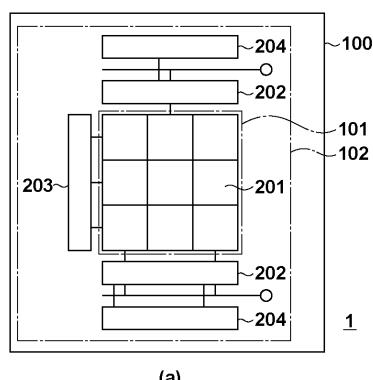

【図1】本発明に係る光電変換装置の例を示す模式的平面図である。

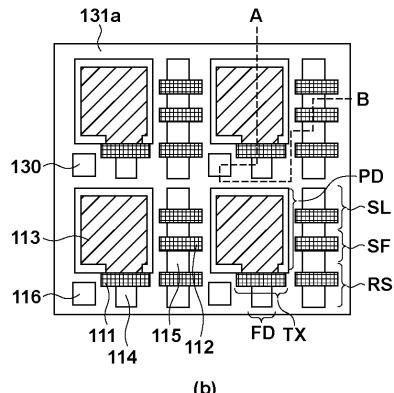

【図2】本発明に係る光電変換装置の例を示す模式的断面図である。

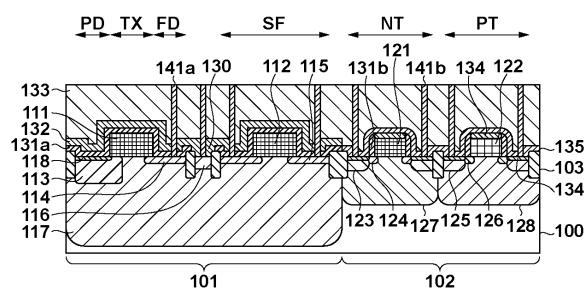

【図3】本発明に係る光電変換装置の例を示す製造プロセスフローの模式的断面図である。

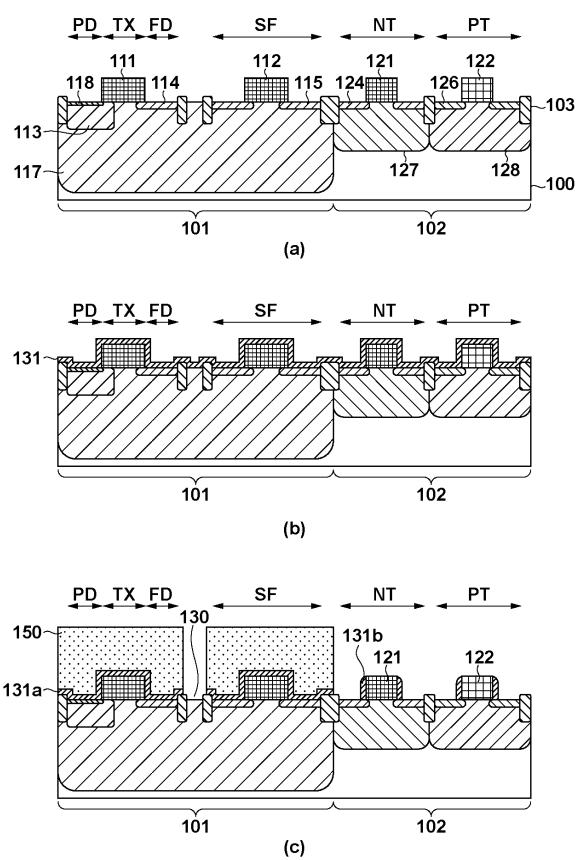

【図4】本発明に係る光電変換装置の例を示す製造プロセスフローの模式的断面図である。

【図5】本発明に係る光電変換装置の例を示す製造プロセスフローの模式的断面図である。

20

**【発明を実施するための形態】**

**【0010】**

以下、本発明の実施の形態について実施例を挙げ、図面を用いて詳細に説明する。本発明は各実施例に限定されるものではなく、発明の趣旨を超えない範囲で、組み合わせ、変更可能である。なお、以下の説明および図面において、複数の図面に渡って共通の構成については共通の符号を付している。そのため、複数の図面を相互に参照して共通する構成を説明し、共通の符号を付した構成については適宜説明を省略する。

**【0011】**

図1(a)に光電変換装置の平面配置図の一例を示す。光電変換装置1は画素回路201が配された画素回路部101と周辺回路(202~204)が配された周辺回路部102とを含む。これら画素回路部101と周辺回路部102は単一の半導体基板100の上に設けられている。

30

**【0012】**

図1(b)に画素回路部101の4つの画素回路201に関する平面配置図の一例を示す。画素回路201は、光電変換素子PDと光電変換素子PDから信号を読み出す読み出し回路とからなる一つの単位である。このような画素回路201が複数配置されている領域が画素回路部101である。画素は、フォトダイオードなどの光電変換素子PD及びこの光電変換素子PDから出力線へ画像信号を読み出すための素子の集合の最小単位である。画素回路201は、光電変換素子PDで生じた電荷の量に基づく信号を生成する増幅素子SFを有する。このような光電変換装置1は、画素増幅型の撮像装置を構成できる。この素子集合に含まれるのは、例えば、転送素子TX、容量素子FD、増幅素子SF、リセット素子RSである。本例では、さらに、選択素子SLも素子集合に含まれる。隣接する光電変換素子PDにおいて、上記素子を共有することも可能であるが、この場合にも光電変換素子PDの信号を読み出すための素子集合の最小単位により画素を定義づけることができる。なお、位相差検出方式の焦点検出を実現するために、1つの画素に複数の光電変換素子PDを設け、画素からの信号を、複数の光電変換素子PDからの信号を合算したものとして扱うこともできる。

40

**【0013】**

図1(a)に示すように、周辺回路部102には信号処理回路202、垂直シフトレジ

50

スタ 2 0 3、水平シフトレジスタ 2 0 4 が含まれる。信号処理回路 2 0 2 は、画素回路 2 0 1 から読み出された信号の増幅や画素のノイズを C D S 处理により除去する回路である。また 2 次元に配置された画素から行単位で複数並列に読み出された信号を、外部に出力するためにシリアルな信号に変換するための回路であっても良い。垂直シフトレジスタ 2 0 3 は画素回路部 1 0 1 に配された画素回路 2 0 1 を行単位で選択して、駆動するための駆動回路である。水平シフトレジスタ 2 0 4 は信号処理回路 2 0 2 を駆動して信号処理回路 2 0 2 から信号を外部に転送するための回路である。光電変換装置 1 において A D 変換を行なう場合には、A D 変換回路が周辺回路に含まれても良い。

#### 【 0 0 1 4 】

まず、本発明に係る光電変換装置 1 について図 2 により説明する。図 2 は図 1 ( b ) の A - B 線における模式的断面図である。本実施例においては、画素回路部に配される素子としてフォトダイオードである光電変換素子 P D と M O S 型ゲートである転送素子 T X 、 M O S 型電界効果トランジスタ ( M O S F E T ) である増幅素子を例に説明する。また各実施例においては特定の素子のみを例にあげて説明するが、画素回路 2 0 1 に配される他の素子に実施例の構造を適用することも可能である。画素回路 2 0 1 を構成するトランジスタを画素トランジスタと総称する。画素トランジスタは、M O S 型電界効果トランジスタ ( M O S F E T ) に限らず接合型電界効果トランジスタ ( J F E T ) であってもよいし、バイポーラトランジスタであってもよい。一方、周辺回路を構成するトランジスタを周辺トランジスタと総称する。周辺トランジスタは M O S 型電界効果トランジスタ ( M O S F E T 、 M O S トランジスタ ) を含む。周辺回路部 1 0 2 には抵抗素子や容量素子など、 M O S F E T 以外の素子を配することもできる。以下、M O S 型電界効果トランジスタのことを M O S トランジスタと称する。なお、M O S 型電界効果トランジスタは絶縁ゲート型電界効果トランジスタと同義であり、ゲート絶縁膜の種類は酸化膜に限定されることはない。

#### 【 0 0 1 5 】

光電変換装置 1 は画素回路部 1 0 1 と周辺回路部 1 0 2 を含む。ここでは、画素回路部 1 0 1 のうち、光電変換素子 P D 、転送素子 T X 、増幅素子 S F の断面構造を示している。そして、周辺回路部 1 0 2 に示されている周辺トランジスタは、信号処理回路 2 0 2 、垂直シフトレジスタ 2 0 3 、水平シフトレジスタ 2 0 4 、 A D 変換回路などのいずれかの回路を構成するものを示している。

#### 【 0 0 1 6 】

シリコンなどの半導体基板 1 0 0 に S T I または選択酸化法 ( L O C O S ) などにより形成された素子分離領域 1 0 3 が配置されている。画素回路部 1 0 1 には、転送 M O S ゲートのゲート電極 1 1 1 、増幅素子 S F のゲート電極 1 1 2 が形成されている。第 1 導電型の不純物領域 1 1 3 は光電変換素子 P D の蓄積領域として機能する。第 1 導電型は、光電変換素子 P D が信号として取り扱う光電荷 ( 信号電荷 ) を多数キャリアとする導電型に一致する導電型であり、信号電荷として電子を用いる場合には N 型となる。半導体基板 1 0 0 の表面と不純物領域 1 1 3 の間には光電変換素子 P D を埋め込み構造とするための第 2 導電型の不純物領域 1 1 8 が形成されている。第 2 導電型は、第 1 導電型とは反対の導電型であり、信号電荷として電子を用いる場合には P 型となる。第 1 導電型の不純物領域 1 1 4 は容量素子 F D の浮遊拡散領域として機能する。転送 M O S ゲートをゲート、不純物領域 1 1 3 をトランジスタのソース、不純物領域 1 1 4 をトランジスタのドレインとみなして、このトランジスタを転送トランジスタと称することもできる。第 1 導電型の不純物領域 1 1 5 は、シングルドレイン構造を有する増幅素子 S F のドレインやソースを構成する。増幅素子のドレインには電源電位が与えられる。増幅素子 S F のソースには選択素子 S L を介して電流源が接続されており、増幅素子 S F はソースフォロワ回路を構成している。不純物領域 1 1 4 はリセット素子 R S のドレインに接続されている。また、不純物領域 1 1 4 は、増幅素子 S F のゲート電極 1 1 2 に接続されている。リセット素子 R S のソースにはリセット電位が与えられ、リセット素子 R S のゲートを O N にすることで、不純物領域 1 1 4 およびゲート電極 1 1 2 の電位がリセットされる。選択素子 S L を用いず

10

20

30

40

50

に増幅素子 S F の電源電位を画素選択用の電位としてもよい。また、リセット電位と電源電位を共用してもよい。

#### 【 0 0 1 7 】

第 2 導電型の不純物領域 1 1 6 には、第 2 導電型のウェル 1 1 7 の電位（ウェル電位）を規定するために基準となる電位が与えられる。ウェル電位は例えば接地電位である。不純物領域 1 1 6 はウェル電位を規定するためのウェルコンタクトの少なくとも一部を構成する。不純物領域 1 1 6 は、光電変換素子 P D の信号電荷として電子を用いる場合にはウェル 1 1 7 と同じ P 型の不純物領域である。不純物領域 1 1 6 は素子分離領域 1 0 3 を構成する素子分離用の絶縁物で囲まれて形成されており、光電変換素子 P D の活性領域や増幅素子 S F の活性領域とは別の活性領域に形成されている。しかし、不純物領域 1 1 6 を光電変換素子 P D の活性領域や増幅素子 S F の活性領域と同じ活性領域に設けることもできる。1 つの画素回路 2 0 1 につき 1 つのウェルコンタクトを設けることができるが、複数の画素回路 2 0 1 につき 1 つウェルコンタクトを設けることもできる。10

#### 【 0 0 1 8 】

画素回路部 1 0 1 には、光電変換素子 P D と増幅素子 S F を覆う誘電体膜 1 3 1 a が設けられている。誘電体膜 1 3 1 a はさらに転送素子 T X 、容量素子 F D ( 不純物領域 1 1 4 ) 、リセット素子 R S および選択素子 S L を覆っている。詳細には、誘電体膜 1 3 1 a は転送素子 T X のゲート電極 1 1 1 の上面、増幅素子 S F のゲート電極 1 1 2 の上面を覆っている。同様に誘電体膜 1 3 1 a は、リセット素子 R S のゲート電極および選択素子 S L のゲート電極を覆っている。酸化シリコン層および窒化シリコン層を含む複層膜から構成される誘電体膜 1 3 1 a は、両者で光電変換素子 P D の表面での入射光の反射を低減する反射防止膜として機能することができる。なお、誘電体膜 1 3 1 a は窒化シリコン層と酸化シリコン層の組み合わせ以外の組み合わせの複層膜であってもよいし、単層膜であってもよい。誘電体膜 1 3 1 a は、不純物領域 1 1 6 の上に位置する開口 1 3 0 を有している。画素回路部 1 0 1 を覆う酸化シリコン層の单層膜である絶縁体膜 1 3 2 は、周辺回路部 1 0 2 においてシリサイド電極を形成する際にシリサイド、例えばコバルトシリサイドなどによる金属汚染から画素回路部 1 0 1 を保護する役割を果たす。絶縁体膜 1 3 2 は窒化シリコン層の单層膜であってもよいし、複層膜であってもよい。20

#### 【 0 0 1 9 】

周辺回路部 1 0 2 には、第 1 導電型の M O S ドラジスタと第 2 導電型の M O S ドラジスタを含む複数の周辺トランジスタが配されている。周辺回路部 1 0 2 において、第 1 導電型の M O S ドラジスタ ( N T ) と第 2 導電型の M O S ドラジスタ ( P T ) が C M O S 回路を構成する場合もある。ゲート電極 1 2 1 は第 1 導電型の周辺トランジスタのゲート電極、ゲート電極 1 2 2 は第 2 導電型の周辺トランジスタのゲート電極である。周辺トランジスタは L D D 構造を有する。すなわち、第 1 導電型の周辺トランジスタのソースとドレインは、第 1 導電型の不純物領域 1 2 3 と、不純物領域 1 2 3 よりも不純物濃度が低い第 1 導電型の不純物領域 1 2 4 とを含んで構成される。同様に、第 2 導電型の周辺トランジスタのソースとドレインは、第 2 導電型の不純物領域 1 2 5 と、不純物領域 1 2 5 よりも不純物濃度が低い第 2 導電型の不純物領域 1 2 6 とを含んで構成される。30

#### 【 0 0 2 0 】

ゲート電極 1 2 1 、 1 2 2 の側面には、酸化シリコン層と窒化シリコン層の積層体であるサイドスペーサ 1 3 1 b が形成されている。サイドスペーサ 1 3 1 b は酸化シリコン層と窒化シリコン層の積層膜をエッティングして残った残存物で形成されている。周辺トランジスタのゲート電極の表面とソースおよびドレインの表面はシリサイド化されている。シリサイド化には、たとえばコバルトシリサイドが用いられる。周辺回路部 1 0 2 を覆う酸化シリコン層と窒化シリコン層の積層膜である絶縁体膜 1 3 5 は窒化シリコン層、酸化シリコン層の組み合わせの複層膜に限らず、他の組み合わせの複層膜もしくは单層膜であってもよい。

#### 【 0 0 2 1 】

絶縁膜 1 3 3 は、画素回路部 1 0 1 および周辺回路部 1 0 2 を覆う。絶縁膜 1 3 3 の上50

面は平坦である。絶縁膜 133 の上には不図示の配線層が設けられており、絶縁膜 133 はこの配線層に対する層間絶縁膜として機能する。画素回路部 101 には画素回路 201 の各素子の不純物領域やゲート電極に接続されたコンタクトプラグ 141a 等の導電体が設けられている。コンタクトプラグ 141a は絶縁膜 133、絶縁体膜 132 および誘電体膜 131a を貫通して設けられている。誘電体膜 131a は、コンタクトプラグ 141a のためのコンタクトホールを形成する時のエッチングストップとして機能する。周辺回路部 102 には周辺トランジスタの不純物領域やゲート電極に接続されたコンタクトプラグ 141b 等の導電体が設けられている。コンタクトプラグ 141b は絶縁膜 133 および絶縁体膜 135 を貫通して設けられている。絶縁体膜 135 は、コンタクトプラグ 141b のためのコンタクトホールを形成する時のエッチングストップとして機能する。コンタクトプラグ 141a、141b は、絶縁膜 133 のエッチングにより形成されたコンタクトホールにタンゲステンなどの導電体を充填して形成されている。画素回路部 101 の誘電体膜 131a と、周辺回路部 102 のサイドスペーサ 131b を形成する誘電体膜とを同じ構成とした場合には、誘電体膜を光電変換装置 1 の表面に一度に形成することができるので、製造コストを低く抑えることができる。

10

#### 【0022】

画素回路部 101 のウェル 117 には第 2 導電型の不純物領域 116 が設けられている。ウェル 117 にはコンタクトプラグ 141a を介して不純物領域 116 に基準電位（接地電位）が与えられる。画素回路部 101 にて基準電位を供給することで、画素回路 201 每の基準電位のばらつきが低減され、シェーディングの発生を抑制することができる。

20 また、MOS トランジスタのソースとドレインは低不純物濃度の不純物領域で構成されるシングルドレイン構造とする。このため、ソース、ドレインに高不純物濃度の不純物領域を含む LDD 構造と比べ、ホットキャリアによるトランジスタ特性の劣化を低く抑えることができる。これは特に、MOS トランジスタが微細化された場合には顕著となる。ホットキャリアによるトランジスタ特性の劣化はゲート長と電源電圧に強く依存し、短いゲート長や高い電源電圧で劣化が大きくなる特性を持つ。本実施例による画素回路部のシングルドレイン構造の MOS トランジスタは、ゲート長が短い微細な MOS トランジスタであっても高い電源電圧で特性の劣化を抑えることができる。

#### 【0023】

一方、周辺回路部 102 において、周辺トランジスタは高不純物濃度の不純物領域及び低不純物濃度の不純物領域からなる LDD 構造のソース、ドレインを有する MOS トランジスタである。そのため、高駆動能力とホットキャリア耐性を両立させることができる。特に画素回路部と比べて周辺回路部においては、画素回路部よりも高速での動作が要求されるため、周辺トランジスタが高駆動能力を有することが重要となる。そのため、本実施例のように画素回路部の MOS トランジスタと周辺回路部の MOS トランジスタの電界緩和領域の構造を異ならせることが重要となる。

30

#### 【0024】

また、画素回路部 101 の誘電体膜 131a はコンタクトホールを開口する異方性ドライエッチングの際のエッチングストップとして用いてもよい。これによりコンタクトが位置合わせずれにより素子分離領域上へ乗り上げた場合でも、コンタクトが素子分離領域や側面のウェル 117 と接触することが無い。このため低不純物濃度の不純物領域 114、115 とウェル 117 間のリーク電流を抑制できる。したがってコンタクトと素子分離領域との距離を短くすることができ、素子の微細化が可能となる。

40

#### 【0025】

次に、実施例に係る光電変換装置 1 の製造方法について説明する。図 3 (a) ~ 図 5 (i) に製造方法のフローを示す。尚、説明のため図 3 (a) ~ 図 5 (i) では画素回路部 101 と周辺回路部 102 を隣接させて描いている。

#### 【0026】

まず、図 3 (a) の工程について説明する。シリコンなどの半導体基板 100 に、STI または選択酸化法 (LOCOS) などにより素子分離領域 103 を形成する。また、半

50

導体基板 100 に素子を形成するための第 1 導電型 (N 型) のウェル 128、第 2 導電型 (P 型) のウェル 117 および 127 を形成する。画素を形成する画素回路部 101 には光電変換素子 PD の第 1 導電型 (N 型) の不純物領域 113 を形成する。また、光電変換素子 PD を埋め込み構造とするために、光電変換素子 PD の表面に第 2 導電型 (P 型) の不純物領域 118 を形成する。また、半導体基板 100 の上にゲート電極 111、112 を形成する。さらに、容量素子 FD を成す浮遊拡散領域 (フローティング・ディフュージョン) としての不純物領域 114、画素回路部 101 のシングルドレイン構造の増幅素子 SF のソースやドレインとなる不純物領域 115 を形成する。このとき、ゲート電極 111、112 をマスクとして用いることができる。これにより増幅素子 SF の第 1 導電型 (N 型) の低不純物濃度の不純物領域 115 が形成される。周辺回路部 102 には、周辺トランジスタとなる MOS トランジスタのゲート電極 121、ゲート電極 122 を形成する。

LDD 構造となる領域に不純物を注入して、第 1 導電型の低不純物濃度の不純物領域 124 及び第 2 導電型の低不純物濃度の不純物領域 126 を形成する。このときもゲート電極 121、122 をマスクとして用いることができる。不純物領域 114 や不純物領域 115、不純物領域 124、不純物領域 126 の形成のためのドーズ量の適当な範囲は、 $5 \times 10^{12} \sim 5 \times 10^{14}$  [ions/cm<sup>2</sup>] であり、好ましくは  $1 \times 10^{13} \sim 1 \times 10^{14}$  [ions/cm<sup>2</sup>] である。ともに第 1 導電型である不純物領域 114、115 の形成のための不純物の注入と、不純物領域 124、126 の形成のための不純物の注入とを並行して行うことができる。

## 【0027】

10

図 3 (a) に示す工程の次に、図 3 (b) に示すように、画素回路部 101 と周辺回路部 102 を覆う酸化シリコン層および窒化シリコン層の誘電体膜 131 を形成する。誘電体膜 131 は光電変換素子 PD、増幅素子 SF 及び周辺トランジスタのゲート電極を覆う。誘電体膜 131 はさらに、リセット素子 RS、選択素子 SL などの他の画素トランジスタや、転送素子 TX のゲート電極 111、容量素子 FD の不純物領域 114 を覆う。積層膜としての誘電体膜 131 は、上層の窒化シリコン層を下層の酸化シリコン層よりも厚くした積層膜を用いることができる。例えば、先に厚みが 5 ~ 20 nm の酸化シリコン層を熱 CVD 法で形成してから、厚みが 20 ~ 100 nm の窒化シリコン層をプラズマ CVD 法で形成することができる。プラズマ CVD 法で形成した窒化シリコン層は水素を多量に含むことができる。そのため、窒化シリコン層を形成した後に 350 °C 以上の熱処理を施すことにより、上層の窒化シリコン層から放出され、下層の酸化シリコン層を透過した水素が、半導体基板 100 に拡散してダンギングボンドの終端化効果が得られる。これによりノイズを低減することができる。また、酸化シリコン層は窒化シリコン層の応力を緩和する層としても機能する。また、酸化シリコン層を形成することで、窒化シリコン層をプラズマ CVD 法で形成する際の半導体基板 100 へのプラズマダメージを低減することができる。

20

## 【0028】

30

次に図 3 (c) に示すように、画素回路部 101 のウェル電位を規定する不純物領域 116 の上方に位置する部分を除く画素回路部上にレジスト 150 を形成し、酸化シリコン層および窒化シリコン層からなる誘電体膜 131 をエッチングする。レジスト 150 によって保護された、誘電体膜 131 の光電変換素子 PD、増幅素子 SF を覆う部分が、誘電体膜 131a として残存する。また、誘電体膜 131 のリセット素子 RS、選択素子 SL などの他の画素トランジスタや、転送ゲートのゲート電極 111、不純物領域 114 を覆う部分も誘電体膜 131a として残存する。一方、レジスト 150 で保護されない周辺回路部 102 では、ゲート電極 121、122 の側面に誘電体膜 131 の一部を残してエッチバックすることにより、誘電体膜 131 の残存物によりサイドスペーサ 131b が形成される。サイドスペーサ 131b となる残存物は酸化シリコン層および窒化シリコン層の積層構造を維持している。このときにエッチングに伴って、画素回路部 101 において、誘電体膜 131 の一部をエッチングして開口 130 を形成する。この開口 130 の形成のために除去されるのは、誘電体膜 131 のウェルコンタクトの不純物領域 116 が形成さ

40

50

れる予定の区域の上方に位置する部分である。この後、ウェルコンタクトがこの開口 130 を介して形成される。サイドスペーサ 131b の形成のためのエッチングと開口 130 の形成のためのエッチングとを並行して行うことで、半導体基板 100 へのダメージが抑制される。さらにこの時、光電変換素子 PD や増幅素子 SF などの画素回路部 101 の素子の上で誘電体膜 131 をエッチングしないことで、これらの素子にエッチングダメージが加わることを避け、ノイズを低減することができる。特に光電変換素子 PD や増幅素子 SF へのエッチングダメージは暗電流や固定パターンノイズの原因となり得るため、このようにすることでノイズ特性に優れた光電変換装置を得ることができる。

#### 【0029】

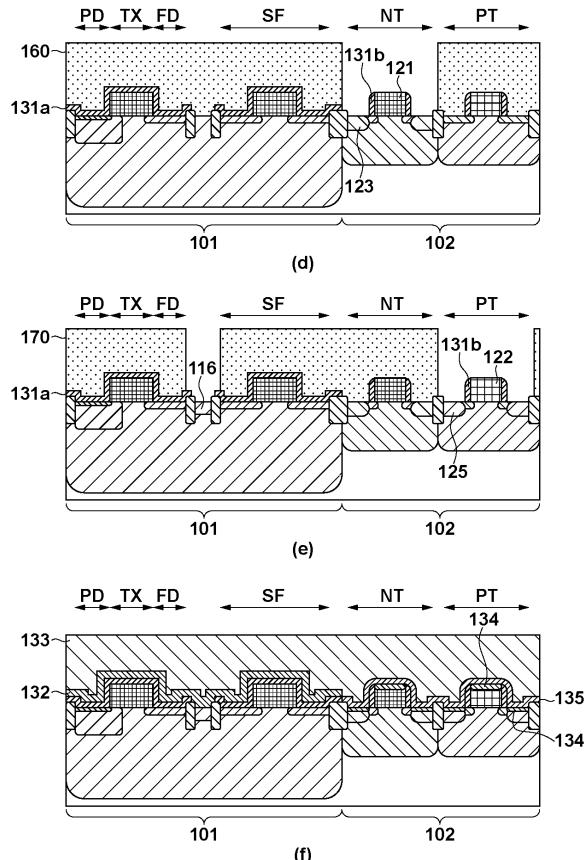

次に図 4 (d) に示すように、レジスト 160 を画素回路部 101 と周辺回路部 102 に形成する。このとき、レジスト 160 は周辺回路部 102 の第 1 導電型 (N 型、NT) の MOS トランジスタの部分に開口を有するように形成する。そして、レジスト 160 及び、周辺回路部 102 の第 1 導電型 (N 型) の MOS トランジスタのゲート電極 121 とサイドスペーサ 131b をマスクとして用い、第 1 導電型 (N 型) 不純物を注入する。これによりサイドスペーサ 131b の側面に自己整合した高不純物濃度のソース、ドレインの第 1 導電型の不純物領域 123 が形成される。

#### 【0030】

同様に、図 4 (e) に示すように、画素回路部 101 の不純物領域 116 と周辺回路部 102 の第 2 導電型 (P 型、PT) の MOS トランジスタの部分に開口を有するようにレジスト 170 を形成する。次に、レジスト 170 及び、ゲート電極 122 とサイドスペーサ 131b をマスクとして用い、第 2 導電型 (P 型) の不純物を注入する。この不純物の注入により、サイドスペーサ側面に自己整合したソース、ドレインの高不純物濃度の不純物領域 125 が形成される。このとき、並行して画素回路部 101 の不純物領域 116 にも第 2 導電型 (P 型) の不純物を、開口 130 を介してウェル 117 に注入することにより、ウェルコンタクトの不純物領域 116 を高不純物濃度の第 2 導電型の不純物領域として形成することができる。不純物領域 123 や不純物領域 125、不純物領域 116 の形成のためのドーズ量の適当な範囲は、 $5 \times 10^{14} \sim 5 \times 10^{16}$  [ions/cm<sup>2</sup>] であり、好ましくは $1 \times 10^{15} \sim 1 \times 10^{16}$  [ions/cm<sup>2</sup>] である。

#### 【0031】

以上の工程により周辺回路部 102 の MOS トランジスタの構造を LDD 構造にすると共に、ウェルコンタクトの不純物領域 116 の第 2 導電型の不純物濃度を高くすることができるので、不純物領域 116 のコンタクト抵抗を低くできる。ウェルコンタクトの不純物領域の形成のための不純物の注入と周辺回路部の第 2 導電型の MOS トランジスタのソースとドレインへの形成のための不純物の注入を同時にしている。この後にアニール処理を行うこともできる。

#### 【0032】

次に図 4 (f) に示すように、サリサイドプロセスにおいて画素回路部 101 を保護するための酸化シリコン層の单層膜である絶縁体膜 132 を画素回路部 101 に形成する。絶縁体膜 132 は開口 130 を覆うように形成されている。その後、周辺回路部 102 における MOS トランジスタのゲート電極上面にサリサイドにプロセスによるゲート電極のシリサイド化によって、コバルトシリサイド等のシリサイド層 134 を形成する。サリサイドプロセスによってシリサイド層 134 が画素回路部 101 に形成されるとシリサイド層 134 と半導体基板 100 の界面がノイズ源となり得る。しかし、開口 130 が絶縁体膜 132 で覆われた状態でサリサイドプロセスを行うことで、開口 130 の下に位置する半導体基板 100 の表面 (不純物領域 116 の表面) がシリサイド化されることを回避できる。また周辺回路部 102 の MOS トランジスタのソース及びドレインの表面もコバルトなどによりシリサイド化する。次に、コンタクトホール形成時のエッチングストップとして機能する酸化シリコン層および窒化シリコン層の積層膜である絶縁体膜 135 を周辺回路部 102 に形成する。絶縁体膜 135 はパターニングを経て周辺回路部 102 に形成され画素回路部 101 には形成されない。さらに、画素回路部 101 および周辺回路部 1

10

20

30

40

50

02に渡ってBPSGなどのケイ酸塩ガラスやHDP-CVD法などで形成された酸化シリコンからなる絶縁膜133を全面に形成する。絶縁膜133の上面は、リフロー法、エッチバック法、CMP法などにより平坦化される。この段階までに、800を超えるアニール処理によりウェルコンタクトの不純物領域116に注入した不純物の熱拡散、活性化を行って、コンタクト抵抗をより低くできる。後述するコンタクトホールを形成した後では、このような高温のアニール処理を行うことが困難であるため、コンタクトホールを形成する前に高温のアニール処理を行うのがよい。

#### 【0033】

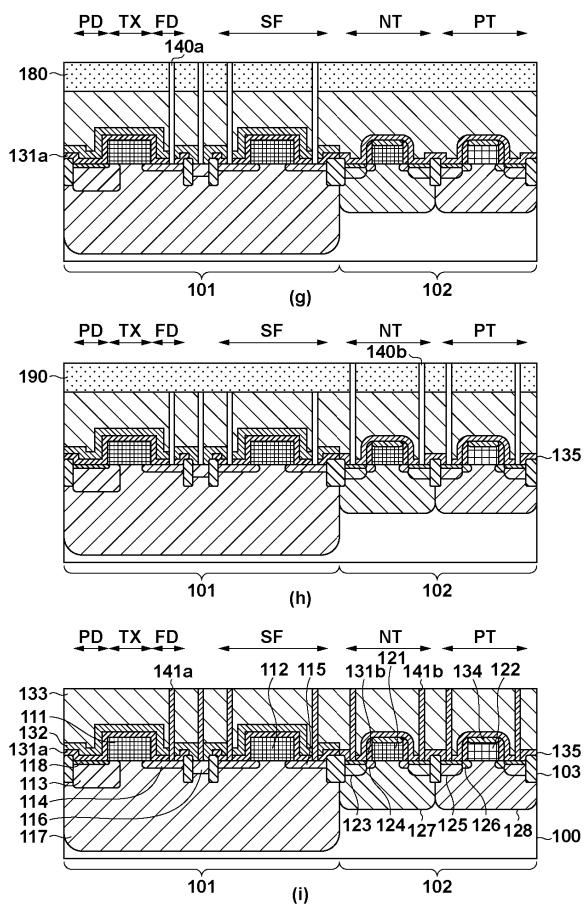

次に図5(g)に示すように、画素回路部101と周辺回路部102を画素回路部101上に開口を有するレジスト180で覆う。画素回路部101の酸化シリコン層および窒化シリコン層からなる誘電体膜131aをエッチングストップに用いて、コンタクトホール140aを異方性ドライエッ칭により開口する。画素回路部101にて形成された複数のコンタクトホール140aの一部は、絶縁膜133の不純物領域116の上に位置する部分に形成される。コンタクトホール140aの一部は開口130内に誘電体膜131aに囲まれた状態で形成されることになる。コンタクトホール140aの幅(径)は開口130の幅(径)よりも小さくすることができる。そして画素回路部101のコンタクトホール底部が接触する部分が各不純物領域に自己整合したコンタクトホールを形成する。またこのときコンタクトホール底部に露出する部分は金属配線による電気的な接続が可能な不純物濃度を確保することが望ましい。そのため、コンタクトホールを介して不純物領域116、114、115などに不純物を注入してもよい。コンタクトホール140aを介して不純物領域114、115に注入される不純物は不純物領域114、115と同じ第1導電型であることが好ましい。コンタクトホール140aを介して不純物領域116に注入される不純物は不純物領域116の導電型とは反対の第1導電型であってもよいし、第2導電型であってもよいし、この両方であってもよい。

#### 【0034】

次に図5(h)に示すように、レジスト180を除去して、画素回路部101と周辺回路部102を周辺回路部102上に開口を有するレジスト190で覆う。レジスト190はコンタクトホール140aを覆う。次に、周辺回路部102の酸化シリコン層および窒化シリコン層からなる絶縁体膜135をエッチングストップに用いて、周辺回路部102に異方性ドライエッ칭によりコンタクトホール140bを開口する。続いてレジスト190を除去して、コンタクトホール140a、140bの中に導電体を充填してコンタクトプラグ141a、141bを形成する。こうして図5(i)に示すような光電変換装置1が得られる。ここでは、周辺回路部102のコンタクトホール140bを画素回路部101のコンタクトホール140aを形成した後に形成したが、コンタクトホール140bをコンタクトホール140aの前に形成してもよい。このようにコンタクトホール140a、140bを別々に形成することで、シリサイド層134の金属による画素回路部101の不純物領域の金属汚染を低減できる。しかし、コンタクトホール140bとコンタクトホール140aを並行して形成してもよい。

#### 【0035】

周辺回路部102のサイドスペーサ131bをエッチバックにて形成する工程において、並行して、画素回路部101の不純物領域116の上方に位置する部分の誘電体膜131aをエッチバックして開口130を形成する。不純物領域116の上方に開口130を形成する工程をサイドスペーサ131bの形成と一緒にに行っている。また、周辺回路部102の第2導電型のMOSトランジスタのソース、ドレインとすべき領域への不純物の注入と並行して、不純物領域116にも不純物を注入する。不純物領域116に不純物を注入する工程を他の注入工程と一緒にに行うことができる。これにより、不純物領域116の形成を、BPSG等の絶縁膜133を形成してからコンタクトホールを開口して行う場合と比較して、工程を削減して製造コストを低く抑えることができる。さらには、不純物領域116に不純物を注入した後にアニール処理を加えることで不純物領域116は十分に活性化され、ウェル117と十分に接続され、コンタクトプラグ141aとの接触抵抗を

10

20

30

40

50

より低くすることができる。ウェルコンタクトの抵抗を低くできるので、撮像面内での基準電位の一定化をさらに図ることが可能となり、シェーディングによる画像性能の低下を抑制することができる。

【図1】

(a)

(b)

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 大貫 裕介

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 成瀬 裕章

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 楠川 将司

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 廣田 克範

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 梶尾 誠哉

(56)参考文献 特開2011-29604 (JP, A)

特開2005-302836 (JP, A)

特開2006-73607 (JP, A)

特開2008-41726 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H01L 31/08