(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2019-511168

(P2019-511168A)

(43) 公表日 平成31年4月18日(2019.4.18)

(51) Int.Cl.

H03B 5/20 (2006.01)

H03K 3/03 (2006.01)

F 1

H03B 5/20

H03K 3/03

テーマコード(参考)

A 5J043

5J081

審査請求 未請求 予備審査請求 有 (全 25 頁)

(21) 出願番号 特願2018-545918 (P2018-545918)

(86) (22) 出願日 平成29年2月10日 (2017.2.10)

(85) 翻訳文提出日 平成30年10月23日 (2018.10.23)

(86) 國際出願番号 PCT/US2017/017518

(87) 國際公開番号 WO2017/151295

(87) 國際公開日 平成29年9月8日 (2017.9.8)

(31) 優先権主張番号 62/302,735

(32) 優先日 平成28年3月2日 (2016.3.2)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 15/191,350

(32) 優先日 平成28年6月23日 (2016.6.23)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔡田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

最終頁に続く

(54) 【発明の名称】可変周波数RC発振器

## (57) 【要約】

プログラマブル出力周波数を有する発振器回路は、負の利得と、第1の遅延セクションに供給される制御信号によって設定される可変遅延とを有する第1の遅延セクションを含み得る。負の利得および固定遅延を有する第2の遅延セクションは、第1の遅延セクションと直列に接続され得る。発振器回路は、第1の遅延セクションの遅延および第2の遅延セクションの遅延に依存する周波数を有する第2の遅延セクションの出力を備える出力を含み得る。

【選択図】図1A

Fig. 1A

## 【特許請求の範囲】

## 【請求項 1】

プログラマブル出力周波数を有する発振器回路であつて、

入力端および出力端を有する第1の遅延セクションと、前記第1の遅延セクションは、

前記入力端と前記出力端との間の負の利得を有し、前記第1の遅延セクションは、前記第

1の遅延セクションに供給される制御信号によって設定される可変遅延を有する、

前記第1の遅延セクションと直列に電気的に接続された第2の遅延セクションと、前記第

2の遅延セクションは、入力端および出力端を有し、前記第2の遅延セクションは、前

記入力端と前記出力端との間の負の利得を有し、前記第2の遅延セクションは、固定遅延

を有する、

前記第1の遅延セクションおよび前記第2の遅延セクションによる前記遅延の関数である

周波数を有する出力信号のための回路出力と、前記回路出力は、前記第2の遅延セクシ

ョンの前記出力端を備える、

回路。

## 【請求項 2】

前記第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネット

ワークと、前記第1のRCネットワークと直列に接続され、かつ、抵抗器および可変キャ

パシタを備える第2のRCネットワークとを備え、前記第1の遅延セクションの遅延は、

前記第1のRCネットワークおよび前記第2のRCネットワークの前記可変キャパシタの

容量に基づいて決定される、請求項1に記載の回路。

## 【請求項 3】

前記制御信号は、前記第1のRCネットワークの前記可変キャパシタの前記容量を設定

し、追加の制御信号は、前記第2のRCネットワークの前記可変キャパシタの前記容量を

設定する、請求項2に記載の回路。

## 【請求項 4】

前記第1の遅延セクションは、抵抗器および可変キャパシタを備えるRCネットワーク

を備え、前記第1の遅延セクションに供給される前記制御信号は、前記第1のRCネット

ワークの前記可変キャパシタの容量を設定し、前記第1の遅延セクションの遅延は、前記

可変キャパシタの前記容量に基づいて決定される、請求項1に記載の回路。

## 【請求項 5】

前記第1の遅延セクションは、複数のスイッチドキャパシタを備え、前記制御信号は、

前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定する

、請求項1に記載の回路。

## 【請求項 6】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタは、ノー

ドをDC電圧に電気的に接続させる、請求項5に記載の回路。

## 【請求項 7】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタは、ノー

ドを接地電位に電気的に接続させる、請求項5に記載の回路。

## 【請求項 8】

前記制御信号は、nビットワードである、請求項5に記載の回路。

## 【請求項 9】

前記第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネット

ワークを備える、請求項1に記載の回路。

## 【請求項 10】

前記固定値容量成分の少なくとも1つのノードは、前記発振器回路の電源電圧より上に

スイングする、請求項9に記載の回路。

## 【請求項 11】

前記固定値容量成分の前記少なくとも1つのノードは、接地電位より下にスイングする

、請求項10に記載の回路。

10

20

30

40

50

**【請求項 1 2】**

前記第1の遅延セクションは、フィードバックループにおいて前記第2の遅延セクションを介して前記回路出力に電気的に接続される、請求項1に記載の回路。

**【請求項 1 3】**

発振器回路であって、

入力端および出力端を有する第1の遅延セクションと、前記第1の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネットワークと、前記第1のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える第2のRCネットワークとを備える、

前記第1の遅延セクションの遅延を設定するために、前記第1のRCネットワークの少なくとも前記可変キャパシタに供給される少なくとも1つの制御信号と、

前記第1の遅延セクションと直列に電気的に接続された第2の遅延セクションと、前記第2の遅延セクションは、入力端および出力端を有し、第2の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第2の遅延セクションは、固定遅延を有する、

前記第1の遅延セクションおよび前記第2の遅延セクションによる前記遅延の関数である周波数を有する出力信号のための回路出力と、前記回路出力は、前記第2の遅延セクションの前記出力端を備え得る、

回路。

10

**【請求項 1 4】**

前記第1の遅延セクションにおける前記第1のRCネットワークおよび前記第2のRCネットワーク中の前記可変キャパシタの各々は、複数のスイッチドキャパシタを備え、前記プログラマブル遅延段に供給される前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定する、請求項13に記載の回路。

**【請求項 1 5】**

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、DC電圧に電気的に接続される、請求項14に記載の回路。

**【請求項 1 6】**

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、接地電位に電気的に接続される、請求項14に記載の回路。

30

**【請求項 1 7】**

前記制御信号は、前記第1のRCネットワーク中の前記可変キャパシタに供給され、前記回路は、前記第2のRCネットワーク中の前記可変キャパシタに供給される追加の制御信号をさらに備える、請求項13に記載の回路。

**【請求項 1 8】**

前記第1の遅延セクションは、第2のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える少なくとも第3のRCネットワークをさらに備える、請求項13に記載の回路。

**【請求項 1 9】**

前記第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネットワークを備え、前記容量成分の少なくとも1つのノードは、前記発振器回路の電源電圧より上にスイングする、請求項13に記載の回路。

40

**【請求項 2 0】**

前記容量成分の前記少なくとも1つのノードは、接地電位より下にスイングする、請求項19に記載の回路。

**【請求項 2 1】**

発振器回路であって、

第1のインバータ段と、

前記第1のインバータ段の出力に電気的に接続された入力を有する第2のインバータ段

50

と、前記第2のインバータ段は、前記発振器回路の出力信号のための出力を有する、容量素子に接続された抵抗素子を備えるR C回路と、前記R C回路は、前記第2のインバータ段の前記入力と前記出力との間に電気的に接続される、

少なくとも1つの可変遅延段に供給される制御信号によって設定される遅延を有する前記少なくとも1つの可変遅延段と、前記少なくとも1つの可変遅延段は、前記抵抗素子および前記キャパシタ素子を接続する前記R C回路におけるノードと、前記第1のインバータ段の入力との間に電気的に接続される、

を備え、

前記出力信号の周波数は、前記少なくとも1つの可変遅延段の遅延に依存する、回路。

10

#### 【請求項22】

前記少なくとも1つの可変遅延段と直列に接続され、かつ、少なくとも1つの追加の可変遅延段に供給される制御信号に依存する遅延を有する前記少なくとも1つの追加の可変遅延段をさらに備える、請求項21に記載の回路。

#### 【請求項23】

前記抵抗素子および前記キャパシタ素子を接続する前記ノードにおける電圧レベルは、前記発振器回路の動作中、前記発振器回路の電源電圧より上および下に、および接地電位より上および下にスイングする、請求項21に記載の回路。

#### 【請求項24】

前記少なくとも1つの可変遅延段は、抵抗器および可変キャパシタを備え、前記少なくとも1つの可変遅延段に供給される前記制御信号は、前記可変キャパシタの容量を設定し、前記少なくとも1つの可変遅延段の前記遅延は、前記可変キャパシタの前記容量に依存する、請求項21に記載の回路。

20

#### 【請求項25】

前記少なくとも1つの可変遅延段は、複数のスイッチドキャパシタを備え、前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に設定する、請求項21に記載の回路。

#### 【請求項26】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、DC電圧にまたは接地電位に電気的に接続される、請求項25に記載の回路。

30

#### 【請求項27】

前記R C回路の前記容量素子の少なくとも1つのノードは、発振器回路の電源電圧より上、および、接地電位より下にスイングする、請求項21に記載の回路。

#### 【発明の詳細な説明】

#### 【関連出願への相互参照】

#### 【0001】

[0001] 米国特許法第119条(e)の定めにより、本願は、2016年3月2日に出願された米国仮出願第62/302,735号の出願日の権利を有し、その利益を主張するもので、その内容があらゆる目的のために参照により本明細書に全部組み込まれる。

40

#### 【技術分野】

#### 【0002】

[0002] 本開示は一般に、発振器に関し、より具体的には、可変周波数を有するR C発振器に関する。

#### 【背景技術】

#### 【0003】

[0003] デジタル論理回路の設計において、大規模集積技法は、多数の構成要素が单一シリコンチップ上に製造される構造をもたらしてきた。デジタル回路構成は通常それらの動作に時間基準を提供するために様々なクロック信号を要する。そのようなクロック信号は、多様な設計となる発振器回路によって生成される。1つのそのような設計は、抵抗器/キャパシタ(R C)ネットワークに基づくもので、R C発振器と呼ばれる。

50

## 【0004】

[0004] 従来のRC発振器は、低成本のタイミングソースを提供できる。さらに、従来のRC発振器は、集積回路上に製造することが困難であり得るインダクタ（例えば、図5参照）の使用を回避する。RC発振器は、その有用性を増大させるために抵抗Rまたは容量Cを変更することによって可変周波数の生成を可能にし得る。

## 【発明の概要】

## 【0005】

[0005] 本開示の態様に従って、プログラマブル出力周波数を有する発振器回路は、入力端および出力端を有する第1の遅延セクションを備え得る。第1の遅延セクションは、入力端と出力端との間の負の利得と、第1の遅延セクションに供給される制御信号によって設定される可変遅延とを有し得る。発振器は、第1の遅延セクションと直列に電気的に接続された第2の遅延セクションをさらに備え得る。第2の遅延セクションは、入力端および出力端と、入力端と出力端との間の負の利得とを有し得る。第2の遅延セクションは、固定遅延を有し得る。発振器は、第1の遅延セクションおよび第2の遅延セクションによる遅延の関数である周波数を有する出力信号のための回路出力をさらに備え得る。回路出力は、第2の遅延セクションの出力端を備え得る。

10

## 【0006】

[0006] いくつかの実施形態において、第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネットワークと、この第1のRCネットワークと直列に接続され、かつ、同じく抵抗器および可変キャパシタを備える第2のRCネットワークとを含み得る。第1の遅延セクションの遅延は、第1のRCネットワークおよび第2のRCネットワークの可変キャパシタの容量に基づいて決定され得る。制御信号は、第1のRCネットワークの可変キャパシタの容量を設定し得、追加の制御信号は、第2のRCネットワークの可変キャパシタの容量を設定し得る。

20

## 【0007】

[0007] いくつかの実施形態において、第1の遅延セクションは、抵抗器および可変キャパシタを備えるRCネットワークを含み得る。第1の遅延セクションに供給される制御信号は、第1のRCネットワークの可変キャパシタの容量を設定し得る。第1の遅延セクションの遅延は、可変キャパシタの容量に基づき得る。

30

## 【0008】

[0008] いくつかの実施形態において、第1の遅延セクションは、複数のスイッチドキャパシタを含み得、ここにおいて、制御信号は、複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定する。いくつかの実施形態において、スイッチドキャパシタがON状態にあるとき、このスイッチドキャパシタは、ノードをDC電圧に電気的に接続させる。他の実施形態において、スイッチドキャパシタがON状態にあるとき、このスイッチドキャパシタは、ノードを接地電位に電気的に接続させる。制御信号は、nビットワードであり得る。

## 【0009】

[0009] いくつかの実施形態において、第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネットワークを含み得る。固定値容量成分の少なくとも1つのノードは、発振器回路の電源電圧より上にスイング(swing)し得る。いくつかの実施形態において、固定値容量成分の少なくとも1つのノードは、接地電位より下にスイングし得る。

40

## 【0010】

[0010] いくつかの実施形態において、第1の遅延セクションは、フィードバックループにおいて第2の遅延セクションを介して回路出力に電気的に接続され得る。

## 【0011】

[0011] 本開示の態様に従って、発振器回路は、入力端および出力端を有する第1の遅延セクションを備え得る。第1の遅延セクションは、入力端と出力端との間の負の利得を有し得る。第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネ

50

ットワークと、この第1のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える第2のRCネットワークとを含み得る。発振器回路は、第1の遅延セクションの遅延を設定するために、少なくとも第1のRCネットワークの可変キャパシタに供給される少なくとも1つの制御信号を含み得る。発振器回路は、第1の遅延セクションと直列に電気的に接続された第2の遅延セクションを含み得る。第2の遅延セクションは、入力端および出力端と、入力端と出力端との間の負の利得とを有し得る。第2の遅延セクションは、固定遅延を有し得る。発振器回路は、第1の遅延セクションおよび第2の遅延セクションによる遅延の関数である周波数を有する出力信号のための回路出力を含み得る。回路出力は、第2の遅延セクションの出力端を備え得る。

【0012】

10

[0012] いくつかの実施形態において、第1の遅延セクションにおける第1および第2のRCネットワーク中の可変キャパシタの各々は、複数のスイッチドキャパシタを備え得、ここにおいて、プログラマブル遅延段に供給される制御信号は、複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定する。いくつかの実施形態において、スイッチドキャパシタがON状態にあるとき、このスイッチドキャパシタのノードは、DC電圧に電気的に接続されている。他の実施形態において、スイッチドキャパシタがON状態にあるとき、このスイッチドキャパシタのノードは、接地電位に電気的に接続されている。

【0013】

20

[0013] いくつかの実施形態において、制御信号は、第1のRCネットワーク中の可変キャパシタに供給され得る。発振器回路は、第2のRCネットワーク中の可変キャパシタに供給される追加の制御信号をさらに含み得る。

【0014】

[0014] いくつかの実施形態において、第1の遅延セクションは、第2のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える少なくとも第3のRCネットワークをさらに備え得る。

【0015】

30

[0015] いくつかの実施形態において、第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネットワークを備え得る。容量成分の少なくとも1つのノードは、発振器回路の電源電圧より上にスイングし得る。容量成分の少なくとも1つのノードはさらに、接地電位より下にスイングし得る。

【0016】

40

[0016] 本開示の態様に従って、発振器回路は、第1のインバータ段と、この第1のインバータ段の出力に電気的に接続された入力を有する第2のインバータ段とを備え得る。第2のインバータ段は、発振器回路の出力信号のための出力を有し得る。発振器回路は、容量素子に接続された抵抗素子を備えるRC回路を備え得る。RC回路は、第2のインバータ段の入力と出力との間に電気的に接続され得る。発振器回路は、少なくとも1つの可変遅延段に供給される制御信号によって設定される遅延を有する少なくとも1つの可変遅延段を備え得る。少なくとも1つの可変遅延段は、抵抗素子およびキャパシタ素子を接続するRC回路におけるノードと、第1のインバータ段の入力との間に電気的に接続され得る。出力信号の周波数は、少なくとも1つの可変遅延段の遅延に依存し得る。

[0017] いくつかの実施形態において、発振器回路は、少なくとも1つの可変遅延段と直列に接続され、かつ、少なくとも1つの追加の可変遅延段に供給される制御信号に依存する遅延を有する少なくとも1つの追加の可変遅延段をさらに備え得る。

【0017】

[0018] いくつかの実施形態において、抵抗素子およびキャパシタ素子を接続するノードにおける電圧レベルは、発振器回路の動作中、発振器回路の電源電圧より上および下に、および、接地電位より上および下にスイングし得る。

【0018】

50

[0019] いくつかの実施形態において、少なくとも1つの可変遅延段は、抵抗器および

可変キャパシタを備え得、ここにおいて、少なくとも1つの可変遅延段に供給される制御信号は、可変キャパシタの容量を設定する。少なくとも1つの可変遅延段の遅延は、可変キャパシタの容量に依存し得る。

【0019】

[0020] いくつかの実施形態において、少なくとも1つの可変遅延段は、複数のスイッチドキャパシタを備え得、ここにおいて、制御信号は、複数のスイッチドキャパシタの各々をON状態またはOFF状態に設定する。いくつかの実施形態において、スイッチドキャパシタがON状態にあるとき、スイッチドキャパシタのノードは、DC電圧または接地電位に電気的に接続されている。

【0020】

[0021] いくつかの実施形態において、RC回路の容量素子の少なくとも1つのノードは、発振器回路の電源電圧より上、および、接地電位より下にスイングする。

【0021】

[0022] 以下の詳細な説明および添付の図面は、本開示の特性および利点のより良い理解を与える。

【0022】

[0023] 後に続く記述および特に図面に関して、示される詳細が、例証のための例を表し、本開示の概念的な態様および原理の説明を提供するために提示されることが強調される。この点に関して、本開示の根本的な理解に要することを超えて実施の詳細を示すための試みはなされていない。後に続く記述は、図面と併せて、本開示に従った実施がどのように実践され得るかを当業者に明らかにする。様々な図面および証明となる説明における同様または同一の要素を識別するか、そうでなければ参照するために同様または同一の参考番号が使用され得る。添付の図面は、次の通りである。

10

20

30

40

50

【図面の簡単な説明】

【0023】

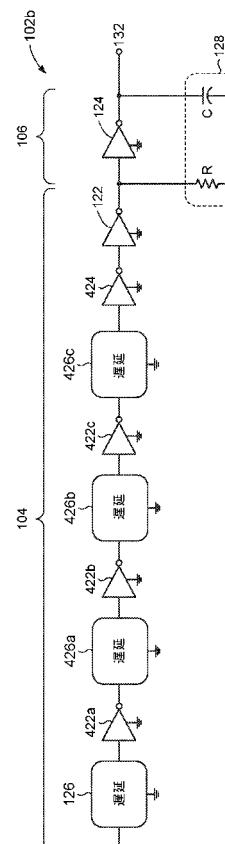

【図1A】本開示に従った発振器回路を示す。

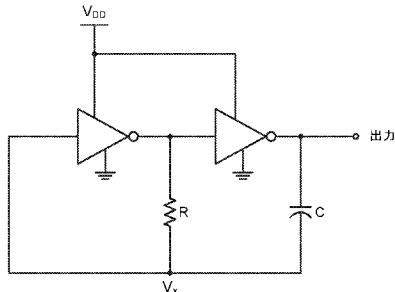

【図1B】本開示に従った発振器回路を示す。

【図2】本開示に従った発振器回路を示す。

【図2A】本開示に従った可変キャパシタの詳細を示す。

【図3】本開示に従った発振器回路を示す。

【図3A】本開示に従った可変キャパシタの詳細を示す。

【図4A】本開示に従った代替の実施形態を例示する。

【図4B】本開示に従った代替の実施形態を例示する。

【図5】従来のRC発振器の例を示す。

【発明の詳細な説明】

【0024】

[0031] 以下の説明では、説明の目的上、本開示の完全な理解を与えるために、多数の例および特定の詳細が示される。しかしながら、特許請求の範囲において表現されている本開示が、これらの例における特徴のうちのいくつかまたは全てを、単独でまたは以下で説明される他の特徴と組み合わせて含み得、本明細書で説明される特徴および概念の変形および均等物をさらに含み得ることは当業者に明らかであろう。

【0025】

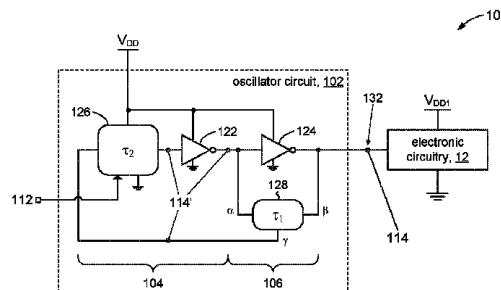

[0032] 図1Aは、本開示の実施形態に従った電子回路10を示す。電子回路10は、発振器回路102および電子回路構成(electronic circuitry)12を含み得る。発振器回路102は、例えば、電子回路構成12によって使用され得る出力信号(例えば、クロック信号132)のための出力114を有し得る。電子回路10は、電子デバイス(図示されない)中の構成要素であり得る。発振器回路102は、電源V<sub>DD</sub>によって電力供給され得、電子回路構成12は、電源V<sub>DD1</sub>によって電力供給され得る。いくつかの実施形態において、V<sub>DD</sub>は、V<sub>DD1</sub>と同じであり得、他の実施形態において、V<sub>DD</sub>は、V<sub>DD1</sub>と異なり得る。

## 【0026】

[0033] 発振器 102 は、第 1 の遅延セクション 104 と、この第 1 の遅延セクション 104 と直列に電気的に接続された第 2 の遅延セクション 106 とを備え得る。本開示に従い、第 1 の遅延セクション 104 は、第 1 の遅延セクション 104 の入力端と第 1 の遅延セクション 104 の出力端との間の負の利得を特徴とし得る。図 1A を参照して、例えば、いくつかの実施形態において、第 1 の遅延セクション 104 は、反転段 122 と直列に接続された遅延段 126 を含み得る。以下でより詳細に説明されるように、第 1 の遅延セクション 104 は、可変遅延を有することをさらに特徴とし得る。さらに、負の利得により、入力端における（例えば、電圧の）所与の正の変化が出力端において（電圧の）負の変化を生じさせることが意味される。

10

## 【0027】

[0034] 第 1 の遅延セクション 104 の入力端は、遅延段 126 の入力側によって定義され得る。第 1 の遅延セクション 104 の出力端は、反転段 122 の出力によって定義され得る。遅延段 126 の利得が正であることは以下の説明から明らかになるであろう。反転段 122 が負の利得を有するため、第 1 の遅延セクション 104 は、負の利得を有する。いくつかの実施形態において、反転段 122 は、図 1A に示されるように単一のインバータを備え得る。他の実施形態において、反転段 122 は、任意の奇数の数のインバータ、そして一般に、負の利得を提供できる任意の適切な回路構成を備え得る。

20

## 【0028】

[0035] 第 2 の遅延セクション 106 は、同様に、その入力端とその出力端との間の負の利得を特徴とし得る。いくつかの実施形態において、第 2 の遅延セクション 106 は、遅延段 128 の両側に（と並行に）、例えば、遅延段 128 の端子 および において接続された反転段 124 を含み得る。第 2 の遅延セクション 106 の入力端および出力端は、それぞれ、反転段 124 の入力および出力であり得る。反転段 124 が負の利得を有するため、第 2 の遅延セクション 106 は、負の利得を有する。いくつかの実施形態において、反転段 124 は、図 1A に示されるように単一のインバータを備え得る。他の実施形態において、反転段 124 は、任意の奇数の数のインバータ、そして一般に、負の利得を提供できる任意の適切な回路構成を備え得る。

20

## 【0029】

[0036] 第 1 の遅延セクション 104 は、クロック信号 132 を作り出すために振動が伝播できるフィードバックループを定義するために、第 2 の遅延セクション 106 を介して出力 114 に接続され得る。クロック信号 132 の周波数  $f_{CLOCK}$  は一般に、遅延段 128 の遅延  $\tau_1$  および遅延段 126 の遅延  $\tau_2$  の関数である。クロック信号 132 は、図 1A に描かれるように、第 2 の反転段 124 の出力において引き出され(tapped out) 得るか別の方法で作り出され得る。しかしながら、クロック信号 132 がループ内の他の点 114' で取得され得ることは理解される。

30

## 【0030】

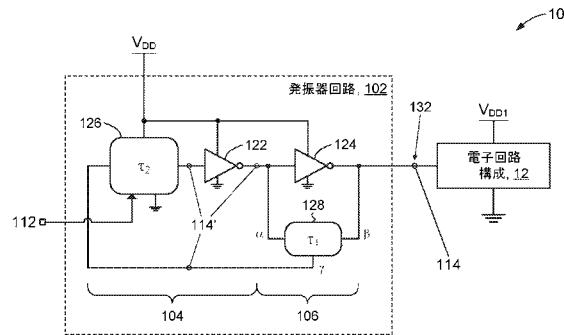

[0037] 図 1B を参照すると、いくつかの実施形態において、遅延段 128 は、抵抗器 R およびキャパシタ C を備える R C ネットワークを備え得る。遅延段 128 の端子 は、抵抗器 R に接続され得、キャパシタ C は、端子 に接続され得る。遅延段 128 の端子 は、抵抗器 R およびキャパシタ C が接続されたノード  $V_x$  に接続され得る。R C ネットワークの遅延  $\tau_1$  は、一般に、 $R \times C$  として定義される（R C 時定数と呼ばれることがある）時定数の関数であり、これは、抵抗器 R およびキャパシタ C のそれぞれの素子値を表す。いくつかの実施形態において、抵抗器 R およびキャパシタ C は、固定値の素子であり得る。従って、遅延段 128 は、固定遅延を提供し得る。

40

## 【0031】

[0038] 発振器回路 102 中の他の素子（例えば、反転段 122, 124、遅延段 126）と比べて、ノード  $V_x$  が接地電位に接続されないことに留意されたい。むしろ、ノード  $V_x$  は、「浮遊」ノードであり、これは、発振器回路 102 の動作中、キャパシタ C にわたる電圧が変動することに伴ってノード  $V_x$  における電位が変動し得ることを意味する

50

。例えば、動作中、ノード  $V_x$  における電圧は、出力 114においてクロック信号 132 のサイクルの半分で電源電圧より上および下にスイングし得、このサイクルの残りの半分で接地電位より上および下にスイングし得る。本開示のこの態様が以下に説明される。

#### 【0032】

[0039] 図 1A に戻り、いくつかの実施形態に従って、遅延段 126 は、可変（チューナブル、プログラマブル）遅延を有し得る。遅延段 126 は、遅延段 126 の遅延  $_{2}$  を選択するか別の方法で設定するためにセレクタ入力信号 112 を受け得る。いくつかの実施形態において、セレクタ入力 112 は、デジタルコードであり得る。本開示に従って、セレクタ入力 112 は、電子回路 10 の動作中、遅延段 126 に対して異なる遅延  $_{2}$  を選択するために変化し得る。例えば、セレクタ入力 112 は、遅延段 126 に異なるデジタルコードを提供し得、ゆえに、遅延  $_{2}$  のオンザフライ選択を可能にする。

10

#### 【0033】

[0040] 発振器回路 102 における振動の周波数は、遅延  $_{1}$  および  $_{2}$  に従って制御され得る。遅延  $_{1}$  は、例えば、遅延段 128 中の抵抗器 R およびキャパシタ C に対して適切な素子値を選択することで、設計段階の間に決定され得る。遅延  $_{2}$  の遅延は、適切なセレクタ入力 112 を遅延段 126 に供給することで設定され得る。遅延段 126 の遅延  $_{2}$  が、オンザフライで設定され得るため、発振器回路 102 によって作り出されるクロック信号 132 の周波数は、同様に、オンザフライで、すなわち、適切なセレクタ入力 112 を遅延段 126 に供給することで、設定され得る。

20

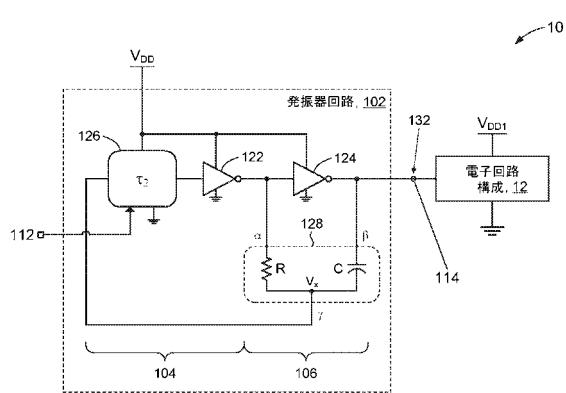

#### 【0034】

[0041] 図 2 は、本開示のいくつかの実施形態に従った、第 1 の遅延セクション 104 の遅延段 126 についての追加の詳細を示す。いくつかの実施形態において、例えば、遅延段 126 は、高い入力インピーダンスの非反転入力バッファ 202 および可変 R C ネットワーク 204 を備え得る。入力バッファ 202 のための電源（supply）（図示されない）は、例えば、図 1A において例示されるように、遅延段 126 に供給される  $V_{DD}$  電源であり得る。

#### 【0035】

[0042] 可変 R C ネットワーク 204 は、抵抗器 R<sub>1</sub> および可変キャパシタ C<sub>1</sub> を備え得る。セレクタ入力 112 は、可変キャパシタ C<sub>1</sub> に対する容量を選択するか別の方法で設定するために、可変キャパシタ C<sub>1</sub> に供給され得る n ビット信号バスであり得る。遅延段 126 の遅延  $_{2}$  は、抵抗器 R<sub>1</sub> および可変キャパシタ C<sub>1</sub> のそれぞれの値である R<sub>x</sub> C<sub>x</sub> として定義される時定数に基づいて決定され得る。従って、遅延  $_{2}$  は、可変キャパシタ C<sub>1</sub> の容量設定に依存して設定され得る。

30

#### 【0036】

[0043] 当業者であれば、任意の適切な遅延回路構成が遅延段 126 に使用され得ることを認識するはずである。要点を例示するためだけに、例えば、他の実施形態において、遅延段 126 は、固定キャパシタを充電するためにチューナブル電流源を用い得る。遅延段 126 は、チューナブル電流源および / またはチューナブルキャパシタを有する電流枯渇インバータ、等を使用し得る。

40

#### 【0037】

[0044] 図 2A は、可変キャパシタ C<sub>1</sub> の追加の詳細を示す。いくつかの実施形態に従って、可変キャパシタ C<sub>1</sub> は、n 個の固定値スイッチド容量素子 C<sub>x</sub> のセットを含み得る。容量素子 C<sub>x</sub> は、互いに並列に接続され得る。例えば、各容量素子 C<sub>x</sub> は、抵抗器 R<sub>1</sub> と、対応するスイッチ M<sub>0</sub> ~ M<sub>n-1</sub> を介した接地電位接続との間の接続を有し得る。他の実施形態において、容量素子 C<sub>x</sub> が、並列にでなく接続トポロジで配列され得ることが認識されるであろう。

#### 【0038】

[0045] 容量素子 C<sub>x</sub> は、発振器回路 102 の所与のアプリケーションに適した任意の半導体技術を使用して実現され得る。要点を例示するためだけに、様々な実施形態において、容量素子 C<sub>x</sub> は、P N 接合キャパシタ、MOSFET ゲートキャパシタ、金属 - 絶縁

50

体 - 金属 (MIM) キャパシタ、金属 - 酸化物 - 金属 (MOM) キャパシタ、等であり得る。容量素子  $C_x$  は、同じ半導体技術に基づき得るか、それらは、異なる技術に基づき得る。いくつかの実施形態において、容量素子  $C_x$  の各々は、同じ容量を有し得る。他の実施形態において、容量素子  $C_x$  は、異なる容量を有し得る。

【0039】

[0046] 容量素子  $C_x$  は、対応するスイッチ  $M_0 \sim M_{n-1}$  のセットを介した接地電位に選択的に切り替えられ得る。スイッチ  $M_0 \sim M_{n-1}$  は、任意の適切なスイッチングデバイスであり得る。いくつかの実施形態において、例えば、スイッチ  $M_0 \sim M_{n-1}$  は、例えば、図 2A に示されている NMOS トランジスタのような半導体スイッチであり得、しかしながら、他の実施形態において、例えば、N F E T のような他のトランジスタ技術または設計が使用され得る。いくつかの実施形態において、全てのスイッチ  $M_0 \sim M_{n-1}$  は、同じ技術に基づき得るか、それらは、いくつかの異なる技術に基づき得る。セレクタ入力 112 を備える  $n$  本の信号線の各々は、スイッチ  $M_0 \sim M_{n-1}$  のうちのそれぞれのスイッチに接続され得る。例えば、図 2A において、セレクタ入力 112 の各信号線は、スイッチ  $M_0 \sim M_{n-1}$  のそれぞれのゲート端子に接続される。セレクタ入力 112 への入力は、発振器回路 102 にまたは電子回路 10 (図 1A) に関連付けられたデジタル論理または他の適切な回路構成によって生成され得る。

10

【0040】

[0047] 本開示に従って、図 2A の容量素子  $C_x$  のノードは、ノード  $V_x$  に関連して上で説明したような浮遊ノードでない。むしろ、いくつかの実施形態において、容量素子  $C_x$  のノードは、接地電位に電気的に接続され得るかそうでなければそれを基準とし得る。他の実施形態において、容量素子  $C_x$  は、DC 電圧、例えば、 $V_{DD}$  のような電源電圧、に電気的に接続され得るかそうでなければそれを基準し得る。より一般には、当業者は、容量素子  $C_x$  が、任意の適切な低インピーダンスノードに電気的に接続され得ることを認識するであろう。

20

【0041】

[0048] 動作中、セレクタ入力 112 における  $n$  本の信号線のうちの任意の 1 つまたは複数は、それらの対応するスイッチ  $M_0 \sim M_{n-1}$  を、故に、対応する容量素子  $C_x$  を ON にするためにアサートされ(assert)得る。ON 状態にあるスイッチ (例えば、 $M_0$ ) は、その対応する容量素子  $C_x$  を R C ネットワーク 204 に接続し (スイッチオンされる)、反対に、OFF 状態にあるスイッチは、その対応する容量素子  $C_x$  を R C ネットワーク 204 から切断する (スイッチオフされる)。図 2A に示されるように、容量素子  $C_x$  が並列に接続されている場合、例えば、可変キャパシタ  $C_1$  の容量は、スイッチオンされた容量素子の合計として計算され得る。ゆえに、遅延段 126 の遅延  $z_2$  は、R C ネットワーク 204 において、どの容量素子がスイッチオンされ、どれがスイッチオフされるかに依存して設定され得る。

30

【0042】

[0049] いくつかの実施形態において、抵抗器  $R_1$  は、図 2A に示されるような固定値素子であり得る。他の実施形態 (図示されない) において、抵抗器  $R_1$  は、可変抵抗器であり得、キャパシタ  $C_1$  は、固定値素子であり得る。さらに他の実施形態において、抵抗器  $R_1$  は、可変抵抗器であり得、キャパシタ  $C_1$  は、可変キャパシタであり得る。

40

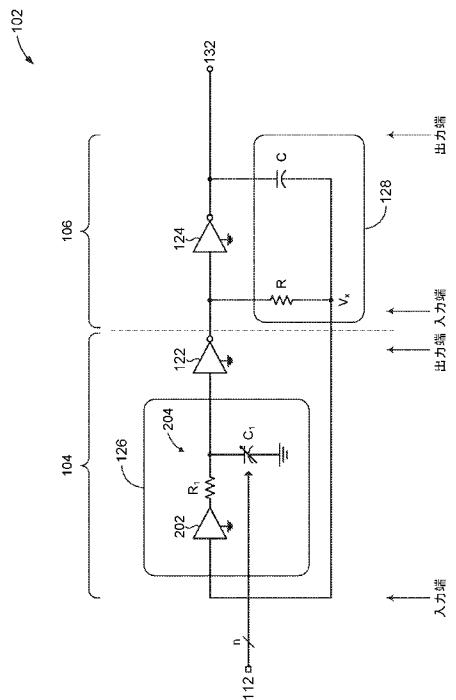

【0043】

[0050] 図 3 を参照すると、本開示に従つたいくつかの実施形態において、第 1 の遅延セクション 104 は、遅延段 126 と直列に接続された追加の遅延段 326 を備え得る。入力インバータ 322 は、遅延段 126 の出力において生じる振動を、追加の遅延段 326 の入力に結合するために設けられ得る。換言すると、インバータ 322 は、振動を維持する。出力インバータ 324 は、第 1 の遅延セクション 104 の入力端と出力端との間の正味の (net) 負の利得を維持するために設けられ得る。入力インバータ 322 および出力インバータ 324 のための電源 (図示されない) は、例えば、図 1A において例示されるような遅延段 126 に供給されるのと同じ  $V_{DD}$  電源であり得る。いくつかの実施形態

50

において、追加の遅延段 326 は、発振器回路 102 のノイズパフォーマンスを改善できる。

【0044】

[0051] 追加の遅延段 326 は、抵抗器  $R_2$  および可変キャパシタ  $C_2$  を備える可変 RC ネットワーク 304 を含み得る。セレクタ入力 312 は、可変キャパシタ  $C_2$  に対する容量を選択するか別の方法で設定するために、可変キャパシタ  $C_2$  に供給され得る  $m$  ビット信号バスを備え得る。追加の遅延段 326 は、抵抗器  $R_2$  および可変キャパシタ  $C_2$  のそれぞれの値である  $R \times C$  として定義される時定数に基づいて決定され得る遅延  $_{33}$  を供給し得る。従って、追加の遅延段 326 によって供給される遅延  $_{33}$  は、可変キャパシタ  $C_2$  の容量設定に依存して設定され得る。

10

【0045】

[0052] 図 3A は、可変キャパシタ  $C_2$  の追加の詳細を示す。いくつかの実施形態に従って、可変キャパシタ  $C_2$  は、 $m$  個の固定値スイッチド容量素子  $C_y$  のセットを備え得る。容量素子  $C_y$  は、互いに並列に接続され得る。換言すると、各容量素子  $C_y$  は、抵抗器  $R_2$  と、対応するスイッチ  $M_0 \sim M_{m-1}$  を介した接地電位接続との間の接続を有し得る。他の実施形態において、容量素子  $C_y$  は、並列でなく接続トポロジで接続され得ることが認識されるであろう。

20

【0046】

[0053] 容量素子  $C_y$  は、発振器回路 102 の所与のアプリケーションに適した任意の半導体技術を使用して実現され得る。要点を例示するためだけに、様々な実施形態において、容量素子  $C_y$  は、PN 接合キャパシタ、MOSFET ゲートキャパシタ、金属-絶縁体-金属 (MIM) キャパシタ、金属-酸化物-金属 (MOM) キャパシタ、等であり得る。容量素子  $C_y$  は、同じ半導体技術に基づき得るか、それらは、異なる技術に基づき得る。いくつかの実施形態において、容量素子  $C_y$  の各々は、同じ容量を有し得る。他の実施形態において、容量素子  $C_y$  は、異なる容量であり得る。

20

【0047】

[0054] 容量素子  $C_y$  は、対応するスイッチ  $M_0 \sim M_{m-1}$  のセットを介した接地電位に選択的に切り替えられ得る。スイッチ  $M_0 \sim M_{m-1}$  は、任意の適切なスイッチングデバイスであり得る。いくつかの実施形態において、例えば、スイッチ  $M_0 \sim M_{m-1}$  は、例えば、図 3A に示されている PNP トランジスタのような半導体スイッチであり得る。いくつかの実施形態において、全てのスイッチ  $M_0 \sim M_{m-1}$  は、同じ技術に基づき得るか、それらは、異なる技術に基づき得る。セレクタ入力 312 を備える  $m$  本の信号線の各々は、スイッチ  $M_0 \sim M_{m-1}$  のうちのそれぞれのスイッチに接続され得る。セレクタ入力 312 への入力は、発振器回路 102 にまたは電子回路 10 (図 1A) に関連付けられたデジタル論理または他の適切な回路構成によって生成され得る。

30

【0048】

[0055] 本開示に従って、図 3A の容量素子  $C_y$  のノードは、浮遊していない。むしろ、容量素子  $C_y$  のノードは、接地電位に電気的に接続され得る。当業者であれば、他の実施形態において、容量素子  $C_y$  は、DC 電圧 (例えば、電源  $V_{DD}$ ) に電気的に接続され得ることを認識するであろう。より一般には、容量素子  $C_y$  は、任意の適切な低インピーダンスノードに電気的に接続され得る。

40

【0049】

[0056] 動作中、セレクタ入力 312 における  $m$  本の信号線のうちの任意の 1 つまたは複数は、それらの対応するスイッチ  $M_0 \sim M_{m-1}$  を ON にするためにアサートされ得る。ON 状態にあるスイッチ (例えば、 $M_0$ ) は、その対応する容量素子を RC ネットワーク 304 に接続し (スイッチオンされる)、反対に、OFF 状態にあるスイッチは、その対応する容量素子を RC ネットワーク 304 から切断する (スイッチオフされる)。図 3A に示されるように、容量素子  $C_y$  が並列に接続されている場合、例えば、可変キャパシタ  $C_2$  の容量は、スイッチオンされた容量素子の合計として計算され得る。ゆえに、追加の遅延段 326 の遅延  $_{33}$  は、RC ネットワーク 304 において、どの容量素子  $C_y$  がス

50

イッヂオンされ、どれがスイッヂオフされるかに依存して設定され得る。

【0050】

[0057] いくつかの実施形態において、抵抗器  $R_2$  は、図3Aに示されるような固定値素子であり得る。他の実施形態(図示されない)において、抵抗器  $R_2$  は、可変抵抗器であり得、キャパシタ  $C_2$  は、固定値素子であり得る。さらに他の実施形態(図示されない)において、抵抗器  $R_2$  は、可変抵抗器であり得、キャパシタ  $C_2$  は、可変キャパシタであり得る。

【0051】

[0058] いくつかの実施形態において、それぞれの遅延段126, 326のセレクタ入力112, 312は、同じ選択入力を受け得、例えば、同じnビットコードが、各セレクタ入力112, 312に供給され得る。他の実施形態において、各セレクタ入力112, 312は、異なる選択入力を受け得る。

10

【0052】

[0059] 発振器回路102における振動の周波数は、遅延  $_{1,2}$ 、および  $_{3}$ に従って制御され得る。上で説明したように、遅延段128における遅延  $_{1,2}$  は、抵抗器  $R$  およびキャパシタ  $C$  に対して固定であり得る。遅延段126の遅延  $_{1,2}$  は、遅延段126のためのセレクタ入力112を備える好適なビット線をアサートすることで設定され得る。同様に、遅延段326における  $_{3}$  は、セレクタ信号312を備える好適なビット線をアサートすることで設定され得る。従って、クロック信号132の周波数は、可変遅延  $_{1,2}$  および  $_{3}$  の関数として選択され得る。

20

【0053】

[0060] 本開示に従つたいくつかの実施形態において、第1の遅延セクション104は、直列に接続されたいくつかの追加の遅延段を備え得る。例えば、図4Aは、本開示のいくつかの実施形態に従つた、発振器回路102aの略図である。第1の遅延セクション104は、遅延段126と、2つの追加の遅延段426a, 426bとを備え得る。インバータ422a, 422bは、遅延段間で信号を結合するために設けられ得る。例えば、インバータ422aは、遅延段126と遅延段422aとの間で信号を結合し得、同様に、インバータ422bは、遅延段422aと遅延段422bとの間で信号を結合し得る。第1の遅延セクション104を構成する(comprise)インバータ422a, 422b, 122が正味の負の利得を供給することに留意されたい。

30

【0054】

[0061] 図4Bは、3つの追加の遅延段426a, 426b, 426cと、インバータ422a, 422b, 422c, 422dとを有する第1の遅延セクション102を備える発振器回路102bの略図である。インバータ422a～422cは、遅延段126および426～426cの間で信号を結合する。インバータ424が第1の遅延セクション104に正味の負の利得を供給することが判る。

30

【0055】

技術的な効果および利点

[0062] 図5に示されるような従来のRC発振器設計は、多くの望ましい特性を有する。そのような設計は一般に、電源電圧の変化に反応しない。この設計は、比較的シンプルであり、構成要素をほとんど有さない。結果として、これらのRC発振器は、低ノイズパフォーマンスを達成できる。例えば、いくつかの設計は、理論上の下限を3dBしか上回らないノイズレベルを達成し得る。それらの比較的シンプルな設計により、RC発振器は、ICチップ上でより小さい設置面積を有する。

40

【0056】

[0063] 本開示は、RC発振器のユーティリティをさらに改善するためにプログラマブル周波数の能力を有する発振器回路を提供する。図5に示されるように、例えば、基本のRC発振器設計は、2つのインバータ(例えば、反転段122, 124)と、抵抗器  $R$  およびキャパシタ  $C$  を備えるRCネットワークとを備える。RCネットワークは、RC発振器の動作周波数を設定する遅延を提供する。従って、RまたはCのいずれかの素子値を変

50

動させることは、RC発振器の動作周波数におけるプログラマビリティを提供するのに役立つ。

【0057】

[0064] しかしながら、RまたはCを作る方法は、実用的であり得ない。プログラマブル抵抗器は、設けることが困難であり得る。高プログラマビリティは、わずかな増加で全体のRを修正する能力を必要とする。これは、低いON抵抗を有する多数のスイッチおよび抵抗器の大型のネットワークを必要とする。さらに、スイッチの端子間電圧は、振動サイクルにわたって変動し得、その結果スイッチ設計を複雑にする。可変抵抗器を構築するためにスイッチド抵抗器を使用することは、実用的であり得ない。

【0058】

[0065] プログラマブルキャパシタは、ノード $V_x$ における挙動によりキャパシタCが「浮遊」キャパシタであるため、困難であり得る。上で説明したように、ノード $V_x$ における電圧が、出力のサイクルの半分で電源電圧より上および下にスイングし、このサイクルの残りの半分で接地電位より上および下にスイングし得るため、ノード $V_x$ は、浮遊ノードである。プログラマブルキャパシタは典型的に、スイッチドキャパシタ素子のバンクを備える。スイッチのソース（またはドレイン）がノード $V_x$ において接続されている場合、スイッチの状態は、サイクルの一部の間は順方向バイアスがかけられた状態になり得、本来ならばOFF（導通していない）状態にあるときに導通する。浮遊ノード $V_x$ の存在は、可変遅延RCネットワークを、故に、可変周波数発振器回路を提供するために、このロケーションにおいて可変キャパシタを使用することの課題を提示する。ゆえに、可変キャパシタを構築するために、Cをスイッチドキャパシタのバンクに置き換えることは、容易には達成されないであろう。

【0059】

[0066] 本開示に従った発振器回路は、この課題を克服できる。図1Bに示されるように、遅延段126は、RCネットワーク128とは別に設けられることができる。遅延段126は、回路の電圧スイングが遅延段126の動作に極めて少ない影響を与えるように、接地され得る。

【0060】

[0067] 上の説明は、特定の実施形態の態様がどのように実施され得るかの例とともに本開示の様々な実施形態を例示する。上の例は、唯一の実施形態であるとみなされるべきでなく、以下の特許請求の範囲によって定義されるような、特定の実施形態の柔軟性および利点を例示するために提示されている。上の開示および以下の特許請求の範囲に基づいて、他の配置、実施形態、実施、および同等物は、特許請求の範囲によって定義される本開示の範囲から逸脱することなく用いられ得る。

【図 1 A】

Fig. 1A

【図 1 B】

Fig. 1B

【図 2】

Fig. 2

【図 2 A】

Fig. 2A

【図3】

Fig. 3

【図3A】

Fig. 3A

【図4A】

Fig. 4A

【図4B】

Fig. 4B

【図 5】

Fig. 5

(先行技術)

## 【手続補正書】

【提出日】平成30年11月6日(2018.11.6)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

## 【特許請求の範囲】

## 【請求項1】

プログラマブル出力周波数を有する発振器回路であって、

出力信号を出力するように構成された回路出力と、

入力端および出力端を有する第1の遅延セクションと、前記第1の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第1の遅延セクションは、前記第1の遅延セクションに供給される制御信号によって設定される可変遅延を供給するよう構成される。

前記第1の遅延セクションと前記回路出力との間に直列に電気的に接続された第2の遅延セクションと、前記第2の遅延セクションは、入力端および出力端を有し、前記第2の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第2の遅延セクションは、固定遅延を供給するよう構成される、

を備え、

前記出力信号は、前記第1の遅延セクションによる前記遅延および前記第2の遅延セクションによる前記遅延の関数である周波数を有する、

回路。

## 【請求項2】

前記第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネット

ワークと、前記第1のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える第2のRCネットワークとを備え、前記第1の遅延セクションの遅延は、前記第1のRCネットワークおよび前記第2のRCネットワークの前記可変キャパシタの容量に基づいて決定される、請求項1に記載の回路。

【請求項3】

前記制御信号は、前記第1のRCネットワークの前記可変キャパシタの前記容量を設定するように構成され、追加の制御信号は、前記第2のRCネットワークの前記可変キャパシタの前記容量を設定するように構成される、請求項2に記載の回路。

【請求項4】

前記第1の遅延セクションは、抵抗器および可変キャパシタを備えるRCネットワークを備え、前記第1の遅延セクションに供給される前記制御信号は、前記第1のRCネットワークの前記可変キャパシタの容量を設定するように構成され、前記第1の遅延セクションの遅延は、前記可変キャパシタの前記容量に基づいて決定される、請求項1に記載の回路。

【請求項5】

前記第1の遅延セクションは、複数のスイッチドキャパシタを備え、前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定するように構成される、請求項1に記載の回路。

【請求項6】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタは、ノードをDC電圧に電気的に接続させる、請求項5に記載の回路。

【請求項7】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタは、ノードを接地電位に電気的に接続させる、請求項5に記載の回路。

【請求項8】

前記制御信号は、nビットワードである、請求項5に記載の回路。

【請求項9】

前記第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネットワークを備える、請求項1に記載の回路。

【請求項10】

前記固定値容量成分の少なくとも1つのノードは、前記発振器回路の電源電圧より上にスイングするように構成される、請求項9に記載の回路。

【請求項11】

前記固定値容量成分の前記少なくとも1つのノードは、接地電位より下にスイングするように構成される、請求項10に記載の回路。

【請求項12】

前記第1の遅延セクションは、フィードバックループにおいて前記第2の遅延セクションを介して前記回路出力に電気的に接続される、請求項1に記載の回路。

【請求項13】

発振器回路であって、

出力信号を出力するように構成された回路出力と、

入力端および出力端を有する第1の遅延セクションと、前記第1の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネットワークと、前記第1のRCネットワークと直列に接続されたインバータと、前記インバータの出力と直列に接続され、かつ、抵抗器および可変キャパシタを備える第2のRCネットワークとを備える、

前記第1の遅延セクションの遅延を設定するために、前記第1のRCネットワークの少なくとも前記可変キャパシタに供給される少なくとも1つの制御信号と、

前記第1の遅延セクションと前記回路出力との間に直列に電気的に接続された第2の遅延セクションと、前記第2の遅延セクションは、入力端および出力端を有し、第2の遅延

セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第2の遅延セクションは、固定遅延を有する、

を備え、

前記出力信号は、前記第1の遅延セクションによる前記遅延および前記第2の遅延セクションによる前記遅延の関数である周波数を有し、前記回路出力は、前記第2の遅延セクションの前記出力端を備え得る、

回路。

#### 【請求項14】

前記第1の遅延セクションにおける前記第1のRCネットワークおよび前記第2のRCネットワーク中の前記可変キャパシタの各々は、複数のスイッチドキャパシタを備え、前記プログラマブル遅延段に供給される前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定するように構成される、請求項13に記載の回路。

#### 【請求項15】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、DC電圧に電気的に接続される、請求項14に記載の回路。

#### 【請求項16】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、接地電位に電気的に接続される、請求項14に記載の回路。

#### 【請求項17】

前記制御信号は、前記第1のRCネットワーク中の前記可変キャパシタに供給され、前記回路は、前記第2のRCネットワーク中の前記可変キャパシタに供給される追加の制御信号をさらに備える、請求項13に記載の回路。

#### 【請求項18】

前記第1の遅延セクションは、前記第2のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える少なくとも第3のRCネットワークをさらに備える、請求項13に記載の回路。

#### 【請求項19】

前記第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネットワークを備え、前記容量成分の少なくとも1つのノードは、前記発振器回路の電源電圧より上にスイングするように構成される、請求項13に記載の回路。

#### 【請求項20】

前記容量成分の前記少なくとも1つのノードは、接地電位より下にスイングするように構成される、請求項19に記載の回路。

#### 【請求項21】

発振器回路であって、

第1のインバータ段と、

前記第1のインバータ段の出力に電気的に接続された入力を有する第2のインバータ段と、前記第2のインバータ段は、前記発振器回路の出力信号のための出力を有する、

容量素子に接続された抵抗素子を備える固定遅延段と、前記固定遅延段は、前記第2のインバータ段の前記入力と前記出力との間に電気的に接続される、

少なくとも1つの可変遅延段に供給される制御信号によって設定される遅延を有する前記少なくとも1つの可変遅延段と、前記少なくとも1つの可変遅延段は、前記抵抗素子および前記キャパシタ素子を接続する前記固定遅延段におけるノードと、前記第1のインバータ段の入力との間に電気的に接続される、

を備え、

前記出力信号の周波数は、前記少なくとも1つの可変遅延段の遅延に依存する、回路。

#### 【請求項22】

前記少なくとも1つの可変遅延段と直列に接続され、かつ、少なくとも1つの追加の可

変遅延段に供給される制御信号に依存する遅延を有する前記少なくとも1つの追加の可変遅延段をさらに備える、請求項21に記載の回路。

【請求項23】

前記抵抗素子および前記キャパシタ素子を接続する前記ノードにおける電圧レベルは、前記発振器回路の動作中、前記発振器回路の電源電圧より上および下に、および接地電位より上および下にスイングする、請求項21に記載の回路。

【請求項24】

前記少なくとも1つの可変遅延段は、抵抗器および可変キャパシタを備え、前記少なくとも1つの可変遅延段に供給される前記制御信号は、前記可変キャパシタの容量を設定し、前記少なくとも1つの可変遅延段の前記遅延は、前記可変キャパシタの前記容量に依存する、請求項21に記載の回路。

【請求項25】

前記少なくとも1つの可変遅延段は、複数のスイッチドキャパシタを備え、前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に設定する、請求項21に記載の回路。

【請求項26】

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、DC電圧にまたは接地電位に電気的に接続される、請求項25に記載の回路。

【請求項27】

前記固定遅延段の前記容量素子の少なくとも1つのノードは、前記発振器回路の電源電圧より上、および、接地電位より下にスイングするように構成される、請求項21に記載の回路。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0060

【補正方法】変更

【補正の内容】

【0060】

[0067] 上の説明は、特定の実施形態の態様がどのように実施され得るかの例とともに本開示の様々な実施形態を例示する。上の例は、唯一の実施形態であるとみなされるべきでなく、以下の特許請求の範囲によって定義されるような、特定の実施形態の柔軟性および利点を例示するために提示されている。上の開示および以下の特許請求の範囲に基づいて、他の配置、実施形態、実施、および同等物は、特許請求の範囲によって定義される本開示の範囲から逸脱することなく用いられ得る。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

[C1]

プログラマブル出力周波数を有する発振器回路であつて、

入力端および出力端を有する第1の遅延セクションと、前記第1の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第1の遅延セクションは、前記第1の遅延セクションに供給される制御信号によって設定される可変遅延を有する、

前記第1の遅延セクションと直列に電気的に接続された第2の遅延セクションと、前記第2の遅延セクションは、入力端および出力端を有し、前記第2の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第2の遅延セクションは、固定遅延を有する、

前記第1の遅延セクションおよび前記第2の遅延セクションによる前記遅延の関数である周波数を有する出力信号のための回路出力と、前記回路出力は、前記第2の遅延セクションの前記出力端を備える、

回路。

[C2]

前記第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネット

ワークと、前記第1のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える第2のRCネットワークとを備え、前記第1の遅延セクションの遅延は、前記第1のRCネットワークおよび前記第2のRCネットワークの前記可変キャパシタの容量に基づいて決定される、C1に記載の回路。

[C3]

前記制御信号は、前記第1のRCネットワークの前記可変キャパシタの前記容量を設定し、追加の制御信号は、前記第2のRCネットワークの前記可変キャパシタの前記容量を設定する、C2に記載の回路。

[C4]

前記第1の遅延セクションは、抵抗器および可変キャパシタを備えるRCネットワークを備え、前記第1の遅延セクションに供給される前記制御信号は、前記第1のRCネットワークの前記可変キャパシタの容量を設定し、前記第1の遅延セクションの遅延は、前記可変キャパシタの前記容量に基づいて決定される、C1に記載の回路。

[C5]

前記第1の遅延セクションは、複数のスイッチドキャパシタを備え、前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定する、C1に記載の回路。

[C6]

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタは、ノードをDC電圧に電気的に接続させる、C5に記載の回路。

[C7]

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタは、ノードを接地電位に電気的に接続させる、C5に記載の回路。

[C8]

前記制御信号は、nビットワードである、C5に記載の回路。

[C9]

前記第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるRCネットワークを備える、C1に記載の回路。

[C10]

前記固定値容量成分の少なくとも1つのノードは、前記発振器回路の電源電圧より上にスイングする、C9に記載の回路。

[C11]

前記固定値容量成分の前記少なくとも1つのノードは、接地電位より下にスイングする、C10に記載の回路。

[C12]

前記第1の遅延セクションは、フィードバックループにおいて前記第2の遅延セクションを介して前記回路出力に電気的に接続される、C1に記載の回路。

[C13]

発振器回路であって、

入力端および出力端を有する第1の遅延セクションと、前記第1の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第1の遅延セクションは、抵抗器および可変キャパシタを備える第1のRCネットワークと、前記第1のRCネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える第2のRCネットワークとを備える、

前記第1の遅延セクションの遅延を設定するために、前記第1のRCネットワークの少なくとも前記可変キャパシタに供給される少なくとも1つの制御信号と、

前記第1の遅延セクションと直列に電気的に接続された第2の遅延セクションと、前記第2の遅延セクションは、入力端および出力端を有し、第2の遅延セクションは、前記入力端と前記出力端との間の負の利得を有し、前記第2の遅延セクションは、固定遅延を有する、

前記第1の遅延セクションおよび前記第2の遅延セクションによる前記遅延の関数である周波数を有する出力信号のための回路出力と、前記回路出力は、前記第2の遅延セクションの前記出力端を備え得る、

回路。

[ C 1 4 ]

前記第1の遅延セクションにおける前記第1のR C ネットワークおよび前記第2のR C ネットワーク中の前記可変キャパシタの各々は、複数のスイッチドキャパシタを備え、前記プログラマブル遅延段に供給される前記制御信号は、前記複数のスイッチドキャパシタの各々をON状態またはOFF状態に選択的に設定する、C 1 3に記載の回路。

[ C 1 5 ]

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、DC電圧に電気的に接続される、C 1 4に記載の回路。

[ C 1 6 ]

スイッチドキャパシタが前記ON状態にあるとき、前記スイッチドキャパシタのノードは、接地電位に電気的に接続される、C 1 4に記載の回路。

[ C 1 7 ]

前記制御信号は、前記第1のR C ネットワーク中の前記可変キャパシタに供給され、前記回路は、前記第2のR C ネットワーク中の前記可変キャパシタに供給される追加の制御信号をさらに備える、C 1 3に記載の回路。

[ C 1 8 ]

前記第1の遅延セクションは、第2のR C ネットワークと直列に接続され、かつ、抵抗器および可変キャパシタを備える少なくとも第3のR C ネットワークをさらに備える、C 1 3に記載の回路。

[ C 1 9 ]

前記第2の遅延セクションは、固定値抵抗成分および固定値容量成分を備えるR C ネットワークを備え、前記容量成分の少なくとも1つのノードは、前記発振器回路の電源電圧より上にスイングする、C 1 3に記載の回路。

[ C 2 0 ]

前記容量成分の前記少なくとも1つのノードは、接地電位より下にスイングする、C 1 9に記載の回路。

[ C 2 1 ]

発振器回路であって、

第1のインバータ段と、

前記第1のインバータ段の出力に電気的に接続された入力を有する第2のインバータ段と、前記第2のインバータ段は、前記発振器回路の出力信号のための出力を有する、

容量素子に接続された抵抗素子を備えるR C 回路と、前記R C 回路は、前記第2のインバータ段の前記入力と前記出力との間に電気的に接続される、

少なくとも1つの可変遅延段に供給される制御信号によって設定される遅延を有する前記少なくとも1つの可変遅延段と、前記少なくとも1つの可変遅延段は、前記抵抗素子および前記キャパシタ素子を接続する前記R C 回路におけるノードと、前記第1のインバータ段の入力との間に電気的に接続される、

を備え、

前記出力信号の周波数は、前記少なくとも1つの可変遅延段の遅延に依存する、

回路。

[ C 2 2 ]

前記少なくとも1つの可変遅延段と直列に接続され、かつ、少なくとも1つの追加の可変遅延段に供給される制御信号に依存する遅延を有する前記少なくとも1つの追加の可変遅延段をさらに備える、C 2 1に記載の回路。

[ C 2 3 ]

前記抵抗素子および前記キャパシタ素子を接続する前記ノードにおける電圧レベルは、

前記発振器回路の動作中、前記発振器回路の電源電圧より上および下に、および接地電位より上および下にスイングする、C 2 1 に記載の回路。

[ C 2 4 ]

前記少なくとも 1 つの可変遅延段は、抵抗器および可変キャパシタを備え、前記少なくとも 1 つの可変遅延段に供給される前記制御信号は、前記可変キャパシタの容量を設定し、前記少なくとも 1 つの可変遅延段の前記遅延は、前記可変キャパシタの前記容量に依存する、C 2 1 に記載の回路。

[ C 2 5 ]

前記少なくとも 1 つの可変遅延段は、複数のスイッチドキャパシタを備え、前記制御信号は、前記複数のスイッチドキャパシタの各々を ON 状態または OFF 状態に設定する、C 2 1 に記載の回路。

[ C 2 6 ]

スイッチドキャパシタが前記 ON 状態にあるとき、前記スイッチドキャパシタのノードは、DC 電圧にまたは接地電位に電気的に接続される、C 2 5 に記載の回路。

[ C 2 7 ]

前記 RC 回路の前記容量素子の少なくとも 1 つのノードは、発振器回路の電源電圧より上、および、接地電位より下にスイングする、C 2 1 に記載の回路。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2017/017518 |

|---------------------------------------------------|

|                                                                       |

|-----------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. H03K3/03 H03B5/20<br>ADD. |

|-----------------------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                             |

|-------------------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>H03K H03B H03L |

|-------------------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) |

|------------------------------------------------------------------------------------------------------------------------------|

|                        |

|------------------------|

| EPO-Internal, WPI Data |

|------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                    | Relevant to claim No.               |

|-----------|-------------------------------------------------------------------------------------------------------|-------------------------------------|

| X         | WO 2013/141837 A1 (SUMESAGLAM TANER [US])<br>26 September 2013 (2013-09-26)                           | 1-5,8,9,<br>12,21,24                |

| A         | paragraph [0024] - paragraph [0035];<br>figures 1-5<br>-----                                          | 10,11,<br>19,23,27                  |

| X         | US 2008/136545 A1 (FAYNEH EYAL [IL] ET AL)<br>12 June 2008 (2008-06-12)                               | 1,6,7,<br>13-18,<br>21,22,<br>25,26 |

| A         | paragraph [0009]; figures 1-3<br>paragraph [0014] - paragraph [0015]<br>-----                         | 10,11,<br>19,23,27                  |

| A         | US 2013/320955 A1 (KRATYUK VOLODYMYR [US]<br>ET AL) 5 December 2013 (2013-12-05)<br>figure 2<br>----- | 1-27                                |

|                                                            |

|------------------------------------------------------------|

| Further documents are listed in the continuation of Box C. |

|------------------------------------------------------------|

|                          |

|--------------------------|

| See patent family annex. |

|--------------------------|

|                                           |

|-------------------------------------------|

| * Special categories of cited documents : |

|-------------------------------------------|

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

|                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |

|-----------------------------------------------|

| "&" document member of the same patent family |

|-----------------------------------------------|

|                                                           |

|-----------------------------------------------------------|

| Date of the actual completion of the international search |

|-----------------------------------------------------------|

|                                                    |

|----------------------------------------------------|

| Date of mailing of the international search report |

|----------------------------------------------------|

|               |

|---------------|

| 21 April 2017 |

|---------------|

|            |

|------------|

| 03/05/2017 |

|------------|

|                                      |

|--------------------------------------|

| Name and mailing address of the ISA/ |

|--------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 |

|------------------------------------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| Authorized officer |

|--------------------|

|                    |

|--------------------|

| Mesplede, Delphine |

|--------------------|

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2017/017518

| Patent document cited in search report | Publication date | Patent family member(s)                                | Publication date                       |

|----------------------------------------|------------------|--------------------------------------------------------|----------------------------------------|

| WO 2013141837 A1                       | 26-09-2013       | CN 104285375 A<br>US 2013271227 A1<br>WO 2013141837 A1 | 14-01-2015<br>17-10-2013<br>26-09-2013 |

| US 2008136545 A1                       | 12-06-2008       | NONE                                                   |                                        |

| US 2013320955 A1                       | 05-12-2013       | NONE                                                   |                                        |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DJ,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JP,KE,KG,KH,KN,KP,KR,KW,KZ,LA,LC,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ

(74)代理人 100184332

弁理士 中丸 慶洋

(72)発明者 ワン、ケビン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ソン、チャオ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 シバクマー、シャム

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

F ターム(参考) 5J043 LL01 LL04

5J081 AA08 AA09 CC07 CC22 EE03 EE04 EE19 KK02 KK07 KK14