(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4260632号

(P4260632)

(45) 発行日 平成21年4月30日(2009.4.30)

(24) 登録日 平成21年2月20日(2009.2.20)

(51) Int.Cl.

G06F 13/16 (2006.01)

H04N 5/44 (2006.01)

F 1

G06F 13/16 510A

H04N 5/44 Z

請求項の数 3 (全 8 頁)

(21) 出願番号 特願2003-555795 (P2003-555795)

(86) (22) 出願日 平成14年12月11日 (2002.12.11)

(65) 公表番号 特表2005-514814 (P2005-514814A)

(43) 公表日 平成17年5月19日 (2005.5.19)

(86) 國際出願番号 PCT/US2002/039503

(87) 國際公開番号 WO2003/055203

(87) 國際公開日 平成15年7月3日 (2003.7.3)

審査請求日 平成17年12月8日 (2005.12.8)

(31) 優先権主張番号 10/024,981

(32) 優先日 平成13年12月19日 (2001.12.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 501263810

トムソン ライセンシング

Thomson Licensing

フランス国, エフ-92100 プロ

ニュ ビヤンクール, ケ アルフォンス

ル ガロ, 46番地

46 Quai A. Le Gallio

, F-92100 Boulogne-

Billancourt, France

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

最終頁に続く

(54) 【発明の名称】信号制御ラインを共有する装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリと、装置の少なくとも一つの動作を制御する制御回路とを含む第1の回路基板と、

制御ラインを介して前記第1の回路基板と動作可能に結合された、前記制御ラインに結合されたコントローラを含む第2の回路基板とを含み、

前記メモリと前記制御回路は前記制御ラインに結合され、

前記コントローラは、前記装置のオフ状態において前記制御回路に影響を与えることなく前記制御ラインを介して前記メモリから動作データを読み出し、前記装置のオン状態において前記制御ラインを介して前記制御回路に制御信号を送信して、読み出した前記動作データに応じて前記制御回路を制御する装置。

## 【請求項 2】

前記装置の前記少なくとも1つの動作は偏向動作を含む、請求項1記載の装置。

## 【請求項 3】

オン・オフ状態を有するテレビ信号レシーバを動作させる方法であって、

制御ラインを介して結合された第1と第2の回路基板であって、前記第1の回路基板はその上に含まれ前記制御ラインに結合されたメモリデバイスと制御回路とを有し、前記第2の回路基板はその上に含まれ前記制御ラインに結合されたコントローラを有する第1と第2の回路基板とを設けるステップと、

前記テレビ信号レシーバが前記オフ状態にあるとき、前記コントローラを用いて、前記

制御回路に影響することなく、前記制御ラインを介して前記メモリデバイスから動作データを読み出すステップと、

前記テレビ信号レシーバが前記オン状態にあるとき、前記読み出した動作データに応じて、前記コントローラから、前記制御回路に、前記制御ラインを介して、制御信号を送信するステップとを含む方法。

【発明の詳細な説明】

【発明の詳細な説明】

【0001】

本発明は、テレビ信号レシーバ等の、複数の回路基板にマウントされた部品からなる電気機器に関し、特に、信号制御ラインを共有可能とすることにより、該機器の回路基板間で必要とされる接続の数を減らす方法に関する。 10

【0002】

テレビ信号レシーバ等の電気機器は、多くの場合一以上の回路基板を含む。各回路基板は、様々な機器の動作を実行可能とする集積回路（I C）や他の要素等のマウントされた電気部品を含む。テレビ信号レシーバの従来のデザインは、多くの場合、単一の回路基板のみを使っていた。これらの従来のデザインでは、基板面積を最大限利用するというインセンティブが働いていた。しかし、単一の回路基板のみが使用されていたので、他の回路基板との接続に関する問題はなかった。

【0003】

一方、テレビ信号レシーバの現在の設計には、複数の回路基板を使用することがある。 20 単一基板と比較して、複数の回路基板を使用すると、回路設計をモジュール化できるため特に魅力的である。特に、単一回路基板のみを使用する場合に頻発するように、異なる基盤セクションを全レシーバ回路のレイアウトを再構成することなくリデザインできる。さらに、複数の回路基板を使用すると、一グループの回路に片面基板、他の回路に多層基板を使用できる。

【0004】

長所にもかかわらず、複数基板を使用すると、異なるボード間の接続に関する問題が発生することがある。特に、回路基板間の接続をするためのコネクター（例えば、ピン）の数を減らすことが望ましい。コネクターの数を減らすことは、各コネクターのコストが無視できないので、特に所望されている。このことは、製品のコストが競合間のドライビングフォースであり、生産数量が大きいので製品一台あたりの小さなコストが重要であるコンシューマエレクトロニクス産業などの特定の産業において、非常に重要となる。したがって、テレビ信号レシーバなどの機器の回路基板間に必要とされる接続数を減らす技術が必要となる。本発明はこれらの問題等を解決するものである。 30

【0005】

本発明によると、テレビ信号レシーバ等の装置は第1と第2の回路基板を含む。第1の回路基板はメモリ等の第1の電子デバイスと、装置の少なくとも一つの機能を制御する制御回路等の第2の電子デバイスとを含む。第2の回路基板は制御ラインを介して第1の回路基板に動作可能に結合している。第2の回路基板は、第1と第2の信号フォーマットにより第1と第2の制御信号をそれぞれ生成するコントローラを含む。制御ラインは、装置が第1の動作状態にあるとき、第1の制御信号をコントローラから第1のデバイスへ送信し、装置が第2の動作状態にあるとき第2の制御信号をコントローラから制御回路へ送信する。前記の装置により実行される方法もここに開示される。 40

【0006】

添付した図面とともに本発明の実施形態の以下の説明を参照すれば、上記の本発明の特徴と長所等、およびそれらの達成の仕方はより明らかとなり、本発明をよりよく理解できるであろう。

【0007】

ここに示した例示は、本発明の好ましい実施形態を示すものであり、そのような例示は本発明の範囲をいかなる態様においても限定するものと解してはならない。 50

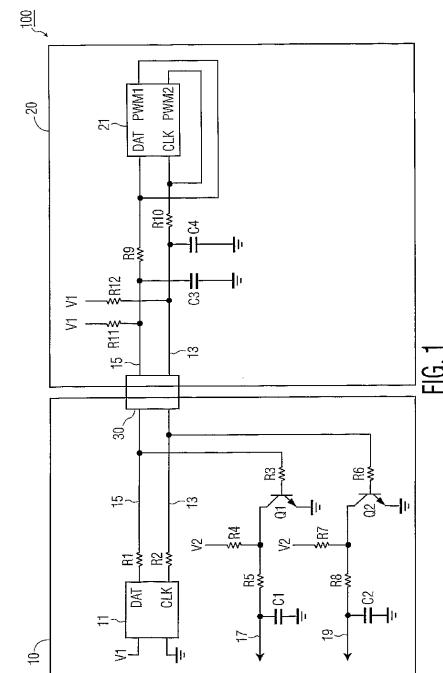

## 【0008】

図面を参照して、特に図1を参照して、本発明を実施するのに好適な装置100の関係する部分の図面が示されている。例示と説明の目的において、図1の装置100はテレビ信号レシーバとして表現されている。しかし、本発明の原理は、複数の回路基板を使用する他のタイプの電子機器に適用してもよいことを、ここに特に述べておく。

## 【0009】

図1のレシーバ100は、第1の回路基板10、第2の回路基板20、および基板コネクター30を含む。一例としての実施形態によると、第1の回路基板10は、レシーバ100の電源と偏向機能に関係する動作を可能とし、第2の回路基板20は、レシーバ100の信号処理機能に関係する動作を可能とする。第1の基板10は第2の回路基板20に基板コネクター30を経由して電気的に接続されている。

10

## 【0010】

第1の回路基板10は、レシーバ100の偏向動作を制御するために使用される電圧データ等であるデータを記憶する不揮発性メモリとして動作する、電気的消去可能プログラマブルリードオンリーメモリ(EEPROM)11を含む。EEPROM11は、クロック(CLK)端子とデータ(DAT)端子を含み、この一例としての実施形態においては3.3Vである電源V1により電力を供給されている。CLK端子はシリアルクロックライン(SCL)13に電気的に結合されており、DAT端子はシリアルデータライン(SDL)15に電気的に結合されている。一実施形態によると、SCL13とSDL15は、集合として集積回路間(IIC、通常は「IスクエアードC」と発音する)バスを表し、バスラインまたは制御ラインとして参照される。

20

## 【0011】

様々なICの間の制御信号とデータ信号を転送するIICバスのフォーマットと仕様は、当業者には周知である。一般的に、IICバスは、二つ以上のICがバス経路上で通信する2送信媒体、2方向デジタルバスである。「マスター」動作モードで動いているICは、バス上のデータ転送動作を開始し、データ転送を許すためのクロック信号を生成する。「スレーブ」動作モードで動いているICは、マスターICにより動作させられている、またはマスターICに通信しているICであり、スレーブICはデータを送信するか受信するかを指示されている。各ICはそれ自身のユニークなアドレスを持ち、マスターICが通信を開始および終了する。SCL13とSDL15により表されるIICバスに関するさらに詳細は後で説明する。

30

## 【0012】

第1の回路基板10は8つの抵抗R1-R8、2つのキャパシタC1、C2、2つのトランジスタQ1、Q2も含む。抵抗R1、R2は、SDL15とSCL13それぞれに抵抗を生成するために設けられている。本実施形態において、抵抗R1とR2は各々1Kオームの抵抗を与える。図1に示したように、SCL13とSDL15は、2つの分離した制御チャンネルを設けるため、第1の回路基板10内でタップされている。特に、SDL15は、参照番号17で表された出力信号を生成する第1の制御チャンネルを設けるためにタップされ、SCL13は、参照番号19で表される出力信号を生成する第2の制御チャンネルを設けるためにタップされている。出力信号17と19は、レシーバ100の偏向動作を制御する。第1と第2の制御チャンネルをなす回路は、制御回路としてここに集合的に参照される。

40

## 【0013】

第1の制御チャンネルは、抵抗R3-R5、キャパシタC1、トランジスターQ1を含む。抵抗R3は、SDL15とトランジスタQ1のベースジャンクションの間に抵抗を設け、好ましくは10Kオームである。トランジスターQ1はn型バイポーラジャンクショントランジスター(BJT)として好ましくは実施される。トランジスターQ1のコレクタージャンクションは、第1の制御チャンネルに出力バスを設ける。抵抗R4は、プルアップ抵抗として動作し、電源V2に電気的に結合しており、一実施形態によると5.1ボルトである。抵抗R4の好ましい値は1Kオームである。抵抗R5とキャパシタC1は、

50

時定数を決定し、好みしくはそれぞれ  $1\text{ K}\Omega$  と  $820\text{ nF}$  の値を有する。本実施形態によると、出力信号 17 はフライバックトランス（図示せず）の電圧を決めるのに使用され、レシーバ 100 の偏向動作で使用される。

#### 【0014】

第 2 の制御チャンネルは、抵抗 R6 - R8、キャパシター C2、トランジスタ Q2 を含む。抵抗 R6 は SCL13 とトランジスター Q2 のベースジャンクションの間に抵抗を設け、好みしい値は  $10\text{ K}\Omega$  である。トランジスター Q2 は n 型 BJT として実施されることが好みしい。トランジスター Q2 のコレクタージャンクションは、第 2 の制御チャンネルのために出力バスを設ける。抵抗 R7 はプルアップ抵抗として動作し、電源 V2 に電気的に結合しており、前述のとおり  $5.1\text{ V}$  であることが好みしい。抵抗 R7 の好みしい値は  $1\text{ K}\Omega$  である。抵抗 R8 とキャパシター C2 は時定数を決定し、それぞれ好みしい値は  $1\text{ K}\Omega$  と  $820\text{ nF}$  である。本実施形態によると、出力信号 19 はフライバックトランス（図示せず）の電圧を制御するのに使用される。抵抗 R3 と R6 は、IIC バスのローディングを避けるため十分高い抵抗値を有するように選択されることが好みしい。10

#### 【0015】

第 2 の回路基板 20 は、レシーバ 100 の様々な動作を制御するマイクロコントローラ 21 を含む。第 1 の回路基板 10 の EEPROM11 のように、マイクロコントローラ 21 も、CLK 端子と DAT 端子を含む。CLK 端子は SCL13 に電気的に結合しており、DAT 端子は SDL15 に電気的に結合している。図 1 には明示的には示していないが、マイクロコントローラ 21 は電源 V1 のような電源に電気的に接続されている。「マイクロコントローラ」と「コントローラ」という用語は、ここでは交換可能に使用される。20

#### 【0016】

マイクロコントローラ 21 は、第 1 と第 2 の PWM 信号をそれぞれ出力する第 1 と第 2 のパルス幅変調（PWM）端子（PWM1 と PWM2）も含む。PWM1 と PWM2 端子は、SDL15 と SCL13 にそれぞれ電気的に結合しており、第 1 と第 2 の PWM 信号を第 1 の回路基板 10 の第 1 と第 2 の制御チャンネルにそれぞれ与える。したがって、第 1 の PWM 信号は出力信号 17 を生成するために使用され、第 2 の PWM 信号は出力信号 19 を生成するために使用される。PWM 信号を好みしい実施形態において使用するが、もちろんこの他のフォーマットの信号を使用してもよい。30

#### 【0017】

第 2 の回路基板 20 は 4 つの抵抗 R9 - R12、2 つのキャパシター C3 と C4 を含む。抵抗 R9 とキャパシタ C3 は、SDL15 からラジオ周波数の干渉を除去するように動作し、一方、抵抗 R10 とキャパシタ C4 は SCL13 からラジオ周波数の干渉を除去するように動作する。一実施形態によると、抵抗 R9 と R10 は各々  $1\text{ K}\Omega$  の値を有し、キャパシタ C3 と C4 は各々  $100\text{ pF}$  の値を有する。抵抗 R11 と R12 はプルアップ抵抗として動作し、前に  $3.3\text{ V}$  と示した電源 V1 に電気的に結合されている。抵抗 R11 と R12 は各々  $10\text{ K}\Omega$  の値を有する。

#### 【0018】

動作において、IIC バス（すなわち、SCL13 と SDL15）は、マイクロコントローラ 21 の 2 つの異なった動作の間で共有される。特に、レシーバ 100 が第 1 の動作状態（すなわち、レシーバ 100 が電源に接続されているが、OFF 状態であるとき）であるとき、マイクロコントローラ 21 はマスター IIC として動作し、スレーブ IIC として動作する EEPROM11 からデータを読み出すために、第 1 の制御信号を EEPROM に SCL13 と SDL15 を経由して送信する。DAT ピンそれ自体は入出力ラインであり、CLK それ自体は出力ピンとして動作する。PWM1 と PWM2 ピンは、入力ラインとして動作するか、高インピーダンス状態である。ピンの状態は、例えばデータ指示抵抗を用いて、現動作状態に応じてマイクロコントローラにより決定される。マイクロコントローラ 21 と EEPROM11 は、第 1 の動作状態の間、スタンバイ電源、すなわち電源 V1 から電力を受ける。一実施形態によると、マイクロコンピュータ 21 により EEPROM

ROM11から読み出されたデータは、レシーバ100の偏向動作を制御するために使用する電圧データを含む。

【0019】

データ読み出し動作の間に、SCL13はマイクロコントローラ21からEEPROM11へクロック信号を伝播する。SDL15は、シリアルデジタルトランザクションを用いてデータを転送するために使用される。普通、1以上のビットが、アクノレッジビットとして使用される。一例のデザインによると、SCL13とSDL15が両方とも論理ハイ状態にあるとき、マイクロコントローラ21とEEPROM11の間でデータを転送することはできない。SCL13が論理ハイ状態にあるとき、SDL15上での論理ハイ状態から論理ロー状態への遷移は、IICバス上のデジタルデータの交換のためにスタート条件を示す。逆に、SCL13が論理ハイ状態にあるとき、SDL15上での論理ロー状態から論理ハイ状態への遷移は、ストップ条件を示す。一実施形態において、マイクロコントローラ21は、SDL15上で転送されるデジタルデータの各ビットの1クロックパルスを生成し、SDL15上の論理状態は、SCL13上のクロック信号が論理ロー状態にあるときにのみ、変化することができる。もちろん、前述の信号プロトコル以外の信号プロトコルを使用してもよい。マイクロコントローラ21がデータをEEPROM11から読み出すとき、マイクロコントローラ21のPWM1端子とPWM2端子は高インピーダンス状態であり、抵抗R3とR6は第1と第2の制御チャンネルがSCL13とSDL15をローディングしないようにする。第1の動作状態の間に、トランジスタQ1とQ2の集まりに与えられたV2はロー状態であり、それゆえ、Q1とQ2への信号の供給は、端子17と19に関連した制御回路になんら効果を及ぼさない。

10

【0020】

レシーバ100が第2の動作状態（すなわち、レシーバ100が電源に接続されており、ON状態であるとき）にあるとき、マイクロコントローラ21のDATとCLK端子はハイインピーダンス状態にあり、PWM1とPWM2端子は第1と第2のPWM信号をそれぞれ出力するように使用されてもよい。第1と第2のPWM信号は、ここで第2の制御信号と参照されてもよい。PWM1端子は、SDL15に電気的に結合しており、出力信号17の生成を可能とするために、第1のPWM信号を第1の回路基板10の第1の制御チャンネルに与える。同様に、PWM2端子は、SCL13に電気的に結合しており、出力信号19の生成を可能とするために、第2のPWM信号を第1の回路基板10の第2の制御チャンネルに与える。本実施形態において、第1と第2のPWM信号は、レシーバ100がOFF状態のときに、EEPROM11から読み出された電圧データにより、マイクロコンピュータ21により生成される。前述のように、SCL13とSDL15は、マイクロコントローラ21の2つの異なる動作の間で共有されている。2つの動作の間に異なるタイプの信号が送信される、二つの異なる動作の間に使用される二つの異なる構成要素の間で、二つのラインを共有することにより、基板10と20の間で必要となるコネクターの数が削減される。

20

【0021】

第1と第2のPWM信号が第1の回路基板10の制御回路に送信されるとき、上述のとおり、EEPROM11が不注意に書き込まれ、記憶しているデータを破損するという潜在的な問題がある。特に、PWM信号がIICバス上を送信されるとき、もしスタート条件が生成されれば（すなわち、SCL13が論理ハイ状態にあるときSDL15が論理ハイ状態から論理ロー状態に遷移するとき）、およびPWM信号のフェージングにより生成されたアドレス情報がEEPROM11のアドレス情報に対応するとき、EEPROM11は、マイクロプロセッサ21により誤って書き換えられることがある。上記に対応するそのような信号が生じるポテンシャルはあまりない。しかし、この潜在的な問題を避けるひとつのアプローチは、EEPROM11の複数の場所に冗長的にデータを記憶することである。一実施形態によると、与えられたデータの単位は、EEPROM11の5つの異なるメモリ位置に冗長的に記憶することができる。その後、データが読み出されるとき、データを読んでいる構成要素（例えばプロセッサ21）は、データが破損したか判断

30

40

50

する統計的閾値を適用する。例えば、データがEEPROM11内の五つの異なった位置に記憶されたとき、そのデータを読んでいる構成要素は、五つのメモリ位置のうち3つが同じデータであれば、そのデータが有効であると判断してもよい。他の統計的閾値ももちろん使用可能である。

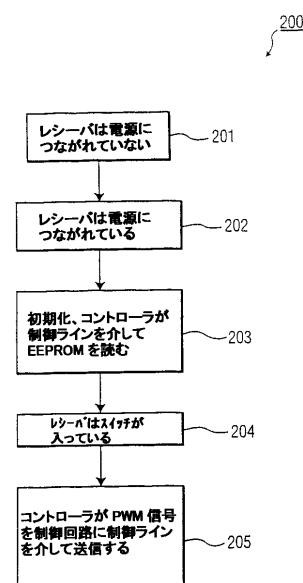

【0022】

図2を参照して、本発明を実施する一例としてのステップが示されたフローチャート200が示されている。例示と説明の目的で、図2のステップを図1のテレビ信号レシーバ100を参照して説明する。

【0023】

ステップ201において、レシーバ100は電源が入っていない状態である。すなわち、レシーバ100は、家庭の電源プラグ等の電源に接続されていない。ステップ202において、レシーバ100は電源に接続され（例えば、プラグが差し込まれる）、しかしスイッチはONになっていない。すなわち、レシーバ100はステップ202で第1の動作状態に入る。前に示したとおり、マイクロコントローラ21とEEPROM11等のレシーバ100の構成要素は、第1の動作状態の間、スタンバイ電源すなわち電源V1から、電力を受け取る。

【0024】

ステップ202で電源に接続されるのに応じて、プロセスフローはステップ203に進み、レシーバ100は初期化プロセスを実行する。特に、この初期化プロセスの一部として、マイクロコントローラ21はマスターICとして動作し、EEPROM11にSCL13とSDL15を経由して、スレーブICとして動作する、EEPROM11からデータを読むために、第1の制御信号を送信する。一実施形態によると、マイクロコントローラ21によりEEPROM11から読み出されたデータは、レシーバ100の偏向動作を制御するのに使用される電圧データを含む。マイクロコントローラ21は、内部メモリ（図示せず）に読み出したデータを保存し、レシーバ100がプログラミングされている、すなわちパワーが供給されている限り、そこに保持される。

【0025】

次に、ステップ204で、レシーバ100が、例えば、ハンドヘルドのリモートコントロールユニットのような入力ターミナルへのユーザのインプットにより、スイッチオンされる。前に述べたとおり、レシーバ100は、電源に接続されスイッチがONになっているとき、第2の動作状態にある。したがって、ステップ204で、レシーバ100は第2の動作状態に入る。第2の動作状態の間、プロセスフローはステップ205に進み、マイクロコントローラ21は第2の制御信号、すなわち第1と第2のPWM信号を、第1の回路基板10の制御回路に送信する。すなわち、PWM1端子は、第1のPWM信号をSDL15に出力し、第1のPWM信号を第1の回路基板10の第1の制御チャンネルに与え、出力信号17の生成を可能とする。同様に、PWM2端子は第2のPWM信号をSCL13に出力し、第2のPWM信号を第1の回路基板10の第2の制御チャンネルに与え、出力信号19の生成を可能とする。前に示したとおり、第1と第2のPWM信号は、ステップ203でEEPROM11から読み出した電圧データにより、マイクロコントローラ21により生成されてもよい。前述のように、SCL13とSDL15は、マイクロコントローラ21の二つの異なる動作の間で共有される。

【0026】

本発明はテレビ信号レシーバに関して説明したが、本発明はディスプレイ装置を有する有しないに係らず、様々なシステムに適用可能である。ここに使用した「テレビ信号レシーバ」または「レシーバ」という用語は、ディスプレイデバイスを含むテレビセットやモニターを含む、しかしこれには限定されない、様々なタイプの装置とシステム、およびセットトップボックス、ビデオテープレコーダ（VTR）、デジタルバーサタイルディスク（DVD）プレーヤ、ビデオゲームボックス、パーソナルビデオレコーダ（PVR）等のシステムや装置、ディスプレイデバイスを含まないかもしれない他の装置を含む事を意図している。

10

20

30

40

50

## 【0027】

この発明は好ましいデザインを有するものとして説明したが、本発明はこの開示の精神と範囲内においてさらに変更することができる。例えば、ここに開示したコントロールラインは、装置の異なる動作状態において、メモリや偏向回路以外の機器を制御するために使用することができる。この出願は、本発明の一般的な原理を用いた本発明のバリエーション、使用、または適合をカバーすることを意図している。さらに、この出願は、本発明が関係し、添付したクレームの限定に当てはまる前記技術分野における知られまたは慣用されたプラクティスになるように、本開示からのそのようなかい離をカバーすることを意図している。

## 【図面の簡単な説明】

10

## 【0028】

【図1】本発明を実施するのに好適な装置の関連する部分の図である。

【図2】本発明を実施するステップを示すフローチャートである。

【図1】

【図2】

---

フロントページの続き

(72)発明者 テスティン, ウィリアム, ジョン

アメリカ合衆国, インディアナ州 46236, インディアナポリス, ウィノナ・ドライブ 68

08

審査官 多賀 実

(56)参考文献 特開平04-072970 (JP, A)

特表平09-509814 (JP, A)

国際公開第98/032277 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G06F12/00-12/06

G06F13/16

H04N5/44